Результат интеллектуальной деятельности: СПОСОБ ИСПЫТАНИЙ ЭЛЕКТРОННОЙ СХЕМЫ НА ОТКАЗОУСТОЙЧИВОСТЬ И СТЕНД ДЛЯ ЕГО РЕАЛИЗАЦИИ

Вид РИД

Изобретение

Изобретение относится к испытаниям на надежность. Технический результат - автоматизация испытаний, сокращение времени испытаний, имитация отказа элементов, уменьшение вероятности отказов схемы за счет выявления элементов, отказ которых приводит к неработоспособному состоянию электронной схемы.

Элементы электронных схем обладают высокой надежностью, их отказы происходят редко. Отказоустойчивость электронных схем оценивают с помощью расчетных методов, на основе математических моделей надежности элементов и их взаимных связей друг с другом.

Известен способ испытания радиоэлектронной аппаратуры на надежность. Сущность способа заключается в проведении определенным образом замеров выходного параметра РЭА, позволяющих промоделировать и повысить ее отказоустойчивость к воздействию климатических и механических внешних дестабилизирующих факторов, оптимизировать ее параметрическую надежность. Для получения целевых функций задач оптимизации используются регрессионные полиномиальные модели, построенные методом наименьших квадратов по данным испытаний. Затем осуществляют в одном случае направленный градиентный поиск области оптимума и вычислительный эксперимент, в другом - статистическое моделирование и повторное построение регрессионной полиномиальной модели и снова вычислительный эксперимент. В результате подбирают номинальные значения параметров ЭРЭ и их погрешности, при которых надежность РЭА максимальна, а стоимость не превышает заданную величину (Заявка на изобретение 5066418 МПК G01R 31/28. Способ испытания радиоэлектронной аппаратуры на надежность, автор Лаптев А.К., дата подачи 25.08.1992, опубл. 10.04.1997).

Расчетные методы необходимо дополнить натурными испытаниями макета схемы. Сложность заключается в том, чтобы смоделировать отказы отдельных элементов.

Часто при таких испытаниях происходит разрушение электронной схемы, когда выполняют короткое замыкание или обрыв контактов ее элементов. После таких испытаний схема неисправна и непригодна к дальнейшему использованию.

В изобретении предложен способ проведения неразрушающих испытаний на отказоустойчивость, после которого схема сохраняет работоспособность.

Заявленный способ позволяет быстро вносить изменения в электронную схему, без ее перепайки.

Заявленный способ позволяет реализовать и провести испытания для разных схем, используя стандартный набор унифицированных элементов.

При заявленном способе имитируются разные отказы отдельных элементов - «константа 0», «константа 1», « обрыв», «короткое замыкание». Имеется возможность последовательно сформировать цепочки отказов или выбирать неисправные элементы случайным образом.

Заявленный способ и стенд для испытаний электронной схемы на отказоустойчивость поясняются чертежами.

На фиг. 1-4 приведена последовательность шагов для испытаний электронной схемы на отказоустойчивость.

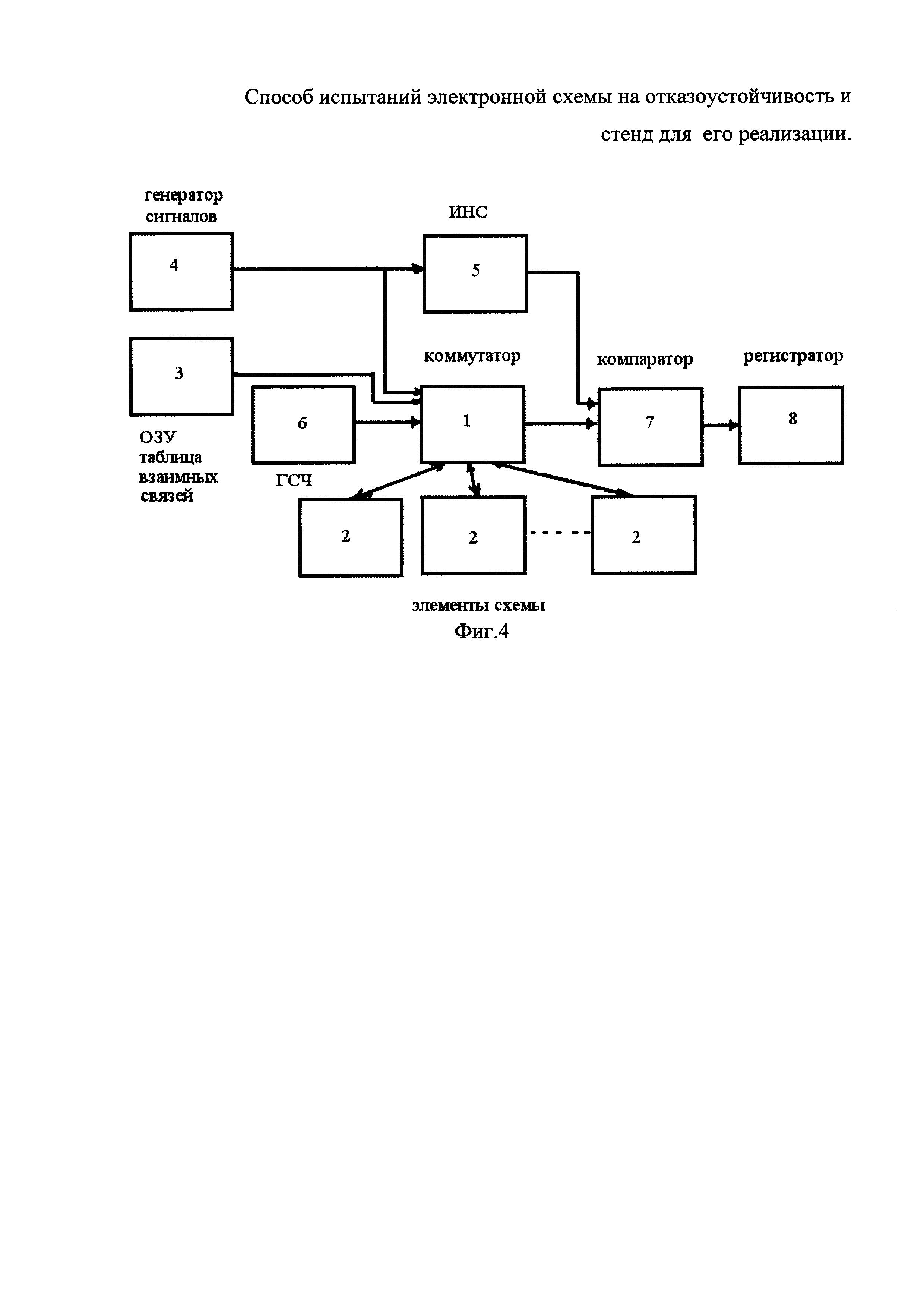

На фиг. 4 приведена схема устройства стенда для испытаний электронной схемы на отказоустойчивость.

Устройство стенда включает:

- коммутатор 1;

- элементы схемы 2;

- оперативное запоминающее устройство (ОЗУ) 3;

- генератор сигналов 4;

- искусственная нейронная сеть (ИНС) 5;

- генератор случайных чисел 6;

- компаратор 7;

- регистратор 8.

Пример действий для реализации заявленного способа испытаний электронной схемы на отказоустойчивость приведен на фиг. 1-3.

Способ испытаний электронной схемы на отказоустойчивость включает следующие этапы.

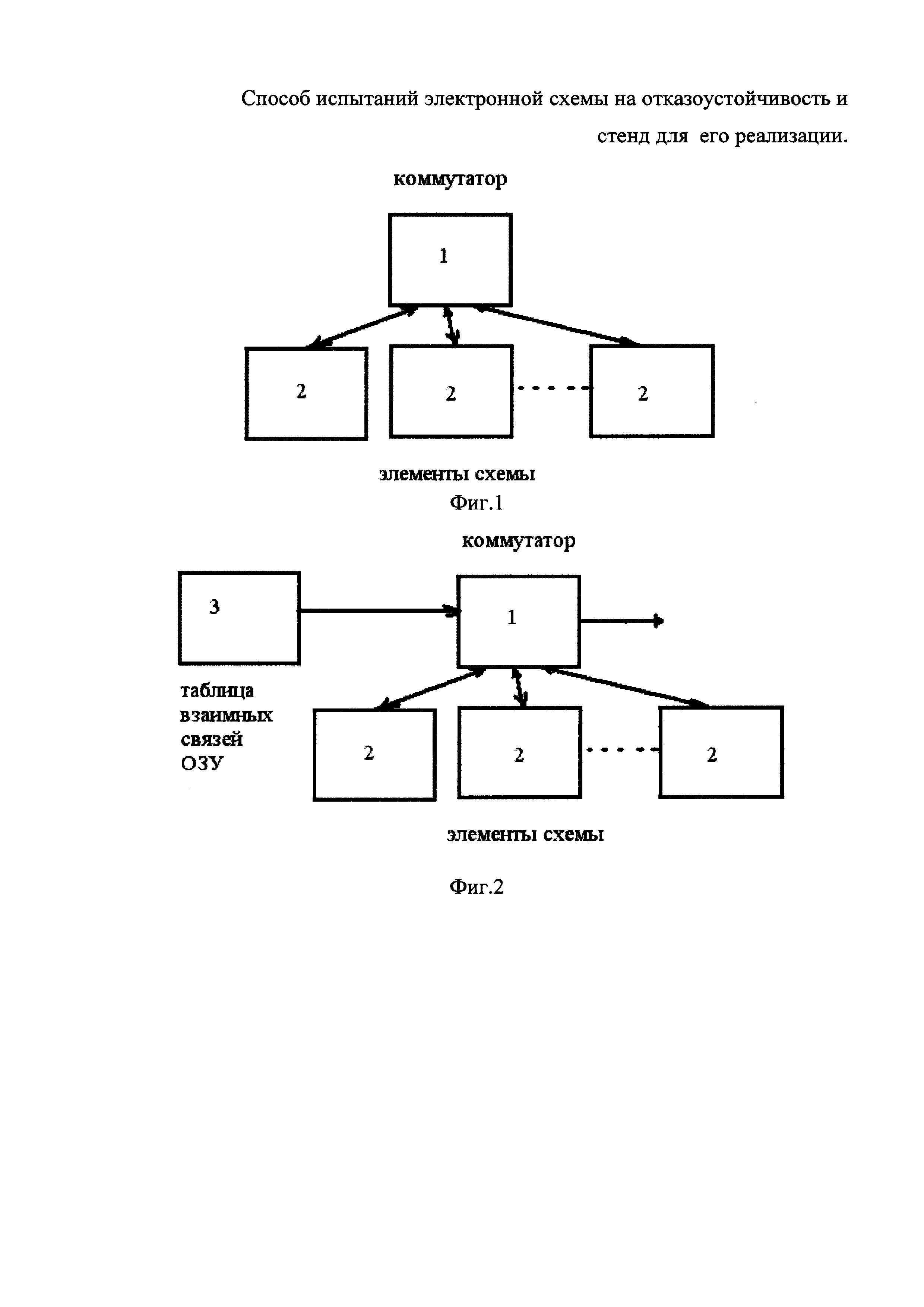

1. К входам и выходам коммутатора 1 подключают входы и выходы элементов схемы 2, см. фиг. 1

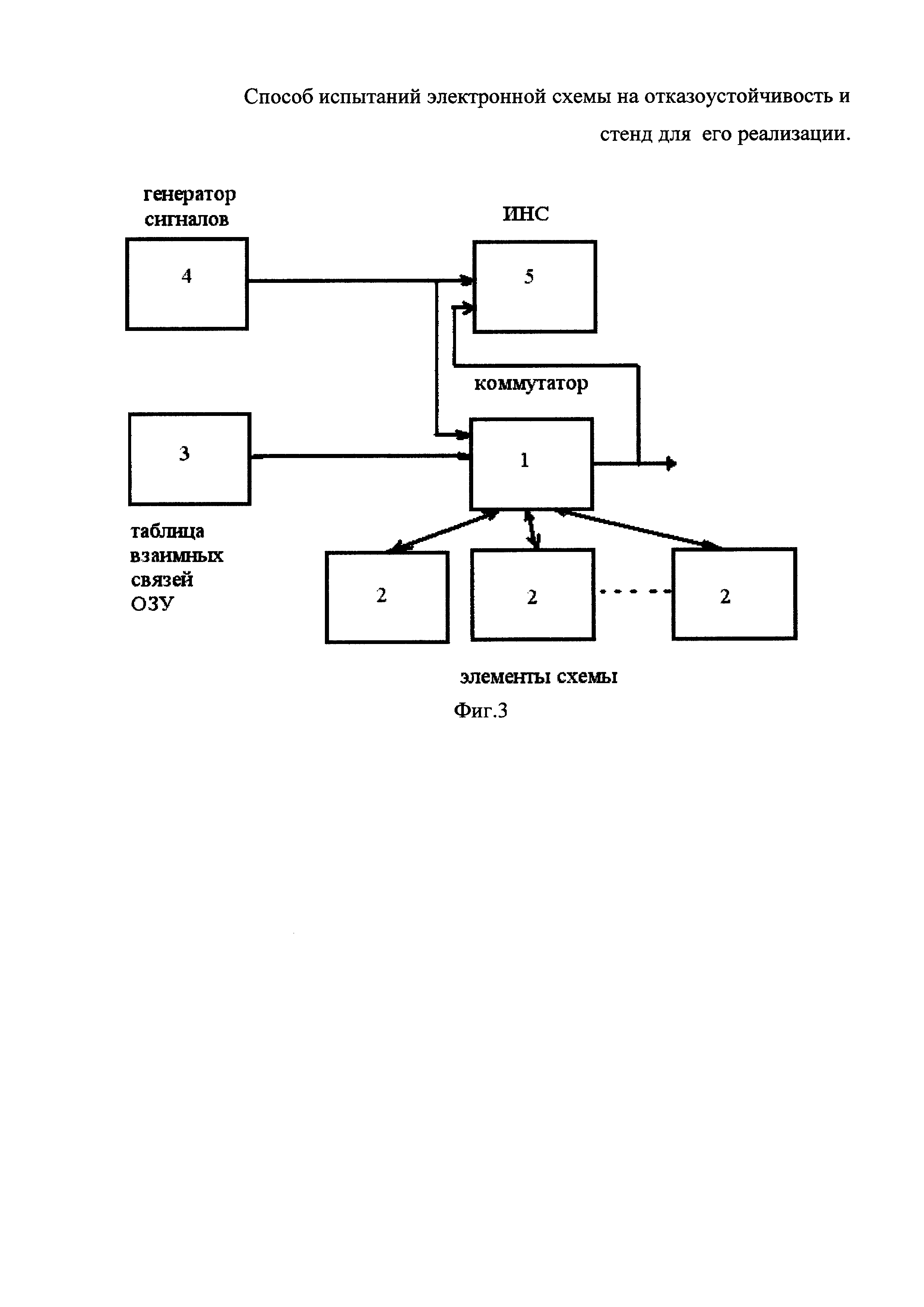

2. Формируют таблицу взаимных связей элементов электронной схемы и записывают ее в ОЗУ, см. фиг. 2. Таблица взаимных связей элементов электронной схемы содержит элементы x[I,j], которые принимают значения «0» или «1». Если i-тый вход коммутатора не связан j-тым выходом, то x[I,j]=0. Если i-тый вход коммутатора связан с j-тым выходом, то x[I,j]=1. Из ОЗУ таблицу взаимных связей элементов копируют в память коммутатора 1. Коммутатор соединяет элементы схемы, используя таблицу взаимных связей.

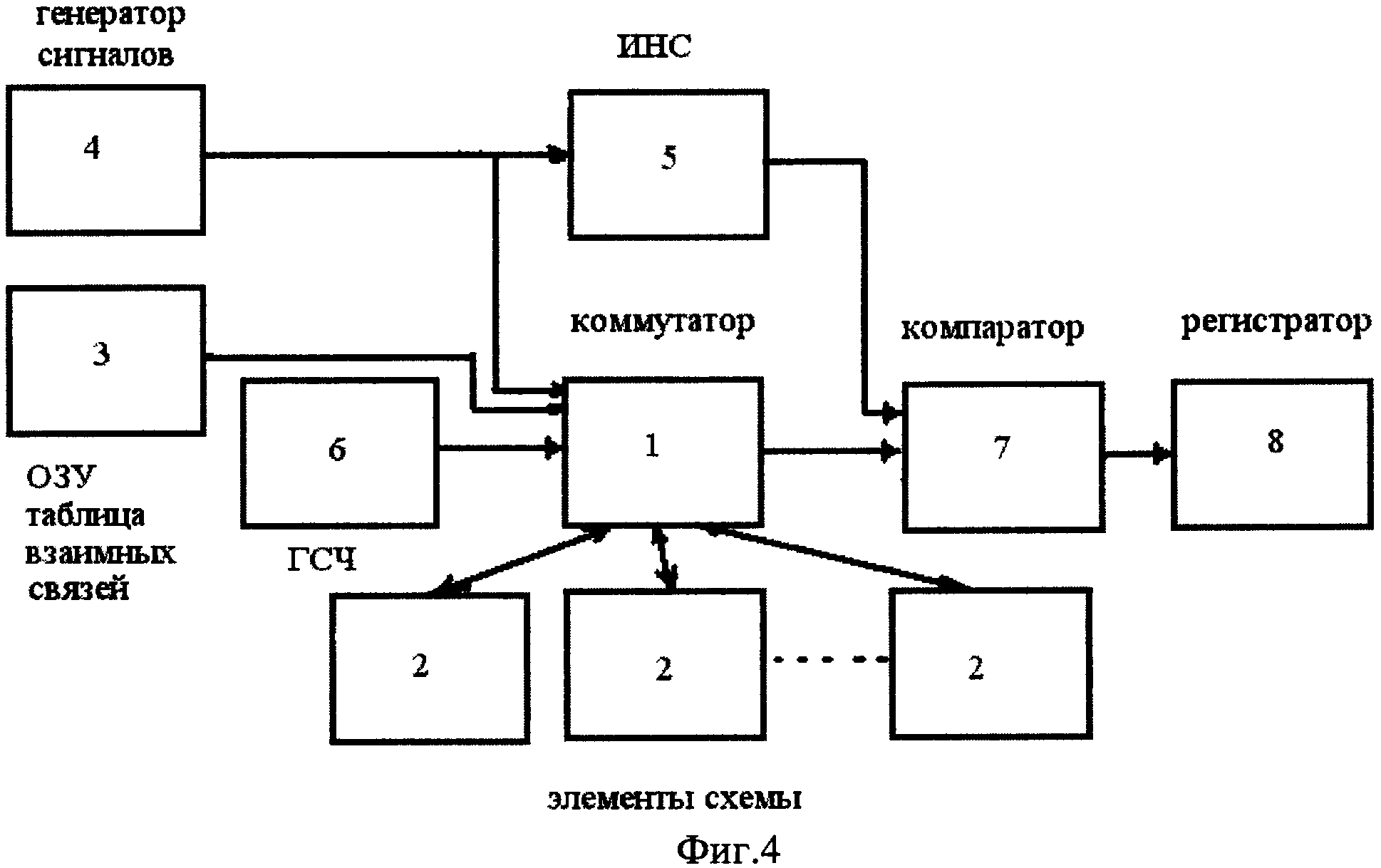

3. К входам коммутатора подключают генератор входных сигналов 4, см. фиг. 3. Эти сигналы через коммутатор подают на входы электронной схемы.

4. Обучают ИНС, используя обучающую выборку в форме (входные сигналы-выходные сигналы) в исправном и работоспособном состоянии электронной схемы. Генератор входных сигналов подключают к входам ИНС.

5. Одноименные сигналы с выходов электронной схемы и обученной ИНС подают на соответствующие входы компаратора 7.

6. Моделируют отказ элемента с помощью генератора случайных чисел 4, см. фиг. 4. Случайное число задает ячейку таблицы взаимных связей, где изменяется информация, инвертируется записанное значение.

7. Если отказ элемента изменяет сигналы на одном из выходов электронной схемы, то на выходе компаратора 7 формируется сигнал отказа электронной схемы, который фиксирует регистратор 8.

8. Если отказ элемента не меняет сигналы на выходах электронной схемы, то на выходе компаратора 7 формируется сигнал работоспособного состояния, который фиксирует регистратор 8.

Стенд для испытаний электронной схемы на отказоустойчивость работает следующим образом, см. фиг. 4. Стенд для испытаний электронной схемы на отказоустойчивость включает коммутатор 1. К входам и выходам коммутатора 1 подключены входы и выходы элементов схемы 2. К входам коммутатора подсоединены оперативное запоминающее устройство (ОЗУ) 3, генератор сигналов 4, генератор случайных чисел 6. Одноименные выходы коммутатора 1 и ИНС 5 подсоединены к соответствующим входам компаратора 7. Выход генератора сигналов 4 подсоединен к входу обученной искусственной нейронной сети (ИНС) 5 Выход компаратора 7 подключен к входу регистратора 8.

Устройство работает следующим образом. Взаимные соединения элементов 2 схемы задаются в таблице, которая хранится в памяти коммутатора 1. Эта таблица формируется и заносится в ОЗУ 3, а из ОЗУ копируется в память коммутатора. На входы электронной схемы подают сигналы с выходов генератора сигналов 4. Генератор сигналов 4 подключается к входам электронной схемы через коммутатор 1. Коммутатор 1 выполняет соединения элементов электронной схемы 2 друг с другом по входам и выходам. На выходах электронной схемы формируются выходные сигналы, которые через коммутатор 1 поступают на входы компаратора 7. На соответствующие входы компаратора 7 поступают одноименные сигналы с выходов обученной ИНС 5 и коммутатора 1. Входы ИНС 4 подключены к генератору сигналов 4. ИНС формирует выходные сигналы электронной схемы в ее работоспособном состоянии. Неисправность элементов электронной схемы моделирует генератор случайных чисел 6, выход которого подсоединен к входу коммутатора 1. По сигналу с выхода генератора случайных чисел 6 выбирается ячейка оперативной памяти, куда заносится сигнал неисправности. Моделируют отказы «константа 0», «константа 1», «обрыв», «короткое замыкание». При отказах «константа 0» и «обрыв» на выходе неисправного элемента формируется сигнал «0», не зависящий от входных сигналов. При отказах «константа 1» и «короткое замыкание» на выходе неисправного элемента формируется сигнал «1», не зависящий от входных сигналов. На выходах коммутатора 1 формируются выходные сигналы неисправной электронной схемы, которые поступают на второй вход компаратора 7. Компаратор сравнивает выходные сигналы неисправной схемы с эталоном, сигналами на одноименных выходах ИНС 5. При расхождении сигналов на одноименных входах компаратор 7 формирует сигнал обнаруженного отказа электронной схемы, который передается и фиксируется в регистраторе 8.

Технический результат заявленного способа испытаний электронной схемы на отказоустойчивость состоит в автоматизации, сокращении времени и экспериментальной проверке математической модели надежности электронной схемы.

Технический результат заявленного способа испытаний электронной схемы на отказоустойчивость состоит в том, что согласно изобретению, сначала к входам и выходам коммутатора подключают входы и выходы элементов электронной схемы, затем формируют таблицу взаимных связей элементов, где в элементе таблицы x[I,j] записаны числа «0» или «1», причем «0» означает отсутствие связи i-го входа и j-го выхода, а «1» означает соединение i-го входа с j-тым выходом, таблицу взаимных связей заносят в оперативное запоминающее устройство, которое подсоединяют к входам коммутатора, после чего таблицу взаимных связей элементов копируют в память коммутатора, потом генератор сигналов подключают к входам коммутатора, на выходах которого формируются выходные сигналы работоспособного состояния электронной схемы, после этого обучают искусственную нейронную сеть (ИНС), используя пары векторов (входные сигналы электронной схемы - выходные сигналы электронной схемы), затем генератор случайных чисел подключают к входу коммутатора, генерируют случайное число и по нему выбирают ячейку таблицы взаимных связей, информацию в ячейке инвертируют, моделируя отказ элемента, после этого на выходах коммутатора формируются сигналы, соответствующие отказу одного из элементов электронной схемы, одноименные выходы коммутатора и ИНС подсоединяют к входам компаратора, затем выход генератора сигналов подсоединяют к входу обученной ИНС, выход которой используют как эталон и подключают к одноименным входам компаратора, выход которого подключают к входу регистратора, при расхождении сигналов на одноименных входах компаратора, на его выходе формируется сигнал отказа электронной схемы, который фиксируется в регистраторе.

Технический результат заявленного стенда для испытаний электронной схемы на отказоустойчивость по способу п. 1 состоит в том, что согласно изобретению стенд включает коммутатор, элементы электронной схемы, оперативную память, генератор сигналов, генератор случайных чисел, ИНС, компаратор и регистратор, причем входы коммутатора подключены к выходам элементов электронной схемы, к оперативному запоминающему устройству, к генератору сигналов, к генератору случайных чисел, а выходы коммутатора подсоединены к входам элементов электронной схемы, к входам компаратора, причем выход генератора сигналов подключен к входам искусственной нейронной сети (ИНС), одноименные выходы которой подключены к входам компаратора, выход которого подключен к входу регистратора.

Заявленные в изобретении способ и стенд для испытаний электронной схемы на отказоустойчивость и могут быть реализованы аппаратными, программными или аппаратно-программными средствами на базе микропроцессоров, микроконтроллеров, нейрочипов.

Указанные в независимом пункте формулы признаки являются существенными и взаимосвязаны между собой с образованием устойчивой совокупности необходимых признаков, достаточной для получения требуемого технического результата.

Свойства, регламентированные в заявленном способе отдельными признаками, общеизвестны из уровня техники и не требуют дополнительных пояснений.

Следует отметить, что заявленная совокупность существенных признаков обеспечивает в соединении синергетический (сверхсуммарный) результат.

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного способа следующей совокупности условий:

- заявленный способ имеет практическое применение, предназначен для проведения испытаний электронных схем на отказоустойчивость;

- для заявленного способа в том виде, как он охарактеризован в независимом пункте нижеизложенной формулы, подтверждена возможность его осуществления с помощью известных из уровня техники на дату приоритета средств и методов;

- при осуществлении способа достигается усматриваемый заявителем технический результат.

На основании изложенного, заявленный способ испытаний электронной схемы на отказоустойчивость и стенд для его реализации соответствуют требованию условия патентоспособности «новизна» и «изобретательский уровень».