Результат интеллектуальной деятельности: КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ

Вид РИД

Изобретение

Область техники

Один или несколько аспектов относятся, в общем, к конфигурациям вычислительных окружений и, прежде всего, к изменению конфигураций таких окружений.

Уровень техники

Вычислительные окружения предлагают диапазон инструментов и функций в зависимости от архитектурных конфигураций окружений. Две архитектуры, предложенные International Business Machines Corporation, Армонк, Нью-Йорк, включают в себя ESA/390 и z/Архитектуру.

ESA/390 является предшествующей архитектурой по отношению к z/Архитектуре. Однако, когда z/Архитектура была введена, поддержка ESA/390 была продолжена. Для поддержки обеих архитектур в одном окружении требуется следовать некоторым процедурам. Например, при включении загружается ESA/390, а затем, при желании, может быть сделано переключение на z/Архитектуру.

Это позволяет унаследованному программному обеспечению продолжать выполнение без изменений. Другие такие процедуры предоставляются с целью поддержки обеих архитектурных конфигурации в одном окружении.

Однако тестирование виртуальной памяти является затратным. По мере того, как архитектура приближается к концу своего жизненного цикла, может оказаться желательным предоставление традиционных окружений, например для систем с использованием минимальной поддержки архитектуры, таких как операционные системы DOS (например, такие как MS DOS или CMS), которые функционируют, прежде всего, в качестве окружений интерпретатора командной строки, или для окружений, использующихся для выполнения части BIOS (и которые могут производить выполнение без связанных с виртуальной памятью сложностей).

Поэтому на уровне техники существует потребность в рассмотрении вышеупомянутой проблемы.

Сущность изобретения

Недостатки известного уровня техники преодолеваются и преимущества обеспечиваются посредством предоставления компьютерного программного продукта для реконфигурирования вычислительного окружения. Компьютерный программный продукт включает в себя, например, машиночитаемый информационный носитель, считываемый посредством устройства обработки данных, и сохраняющий подлежащие выполнению посредством устройства обработки данных команды для осуществления способа. Способ включает в себя, например, выявление посредством процессора того, что средство конфигурации архитектурного режима инсталлировано в вычислительном окружении, сконфигурированном для нескольких архитектурных режимов и имеющем заданную последовательность включения, которая предназначена для включения вычислительного окружения в одном архитектурном режиме из нескольких архитектурных режимов, причем один архитектурный режим содержит первую архитектуру системы команд и имеет первый набор поддерживаемых сервисов, на основании выявления того, что средство конфигурации архитектурного режима инсталлировано, проведение посредством процессора реконфигурирования вычислительного окружения для ограничения использования одного архитектурного режима, причем реконфигурирование включает в себя: выборку отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме из нескольких архитектурных режимов, причем другой архитектурный режим отличен от одного архитектурного режима, и другой архитектурный режим содержит вторую архитектуру системы команд и имеет второй набор поддерживаемых сервисов, и выполнение отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме вместо одного архитектурного режима, ограничивая использование одного архитектурного режима.

При рассмотрении с позиции первого аспекта, настоящее изобретение предоставляет способ реконфигурирования вычислительного окружения, причем способ содержит: выявление посредством процессора того, что средство конфигурации архитектурного режима инсталлировано в вычислительном окружении, сконфигурированном для нескольких архитектурных режимов и имеющем заданную последовательность включения, которая предназначена для включения вычислительного окружения в одном архитектурном режиме из нескольких архитектурных режимов, причем один архитектурный режим содержит первую архитектуру системы команд и имеет первый набор поддерживаемых сервисов, на основании выявления того, что средство конфигурации архитектурного режима инсталлировано, проведение посредством процессора реконфигурирования вычислительного окружения для ограничения использования одного архитектурного режима, причем реконфигурирование включает в себя: выборку отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме из нескольких архитектурных режимов, причем другой архитектурный режим отличен от одного архитектурного режима, и другой архитектурный режим содержит вторую архитектуру системы команд и имеет второй набор поддерживаемых сервисов, и выполнение отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме вместо одного архитектурного режима, ограничивая использование одного архитектурного режима.

При рассмотрении с позиции другого аспекта, настоящее изобретение предоставляет способ конфигурирования вычислительного окружения, причем способ содержит: конфигурирование посредством процессора вычислительного окружения для выполнения операций в выбранном архитектурном режиме, конфигурирование содержащее: начало инициализации вычислительного окружения с использованием сохраненного слова состояния программы, причем сохраненное слово состояния программы имеет формат архитектурного режима, отличающегося от выбранного архитектурного режима, выявление того, что сохраненное слово состояния программы имеет формат архитектурного режима, отличающегося от выбранного архитектурного режима, на основании выявления того, что сохраненное слово состояния программы имеет формат архитектурного режима, отличающегося от выбранного архитектурного режима, проведение автоматического изменения сохраненного слова состояния программы для приобретения им формата выбранного архитектурного режима, причем автоматическое изменение выполняется в отсутствии явного запроса на переключение на выбранный архитектурный режим, и завершение инициализации вычислительного окружения с помощью измененного слова состояния программы для конфигурирования вычислительного окружения в выбранном архитектурном режиме.

При рассмотрении с позиции другого аспекта, настоящее изобретение предоставляет компьютерную систему для реконфигурирования вычислительного окружения, компьютерную систему содержащую: память, а также сообщенный с памятью процессор, причем компьютерная система сконфигурирована для осуществления способа, способа содержащего: выявление посредством процессора того, что средство конфигурации архитектурного режима инсталлировано в вычислительном окружении, сконфигурированном для нескольких архитектурных режимов и имеющем заданную последовательность включения, которая предназначена для включения вычислительного окружения в одном архитектурном режиме из нескольких архитектурных режимов, причем один архитектурный режим содержит первую архитектуру системы команд и имеет первый набор поддерживаемых сервисов, на основании выявления того, что средство конфигурации архитектурного режима инсталлировано, проведение посредством процессора реконфигурирования вычислительного окружения для ограничения использования одного архитектурного режима, причем реконфигурирование включает в себя: выборку отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме из нескольких архитектурных режимов, причем другой архитектурный режим отличен от одного архитектурного режима, и другой архитектурный режим содержит вторую архитектуру системы команд и имеет второй набор поддерживаемых сервисов, и выполнение отличной последовательности включения для включения вычислительного окружения в другом архитектурном режиме вместо одного архитектурного режима, ограничивая использование одного архитектурного режима.

При рассмотрении с позиции другого аспекта, настоящее изобретение предоставляет машиночитаемый информационный носитель, считываемый посредством устройства обработки данных и содержащий программу для реконфигурирования вычислительного окружения, включающую в себя команды, выполняемые посредством устройства обработки данных для осуществления соответствующего предлагаемого в изобретении способа. При рассмотрении с позиции другого аспекта, настоящее изобретение предоставляет машиночитаемый информационный носитель, считываемый посредством устройства обработки данных и содержащий программу для конфигурирования вычислительного окружения, включающую в себя команды, выполняемые посредством устройства обработки данных для осуществления соответствующего предлагаемого в изобретении способа.

При рассмотрении с позиции другого аспекта, настоящее изобретение предоставляет машиночитаемый информационный носитель, в котором сохранена компьютерная программа, содержащая участки программного кода и загружаемая во внутреннюю память цифровой вычислительной машины, когда данная программа выполняется на компьютере для осуществления предлагаемого в изобретении способа.

Относящиеся к одному или нескольким вариантам осуществления способы и системы также описаны и заявлены в настоящем документе. Кроме того, относящиеся к одному или нескольким вариантам осуществления услуги также описаны и могут быть заявлены в настоящем документе.

Осуществлены дополнительные функции и преимущества. Другие варианты осуществления и аспекты подробно описываются в настоящем документе и считаются частью заявленного изобретения.

Краткое описание чертежей

Настоящее изобретение в дальнейшем описывается исключительно в качестве примера со ссылками на предпочтительные варианты осуществления, как показано на последующих чертежах:

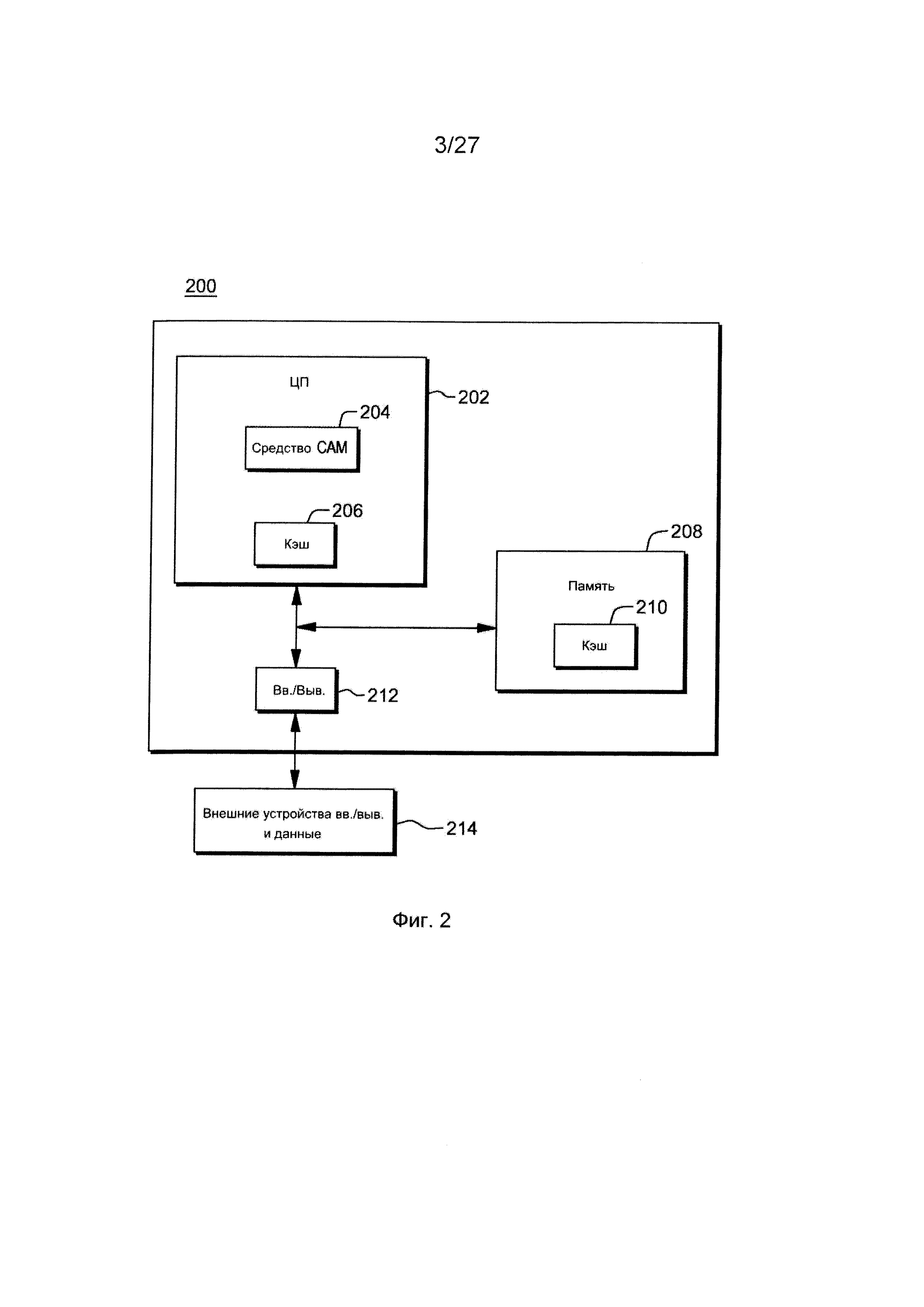

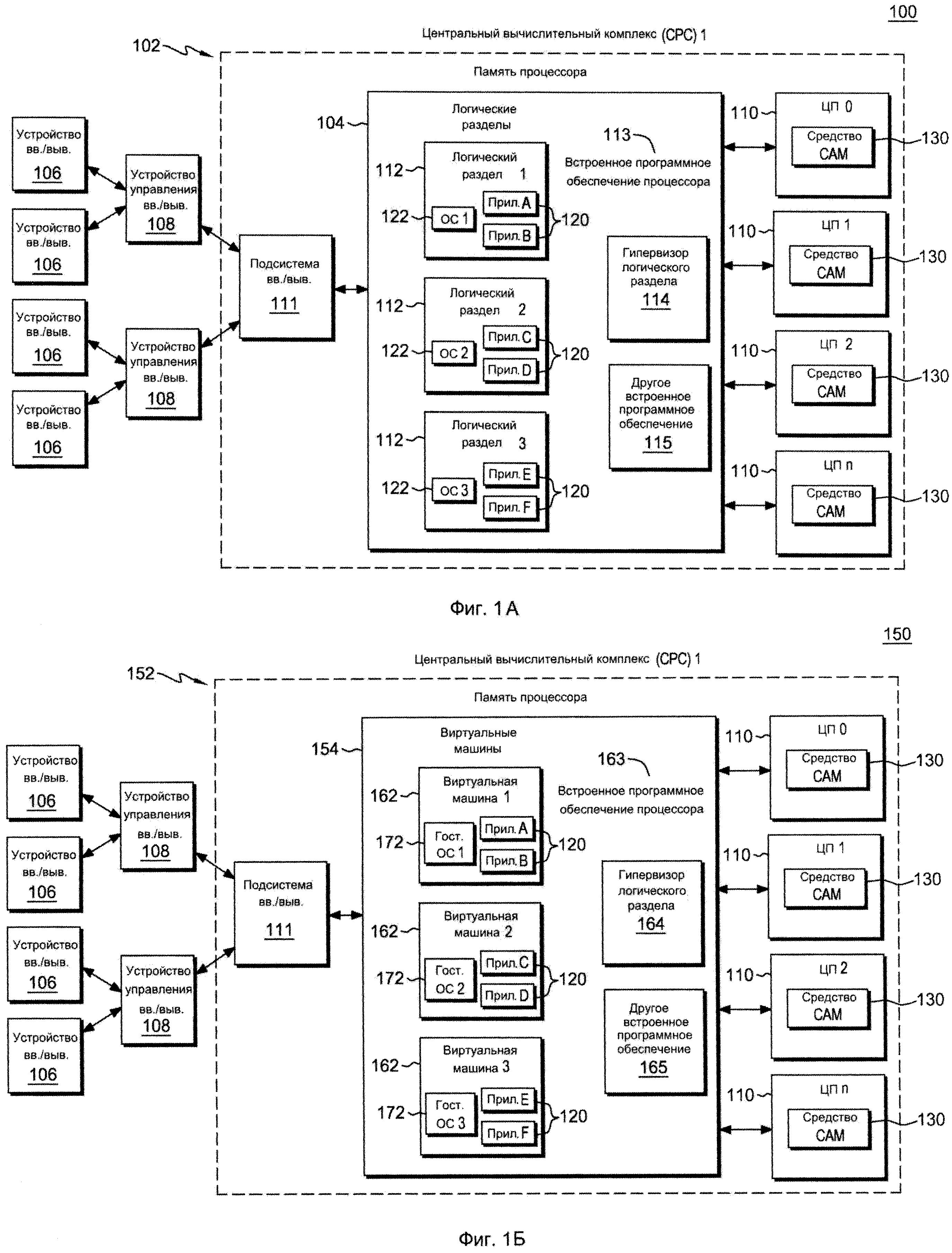

Фиг. 1А изображает один пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима согласно предпочтительному варианту осуществления настоящего изобретения,

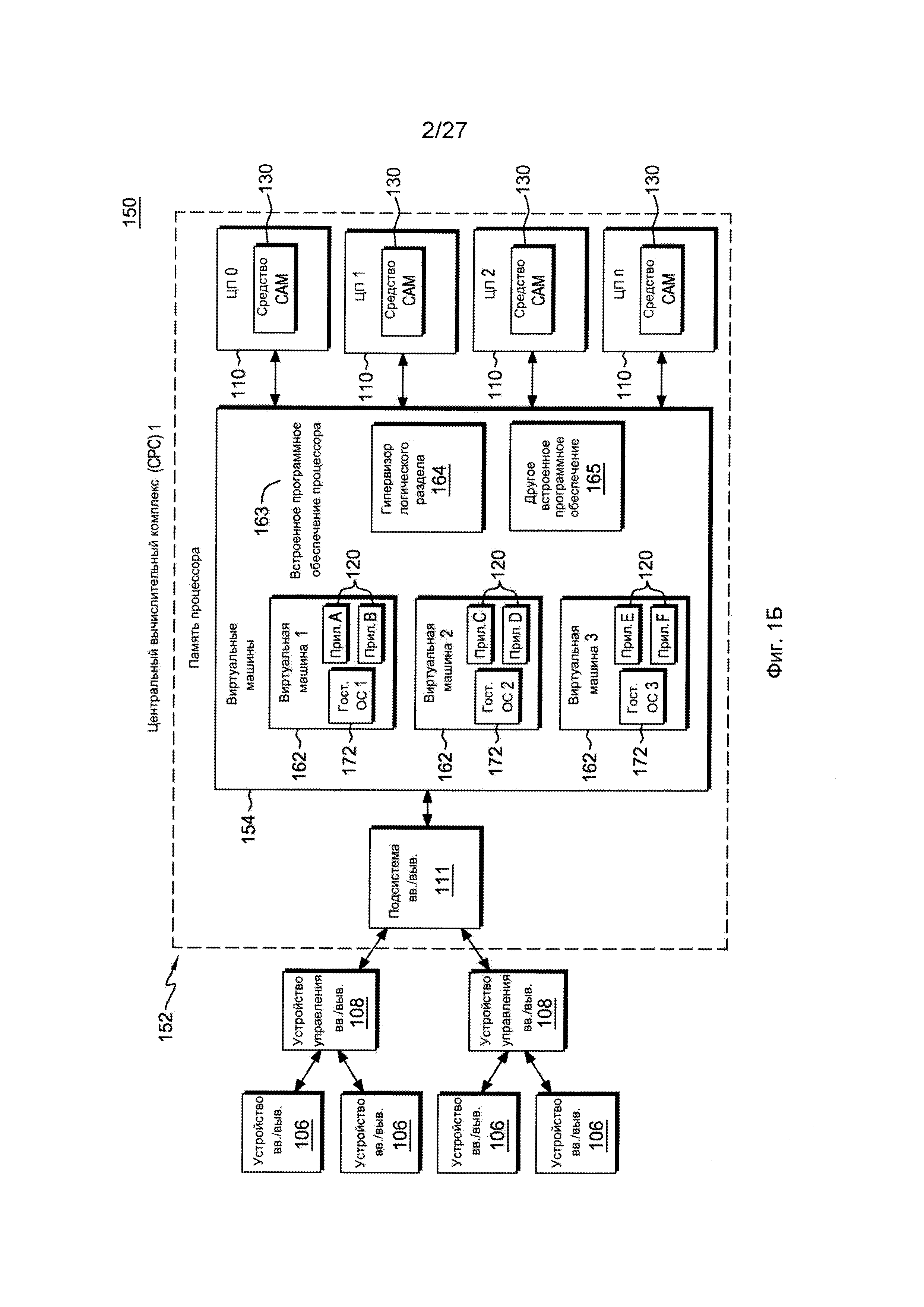

Фиг. 1Б изображает один пример виртуального вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима согласно предпочтительному варианту осуществления настоящего изобретения,

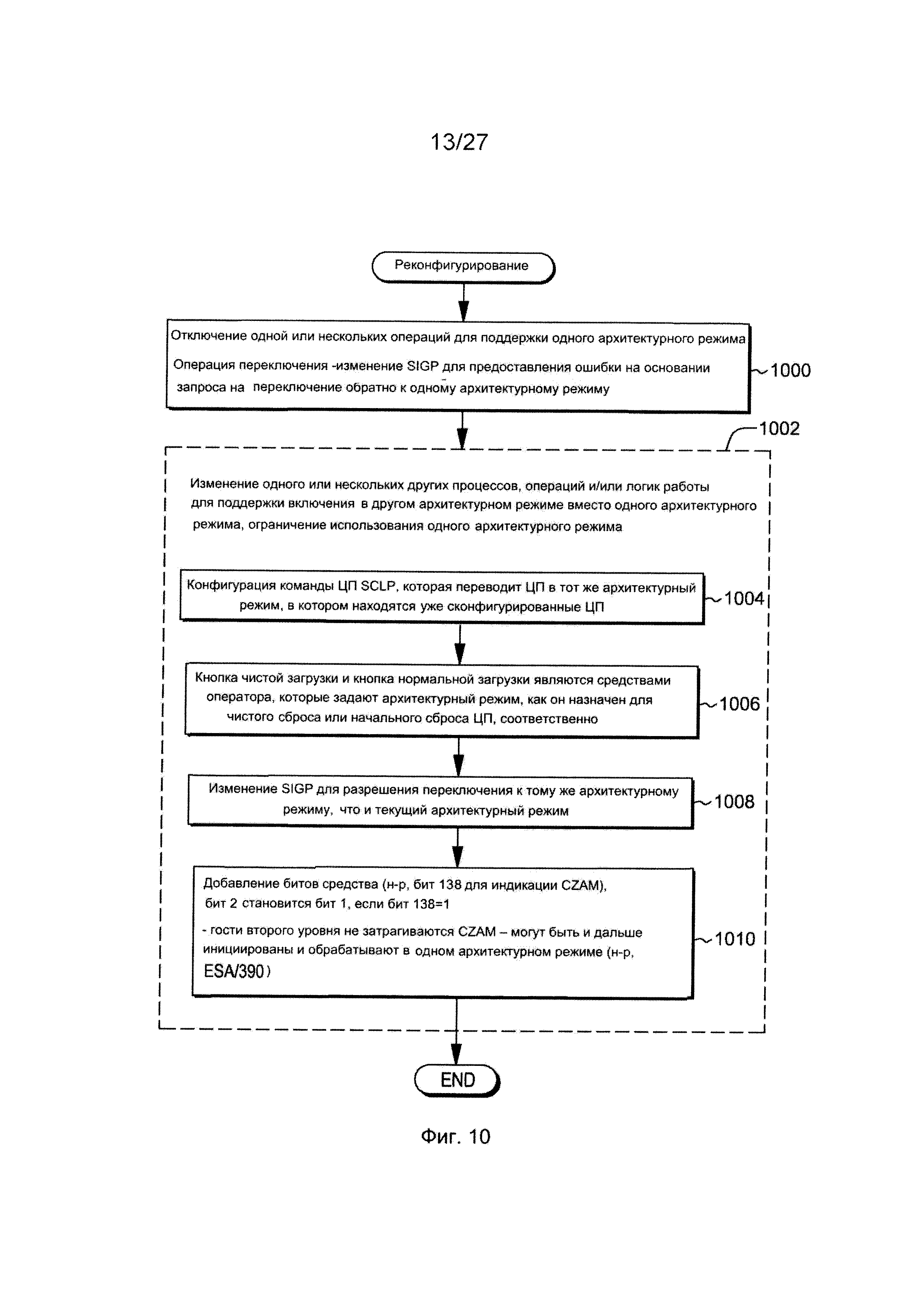

Фиг. 2 изображает другой пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима согласно предпочтительному варианту осуществления настоящего изобретения,

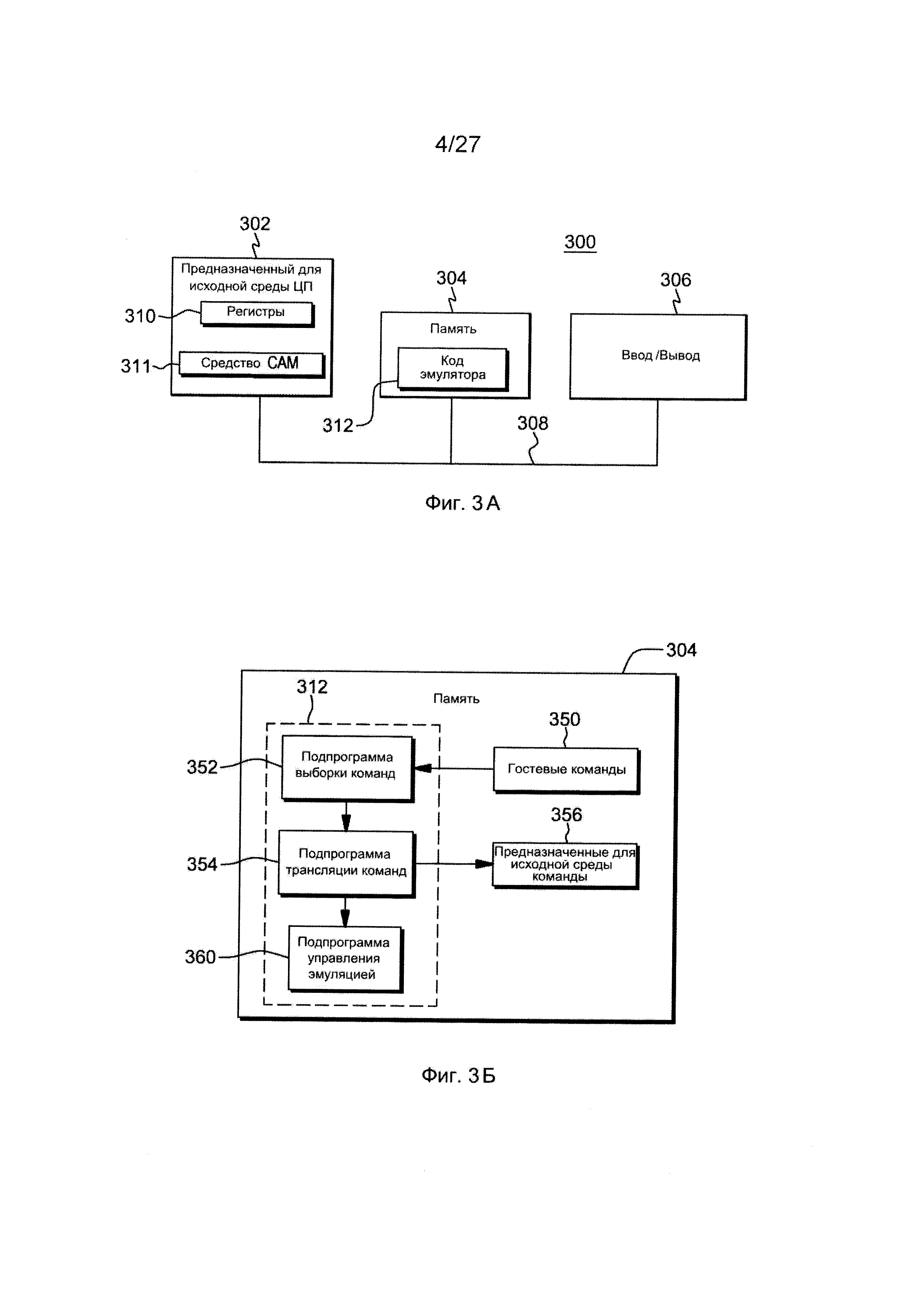

Фиг. 3А изображает еще один пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима согласно предпочтительному варианту осуществления настоящего изобретения,

Фиг. 3Б изображает более подробную информацию по памяти на фиг. 3А согласно предпочтительному варианту осуществления настоящего изобретения,

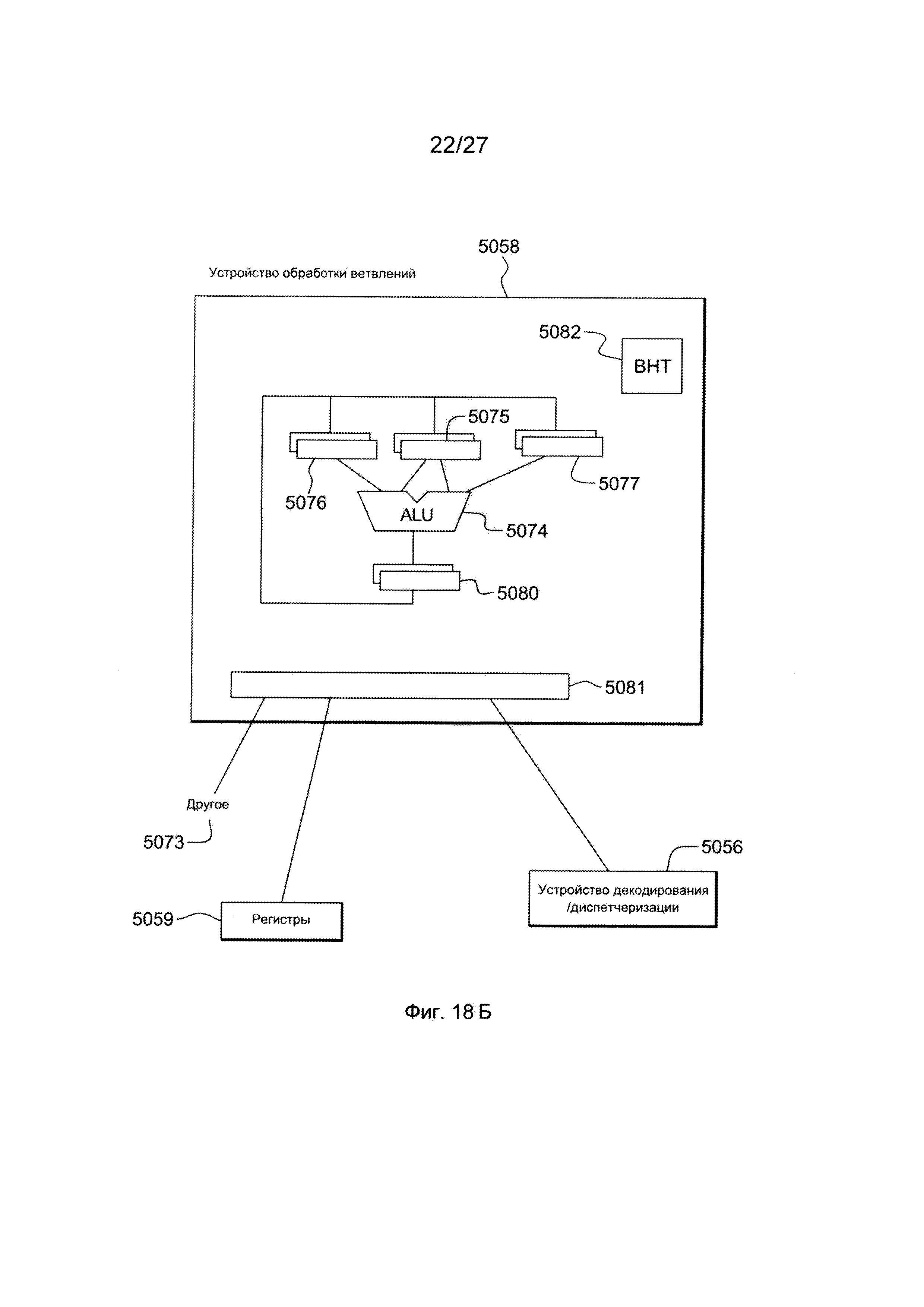

Фиг. 4А изображает один вариант осуществления логики для включения вычислительного окружения в одном архитектурном режиме согласно предпочтительному варианту осуществления настоящего изобретения,

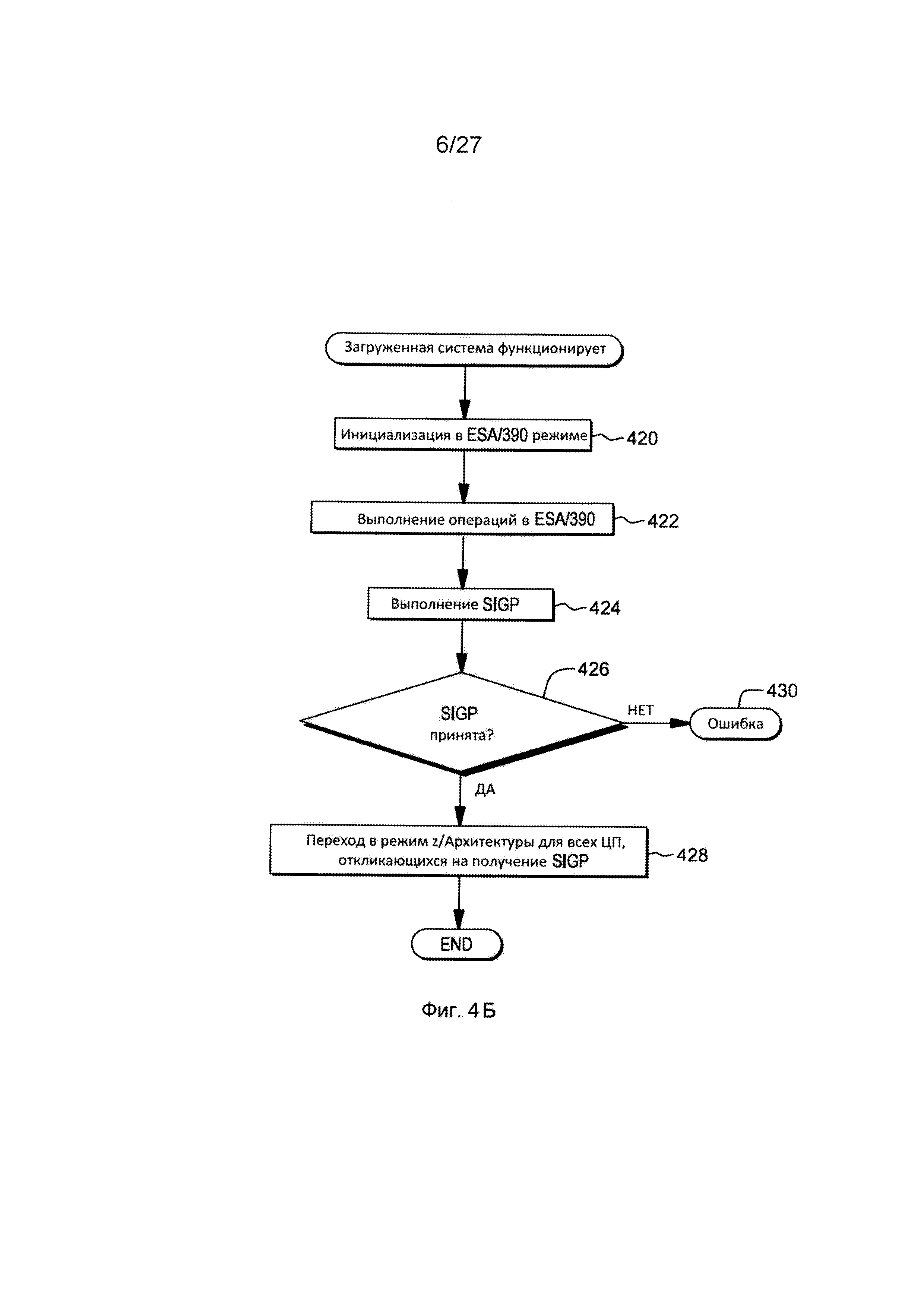

Фиг. 4В изображает один вариант осуществления последующей обработки, связанной с процессом включения на фиг. 4А согласно предпочтительному варианту осуществления настоящего изобретения,

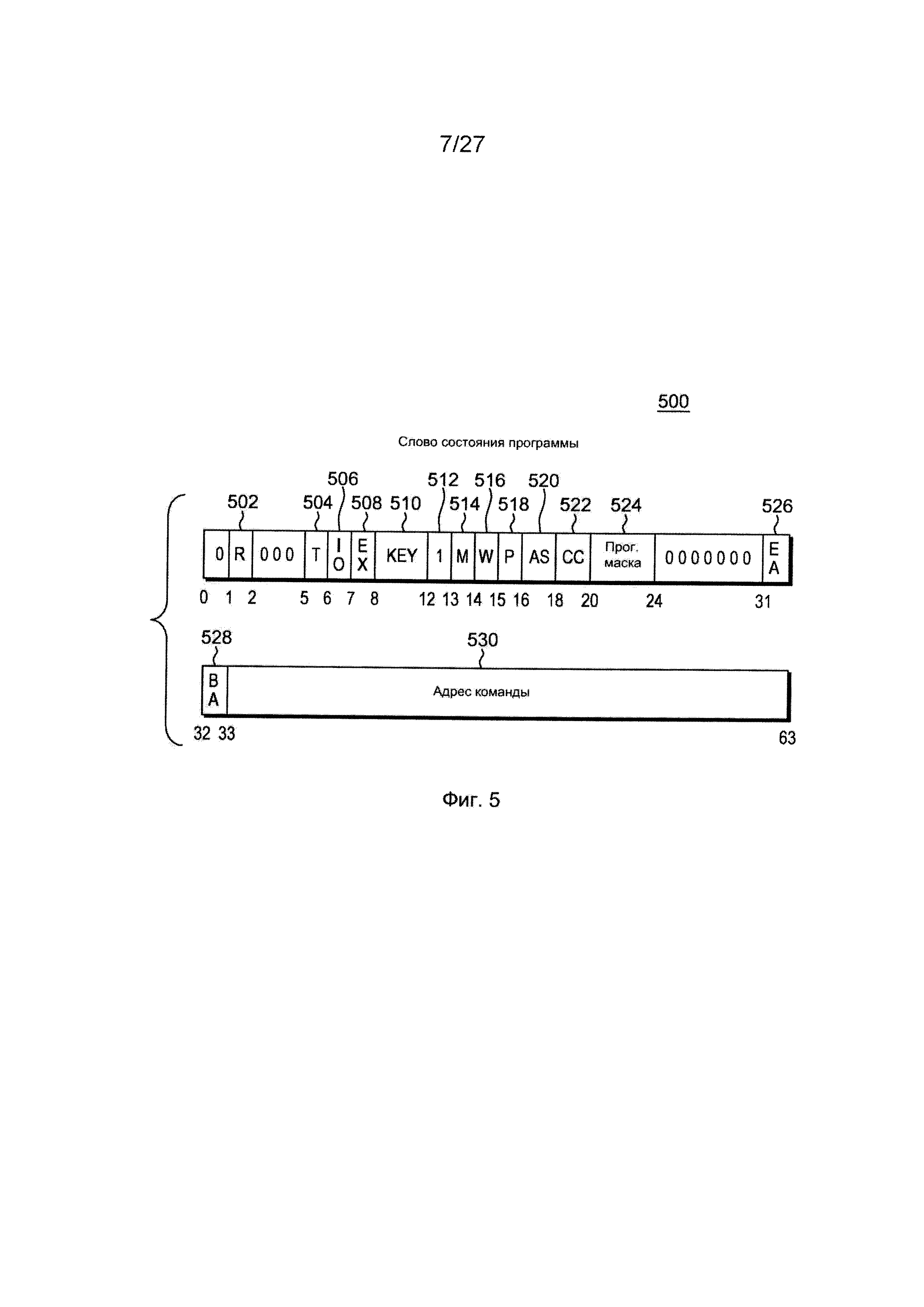

Фиг. 5 изображает один вариант осуществления формата слова состояния программы согласно предпочтительному варианту осуществления настоящего изобретения,

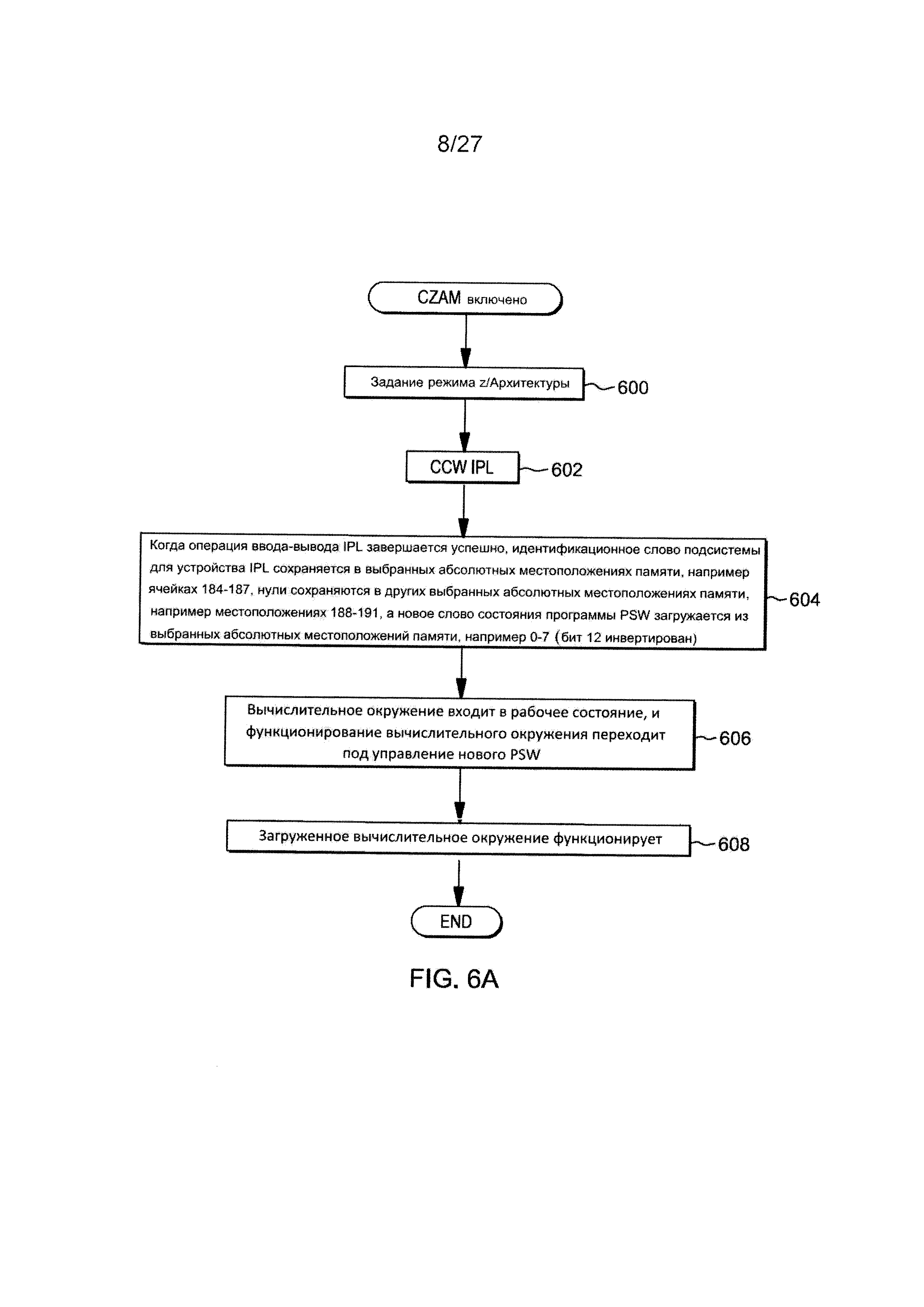

Фиг. 6А изображает один вариант осуществления логики для включения вычислительного окружения в архитектурном режиме, отличающемся от одного архитектурного режима, включение для которого показано на фиг. 4А, согласно предпочтительному варианту осуществления настоящего изобретения,

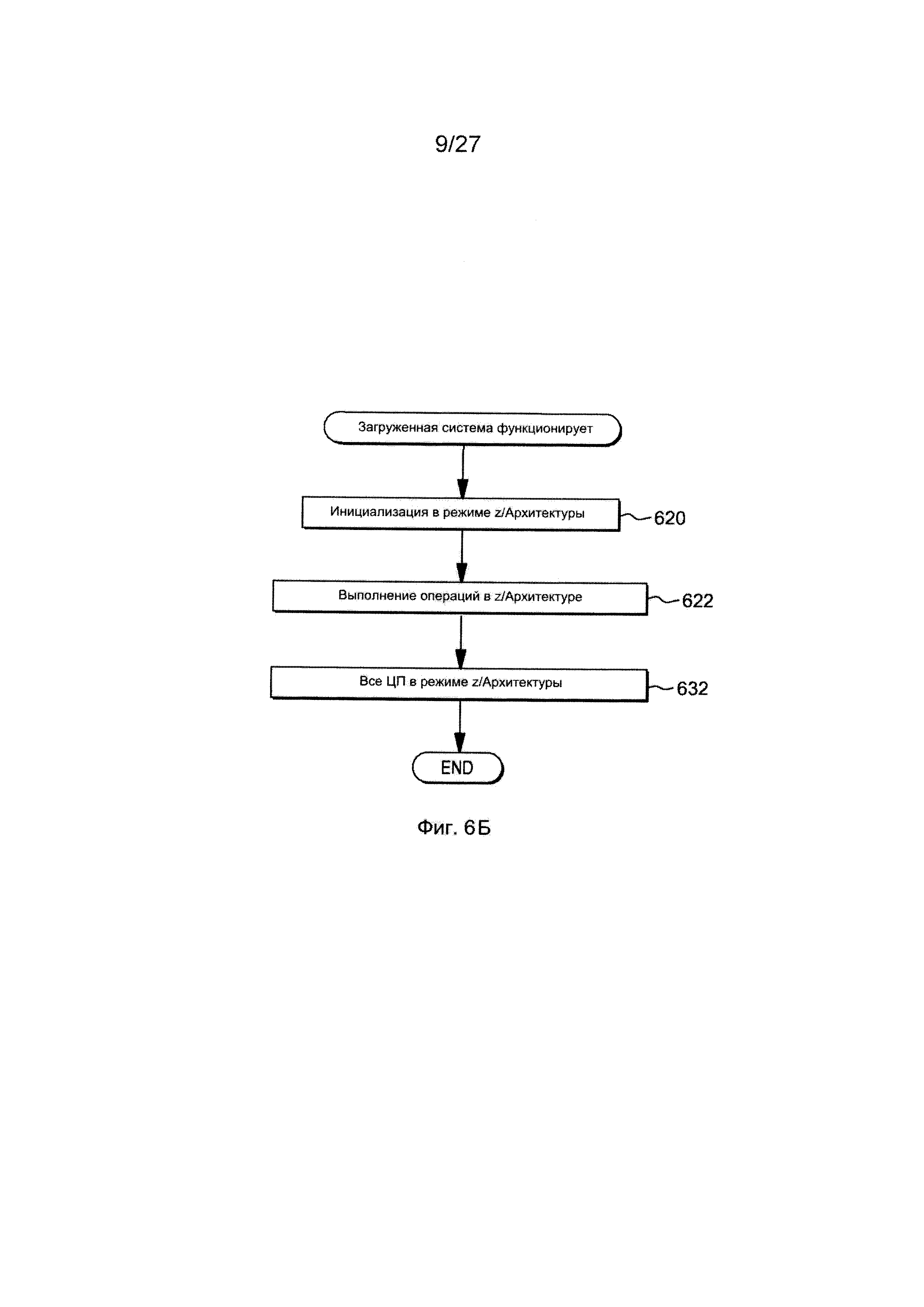

Фиг. 6Б изображает один вариант осуществления последующей обработки, связанной с процессом включения на фиг. 6А согласно предпочтительному варианту осуществления настоящего изобретения,

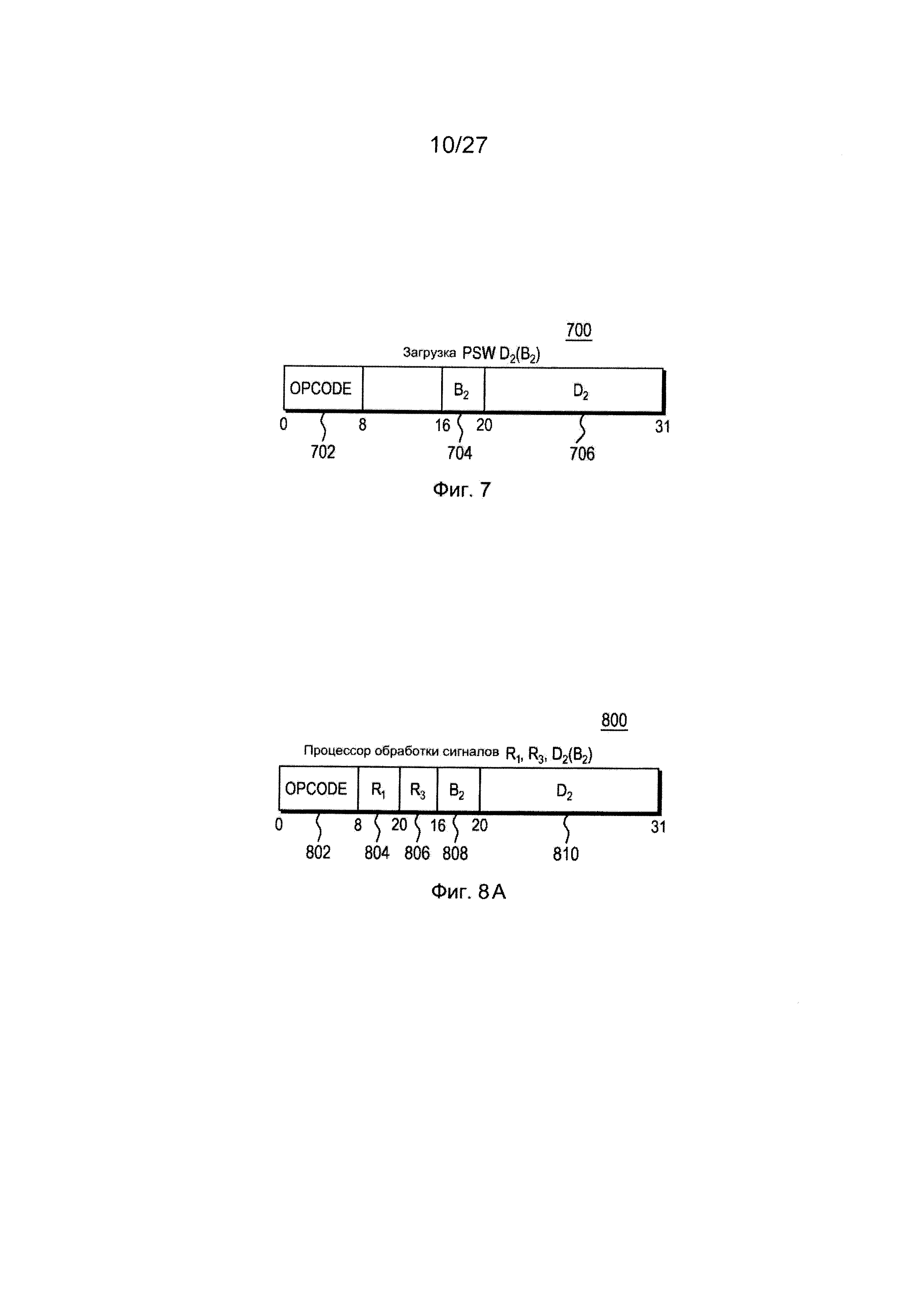

Фиг. 7 изображает один пример формата команды загрузки слова состояния программы согласно предпочтительному варианту осуществления настоящего изобретения,

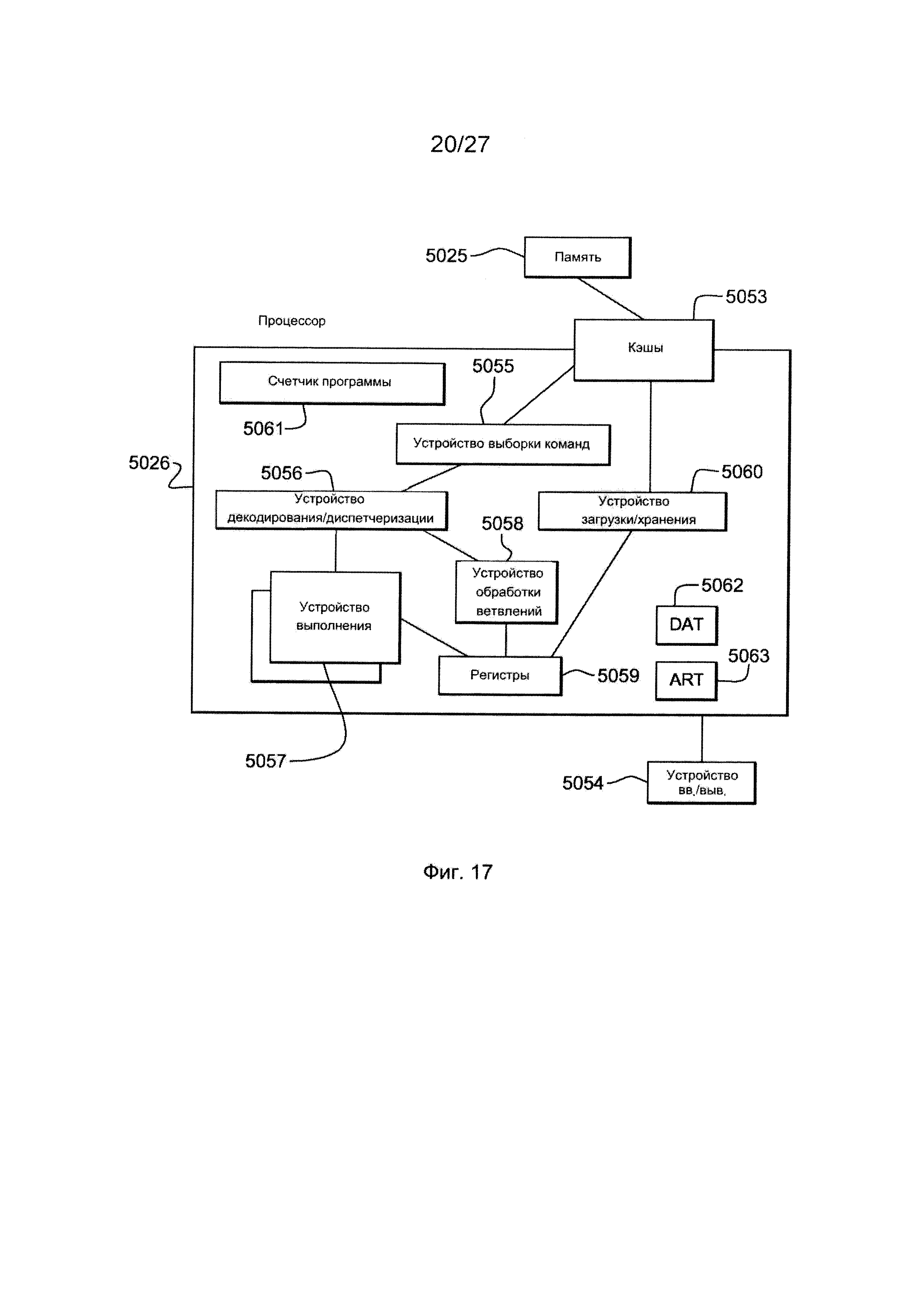

Фиг. 8А изображает один пример формата команды процессора обработки сигналов согласно предпочтительному варианту осуществления настоящего изобретения,

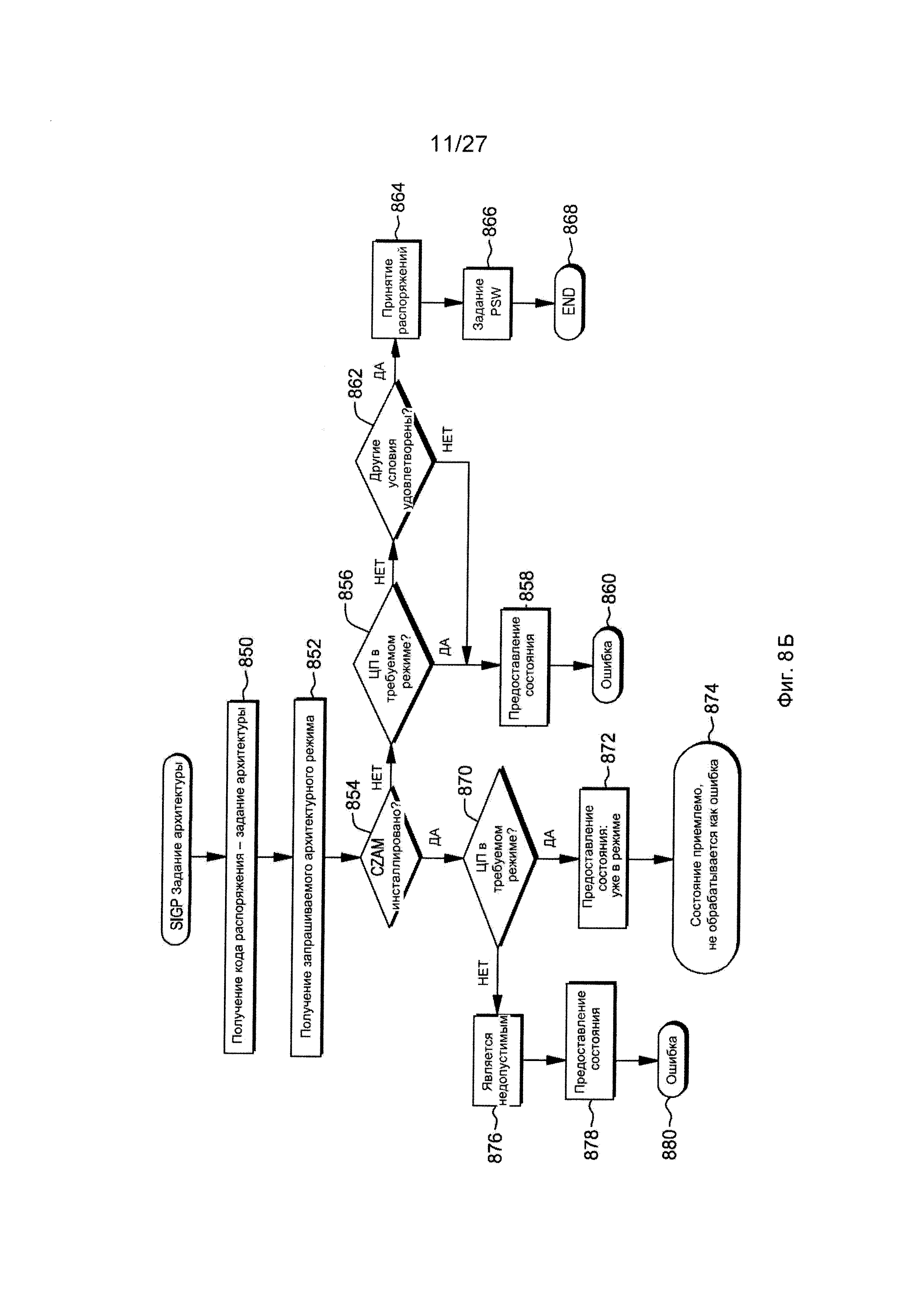

Фиг. 8Б изображает один вариант осуществления обработки, связанный с командой процессора обработки сигналов на фиг. 8А, согласно предпочтительному варианту осуществления настоящего изобретения,

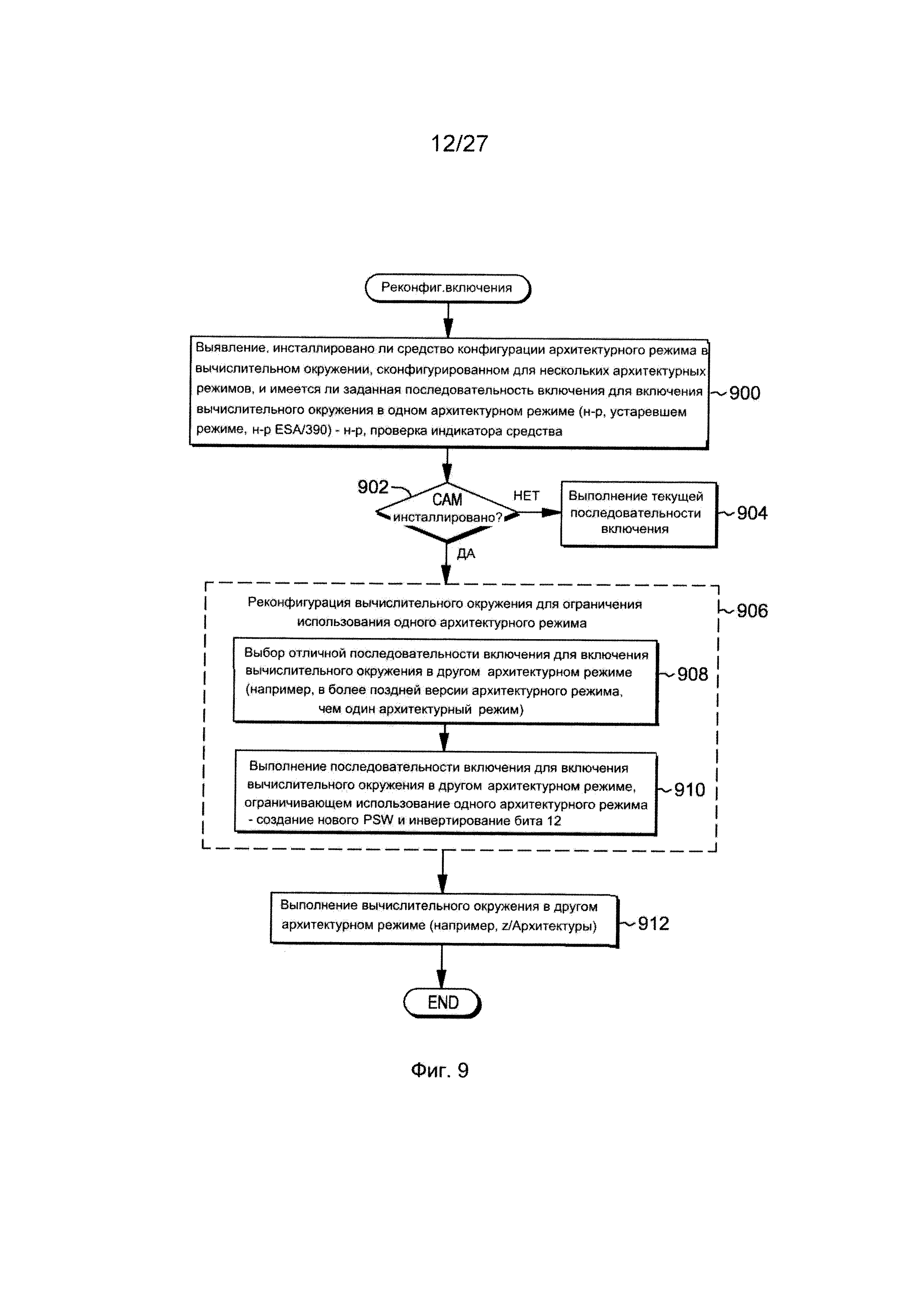

Фиг. 9 изображает один вариант осуществления логики для включения вычислительного окружения в реконфигурированной конфигурации согласно предпочтительному варианту осуществления настоящего изобретения,

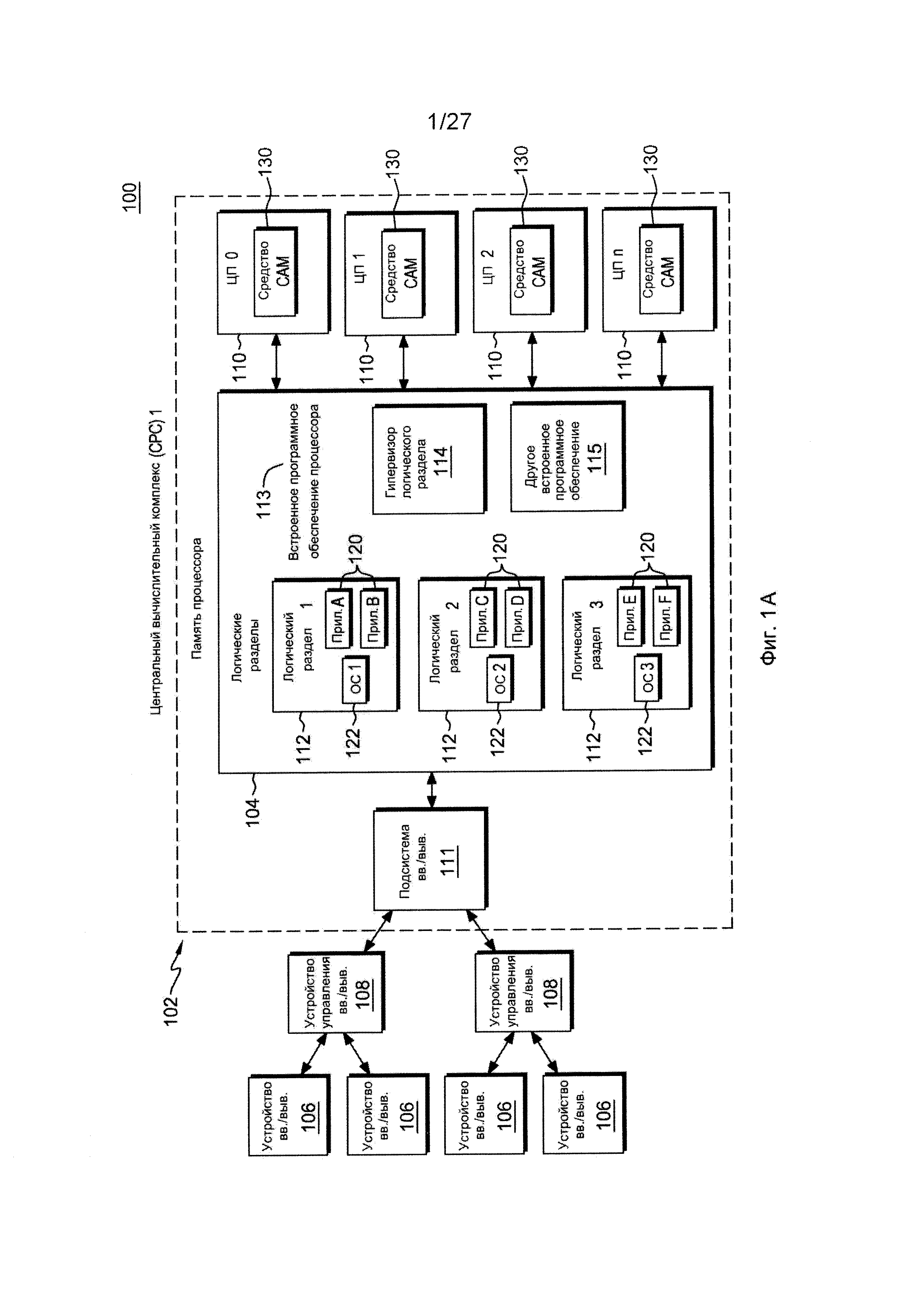

Фиг. 10 изображает другие необходимые изменения при реконфигурировании вычислительного окружения согласно предпочтительному варианту осуществления настоящего изобретения,

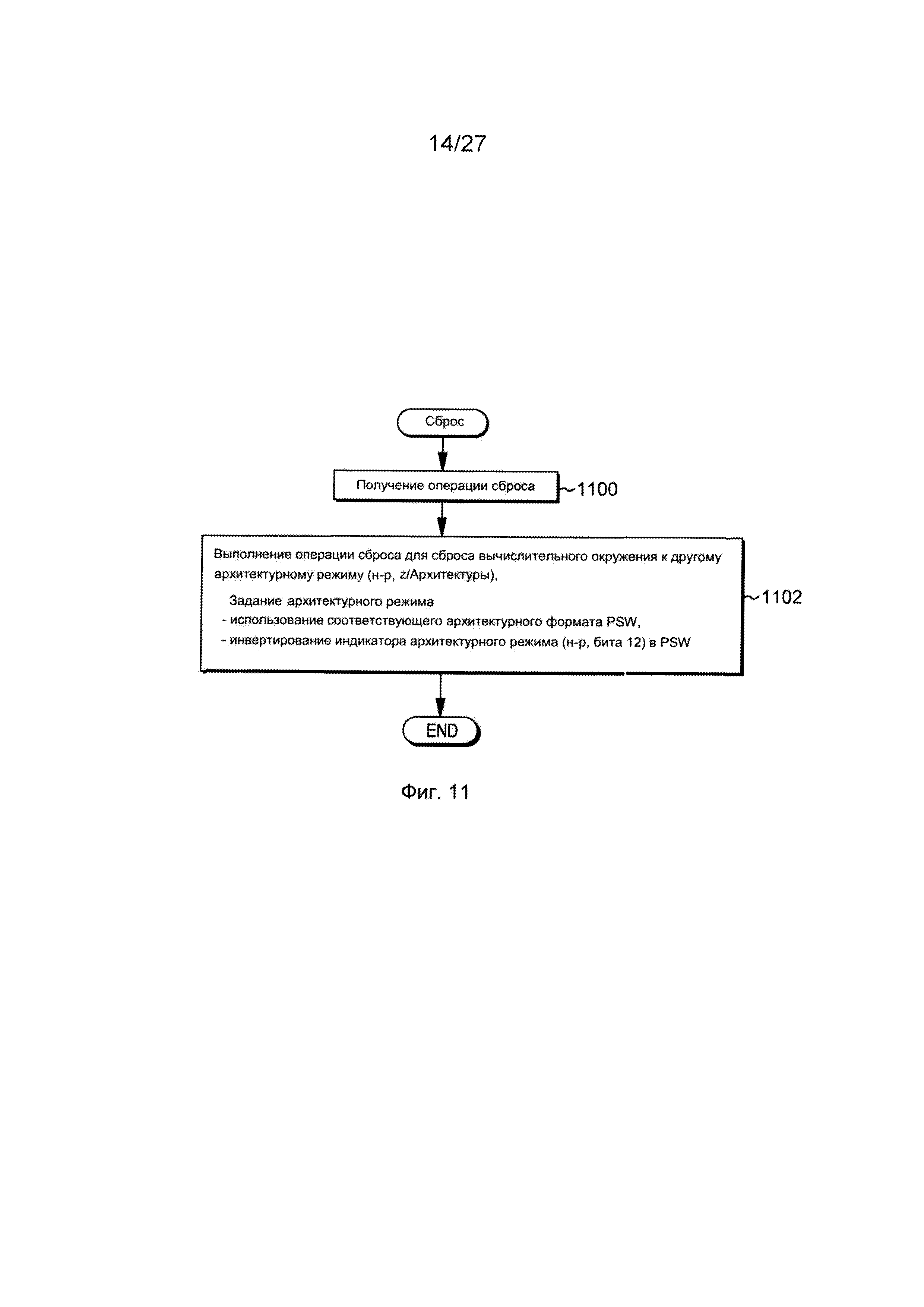

Фиг. 11 изображает один вариант осуществления логики для сброса вычислительного окружения,

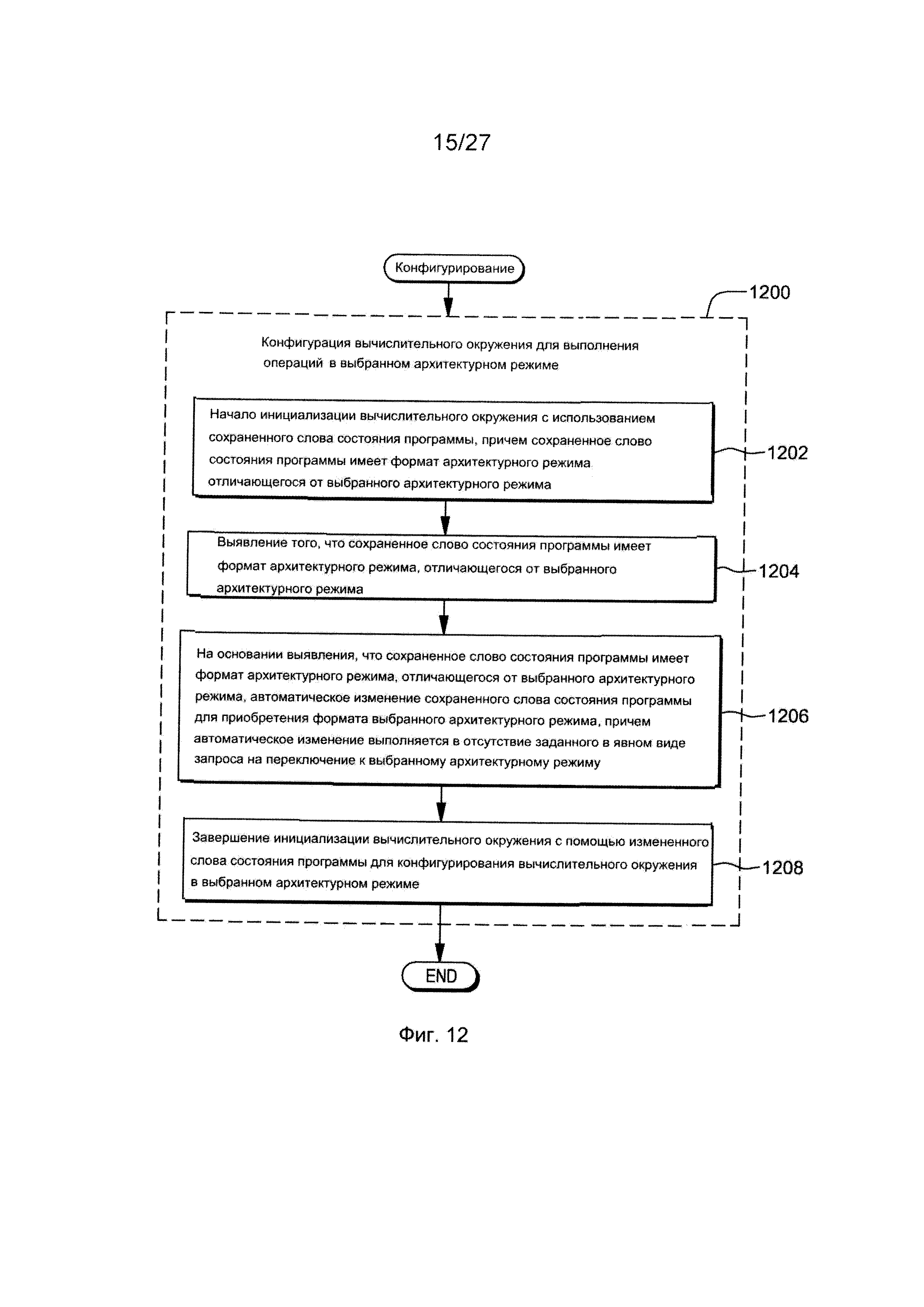

Фиг. 12 изображает один вариант осуществления логики для конфигурирования вычислительного окружения согласно предпочтительному варианту осуществления настоящего изобретения,

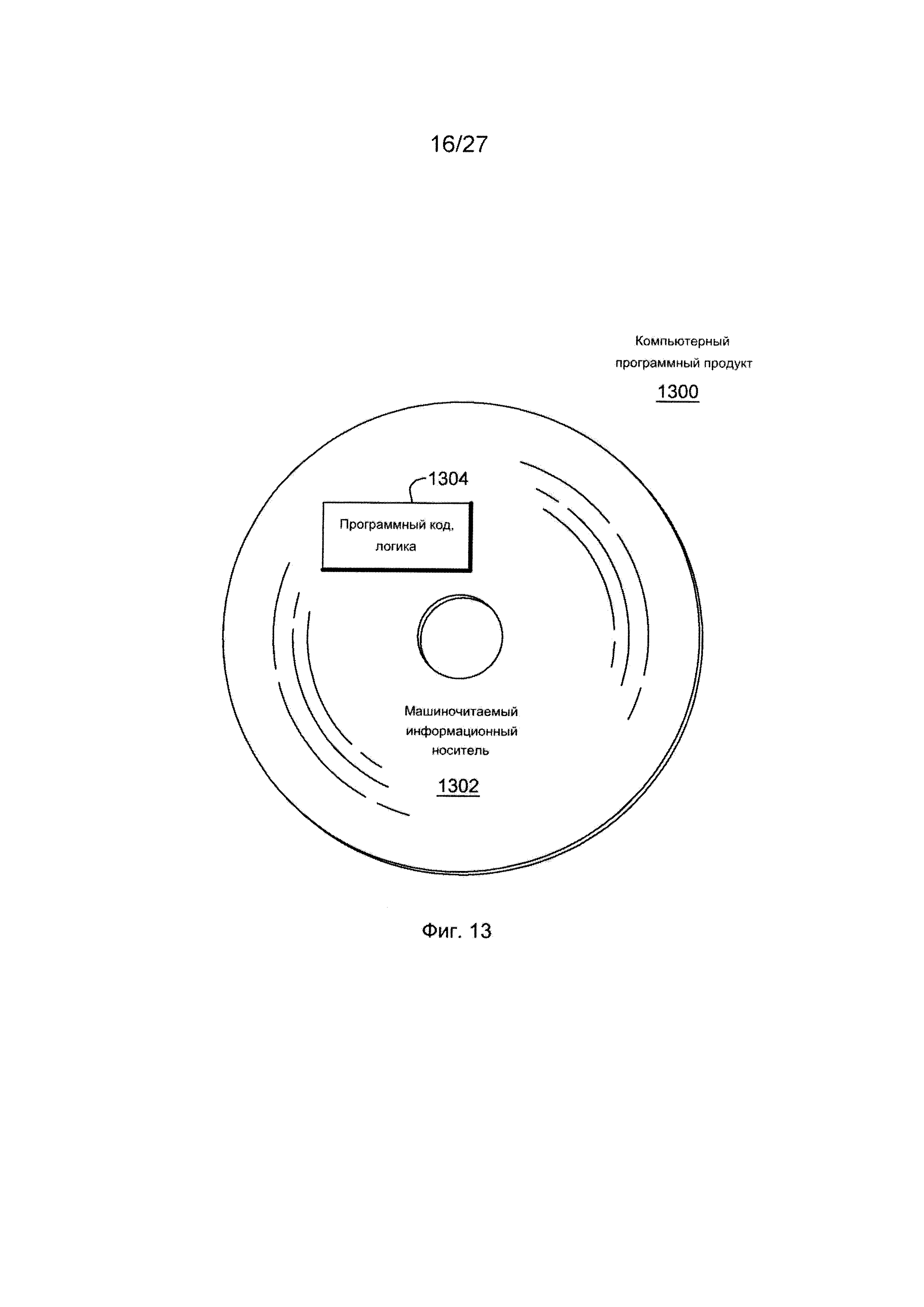

Фиг. 13 изображает один вариант осуществления компьютерного программного продукта согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

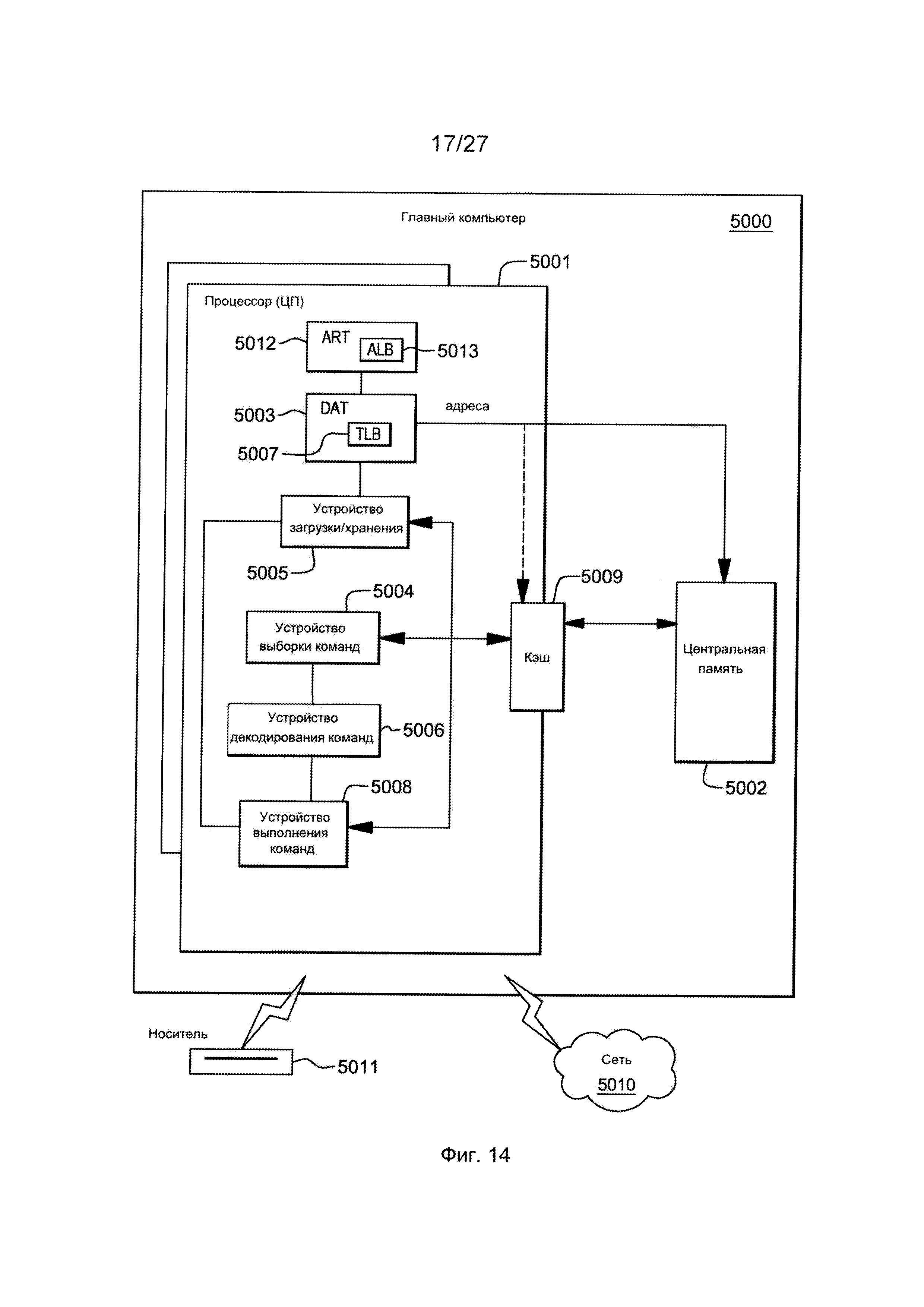

Фиг. 14 изображает один вариант осуществления системы хост-компьютера согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

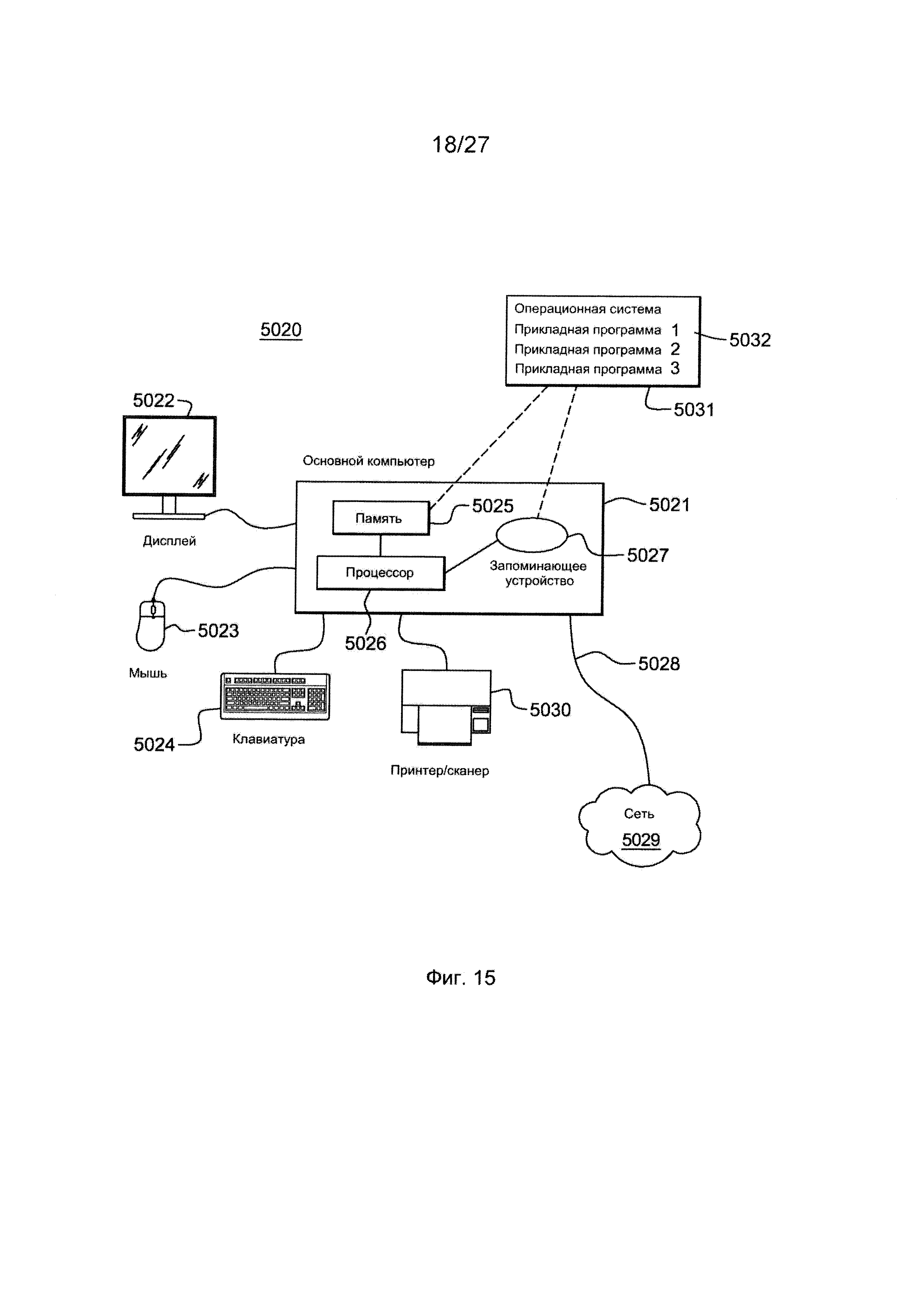

Фиг. 15 изображает другой пример компьютерной системы согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

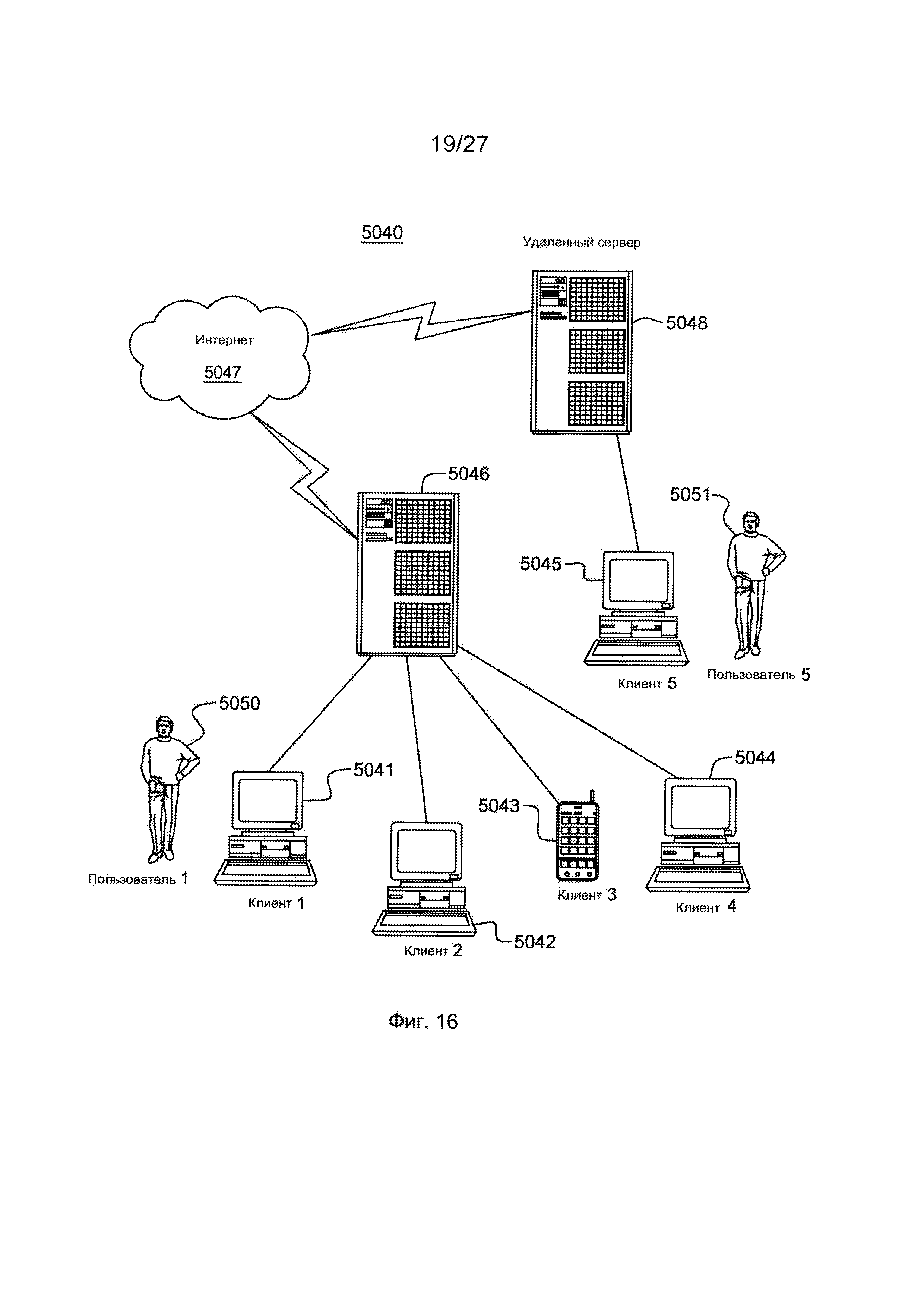

Фиг. 16 изображает другой пример содержащей компьютерную сеть компьютерной системы согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

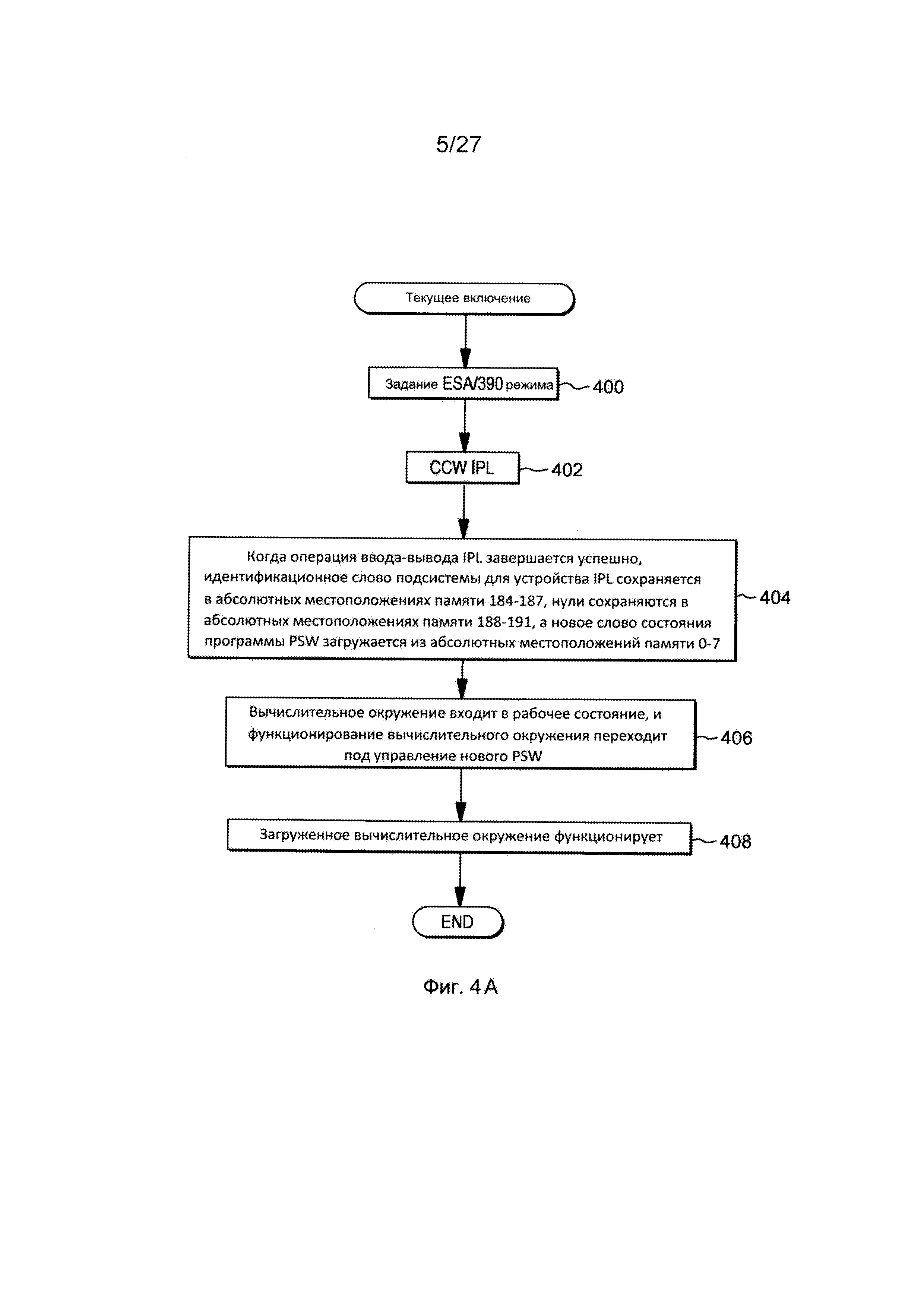

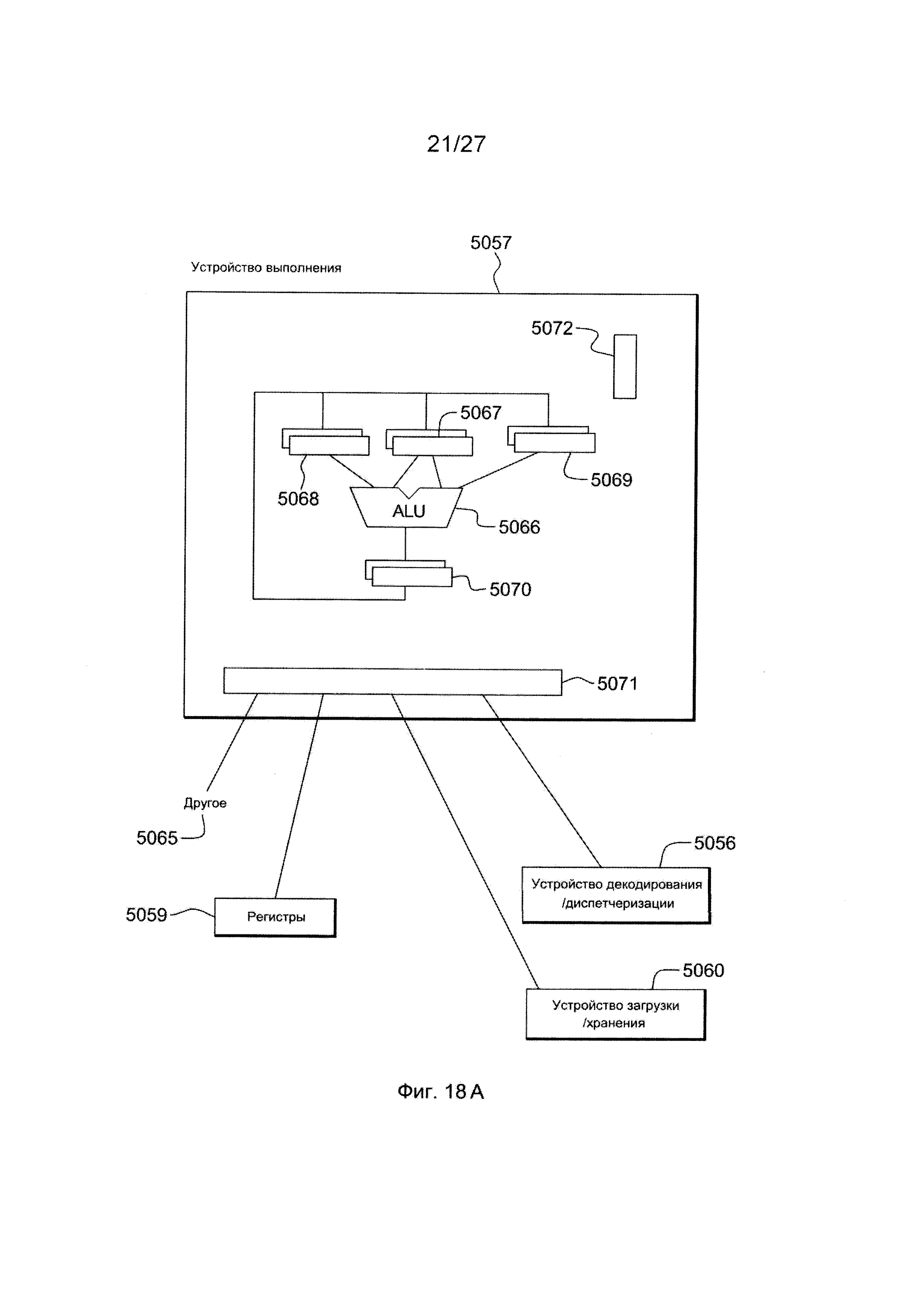

Фиг. 17 изображает один вариант осуществления различных элементов компьютерной системы согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

Фиг. 18А изображают один вариант осуществления устройства выполнения компьютерной системы на фиг. 17 согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

Фиг. 18Б изображает один вариант осуществления устройства обработки ветвлений компьютерной системы на фиг. 17 согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

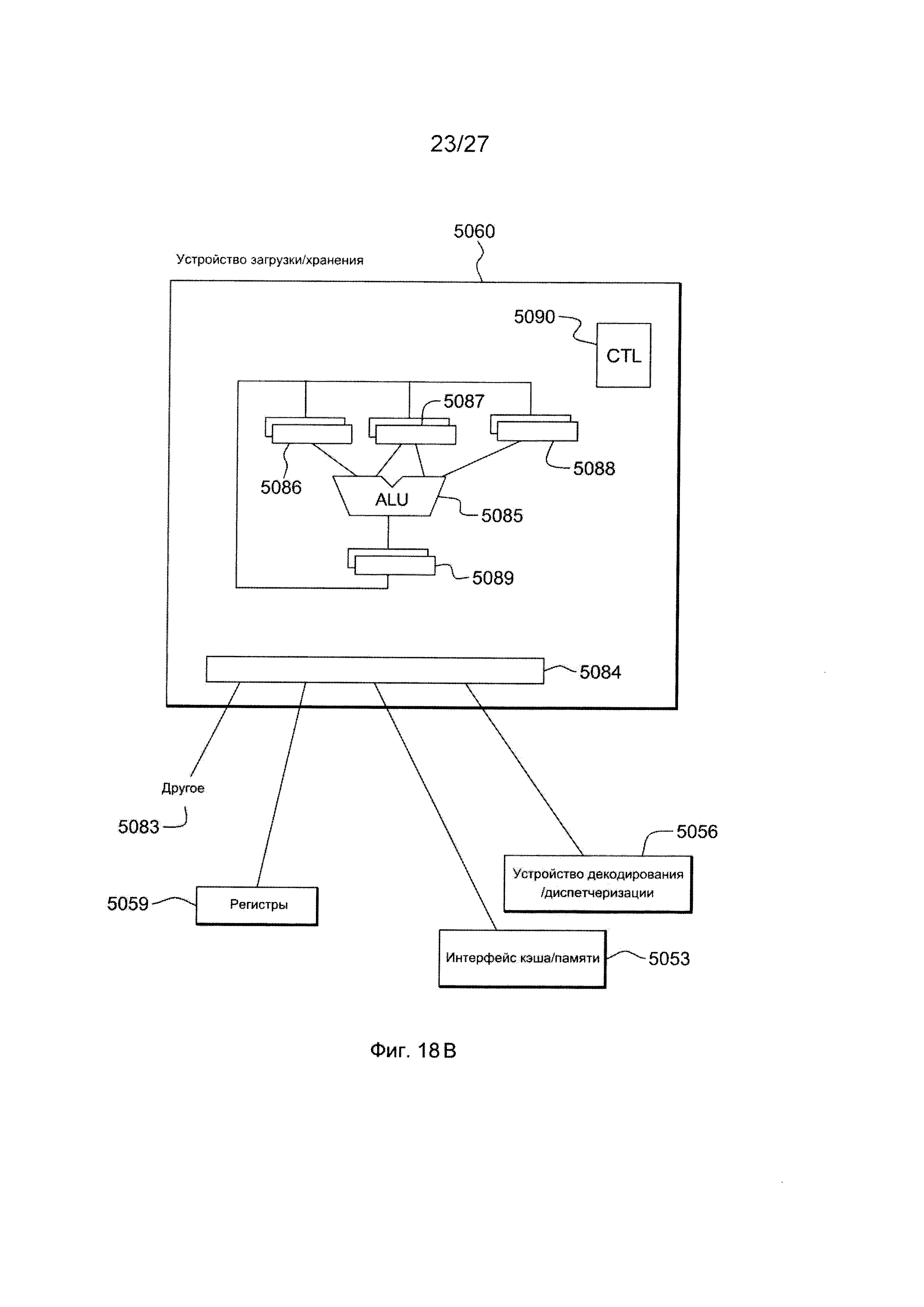

Фиг. 18В изображает один вариант осуществления устройства загрузки и хранения компьютерной системы на фиг. 17 согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

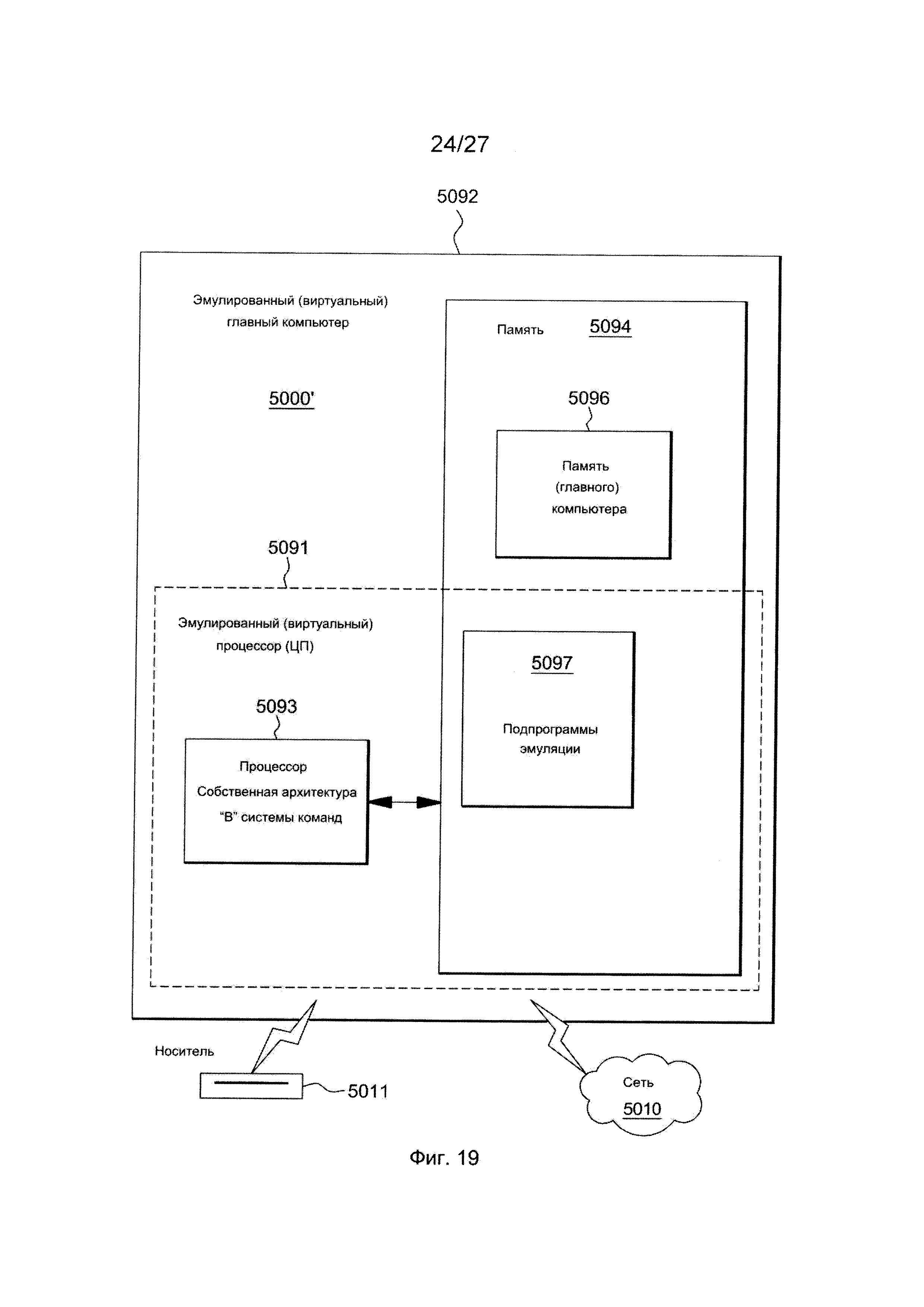

Фиг. 19 изображает один вариант осуществления эмулированной системы хост-компьютера согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

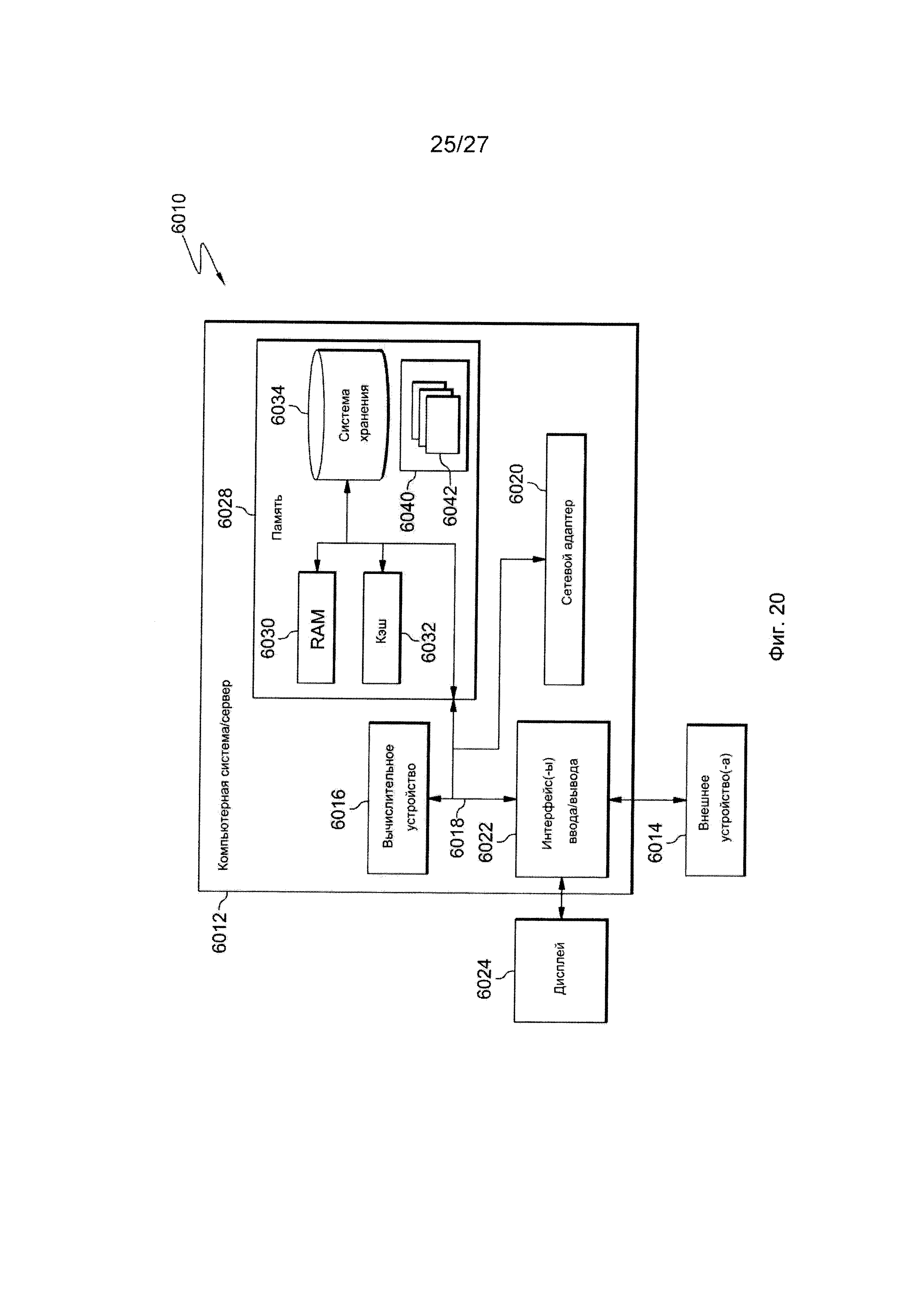

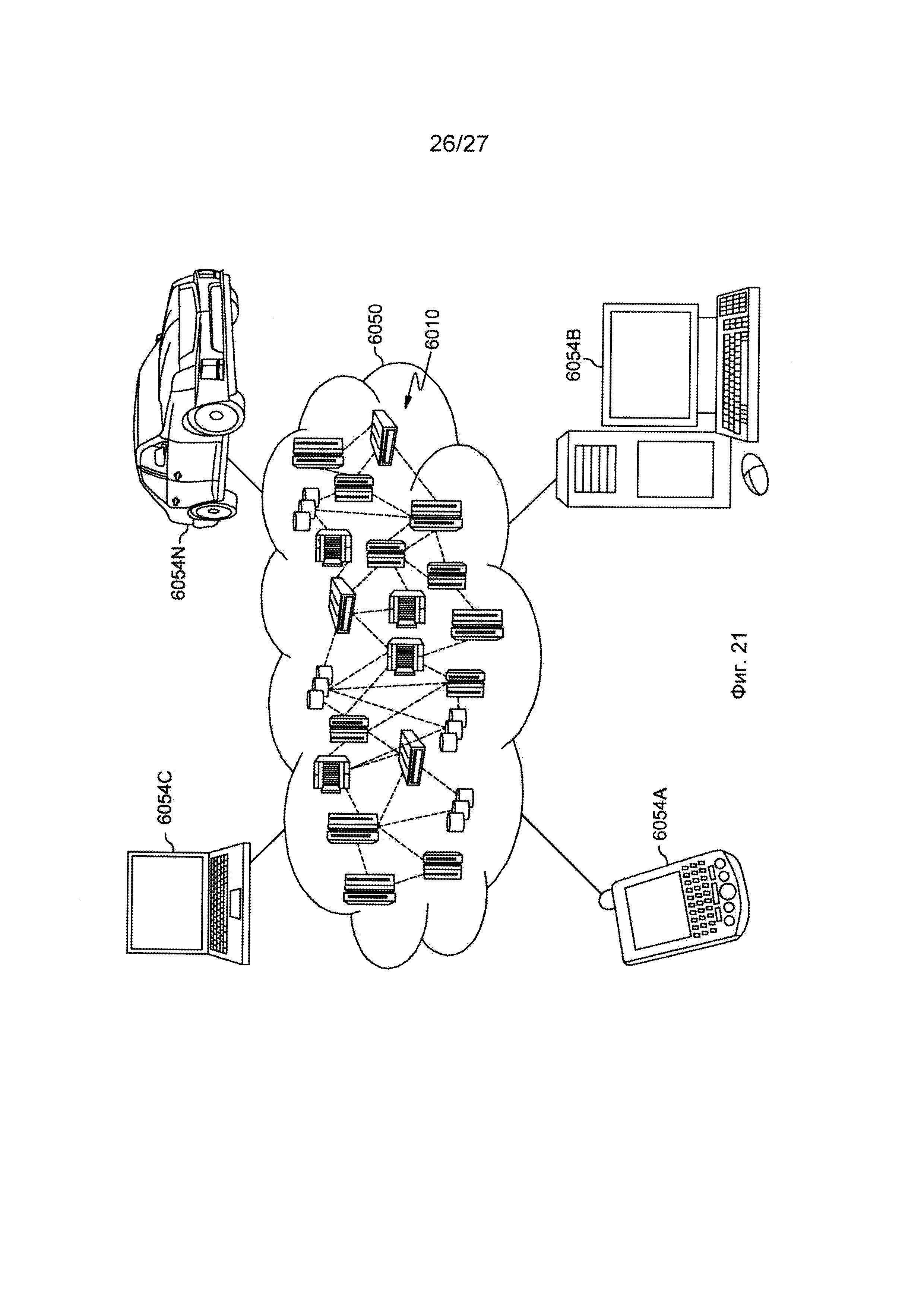

Фиг.20 изображает один вариант осуществления узла облачных вычислений согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения,

Фиг. 21 изображает один вариант осуществления окружения облачных вычислений согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения, и

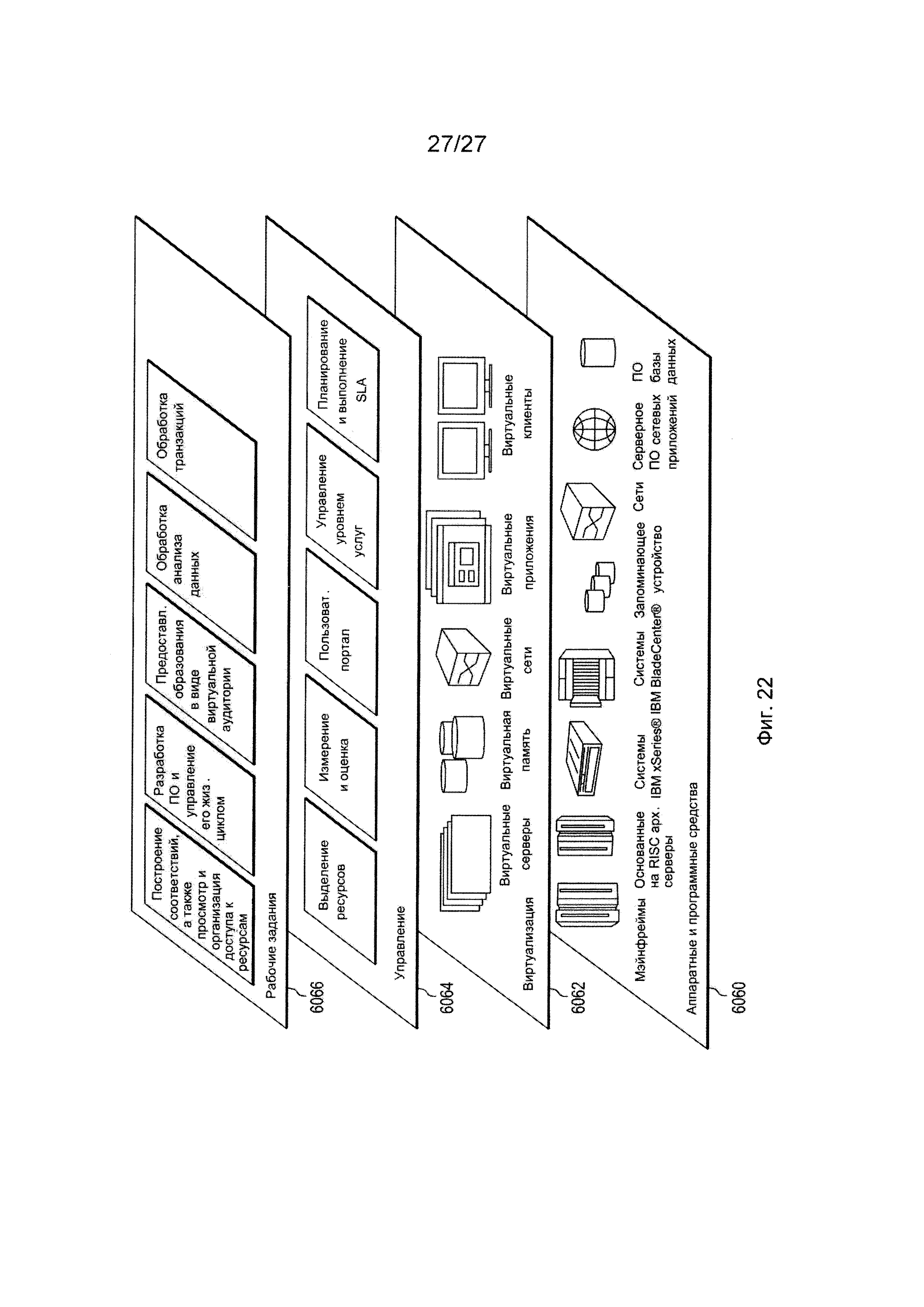

Фиг. 22 изображает один пример уровней модельной абстракции согласно известному уровню техники, в котором может быть реализован предпочтительный вариант осуществления настоящего изобретения.

Подробное описание

Согласно одному аспекту предоставляется инструмент, который ограничивает использование конфигурации посредством сконфигурированного для поддержки множественных конфигураций вычислительного окружения таким образом, что один или несколько аспектов ограниченной конфигурации являются недоступными для использования. В качестве примера, процессор конфигурируется в конфигурации архитектурного режима (САМ). В САМ, вычислительное окружение (например, процессор, логический раздел, гость), которое первоначально является сконфигурированным для нескольких архитектур, например устаревшей архитектуры и расширенной архитектуры, реконфигурируется таким образом, что оно более не поддерживает один или несколько аспектов по меньшей мере одной архитектуры, такой как устаревшая архитектура. В такой конфигурации, неподдерживаемые аспекты архитектуры не являются доступными.

В качестве одного конкретного примера, в вычислительных окружениях, поддерживающих множественные архитектуры, такие как ESA/390 и z/Архитектура, предоставляется средство конфигурации архитектурного режима (CZAM) для z/Архитектуры, которое удаляет способность использования аспектов ESA/390. Вместо этого используется z/Архитектура (и/или, в других вариантах осуществления, другая архитектура, отличная от ESA/390). CZAM может быть применено к предназначенной для исходной среды машине, логическому разделу и/или виртуальному гостю, в качестве примеров.

Один пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима описан со ссылками на фиг. 1А. Как показано на фиг. 1А, в одном примере вычислительное окружение 100 основано на z/Архитектуре, предлагаемой International Business Machines (IBM®) Corporation, Армонк, Нью-Йорк), z/Архитектура описана в публикации патента IBM под названием «z/Архитектура, принципы работы» (z/Architecture, Principles of Operation), публикация №SA22-7932-09, 10-й выпуск, сентябрь 2012. Хотя вычислительное окружение основано на z/Архитектуре, в одном предпочтительном варианте осуществления оно также поддерживает одну или несколько других архитектурных конфигураций, таких как ESA/390.

В качестве примера, вычислительное окружение 100 включает в себя центральный вычислительный комплекс (СРС) 102, присоединенный к одному или нескольким устройствам 106 ввода/вывода (I/O) через одно или несколько устройств 108 управления. Центральный вычислительный комплекс 102 включает в себя, например, память 104 процессора (известную также под названием оперативная память, основная память, центральная память), соединенную с одним или несколькими центральными процессорами (известными также под названием центральных вычислительных устройств (ЦП)) 110, и с подсистемой 111 ввода/вывода, каждый из указанных элементов описан ниже.

Память 104 процессора включает в себя, например, один или несколько разделов 112 (например, логических разделов), а также встроенное программное обеспечение 113 процессора, которое включает в себя гипервизор 114 логического раздела и другое встроенное программное обеспечение 115 процессора. Один пример гипервизора 114 логического раздела представлен администратором ресурсов процессора/системы Processor Resource/Systems Manager™ (PR/SM), предлагаемым International Business Machines Corporation, Армонк, Нью-Йорк.

Логический раздел функционирует как отдельная система и имеет в себе одно или несколько приложений 120 и, опционально, резидентную операционную систему 122, которая может отличаться для каждого логического раздела. В одном предпочтительном варианте осуществления операционная система является z/OS операционной системой, z/VM операционной системой, z/Linux операционной системой или операционной системой TPF, предлагаемой International Business Machines Corporation, Армонк, Нью-Йорк. Логическими разделами 112 управляет гипервизор 114 логических разделов, который реализован посредством встроенного программного обеспечения, функционирующего на процессорах 110. При рассмотрении в настоящем документе, встроенное программное обеспечение включает в себя, например, микрокод и/или милликод процессора. Он включает в себя, например, команды аппаратного уровня и/или структуры данных, используемые в реализации высокоуровневого машинного кода. В одном предпочтительном варианте он включает в себя, например, проприетарный код, обычно поставляемый как микрокод, который включает в себя выверенное программное обеспечение или микрокод, специфичный для используемого оборудования и управляющий доступом операционной системы к оборудованию системы.

Центральные процессоры 110 являются физическими процессорными ресурсами, выделенными логическим разделам. Конкретно, каждый логический раздел 112 имеет один или несколько логических процессоров, каждый из которых представляет собой, полностью или частично, выделенный разделу физический процессор 110. Логические процессоры конкретного раздела 112 могут быть либо выделены разделу таким образом, что базовый процессорный ресурс 110 резервируется для данного раздела, либо быть используемыми совместно с другим разделом таким образом, что базовый процессорный ресурс является потенциально доступным другому разделу. В одном из вариантов, один или несколько из ЦП включают в себя описанные в настоящем документе аспекты средства 130 конфигурации архитектурного режима.

Подсистема 111 ввода/вывода направляет поток информации между устройствами 106 ввода-вывода и основной памятью 104. Эта подсистема соединена с центральным вычислительным комплексом в том плане, что она может быть как частью центрального вычислительного комплекса, так и быть выполненной отдельной от него. Подсистема I/O освобождает центральные процессоры от задач сообщения непосредственно с устройствами ввода-вывода и позволяет обработке данных продолжаться одновременно с обработкой ввода/вывода.

Для обеспечения связи подсистема I/O использует коммуникационные адаптеры I/O.

Существуют различные типы коммуникационных адаптеров, в том числе, например, каналы, адаптеры I/O, платы протокольной управляющей информации (PCI), платы Ethernet, платы интерфейса хранения малых вычислительных машин (SCSI) и т.д. В описанном здесь конкретном примере коммуникационные адаптеры I/O являются каналами, и поэтому, подсистема I/O в настоящем документе называется канальной подсистемой. Тем не менее, данный пример является только одним из многих. Также могут использоваться и другие типы подсистем I/O.

Подсистема I/O использует один или несколько трактов ввода/вывода в качестве коммуникационных каналов при управлении потоком информации к устройствам 106 ввода-вывода или от них. В этом конкретном примере эти тракты называются канальными трактами, поскольку коммуникационные адаптеры являются каналами.

Другой пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства САМ описан со ссылками на фиг. 1Б. В этом примере вычислительное окружение 150 включает в себя центральный вычислительный комплекс 152, предоставляющий поддержку виртуальной машине. СРС 152 соединен с одним или несколькими устройствами 106 ввода/вывода (I/O) через одно или несколько устройств 108 управления. Центральный вычислительный комплекс 152 включает в себя, например, память 154 процессора (известную также под названием оперативная память, основная память, центральная память), соединенную с одним или несколькими центральными процессорами (известными также под названием центральных вычислительных устройств (ЦП)) 110, и с подсистемой 111 ввода/вывода.

Память процессора 154 включает в себя, например, одну или несколько виртуальных машин 162, а также встроенное программное обеспечение 163 процессора, который включает в себя хост-гипервизор 164 и другое встроенное программное обеспечение 165 процессора. Один пример хост-гипервизора 164 представлен z/VM®, предлагаемым International Business Machines Corporation, Армонк, Нью-Йорк.

Поддержка виртуальной машины со стороны СРС предоставляет возможность управления большим количеством виртуальных машин 162, каждая из которых способна к хостингу гостевой операционной системы 172, такой как Linux®. Каждая виртуальная машина 162 способна к функционированию в качестве отдельной системы. Это означает, что каждая виртуальная машина может быть независимо сброшена, может служить хостом для гостевой операционной системы и может работать с различными программами 120. Операционная система или прикладная программа, работающая в виртуальной машине, представляется как имеющая доступ к полной системе, но в действительности, только ее часть является доступной. Linux является зарегистрированной торговой маркой Linus Torvalds в Соединенных Штатах, в других странах, или в обеих юрисдикциях.

В этом конкретном примере модель виртуальных машин является моделью V=V, в которой абсолютная или реальная память виртуальной машины поддерживается виртуальной памятью хоста вместо реальной или абсолютной памяти. Каждая виртуальная машина имеет пространство виртуальной линейной памяти. Физические ресурсы принадлежат хосту 164, и совместно используемые физические ресурсы по мере необходимости диспетчеризируются посредством хоста к гостевым операционным системам для удовлетворения их вычислительных потребностей.

Такая модель виртуальной машины V=V (то есть, гость со страничной организацией) подразумевает, что взаимодействиями между гостевыми операционными системами и физическими совместно используемыми ресурсами машины управляет хост, поскольку большое количество гостей обычно исключает для хоста возможность простого разделения и присвоения аппаратных ресурсов сконфигурированным гостям. Один или несколько аспектов модели V=V, кроме того, описаны в публикации IBM® под названием «z/VM: Выполнение гостевых операционных систем» (Running Guest Operating Systems), IBM® публикация № SC24-5997-02, октябрь 2001.

Центральные процессоры 110 являются физическими процессорными ресурсами, которые присваиваются виртуальной машине. Например, виртуальная машина 162 включает в себя один или несколько логических процессоров, каждый из которых представляет, полностью или частично, физический процессорный ресурс 110, который может быть динамическим образом выделен виртуальной машине. Виртуальными машинами 162 управляет хост 164.

В одном предпочтительном варианте осуществления аппаратное оборудование/встроенное программное обеспечение хоста (например, z/VM®) и процессора (например, System z) взаимодействуют друг с другом управляемым совместным способом с целью обработки операций гостевой операционной системы V=V без необходимости в передаче управления между гостевой операционной системой и хостом. Гостевые операции могут быть выполнены непосредственно, без вмешательства хоста, с помощью средства, позволяющего командам выполняться в режиме интерпретации для гостя с режимом записи в память со страничной организацией. Это средство предоставляет команду запуска выполнения в режиме интерпретации (Start Interpretive Execution) (SIE), которую хост может выдавать путем назначения блока управления, называемого описанием состояния, который содержит состояние и управляющие воздействия гостя (виртуальной машины), такие как управляющие элементы выполнения и управляющие элементы режима. Команда переводит машину в режим интерпретационного выполнения, в котором гостевые команды и прерывания обрабатываются непосредственно до тех пор, пока не возникает состояние, требующее вмешательства хоста. Когда такое состояние возникает, выполнение в режиме интерпретации заканчивается и, либо реализуется прерывание хоста, либо команда SIE завершает сохранение деталей возникшего состояния, это последнее действие вызывают перехватом. Один пример выполнения в режиме интерпретации описан в работе «Система/370 - Расширенная архитектура/Выполнение в режиме интерпретации» (System/370 Extended Architecture/Interpretive Execution), IBM публикация №SA22-7095-01, сентябрь 1985.

Конкретно, в одном предпочтительном варианте осуществления средство выполнения в режиме интерпретации предоставляет команду для выполнения виртуальных машин. Эта команда, называемая запуском выполнения в режиме интерпретации (Start Interpretative Execution) (SIE), выпускается хостом, создающим гостевое окружение выполнения. Хост является управляющей программой, которая непосредственно управляет реальной машиной, а гость относится к любой виртуальной или интерпретируемой машине. Машина переводится в режим интерпретационного выполнения посредством хоста, который выдает команду SIE. В этом режиме машина предоставляет функции выбранной архитектуры (например, z/Архитектуры, ESA/390). Функции включают в себя, например, среди прочего, выполнение привилегированных и проблемных программных команд, трансляцию адресов, обработку прерываний и согласование по времени. Машина, как говорят, интерпретирует функции, которые она выполняет в контексте виртуальной машины.

Команда SIE имеет операнд, называемый описанием состояния, который включает в себя информацию, относящуюся к текущему состоянию гостя. Когда выполнение SIE заканчивается, представляющая состояние гостя информация, включая сюда PSW гостя, сохраняется в описании состояния прежде, чем управление будет возвращено хосту.

Архитектура выполнения в режиме интерпретации предоставляет режим записи в память для абсолютной памяти, называемый режимом записи в память со страничной организацией. В режиме записи в память со страничной организацией динамическая трансляция адресов на уровне хоста используется для отображения гостевой основной памяти. Хост имеет способность к распределению реальной памяти гостей с режимом записи в память со страничной организацией по применимым пакетам в произвольных местоположениях в основной памяти хоста при помощи DAT хоста, и к разбиению гостевых данных на страницы для вспомогательной памяти. Такая техника обеспечивает гибкость при выделении реальных машинных ресурсов и, в то же время, сохраняет для гостя ожидаемое внешнее представление непрерывного диапазона абсолютной памяти.

Окружение виртуальной машины может дважды вызывать DAT для применения: сначала на гостевом уровне, для трансляции гостевого виртуального адреса посредством управляемых гостем трансляционных таблиц в гостевой действительный адрес, а затем, для гостя со страничной организацией, на уровне хоста, для трансляции соответствующего виртуального адреса хоста в действительный адрес хоста.

В определенных случаях, хосту приходится вмешиваться в обычно делегируемые машине операции. С этой целью описание состояния включает в себя управляющие элементы, задаваемые хостом для «прерывания» или перехвата особых состояний. Биты управления перехватом запрашивают возвращение машиной управления к имитации хоста при встрече с конкретными гостевыми командами. Интервенционные управляющие элементы захватывают основные сведения по активированному состоянию в PSW таким образом, что хост может предоставить для гостя прерывание, которое он удерживает отложенным. В то время как интерпретация продолжается, интервенционные управляющие элементы могут быть асинхронным образом заданы посредством хоста на другом реальном процессоре. Машина периодически повторно выбирает управляющие элементы из памяти таким образом, что распознаются обновленные значения. Гостевые прерывания, таким образом, могут быть сделаны отложенными без преждевременного нарушения интерпретации.

В одном предпочтительном варианте настоящего изобретения, управляющие элементы режима в описании состояния задают выполнение гостя в режиме ESA/390 или z/Архитектуры, а также выбирают один из нескольких способов представления гостевой основной памяти гостевой виртуальной машины в памяти хоста. Согласно одному предпочтительному варианту настоящего изобретения, в управляющем элементе состояния предоставляется бит управления для выбора между пребыванием гостя в первом или втором архитектурном режиме (например, z/Архитектуре или ESA/390, соответственно). Согласно другому предпочтительному варианту настоящего изобретения, две различные команды могут предоставлять хосту способность по созданию первой и второй гостевой виртуальной машины, например, могут быть предоставлены различные команды SIEz и SIEe для запуска гостевых машин в режиме z/Архитектуры и ESA/390, соответственно.

Команда SIE прогоняет диспетчеризированный управляющей программой виртуальный сервер до тех пор, пока либо интервал времени сервера не оказывается использованным, либо сервер не попытается выполнить операцию, которую не могут виртуализировать аппаратные средства, или для выполнения которой управляющая программа должна восстановить свое управление. На этом этапе выполнение команды SIE заканчивается и управление возвращается к управляющей программе, которая либо имитирует команду, либо переводит виртуальный сервер в состояние принудительного ожидания. По завершении, управляющая программа вновь вводит виртуальный сервер в план для выполнения, и цикл вновь запускается. Таким образом, полные возможности и скорость ЦП являются доступными для виртуального сервера. Перехвату подвергаются только те привилегированные команды, которые требуют помощи со стороны управляющей программы или проверки ею их правильности. Такие перехваты SIE, как они известны, также используются управляющей программой для накладывания ограничений на операции, которые виртуальный сервер может выполнять на физическом устройстве.

Более подробная информация относительно SIE изложена в работе «Интерпретирующе-выполняющая архитектура ESA/390, основания для VM/ESA» (ESA/390 interpretive-execution architecture, foundation for VM/ESA), Осисек и др. (Osisek et al), IBM Systems Journal, том 30, №1, январь 1991, стр. 34-51.

Другой пример вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима описан со ссылками на фиг. 2. В этом примере вычислительное окружение 200 включает в себя неразбитое на разделы окружение, которое может быть сконфигурировано для нескольких архитектурных режимов, в том числе, z/Архитектуры и ESA/390. Это окружение включает в себя, например, процессор (центральное вычислительное устройство - ЦП) 202, который включает в себя, например, средство 204 конфигурации архитектурного режима, а также один или несколько кэшей 206. Процессор 202 коммуникативно соединен с имеющим один или несколько кэшей 210 участком 208 памяти и с подсистемой 212 ввода/вывода (I/O). Подсистема I/O 212 коммуникативно соединена с внешними устройствами 214 ввода-вывода, которые могут включать в себя, например, устройства ввода данных, датчики и/или устройства вывода, такие как дисплеи. Другой предпочтительный вариант настоящего изобретения вычислительного окружения для охвата и использования одного или нескольких аспектов средства конфигурации архитектурного режима описан со ссылками на фиг. 3А. В этом примере вычислительное окружение 300 включает в себя, например, предназначенное для исходной среды центральное вычислительное устройство (ЦП) 302, память 304, а также одно или несколько устройств ввода-вывода и/или интерфейсов 306, соединенных друг с другом, например, через одну или несколько шин 308 и/или других присоединений. Например, вычислительное окружение 300 может включать в себя процессор PowerPC или сервер Power Systems, предлагаемые International Business Machines Corporation, Армонк, Нью-Йорк, HP Superdome с процессорами Intel Itanium II, предлагаемые Hewlett Packard, Пало-Альто, Калифорния, и/или другие машины, основанные на архитектурах, предлагаемых International Business Machines Corporation, Hewlett Packard, Intel, Oracle или другими. Intel и Itanium являются торговыми марками или зарегистрированными торговыми марками Intel Corporation или ее филиалов в Соединенных Штатах и других странах.

Предназначенное для исходной среды центральное вычислительное устройство 302 включает в себя один или несколько предназначенных для исходной среды регистров 310, таких как один или несколько регистров общего назначения и/или один или несколько регистров особого назначения, используемых в процессе обработки в пределах окружения, а также средство 311 конфигурации архитектурного режима. Эти регистры включают в себя информацию, представляющую состояние окружения на какой-либо конкретный момент времени.

Кроме того, предназначенное для исходной среды центральное вычислительное устройство 302 выполняет команды и код, которые сохраняются в памяти 304. В одном конкретном примере центральное вычислительное устройство выполняет код 312 эмулятора, сохраняемый в памяти 304. Этот код активирует вычислительное окружение, сконфигурированное в одной архитектуре, для эмуляции одной или нескольких других архитектур. Например, код 312 эмулятора позволяет основанным на отличных от z/Архитектуры архитектурах машинам, таким как процессоры PowerPC, серверы Power Systems, серверы HP Superdome или другие, эмулировать z/Архитектуру (и/или ESA/390) и выполнять программное обеспечение и команды, разработанные на основе z/Архитектуры.

Более подробная информация относительно кода 312 эмулятора приведена со ссылками на фиг. 3Б. Сохраняемые в памяти 304 гостевые команды 350 содержат команды программного обеспечения (например, коррелирующие с машинными командами), которые были разработаны для выполнения в архитектуре, отличной от таковой для предназначенного для исходной среды ЦП 302. Например, гостевые команды 350 могут быть разработаны для выполнения на процессоре 202 z/Архитектуры, но вместо этого, эмулируются на предназначенном для исходной среды ЦП 302, который может быть представлен, например, процессором Intel Itanium II. В одном примере, код 312 эмулятора включает в себя подпрограмму 352 выборки команд для получения одной или нескольких гостевых команд 350 из памяти 304 и, опционально, для предоставления локальной буферизации для полученных команд. Данный код также включает в себя подпрограмму 354 трансляции команд для выявления типа полученной гостевой команды и для трансляции гостевой команды в одну или несколько соответствующих команд 356 исходной среды. Такая трансляция включает в себя, например, идентификацию функции, которая подлежит выполнению посредством гостевой команды, и выбор предназначенной для исходной среды команды (команд) для выполнения этой функции.

Кроме того, код 312 эмулятора включает в себя подпрограмму 360 управления эмуляцией для принуждения команд исходной среды к выполнению. Подпрограмма 360 управления эмуляцией может принудить предназначенное для исходной среды ЦП 302 к выполнению подпрограммы команд исходной среды, которые эмулируют одну или несколько ранее полученных гостевых команд и, в конце такого выполнения, возвращают управление подпрограмме выборки команд для эмуляции получения следующей гостевой команды или группы гостевых команд. Выполнение команд 356 исходной среды может включать в себя загрузку данных в регистр из памяти 304, сохранение данных обратно в память из регистра, или выполнение арифметической или логической операции некоторого типа, как задано подпрограммой трансляции.

Каждая подпрограмма, например, реализуется в программном обеспечении, сохраняемом в памяти и выполняемом посредством предназначенного для исходной среды центрального вычислительного устройства 302. В других примерах, одна или несколько из числа подпрограмм или операций, реализуются во встроенном программном обеспечении, аппаратных средствах, программном обеспечении или в некоторой комбинации из этих средств. Регистры эмулированного процессора могут быть эмулированы с помощью регистров 310 предназначенного для исходной среды ЦП или при помощи местоположений в памяти 304. В предпочтительных вариантах осуществления гостевые команды 350, команды 356 исходной среды и код 312 эмулятора могут находиться в той же самой памяти или могут быть рассредоточены среди различных запоминающих устройств.

Описанные выше вычислительные окружения являются только примерами пригодных к использованию вычислительных окружений. Могут быть использованы и другие окружения, в том числе, но не ограничиваясь, другие неразбитые на разделы окружения, другие разбитые на разделы окружения и/или другие эмулированные окружения, варианты осуществления не ограничиваются каким-либо окружением.

Согласно одному или несколькими аспектам средство конфигурации архитектурного режима (САМ) инсталлируется в одном или нескольких процессорах (например, центральных вычислительных устройствах) вычислительного окружения для управления реконфигурированием окружения. Например, когда средство САМ инсталлировано в вычислительном окружении, поддерживающем несколько архитектурных режимов, вычислительное окружение реконфигурируется таким образом, что ограничивается использование одного или нескольких аспектов по меньшей мере одного из архитектурных режимов.

Один конкретный пример средства конфигурации архитектурного режима представлен средством конфигурации архитектурного режима (CZAM) для z/Архитектуры. Инсталляция CZAM обозначается, например, индикатором инсталляции средства, например битом 138, которому задается значение, например, единица. В одном конкретном примере, когда биту 138 задано значение единица, средство CZAM инсталлировано, и, когда инсталлировано, нормальный сброс и чистый сброс переводят конфигурацию в архитектурный режим z/Архитектуры. Таким образом, биту функции, например биту 2, указывающему на активность архитектурного режима z/Архитектуры, также задается значение единица, в данном примере.

За счет инсталляции CZAM вычислительное окружение (например, одиночный процессор, логический раздел, виртуальный гость и т.д.) реконфигурируется таким образом, что более не поддерживаются один или несколько аспектов выбранной архитектуры, например ESA/390. Различные более не поддерживающиеся аспекты и/или некоторые затронутые установкой CZAM процессы описаны ниже.

Хотя в описанных в настоящем документе вариантах осуществления совокупность архитектурных режимов включает в себя устаревшую архитектуру (например, ESA/390) и расширенную архитектуру (например, z/Архитектуру), и аспекты устаревшей архитектуры ESA/390 более не поддерживаются, другие варианты осуществления могут включать в себя другие архитектуры. ESA/390 и z/Архитектура являются только примерами.

Один из затронутых инсталляцией CZAM процессов представлен процессом включения. Для описания того, как этот процесс затрагивается, первоначально описан процесс включения для окружения, поддерживающего множественные архитектурные конфигурации и не включающего в себя функцию CZAM, со ссылками на фиг. 4А-4Б, а затем процесс включения для окружения, сконфигурированного для множественных архитектурных конфигураций, и включающего в себя средство CZAM, описан со ссылками на фиг. 6А-6Б. Включение для системы содержит, например, этапы запуска системы и инициации последовательности загрузки или других средств инициирования операций в системе. Это может соответствовать физическому включению, аппаратному сбросу и/или виртуальному включению (например, в эмулированной системе, виртуальной машине или гостевом окружении).

При обращении первоначально к фиг. 4А, при условии, что процессор вычислительного окружения был включен, а кнопка оператора, например кнопка нормальной загрузки или кнопка чистой загрузки, была активирована, процессор входит в состояние загрузки и задает вычислительному окружению конкретный архитектурный режим, например режим ESA/390, ЭТАП 400. Например, выполняется начальная загрузка программы (IPL), такая как начальная загрузка программы (IPL) управляющего слова (CCW) канала, ЭТАП 402. Начальная загрузка программы предоставляет ручные средства для принуждения к считыванию программы из заданного устройства и для инициирования выполнения этой программы. IPL типа CCW инициируется вручную посредством задания средствам управления адресом загрузочного устройства значения в виде четырехзначного числа для обозначения устройства ввода данных, и посредством последующей активации кнопки чистой загрузки или нормальной загрузки для конкретного ЦП.

Активация кнопки чистой загрузки вызывает выполнение чистого сброса на конфигурации, а активация кнопки нормальной загрузки вызывает выполнение начального сброса ЦП на данном ЦП (ЦП, на котором кнопка была активирована), сброс ЦП подлежит распространению на все другие ЦП в конфигурации, а сброс подсистемы выполняется на остаточной части конфигурации. Активация кнопки чистой загрузки или кнопки нормальной загрузки задает архитектурный режим (например, ESA/390).

В загрузочной части операции, после выполнения сброса, этот ЦП входит в состояние загрузки. Данный ЦП не обязательно входит в остановленное состояние в процессе выполнение операций по сбросу. Индикатор загрузки включен, когда ЦП находится в состоянии загрузки.

Впоследствии, инициируется операция считывания из устройства ввода-вывода, указанного посредством средств управления адресом загрузочного устройства. Эффект выполнения программы управления работой канала ввода-вывода состоит в том, как если формат 0 управляющего слова CCW канала, начинающийся в абсолютной местоположении 0 памяти, задает команду считывания с нулевыми значениями битов модификатора, адресом данных ноль, отсчетом байтов 24, с метками команды с признаком цепочки и SLI (интерпретатора логики служб) равными единицам, и всеми другими метками равными нолям.

Когда операция ввода-вывода IPL завершается успешно, идентификационное слово подсистемы для устройства IPL сохраняется в выбранных абсолютных местоположениях памяти (например, ячейках 184-187), нули сохраняются в других выбранных абсолютных местоположениях памяти (например, местоположениях 188-191), а новое слово состояния программы (PSW) загружается из выбранных абсолютных местоположений памяти (например, местоположений 0-7), ЭТАП 404. Слово состояния программы управляет операциями вычислительного окружения.

Если загрузка PSW является успешной, и не обнаружено каких-либо сбоев машины, данный ЦП покидает состояние загрузки, и индикатор нагрузки выключается. Если управление производительностью задано в положение обработки, ЦП входит в рабочее состояние, и функционирование вычислительного окружения переходит под управление нового слова (PSW) состояния программы, ЭТАП 406. Загруженное вычислительное окружение затем функционирует, ЭТАП 408, как далее описано со ссылками на фиг.4Б.

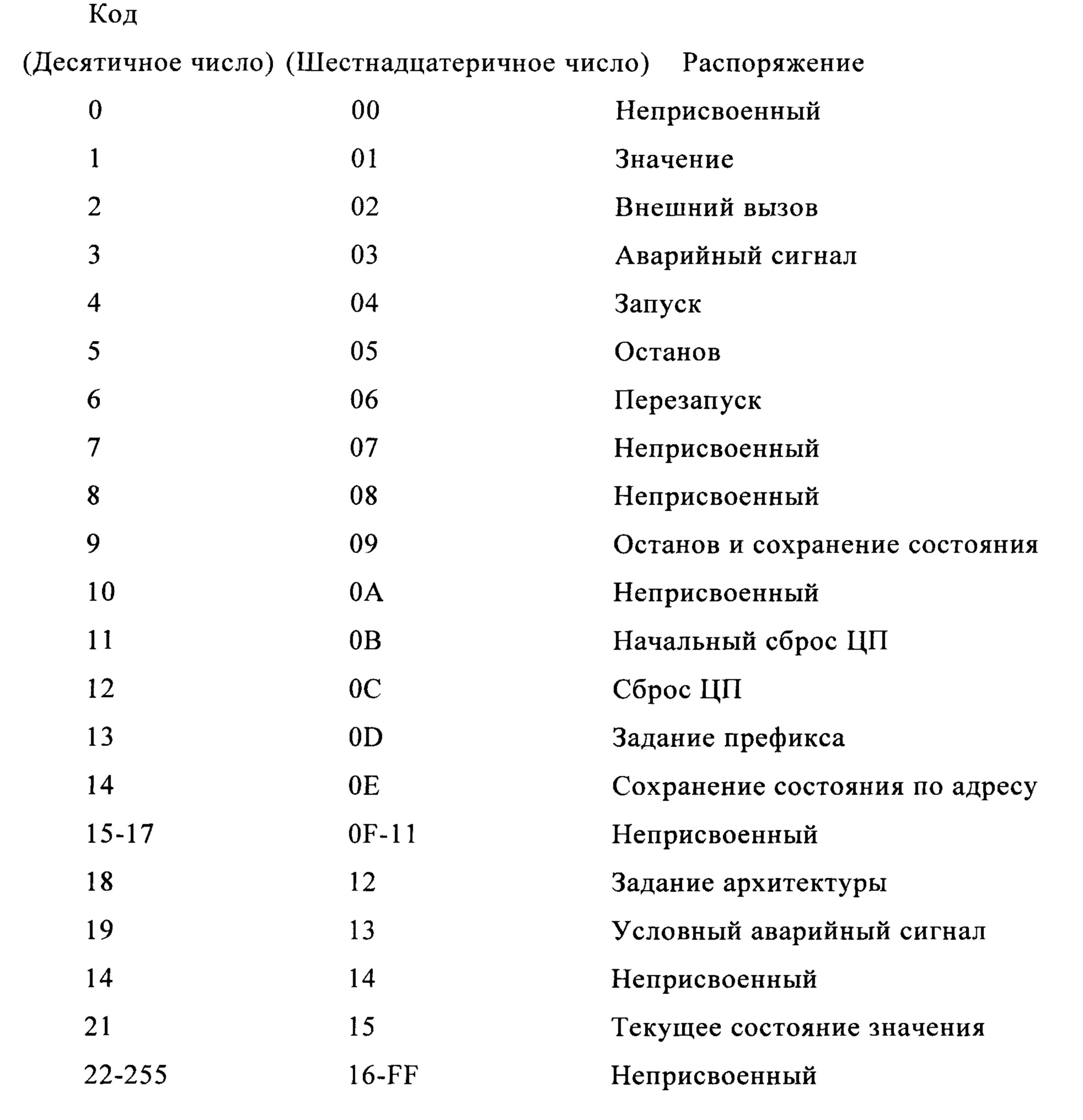

Согласно фиг. 4Б, загруженное вычислительное окружение инициируется в режиме ESA/390, ЭТАП 420 и, таким образом, операции выполняются в режиме ESA/390, ЭТАП 422. В некоторый момент может быть выполнен запрос на изменение архитектурного режима от ESA/390 к z/Архитектуре. Конкретно, программа отправляет код распоряжения (например, код, обозначающий задание архитектуры) к процессору, который выдает команду процессора (SIGP) обработки сигналов с кодом распоряжения для переключения от режима ESA/390 к режиму z/Архитектуры, ЭТАП 424. Например, используется средство подачи сигнала и ответа ЦП, который включает в себя команду процессора обработки сигналов (описанную ниже) и механизм для интерпретирования кодов распоряжений сервера и реагирования на них, в том числе, на код задания архитектуры. Средство предоставляет возможности связи между ЦП, включая сюда передачу, получение и декодирование набора присвоенных кодов распоряжений, инициирование указанной операции, а также отправку ответа к ЦП обработки сигналов. Посредством использования задания архитектуры архитектурному режиму задается требуемая конфигурация, например z/Архитектура. Более подробная информация по этой обработке приведена ниже.

После этого, производится выявление относительно того, была ли операция SIGP принята, ИНФОРМАЦИОННЫЙ ЗАПРОС 426. На основании кода возврата могут быть диагностированы несколько состояний ошибки, включая сюда указание на «недопустимый параметр», когда было выявлено, что ЦП уже находится в заданном посредством кода архитектурном режиме (то есть, что задание архитектуры представляет собой переключение к текущему режиму как таковому, в отличие от переключения с одного режима к другому режиму). Если SIGP принимается, а задание архитектуры представляет собой допустимую операцию по переключению режима, то все получившие операцию SIGP процессоры вычислительного окружения переходят в режим z/Архитектуры с использованием, например, описанной в настоящем документе обработки задания архитектуры, ЭТАП 428. Однако, если операция SIGP не является допустимой, обозначается ошибка, ЭТАП 430.

Как описано выше, операция включения загружает слово состояния программы. Один предпочтительный вариант настоящего изобретения формата слова состояния программы (PSW) описан со ссылками на фиг. 5. Согласно фиг. 5, в этом примере формат слова состояния программы является форматом ESA/390, за исключением того, что бит 31 показан как ЕА, как обозначено ниже. В одном предпочтительном варианте осуществления настоящего изобретения слово 500 состояния программы включает в себя, в качестве примера, следующие поля:

Маска PER (R) 502: Бит 1 управляет активацией в ЦП прерываний, связанных с регистрацией (PER) программных событий. Когда бит представлен нолем, никакое событие PER не может вызвать прерывание. Когда бит представлен единицей, прерывания разрешены согласно битам маски события PER в регистре 9 управления,

Режим DAT (Т) 504: Бит 5 управляет наличием скрытой динамической трансляции (DAT) адресов для логических адресов и адресов команд, используемых для получения доступа к памяти. Когда бит представлен нолем, DAT выключена, и логические адреса и адреса команд обрабатываются как действительные адреса. Когда бит представлен единицей, DAT включена, а механизм динамической трансляции адресов вызван.

Маска ввода/вывода (10) 506: Бит 6 управляет активацией в ЦП прерываний для I/O. Когда бит представлен нолем, прерывание I/O не может произойти. Когда бит представлен единицей, прерывания I/O подвергаются воздействию битов маски подкласса прерывания I/O в регистре 6 управления. Когда бит маски подкласса прерывания I/O представлен нолем, прерывание I/O для данного подкласса прерывания I/O не может произойти, когда бит маски подкласса прерывания I/O представлен единицей, прерывание I/O для данного подкласса прерывания I/O может произойти.

Внешняя маска (ЕХ) 508: Бит 7 управляет активацией в ЦП прерываний посредством условий, включаемых во внешний класс. Когда бит представлен нолем, внешнее прерывание не может произойти. Когда бит представлен единицей, внешнее прерывание подвергается воздействию соответствующих битов подкласса внешней маски в регистре 0 управления. Когда бит подкласса представлен нолем, связанные с подклассом условия не могут вызвать прерывание. Когда бит подкласса представлен единицей, прерывание в этом подклассе может произойти.

Ключ PSW (Key) 510: Биты 9-11 формируют ключ доступа для обращения к памяти посредством ЦП. Если обращение является объектом управляемой ключом защиты, ключ PSW согласовывается с ключом защиты памяти при сохранении информации или при выборке информации из защищенного от выборки местоположения. Тем не менее, для каждого из числа операндов Перейти к первичному выражению, Перейти ко вторичному выражению, Перейти с ключом, Перейти с исходным ключом и Перейти с целевым ключом, а также для одного или для обоих операндов Перейти с необязательными спецификациями, вместо ключа PSW используется ключ доступа, заданный как операнд.

Бит 12 512: Этот бит указывает на текущий архитектурный режим. Он имеет значение единица для формата PSW для ESA/390. Для формата PSW для z/Архитектуры это значение бита задается нолем. При пребывании в режиме z/Архитектуры, загрузка расширенной PSW команды (LPSWE) задана для загрузки истинного PSW для z/Архитектуры (которое имеет другой формат, отличный от описанного в настоящем документе формата, и включающий в себя наличие адреса команды в битах 64-127). Тем не менее, загрузка PSW (LPSW) в ESA/390 все еще поддерживается и может быть использована для загрузки формата PSW для ESA/390. Когда LPSW выполняется, а вычислительное окружение находится в режиме z/Архитектуры, процессор расширяет формат PSW для ESA/390 до формата для z/Архитектуры, включая сюда инвертирующий бит 12. Эта операция является обратной к сворачиванию формата PSW для z/Архитектуры, которое операционная система выполняет для создания формата PSW для ESA/390. Таким образом, в вычислительных окружениях, поддерживающих и ESA/390 и z/Архитектуру, когда копия PSW размещается в памяти, операционная система сворачивает полное PSW для z/Архитектуры к размеру и формату PSW для ESA/390. Таким образом другое программное обеспечение с зависимостями от формата PSW может не знать о Z/Архитектуре PSW.

Маска машинного контроля (М) 514: Бит 13 управляет активацией в ЦП прерываний посредством условий машинного контроля. Когда бит представлен нолем, прерывание машинного контроля не может произойти. Когда бит представлен единицей, прерывания машинного контроля вследствие повреждения системы и повреждения обработки команд являются разрешенными, но прерывания вследствие других условий подкласса машинного контроля подвергаются воздействию битов маски подкласса в регистре 14 управления.

Состояние ожидания (W) 516: Когда бит 14 представлен единицей, ЦП ожидает, то есть, посредством ЦП никакие команды не обрабатываются, но могут иметь место прерывания. Когда бит 14 представлен нолем, выборка и выполнение команды происходят нормальным способом. Когда бит представлен единицей, индикатор ожидания представлен единицей.

Заданный режим (Р) 518: Когда бит 15 представлен единицей, ЦП находится в заданном режиме. Когда бит 15 представлен нолем, ЦП находится в супервизорном режиме. В супервизорном режиме все команды являются допустимыми. В заданном режиме являются допустимыми только те команды, которые предоставляют значащую информацию заданной программе, и которые не могут затронуть целостность системы, такие команды называют непривилегированными командами. Команды, которые не являются допустимыми в заданном режиме, называют привилегированными командами. Когда ЦП в заданном режиме пытается выполнить привилегированную команду, распознается исключение по привилегированной операции. Другая группа команд, называемых полупривилегированными командами, выполняется посредством ЦП в заданном режиме только в том случае, когда выполняются специальные проверки полномочий, в противном случае, распознается исключение по привилегированной операции или какое-либо другое программное исключение, в зависимости от того конкретного требования, которое было нарушено.

Управление адресным пространством (AS) 520: Биты 16 и 17 совместно с битом 5 PSW управляют режимом трансляции.

Условный код (СС) 522: Биты 18 и 19 представляют собой два бита условного кода.

Условному коду присваивают значения 0, 1, 2 или 3 в зависимости от результата, полученного при выполнении конкретных команд. Большинство арифметических и логических операций, а также некоторые другие операции присваивают значения условного кода. Команда BRANCH ON CONDITION (перехода по условию) может задавать любой выбор значений условного кода в качестве критерия ветвления.

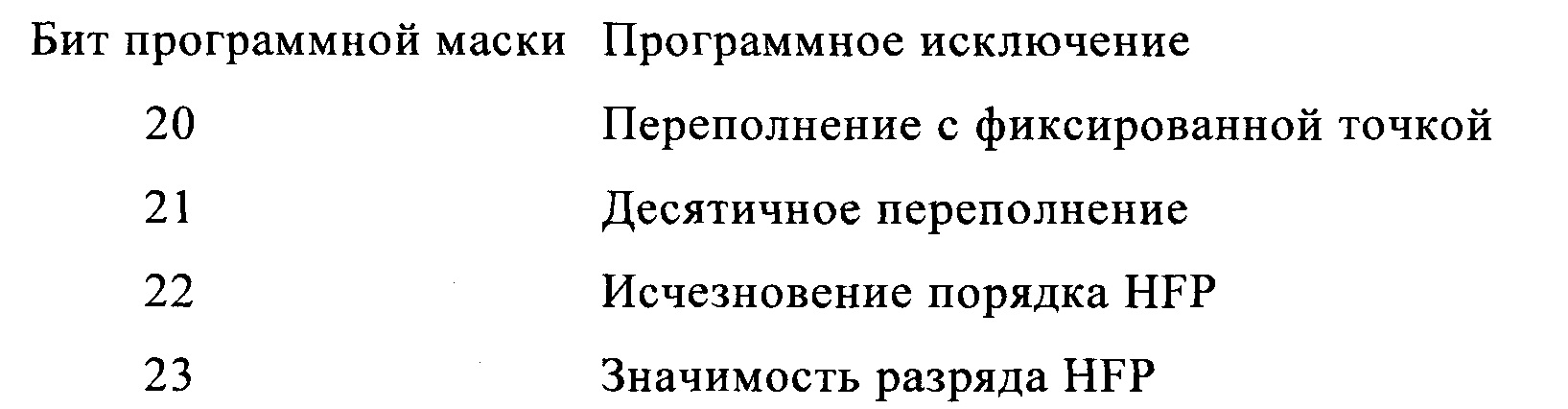

Программная маска 524: Биты 20-23 представляют собой четыре бита программной маски. Каждый бит связан с программным исключением нижеследующим образом:

Когда бит маски представлен единицей, результатом исключения является прерывание. Когда бит маски представлен нолем, не происходит никакого прерывания. Задание бита маски исчезновения порядка HFP для бита маски значимости разряда HFP также задает способ завершения операции при осуществлении соответствующего исключения.

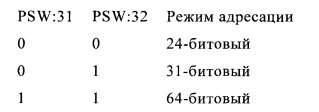

Расширенный режим адресации (ЕА) 526: Бит 31 управляет размером исполнительных адресов и образованием исполнительных адресов совместно с битом 32, основным битом режима адресации. Когда бит 31 представлен нолем, режимом адресации управляет бит 32. Когда оба бита 31 и 32 представлены единицами, задается 64-битовая адресация.

Основной режим адресации (ВА) 528: Биты 31 и 32 управляют размером исполнительных адресов и образованием исполнительных адресов. Когда оба бита 31 и 32 представлены нолями, задается 24-битовая адресация. Когда бит 31 представлен нолем, а бит 32 представлен единицей, задается 31-битовая адресация. Когда оба бита 31 и 32 представлены единицами, задается 64-битовая адресация. Бит 31 равный единице и бит 32 равный нолю представляют собой недопустимую комбинацию, вызывающую распознавание исключения по спецификации. Режим адресации не управляет размером адресов PER, или адресов, используемых для получения доступа к DAT, ASN, вызываемому управлению блоком, таблицам связей, входных записей и слежения или спискам доступа или стеку соединений. Управление режимом адресации посредством битов 31 и 32 PSW можно подытожить следующим образом:

Адрес 530 команды: Биты 33-63 PSW представляют собой адрес команды. Адрес обозначает местоположение крайнего левого байта следующей подлежащей выполнению команды, если ЦП не находится в состоянии ожидания (бит 14 PSW равен единице).

Согласно аспекту изобретения, когда средство конфигурации архитектурного режима, такое как средство конфигурации архитектурного режима (CZAM) для z/Архитектуры инсталлировано и активировано в вычислительном окружении, процесс включения изменяется. Один предпочтительный вариант осуществления настоящего изобретения процесса включения CZAM описан со ссылками на фиг. 6А.

Согласно фиг. 6А, на основании включения процессора вычислительного окружения, вычислительное окружение пребывает в конкретном архитектурном режиме, заданном средством конфигурации архитектурного режима, например режима z/Архитектуры (также называемом ESAME), когда инсталлировано CZAM, ЭТАП 600. Например, выполняется, как описано выше, начальная загрузка (IPL) программы, такая как начальная загрузка (IPL) программы управляющего слова (CCW) канала, ЭТАП 602, и когда операция ввода-вывода IPL завершается успешно, идентификационное слово подсистемы для устройства IPL сохраняется в выбранных местоположениях абсолютной памяти (например, местоположениях 184-187), ноли сохраняются в других выбранных местоположениях абсолютной памяти (например, местоположениях 188-191), и в этом варианте осуществления 16-байтовое новое слово (PSW) состояния программы создается из выбранных местоположений абсолютной памяти (например, местоположений 0-7), ЭТАП 604. Новое 16-байтовое PSW образуется, например, из содержимого выбранного двойного слова памяти (например, местоположений 0-7). Бит 12 двойного слова должен иметь значение единица, в противном случае, может быть обозначена ошибка. (Ошибка может быть представлена распознанным исключением по спецификации, по машинному контролю или индикацией какой-либо другой ошибки.) Биты 0-32 вновь созданного PSW задаются по битам 0-32 выбранного двойного слова, кроме бита 12, значение которого инвертируется. Битам 33-96 вновь созданного PSW задаются нулевые значения. Позиции битов 97-127 вновь созданного PSW инициализируются по битам 33-63 выбранного двойного слова.

В одном предпочтительном варианте осуществления настоящего изобретения поля PSW, которые должны быть загружены командой, не проверяются на допустимость перед их загрузкой. В одном предпочтительном варианте осуществления настоящего изобретения бит 12 PSW проверяется на допустимость. В еще предпочтительном варианте осуществления настоящего изобретения все поля проверяются на допустимость. В другом предпочтительном варианте осуществления любые биты, не проверенные до загрузки PSW, проверяются на допустимость после того, как PSW было инициализировано, и процессор может указать на ошибку (например, путем активации распознанного исключения по спецификации, машинному контролю или индикации какой-либо другой ошибки.)

Вычислительное окружение входит в рабочее состояние, и функционирование вычислительного окружения переходит под управление нового слова (PSW) состояния программы, ЭТАП 606. Загруженное вычислительное окружение затем функционирует, ЭТАП 608, как далее описано со ссылками на фиг. 6Б.

Согласно фиг. 6Б, загруженное вычислительное окружение инициируется в режиме z/Архитектуры, ЭТАП 620 и, таким образом, операции выполняются в режиме z/Архитектуры, ЭТАП 622. Не является необходимым какое-либо переключение режима, и обработка непосредственно продолжается обработкой в режиме z/Архитектуры. Тем самым, в одном предпочтительном варианте осуществления настоящего изобретения следующие этапы не являются необходимыми: Операция процессора (SIGP) обработки сигналов по переключению из режима ESA/390 к режиму z/Архитектуры, выявление того, является ли операция SIGP допустимой операцией, переход к z/Архитектуре, в случае допустимости операции, или индикация ошибки в случае недопустимости операции SIGP.

Все процессоры вычислительного окружения (то есть, конфигурируемого окружения, например одиночный процессор, логический раздел, гостевая VM), находятся в режиме z/Архитектуры без выполнения вышеупомянутых этапов. Таким образом, как описано в настоящем документе, согласно одному аспекту способность к загрузке или к включению в режиме ESA/390 удаляется из вычислительного окружения, сконфигурированного для обеих ESA/390 и z/Архитектуры. Конкретно, хотя вычислительное окружение сконфигурировано для поддержки множественных архитектур, предоставляется инструмент ограничения конкретных аспектов по меньшей мере одной из сконфигурированных архитектур, одним из аспектов которого является способность к включению в этой архитектуре.

В одном или нескольких предпочтительных вариантах осуществления включение в режиме z/Архитектуры предоставляет механизм для задания одного элемента из числа: (1) логического раздела (гость-1), и (2) логического раздела и гостя-2, в качестве загружаемого и сбрасываемого в режиме z/Архитектуры без потребности в загрузке в режиме ESA/390. Этот признак может быть инсталлирован безусловным образом или под управлением переключателя конфигураций.

Последовательность загрузки относительно инициализации PSW изменяется. Например, в конце IPL, загружается PSW IPL в абсолютные местоположения 0-7. Как делается в настоящее время, когда условием сброса является ESA/390, бит 12 представлен единицей, что обеспечивает допустимость ESA/390 IPL PSW, и программа продолжает выполнять команды в архитектурном режиме ESA/390. При инсталлированном CZAM условием сброса является z/Архитектура, бит 12 по прежнему равен единице, что делает допустимым ESA/390 IPL PSW, но бит 12 инвертируется в процессе формирования 16-байтового текущего PSW z/Архитектуры, как задано выше.

В дополнение к процессу включения, инсталляция средства конфигурации архитектурного режима также может изменить или затронуть и другие процессы, логики работы и/или операции. Эти затронутые процессы, логики работы и/или операции являются специфичными для режимов ESA/390 и z/Архитектуры. Однако подобные и/или различные процессы могут быть затронуты и при других типах архитектуры. Типовые процессы, логики работы и/или операции, которые могут быть затронуты в одном или нескольких вариантах осуществления, включают в себя, например:

(1) Предоставление возможности переключения из режима в тот же режим (например, из режима z/Архитектуры в режим z/Архитектуры) без генерации ошибки (или с игнорированием ошибки). Таким образом, процессор может дать команду SIGP для переключения в режим z/Архитектуры и, если он уже пребывает в этом режиме, то не генерируется какой-либо ошибки. Ранее, попытка переключения к режиму, соответствующему текущему режиму, генерировала ошибку.

(2) Отключение переключения к режиму ESA/390. На основе инсталлирования и активации CZAM переключение к ESA/390 отключается, и теперь генерирует ошибку. Переключение назад к ESA/390 предотвращается путем проверки бита 12 PSW и принятия исключения, если бит 12 не задан для указания на режим z/Архитектуры (что представлено битом 12 со значением «1» в памяти, инвертированном к значению «0» для представления z/Архитектуры в PSW, когда PSW для ESA/390 преобразуют к допустимому для z/Архитектуры PSW).

(3) Изменение функционирования команды загрузки PSW для ограничения обработки бита 12. Если инсталлировано средство конфигурации архитектурного режима для z/Архитектуры, команда загрузки PSW распознает исключение по спецификации, если бит 12 ее второго операнда не является единицей. Команда загрузки PSW загружает биты 0-32 своего второго операнда, за исключением бита 12, который имеет инвертированное значение, а биты 33-63 операнда в качестве, соответственно, битов 0-32 и 97-127 текущего PSW, что задает битам 33-96 текущего PSW нулевые значения.

Более подробная информация относительно команды загрузки PSW описана со ссылками на фиг. 7. В одном предпочтительном варианте осуществления настоящего изобретения команда 700 загрузки PSW включает в себя поле 702 кода операции, включающее в себя код операции для указания на операцию загрузки PSW, основное поле (В2) 704, и поле (D2) 706 смещения. Содержимое общего регистра, на которое указывает поле В2, добавляется к содержимому поля D2 для формирования адреса второго операнда в памяти (называемого вторым адресом операнда).

При выполнении команды загрузки PSW текущее PSW заменяется 16-байтовым PSW, образованным из содержимого двойного слова в местоположении, на которое указывает второй адрес операнда.

Бит 12 двойного слова должен иметь значение единица, в противном случае, в зависимости от модели, может быть распознано исключение по спецификации. Если инсталлировано средство конфигурации архитектурного режима для z/Архитектуры, то исключение по спецификации распознается в том случае, если бит 12 двойного слова не является единицей. Биты 0-32 двойного слова, за исключением бита 12, который имеет инвертированное значение, размещаются в положениях 0-32 текущего PSW. Биты 33-63 двойного слова размещаются в положениях 97-127 текущего PSW. Битам 33-96 текущего PSW задаются нулевые значения.

Функция преобразования в последовательную форму и синхронизации контрольной точки выполняется прежде или после выборки операнда, и вновь после завершения операции.

Операнд должен быть назначен на границе двойного слова, в противном случае, распознается исключение по спецификации. Если бит 12 операнда представлен нолем, в зависимости от модели, может быть распознано исключение по спецификации.

Поля PSW, которые должны быть загружены посредством команды, не проверяются на допустимость перед их загрузкой, за исключением проверки бита 12. Однако сразу после загрузки распознается исключение по спецификации и происходит прерывание программы, когда для недавно загруженного PSW является истинным любое из последующих условий:

- Любой из битов 0, 2-4, 12 или 24-30 представлен единицей.

- Биты 31 и 32 оба равны нолю, но не все биты 97-103 представлены нолями.

- Биты 31 и 32 представлены единицей и нолем, соответственно.

В этих случаях операция завершается, а получающийся код длины команды равен 0.

Операция подавляется на всех исключениях адресации и защиты.

Получающийся условный код: код задается, как указано в новом загруженном PSW.

Программные исключения:

- Доступ (выборка, операнд 2)

- Привилегированная операция

- Спецификация

Примечание по программированию: Второй операнд должен иметь формат ESA/390 PSW. Если бит 12 операнда представлен нолем, исключение по спецификации распознается в процессе или после выполнения команды LOAD PSW.

Более подробная информация относительно PSW приведена в статье «Разработка и реквизиты z/Архитектуры» (Development and Attributes of z/Architecture), Пламбек и др. (Plambeck et al), IBM J. Res. & Dev., Vol. 46, №4/5, июль/сентябрь 2002.

В дополнение к вышеупомянутым процессам, операциям и/или логикам работы, которые могут быть изменены вследствие инсталляции средства конфигурации архитектурного режима, в одном или нескольких вариантах осуществления также может быть изменен режим сброса, как объяснено ниже. (4) Изменение режима сброса (например, для сброса, чистого сброса и других действий для сброса). Когда инсталлировано средство CZAM, сброс ЦП задает архитектурному режиму режим z/Архитектуры, если это вызывается посредством активации, например посредством кнопки нормальной загрузки.

Имеется несколько функций сброса, которые включены в качестве составной части в режимы ESA/390 и z/Архитектуры, включая сюда, например, сброс ЦП, начальный сброс ЦП, сброс подсистемы, чистый сброс и сброс включения, каждая из которых описана ниже.

Сброс ЦП

Сброс ЦП предоставляет средства для очистки указателей проверки оборудования, а также какой-либо проистекающей непредсказуемости в состоянии ЦП с наименьшим возможным объемом уничтожаемой информации. Конкретно, такой сброс используют для очистки условий проверки, когда состояние ЦП должно быть сохранено для анализа или возобновления операции. Если средство конфигурации архитектурного режима (CZAM) для z/Архитектуры не инсталлировано, сброс ЦП задает архитектурному режиму режим ESA/390, если это вызывается активацией кнопки нормальной загрузки (средство оператора). Когда средство CZAM инсталлировано, сброс ЦП задает архитектурному режиму режим z/Архитектуры, если это вызывается активацией кнопки нормальной загрузки. Когда сброс ЦП задает режим ESA/390, он сохраняет текущее PSW таким образом, что PSW может быть восстановлено посредством распоряжения на задание архитектуры от процессора обработки сигналов, которое изменяет архитектурный режим обратно к z/Архитектуре.

В одном предпочтительном варианте осуществления настоящего изобретения сброс ЦП вызывает следующие действия:

1. Выполнение текущей команды или другой последовательности обработки, такой как прерывание, завершается, и все условия прерывания программы и прерывания обслуживания вызова супервизора очищаются.

2. Очищаются какие бы то ни было незаконченные условия внешнего прерывания, которые являются локальными для данного ЦП. Перемещаемые условия внешнего прерывания не очищаются.

3. Очищаются какие бы то ни было незаконченные условия прерывания машинного контроля и индикации ошибки, которые являются локальными для данного ЦП, а также любые состояния контрольного останова. Перемещаемые условия прерывания машинного контроля не очищаются. Любое условие машинного контроля, о котором сообщается всем ЦП в конфигурации, и которое было сделано отложенным для ЦП, считается для данного ЦП локальным.

4. Очищаются все копии выбранных с упреждением команд или операндов. Кроме того, очищаются любые результаты, которые подлежат сохранению вследствие выполнения команд в текущем интервале контрольной точки.

5. Ассоциативный буфер ART (трансляции регистра доступа) и ассоциативный буфер трансляции очищаются от записей.

6. Если сброс вызывается активацией кнопки нормальной загрузки на любом ЦП в конфигурации, происходят следующие действия:

А. Когда средство CZAM не инсталлировано, архитектурный режим ЦП (и всех других ЦП в конфигурации вследствие выполненных ими начального сброса ЦП или сбросов ЦП) изменяется от режима z/Архитектуры к режиму ESA/390. Если средство CZAM инсталлировано, архитектурному режиму ЦП (и всех других ЦП в конфигурации вследствие выполненных ими начального сброса ЦП или сбросов ЦП) задается режим z/Архитектуры.

Б. Когда средство CZAM не инсталлировано, текущее PSW сохраняется для последующего использования посредством распоряжения на задание архитектуры от процессора обработки сигналов, восстанавливающего режим z/Архитектуры.

В. Когда средство CZAM не инсталлировано, текущее PSW изменяется с 16 байтов до восьми байтов. Биты восьмибайтового PSW задаются следующим образом: биты 0-11 и 13-32 задаются равными тем же самым битам 16-байтового PSW, бит 12 задается равным единице, а биты 33-63 задаются равными битам 97-127 16-байтового PSW.

Сброс ЦП, вызванный активацией системы кнопкой нормального сброса или распоряжением на сброс ЦП от процессора обработки сигналов, а также любой сброс ЦП в режиме ESA/390, не затрагивают захваченный словом PSW z/Архитектуры регистр (то есть, слово PSW, сохраненное при последнем переходе ЦП из режима z/Архитектуры к режиму ESA/390 вследствие распоряжения на задание архитектуры с кодом 0, или сброса ЦП вследствие активации кнопкой нормальной загрузки).

7. ЦП пребывает в остановленном состоянии по завершении действий 1-6. Когда за функцией сброса на таком ЦП следует последовательность IPL типа CCW, по завершении функции сброса ЦП входит в состояние загрузки, и не обязательно входит в остановленное состояние в процессе выполнения операции по сбросу. Когда за функцией сброса на таком ЦП следует управляемая списком последовательность IPL, ЦП входит в рабочее состояние и не обязательно входит в остановленное состояние в процессе выполнения операции по сбросу.

Регистры, содержание памяти и состояние внешних по отношению к ЦП условий остаются в результате сброса ЦП неизменными. Однако последующее содержимое регистра, местоположения или состояния являются непредсказуемыми, если происходит операция, изменяющая содержимое во время сброса. Удерживаемая посредством ЦП при выполнении команды PERFORM LOCKED OPERATION (выполнения заблокированной операции) блокировка не разблокируется при сбросе ЦП.

Когда функция сброса в ЦП инициируется во время выполнения ЦП команды I/O или выполнения прерывания I/O, текущая операция между ЦП и канальной подсистемой может быть или может не быть завершена, и результирующее состояние ассоциированной функции канальной подсистемы может быть непредсказуемым.

Примечания по программированию:

1. Большинство операций, которые могут изменить состояние, условие или содержимое поля, не могут произойти, когда ЦП находится в остановленном состоянии. Однако некоторые функции процессора обработки сигналов и некоторые функции оператора могут изменить эти поля. Для устранения возможности потери поля при выпуске сброса ЦП, ЦП должен быть остановлен, и никакие функции оператора не должны происходить.

2. Если архитектурный режим изменяется на режим ESA/390, и бит 31 текущего PSW равен единице, PSW является недопустимым.

Начальный сброс ЦП

Начальный сброс ЦП предоставляет функции сброса ЦП совместно с инициализацией программируемых регистров текущего PSW, захваченного PSW z/Архитектуры, таймера ЦП, компаратора часов, префикса, управления прерыванием адресов событий, управления с плавающей точкой и времени (TOD) суток. Если средство CZAM не инсталлировано, начальный сброс ЦП задает архитектурному режиму режим ESA/390, если это вызывается активацией кнопки нормальной загрузки. Когда средство CZAM инсталлировано, начальный сброс ЦП задает архитектурному режиму режим z/Архитектуры, если это вызывается активацией кнопки нормальной загрузки.

Начальный сброс ЦП сочетает функции сброса ЦП со следующими функциями очистки и инициализации:

1. Когда средство CZAM не инсталлировано, если сброс вызывается активацией кнопки нормальной загрузки, архитектурному режиму ЦП (и всех других ЦП в конфигурации) задается режим ESA/390. В противном случае, если средство CZAM инсталлировано, архитектурному режиму ЦП (и всех других ЦП в конфигурации) задается режим z/Архитектуры.

2. Содержимому программируемых регистров текущего PSW, захваченного PSW z/Архитектуры, префикса, таймера ЦП, компаратора часов и TOD задаются нулевые значения. Когда последовательность IPL следует за функцией сброса на данном ЦП, содержимое PSW не обязательно задается нулевым.

Содержимому регистров управления задаются их начальные для z/Архитектуры значения. Значения всех 64 битов регистров управления задаются независимо от пребывания ЦП в архитектурном режиме ESA/390 или z/Архитектуры.

4. Содержимому регистра управления с плавающей точкой задается нулевое значение.

5. Содержимое регистра адреса события прерывания инициализируется к шестнадцатеричному числу.

Эти функции очистки и инициализация включают в себя проверку правильности.

Задание текущему PSW нулевого значения при нахождении ЦП в архитектурном режиме ESA/390 в конце операции приводит к недопустимому PSW, поскольку бит PSW 12 в этом режиме должен быть равен единице. Таким образом, в этом случае, если ЦП пребывает в рабочем состоянии после сброса без предварительного введения нового PSW, распознается исключение по спецификации.

Сброс подсистемы

Сброс подсистемы предоставляет средства для очистки перемещаемых условий прерывания, а также для вызова сброса системы I/O.

Чистый сброс

Чистый сброс вызывает выполнение начального сброса ЦП и сброса подсистемы, а также, дополнительно, очищает или инициализирует все местоположения памяти и регистры во всех ЦП в конфигурации, за исключением часов TOD. Такая очистка является полезной при отладке программ и при обеспечении пользовательской конфиденциальности. Чистый сброс также разблокирует все блокировки, используемые командой PERFORM LOCKED OPERATION (выполнения заблокированной операции). Если средство CZAM не инсталлировано, чистый сброс задает архитектурному режиму режим ESA/390. Когда средство CZAM инсталлировано, чистый сброс задает архитектурному режиму режим z/Архитектуры. Очистка не затрагивает внешнюю память, такую как запоминающие устройства с прямым доступом, используемые управляющей программой для сохранения содержимого неадресуемых страниц.

Чистый сброс сочетает функцию начального сброса ЦП с функцией инициализации, вызывающей следующие действия:

1. Когда средство CZAM не инсталлировано, архитектурному режиму всех ЦП в конфигурации задается режим ESA/390. Если средство CZAM инсталлировано, архитектурному режиму всех ЦП в конфигурации задается режим z/Архитектуры.

2. Регистрам доступа, общему и с плавающей точкой всех ЦП в конфигурации задаются нулевые значения. Всем 64 битам общих регистров задаются нулевые значения независимо от пребывания ЦП в архитектурном режиме ESA/390 или z/Архитектуры на момент инициирования функции чистого сброса.

3. Содержимому основной памяти в конфигурации и ассоциированных ключей защиты памяти задаются нулевые значения с допустимым кодом проверки блокировок.

4. Используемые каким-либо ЦП в конфигурации блокировки разблокируются при выполнении команды PERFORM LOCKED OPERATION.

5. Выполняется сброс подсистемы.

Проверка правильности входит в состав процессов задания значений регистрам, а также очистки памяти и ключей защиты памяти. Примечания по программированию:

1. Архитектурный режим не изменяется посредством активации кнопки нормального сброса системы или выполнения распоряжения процессора обработки сигналов на сброс ЦП или основной сброс ЦП. Все ЦП в конфигурации находятся в том же самом архитектурном режиме.

2. Для предотвращения воздействия операции сброса ЦП на содержимое полей, которые должны оставаться неизменными, ЦП во время сброса не должен выполнять команды и должен быть деактивирован для всех прерываний. За исключением функционирования таймера ЦП и для возможности появления прерывания машинного контроля, вся активность ЦП может быть остановлена путем перевода ЦП в состоянии ожидания и путем отключения его для I/O и внешних прерываний. Во избежание возможности вызывания сброса в то время, когда обновляется таймер ЦП или происходит прерывание машинного контроля, ЦП должен пребывать в остановленном состоянии.

3. Сброс ЦП, начальный сброс ЦП, сброс подсистемы и чистый сброс не затрагивают значение и состояние часов TOD.