Результат интеллектуальной деятельности: СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР

Вид РИД

Изобретение

Изобретение относится к радиотехнике.

Известен способ подстройки частоты [1], в котором на первом выходе фазового детектора формируют импульс по фронту опорного сигнала, на втором выходе фазового детектора формируют импульс по фронту тактов, а после появления обоих импульсов формируют срезы импульсов на обоих выходах фазового детектора, импульсы на первом и втором выходах фазового детектора преобразуют соответственно в сигналы положительной и отрицательной полярности, которые затем суммируют, фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты. Способ имеет зоны поиска и удержания от 0° до 360°.

Способ [1] имеет следующие недостатки:

• в режиме удержания работает только с сигналами равных частот (не может подстраивать такты по принятым данным);

• для его реализации требуется токовый преобразователь, которого нет в цифровых ПЛИС;

Известен способ подстройки частоты [2], в котором опорный и тактовый сигналы перемножают, полученный сигнал фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты. Для логических сигналов функцию умножителя выполняет логический элемент «исключающее ИЛИ» (см., например, описание фазового детектора 1 микросхемы CD 4046 ф. RCA или ее аналогов: HEF 4046B, CDD 4046B или К564ГП [3]).

Способ [2] отличается простым фазовым детектором, но имеет следующие недостатки:

• скважность импульсных сигналов должна быть близка к 2;

• работает только при равных и кратных частотах;

• не может подстраивать тактовую частоту по фронтам данных при приеме дискретных сигналов;

• подстройка происходит по фронтам и срезам импульсов, что снижает точность и увеличивает фазовый шум, т.к. реально скважность всегда отличается от 2;

• область поиска (удержания) составляет от 0° до 180° (в зоне от 180° до 360° инвертируются скважность выходного сигнала умножителя и знак подстройки, что увеличивает время поиска, а в режиме удержания уход разности фаз от номинальных 90° за границы области 0÷180° приведет к потере захвата и новому поиску).

Известен фазовый детектор [1], содержащий содержит два D-триггера, два логических элемента И, два буфера. Сравнение любой пары фронтов опорного и тактового сигналов в фазовом детекторе [1] приводит к «арбитражу» в момент сброса D-триггеров. При «арбитраже» возможны нестабильный переходный процесс, увеличение времени переключения при формировании фронта, колебательная аномалия или метастабильная аномалия [4], что приводит к увеличению фазового шума и снижению быстродействия.

Известен логический элемент «исключающее ИЛИ» [3], который выполняет функцию фазового детектора импульсных сигналов - умножителя в способе [2]. Его преимущества и недостатки определяются способом подстройки частоты [2] и были описаны выше.

Наиболее близким (прототипом) является фазовый детектор [5], который содержит три D-триггера и четыре логических элемента И. Это устройство может работать при кратных частотах, что позволяет использовать его для подстройки тактовой частоты по фронтам данных при приеме дискретных сигналов. Фазовый детектор имеет следующие недостатки:

• предназначен для совместной работы с двухполярным токовым формирователем, который отсутствует в цифровых ПЛИС;

• при появлении фронта опорного сигнала в окрестности фронта тактов появляется «арбитраж» [4]. Ширина опасного временного интервала меньше времени переключения D-триггера, но он расположен в центре рабочей зоны удержания. Возможные колебательная или метастабильная аномалии [4] увеличивают фазовый шум и снижают быстродействие.

Наиболее близкими к предлагаемым являются способ [2] и фазовый детектор [5] (прототипы).

Цель изобретения (технический результат) - повышение функциональных надежности (устранение «арбитража» в зоне удержания) и расширение функциональных возможностей способа подстройки частоты, в части:

• расширения области поиска и удержания;

• обеспечения работы с произвольной кратностью периода опорного сигнала к тактам, возможности изменения этой кратности, переменной скважности опорного сигнала во время работы (возможность подстройки частоты тактов по фронтам данных при приеме дискретных сигналов);

• повышения точности и снижение фазового шума за счет перехода от подстройки по фронтам и срезам к подстройке по фронтам.

Технический результат достигается тем, что:

1) в способе подстройки частоты, в котором на выходе фазового детектора формируют импульсы, которые фильтруют, и полученным сигналом управляют частотой генератора, частоту генератора делят и формируют тактовые сигналы для фазового детектора, при этом после появления в первой половине периода тактов фронта опорного сигнала формируют фронт импульса на выходе фазового детектора, а при отсутствии фронта опорного сигнала в первой половине периода тактов фронт импульса на выходе фазового детектора формируют в начале второй половины периода тактов, при появлении фронта опорного сигнала в первых трех четвертях периода тактов срез импульса на выходе фазового детектора формируют в начале четвертой четверти периода тактов, а при появлении фронта опорного сигнала в четвертой четверти периода тактов срез импульса на выходе фазового детектора формируют в следующем периоде тактов.

2) при появлении фронта опорного сигнала в четвертой четверти периода тактов срез импульса на выходе фазового детектора формируют в начале второй четверти периода следующего периода тактов

3) частоту генератора делят в два этапа, при этом на втором этапе 4-кратную тактовую частоту делят в 4 раза до тактовой частоты, а в фазовом детекторе используют импульсы 4 кратной тактовой частоты и несколько сигналов с выходов второго делителя.

4) в фазовый детектор, дополнительно введены два элемента ИЛИ и логический преобразователь, вход опорной частоты соединен с D-входом первого D-триггера, выход которого соединен с D-входом второго D-триггера, выход первого элемента И соединен с первым входом первого элемента ИЛИ и с D-входом третьего D-триггера, первый выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с СЕ-входом третьего D-триггера, выход второго элемента И соединен с другим входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с выходом фазового детектора, три выхода логического преобразователя соединены попарно соответственно с СЕ-входом первого D-триггера и другими входами второго элементов И и ИЛИ, входы логического преобразователя соединены попарно соответственно с дополнительными тактовыми входами фазового детектора.

Группа изобретений связана общим замыслом и удовлетворяет требованию единства изобретения, т.к. фазовый детектор является частью устройства для осуществления предложенного способа. При анализе уровня техники и новизны заявляемых объектов не обнаружены аналоги с перечисленной совокупностью вышеназванных признаков. Следовательно, описанное техническое решение соответствует критерию "новизна".

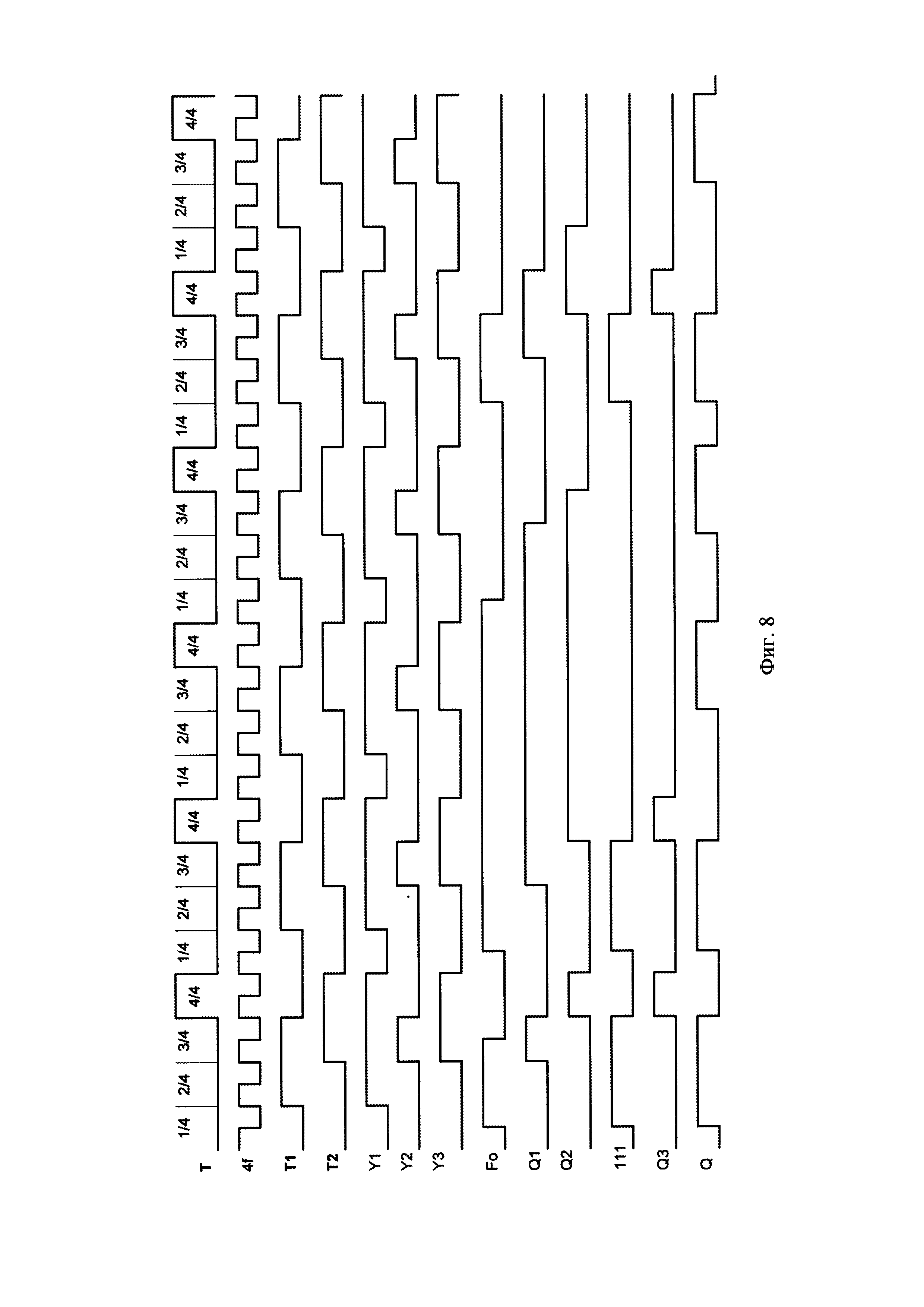

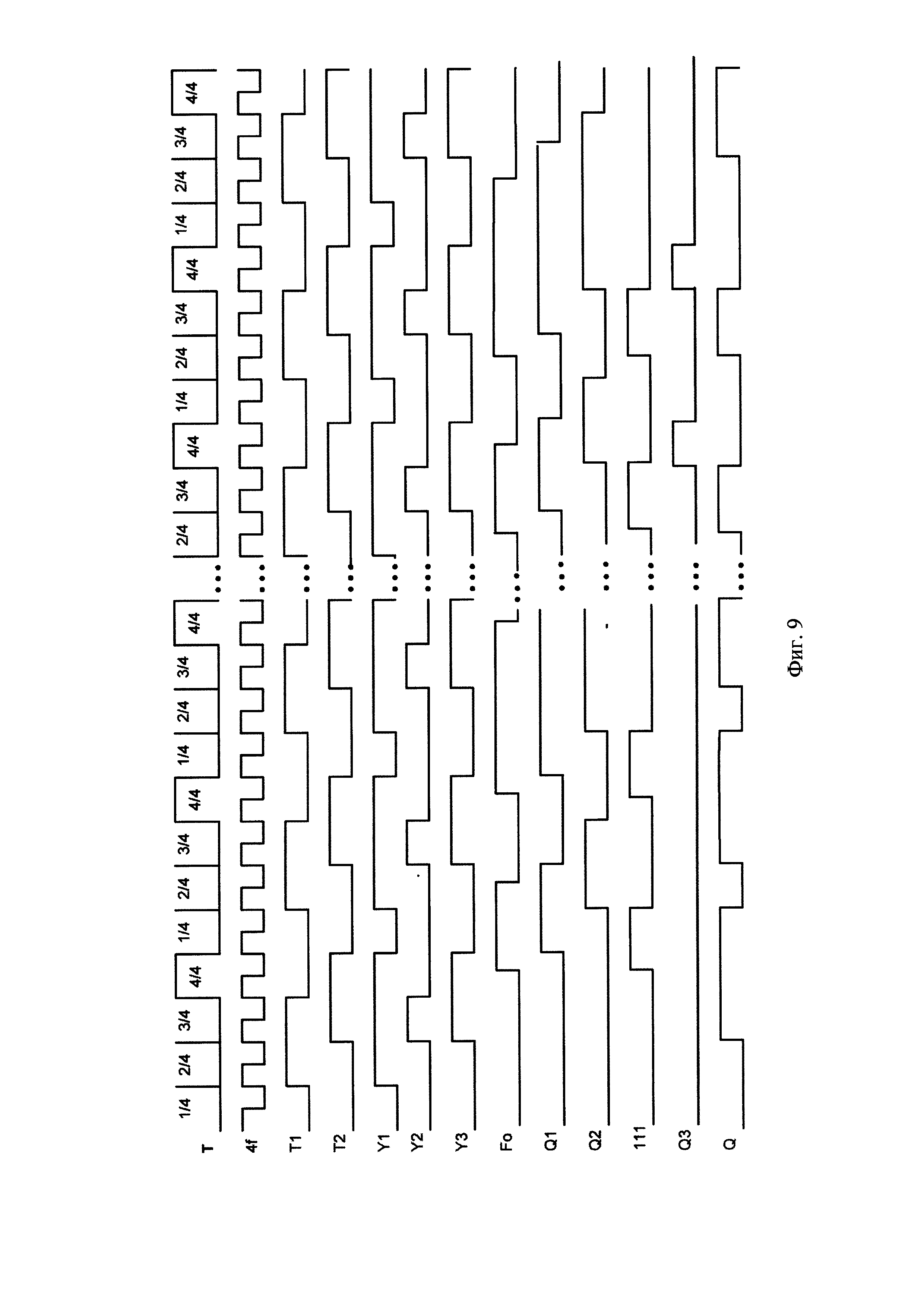

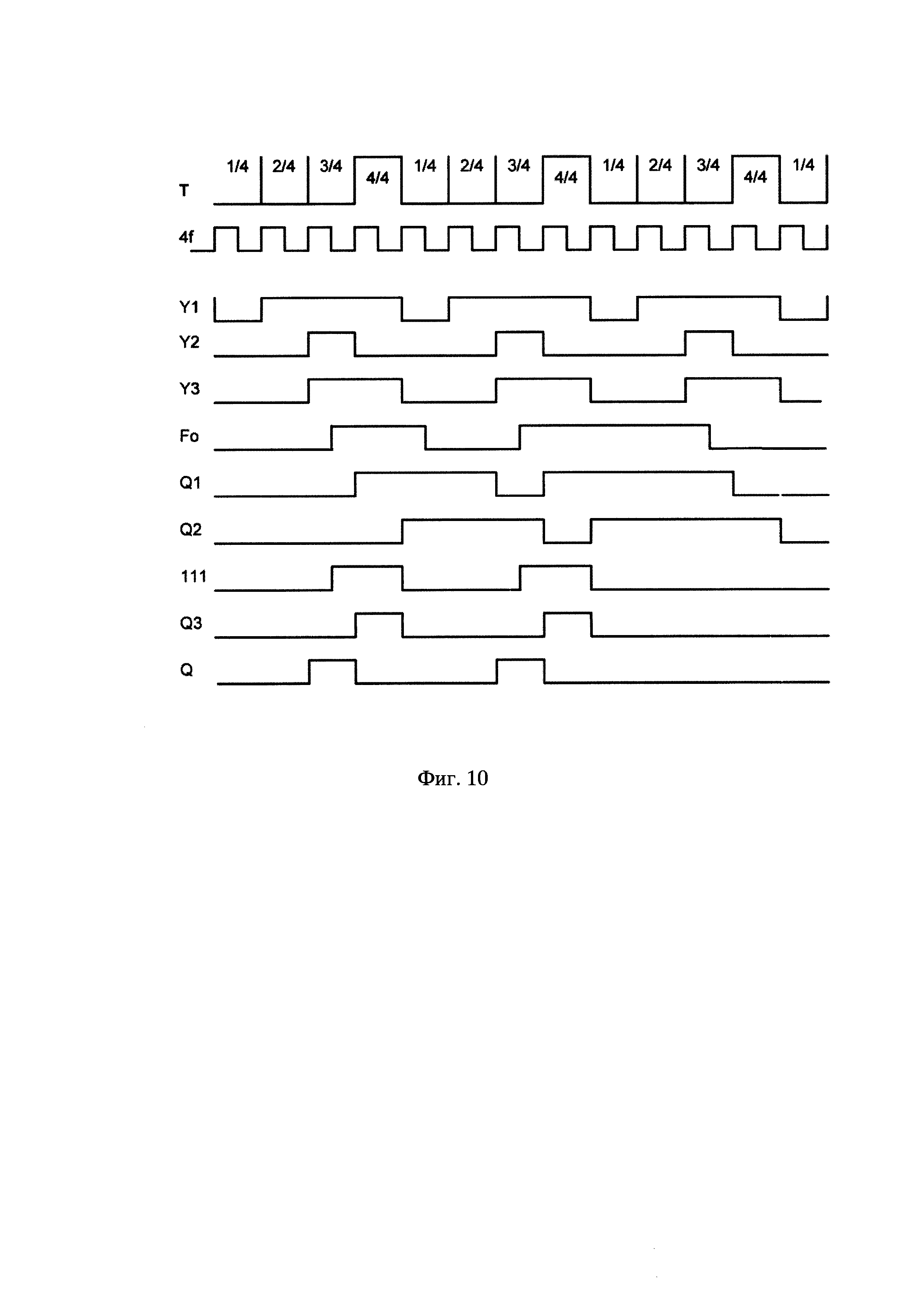

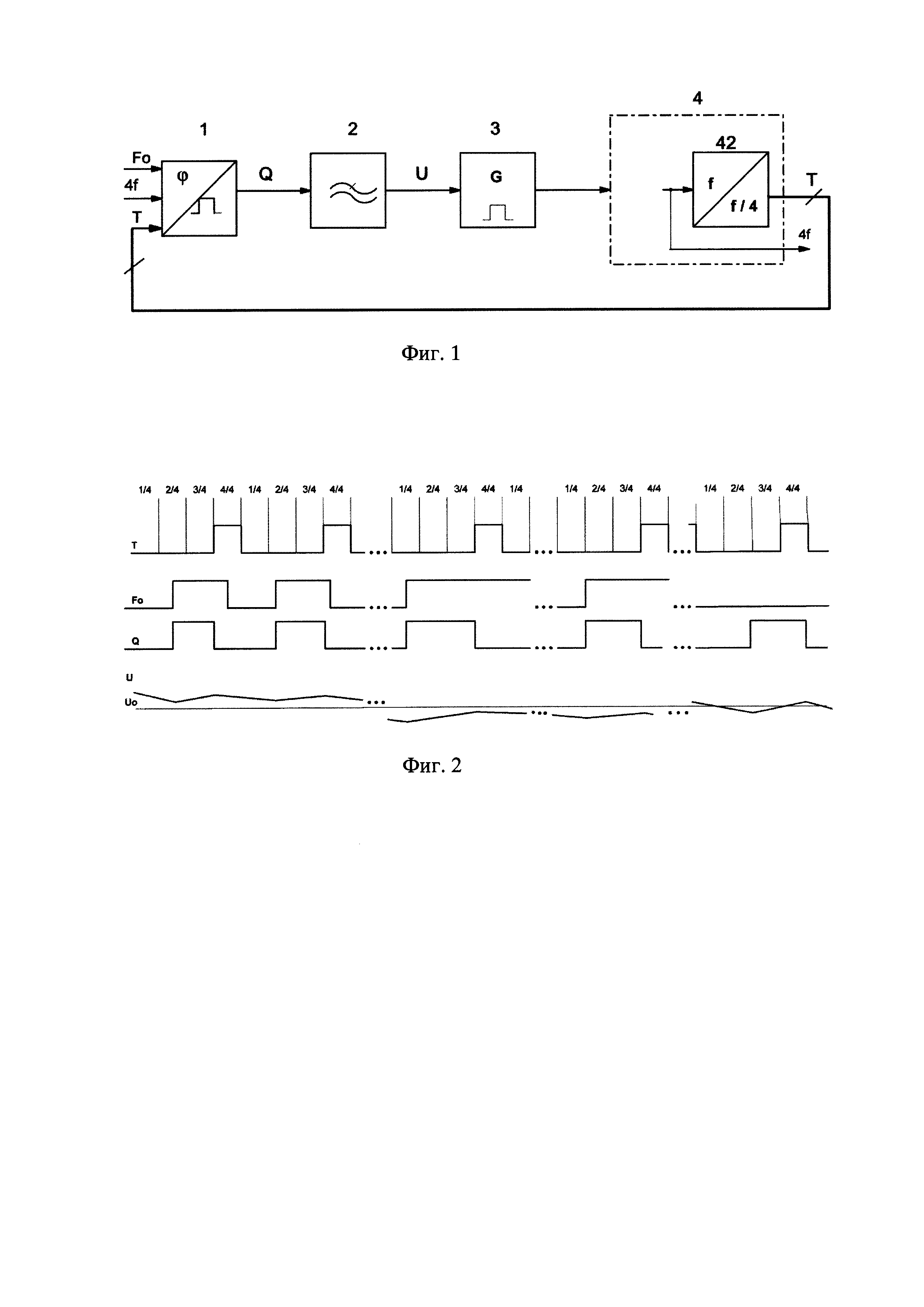

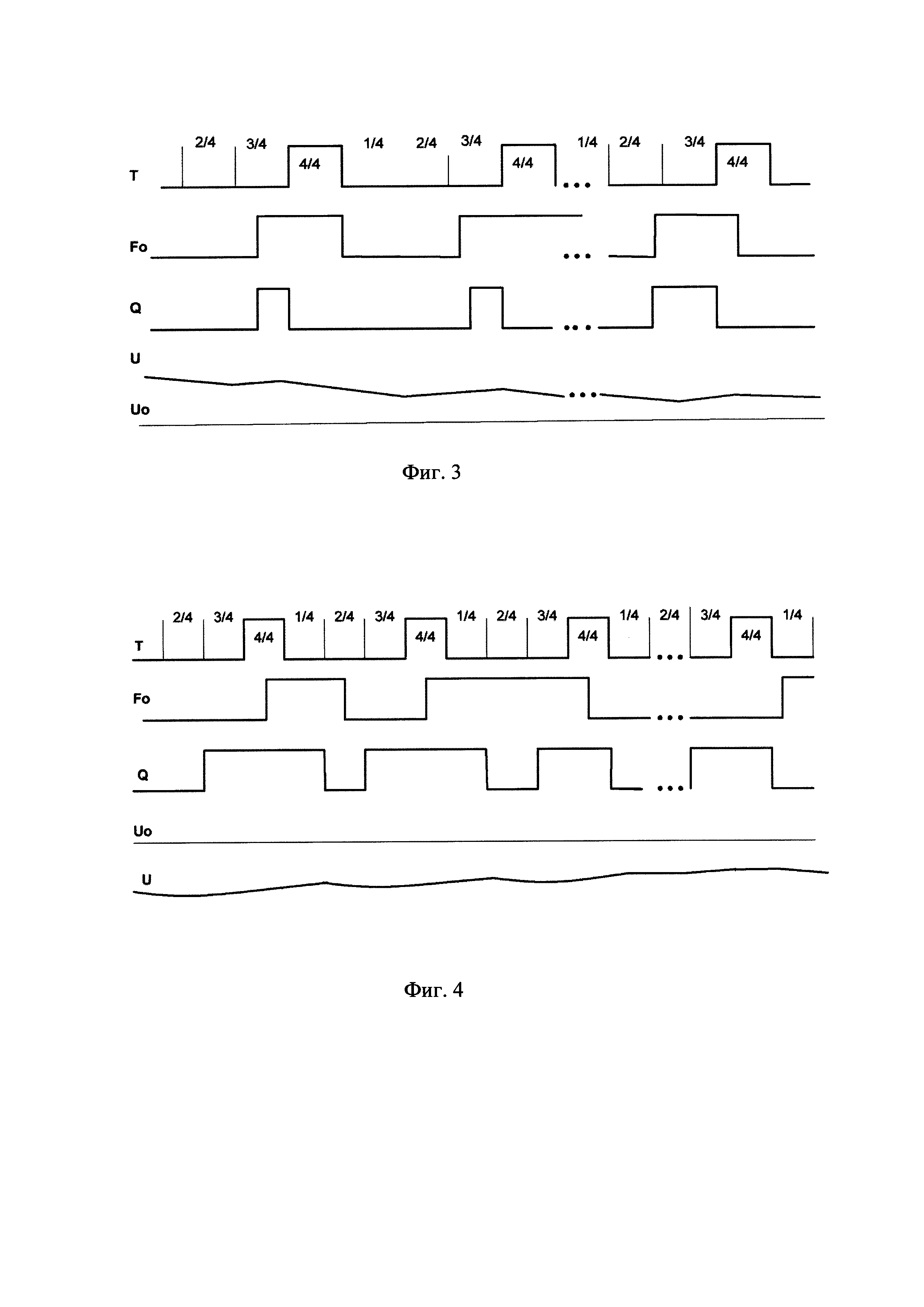

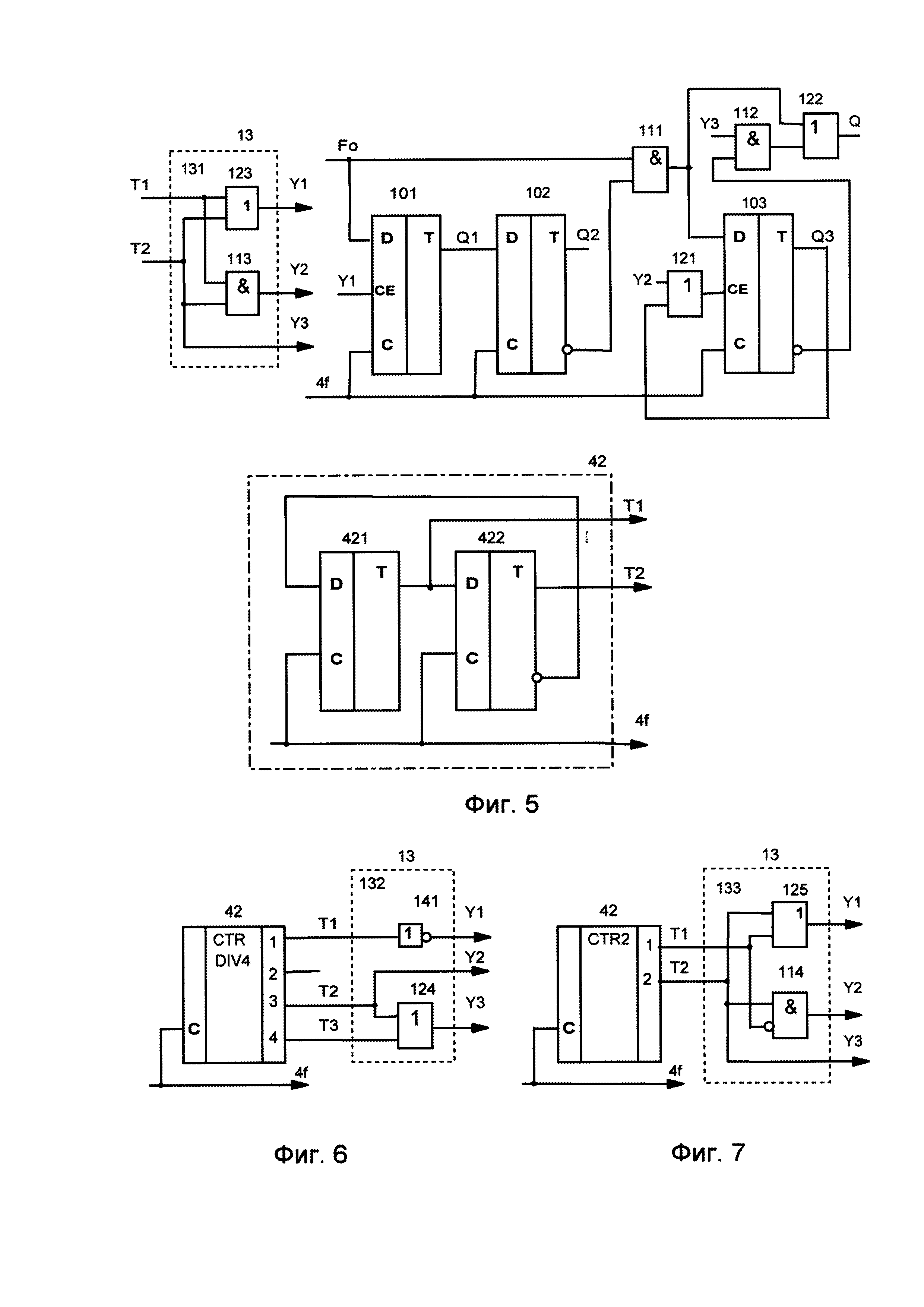

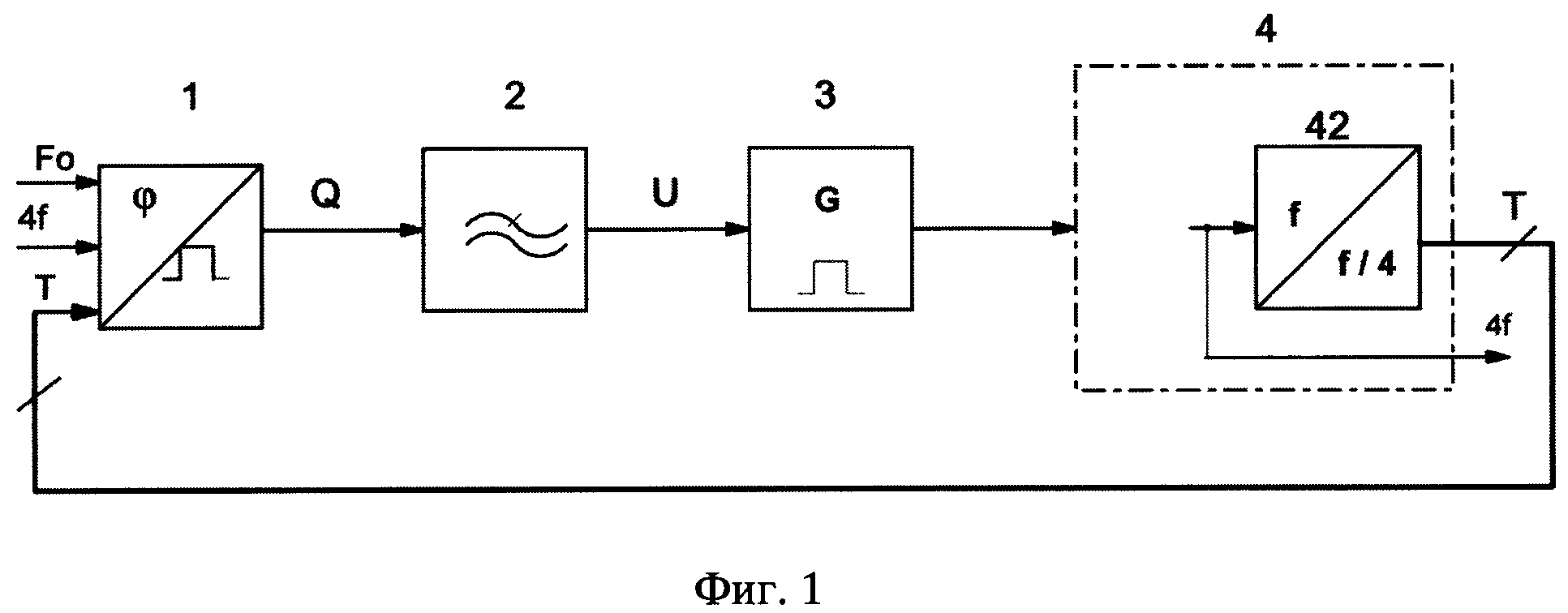

Предлагаемый способ представлен на фиг.1÷4. Временные диаграммы фиг. 2, 3 и 4 построены для фронтов опорного сигнала, появляющихся в первой половине, в третьей и четвертой четвертях периода тактов соответственно. На фиг. 5 приведена схема фазового детектора с логическим преобразователем рефлексного кода (кода Либау-Крейга) по пп. 4 и 5 формулы изобретения. На фиг. 6 и 7 приведены логические преобразователи унитарного и двоичного кода соответственно. На фиг. 8, 9 и 10 - временные диаграммы работы фазового детектора (фиг. 5) при разных фазах фронтов опорного частоты.

На фиг. 1 представлен способ подстройки частоты, в котором на выходе фазового детектора 1 формируют импульсы Q, которые фильтруют 2, и полученным сигналом U управляют частотой генератора 3. Частоту генератора 3 делят 4 и формируют тактовые сигналы Т для фазового детектора 1.

На втором этапе деления частоты 42 4-кратную тактовую частоту 4f делят в 4 раза до тактовой частоты. В фазовом детекторе используют 4-кратную тактовую частоту 4f и несколько тактовых сигналов с выходов делителя 42. При фильтрации 2 однополярных импульсов с выхода фазового детектора должны осуществляться сдвиг уровня постоянной составляющей вниз по входу на полусумму логических уровней сигнала Q (для КМОП схем - на половину напряжения питания), выделение постоянной составляющей «сдвинутого» сигнала Q и сдвиг сигнала U в центр рабочей области регулирования частотой генератора 3. В рабочей области генератора 3 фильтрация должна быть линейной: равенство скоростей роста и спада напряжения U и их независимость от значений U. Возможно применение цифровой фильтрации.

На временных диаграммах абстрактный сигнал тактовый сигнал Т, представляющий несколько сигналов с выходов делителя 42, условно изображен как импульс в четвертой четверти периода тактов, полярности сигналов Q и U соответствуют повышению частоты генератора 3 при увеличении напряжения U и используются следующие обозначения:

1/4, 2/4, 3,/4 и 4/4 - части периода тактов;

Uo - значение напряжения U в конце подстройки. На фиг. 2 показано, что:

• после появления в первой половине периода тактов фронта опорного сигнала Fo формируют фронт импульса на выходе Q фазового детектора (первые четыре фронта Q);

• при отсутствии фронта опорного сигнала в первой половине периода тактов фронт импульса на выходе фазового детектора Q формируют в начале второй половины периода тактов, а срез импульса - в конце периода (пятый фронт Q);

• при появлении фронта опорного сигнала Fo в первых двух четвертях периода тактов срез импульса на выходе фазового детектора Q формируют в начале четвертой четверти периода тактов (первые четыре фронта Q).

Фиг. 3 иллюстрирует функционирование при появлении фронта опорного сигнала F0 в третьей четверти периода тактов, (фронты сигнала F0 1÷3) В первой половине этих периодов отсутствуют фронты F0 и в начале второй половины формируют фронты импульсов на выходе фазового детектора Q, а срезы импульсов формируют в начале четвертой четверти периодов тактов. В тактовом периоде, когда фронт сигнала F0 появляется в третьей четверти периода, скважность импульса Q равна 4. Средняя скважность Q будет больше 2, напряжение U и частота генератора 3 снижаются, поэтому после нескольких периодов фронт сигнала F0 переходит во вторую четверть периода (последний фронт сигнала F0).

Фиг. 4 иллюстрирует функционирование для фронта опорного сигнала F0 в четвертой четверти периода тактов, В первой половине периода тактов отсутствует фронт F0, и в начале второй половины периода тактов формируют фронт импульса на выходе фазового детектора Q, а его срез сигнала формируют в начале второй четверти следующего периода тактов (по п. 2 формулы изобретения). В тактовом периоде, в котором появляется фронт сигнала F0, скважность импульса Q равна 4/3. Средняя скважность Q будет меньше 2, напряжение U и частота генератора 3 растут, поэтому после нескольких периодов тактов фронт сигнала F0 переходит в первую четверть следующего периода (на диаграмме последний фронт сигнала F0).

На фиг. 5 приведена схема фазового детектора, содержащего три D-триггера 101, 102 и 103 и два элемента И 111 и 112, тактовый вход 4f соединен с С-входами трех D-триггеров, вторые выходы второго и третьего D-триггеров 102 и 103 соединены попарно соответственно с первыми входами первого и второго элементов И 111 и 112, D-вход первого D-триггера 101 соединен с другим входом первого элемента И 111, фазовый детектор содержит два элемента ИЛИ 121, 122 и логический преобразователь 13, вход опорной частоты 4Fo соединен с D-входом первого D-триггера 101, выход которого соединен с D-входом второго D-триггера 102, выход первого элемента И 111 соединен с первым входом второго элемента ИЛИ 122 и с D-входом третьего D-триггера 103, первый выход которого соединен с первым входом второго элемента ИЛИ 122, выход которого соединен с СЕ-входом третьего D-триггера 103, выход второго элемента И 112 соединен с вторым входом второго элемента ИЛИ 122, выход второго элемента ИЛИ 122 соединен с выходом фазового детектора Q, три выхода логического преобразователя Y1, Y2 и Y3 соединены попарно соответственно с СЕ-входом первого D-триггера 101, вторым входом первого элемента ИЛИ 121 и вторым входом второго элемента И 112, входы логического преобразователя 13 соединены попарно соответственно с дополнительными тактовыми входами фазового детектора Т1 и Т2.

Логический преобразователь 13 выполнен как логический преобразователь рефлексного кода 131, который содержит логические элементы ИЛИ 123 и И 113, три выхода логического преобразователя 131 Y1, Y2 и Y3 соединены попарно соответственно с выходом элемента ИЛИ 123, выходом элемента И 113 и вторым входом преобразователя рефлексного кода Т2, первый и второй входы логического преобразователя рефлексного кода 131 соединены попарно соответственно с первыми и вторыми входами элементов ИЛИ 123 и И 113.

На фиг. 5 также приведена известная схема счетчика в рефлексном коде 42 на двух D-триггерах 421 и 422 (см. например, [6, 7]).

На фиг. 6 приведен логический преобразователь унитарного кода 132, который содержит логический элемент ИЛИ 124 и инвертор 141, три выхода логического преобразователя унитарного кода 132 Y1, Y2 и Y3 соединены попарно соответственно с выходом инвертора 141, вторым входом преобразователя унитарного кода 132 и выходом элемента ИЛИ 124, входы которого соединены попарно соответственно со вторым и третьим входами логического преобразователя унитарного кода 132, первый вход которого соединен с входом инвертора 141. На фиг. 6 также приведены соединения входов фазового детектора Т1,Т2, ТЗ с логическим преобразователя 13 и выходами 4-разрядного счетчика с унитарным кодированием 42 со входами фазового детектора T1, Т2, ТЗ. Отметим, что здесь второй выход счетчика 42 не используется. Используется последовательность состояний {1000, 0100, 0010, 0001} (см., например, [6,7]).

На фиг. 7 приведен логический преобразователь двоичного взвешенного кода 133, который содержит логические элементы ИЛИ 125 и И 114, причем первый вход элемента И 114 инверсный, три выхода логического преобразователя двоичного кода 133 Y1, Y2 и Y3 соединены попарно соответственно с выходом элемента ИЛИ 125, выходом элемента И 114 и вторым входом преобразователя двоичного кода 133 и выходом элемента И 114, первый и второй входы логического преобразователя двоичного кода 133 соединены попарно соответственно с первыми и вторыми входами элементов ИЛИ 125 и И 114. На фиг. 7 также приведены соединения входов фазового детектора T1, Т2, ТЗ с логическим преобразователя 132 и выходами 2-х разрядного двоичного счетчика 42. Последовательность состояний: 00, 01, 01 и 11 (см., например, [6]).

На фиг. 8 приведена временная диаграмма работы фазового детектора (фиг. 5) при появлении фронта Fo в первой четверти периода тактов (1-й и 2-й периоды) и в центре зоны удержания на границе первой и второй четвертей (5-й период). Первый D-триггер 101 не переключается в начале второй четверти периода тактов. Второй D-триггер 102 может переключаться в любой четверти периода. Третий D-триггер 103 может переключиться в лог.1 только в начале четвертой четверти периода тактов, а - в 0 в любой четверти периода. При появлении фронта Fo в первой четверти периода тактов на выходе фазового детектора Q формируется импульс с линейной широтно-импульсной модуляцией (ШИМ) длительности в границах от 1/2 до 4/3 периода тактов, при этом скважность импульса Q (отношение периода тактов к длительности импульса) лежит в интервале от 4/3 до 2 (на фиг. 8 - 8/5). Это соответствует увеличению напряжения U и частоты генератора 3. В остальных периодах скважность - 2.

Функциональная надежность (отсутствие арбитража) в режиме удержания обеспечивается тем, что первый D-триггер 101 не переключается в центре зоны удержания (в конце первой четверти периода тактов).

На фиг. 9 приведена временная диаграммы работы фазового детектора при появлении фронтов опорной частоты Fo: в четвертой четверти периода (1-й и 2-й периоды), во второй четверти периода (3-й и 4-й период) и на границе первой и второй четвертей периода (5-й период). В следующих периодах после появления фронтов опорного частоты Fo в четвертой четверти периода периодах тактов скважность сигнала Q составляет 4/3 (во 2-м и 3-м на фиг. 9). Это соответствует корректному увеличению частоты генератора 3 в зоне 270°÷360°.

Для фронта Fo, поступившего во второй четверти периода, фазовый детектор работает линейно с ШИМ и скважность Q ограничена интервалом от 2 до 4 (на фиг. 9 -8/3). Это соответствует уменьшению напряжения U и частоты генератора 3.

В остальных периодах скважность сигнала Q составляет 2.

Появление фронта опорной частоты Fo на границе первой и второй четвертей периода (5-й период фиг. 9) соответствует отсутствию фазовой ошибки.

На фиг. 10 приведена временная диаграммы работы фазового детектора при появлении фронтов опорного частоты Fo в третьей четверти периода (1-й и 2-й периоды). В первых двух периодах тактов фронт сигнала Y3 в начале третьей четверти опережает фронт Fo и на выходе третьего D-триггера Q3 формируется импульс в четвертой четверти периода. На выходе Q формируется импульс в третьей четверти периода. В первых двух периодах тактов скважность сигнала Q равняется 4, что соответствует уменьшению напряжения U и частоты генератора 3. В остальных периодах скважность сигнала Q составляет 2.

Фазовые детекторы с другими вариантами построения логического преобразователя (фиг. 6 и 7) работают аналогично

Таким образом, способ по предложению может работать с опорным сигналом различной скважности, при любой кратности периода опорного сигнала к тактам и при изменениях кратности и скважности в процессе работы, подстраивать частоту тактов по фронтам данных, а фазовый детектор не подвержен «арбитражу» в зоне удержание.

Источники информации

1. Патент US 5892380, кл. 337/172, 06.04.1999.

2. Гребен А.В. Проектирование аналоговых интегральных схем, Пер. с англ. – М.: Энергия 1976, 266 с, стр. . 196 рис. 9-17.

3. Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Металлургия 1988, 352 с, стр. 279 рис. 2.73 а, стр. , 282 рис. 2.75 а, б.

4. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И. Варшавского. - М.: Наука, Гл. ред. физмат, лит., 1986. 400 с, стр. 284-294 § 9.1-9.3, стр. 310 § 9.6.

5. Патент РФ 2622628, МПК H03D 13/00, 08.08.2016 (фиг. 3 и 4).

6. Трачик В. Дискретные устройства автоматики: Пер. с польск.; Под ред. Д.А. Поспелова. - М.: Энергия, 1978 - 456 с, стр. 325 рис. 5 - 37 а и 6, стр. 328 рис. 5 - 39 а и 6, стр. 329 рис. 5-41 а и 6.

7. Проектирование микроэлектронных цифровых устройств / Под ред. С.А. Майорова - М.: Сов. радио, 1977, 272 с, стр. 175 рис. 5 -18 а и 6, стр. 182 рис. 5 -22.