Результат интеллектуальной деятельности: ВЫСОКОЧАСТОТНЫЙ ВЕКТОРНЫЙ ФАЗОВРАЩАТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к областям радиотехники и связи и может быть использовано при разработке высокочастотных монолитных интегральных схем фазовращателей.

Известен фазовращатель [патент FR №2984638, МПК Н03Н 11/20, H04L 27/10, опубликованный 21.06.2013], состоящий из двух усилителей с переменным коэффициентом усиления в виде ячеек Гильберта, нагрузки и преобразователей частоты. Фазовый сдвиг осуществляется за счет перемножения высокочастотного сигнала с квадратурными опорными сигналами и переносом на промежуточную частоту. Недостатком данной схемы является увеличенная ошибка установки фазы, зависящая от амплитудно-фазового дисбаланса опорного колебания.

Известен фазовращатель [патент US №8687968, МПК Н04В 10/00, Н04В 10/50, опубликованный 01.04.2014], состоящий из фазосдвигающей цепи с двумя входами, двух усилителей с переменным коэффициентом усиления, сумматора и схемы управления. В качестве фазосдвигающей цепи предложено использование схемы из нескольких дифференциальных усилителей или полифазного RC-фильтра с дифференциальным входом. При этом для работы фазовращателя необходим входной дифференциальный сигнал, что требует введения в схему симметрирующего устройства для преобразования входного небалансного сигнала. Недостатком данной схемы являются увеличенная ошибка установки фазы и массогабаритные характеристики фазовращателя, снабженного симметрирующим устройством.

Известен фазовращатель [патент RU №2510980, МПК Н01Р 1/18, опубликованный 10.04.2012], выбранный за прототип, который включает полифазный RC-фильтр с двумя входами, аналоговый квадратурный дифференциальный сумматор, состоящий из двух дифференциальных усилителей с переменным коэффициентом усиления в виде ячеек Гильберта и нагрузки, источник питания, цифроаналоговый преобразователь, источник напряжений смещения, преобразователь дифференциального сигнала в небалансный. Выходы полифазного RC-фильтра соединены со входами аналогового квадратурного дифференциального сумматора. Выходы сумматора подключены к входам преобразователя дифференциального сигнала в небалансный. Для работы фазовращателя требуется входной дифференциальный сигнал, формируемый из небалансного сигнала внешним входным симметрирующим устройством с одним входом и двумя выходами. Первый выход симметрирующего устройства подключен к первому входу полифазного RC-фильтра, второй выход симметрирующего устройства подключен ко второму входу полифазного RC-фильтра. Недостатком данной схемы является увеличение ошибки установки фазы из-за использования внешнего входного симметрирующего устройства, поскольку амплитудно-фазовый дисбаланс симметрирующего устройства непосредственно влияет на амплитуды и фазы сигналов, в результате сложения которых формируется выходной сигнал фазовращателя. Кроме этого, схема с внешними элементами имеет худшие массогабаритные характеристики по сравнению с полностью интегральным решением.

Технической проблемой изобретения является создание фазовращателя с небалансным входом, уменьшенной ошибкой установки фазы и улучшенными массогабаритными характеристиками за счет исключения внешнего входного симметрирующего устройства.

Сущность предлагаемого технического решения заключается в том, что аналогично прототипу высокочастотный векторный фазовращатель включает полифазный RC-фильтр, первый вход которого является входом фазовращателя, аналоговый квадратурный дифференциальный сумматор, состоящий из двух дифференциальных усилителей с переменным коэффициентом усиления в виде ячеек Гильберта и нагрузки, подключенной к шине питания, цифроаналоговый преобразователь, источник напряжений смещения, преобразователь дифференциального сигнала в небалансный. В отличие от прототипа второй вход полифазного RC-фильтра заземлен. Дополнительно фазовращатель содержит блок ослабления синфазной составляющей, имеющий дифференциальный вход, соединенный с аналоговым квадратурным дифференциальным сумматором, два входа напряжений смещения, подключенные к выходам источника напряжений смещения, дифференциальный выход, соединенный с преобразователем дифференциального сигнала в небалансный.

Блок ослабления синфазной составляющей, в частном случае, может содержать первый, второй, третий, четвертый, пятый, шестой конденсаторы, первый, второй, третий, четвертый, пятый, шестой резисторы, первый, второй, третий, четвертый, пятый, шестой МОП-транзисторы, первую и вторую катушки индуктивности.

Первый конденсатор подключен к истоку первого МОП-транзистора, стоку второго МОП-транзистора и второму конденсатору. Третий конденсатор подключен к истоку третьего МОП-транзистора, стоку четвертого МОП-транзистора и четвертому конденсатору. Исток второго МОП-транзистора и исток четвертого МОП-транзистора соединены. Затвор второго МОП-транзистора и затвор четвертого МОП-транзистора соединены. Затвор первого МОП-транзистора подключен к первому резистору и четвертому конденсатору. Затвор третьего МОП-транзистора подключен ко второму резистору и второму конденсатору. Первый резистор и второй резистор соединены. Сток первого МОП-транзистора подключен к истоку пятого МОП-транзистора и пятому конденсатору. Сток третьего МОП-транзистора подключен к истоку шестого МОП-транзистора и шестому конденсатору. Затвор пятого МОП-транзистора подключен к третьему резистору и шестому конденсатору. Затвор шестого МОП-транзистора подключен к четвертому резистору и пятому конденсатору. Сток пятого МОП-транзистора подключен к первой катушке индуктивности и пятому резистору. Сток шестого МОП-транзистора подключен ко второй катушке индуктивности и шестому резистору. Первая и вторая катушка индуктивности, третий, четвертый, пятый и шестой резисторы соединены.

Дифференциальный вход блока ослабления синфазной составляющей состоит из положительного и отрицательного входов. Положительный вход блока ослабления синфазной составляющей подключен к первому конденсатору. Отрицательный вход блока ослабления синфазной составляющей подключен к третьему конденсатору. Исток второго МОП-транзистора и исток четвертого МОП-транзистора заземлены. Затвор второго МОП-транзистора и затвор четвертого МОП-транзистора подключены к первому входу напряжения смещения. Первый резистор и второй резистор подключены ко второму входу напряжения смещения. Третий, четвертый, пятый, шестой резисторы, первая и вторая катушки индуктивности подключены к шине питания. Дифференциальный выход блока ослабления синфазной составляющей состоит из первого и второго выходов. Положительный выход блока ослабления синфазной составляющей подключен к первой катушке индуктивности, пятому резистору и стоку пятого МОП-транзистора. Отрицательный выход блока ослабления синфазной составляющей подключен ко второй катушке индуктивности, шестому резистору и стоку шестого МОП-транзистора.

Введение блока ослабления синфазной составляющей позволяет подключить небалансный выход источника сигнала напрямую к первому входу полифазного RC-фильтра, заземлив второй вход. При небалансном входном сигнале с выхода полифазного RC-фильтра на входы аналогового квадратурного дифференциального сумматора поступают непротивофазные сигналы с различными амплитудами и фазами. Из-за низкого коэффициента ослабления синфазной составляющей дифференциальных усилителей, входящих в состав аналогового квадратурного дифференциального сумматора, выходной сигнал сумматора содержит как разностную, так и синфазную компоненты. Блок ослабления синфазной составляющей увеличивает коэффициент ослабления синфазной составляющей. В результате отсутствует потребность во внешнем входном симметрирующем устройстве, существенно увеличивающем ошибку установки фазы из-за собственного амплитудно-фазового дисбаланса. При этом достигается уменьшение массогабаритных характеристик за счет полностью интегрального исполнения фазовращателя.

Блок ослабления синфазной составляющей также может быть реализован на основе трансформатора, например, по патенту US №20140225698, МПК H01F 27/29, H01F 41/04, опубликованному 01.04.2014, или дифференциального усилителя, например, по патенту US №3970950, МПК H03F 3/45, опубликованному 20.07.1976.

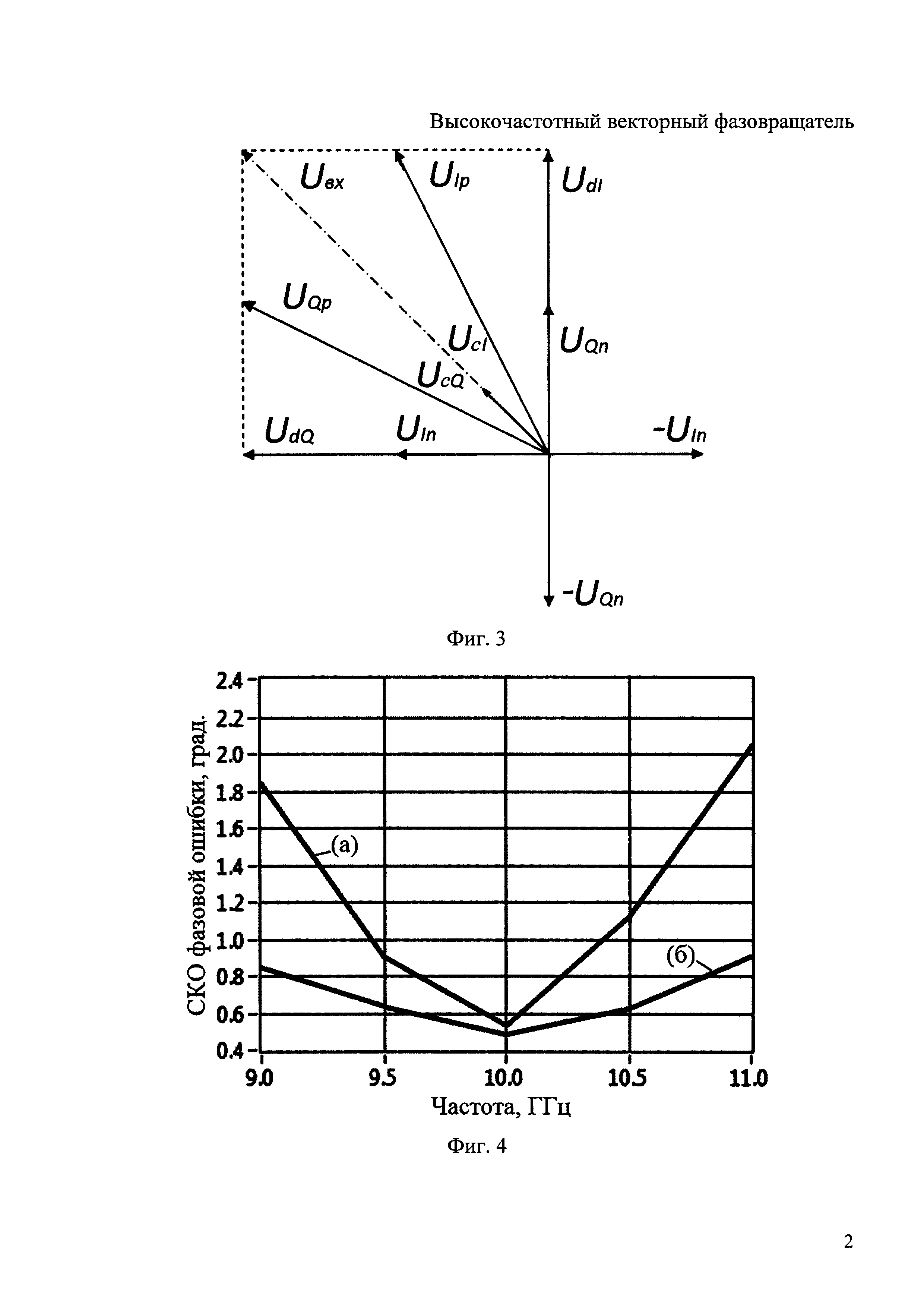

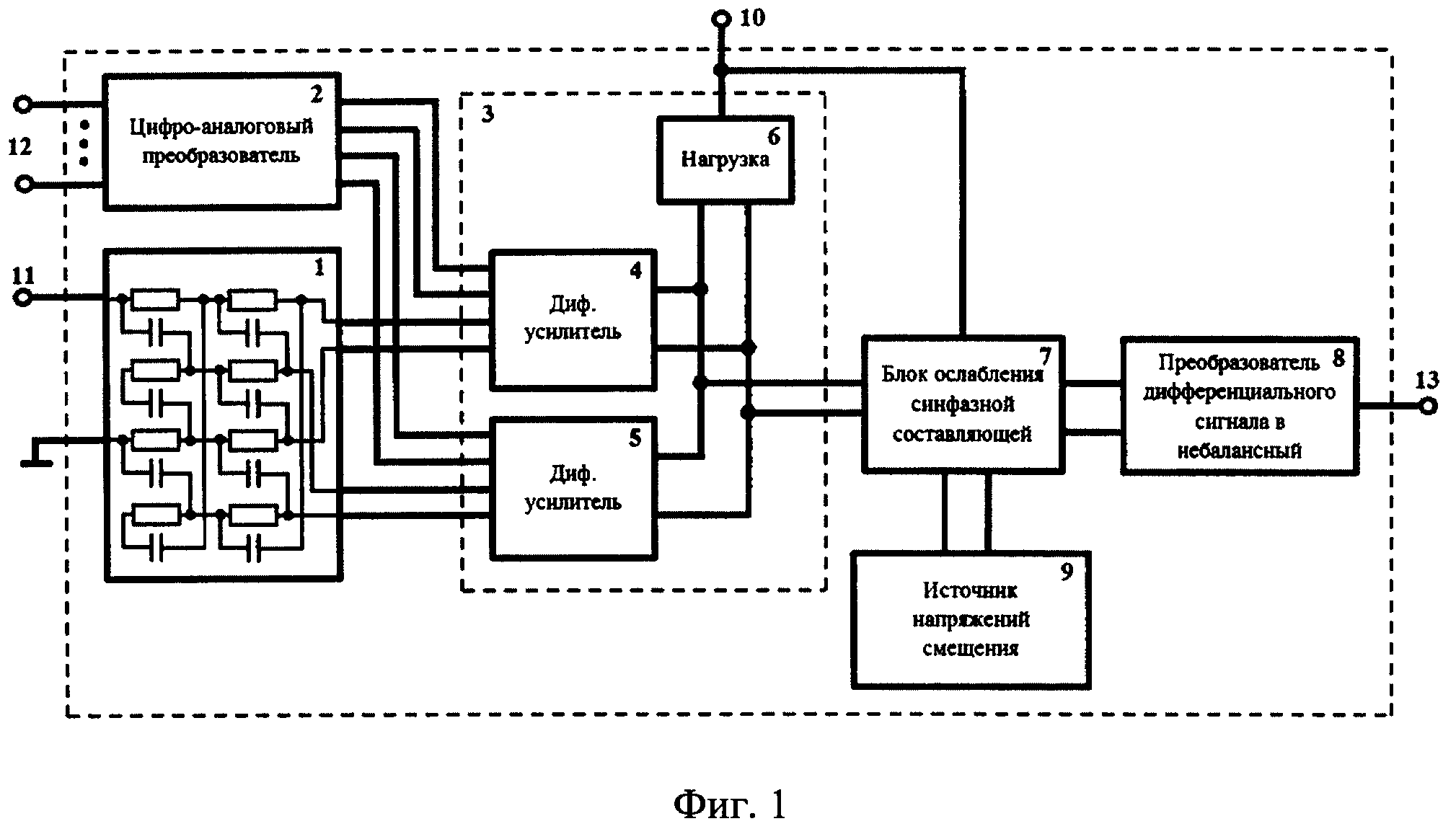

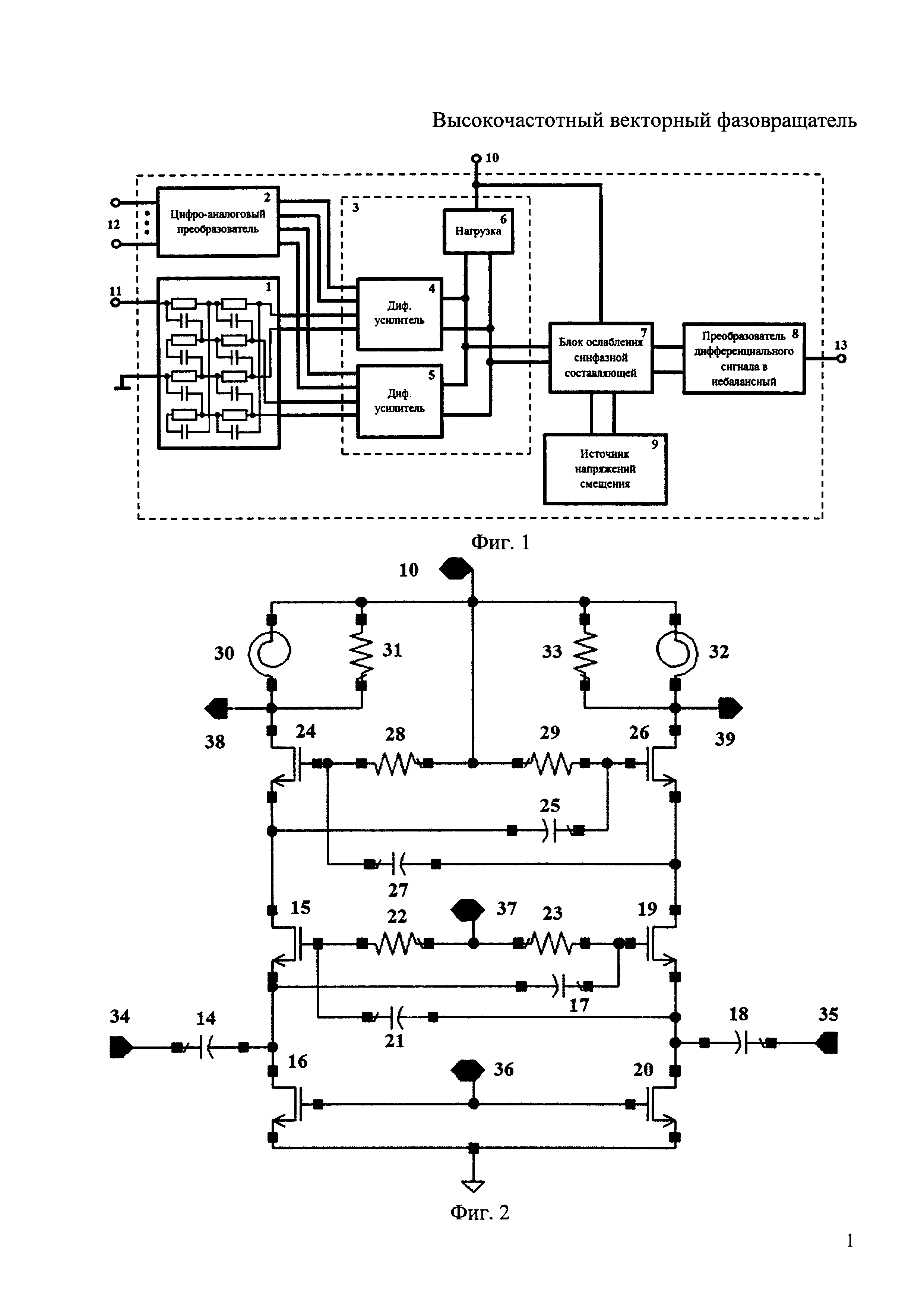

Предлагаемое изобретение иллюстрируется графическими материалами, представленными на фиг. 1-4:

на фиг. 1 изображена структурная схема фазовращателя;

на фиг. 2 изображена принципиальная схема частного случая реализации блока ослабления синфазной составляющей;

на фиг. 3 представлена векторная диаграмма полифазного RC-фильтра с небалансным входом;

на фиг. 4 представлены зависимости среднеквадратичного отклонения ошибки установки фазы от частоты для фазовращателя, снабженного симметрирующим устройством, и предлагаемого фазовращателя.

Высокочастотный векторный фазовращатель (фиг. 1) включает полифазный RC-фильтр 1, цифроаналоговый преобразователь 2, аналоговый квадратурный дифференциальный сумматор 3, дифференциальные усилители 4 и 5, нагрузку 6, блок 7 ослабления синфазной составляющей, преобразователь 8 дифференциального сигнала в небалансный, источник 9 напряжений смещения, шину питания 10. При этом высокочастотный небалансный вход полифазного RC-фильтра 11 является входом фазовращателя, входы цифроаналогового преобразователя 2 являются входами 12 цифровых управляющих сигналов фазовращателя, выход преобразователя 8 дифференциального сигнала в небалансный является высокочастотным небалансным выходом 13 фазовращателя.

К выходам полифазного RC-фильтра 1 подключены высокочастотные входы аналогового квадратурного дифференциального сумматора 3, который состоит из двух одинаковых дифференциальных усилителей 4 и 5 с переменным коэффициентом усиления на основе ячейки Гильберта. Управляющий дифференциальный вход каждого усилителя 4 и 5 подключен к одной из двух пар дифференциальных выходов цифроаналогового преобразователя 2. Дифференциальные выходы усилителей 4 и 5 подключены к выводам нагрузки 6, которая обеспечивает питание усилителей 4 и 5 от шины питания 10, и к дифференциальному входу блока 7 ослабления синфазной составляющей. Дифференциальный вход преобразователя 8 дифференциального сигнала в небалансный подключен к дифференциальному выходу блока 7 ослабления синфазной составляющей. Выходы источника 9 напряжений смещения подключены к входам напряжений смещения блока 7 ослабления синфазной составляющей.

Принципиальная схема частного случая реализации блока ослабления синфазной составляющей изображена на фиг. 2 и состоит из первого, второго, третьего, четвертого, пятого, шестого конденсаторов, первого, второго, третьего, четвертого, пятого, шестого резисторов, первого, второго, третьего, четвертого, пятого, шестого МОП-транзисторов, первой и второй катушек индуктивности, соединенных следующим образом: первый конденсатор 14 подключен к истоку первого МОП-транзистора 15, стоку второго МОП-транзистора 16 и второму конденсатору 17. Третий конденсатор 18 подключен к истоку третьего МОП-транзистора 19, стоку четвертого МОП-транзистора 20 и четвертому конденсатору 21. Исток второго МОП-транзистора 16 и исток четвертого МОП-транзистора 20 соединены. Затвор второго МОП-транзистора 16 и затвор четвертого МОП-транзистора 20 соединены. Затвор первого МОП-транзистора 15 подключен к первому резистору 22 и четвертому конденсатору 21. Затвор третьего МОП-транзистора 19 подключен ко второму резистору 23 и второму конденсатору 17. Первый резистор 22 и второй резистор 23 соединены. Сток первого МОП-транзистора 15 подключен к истоку пятого МОП-транзистора 24 и пятому конденсатору 25. Сток третьего МОП-транзистора 19 подключен к истоку шестого МОП-транзистора 26 и шестому конденсатору 27. Затвор пятого МОП-транзистора 24 подключен к третьему резистору 28 и шестому конденсатору 27. Затвор шестого МОП-транзистора 26 подключен к четвертому резистору 29 и пятому конденсатору 25. Сток пятого МОП-транзистора 24 подключен к первой катушке индуктивности 30 и пятому резистору 31. Сток шестого МОП-транзистора 26 подключен ко второй катушке индуктивности 32 и шестому резистору 33. Третий резистор 28, четвертый резистор 29, пятый резистор 31, шестой резистор 33, первая катушка индуктивности 30, вторая катушка индуктивности 32 соединены.

Дифференциальный вход блока 7 ослабления синфазной составляющей состоит из положительного входа 34 и отрицательного входа 35. Положительный вход 34 блока 7 ослабления синфазной составляющей подключен к первому конденсатору 14. Отрицательный вход 35 блока 7 ослабления синфазной составляющей подключен к третьему конденсатору 18. Исток второго МОП-транзистора 16 и исток четвертого МОП-транзистора 20 заземлены. Затвор второго МОП-транзистора 16 и затвор четвертого МОП-транзистора 20 подключены к первому входу 36 напряжения смещения. Первый резистор 22 и второй резистор 23 подключены ко второму входу 37 напряжения смещения. Третий 28, четвертый 29, пятый 31, шестой 33 резисторы, первая 30 и вторая 32 катушки индуктивности подключены к шине питания 10. Дифференциальный выход блока 7 ослабления синфазной составляющей состоит из положительного выхода 38 и отрицательного выхода 39. Положительный выход 38 блока 7 ослабления синфазной составляющей подключен к первой катушке индуктивности 30, пятому резистору 31 и стоку пятого МОП-транзистора 24. Отрицательный выход 39 блока 7 ослабления синфазной составляющей подключен ко второй катушке индуктивности 32, шестому резистору 33 и стоку шестого МОП-транзистора 26.

Фазовращатель работает следующим образом. Входной небалансный сигнал Uвх поступает на вход 11 фазовращателя и, проходя через полифазный RC-фильтр 1, преобразуется в четыре выходных сигнала полифазного RC-фильтра UIp, UQp, UIn, UQn (фиг. 3), которые поступают на аналоговый квадратурный дифференциальный сумматор 3.

Пара сигналов UIp и UIn поступает на дифференциальный усилитель 4, где при вычитании формируется сигнал, содержащий разностную UdI и синфазную UcI составляющие. Пара сигналов UQp и UQn поступает на дифференциальный усилитель 5, где при вычитании формируется сигнал, содержащий разностную UdQ и синфазную UcQ составляющие. Выходные сигналы усилителей 4 и 5, амплитуды которых определяются сигналами на дифференциальных выходах цифроаналогового преобразователя 2, складываются в общей нагрузке 6. В результате на выходе квадратурного дифференциального сумматора 3 формируется выходной дифференциальный сигнал, содержащий противофазный сигнал с требуемым фазовым сдвигом, и паразитный синфазный сигнал. Сигналы с выходов аналогового квадратурного дифференциального сумматора 3 поступают на входы 34 и 35 блока 7 ослабления синфазной составляющей, где происходит подавление паразитного синфазного сигнала.

Сигнал, поступающий на вход 34 блока 7 ослабления синфазной составляющей через конденсатор 14, подается на исток МОП-транзистора 15 и через конденсатор 17 - на затвор МОП-транзистора 19. Сигнал, поступающий на вход 35 блока 7 ослабления синфазной составляющей через конденсатор 18, подается на исток МОП-транзистора 19 и через конденсатор 21 - на затвор МОП-транзистора 15.

Для противофазного сигнала при увеличении напряжения на истоке МОП-транзистора 15 и затворе МОП-транзистора 19 происходит уменьшение напряжения на истоке МОП-транзистора 19 и затворе МОП-транзистора 15, при уменьшении напряжения на истоке МОП-транзистора 15 и затворе МОП-транзистора 19 происходит увеличение напряжения на истоке МОП-транзистора 19 и затворе МОП-транзистора 15. Таким образом, на одном полупериоде МОП-транзистор 15 уменьшает протекающий ток, а МОП-транзистор 19 увеличивает протекающий ток, в то время как на другом полупериоде МОП-транзистор 19 уменьшает протекающий ток, а МОП-транзистор 15 увеличивает протекающий ток, что приводит к появлению выходного сигнала на выходах 38 и 39 блока 7.

Для синфазного сигнала при увеличении напряжения на истоке МОП-транзистора 15 и затворе МОП-транзистора 19 происходит увеличение напряжения на истоке МОП-транзистора 19 и затворе МОП-транзистора 15, при уменьшении напряжения на истоке МОП-транзистора 15 и затворе МОП-транзистора 19 происходит уменьшение напряжения на истоке МОП-транзистора 19 и затворе МОП-транзистора 15. Таким образом, напряжение затвор-исток МОП-транзисторов 15 и 19, ток через МОП-транзисторы 15 и 19 и выходной сигнал не изменяются, что приводит к ослаблению синфазной составляющей входного сигнала.

Для увеличения коэффициента ослабления синфазной составляющей последовательно включена еще одна пара МОП-транзисторов 24 и 26 в аналогичном режиме работы. При этом сигнал со стока МОП-транзистора 15 поступает на затвор МОП-транзистора 26 через конденсатор 25, а сигнал со стока МОП-транзистора 19 поступает на затвор МОП-транзистора 24 через конденсатор 27.

МОП-транзисторы 16 и 20 задают рабочие токи схемы. Катушки индуктивности 30 и 32 компенсируют паразитные емкости МОП-транзисторов. Смещение рабочих точек МОП-транзисторов 16, 20 осуществляется через вход 36 источником 9 напряжений смещения. Смещение рабочих точек МОП-транзисторов 15, 19 осуществляется через вход 37 источником 9 напряжений смещения через резисторы 22, 23. Смещение рабочих точек МОП-транзисторов 24, 26 осуществляется шиной питания 10 через резисторы 28 и 29. Сигнал с выходов 38 и 39 блока 7 ослабления синфазной составляющей поступает на вход преобразователя 8, где преобразуется из дифференциальной формы в небалансную и поступает на выход фазовращателя 13 с требуемым фазовым сдвигом.

Для подтверждения решения технической проблемы проведено компьютерное моделирование двух схем шестиразрядных фазовращателей. Первая схема состояла из симметрирующего устройства на основе RLC-цепи, полифазного RC-фильтра с двумя входами, квадратурного дифференциального сумматора, преобразователя дифференциального сигнала в небалансный, цифроаналогового преобразователя, источника нпряжений смещения. Вторая схема состояла из полифазного RC-фильтра с одним входом, второй вход заземлен, квадратурного дифференциального сумматора, блока подавления синфазной составляющей, преобразователя дифференциального сигнала в небалансный, цифроаналогового преобразователя, источника напряжений смещения. В качестве цифроаналогового преобразователя и источника напряжений смещения в обоих случаях были использованы идеальные источники для исключения влияния ошибок этих блоков. Моделирование зависимостей абсолютной ошибки установки фазы от частоты в полосе 9,0-11,0 ГГц для каждого значения управляющего сигнала проводилось при одинаковых высокочастотных и цифровых управляющих сигналах. На фиг. 4 представлены зависимости среднеквадратичного отклонения ошибки установки фазы от частоты, вычисленные на основе значений абсолютной ошибки установки фазы, для схемы с симметрирующим устройством (а) и для предлагаемого технического решения (б). Как видно из приведенных зависимостей, применение предлагаемого технического решения позволяет уменьшить ошибку установки фазы более чем в два раза при отстройке на 1 ГГц от центральной частоты диапазона. При этом чем шире полоса рабочих частот и хуже характеристики симметрирующего устройства, тем значительнее уменьшение ошибки установки фазы фазовращателя за счет применения предложенного технического решения.

Предложенное схемотехническое решение позволило синтезировать схему фазовращателя с небалансным входом без использования дополнительного симметрирующего устройства, что позволило снизить ошибку установки фазы фазовращателя за счет исключения амплитудно-фазового дисбаланса симметрирующего устройства и уменьшить массогабаритные характеристики за счет полностью интегрального исполнения без использования внешних элементов.