Результат интеллектуальной деятельности: Аналоговый интегратор

Вид РИД

Изобретение

Изобретение относится к промышленной электронике, аналого-цифровой технике и схемотехнике. Оно, в частности, может быть использовано для интегрирования аналоговых электрических напряжений, изменяющихся во времени.

Известна схема интегратора (Опадчий Ю.Ф., Глудкин Ю.П., Гуров А.И. Аналоговая и цифровая электроника. – М.: Горячая линия. – Телеком, 2003, с.306, рис. 8.12, а), содержащий операционный усилитель, резистор и конденсатор, неинвертирующий вход операционного усилителя заземлён, один из выводов резистора соединён с его инвертирующим входом, а другой вывод образует вход схемы интегратора относительно «земли», конденсатор включен между инвертирующим входом операционного усилителя и его выходом, этот выход также образует выход схемы интегратора относительно «земли» .

Недостатком его является ограниченная точность интегрирования. Идеального преобразования электрических сигналов в том числе идеального интегрирования, как правило, не бывает. Погрешность операции интегрирования ограничивает точность интегрирования. Эта погрешность зависит от эквивалентной постоянной времени интегрирования

где R и С – сопротивление и ёмкость интегратора, K – коэффициент усиления операционного усилителя (справочный параметр). В частности, при воздействии на вход интегратора чередующихся перепадов напряжения положительной и отрицательной полярности с плоскими вершинами между перепадами на выходе получается чередующиеся возрастания и убывания напряжений по закону близкому к линейному. Например, в интервале времени  возрастания выходного напряжения коэффициент нелинейности определяется известным выражением

возрастания выходного напряжения коэффициент нелинейности определяется известным выражением

В данном случае этот коэффициент является относительной погрешностью интегрирования. Для обеспечения малой погрешности интегрирования  (2) значение эквивалентной постоянной времени

(2) значение эквивалентной постоянной времени  (1) следует выбирать большим во многом за счёт увеличения коэффициента усиления K операционного усилителя. Значение K является ограниченным и соответствует современным уровням схемотехники и технологии изготовления изделий микроэлектроники. Ограниченное значение K, ограничивает эквивалентную постоянную времени

(1) следует выбирать большим во многом за счёт увеличения коэффициента усиления K операционного усилителя. Значение K является ограниченным и соответствует современным уровням схемотехники и технологии изготовления изделий микроэлектроники. Ограниченное значение K, ограничивает эквивалентную постоянную времени  (1) и ограничивает повышение точности интегрирования. Имеется потребность в повышении точности интегрирования электрических сигналов.

(1) и ограничивает повышение точности интегрирования. Имеется потребность в повышении точности интегрирования электрических сигналов.

Наиболее близкой по технической сущности и достигаемому результату является выбранный в качестве прототипа аналоговый интегратор (Патент РФ № 2602374. Аналоговый интегратор / Г.И. Передельский, Бюл. 2016, № 32), содержащий два операционных усилителя, два конденсатора и четыре резистора, первый резистор подключен к инвертирующему входу первого операционного усилителя, второй вывод этого резистора образует вход относительно «земли» аналогового интегратора, второй резистор включен между «землей» и инвертирующим входом первого операционного усилителя, инвертирующий вход второго операционного усилителя соединён с первым выводом первого конденсатора и с общим выводом первого резистора и инвертирующего входа первого операционного усилителя, к выходу этого усилителя подключена цепь из последовательно соединённых третьего и четвёртого резисторов, свободный вывод последнего резистора заземлен, а параллельно третьему резистору включен второй конденсатор, общий вывод второго конденсатора, третьего и четвёртого резисторов соединён с неинвертирующим входом второго операционного усилителя, второй (свободный) вывод первого конденсатора соединён с выходом второго операционного усилителя и полученный общий вывод является выходом относительно «земли» аналогового интегратора.

Недостатком его является ограниченная точность интегрирования, определяющаяся погрешностью операции интегрирования.

В частности, при воздействии на вход интегратора чередующихся перепадов напряжения положительной и отрицательной полярности с плоскими вершинами относительная погрешность интегрирования определяется выражением

(3)

(3)

где  – интервал времени между двумя соседними перепадами входного напряжения,

– интервал времени между двумя соседними перепадами входного напряжения,  и

и  – сопротивление и емкость интегрирующей цепи,

– сопротивление и емкость интегрирующей цепи,  и

и  - коэффициенты усиления первого и второго операционного усилителя и

- коэффициенты усиления первого и второго операционного усилителя и  − коэффициент передачи делителя напряжения на двух последовательно соединённых резисторах. Для обеспечения малого значения относительной погрешности интегрирования следует обеспечить большое значение знаменателя в (3). Это во многом можно реализовать за счёт увеличения значения коэффициентов усиления

− коэффициент передачи делителя напряжения на двух последовательно соединённых резисторах. Для обеспечения малого значения относительной погрешности интегрирования следует обеспечить большое значение знаменателя в (3). Это во многом можно реализовать за счёт увеличения значения коэффициентов усиления  и

и  . Но реально коэффициент усиления операционных усилителей является ограниченным и имеет определённое, конкретное значение. В рамках ограниченных и определённых значений этих коэффициентов следует найти возможность для уменьшения погрешности интегрирования.

. Но реально коэффициент усиления операционных усилителей является ограниченным и имеет определённое, конкретное значение. В рамках ограниченных и определённых значений этих коэффициентов следует найти возможность для уменьшения погрешности интегрирования.

Задача, на решение которой направлено изобретение, состоит в уменьшении погрешности интегрирования.

Это достигается тем, что в аналоговый интегратор, содержащий два операционных усилителя, два конденсатора и четыре резистора, первый резистор подключен к инвертирующему входу первого операционного усилителя, второй вывод этого резистора образует вход относительно «земли» аналогового интегратора, второй резистор включен между «землей» и инвертирующим входом первого операционного усилителя, инвертирующий вход второго операционного усилителя соединён с первым выводом первого конденсатора и с общим выводом первого резистора и инвертирующего входа первого операционного усилителя, к выходу этого усилителя подключена цепь из последовательно соединённых третьего и четвёртого резисторов, свободный вывод последнего резистора заземлён, а параллельно третьему резистору включен второй конденсатор, общий вывод второго конденсатора, третьего и четвёртого резисторов соединён с неинвертирующим входом второго операционного усилителя, введены дополнительный операционный усилитель, дополнительный конденсатор, два дополнительных резистора и изменено соединение элементов, инвертирующий вход дополнительного операционного усилителя соединён с общим выводом имеющегося первого резистора, инвертирующих входов имеющихся двух операционных усилителей и имеющегося первого конденсатора, выход дополнительного операционного усилителя образует выход относительно «земли» аналогового интегратора, с этим выходом соединён второй (свободный) вывод имеющегося первого конденсатора, между инвертирующим входом дополнительного операционного усилителя и выходом имеющегося второго операционного усилителя включены параллельно соединённые дополнительный конденсатор и дополнительный первый резистор, второй дополнительный резистор включен между «землей» и общим выводом дополнительного конденсатора, дополнительного первого резистора и неинвертирующего входа дополнительного операционного усилителя.

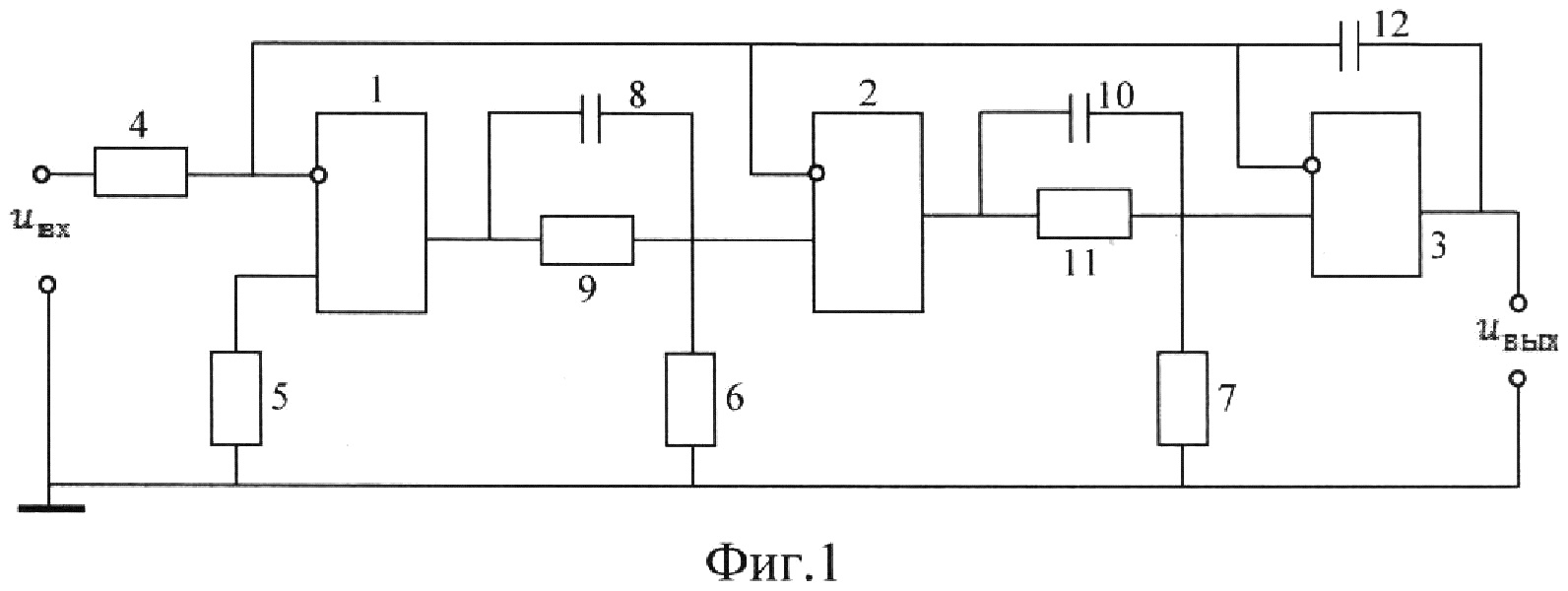

Сущность изобретения поясняется чертежом (фиг.1).

Аналоговый интегратор содержит три операционных усилителя 1, 2 и 3. Инвертирующие входы их соединены вместе и образуют общий вывод инвертирующих входов операционных усилителей. К этому общему выводу подключен первый вывод резистора 4, второй вывод которого образует вход относительно «земли» аналогового интегратора. Выход третьего операционного усилителя 3 образует выход относительно «земли» аналогового интегратора. Неинвертирующие входы каждого операционного усилителя через резисторы 5, 6 и 7 соединены с «землёй». Между выходом первого операционного усилителя 1 и общим выводом резистора 6 и неинвертирующего входа второго операционного усилителя 2 включены параллельно соединенные конденсатор 8 и резистор 9. Также между выходом второго операционного усилителя 2 и общим выводом резистора 7 и неинвертирующего входа третьего операционного усилителя 3 включены параллельно соединённые конденсатор 10 и резистор 11. Между общим выводом инвертирующих входов всех трёх операционных усилителей и выходом третьего операционного усилителя 3 включен конденсатор 12.

В исходном состоянии входное напряжение аналогового интегратора равно нулю ( ), выходное напряжение его тоже равно нулю (

), выходное напряжение его тоже равно нулю ( ).

).

Аналоговый интегратор работает следующим образом. При выборе операционных усилителей в схеме на фиг.1 с большим коэффициентом усиления получаем, что напряжение на их инвертирующих входах относительно «земли» имеет весьма малое значение (исчезающее малое значение, виртуальный нуль). Тогда сила электрического тока через резистор 4  определяется выражением

определяется выражением

Этот ток замыкается на ёмкость конденсатора 12

особенно при операционных усилителях с полевыми транзисторами на входах. Сила электрического тока ( ) и напряжение (

) и напряжение ( ) на ёмкости связаны между собой известной зависимостью

) на ёмкости связаны между собой известной зависимостью

(6)

(6)

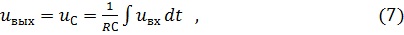

Напряжение на ёмкости с учётом ранее приводимого виртуального нуля является по сути выходным напряжением  аналогового интегратора. Используя (4), (5) из (6), получаем

аналогового интегратора. Используя (4), (5) из (6), получаем

т.е. выходное напряжение аналогового интегратора пропорционально интегралу от его входного напряжения.

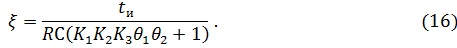

В частном случае при неизменяющемся входном напряжении выходное напряжение интегратора изменяется по почти линейному закону. Относительная погрешность в этом случае совпадает с коэффициентом нелинейности (2), где эквивалентная постоянная времени для схемы на фиг.1.

где ,

,  и

и  – коэффициенты усиления соответственно операционных усилителей 1, 2 и 3,

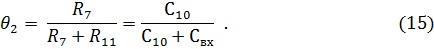

– коэффициенты усиления соответственно операционных усилителей 1, 2 и 3,  − коэффициент передачи делителя на сопротивлениях

− коэффициент передачи делителя на сопротивлениях  и

и  резисторов 6, 9,

резисторов 6, 9,  − коэффициент передачи делителя на сопротивлениях

− коэффициент передачи делителя на сопротивлениях  и

и  резисторов 7, 11

резисторов 7, 11

В аварийных режимах максимальное выходное напряжение (справочный параметр) операционного усилителя 1  может превысить допустимое входное напряжение

может превысить допустимое входное напряжение  операционного усилителя 2 (справочный параметр). Для устранения этого введена электрическая цепь (делитель напряжения) на резисторах 6 и 9. Коэффициент передачи его должен удовлетворять условию

операционного усилителя 2 (справочный параметр). Для устранения этого введена электрическая цепь (делитель напряжения) на резисторах 6 и 9. Коэффициент передачи его должен удовлетворять условию

Вместе с этим сумма сопротивлений  и

и  не должна быть меньше значения минимального сопротивления нагрузки (

не должна быть меньше значения минимального сопротивления нагрузки ( ) операционного усилителя 1 (справочный параметр)

) операционного усилителя 1 (справочный параметр)

Операционные усилители имеют входную паразитную ёмкость ( ). Эта ёмкость операционного усилителя 2 шунтирует резистор 6, поэтому конденсатор 8

). Эта ёмкость операционного усилителя 2 шунтирует резистор 6, поэтому конденсатор 8  введён для ослабления искажения передаваемого сигнала на высоких частотах. Для этого значение коэффициента передачи делителя на сопротивлениях

введён для ослабления искажения передаваемого сигнала на высоких частотах. Для этого значение коэффициента передачи делителя на сопротивлениях  и

и  должно равняться значению коэффициента передачи делителя на ёмкостях

должно равняться значению коэффициента передачи делителя на ёмкостях  и

и

Значение максимального выходного напряжения многих операционных усилителей находится в районе десяти вольт. Допустимое входное напряжение для них лежит в районе единиц вольт. Из (10) значение коэффициента передачи  определяется не на пределе, а с некоторым запасом и предположительно находится в районе значений 0,3÷0,7.

определяется не на пределе, а с некоторым запасом и предположительно находится в районе значений 0,3÷0,7.

Приведённые последние положения для двух операционных усилителей 1 и 2 в полной мере соответствуют таким же положениям для двух операционных усилителей 2 и 3. Этим положениям соответствуют формулы:

которые аналогичны выражениям (10), (11) и (12).

В общем случае при заряде ёмкости от неизменяющегося напряжения зарядный ток убывает. В рассматриваемой схеме на фиг. 1 это убывание электрического тока существенно ослабляется имеющейся отрицательной обратной связью, которая замыкается через ёмкость  . Это приводит к существенному уменьшению погрешности интегрирования. В случае неизменяющегося входного напряжения в интервале времени

. Это приводит к существенному уменьшению погрешности интегрирования. В случае неизменяющегося входного напряжения в интервале времени  относительная погрешность интегрирования аналогового интегратора (фиг.1) с учётом (2) и (8) определяется выражением

относительная погрешность интегрирования аналогового интегратора (фиг.1) с учётом (2) и (8) определяется выражением

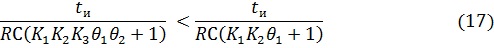

Сопоставление формул (16) и (3) приводит к неравенству

из-за наличия в знаменателе в левой части  . Таким образом, погрешность интегрирования в рассмотренном аналоговом интеграторе (фиг. 1) меньше, чем в прототипе (17).

. Таким образом, погрешность интегрирования в рассмотренном аналоговом интеграторе (фиг. 1) меньше, чем в прототипе (17).