Результат интеллектуальной деятельности: Дифференциатор для обработки аналоговых сигналов (варианты)

Вид РИД

Изобретение

Изобретение относится к электронике и может быть использовано для дифференцирования аналоговых сигналов в непрерывном времени, в частности, в адаптивных линейных фильтрах-компенсаторах высокочастотных потерь в линиях высокоскоростной передачи данных, в измерительных устройствах систем емкостной томографии, нейроморфных зрительных сенсорах, в схемах высокочастотной фильтрации, в схемах быстрого вычисления прогнозируемого приращения входного сигнала в быстродействующих многоразрядных АЦП, использующих аналоговое предсказание.

В указанных технических областях к дифференцирующим устройствам предъявляются высокие требования по ряду параметров, значения которых невозможно достичь при использовании классических решений на основе операционных усилителей. Например, при построении прогноза приращения входного сигнала на основе ряда Тейлора в АЦП с аналоговым предсказанием (см. [1]) требуется быстро вычислять с минимальными искажениями величину прогноза широкополосного сигнала, имеющего большой размах (Vp-p≈1,0 В) с тем, чтобы в рамках временного бюджета одного тактового периода (<10 нс) обеспечить больше времени на дальнейшую обработку сигнала.

Поэтому в последнее время наблюдается рост количества публикаций об устройствах, использующих специализированные схемные решения дифференциаторов. Известна схема низковольтного дифференциатора, работающего в токовом режиме, на основе усилителей тока, управляемых напряжением (см. [5]). Она предназначена для использования в схемах ВЧ-фильтрации. Недостатком известного устройства является узкая область применения.

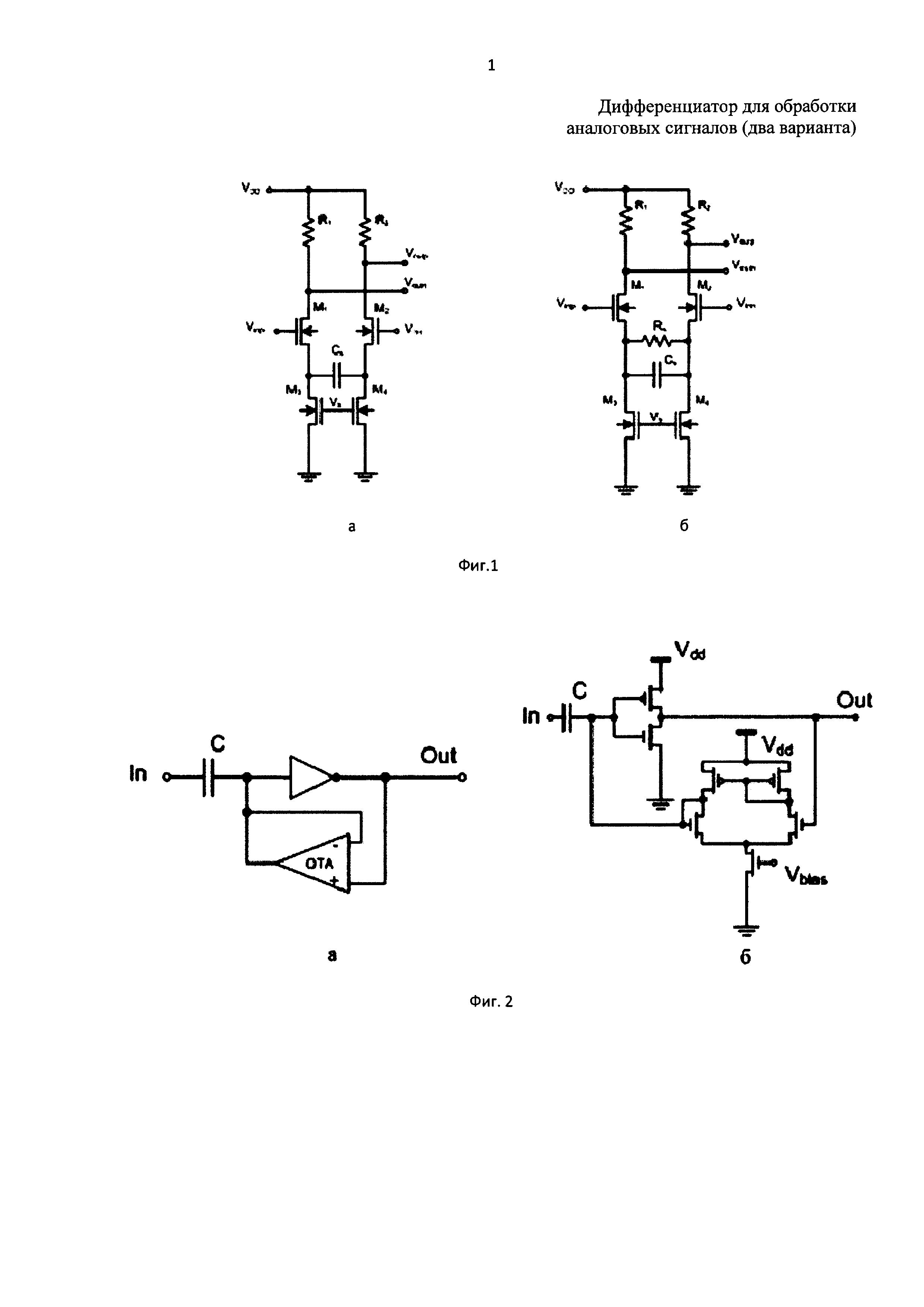

Известна схема дифференциатора, представленная на фиг. 1а (см. [2] и [3]), на основе дифференциального усилителя с конденсатором между истоками транзисторной пары и его модификация на фиг. 1б (см. [4]), которая имеет включенный параллельно конденсатору резистор, регулирующий АЧХ схемы. Недостатком известного устройства является невысокое быстродействие и зависимость линейности этого устройства от частоты. Также недостатком этой схемы является ее использование только в полностью дифференциальном варианте, что сужает область применения.

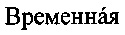

Наиболее близким к заявляемому решению является дифференциатор, выполненный на основе инвертора, охваченного активной обратной связью, построенной на вспомогательном усилителе, который включен в режиме повторителя напряжения (см. [7]). Структурная и принципиальная схемы устройства-прототипа приведены на фиг. 2а и фиг. 2б соответственно. Недостатком известного устройства является его невысокая линейность, например, схема с напряжением питания 3,3 В, предназначенная для изготовления в рамках технологического процесса КМОП-0,35 мкм, имеет значение параметра THD, равное 0,24% (-52,3 дБ), что видно из графика спектра на фиг. 3.  диаграмма входного и выходного сигналов данной схемы, приведенная на фиг. 4, показывает, что дифференциатор имеет задержку, равную ≈193 пс.

диаграмма входного и выходного сигналов данной схемы, приведенная на фиг. 4, показывает, что дифференциатор имеет задержку, равную ≈193 пс.

Техническим результатом патентуемого изобретения является повышение линейности и быстродействия.

Указанный технический результат обеспечивается дифференциатором для обработки аналоговых сигналов (по первому варианту), содержащим дифференцирующий конденсатор, основной усилитель передачи сигнала, вспомогательный усилитель, при этом первая из обкладок дифференцирующего конденсатора подключена к входу дифференциатора, а вторая обкладка соединена с инвертирующим входом вспомогательного усилителя и входом основного усилителя передачи сигнала, выход которого соединен с выходом дифференциатора, причем вспомогательный усилитель, у которого положительный вход подключен к источнику опорного напряжения, имеет коэффициент усиления больше 1, а основной усилитель передачи сигнала содержит транзистор, включенный по схеме с общим затвором, источник тока, резистор нагрузки, при этом положительный электрод источника тока соединен с инвертирующим входом вспомогательного усилителя, второй обкладкой дифференцирующего конденсатора и истоком транзистора, сток которого соединен с резистором нагрузки, при этом выход вспомогательного усилителя соединен с затвором транзистора основного усилителя передачи сигнала.

Транзистор, вспомогательный усилитель и источник тока образуют известную схемную конфигурацию, называемую каскод с активной обратной связью, или регулируемый каскод.

На фиг. 1а изображена принципиальная схема дифференциатора на основе дифференциального усилителя.

На фиг. 1б - модифицированная принципиальная схема дифференциатора на основе дифференциального усилителя.

На фиг. 2а - структурная схема устройства-прототипа.

На фиг. 2б - принципиальная схема устройства-прототипа.

На фиг. 3 - спектр сигнала на выходе устройства-прототипа.

На фиг. 4 -  диаграмма входного и выходного сигналов устройства-прототипа.

диаграмма входного и выходного сигналов устройства-прототипа.

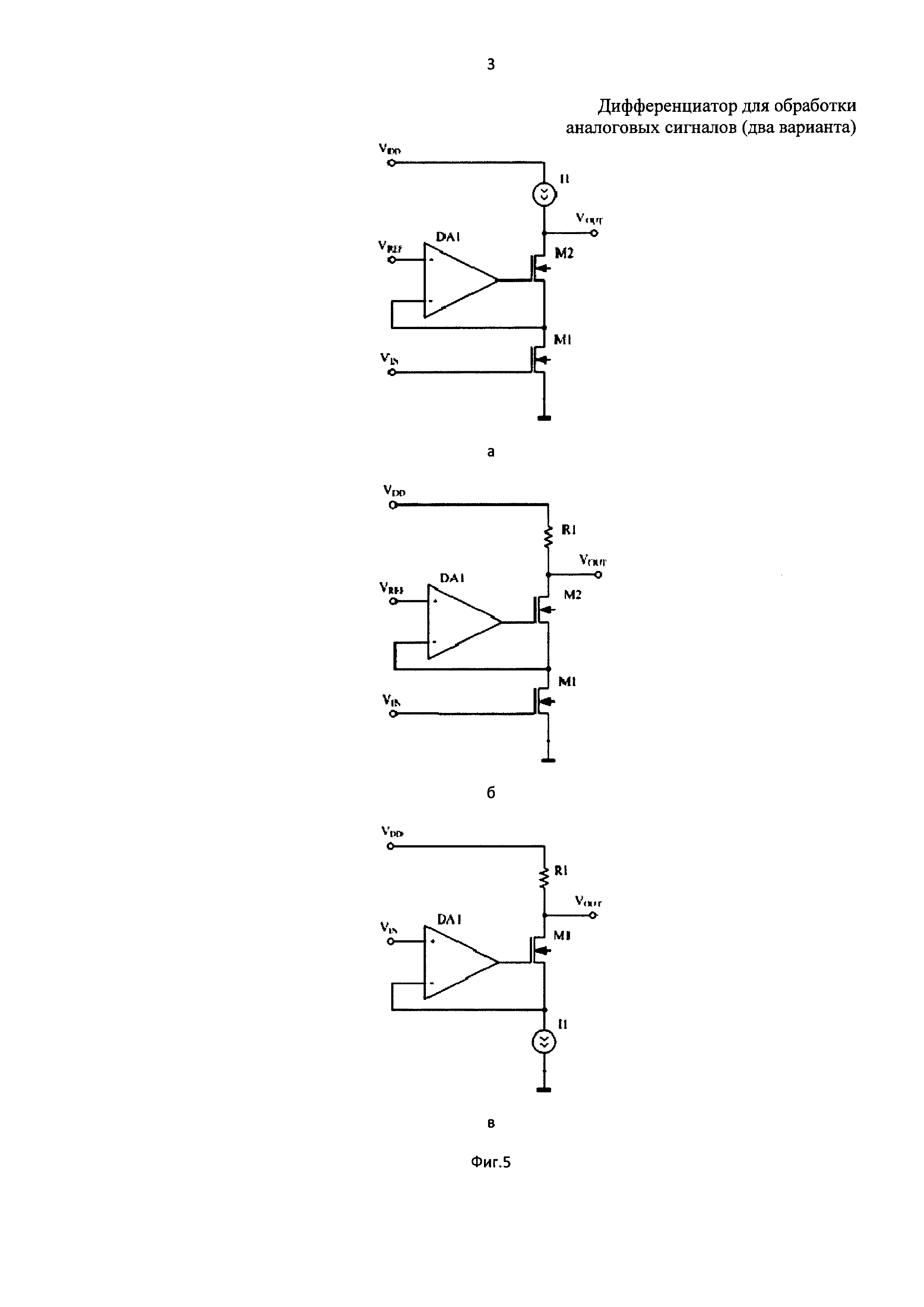

На фиг. 5а - принципиальная схема активного каскода с активной нагрузкой.

На фиг. 5б - принципиальная схема активного каскода с пассивной (резистивной) нагрузкой.

На фиг. 5в - принципиальная схема регулируемого каскода с подачей входного сигнала через вспомогательный усилитель.

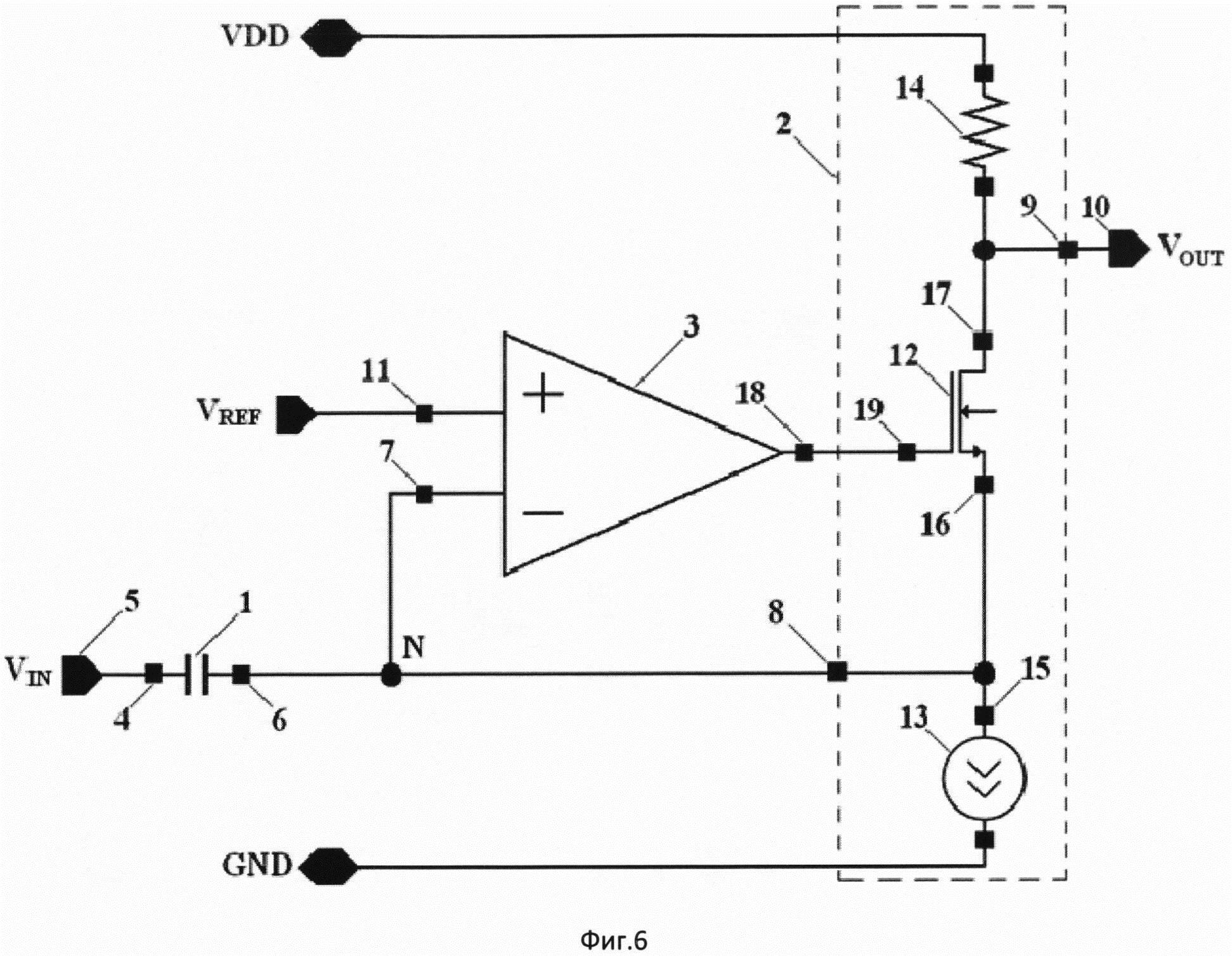

На фиг. 6 - электрическая принципиальная схема патентуемого дифференциатора.

На фиг. 7 - амплитудно-частотная характеристика патентуемого дифференциатора.

На фиг. 8а представлен спектр выходного сигнала патентуемого дифференциатора для частоты 5 МГц.

На фиг. 8б - спектр выходного сигнала патентуемого дифференциатора для частоты 25 МГц.

На фиг. 8в - спектр выходного сигнала патентуемого дифференциатора для частоты 50 МГц.

На фиг. 9 - временная диаграмма входного и выходного сигналов патентуемого дифференциатора.

На фиг. 10 - временная диаграмма входного и выходного сигналов дифференциатора-прототипа.

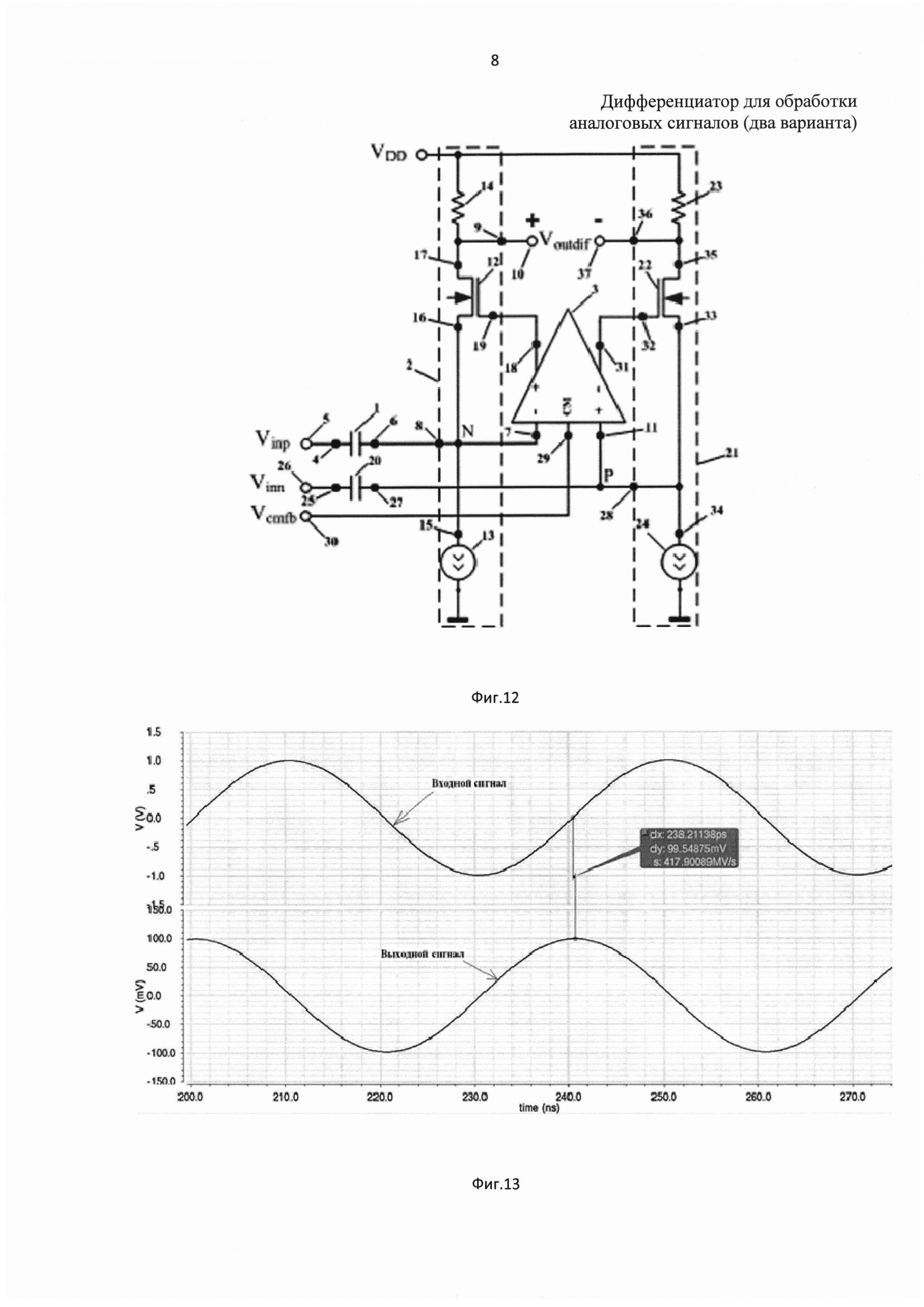

На фиг. 11а - спектр выходного сигнала дифференциатора-прототипа для частоты 5 МГц.

На фиг. 11б - спектр выходного сигнала дифференциатора-прототипа для частоты 25 МГц.

На фиг. 11в - спектр выходного сигнала дифференциатора-прототипа для частоты 50 МГц.

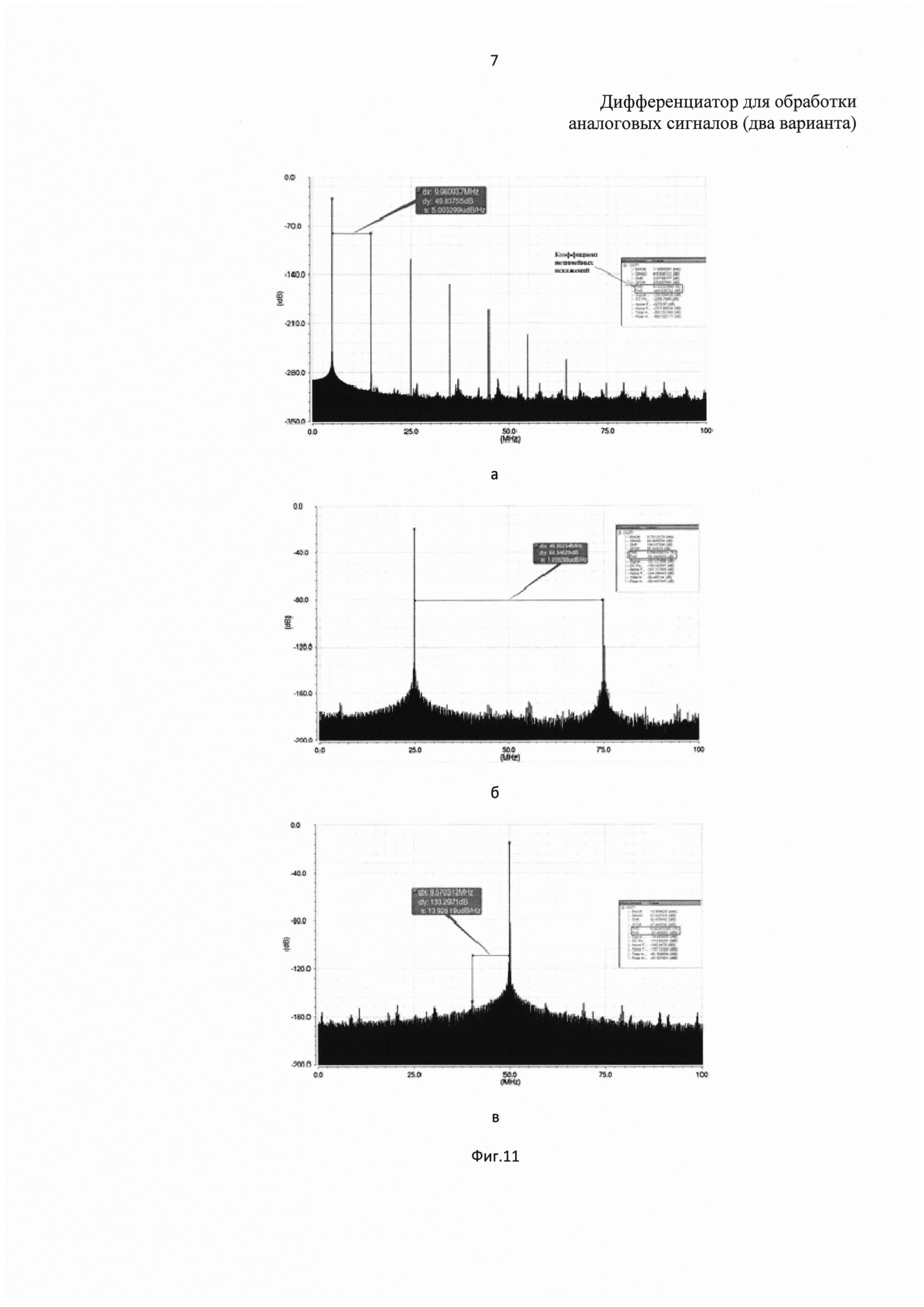

На фиг. 12 - электрическая схема патентуемого дифференциатора в полностью дифференциальном исполнении.

На фиг. 13 -  диаграмма входного и выходного сигналов патентуемого дифференциатора.

диаграмма входного и выходного сигналов патентуемого дифференциатора.

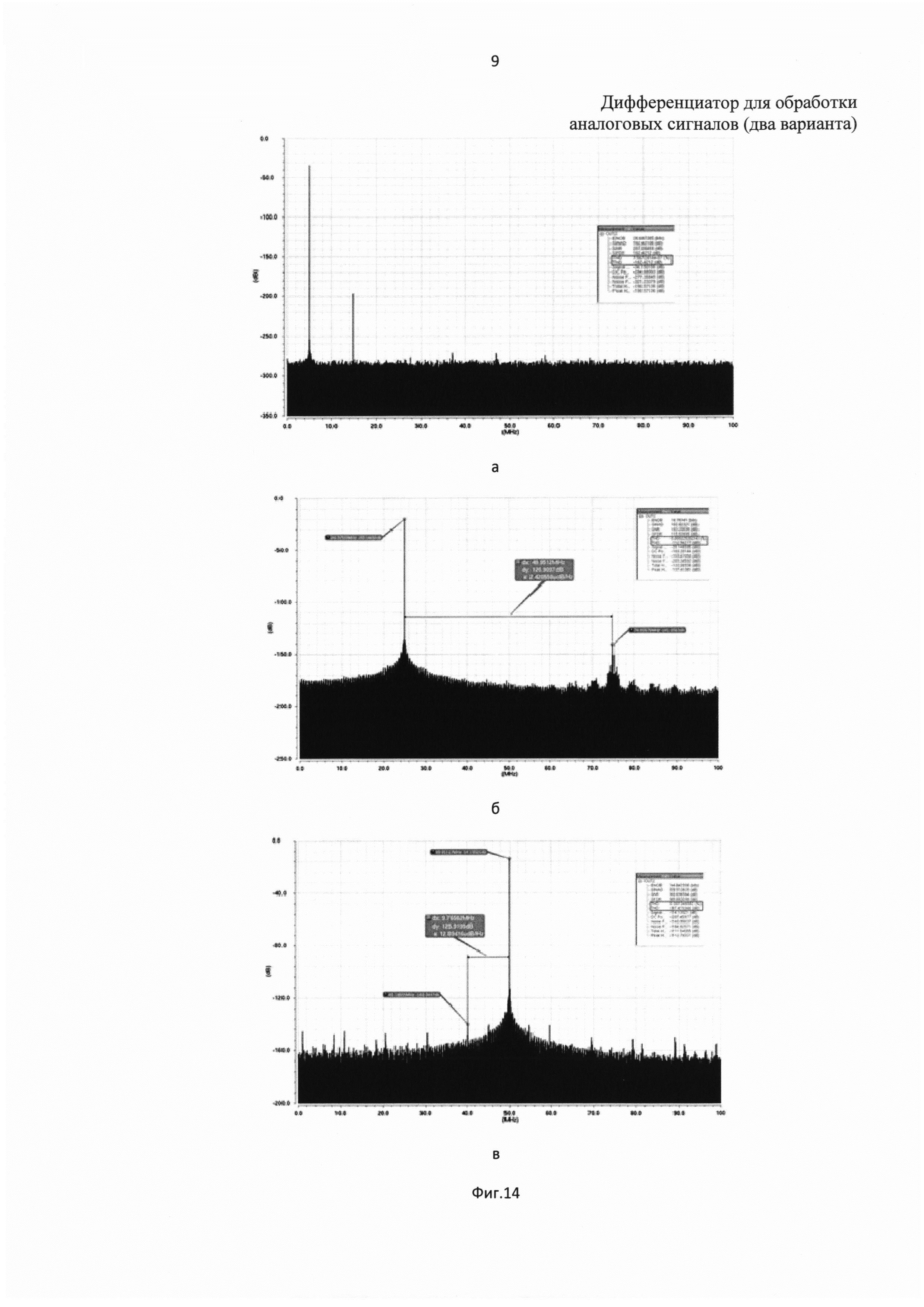

На фиг. 14а - спектр выходного сигнала патентуемого дифференциатора для частоты 5 МГц.

На фиг. 14б - спектр выходного сигнала патентуемого дифференциатора для частоты 25 МГц.

На фиг. 14в - спектр выходного сигнала патентуемого дифференциатора для частоты 50 МГц.

Указанный технический результат обеспечивается дифференциатором для обработки аналоговых сигналов (по первому варианту), приведенным на фиг. 6. Патентуемый дифференциатор для обработки аналоговых сигналов содержит дифференцирующий конденсатор 1, основной усилитель передачи сигнала 2, вспомогательный усилитель 3, при этом первая из обкладок 4 дифференцирующего конденсатора 1 подключена к входу дифференциатора 5, а вторая обкладка 6 соединена с инвертирующим входом 7 вспомогательного усилителя 3 и входом 8 основного усилителя передачи сигнала 2, выход 9 которого соединен с выходом 10 дифференциатора. Вспомогательный усилитель 3, у которого положительный вход 11 подключен к источнику опорного напряжения, имеет коэффициент усиления больше 1, а основной усилитель передачи сигнала 2 содержит транзистор 12, включенный по схеме с общим затвором, источник тока 13, резистор нагрузки 14. Положительный электрод 15 источника тока 13 соединен с инвертирующим входом 7 вспомогательного усилителя 3, второй обкладкой 6 дифференцирующего конденсатора 1 и истоком 16 транзистора 12, сток 17 которого соединен с резистором нагрузки 14, второй электрод которого подключен к шине питания, а отрицательный электрод источника тока 13 соединен с шиной земли. Выход 18 вспомогательного усилителя 3 соединен с затвором 19 транзистора 12 основного усилителя передачи сигнала 2.

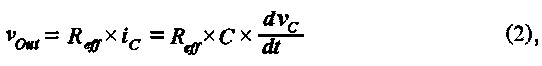

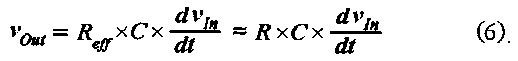

Патентуемый дифференциатор по первому варианту работает следующим образом. Входное напряжение поступает через вход дифференциатора 5 на дифференцирующий конденсатор 1 и формирует протекающий через него сигнальный ток iC, равный

где С - значение емкости дифференцирующего конденсатора, a vC - напряжение на нем. Если входное сопротивление вспомогательного усилителя 3 и выходное сопротивление источника тока 15 имеют достаточно высокие значения, то практически весь сигнальный ток течет через транзистор 12 в резистор нагрузки 14, создавая выходное напряжение

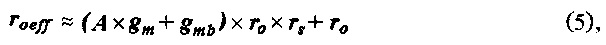

где значение  определяется нагрузочным резистором и параллельно ему подключенным эффективным выходным сопротивлением стока

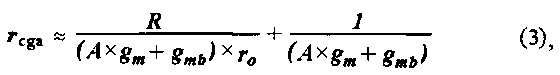

определяется нагрузочным резистором и параллельно ему подключенным эффективным выходным сопротивлением стока  транзистора 12. За счет действия вспомогательного усилителя 3 с предпочтительным коэффициентом усиления много больше единицы, A>>1, во-первых, обеспечивается режим разнополярной направленности изменения напряжений на истоке и затворе (т.е. push-pull operation, или двухтактный режим работы) включенного по схеме с общим затвором транзистора 12, что повышает его эффективную крутизну в (A+1) раз, а во-вторых, в узле «N» обеспечивается потенциал, привязанный к потенциалу опорного напряжения на терминале «VREF». В этом случае напряжение VN≈VREF=const, другими словами, малосигнальное сопротивление этого узла имеет низкое значение. Оно определяется сопротивлением со стороны истока транзистора 12, количественное значение которого, как следует из [8] и [9], находится с помощью выражения

транзистора 12. За счет действия вспомогательного усилителя 3 с предпочтительным коэффициентом усиления много больше единицы, A>>1, во-первых, обеспечивается режим разнополярной направленности изменения напряжений на истоке и затворе (т.е. push-pull operation, или двухтактный режим работы) включенного по схеме с общим затвором транзистора 12, что повышает его эффективную крутизну в (A+1) раз, а во-вторых, в узле «N» обеспечивается потенциал, привязанный к потенциалу опорного напряжения на терминале «VREF». В этом случае напряжение VN≈VREF=const, другими словами, малосигнальное сопротивление этого узла имеет низкое значение. Оно определяется сопротивлением со стороны истока транзистора 12, количественное значение которого, как следует из [8] и [9], находится с помощью выражения

где R - сопротивление резистора нагрузки 14,

gm – крутизна транзистора 12,

gmb - крутизна транзистора 12 по «обратному» затвору,

ro - малосигнальное выходное сопротивление транзистора 12.

Из этого следует, что при достаточно большом значении коэффициента A вспомогательного усилителя сопротивление rcga стремится к нулю. Например, в схеме дифференциатора с напряжением питания 3,3 В, реализованного в рамках технологического процесса КМОП-0,35 мкм, транзистор 12 с размерами W/L=20 мкм/0,35 мкм при сопротивлении резистора нагрузки 1,2 кОм и рабочем токе, равном 1,435 мА, имеет следующие параметры:

gm≈8,7 мА/В, gmb≈24,6 мА/В, ro≈5,3 кОм, поэтому при коэффициенте усиления вспомогательного усилителя A=100 получаем rcga≈1,33 Ом, а при A=1000 rcga≈0,136 Ом.

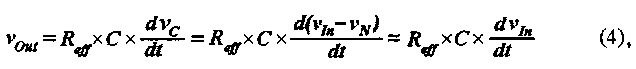

Из этого, в свою очередь, следует, что малосигнальное напряжение в узле «N» при достаточно большом значении коэффициента A практически равно 0, поэтому выражение (2) можно переписать следующим образом:

Далее, из [8] и [9] следует, что значение эффективного сопротивления стока равно

где rs - малосигнальное сопротивление реального источника тока.

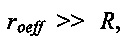

Поскольку обычно  то нагрузка определяется значением резистора нагрузки, поэтому окончательно получаем, что

то нагрузка определяется значением резистора нагрузки, поэтому окончательно получаем, что

Из полученного выражения следует, что линейность заявляемого дифференциатора определяется преимущественно линейностью параметров резистора и конденсатора.

Высокая линейность заявляемого дифференциатора подтверждается линейной АЧХ в широкой полосе частот на фиг. 7 и значениями параметра THD на фиг. 8а-8в, (для частоты 50 МГц THD=0,002%, или -93,5 дБ).

Кроме того, патентуемое устройство обеспечивает высокую точность, которая обусловлена снижением влияния паразитных емкостей на низкоимпедансном входе регулируемого каскода вследствие действия усилителя 3, который обеспечивает квазипостоянный потенциал на истоке транзистора 12 за счет его привязки к потенциалу опорного напряжения на терминале VREF. Кроме того, поскольку выражение (6) содержит только операцию умножения, то вследствие перемножения погрешностей элементов R1 и C1 их влияние на результат также уменьшается.

Быстродействие заявляемого устройства определяется высокими динамическими характеристиками однотранзисторного усилительного каскада на транзисторе 12, включенного по схеме с общим затвором. Это подтверждается на фиг. 9 низким значением задержки сигнала, равной ≈ 270 пс, которое сопоставимо с задержкой устройства-прототипа (193 пс, фиг. 4).

В качестве примера заявляемого устройства приведен вариант его реализации с использованием транзистора N-типа в основном усилителе передачи сигнала, но можно аналогичным образом построить вариант дифференциатора на основе транзистора Р-типа в основном усилителе передачи сигнала. Кроме того, заявляемое устройство может быть реализовано и в дискретном исполнении, и в составе интегральной схемы.

Прототип дифференциатора в полностью дифференциальном исполнении приведен на фиг. 1а (см. [2]) и реализован на основе дифференциального усилителя с конденсатором между истоками транзисторной пары.

Недостатком известного устройства является невысокое быстродействие, что подтверждается временной диаграммой на фиг. 10 (задержка ≈ 2,5 нс), и зависимость линейности этого устройства от частоты, что подтверждается графиками спектров выходных сигналов для трех частот (5 МГц, 25 МГц и 50 МГц) на фиг. 11а÷11в. Значения коэффициентов нелинейных искажений равны соответственно 0,32%, 0,096% и 0,04%.

Техническим результатом патентуемого дифференциатора в полностью дифференциальном исполнении является повышение линейности и быстродействия.

Указанный технический результат обеспечивается дифференциатором для обработки аналоговых сигналов (по второму варианту), содержащим два идентичных усилителя для прямого и инверсного сигналов, каждый из которых содержит усилительный транзистор, резистор нагрузки, источник тока, выполненный на основе транзисторной схемы, положительный электрод которого соединен с истоком усилительного транзистора, а отрицательный электрод подключен к шине земли, при этом сток усилительного транзистора и первый электрод резистора нагрузки одного усилителя подключены к инвертирующему выходу дифференциатора, сток усилительного транзистора и первый электрод резистора нагрузки другого усилителя подключены к неинвертирующему выходу дифференциатора, вторые электроды резисторов нагрузки обоих усилителей подключены к шине питания, в отличии от прототипа в дифференциатор введен второй дифференцирующий конденсатор и полностью дифференциальный усилитель, имеющий коэффициент усиления больше 1 и встроенную схему стабилизации синфазного выходного напряжения, величина которого определяется внешним опорным напряжением, которое подается на специальный вход дифференциального усилителя, при этом первая из обкладок первого дифференцирующего конденсатора подключена к неинвертирующему входу дифференциатора, вторая обкладка первого дифференцирующего конденсатора соединена с инвертирующим входом вспомогательного усилителя и с истоком первого усилительного транзистора, неинвертирующий выход вспомогательного усилителя соединен с затвором первого усилительного транзистора, первая из обкладок второго дифференцирующего конденсатора подключена к инвертирующему входу дифференциатора, вторая обкладка второго дифференцирующего конденсатора соединена с неинвертирующим входом вспомогательного усилителя и с истоком второго усилительного транзистора, инвертирующий выход вспомогательного усилителя соединен с затвором второго усилительного транзистора, вход установки уровня выходного синфазного напряжения вспомогательного усилителя соединен с входом дифференциатора, на который подается опорное напряжение, сток первого усилительного транзистора соединен с неинвертирующим выходом дифференциатора, сток второго усилительного транзистора соединен с инвертирующим выходом дифференциатора.

Таким образом, патентуемый дифференциатор для обработки аналоговых сигналов (по второму варианту) выполнен на основе двух активных каскодов, регулируемых одним полностью дифференциальным усилителем с коэффициентом усиления больше 1, предпочтительно, много больше единицы, А>>1, и с внутренней схемой стабилизации синфазного выходного напряжения, величина которого определяется внешним напряжением Vcmfb.

Патентуемый дифференциатор для обработки аналоговых сигналов, электрическая принципиальная схема которого приведена на фиг. 12, содержит два идентичных дифференцирующих конденсатора 1 и 20, два идентичных основных усилителя 2 и 21 передачи прямого и инверсного сигналов соответственно, вспомогательный усилитель 3 с предпочтительным коэффициентом усиления много большим 1, при этом основной усилитель 2 состоит из усилительного транзистора 12, резистора нагрузки 14, источника тока 13, а основной усилитель 21 состоит из усилительного транзистора 22, резистора нагрузки 23, источника тока 24. Первая обкладка 4 дифференцирующего конденсатора 1 подключена к положительному входу дифференциатора 5, первая обкладка 25 дифференцирующего конденсатора 20 подключена к отрицательному входу дифференциатора 26, вторая обкладка 6 дифференцирующего конденсатора 1 соединена с инвертирующим входом 7 вспомогательного усилителя 3 и входом 8 основного усилителя передачи прямого сигнала 2, выход 9 которого соединен с положительным выходом 10 дифференциатора, а вторая обкладка 27 дифференцирующего конденсатора 20 соединена с положительным входом 11 вспомогательного усилителя 3 и входом 28 основного усилителя передачи инверсного сигнала 21. Вход 29 задания уровня синфазного выходного напряжения вспомогательного усилителя 3 подключен к входу подачи постоянного напряжения 30 дифференциатора, неинвертирующий выход 18 вспомогательного усилителя 3 соединен с затвором 19 усилительного транзистора 12 основного усилителя 2 передачи прямого сигнала, инвертирующий выход 31 вспомогательного усилителя 3 соединен с затвором 32 усилительного транзистора 22 основного усилителя 21 передачи инверсного сигнала. Исток 16 усилительного транзистора 12 соединен с положительным электродом 15 источника тока 13, второй обкладкой 6 дифференцирующего конденсатора 1, инвертирующим входом 7 вспомогательного усилителя 3 и входом 8 основного усилителя передачи прямого сигнала 2, сток 17 усилительного транзистора 12 соединен с первым электродом резистора нагрузки 14, выходом 9 основного усилителя 2 и прямым выходом 10 дифференциатора. Исток 33 усилительного транзистора 22 соединен с положительным электродом 34 источника тока 24, второй обкладкой 27 дифференцирующего конденсатора 20, неинвертирующим входом 11 вспомогательного усилителя 3 и входом 28 основного усилителя передачи инверсного сигнала 21, сток 35 усилительного транзистора 22 соединен с первым электродом резистора нагрузки 23, выходом 36 основного усилителя 21 и инверсным выходом 37 дифференциатора. Вторые электроды резисторов нагрузки 14 и 23 подключены к шине питания, а отрицательные электроды источников тока 13 и 24 подключены к шине земли.

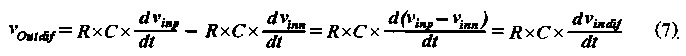

Патентуемый дифференциатор по второму варианту работает следующим образом. Прямой и инверсный входные сигналы, разность между которыми формирует входное дифференциальное напряжение, поступают соответственно через входы дифференциатора 5 и 26 на конденсаторы 1 и 20. Далее прямой сигнал поступает на исток усилительного транзистора 12 основного усилителя 2, который управляется неинвертирующим выходом 18 вспомогательного усилителя 3, а инверсный сигнал - на исток усилительного транзистора основного усилителя 21, который управляется инвертирующим выходом 31 вспомогательного усилителя 3. Функционирование каждого сигнального тракта по отдельности в этой схеме аналогично работе схемы в однофазном варианте, описанном выше и представленном на фиг. 6. Отличие заключается лишь в том, что вспомогательный усилитель 3 стремится свести к нулю разность напряжений на своих входах 7 и 11, другими словами, он формирует равные по величине квазипостоянные напряжения на истоках 16 и 33 усилительных транзисторов 12 и 22 соответственно. Как и в случае описанного ранее однофазного варианта, входы 8 основного усилителя 2 и 28 основного усилителя 21 являются низкоомными, поэтому для каждого сигнального тракта по отдельности применимы формулы (1)÷(6). Выражение для выходного напряжения в рассматриваемом варианте получается следующим образом:

Стабилизированное выходное синфазное напряжение вспомогательного усилителя позволяет установить рабочие точки транзисторов 12 и 22, задавая напряжение на их затворах. Улучшение параметров по сравнению с прототипом подтверждается расчетами, приведенными на фиг. 13 и фиг. 14а-фиг. 14в. Как видно из временной диаграммы на фиг. 13, величина задержки сигнала этой схемы равна 238 пс, а значение параметра THD для частоты 50 МГц, как видно из фиг. 14в, снизилось до 0,001% вследствие пропадания в спектре четных гармоник.

В качестве примера заявляемого устройства приведен вариант его реализации с использованием транзисторов N-типа в усилителях передачи прямого и инверсного сигналов, но можно аналогичным образом построить вариант дифференциатора на основе транзисторов Р-типа.

Источники информации

[1] И.В. Волков, С.В. Румянцев, Ю.М. Фокин. «Многоразрядный быстродействующий аналого-цифровой преобразователь, использующий метод предсказания». МИКРОЭЛЕКТРОНИКА, 2011, том 40, №5, с. 370-380.

[2] Satoshi Matsubara, Hideki Ishida, Kohtaroh Gotoh. «Ultra-High-Speed CMOS Interface Technology». Fujitsu Scientific & Technical Journal (FSTJ) April 2006 (Vol. 42, №2), p. 200-205.

[3] Патент США US 8995520 B2. Analog continuous-time phase equalizer for data transmission. Yasuo Hidaka, кл. H04L, 2015 г.

[4] Srikanth Gondi, Behzad Razavi. «Equalization and Clock and Data Recovery Techniques for 10-Gb/s CMOS Serial-Link Receivers». IEEE JOURNAL OF SOLID-STATE CIRCUITS, vol. 42, №9, Sept. 2007, p. 1999-2011.

[5] C. Aldea, S. Celma and A. Otin. Low-Voltage Differentiator for VHF Filtering. Analog Integrated Circuits and Signal Processing, 33, 107-116, 2002.

[6] Alan A. Stocker. Compact Integrated Transconductance Amplifier Circuit for Temporal Differentiation. ISCAS 2003, Bangkok Thailand, 25-28 May 2003, vol. 1, p. 201-204.

[7] Alireza Moini at al. «An Insect Vision-Based Motion Detection Chip». IEEE JOURNAL OF SOLID-STATE CIRCUITS, Vol. 32, №2, Febr. 1997 p. 279-284.

[8] Behzad Razavi. Design of Analog CMOS Integrated Circuits. New York, 2001, The McGraw-Hill Companies, Inc.

[9] Yun Chiu. On the Operation of CMOS Active-Cascode Gain Stage. Journal of Computer and Communications, 2013, Jan., p. 18-24.