Результат интеллектуальной деятельности: ПОДЛОЖКА МАТРИЦЫ И ПАНЕЛЬ ДИСПЛЕЯ

Вид РИД

Изобретение

ПРЕДПОСЫЛКИ ДЛЯ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

1. ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее раскрытие относится к технологии изготовления жидкокристаллических дисплеев и, более конкретно, к подложке матрицы и панели дисплея.

2. ОПИСАНИЕ УРОВНЯ ТЕХНИКИ

[0002] Жидкокристаллические панели дисплея включают подложку матрицы, подложку фильтрации цвета напротив подложки матрицы и слой жидкого кристалла между ними. Подложка фильтрации цвета включает тонкую пленку из оксида индия и олова (ITO). Подложка матрицы включает пиксели для отображения изображений. Пиксель включает слой пленки ITO для электрического соединения с соответствующим металлическим слоем через сквозное отверстие.

[0003] Вышеупомянутые слои из пленки ITO при взаимодействии создают электрическое поле. Сквозное отверстие может приводить к возникновению бокового электрического поля по краям сквозного отверстия. Боковое электрическое поле возбуждает жидкий кристалл на боковых сторонах, чтобы перекрываться с жидким кристаллом в центральном положении для формирования линий дисклинации.

[0004] Линии дисклинации могут снижать скорость передачи панели дисплея, этим повышая стоимость. При очень большом размере линий дисклинации может иметь место эффект, обусловленный законом Мура.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0005] Цель изобретения заключается в том, чтобы предложить подложку матрицы и панель дисплея для того, чтобы избежать линии дисклинации для улучшения эксплуатационных характеристик дисплея.

[0006] В одном аспекте подложка матрицы включает: по меньшей мере одну линию данных, по меньшей мере одну линию сканирования и пиксель, определяемый этими линией данных и линией сканирования, при этом пиксель включает тонкую пленку ITO и по меньшей мере один металлический слой ниже тонкой пленки ITO, при этом тонкая пленка ITO электрически соединяется с металлическим слоем через сквозное отверстие и тонкая пленка ITO включает прорезь, расположенную между тонкой пленкой ITO и сквозным отверстием, и прорезь расположена так, чтобы избежать линий дисклинации; длина и ширина прорези больше чем 2,5 мкм; и пиксель включает тонкопленочный транзистор, расположенный в стыке линии данных и линии сканирования, и пассивирующий слой, расположенный между тонкой пленкой ITO и металлическим слоем, металлический слой включает металлический слой истока и металлический слой стока тонкопленочного транзистора, сквозное отверстие проходит через пассивирующий слой, чтобы обнажить металлический слой истока или стока, и тонкая пленка ITO расположена выше металлического слоя истока или стока тонкопленочного транзистора через сквозное отверстие.

[0007] При этом прорезь расположена соответственно краю металлического слоя истока или стока, и прорезь проходит в направлении дальше от сквозного отверстия.

[0008] В еще одном аспекте подложка матрицы включает: по меньшей мере одну линию данных, по меньшей мере одну линию сканирования и пиксель, определяемый этими линией данных и линией сканирования, пиксель включает тонкую пленку ITO и по меньшей мере один металлический слой ниже тонкой пленки ITO, тонкая пленка ITO электрически соединяется с металлическим слоем через сквозное отверстие и тонкая пленка ITO включает прорезь, расположенную между тонкой пленкой ITO и сквозным отверстием, и прорезь расположена так, чтобы избежать линий дисклинации.

[0009] При этом длина и ширина прорези больше чем 2,5 мкм.

[0010] При этом пиксель включает тонкопленочный транзистор, расположенный в стыке линии данных и линии сканирования, и пассивирующий слой, расположенный между тонкой пленкой ITO и металлическим слоем, металлический слой включает металлический слой истока и металлический слой стока тонкопленочного транзистора, сквозное отверстие проходит через пассивирующий слой, чтобы обнажить металлический слой истока или стока, и тонкая пленка ITO расположена выше металлического слоя истока или стока тонкопленочного транзистора через сквозное отверстие.

[0011] При этом прорезь расположена соответственно краю металлического слоя истока или стока, и прорезь проходит в направлении дальше от сквозного отверстия.

[0012] При этом пиксель, кроме того, включает пассивирующий слой и изолирующий слой между тонкой пленкой ITO и металлическим слоем, металлический слой включает металлический слой общего электрода, сквозное отверстие проходит через изолирующий слой и пассивирующий слой, чтобы обнажить металлический слой общего электрода, и тонкая пленка ITO расположена выше металлического слоя общего электрода через сквозное отверстие.

[0013] При этом прорезь расположена соответственно краю металлического слоя общего электрода, и прорезь проходит в направлении дальше от сквозного отверстия.

[0014] В еще одном аспекте панель дисплея включает: подложку фильтрации цвета и подложку матрицы напротив подложки фильтрации цвета, подложка матрицы включает по меньшей мере одну линию данных, по меньшей мере одну линию сканирования и пиксель, определяемый этими линией данных и линией сканирования, пиксель включает тонкую пленку ITO и по меньшей мере один металлический слой ниже тонкой пленки ITO, тонкая пленка ITO электрически соединяется с металлическим слоем через сквозное отверстие, тонкая пленка ITO включает прорезь, расположенную между тонкой пленкой ITO и сквозным отверстием, и прорезь расположена так, чтобы избежать линий дисклинации.

[0015] При этом длина и ширина прорези больше чем 2,5 мкм.

[0016] При этом пиксель включает тонкопленочный транзистор, расположенный в стыке линии данных и линии сканирования, и пассивирующий слой, расположенный между тонкой пленкой ITO и металлическим слоем, металлический слой включает металлический слой истока и металлический слой стока тонкопленочного транзистора, сквозное отверстие проходит через пассивирующий слой, чтобы обнажить металлический слой истока или стока, и тонкая пленка ITO расположена выше металлического слоя истока или стока тонкопленочного транзистора через сквозное отверстие.

[0017] При этом прорезь расположена соответственно краю металлического слоя истока или стока и проходит в направлении дальше от сквозного отверстия.

[0018] При этом пиксель, кроме того, включает пассивирующий слой и изолирующий слой между тонкой пленкой ITO и металлическим слоем, металлический слой включает металлический слой общего электрода, сквозное отверстие проходит через изолирующий слой и пассивирующий слой, чтобы обнажить металлический слой общего электрода, и тонкая пленка ITO расположена выше металлического слоя общего электрода через сквозное отверстие.

[0019] При этом прорезь расположена соответственно краю металлического слоя общего электрода и проходит в направлении дальше от сквозного отверстия.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

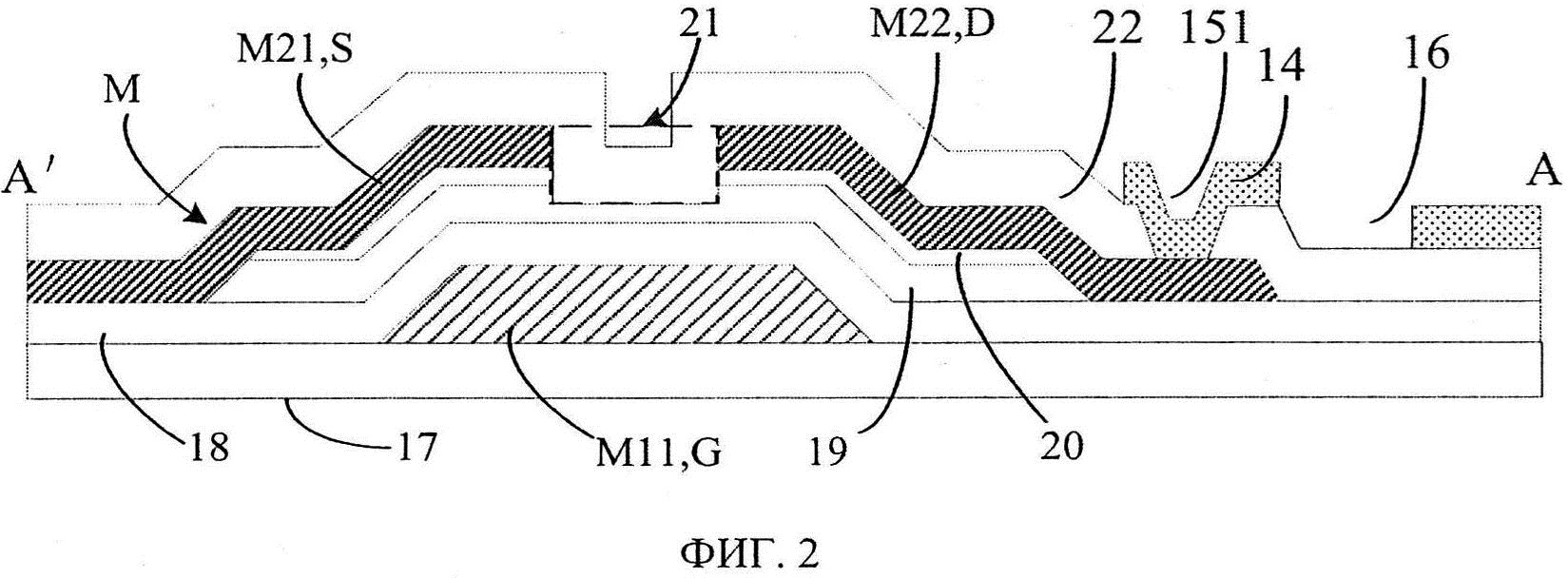

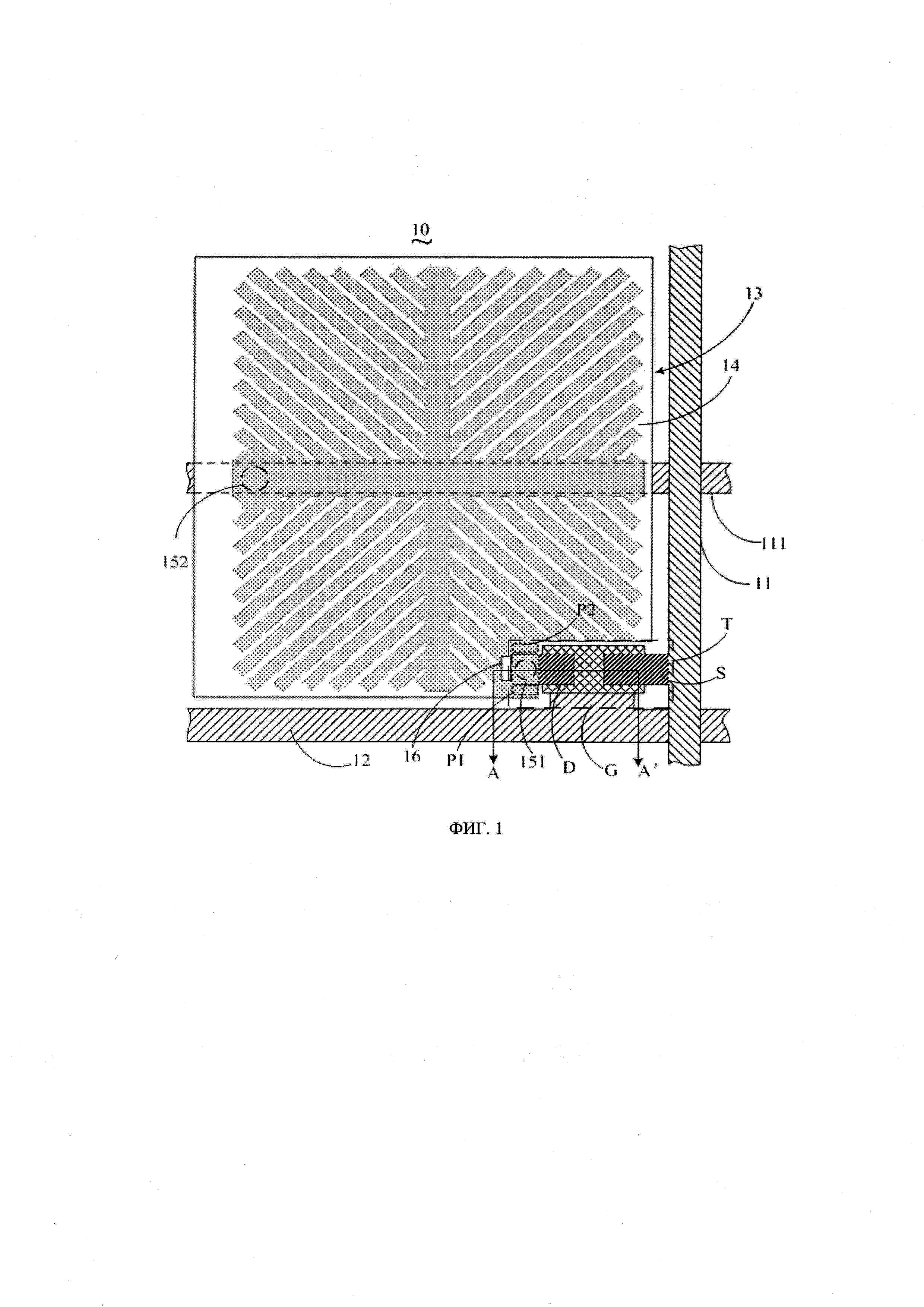

[0020] Фиг. 1 - схематический вид подложки матрицы в соответствии с первым вариантом осуществления.

[0021] Фиг. 2 - вид в поперечном разрезе подложки матрицы с Фиг. 1 по линии А-А'.

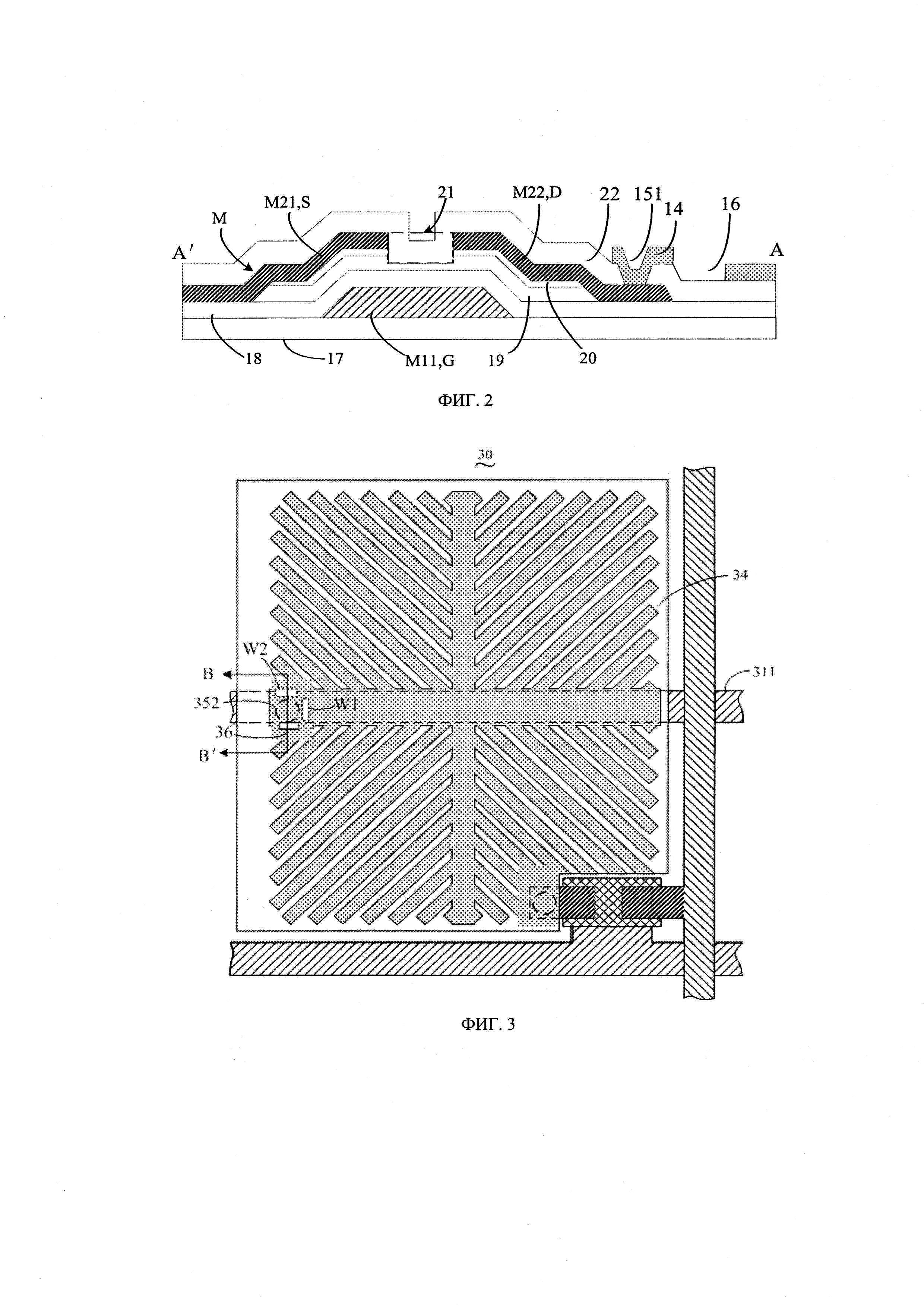

[0022] Фиг. 3 - схематический вид подложки матрицы в соответствии с вторым вариантом осуществления.

[0023] Фиг. 4 - вид в поперечном разрезе подложки матрицы с Фиг. 3 по линии В-В'.

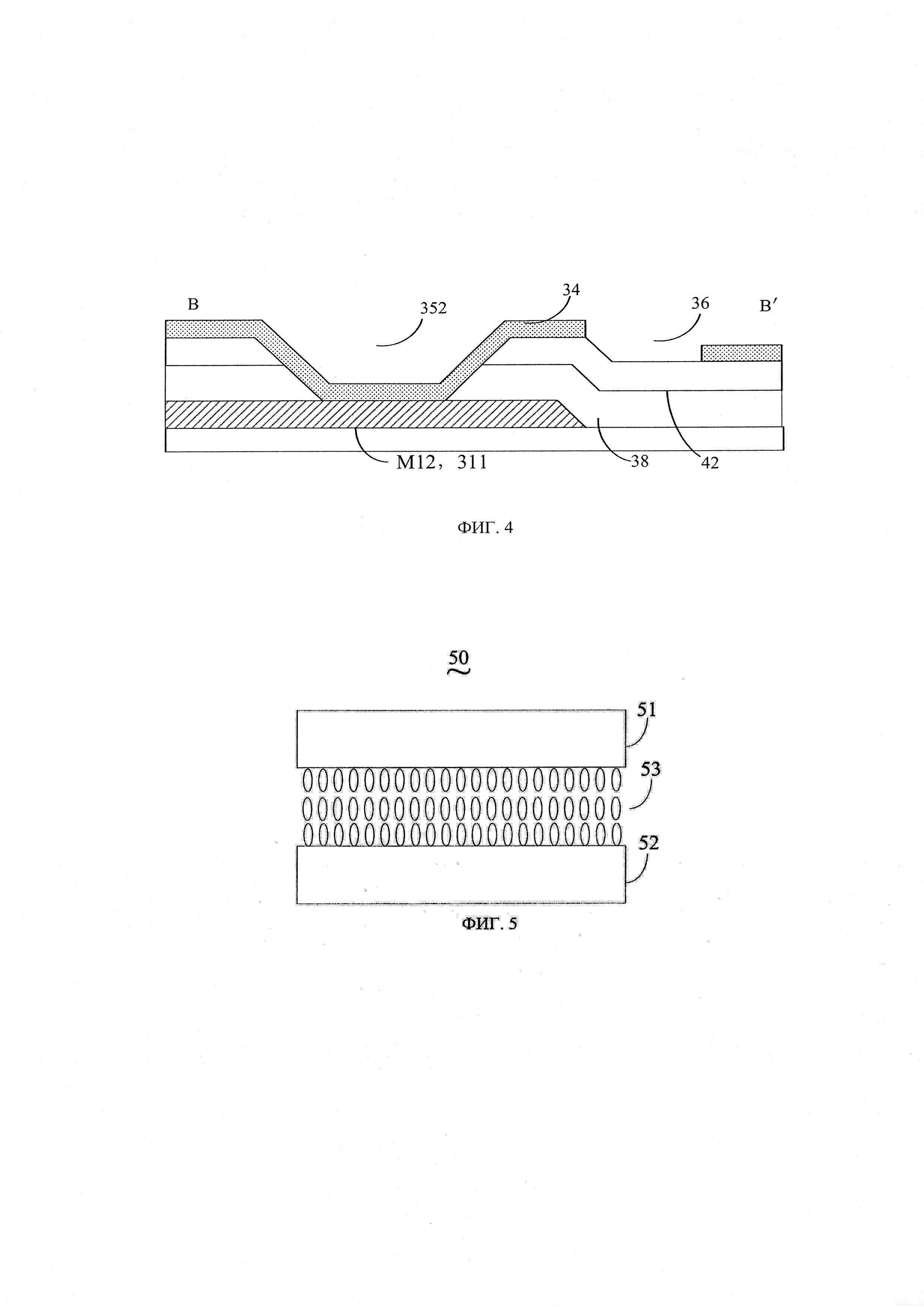

[0024] Фиг. 5 - схематический вид панели дисплея в соответствии с одним вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0025] Варианты осуществления изобретения теперь будут описаны более подробно со ссылками на прилагаемые чертежи, на которых показаны эти варианты осуществления изобретения.

[0026] На Фиг. 1 показан схематический вид подложки матрицы в соответствии с первым вариантом осуществления. На Фиг. 2 показан вид в поперечном разрезе подложки матрицы с Фиг. 1 по линии А-А'. Со ссылкой на Фиг. 1 и 2, подложка матрицы 10 включает по меньшей мере одну линию данных 11, по меньшей мере одну линию сканирования 12 и пиксель 13, определяемый линией данных 11 и линией сканирования 12. Пиксель 13 включает тонкую пленку ITO 14 и по меньшей мере один металлический слой (М) ниже тонкой пленки ITO 14. Тонкая пленка ITO 14 электрически соединяется с металлическим слоем (М) через сквозное отверстие 151. Тонкая пленка ITO 14 включает прорезь 16, расположенную между тонкой пленкой ITO 14 и сквозным отверстием 151. Прорезь 16 расположена так, чтобы избежать возникновения линий дисклинации.

[0027] В одном варианте осуществления пиксель 13 включает транзистор (Т) и общий электрод 111 в стыке линии данных 11 и линии сканирования 12. Транзистор (Т) включает затвор (G), исток (S) и сток (D). Затвор (G) электрически соединяется с линией сканирования 12, исток (S) электрически соединяется с линией данных 11, и сток (D) электрически соединяется с тонкой пленкой ITO 14 через сквозное отверстие 151. Общий электрод 111 параллелен линии сканирования 12 и электрически соединяется с тонкой пленкой ITO 14 через сквозное отверстие 151.

[0028] В одном варианте осуществления металлический слой (М) включает металлический слой затвора (М11), металлический слой истока (М21) и металлический слой стока (М22). Затвор (G) сформирован металлическим слоем затвора (М11), расположенным на стеклянной подложке 17 подложки матрицы 10. Изолирующий слой затвора 18 выполнен на затворе (G) для изоляции затвора (G), истока (S) и стока (D). Полупроводниковый слой 19 и легированный полупроводниковый слой 20 выполнены на изолирующем слое затвора 18. Паз 21 расположен на полупроводниковом слое 19 и легированном полупроводниковом слое 20. Паз 21 проходит через легированный полупроводниковый слой 20 и часть полупроводникового слоя 19. Исток (S) сформирован металлическим слоем истока (М21). Сток (D) сформирован металлическим слоем стока (М22). Металлический слой истока (М21) и металлический слой стока (М22) расположены соответственно на двух боковых сторонах паза 21. Помимо этого металлический слой истока (М21) и металлический слой стока (М22) расположены выше легированного полупроводникового слоя 20. Полупроводниковый слой 19 и легированный полупроводниковый слой 20 предназначены для функционирования в качестве транзисторов. Более конкретно, когда на затвор (G) поступают сигналы включения с линии сканирования 12 для включения транзистора (Т), исток (S) и сток (D) соединяются полупроводниковым слоем 19 и легированным полупроводниковым слоем 20, так что сигналы с линии данных 11 передаются с истока (S) на сток (D). Перед приемом сигналов с линии сканирования 12 или после получения сигналов отключения с линии сканирования 12 для отключения транзистора (Т) полупроводниковый слой 19 и легированный полупроводниковый слой 20 разъединяют исток (S) и сток (D). Пассивирующий слой 22 закрывает металлический слой истока (М21) и металлический слой стока (М22). Сквозное отверстие 151 расположено на пассивирующем слое 22 соответственно местам металлического слоя стока (М22). Помимо этого сквозное отверстие 151 проходит через пассивирующий слой 22, так что металлический слой стока (М22) транзистора (Т) обнажен. Тонкая пленка ITO 14 расположена выше пассивирующего слоя 22 и электрически соединяется с металлическим слоем стока (М22) через сквозное отверстие 151.

[0029] В этом варианте осуществления прорезь 16 расположена соответственно краю металлического слоя стока (М22) транзистора (Т). Предпочтительно длина и ширина прорези 16 больше чем 2,5 микрон (мкм). Прорезь 16 проходит в направлении дальше от сквозного отверстия 151. Например, прорезь 16 расположена в месте, обозначенном "Р1" и "Р2" на Фиг. 1. В других вариантах осуществления прорезь 16 может иметь форму кольца, окружающего сквозное отверстие 151. Место и форма прорези 16 не ограничены вышеуказанными. Следует сказать, что, даже если прорезь 16 расположена между тонкой пленкой ITO 14 и сквозным отверстием 151, тонкая пленка ITO 14 и сквозное отверстие 151 остаются соединенными.

[0030] В этом варианте осуществления металлический слой истока (М21) и металлический слой стока (М22) выполнены из одинаковых металлических материалов.

[0031] В других вариантах осуществления сквозное отверстие 151 расположено на пассивирующем слое 22 соответственно местам металлического слоя истока (М21). То есть, тонкая пленка ITO 14 электрически соединяется с металлическим слоем истока (М21) через сквозное отверстие 151. В этот момент прорезь 16 расположена соответственно краю металлического слоя истока (М21) и проходит в направлении дальше от сквозного отверстия 151.

[0032] Путем расположения прорези 16 между тонкой пленкой ITO 14 и сквозным отверстием 151 на двух боковых сторонах прорези 16 создаются соответствующие электрические поля. Таким образом, боковое электрическое поле через сквозное отверстие 151 ослаблено, чтобы уменьшить возможность возникновения линий дисклинации.

[0033] На Фиг. 3 показан схематический вид подложки матрицы в соответствии с вторым вариантом осуществления. Как показано на Фиг. 3, прорезь 36 расположена между тонкой пленкой ITO 34 и сквозным отверстием 352. На Фиг. 4 показан вид в поперечном разрезе подложки матрицы с Фиг. 3 по линии В-В'. В этом варианте осуществления металлический слой включает металлический слой общего электрода (M12). Общий электрод 311 сформирован металлическим слоем общего электрода (M12). Металлический слой общего электрода (M12) и металлический слой затвора (М11) выполнены из одинакового металлического материала. Помимо этого металлический слой общего электрода (M12) и металлический слой затвора (М11) расположены на одном слое. Изолирующий слой 38 и пассивирующий слой 42 расположены над металлическим слоем общего электрода (M12) по очереди. Сквозное отверстие 352 проходит через изолирующий слой 38 и пассивирующий слой 42, и металлический слой общего электрода (M12) обнажается. Тонкая пленка ITO 34 электрически соединяется с металлическим слоем общего электрода (M12) через сквозное отверстие 352. Прорезь 36 расположена соответственно краю металлического слоя общего электрода (М12). Помимо этого прорезь 36 проходит в направлении дальше от сквозного отверстия 352. В других вариантах осуществления прорезь 36 может быть расположена в месте, обозначенном "W1" и "W2". Прорезь 36 может иметь форму кольца, окружающего сквозное отверстие 352. Место и форма прорези 36 не ограничены вышеуказанными. Следует сказать, что, даже если прорезь 36 расположена между тонкой пленкой ITO 14 и сквозным отверстием 352, тонкая пленка ITO 14 и сквозное отверстие 352 остаются соединенными.

[0034] Также при расположении прорези 36 между тонкой пленкой ITO 14 и сквозным отверстием 352 на двух боковых сторонах прорези 36 создаются соответствующие электрические поля. Таким образом, боковое электрическое поле через сквозное отверстие 352 ослаблено, чтобы уменьшить возможность возникновения линий дисклинации.

[0035] На Фиг. 5 показан схематический вид панели дисплея в соответствии с одним вариантом осуществления. Панель дисплея 50 включает подложку фильтрации цвета 51, описанную выше подложку матрицы 52 напротив подложки фильтрации цвета 51 и слой жидкого кристалла 53.

[0036] В связи с изложенным, тонкая пленка ITO на пикселе электрически соединяется с металлическим слоем через сквозное отверстие. Путем расположения прорези между тонкой пленкой ITO и сквозным отверстием на двух боковых сторонах прорези создаются соответствующие электрические поля. Таким образом, боковое электрическое поле через сквозное отверстие ослаблено, чтобы уменьшить возможность возникновения линий дисклинации.

[0037] Мы полагаем, что описанные выше варианты осуществления и их преимущества будут поняты из описания и что будет очевидно, что в них могут быть внесены разные изменения, но без нарушения сущности и объема изобретения или без ущерба для его материальных преимуществ, при этом приведенные выше примеры являются просто предпочтительными примерами вариантов осуществления изобретения.