ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, фиг. 1 в описании изобретения к патенту РФ 2282234, кл. G06F 7/57, 2006 г.), который содержит n логических модулей и реализует n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, относится сложное управление, обусловленное тем, что для настройки требуется подача соответствующей импульсной последовательности, а также низкие функциональные возможности.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (патент РФ 2324219, кл. G06F 7/57, 2008 г.), который содержит n логических модулей, каждый из которых содержит элемент И, элемент ИЛИ, замыкающий и размыкающий ключи, D-триггер.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, относится сложное управление, обусловленное тем, что для настройки требуется подача соответствующей импульсной последовательности, а также низкие функциональные возможности.

Техническим результатом изобретения является упрощение управления за счет обеспечения реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, с помощью настройки на реализацию требуемой симметрической функции путем подачи на настроечные входы соответствующего двоичного кода, а также расширение функциональных возможностей за счет формирования сигнала готовности результата, что позволяет использовать логический вычислитель как в синхронных, так и в асинхронных схемах.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем управляющий вход, выход, входы значений аргументов, элемент И, два D-триггера, элемент ИЛИ, n двухвходовых коммутаторов, каждый из которых имеет два входа, выход, управляющий вход, нормально замкнутый контакт, подключенный к первому входу коммутатора и выходу коммутатора, нормально разомкнутый контакт, подключенный ко второму входу коммутатора и выходу коммутатора, i-ый вход значений аргументов соединен с управляющим входом i-го коммутатора, i=l,…, n, особенность заключается в том, он дополнительно содержит второй выход, две группы элементов задержки по n элементов в каждой, формирователь фронта, настроечные входы, элемент НЕ, мультиплексор, формирователь спада, причем управляющий вход соединен с входом формирователя фронта, через первый элемент задержки первой группы с первым входом первого коммутатора, вторым входом первого коммутатора, входом первого элемента задержки второй группы, выход i-го коммутатора соединен со вторым входом i+1-го коммутатора и через i+1-ый элемент задержки первой группы соединен с первым входом i+1-го коммутатора, i=l…n-1, выход n-го коммутатора соединен с первым входом элемента И, выход формирователя фронта соединен с входами «Сброс» первого и второго D-триггеров, настроечные входы соединены с соответствующими адресными входами мультиплексора, выход мультиплексора соединен через элемент НЕ со вторым входом элемента И и входом формирователя спада, выход элемента И соединен с входами данных и записи первого D-триггера и первым входом элемента ИЛИ, выход первого D-триггера соединен с первым выходом устройства, выход второго D-триггера соединен со вторым выходом устройства, выход i-го элемента задержки второй группы соединен с входом i+1-го элемента задержки второй группы и i-ым информационным входом мультиплексора (i=l…n-l), выход n-го элемента задержки второй группы соединен с n-ым информационным входом мультиплексора, выход детектора спада соединен с вторым входом элемента ИЛИ, выход которого соединен с входами данных и записи второго триггера.

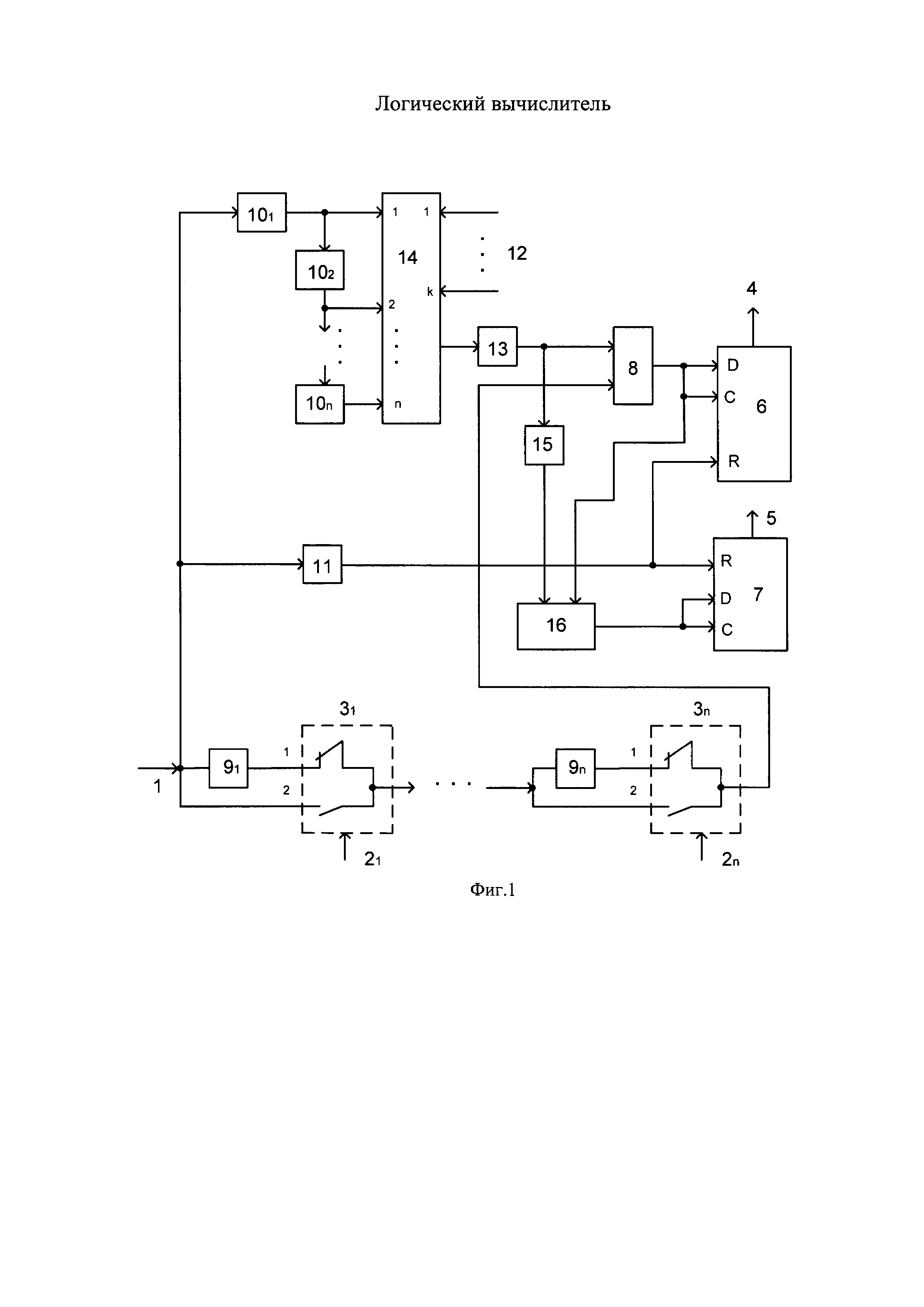

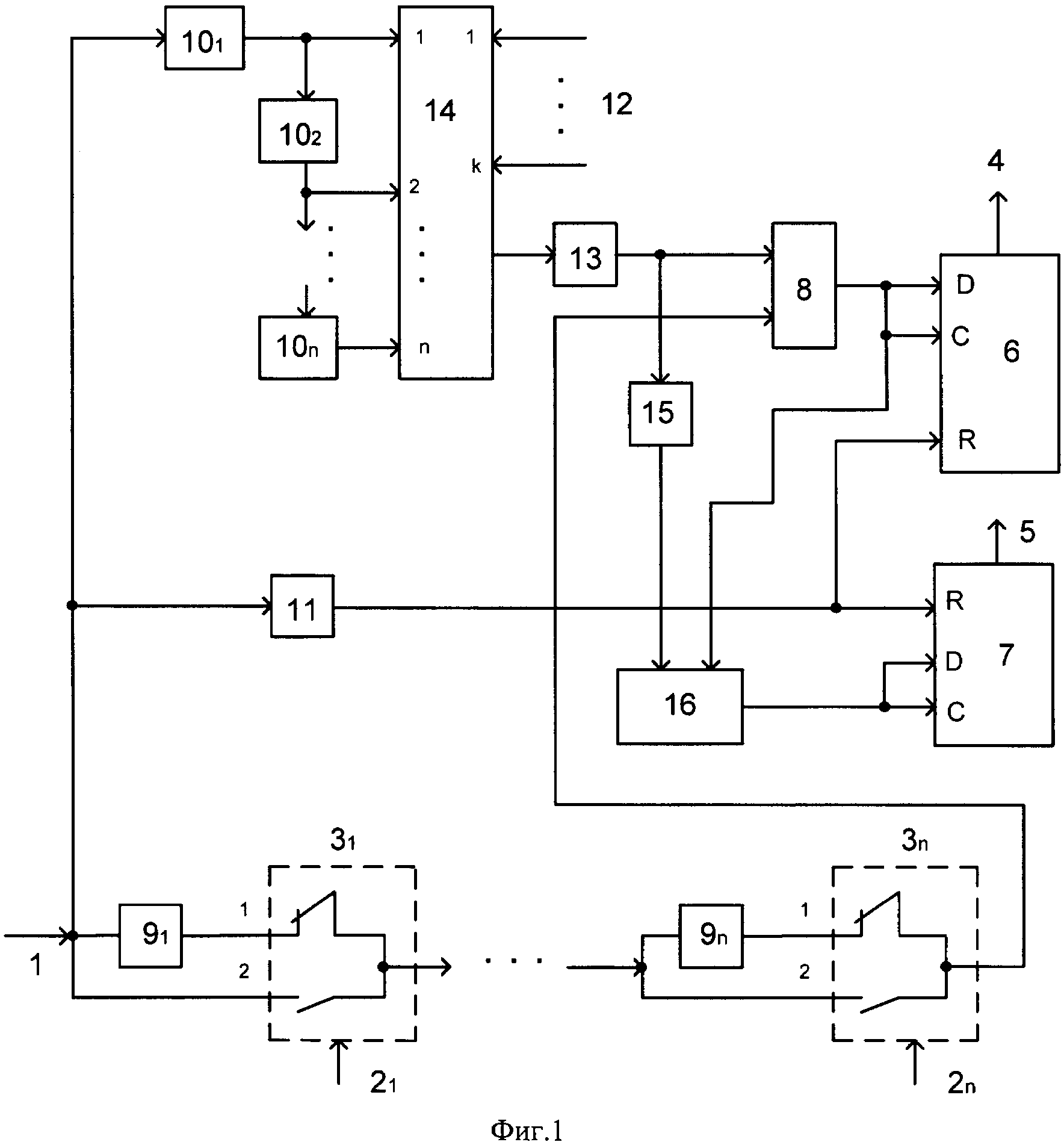

На чертеже представлена функциональная схема логического вычислителя.

Логический вычислитель, предназначенный для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержит управляющий вход 1, входы значений аргументов 2, n двухвходовых коммутаторов 31…3n, каждый из которых имеет два входа, выход, управляющий вход, нормально замкнутый контакт, подключенный к первому входу коммутатора и выходу коммутатора, нормально разомкнутый контакт, подключенный ко второму входу коммутатора и выходу коммутатора, i-ый вход значений аргументов 2i соединен с управляющим входом i-го коммутатора 3i, i=l,…,n, выходы 4 и 5, два D-триггера 6 и 7, элемент И 8, две группы элементов задержки по n элементов в каждой 91…9n, 101…10n, формирователь фронта 11, настроечные входы 12, элемент НЕ 13, мультиплексор 14, формирователь спада 15, элемент ИЛИ 16, управляющий вход 1 соединен с входом формирователя фронта 11, через первый элемент задержки первой группы 91 с первым входом первого коммутатора 31, вторым входом первого коммутатора 31, входом первого элемента задержки второй группы 101, выход i-го коммутатора 3i соединен со вторым входом i+1-го коммутатора 3i+1 и через i+1-ый элемент задержки первой группы 9i+1 с первым входом i+1-го коммутатора 3i+1, i=l...n-l, выход n-го коммутатора 3n соединен с первым входом элемента И 8, выход формирователя фронта 11 соединен с входами «Сброс» первого и второго D-триггеров 6 и 7, настроечные входы 12 соединены с соответствующими адресными входами мультиплексора 14, выход мультиплексора 14 соединен через элемент НЕ 13 со вторым входом элемента И 8 и входом формирователя спада 15, выход элемента И 8 соединен с входами данных и записи первого D-триггера 6 и первым входом элемента ИЛИ 16, выход первого D-триггера 6 соединен с первым выходом 4 устройства, выход второго D-триггера 7 соединен со вторым выходом 5 устройства, выход i-го элемента задержки второй группы 10i соединен с входом i+1-го элемента задержки второй группы 10i+1 и i-ым информационным входом мультиплексора 14 (i=l...n-l), выход n-го элемента задержки второй группы 10n соединен с n-ым информационным входом мультиплексора 14, выход детектора спада 15 соединен с вторым входом элемента ИЛИ 16, выход которого соединен с входами данных и записи второго триггера 7.

Работа логического вычислителя осуществляется следующим образом.

При описании работы введены следующие обозначения:

n - количество аргументов (переменных) в симметрической функции;

X={X1, Х2, …, Хn} - текущие значения аргументов, Xi∈{0,1}, i=l, …, n;

k - количество настроечных входов (поз. 12); k=]log2n[, где]…[означает ближайшее целое, не меньшее, чем выражение в скобках. Например, для n=4 значение k=2, а для n=5 значение k=3.

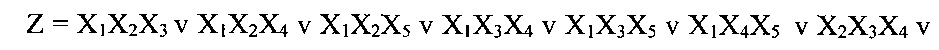

r - количество аргументов, входящих в конъюнкции в дизъюнктивной нормальной форме симметрической функции. Например, для симметричной булевой функции, для n=5

, значение r=3.

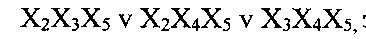

, значение r=3.

Тз - время задержки в элементах задержки 91-9n и 102-10n..

Тк - время задержки в коммутаторах 3

Тмпл - время задержки в мультиплексоре 14,

Тне - время задержки в элементе НЕ 13,

То - время задержки элемента задержки 101,

Тз>То≥nТк+Тмпл+Тне.

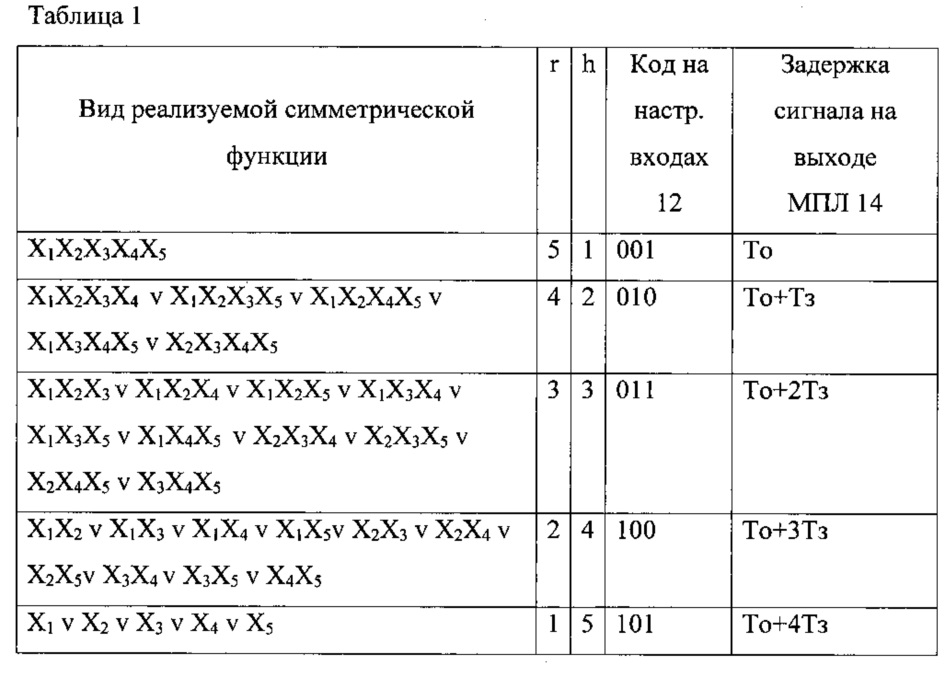

На настроечные входы 12 подается k-разрядный двоичный код десятичного числа h=n-r+l.

В табл. 1 приведен пример значений сигналов для реализации соответствующих симметрических функций для n=5.

На входы значений аргументов 2 подаются значения, текущие значения аргументов X1, Х2, …, Хn. На управляющий вход 1 подается сигнал «1».

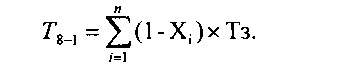

Формирователь фронта 11 формирует импульс, поступающий на входы R - «Сброс» D-триггеров 6 и 7 и они устанавливаются в состояние «0». С управляющего входа 1 сигнал поступает на первый вход элемента И 8 через время Т8-1, определяемое значениями аргументов:

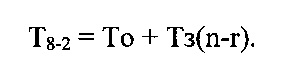

В зависимости от заданного значения r, после подачи управляющего сигнала 1 на втором входе элемента И 8 в течении времени T9-2 сигнал «1», где

Если T8-1<T8-2, то на выходе элемента И 8 после времени T8-1 формируется сигнал «1», который:

- устанавливает первый D-триггер 6 в состояние «1», что свидетельствует о значении симметричной функции для текущих значений аргументов,

- проходит через элемент ИЛИ 16 и устанавливает второй D-триггер 7 в состояние «1», что свидетельствует о готовности результата.

Если T8-1>T8-2, то на выходе элемента НЕ 13 устанавливается после времени T8-2 сигнал «0», который не меняет значение первого D-триггера 6, что свидетельствует о значении «0» симметричной функции для текущих значений аргументов. Изменение значения выходного сигнала на выходе элемента НЕ 13 с «1» на «0» фиксирует формирователь спада 15, который формирует сигнал «1», который проходит через элемент ИЛИ 16 и устанавливает второй D-триггер 7 в состояние «1», что свидетельствует о готовности результата.

Таким образом, значение сигнала «1» на выходе 5 свидетельствует о готовности результата, а значение сигнала на выходе 4 указывает на его значение.

Особенностью работы устройства является то, что время готовности результата зависит от значений аргументов X и для большинства значений меньше чем Тз×n. Это может быть использовано в асинхронных схемах. Следовательно, предлагаемое устройство имеет более широкие функциональные возможности, чем прототип. Подача двоичного кода настройки на настроечные входы устройства осуществляется проще, чем импульсная настройка.

Логический вычислитель, предназначенный для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержащий управляющий вход, выход, входы значений аргументов, элемент И, два D-триггера, элемент ИЛИ, n двухвходовых коммутаторов, каждый из которых имеет два входа, выход, управляющий вход, нормально замкнутый контакт, подключенный к первому входу коммутатора и выходу коммутатора, нормально разомкнутый контакт, подключенный ко второму входу коммутатора и выходу коммутатора, i-ый вход значений аргументов соединен с управляющим входом i-го коммутатора, i=1, …, n, отличающийся тем, что дополнительно содержит второй выход, две группы элементов задержки по n элементов в каждой, формирователь фронта, настроечные входы, элемент НЕ, мультиплексор, формирователь спада, причем управляющий вход соединен с входом формирователя фронта, через первый элемент задержки первой группы с первым входом первого коммутатора, вторым входом первого коммутатора, входом первого элемента задержки второй группы, выход i-го коммутатора соединен со вторым входом i+1-го коммутатора и через i+1-ый элемент задержки первой группы соединен с первым входом i+1-го коммутатора, i=1…n-1, выход n-го коммутатора соединен с первым входом элемента И, выход формирователя фронта соединен с входами «Сброс» первого и второго D-триггеров, настроечные входы соединены с соответствующими адресными входами мультиплексора, выход мультиплексора соединен через элемент НЕ со вторым входом элемента И и входом формирователя спада, выход элемента И соединен с входами данных и записи первого D-триггера и первым входом элемента ИЛИ, выход первого D-триггера соединен с первым выходом устройства, выход второго D-триггера соединен со вторым выходом устройства, выход i-го элемента задержки второй группы соединен с входом i+1-го элемента задержки второй группы и i-ым информационным входом мультиплексора (i=1…n-1), выход n-го элемента задержки второй группы соединен с n-ым информационным входом мультиплексора, выход детектора спада соединен с вторым входом элемента ИЛИ, выход которого соединен с входами данных и записи второго триггера.