Результат интеллектуальной деятельности: Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано в технике связи при формировании имитостойких и структурно скрытных систем сигналов сложной формы, в структуре которых отмечается повышенная степень неопределенности вида, формы, длительности, ансамблевых и других статистических характеристик сигналов сложной формы.

Повышение помехоустойчивости и скрытности радиотехнических систем связи, а также обеспечение имитостойкости процесса передачи данных по каналу радиосвязи при использовании сложных сигналов по типу дискретно-частотных сигналов (ДЧС) достигается за счет расширения спектра ДЧС определенными псевдослучайными последовательностями (ПСП), которые, с точки зрения обеспечения безопасности информации, применяются в системах криптографической защиты информации. При этом такие ПСП должны быть детерминированными, периодическими с требуемыми (заданными) периодами и длинами, обладать высокой структурной скрытностью (то есть реализуемые ПСП должны быть максимально приближены по статистическим свойствам к истинно случайным последовательностям) (см., например, Иванов М.А., Чугунков И.В. Теория, применение и оценка качества генераторов псевдослучайных последовательностей. - М.: Кудиц. - Образ, 2003. С. 14-15).

Отсюда следует, что для достижения больших результатов в повышении вышеуказанных свойств радиотехнических систем связи требуется применение новых (перспективных) алгоритмов синтеза ПСП, позволяющих: увеличивать длину ПСП с шагом близким к 1; вносить неопределенность расположения элементов-чисел в ПСП; значительно увеличивать объем сменных параметров (кодовых форм) систем ПСП при фиксированной длине ПСП, - в том числе обеспечивать наибольшую частость их смены из искомого ансамбля кодовых форм ПСП, и так далее.

Как показано в ряде работ (см., например, Сныткин И.И., Кулюпин Е.Н. Реализация механизма и услуг защиты информации (шифрование потока трафика согласно ГОСТ РИСО 7498) на 1-м уровне логической структуры ISO на основе использования системных свойств и характеристик производных управляющих числовых кодовых последовательностей // Информационная безопасность регионов России (ИБРР-2015) IX Санкт-Петербургская межрегиональная конференция. Санкт-Петербург. 28-30 октября 2015 г.: Материалы конференции / СПОИСУ. СПб., 2015. С. 185-186), наиболее перспективными М-ичными ПСП, с точки зрения безопасности информации, являются системы двукратных производных управляющих числовых кодовых последовательностей аддитивного типа (ДК ПУЧКП AT), формирующиеся из элементов мультипликативных групп конечных полей.

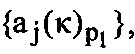

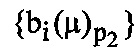

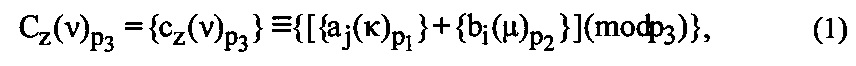

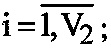

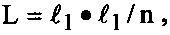

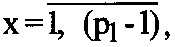

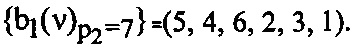

Так, формирование одной z-й ДК ПУЧКП AT  заданной длины L, где:

заданной длины L, где:  - элемент-число (ЭЧ) z-й ДК ПУЧКП AT, а

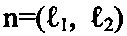

- элемент-число (ЭЧ) z-й ДК ПУЧКП AT, а  - порядковый номер одного ЭЧ в ДК ПУЧКП AT, p3=(p1∨p2), (p1, p2, p3) - простые числа, - в составе кодового словаря

- порядковый номер одного ЭЧ в ДК ПУЧКП AT, p3=(p1∨p2), (p1, p2, p3) - простые числа, - в составе кодового словаря  ДК ПУЧКП AT объема V,

ДК ПУЧКП AT объема V,  , основывается на использовании свойств структуры последовательностей элементов

, основывается на использовании свойств структуры последовательностей элементов

мультипликативных групп соответственно двух полей GF(p1) и GF(p2), далее именуемые как управляющие числовые кодовые последовательности (УЧКП-1 и УЧКП-2 соответственно), и представляет собой процесс последовательного сложения по модулю p3 элементов aj(κ) и bj(μ):

мультипликативных групп соответственно двух полей GF(p1) и GF(p2), далее именуемые как управляющие числовые кодовые последовательности (УЧКП-1 и УЧКП-2 соответственно), и представляет собой процесс последовательного сложения по модулю p3 элементов aj(κ) и bj(μ):

где: (j, i) - номера УЧКП-1 и УЧКП-2 в составе соответствующих словарей объемов V1 и V2,

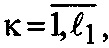

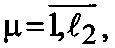

(κ, μ) - номера ЭЧ соответственно в УЧКП-1 и УЧКП-2,- причем:

(κ, μ) - номера ЭЧ соответственно в УЧКП-1 и УЧКП-2,- причем:

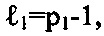

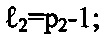

- длины УЧКП-1 и УЧКП-2,

- длины УЧКП-1 и УЧКП-2,  - наибольший общий делитель длин УЧКП-1 и УЧКП-2; p1, p2, p3 - как индексы соответственно при ЭЧ

- наибольший общий делитель длин УЧКП-1 и УЧКП-2; p1, p2, p3 - как индексы соответственно при ЭЧ

и

и  - означают, что приведение значений данных ЭЧ осуществляется по соответствующему модулю p(.).

- означают, что приведение значений данных ЭЧ осуществляется по соответствующему модулю p(.).

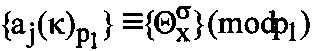

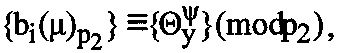

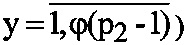

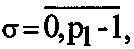

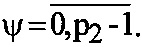

Также необходимо учитывать, что порождающие УЧКП-1 и УЧКП-2 заданных длин представляют собой последовательности элементов  и

и  (которые, по сути, являются соответствующими кодами остатков), то есть

(которые, по сути, являются соответствующими кодами остатков), то есть  и

и  где (Θx, Θy) - x-е и y-е первообразные корни соответствующих полей

где (Θx, Θy) - x-е и y-е первообразные корни соответствующих полей  и

и  (σ, ψ) - значение степени - индексы элементов УЧКП-1 и УЧКП-2, причем число значений

(σ, ψ) - значение степени - индексы элементов УЧКП-1 и УЧКП-2, причем число значений

(где ϕ(.) - функция Эйлера),

(где ϕ(.) - функция Эйлера),

Объем V формируемого кодового словаря  ДК ПУЧКП AT зависит от числа сочетаемых комбинаторным образом по правилу (1) видов и (или) подвидов производящих систем УЧКП-1 и УЧКП-2 соответствующих объемов V1 и V2 (где виды УЧКП-1 и УЧКП-2 составляют изоморфные преобразования первообразных корней над GF(p(.)), а их подвиды соответственно - автоморфные преобразования первообразных корней над GF(p(.)). Отсюда объем V кодового словаря

ДК ПУЧКП AT зависит от числа сочетаемых комбинаторным образом по правилу (1) видов и (или) подвидов производящих систем УЧКП-1 и УЧКП-2 соответствующих объемов V1 и V2 (где виды УЧКП-1 и УЧКП-2 составляют изоморфные преобразования первообразных корней над GF(p(.)), а их подвиды соответственно - автоморфные преобразования первообразных корней над GF(p(.)). Отсюда объем V кодового словаря  определится как

определится как

Важно отметить, что значение объема V кодового словаря  является важнейшим показателем при определении значений имитостойкости Iс сложного сигнала, в частности, перспективных систем ДК ПКДЧС, определяемых как Ic=log2⋅V (см. Сныткин И.И., Спирин А.В., Сныткин Т.И. Технические решения по формированию имитостойких систем кодо-дискретно-частотных сигналов с временным уплотнением информации // Информационная безопасность - актуальная проблема современности. Совершенствование образовательных технологий подготовки специалистов в области информационной безопасности: сб. трудов VIII-IX Всероссийская научно-техническая школа-семинар, г. Геленджик 2010. - Краснодар: ФВАС, 2010. - С. 119).

является важнейшим показателем при определении значений имитостойкости Iс сложного сигнала, в частности, перспективных систем ДК ПКДЧС, определяемых как Ic=log2⋅V (см. Сныткин И.И., Спирин А.В., Сныткин Т.И. Технические решения по формированию имитостойких систем кодо-дискретно-частотных сигналов с временным уплотнением информации // Информационная безопасность - актуальная проблема современности. Совершенствование образовательных технологий подготовки специалистов в области информационной безопасности: сб. трудов VIII-IX Всероссийская научно-техническая школа-семинар, г. Геленджик 2010. - Краснодар: ФВАС, 2010. - С. 119).

В этой связи применение ДК ПУЧКП AT становиться незаменимыми с точки зрения высоких требований помехоустойчивости и скрытности радиотехнических систем связи и имитостойкости применяемых в этих системах сигналов. С учетом отмеченного выигрыша в объеме V кодового словаря  (что особо важно для структурной скрытности сложного сигнала), техническая реализация правила построения ДК ПУЧКП AT будет просто актуальной.

(что особо важно для структурной скрытности сложного сигнала), техническая реализация правила построения ДК ПУЧКП AT будет просто актуальной.

Уже отмечаются разработанные элементы теории УЧКП (см., например, Сныткин И.И., Спирин А.В., Сныткин Т.И. Исследование корреляционных свойств. кодо-дискретно-частотных сигналов и рекомендации по построению словарей управляющих числовых кодовых последовательностей с необходимыми ансамблевыми и корреляционными свойствами // Специальная связь и безопасность информации (ССБИ-2102): сборник трудов международного симпозиума (Россия, Краснодар - Терскол, 20-30 апреля 2012 г.) / Некоммерческое частное образоват. учреждение высш. проф. образования «Кубан. Ин-т информзащиты» (КИИЗ). Краснодар: Экоинвест, 2012. С. 222-227), которые находят свое отражение в технических решениях по формированию сложных сигналов (например, см. патент РФ №2451327 от 20.05.2012 года «Устройство по формированию имитостойких систем дискретно-частотных сигналов с временным уплотнением»), однако технических решений по формированию ПУЧКП к настоящему времени не разработано. В связи с чем, разработка технического решения, в частности, по формированию систем двукратных производных кодовых ДЧС (ДК ПКДЧС), формируемых на основе ДК ПУЧКП AT, является целесообразной, и может быть реализована в устройстве, содержащем блоки формирования УЧКП-1 и УЧКП-2 различной длины (см. фиг. 1).

Известны аналоги, близкие по своей технической сущности к заявленному устройству, например: устройство для формирования элементов мультипликативных групп полей Галуа по авторскому свидетельству СССР №849895 «Устройство для формирования элементов мультипликативных групп полей Галуа» 1979 года; устройство для формирования имитостойких последовательностей сигналов сложной формы по авторскому свидетельству СССР №1203533 «Устройство для формирования имитостойких последовательностей сигналов сложной формы» от 1986 года; устройство для формирования последовательностей дискретно-частотных сигналов по авторскому свидетельству СССР №1444801 «Устройство для формирования последовательностей дискретно-частотных сигналов» от 1988 года. Приведенные устройства обеспечивают формирование всевозможных числовых последовательностей заданной длины в полях GF(p), реализуют алгоритмическую зависимость «тонкой» внутренней структуры (ТВС) элементов поля GF(p) от значений изменяемого первообразного корня Θ (где ТВС есть отличительная закономерность расположения всех элементов-чисел (ЭЧ) в конкретной числовой последовательности).

Однако перечисленные устройства имеют недостаток в том, что они не обеспечивают формирование имитостойких систем ДЧС.

Исходя из необходимости достижения требуемых результатов по формированию ДЧС с заданными (требуемыми) свойствами, наиболее близким по технической сущности и принятому за прототип является устройство по формированию имитостойких систем ДЧС с временным уплотнением по авторскому свидетельству РФ №2451327 «Устройство по формированию имитостойких систем дискретно-частотных сигналов с временным уплотнением», МПК G06F 15/00 (2006.01), заявл. 21.02.2011, опубл. 20.05.2012. Известное устройство содержит счетчик, выходы которого соединены с первой группой входов формирователя остатков, выходы которого соединены с входами регистра сдвигающего, выходы которого соединены со второй группой входов формирователя остатков и с входами записи элементов образующего мультипликатора, управляющий вход которого объединен с управляющими входами счетчика и регистра и является тактовым входом устройства, а выход установки в исходное нулевое состояние образующего мультипликатора, является соответствующим входом счетчика и регистра, а образующий мультипликатор также еще имеет: вход записи первообразного элемента, вход записи единицы, вход начала вычисления, вход записи числа элементов, выход конца вычисления, выход записи числа, являющийся входом формирователя остатков и выходы кодов остатков, причем образующий мультипликатор содержит: блок умножения, регистр сдвигающий, счетчик числа элементов, группу элементов «И», три элемента «И-НЕ», элемент «ИЛИ», элемент «И» и пять элементов задержки, входы записи элементов образующего мультипликатора являются первыми входами элементов «И» группы, выходы которых соединены соответственно с входами блока умножения и являются выходами кодов остатка устройства, выходы блока умножения подключены к входам регистра сдвигающий, выходы которого подключены к соответствующим входам первого элемента «И-НЕ», выход которого подключен к первому входу второго элемента «И-НЕ», первому входу элемента «ИЛИ» и входу первого элемента задержки, выход которого соединен со вторыми входами элементов «И» группы, входом второго элемента задержки и входами счетчика числа элементов, выход которого соединен с входом третьего элемента задержки, вторым входом элемента «ИЛИ» и является выходом конца вычислений устройства, выход элемента «ИЛИ» подключен к первому входу блока умножения, второй вход которого является входом записи числа элементов устройства, выход второго элемента задержки соединен с первым входом третьего элемента «И-НЕ», выход которого объединен с входом канала вычислений устройства и подключен к третьему входу блока умножения, выход которого является выходом установки в исходное нулевое состояние и подключен к входу четвертого элемента задержки, выход которого соединен с выходом пятого элемента задержки и подключен к первому входу элемента «И», выход которого соединен со входом пятого элемента задержки и входом регистра сдвигающего, выход которого соединен со входом формирователя остатков, выход третьего элемента задержки подключен ко второму входу третьего элемента «И-НЕ», второй вход элемента «И» соединен с выходом второго элемента «И-НЕ», второй вход которого является тактовым входом устройства, а четвертый вход блока умножения является входом записи единицы устройства, а также блок формирования систем сложных дискретно-частотных сигналов (БФСС ДЧС), первые входы которого соединены с выходами кодов остатков образующего мультипликатора, а вход записи числа элементов образующего мультипликатора объединен со вторым входом БФСС ДЧС, а вход начала вычисления образующего мультипликатора объединен с третьим входом БФСС ДЧС, а первый выход БФСС ДЧС является тактовым управляющим входом образующего мультипликатора, счетчика и регистра, а второй выход БФСС ДЧС является информационным выходом устройства, причем БФСС ДЧС содержит: дешифратор, «К» входов которого являются первыми входами БФСС ДЧС, a «N» выходов соединены с первыми «N» входами распределителя и «N» входами схемы «ИЛИ», выход которой соединен с первым входом схемы «И», а «n» выходов распределителя соединены с первыми входами группы ключевых схем, вторые входы которых соединены с «n» выходами синтезатора частот, третьи входы соединены с выходами источника дискретной информации, а выходы через многовходовую схему «ИЛИ» соединены с выходом устройства, причем выход источника дискретной информации соединен со входом аналого-цифрового преобразователя, выходы которого соединены с третьими входами делителя с переменными коэффициентом деления, вторым входом которого является вход записи числа элементов, а первым входом - выход генератора тактовых импульсов, а выход делителя с переменным коэффициентом деления является первым входом счетчика, формирователя остатков и образующего мультипликатора и является вторым входом схемы «И», выход которой является тактовым входом распределителя.

Данное устройство-прототип позволяет повышать имитостойкость ДЧС за счет изменения типа (вида), формы и состава сложных сигналов посредством изменения вида манипулирующей функции, что в целом достигается при следующих режимах его работы:

формирование ДЧС при длительности информационной посылки T=const и первообразном корне Θ=var;

формирование ДЧС при длительности информационной посылки T=const, а модуля p=var;

формирование ДЧС при длительности информационной посылки T=var и первообразном корне Θ=var;

формирование ДЧС при длительности информационной посылки Т=var, а модуля p=var.

Как следует из теории конечных полей, например, известное устройство-прототип позволяет формировать ДЧС с базами  то есть 23 реализации базы ДЧС при В≤104 (или длине УЧКП

то есть 23 реализации базы ДЧС при В≤104 (или длине УЧКП  ).

).

Однако помимо этого объем V1 неповторяемых кодовых форм ДЧС, формируемых устройством-прототипом не превышает значений длины  УЧКП, то есть

УЧКП, то есть  (в силу свойств конечных полей). Кроме этого прототип не позволяет изменять количество частотных элементов ДЧС (базу сигнала В) при фиксированной длительности ДЧС. Тогда как для обеспечения заданных параметров по помехоустойчивости, скрытности и имитостойкости требуется большая реализация значений баз В ДЧС в заданных пределах (до В=104) и большее значение объема его сменных параметров (кодовых форм).

(в силу свойств конечных полей). Кроме этого прототип не позволяет изменять количество частотных элементов ДЧС (базу сигнала В) при фиксированной длительности ДЧС. Тогда как для обеспечения заданных параметров по помехоустойчивости, скрытности и имитостойкости требуется большая реализация значений баз В ДЧС в заданных пределах (до В=104) и большее значение объема его сменных параметров (кодовых форм).

Таким образом, перечисленный ряд недостатков ограничивает функциональные возможности устройства-прототипа.

Целью изобретения является расширение класса решаемых задач по формированию более имитостойких и структурно скрытностных сигналов сложной формы на основе программно-управляемой генерации больших объемов кодовых форм и длин ДК ПУЧКП AT.

В устройстве-прототипе имеются существенные признаки, присущие заявленному устройству. Это наличие счетчика, формирователя остатков, регистра, образующего мультипликатора и связи между ними, а также БФ СС ДЧС, причем выходы первого счетчика соединены с первой группой входов формирователя остатков, выходы которого соединены с входами регистра, выходы которого соединены со второй группой входов формирователя остатков и с входами записи элементов образующего мультипликатора, управляющий вход которого объединен с управляющими входами счетчика и регистра и является тактовым входом устройства, а выход установки в исходное нулевое состояние образующего мультипликатора является соответствующим входом счетчика и регистра, а образующий мультипликатор также еще имеет: вход записи первообразного элемента, вход записи единицы, вход начала вычисления, вход записи числа элементов, выход конца вычисления, выход записи числа, являющийся входом формирователя остатков и выходы кодов остатков, причем образующий мультипликатор содержит: блок умножения, регистр сдвига, счетчик числа элементов, группу элементов «И», три элемента «И-НЕ», элемент «ИЛИ», элемент «И» и пять элементов задержки, входы записи элементов образующего мультипликатора являются первыми входами элементов «И» группы, выходы которых соединены соответственно с входами блока умножения и являются выходами кодов остатка устройства, выходы блока умножения подключены к входам регистра сдвига, выходы которого подключены к соответствующим входам первого элемента «И-НЕ», выход которого подключен к первому входу второго элемента «И-НЕ», первому входу элемента «ИЛИ» и входу первого элемента задержки, выход которого соединен со вторыми входами элементов «И» группы, входом второго элемента задержки и входами счетчика числа элементов, выход которого соединен с входом третьего элемента задержки, вторым входом элемента «ИЛИ» является выходом конца вычислений устройства, выход элемента «ИЛИ» подключен к первому входу блока умножения, второй вход которого является входом записи числа элементов устройства, выход второго элемента задержки соединен с первым входом третьего элемента «И-НЕ», выход которого объединен с входом начала вычислений устройства и подключен к третьему входу блока умножения, выход которого является выходом установки в исходное нулевое состояние и подключен к входу четвертого элемента задержки, выход которого соединен с выходом пятого элемента задержки и подключен к первому входу элемента «И», выход которого соединен со входом пятого элемента задержки и входом регистра сдвига, выход которого соединен со входом формирователя остатков, выход третьего элемента задержки подключен ко второму входу третьего элемента «И-НЕ», второй вход элемента «И» соединен с выходом второго элемента «И-НЕ», второй вход которого, является тактовым входом устройства, а четвертый вход блока умножения является входом записи единицы устройства, а БФСС ДЧС, у которого второй и третий входы являются соответствующими входами записи числа элементов и начала вычисления, а его первый выход - тактовым управляющим входом образующего мультипликатора, счетчика и регистра, а второй выход БФСС ДЧС является информационным выходом устройства, причем БФСС ДЧС содержит: дешифратор, девять входов которого являются первыми входами блока формирования систем сложных дискретно-частотных сигналов, a «N» его выходов соединены с первыми «N» входами распределителя и «N» входами схемы «ИЛИ», выход которой соединен с первым входом схемы «И», а «n» выходов распределителя соединены с первыми входами группы ключевых схем, вторые входы которых соединены с «n» выходами источника дискретной информации, а выходы через многовходовую схему «ИЛИ» соединены с выходом устройства, причем выход источника дискретной информации соединен со входом аналого-цифрового преобразователя, выходы которого соединены с третьими входами делителя с переменным коэффициентом деления (ДПКД), вторым входом которого является вход записи числа элементов, а первым входом - выход генератора тактовых импульсов, а выход делителя с переменным коэффициентом деления является первым входом первых счетчика, формирователя остатков и образующего мультипликатора и является вторым входом схемы «И», выход которой является тактовым входом распределителя.

Технической задачей заявляемого устройства является программно-управляемое (с точки зрения выбора видов, подвидов, длин, кодовых форм, объема кодового словаря) формирование систем ДК ПКДЧС с требуемыми структурными и системными характеристиками на основе ДК ПУЧКП AT одним функционально законченным устройством.

Технический результат заявляемого устройства обеспечивается за счет введения новых отличительных признаков в устройстве, а именно: как аналогично первым счетчику, формирователю остатков, регистру, образующему мультипликатору со связями между ними, объединенными в первый блок формирования мультипликативных групп в простых полях Галуа (БФМГ-1), с первого по пятый входы которого являются соответственно входами кода числа элементов, единицы, импульса «начало вычислений», кода числа первообразного элемента и тактовых импульсов от ДПКД БФСС ДЧС, а первой группой выходов и вторым выходом БФМГ-1 являются соответственно выходы кодов остатков и импульса «конец формирования», дополнительно введен второй БФМГ (БФМГ-2), содержащий вторые счетчик, формирователь остатков, регистр, образующий мультипликатор и связи между ними, и имеющий идентичные пять входов и два выхода, что и БФМГ-1, причем БФМГ-1 и БФМГ-2 с блоком циклического поразрядного суммирования элементов конечных полей по модулю (БЦПС) образуют блок формирования двукратных производных управляющих числовых кодовых последовательностей (БФ ДК ПУЧКП AT), в котором первые группы выходов обоих БФМГ подключены соответственно к первой и четвертой группе входов БЦПС, а вторые выходы, первые и четвертые входы БФМГ-1 и БФМГ-2 являются соответственно третьим и вторым выходами, и седьмым, пятым, девятым и восьмым входом БФ ДК ПУЧКП AT, а объединенные вторые, объединенные третьи и объединенные пятые входы БФМГ-1 и БФМГ-2 соответственно являются шестым, десятым и одиннадцатым входами БФ ДК ПУЧКП AT, причем одиннадцатый вход БФ ДК ПУЧКП AT объединен со своим первым входом и пятым входом БЦПС, а десятый вход БФ ДК ПУЧКП AT объединен с пятым входом БЦПС, а вторые, третьи и шестые группы входов БЦПС являются соответственно четвертыми, третьими и вторыми группами входов БФ ДК ПУЧКП AT, а выход БЦПС является первым выходом БФ ДК ПУЧКП AT, а к первому, и с пятого по одиннадцатый входы БФ ДК ПУЧКП AT подключены соответственно первый выход БФСС ДЧС, девятый, восьмой, седьмой, пятый, четвертый, второй и первый выходы СБУ, а со второй по четвертую группу входов БФ ДК ПУЧКП AT подключены соответственно двенадцатая, одиннадцатая и десятая группы выходов СБУ, а первым, третьим и четвертым входами и второй группой входов СБУ являются входы тактовых импульсов, импульса «запись данных», импульса «начало вычисления» и группа входов «код типа кодовой формы ДК ПУЧКП АТ» соответственно, причем первый вход, шестой и третий выходы СБУ подключены соответственно к первому выходу, второму и третьему входам БФСС ДЧС, вторым выходом которого является выход ДК ПКДЧС, причем БЦПС содержит один девятиразрядный параллельный сумматор по модулю с последовательным переносом (ДПС), два идентичных (первый и второй) узла хранения кодов остатков (УХКО), каждый из которых включает группы из восьми сдвиговых регистров и восьми мультиплексоров, причем объединенные первые входы сброса всех шестнадцати сдвиговых регистров являются седьмым входом БЦПС, а их вторые входы тактовых импульсов, вход инвертора и четвертый вход переноса модуля ДПС объединены с пятым входом БЦПС, а первая группа входов БЦПС поразрядно объединена с соответствующими третьими входами каждого из восьми сдвиговых регистров первого УХКО, первой группой входов ДПС и выходами мультиплексоров первого УХКО, а четвертая группа входов БЦПС поразрядно объединена с соответствующими третьими входами каждого из сдвиговых регистров второго УХКО, третьей группой входов ДПС и выходами мультиплексоров второго УХКО, причем в первом УХКО группа выходов с 1 по u, где u≥p1-1, каждого из восьми регистров сдвиговых подключена к первой группе входов с 1 по u соответствующего ей мультиплексора, а во втором УХКО группа выходов с 1 по v, где v≥p2-1, каждого из восьми регистров сдвиговых подключена к первой группе входов с 1 по v соответствующего ей мультиплексора, а вторые группы входов мультиплексоров первого и вторые группы входов мультиплексоров второго УХКО поразрядно объединены соответственно со второй и третьей группой входов БЦПС, а второй вход ДПС соединен с выходом инвертора, а пятая группа входов ДПС является шестой группой входов модуля числа БЦПС, а первая группа выходов ДПС является первой группой выхода БЦПС, а СБУ содержит два дешифратора, шесть восьмиразрядных сдвиговых регистра (ВСР), два восьмиразрядных многорежимных буферных регистра (ВМБР), три диода, генератор группы импульсов (ГГИ), два инвертора, два элемента задержки на такт и элемент «И», причем вторая группа входов СБУ является группой входов первого дешифратора, у которого первая, вторая и четвертая группы выходов поразрядно подключены соответственно к группами входов первого, второго и третьего ВСР, а группа входов третьего ВСР поразрядно соединена с группой входов второго дешифратора, а третья группа выходов первого дешифратора поразрядно соединена с группой входов обоих ВМБР, выходы которых являются двенадцатой группой выходов СБУ, а первая, вторая и третья группы выходов второго дешифратора поразрядно подключены соответственно к группам входов четвертого, пятого и шестого ВСР, причем группы входов четвертого и шестого ВСР объединены соответственно с десятой и одиннадцатой группами выходов СБУ, а выхода всех шести ВСР являются соответственно с четвертого по девятый выходами СБУ, а четвертый вход СБУ объединен с входами первых диода и элемента задержки на такт, установки в состояние «логический ноль» всех шести ВСР, и является своим вторым выходом, а входы «блокировки синхросигнала» всех шести ВСР объединены с выходом первого инвертора, вход которого объединен с выходом ГГИ и входом второго элемента задержки на такт, вторым входом элемента «И» и входами «синхросигнала» всех шести ВСР, а вход ГГИ является третьим входом СБУ, который объединен с входом второго инвертора, выход которого объединен с выходом второго элемента задержки на такт и первым входом элемента «И», причем выход первого элемента «И» является общим входом «выбора режима» всех шести ВСР, а третий вход СБУ также объединен с входом второго диода и с входами «запись» обоих ВМБР, вход «считывание» которых объединен со входом третьего диода и является первым входом СБУ, а объединенные выходы второго и третьего диодов подключены к входу «выбора микросхемы» ВМБР.

Этот признак и позволяет реализовать возможность формирования сложного сигнала в программно-управляемом режиме заданного с большим объемом кодовых форм и базой при фиксированной длительности сигнала.

Проведенный анализ существующих устройств (технических решений) показывает, что аналоги, характеризующиеся совокупностью признаков, тождественны всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявляемого устройству условию патентоспособности «новизна». А результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного устройства, показали, что они не следуют явным образом из уровня техники, в том числе не выявлена известность влияния предусмотренных существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. В связи с чем, заявленное устройство соответствует условию патентоспособности «изобретательский уровень».

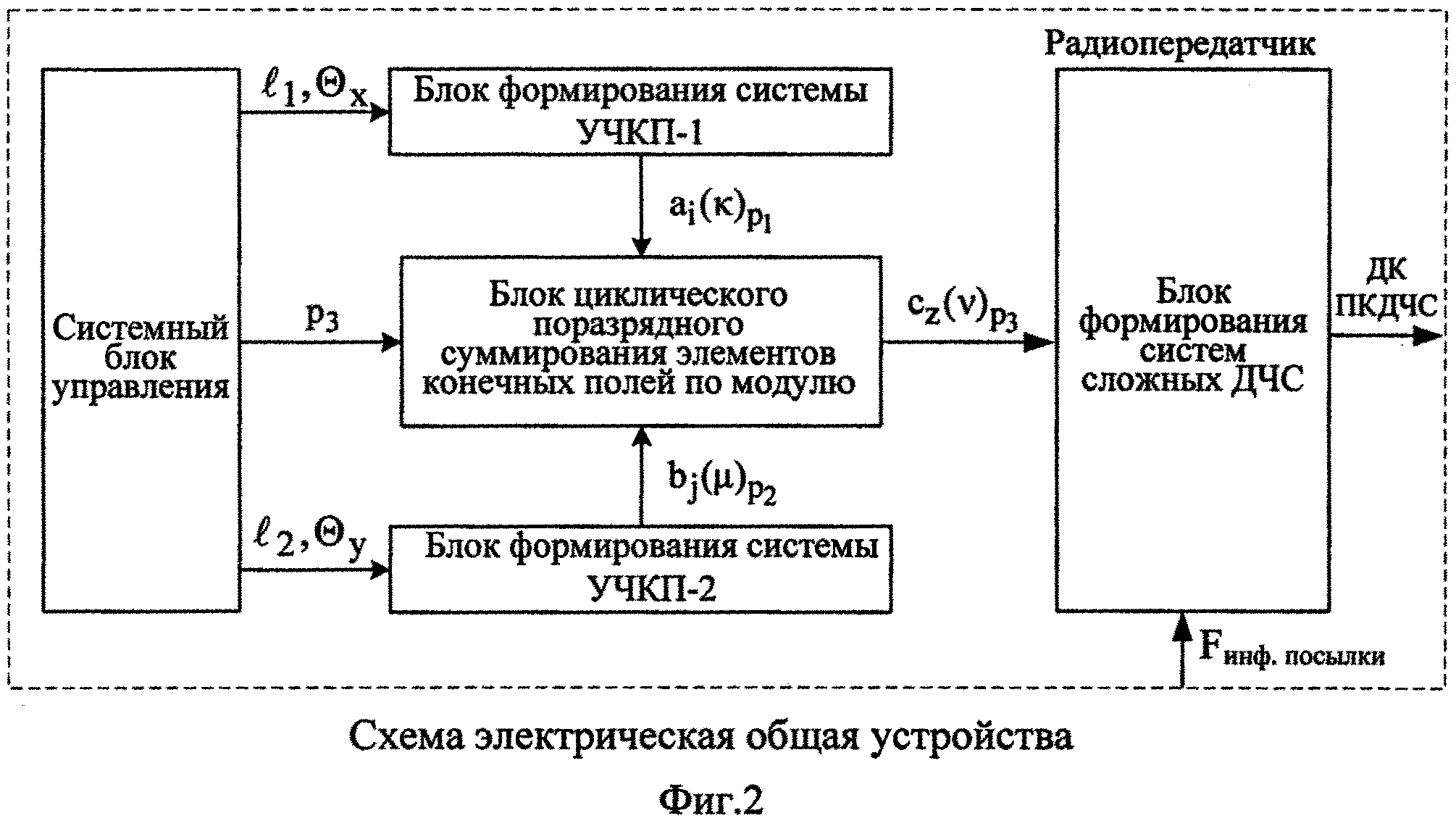

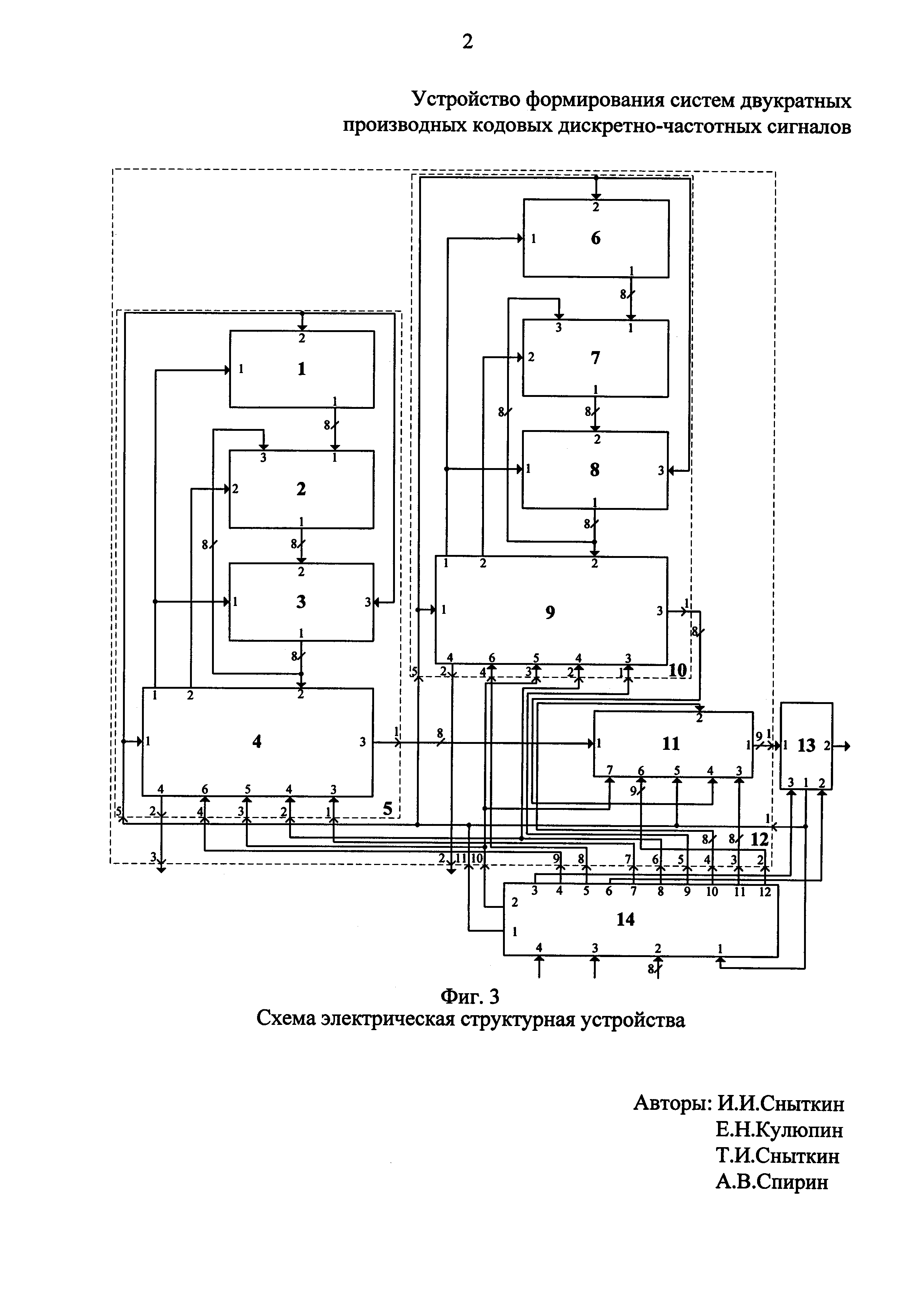

Сущность заявленного устройства (с учетом положений ГОСТ 2.701-2008 «Схемы. Виды и типы. Общие требования к выполнению», а также ГОСТ 2.743-91 «Единая система конструкторской документации. Обозначения условные графические в схемах. Элементы цифровой техники») поясняется представленными на фиг. 2-7 схемами электрическими соответствующих типов.

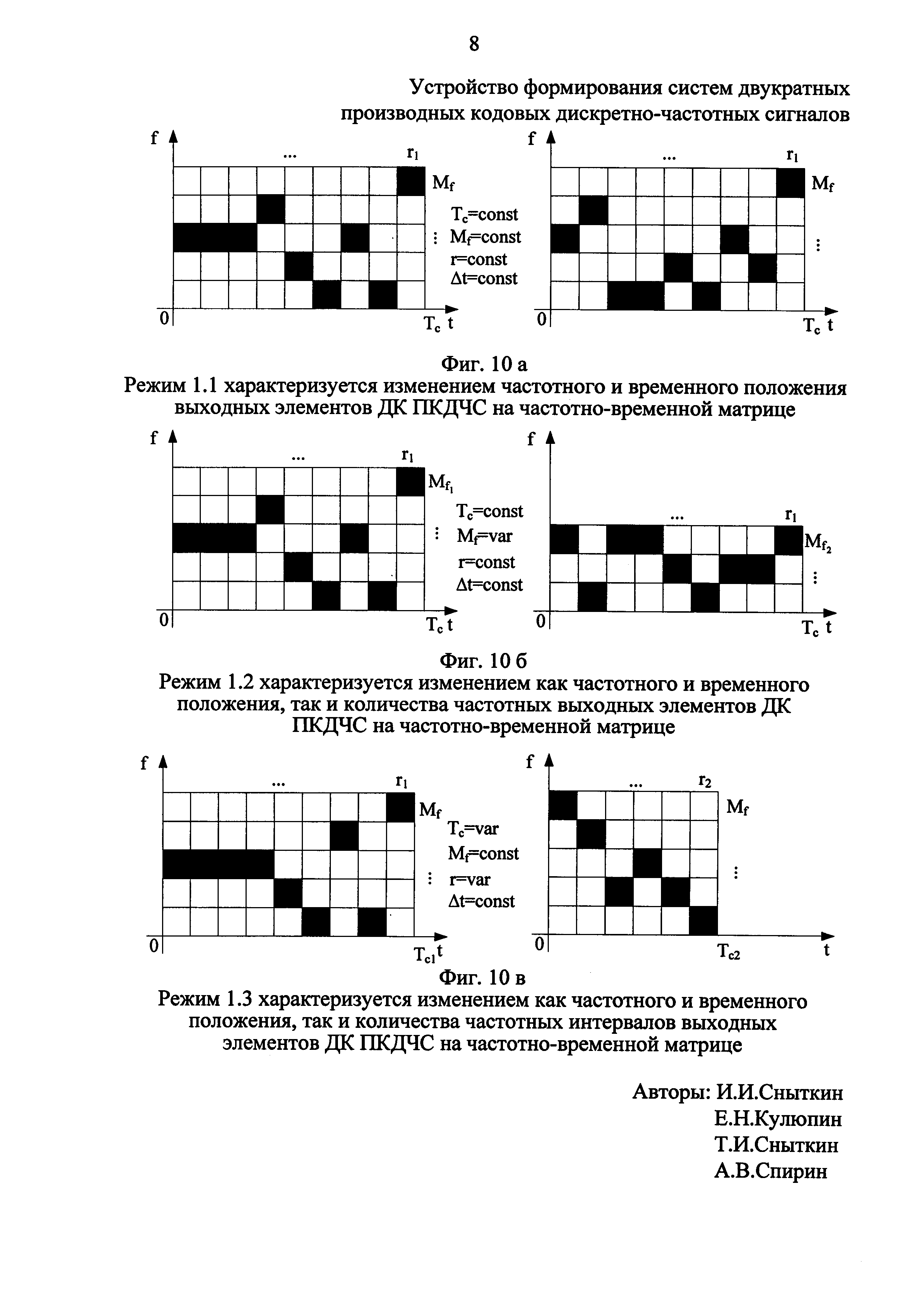

Устройство формирования систем ДК ПКДЧС, схема электрическая общая которого показана на фиг. 2, содержит два идентичных БФМГ, БЦПС, СБУ БФСС и ДЧС.

Устройство формирования систем ДК ПКДЧС, схема электрическая структурная которого показана на фиг. 3, содержит: первые счетчик 1, формирователь остатков 2, регистр 3 и мультиплексор 4, объединенные между собой соответствующими связями в БФМГ-1; идентичные элементы БФМГ-1 - вторые счетчик 6, формирователь остатков 7, регистр 8 и мультиплексор 9, объединенные между собой соответствующими связями в БФМГ-2; БЦПС 11, который объединен соответствующими связями с БФМГ-1 и БФМГ-2 в БФ ДК ПУЧКП AT 12; БФСС ДЧС 13; СБУ 14.

БЦПС 11, схема электрическая функциональная которого показана на фиг. 4, состоит из параллельных регистров сдвигающих 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15; мультиплексоров 11-1.2, 11-1.4, 11-1.6, 11-1.8, 11-1.10, 11-1.12, 11-1.14, 11-1.16, 11-4.2, 11-4.4, 11-4.6, 11-4.8, 11-4.10, 11-4.12, 11-4.14, 11-4.16; инвертора 11-2; девятиразрядного параллельного сумматора по модулю с последовательным переносом (ДПС) 11-3.

Любой их параллельных регистров сдвигающих 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15 предназначен для выполнения сдвига двоичной информации вправо или влево. В заявляемом устройстве он выполняет сдвиг одного из разрядов восьмиразрядного двоичного «кода остатков» от числа, и представляет собой цепочку последовательно соединенных между собой и (где u∈N) D-триггеров (где выход одного триггера является прямым информационным входом другого). Схемотехническое решение параллельного регистра сдвигающего является известным (см., например, Радиотехника: Энциклопедия / Под ред. Ю.Л. Мазора, Е.А. Мачусского, В.И. Правды. - М.: Издательский дом «Додэка-XXI», 2002. С. 763; Новиков Ю.В. Основы информационной схемотехники. Базовые элементы и схемы. Метод проектирования. - М.: Мир, 2001. С. 143, рис. 4.18(б)).

Любой из мультиплексоров 11-1.2, 11-1.4, 11-1.6, 11-1.8, 11-1.10, 11-1.12, 11-1.14, 11-1.16, 11-4.2, 11-4.4, 11-4.6, 11-4.8, 11-4.10, 11-4.12, 11-4.14, 11-4.16 предназначен для коммутации на выход одного из нескольких информационных сигналов согласно коду адреса. В предлагаемом устройстве, в соответствии с поданным на мультиплексор кода C0…C7, будет определяется выбор входа информационных сигналов от прямого выхода одного из u D-триггеров соответствующего регистра сдвигающего (например, см. Радиотехника: Энциклопедия / Под ред. Ю.Л. Мазора, Е.А. Мачусского, В.И. Правды. - М.: Издательский дом «Додэка-XXI», 2002. С. 761).

ДПС 11-3 предназначен для ведения операции суммирования по модулю. В заявляемом устройстве ДПС 11-3 состоит из девяти одноразрядных параллельных сумматоров по модулю. Схема многоразрядного параллельного по модулю с последовательным переносом известна и реализована в патенте РФ №2439661 (опубликовано 10.01.2012, Бюл. №1) (см. фиг. 1, С. 2).

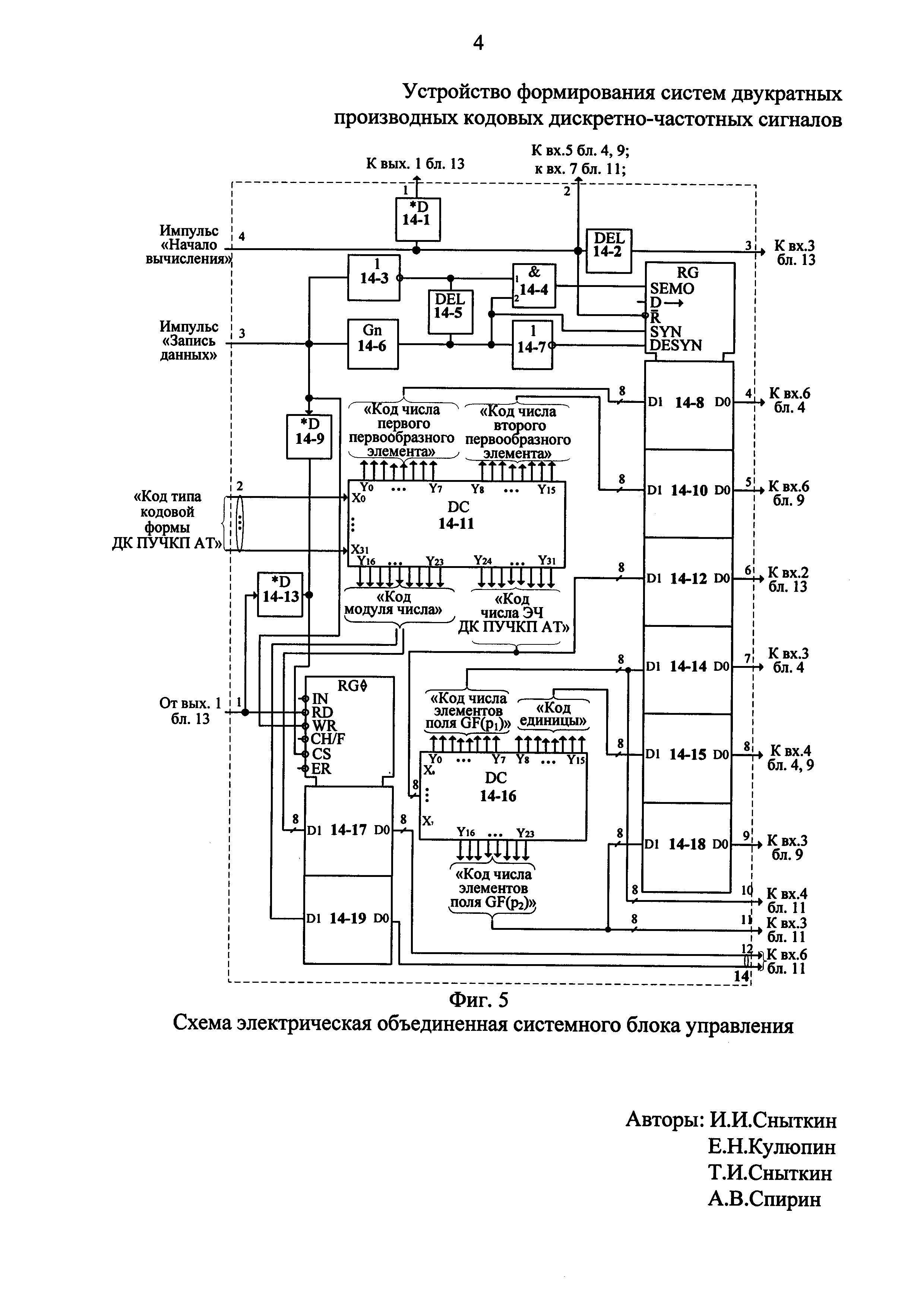

СБУ 14, схема электрическая объединенная которого показана на фиг. 5, содержит: диоды 14-1, 14-9, 14-13, элементы задержки на один такт 14-2, 14-5; инверторы 14-3, 14-7; элемент «И» 14-4; генератор группы импульсов (ГГИ) 14-6; восьмиразрядные сдвиговые регистры 14-8, 14-10, 14-12, 14-14, 14-15, 14-18; дешифраторы 14-11 и 14-16; восьмиразрядные многорежимные буферные регистры (ВМБР) 14-17 и 14-19.

Дешифраторы 14-11 и 14-16 представляют комбинационные схемы, включающие Xn входов и Ym выходов (где n<m (n, m∈N)), предназначенные для преобразования входного двоичного (двоично-десятичного) кода в двоичный код на выходах. В заявляемом устройстве они необходимы для преобразования каждого поступающего двоичного «кода типа кодовой формы ДК ПУЧКП AT заданной длительности» в соответствующие ему двоичные восьмиразрядные «коды числа первого первообразного элемента», «код числа ЭЧ ДК ПУЧКП АТ», «код числа второго первообразного элемента», двоичный код единицы, «код числа элементов поля GF(p1)» и «кода числа элементов поля GF(p2)». Схемотехническое построение дешифраторов 14-11 и 14-16 можно осуществить по известной методике (см., например, Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. Пер. с нем. - М.: Мир, 1982. С. 318).

В качестве восьмиразрядных сдвиговых регистров 14-8, 14-10, 14-12, 14-14, 14-15, 14-18 могут быть использованы серийно-реализованные промышленностью микросхемы КР1533ИР10. Данные микросхемы могут работать в режиме параллельной загрузки и сдвига, и в заявляемом устройстве они необходимы для последовательной записи восьмиразрядного двоичного «кода числа первого первообразного элемента» в блок умножения 4-6 по шестому входу первого образующего мультипликатора 4, восьмиразрядного двоичного «кода числа второго первообразного элемента» - в блок умножения 9-6 по шестому входу второго образующего мультипликатора 9, восьмиразрядного двоичного «кода числа элементов ДК ПУЧКП» - в делитель с переменным коэффициентом деления 13-10 (ДПКД) по второму входу БФСС ДЧС 13, восьмиразрядного двоичного «кода числа элементов поля GF(p1)» - в счетчик 4-12 числа элементов по третьему входу первого образующего мультипликатора 4, восьмиразрядного двоичного «кода единицы» - в блок умножения 4-6 по четвертому входу первого образующего мультипликатора 4 и в блок умножения 9-6 по четвертому входу второго образующего мультипликатора 9, восьмиразрядного двоичного «кода числа элементов поля GF(p2)» - счетчика 9-12 числа элементов по третьему входу второго образующего мультипликатора 9. Схема восьмиразрядного сдвигового регистра известна (например, см. Петровский И.И., Прибыльский А.В., Троян А.А., Чувелев B.C. Логические ИС КР 1533 КР 1554. Справочник. Часть 1. - М.: Бином, 1993. С. 127).

В качестве восьмиразрядных многорежимных буферных регистров 14-17 и 14-19 могут быть использованы серийно реализованные промышленностью микросхемы К588ИР1. Они предназначены для построения интерфейсных блоков процессов, запоминающих устройств, контроллеров внешних устройств. В заявляемом устройстве они необходимы для хранения девятиразрядного двоичного «кода модуля числа» поступающего от третьих прямых выходов дешифратора 14-11. Схема многорежимного буферного регистра известна (например, см. Лебедев О.Н. Микросхемы памяти и их применение. - М.: Радио и связь, 1990. С. 73. Рис. 2.19).

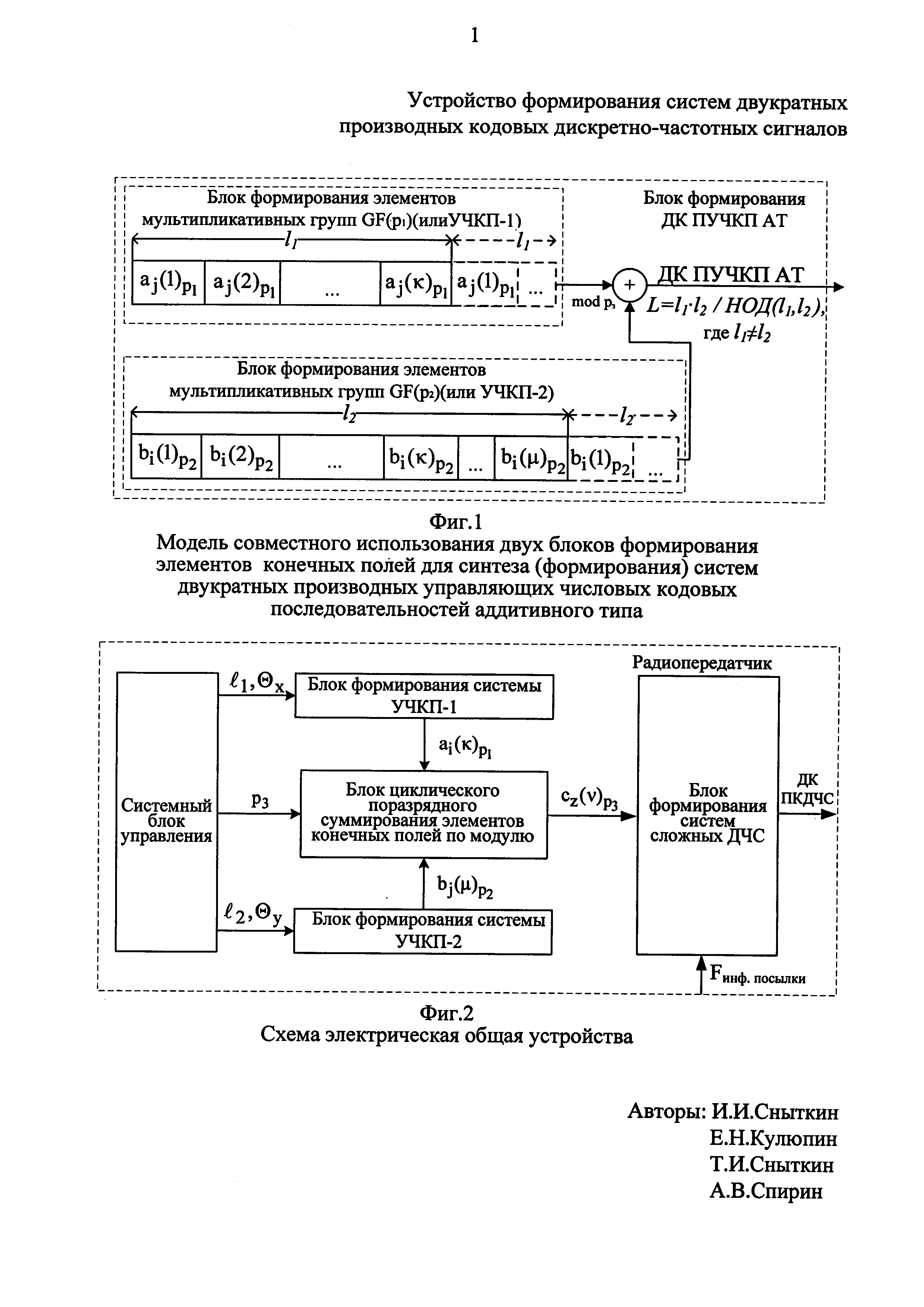

Первый образующий мультипликатор 4, схема электрическая функциональная которого представлена на фиг. 6, также же как и второй образующий мультипликатор 9 (с точки зрения количества составляющих его элементов и связей между ними), состоит из первого, второго, третьего, четвертого и пятого элементов 4-1, 4-3, 4-10, 4-13, 4-14 задержки, группы элементов 4-2 «И», первого, второго и третьего элементов «И-НЕ» 4-4, 4-7, 4-8, регистра 4-5 сдвига, блока 4-6 умножения, элемента «ИЛИ» 4-9, элемента «И» 4-11, счетчика 4-12 числа элементов и соответствующих связей между данными элементами.

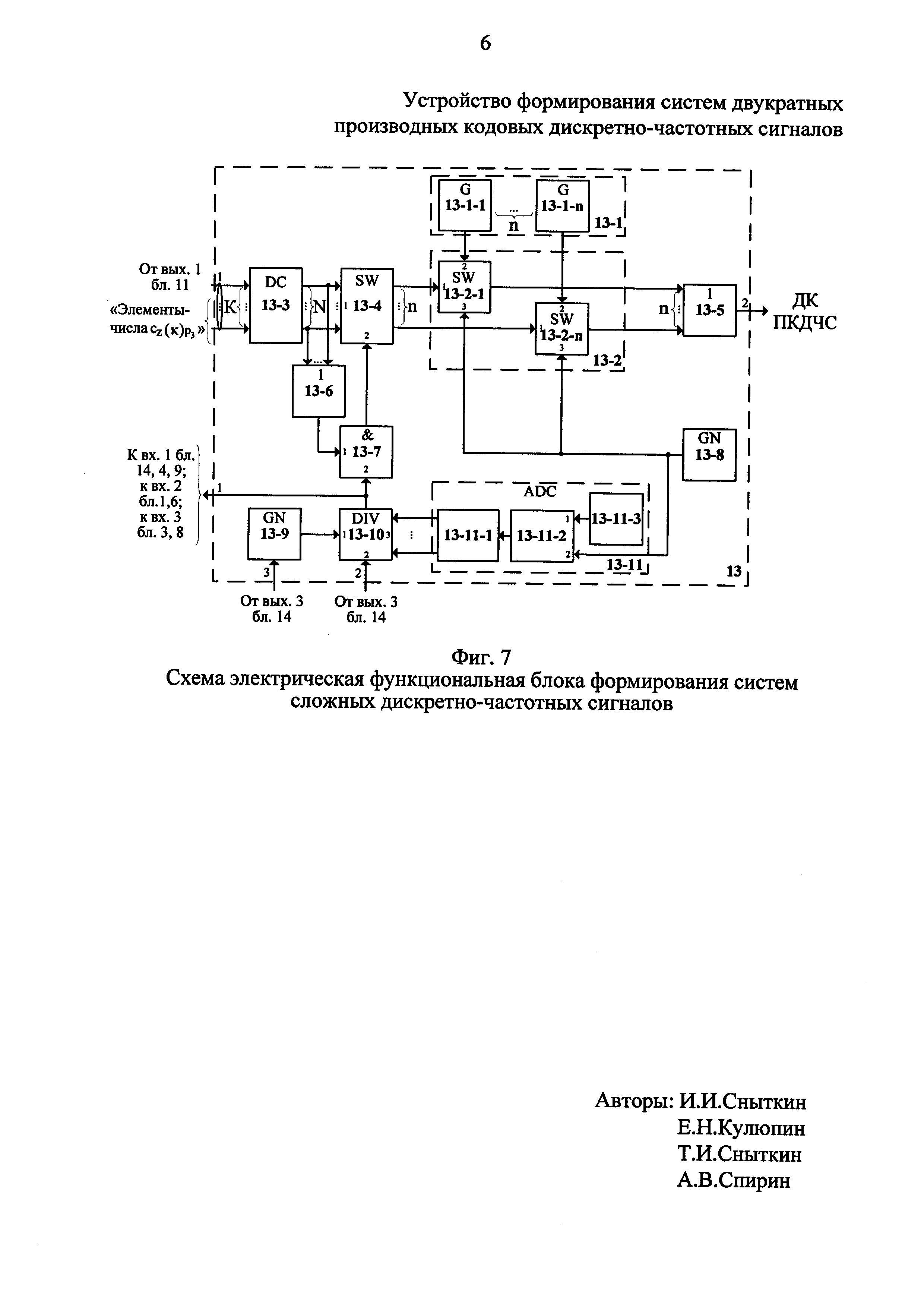

БФСС ДЧС 13, схема электрическая функциональная которого представлена на фиг. 7, состоит из синтезатора частот 13-1, группы 13-2 ключевых схем, дешифратора 13-3, распределителя 13-4, схемы 13-5 «ИЛИ», схемы «ИЛИ» 13-6, схемы «И» 13-7, источника дискретной информации 13-8, генератора тактовых импульсов (ГТИ) 13-9, ДПКД 13-10, аналого-цифрового преобразователя (АЦП) 13-11.

Основными структурными элементами АЦП являются генератор импульсов, вентиль и счетчик. Техническое решение АЦП известно (см. Мазор Ю.Л. Радиотехника: Энциклопедия / Под ред. Ю.Л. Мазора, Е.А. Мачусского, В.И. Правды. - М.: Издательский дом «Додэка-XXI», 2002. С. 752). В заявляемом устройстве АЦП 13-11 преобразует длительность информационного импульса Т в цифровой код. Работа АЦП 13-11 заключается в следующем: информационный импульс открывает на время Т вентиль 13-11-2, на второй вход которого подаются импульсы от генератора импульсов 13-8, с выхода вентиля 13-11-2 эти импульсы поступают на вход счетчика 13-11-1. Счетчик считывает число n поступивших импульсов, количество которых зависит от интервала Т. С выходов счетчиков 13-11-1 снимается параллельный код, соответствующий числу импульсов К.

ДПКД 13-10 является известным устройством (например, см. Мазор Ю.Л. Радиотехника: Энциклопедия / Под ред. Ю.Л. Мазора, Е.А. Мачусского, В.И. Правды. - М.: Издательский дом «Додэка-XXI», 2002. С. 756).

Вне зависимости от режимов работы устройство, схема электрическая структурная которого представлена на фиг. 3, в целом работает следующим образом.

Перед началом работы по второму входу СБУ 14, схема электрическая объединенная которого представлена на фиг. 5, на группу входов X0…X7 дешифратора 14-11 поступает «код типа кодовой формы ДК ПУЧКП АТ» в соответствии с которым на его первой группе выходов Y0…Y7, являющихся входами восьмиразрядного сдвигового регистра 14-8, формируется восьмиразрядный двоичный «код числа первого первообразного элемента», а на второй группе его выходов Y8…Y15, являющихся входами восьмиразрядного сдвигового регистра 14-10, - восьмиразрядный двоичный «код второго первообразного элемента», а на его третьей группе прямых выходов Y16…Y23, являющихся входами многорежимных буферных регистров 14-17 и 14-19, - девяти разрядный двоичный «код модуля числа», а на четвертой группе прямых выходах Y24…Y31 дешифратора 14-11, являющихся входами восьмиразрядного сдвигового регистра с параллельной загрузкой 14-12 и входами Х0…X7 дешифратора 14-16, - двоичный «код числа ЭЧ ДК ПУЧКП АТ». При этом на первой группе выходов Y0…Y7 дешифратора 14-16, являющихся входами восьмиразрядного сдвигового регистра 14-14 и четвертым входом блока 11, формируется восьмиразрядный двоичный «код числа элементов поля GF(p1)», а на его второй группе выходов Y8…Y15, являющихся входами восьмиразрядного сдвигового регистра с параллельной загрузкой 14-15, - восьмиразрядного двоичного «кода единицы», а на его третьей группе выходов Y16…Y23, являющихся входами восьмиразрядного сдвигового регистра 14-18 и третьим входом блока 11, формируется восьмиразрядный двоичный «код числа элементов поля GF(p2)».

Одновременно с поступлением на восьмиразрядную группу входов X0…X7 дешифратора 14-11 восьмиразрядного двоичного «кода типа кодовой формы ДК ПУЧКП АТ» по третьему входу СБУ 14 на вход ГГИ 14-6 поступает импульс «запись данных», включающий, тем самым, ГГИ 14-6 в работу. Импульс «запись данных» также поступает и на вход инвертора 14-3, с выхода которого импульс поступает на первый вход элемента 14-4 «И». А первый импульс ГГИ 14-6, синхронизированный с импульсом «запись данных», одновременно поступает на вход элемента задержки на один такт 14-5, на второй вход элемент «ИЛИ» 14-4, и на вход инвертора 14-7, а также на входы «SYN» синхросигнала восьмиразрядных сдвиговых регистров 14-8, 14-10, 14-12, 14-14, 14-15, 14-18. Поступившие таким образом первые импульсы на управляющие входы всех шести восьмиразрядных сдвиговых регистров, в то числе с выхода элемента «И» 14-4 на входы «SEMO» и с выхода инвертора 14-7 на входы «DESYN», переводят сдвиговые регистры в режим «параллельная загрузка», вследствие чего на восьмиразрядный сдвиговый регистр 14-8 произойдет параллельная загрузка восьмиразрядного двоичного «кода числа первого первообразного элемента», а на восьмиразрядный сдвиговый регистр 14-10 - восьмиразрядный двоичный «код числа второго первообразного элемента», а на восьмиразрядный сдвиговый регистр 14-12 и на группу входов Х0…X7 дешифратора 14-16 - восьмиразрядный двоичный «код числа ЭЧ ДК ПУЧКП АТ», а на восьмиразрядный сдвиговый регистр 14-14 и на четвертый вход блока 11 - восьмиразрядный двоичный «код числа элементов поля GF(p1)», а на восьмиразрядный сдвиговый регистр с параллельной загрузкой 14-15 - восьмиразрядный двоичный «код единицы», а на восьмиразрядный сдвиговый регистр 14-18 и на третий вход блока 11 - восьмиразрядный двоичный «код числа элементов поля GF(p2)». А на переведенные в режим «запись» ВМБР 14-17 и 14-19, за счет поданного одновременно импульса «запись данных» на входы «WR» и (через диод 14-9) «CS» данных ВМБР соответственно, произойдет запись девятиразрядного двоичного «кода модуля числа».

При втором и последующих импульсах от ГГИ 14-6 на прямом выходе элемента «И» 14-4, сигнал сменится с «логического нуля» на «логическую единицу», тем самым сменится режим работы восьмиразрядных сдвиговых регистров 14-8, 14-10, 14-12, 14-14, 14-15, 14-18 с «параллельная загрузка» на режим «сдвига». Вследствие чего будет происходить последовательная запись восьмиразрядного двоичного «кода числа первого первообразного элемента» в блок умножения 4-6 по шестому входу первого образующего мультипликатора 4, а восьмиразрядного двоичного «кода числа второго первообразного элемента» - в блок умножения 9-6 по шестому входу второго образующего мультипликатора 9, а восьмиразрядного двоичного «кода числа элементов ДК ПУЧКП АТ» - в делитель с переменным коэффициентом деления 13-10 по второму входу БФСС ДЧС 13, а восьмиразрядного двоичного «кода числа элементов поля GF(p1)» - в счетчик 4-12 числа элементов по третьему входу первого образующего мультипликатора 4, а восьмиразрядного двоичного «кода единицы» - в блок умножения 4-6 по четвертому входу первого образующего мультипликатора 4 и в блок умножения 9-6 по четвертому входу второго образующего мультипликатора 9, а восьмиразрядного двоичного «кода числа элементов поля GF(p2)» - в счетчик 9-12 числа элементов по третьему входу второго образующего мультипликатора 9.

Работа устройства начинается с подачи импульса «начало вычисления» по четвертому входу СБУ 14. При этом этот импульс одновременно поступит на объединенные входы сброса  восьмиразрядных сдвиговых регистров 14-8, 14-10, 14-12, 14-14, 14-15, 14-18 СБУ 14, устанавливая их в исходное, соответствующее «логическому нулю» состояние, а также импульс поступит на элемент задержки на один такт 14-2, диод 14-1, а через второй выход СБУ 14 импульс поступит также в блоки умножения 4-6 и 9-6 первого и второго образующих мультипликаторов 4 и 11 соответственно, и по седьмому входу БЦПС 11, приводя в исходное (соответствующее логическому «нулю») состояние регистры сдвигающие 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15. С поступившим с выхода диода 14-1 импульса (см. фиг. 8а)) на первый вход мультиплексора 4, второй вход счетчика 1 и третий вход регистра сдвигающего 3, блок 4-6 умножения умножает «единицу» на Θx и записывает результат умножения в регистр 4-5 сдвига, и по окончании этого умножения выдает по соответствующему своему выходу импульс «конец умножения» на первый выход первого образующего мультипликатора 4, приводя в нулевое исходное состояние счетчик 1 и регистр сдвигающий 3, и на элемент задержки 4-14.

восьмиразрядных сдвиговых регистров 14-8, 14-10, 14-12, 14-14, 14-15, 14-18 СБУ 14, устанавливая их в исходное, соответствующее «логическому нулю» состояние, а также импульс поступит на элемент задержки на один такт 14-2, диод 14-1, а через второй выход СБУ 14 импульс поступит также в блоки умножения 4-6 и 9-6 первого и второго образующих мультипликаторов 4 и 11 соответственно, и по седьмому входу БЦПС 11, приводя в исходное (соответствующее логическому «нулю») состояние регистры сдвигающие 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15. С поступившим с выхода диода 14-1 импульса (см. фиг. 8а)) на первый вход мультиплексора 4, второй вход счетчика 1 и третий вход регистра сдвигающего 3, блок 4-6 умножения умножает «единицу» на Θx и записывает результат умножения в регистр 4-5 сдвига, и по окончании этого умножения выдает по соответствующему своему выходу импульс «конец умножения» на первый выход первого образующего мультипликатора 4, приводя в нулевое исходное состояние счетчик 1 и регистр сдвигающий 3, и на элемент задержки 4-14.

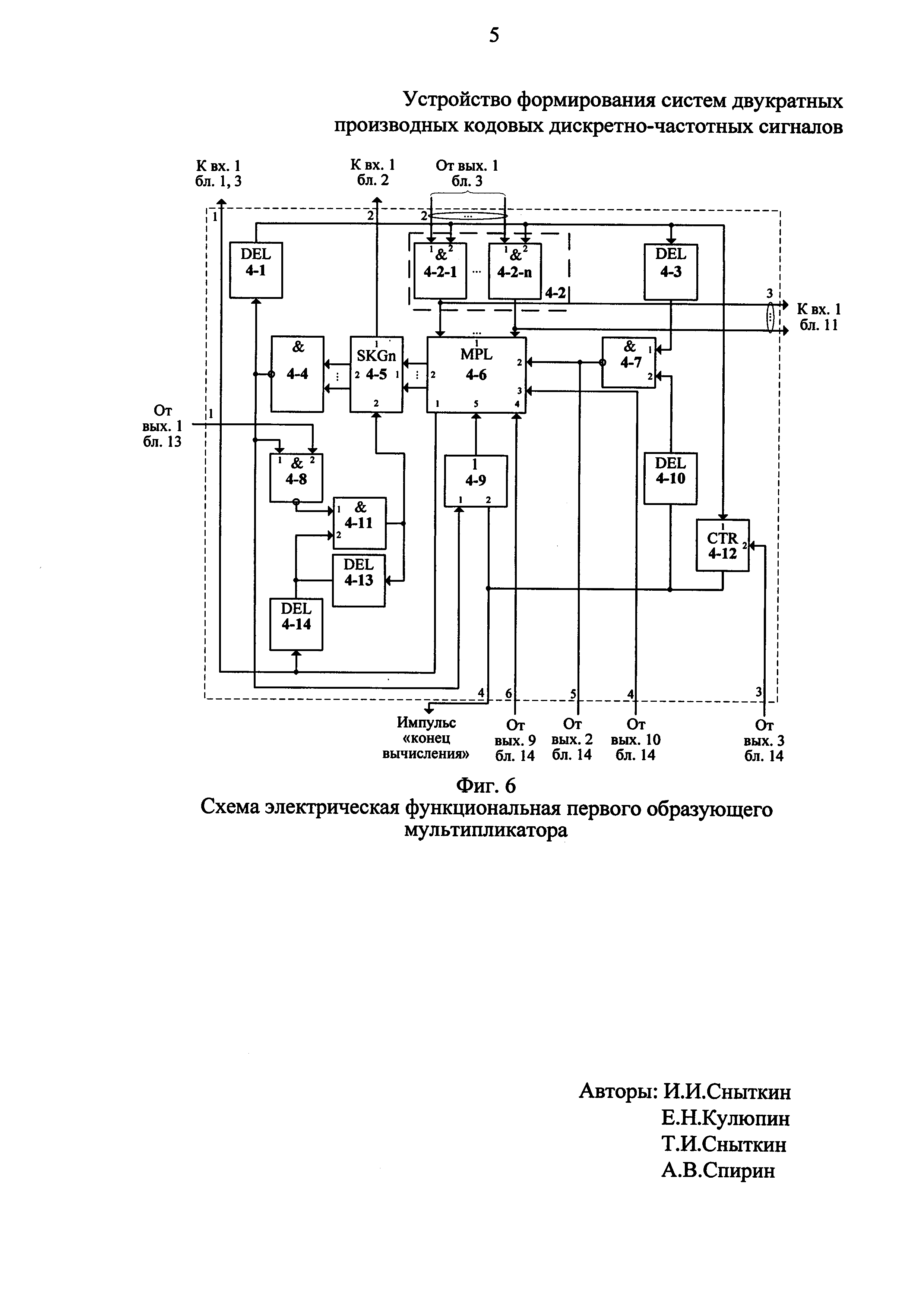

Задержанный импульс с элемента задержки на один такт 14-2 с третьего выхода СБУ 14 поступает на ГТИ 13-9 БФСС ДЧС, схема электрическая функциональная которого представлена на фиг. 7, включая, тем самым, ГТИ 13-9 в работу. Тактовые импульсы с выхода ГТИ 13-9 (см. на фиг. 8б)) проходят через ДПКД 13-10, и с первого выхода БФСС ДЧС 13 поступают на первый вход первого образующего мультипликатора 4, схема электрическая функциональная представлена на фиг. 6. В тактовые моменты, определяемые импульсами БФСС ДЧС 13, первым импульсом с выхода элемента задержки 4-14 открывается элемент «И» 4-11, позволяя тактовому импульсу с выхода элемента «И-НЕ» 4-8 пройти на тактовый вход регистра 4-5 сдвига и элемент 4-13 задержки, который обеспечивает открытие элемента 4-11 «И» в последующие тактовые моменты и прохождение импульсов на тактовый вход регистра 4-5 сдвига. Таким образом, считываемое с регистра 4-5 сдвига число A1=Θx⋅1 в двоичном коде поступает, начиная с младшего разряда, на второй выход записи числа и соответствующий вход формирователя остатков 3, представляющий собой логический узел, состоящий из элементов «И» и «ИЛИ». Тактовые импульсы, поступающие на второй вход элемента «И-НЕ», сопровождают импульсы кода считываемого с регистра 4-5 сдвига числа A1 и поступают на счетчик 1. Выходы счетчика 1 соединены со входами формирователя остатков 2 таким образом, что наличие каждого элемента «И» последнего обуславливается определенным соответствием между состоянием счетчика 1 и последующим разрядом числа. Выходные сигналы формирователя остатков 2 при наличии тактовых импульсов на входе 1 первого образующего мультипликатора 4 запоминаются в регистре 3, имеющем количество разрядов, необходимое для представления наименьшего остатка по модулю p1. При этом каждому триггеру регистра сдвигающего 3 соответствует два элемента «ИЛИ» формирователя остатков 2 (для установки в 0 или 1), причем каждому элементу «ИЛИ» последнего соответствует такое число элементов «И» последнего, сколько возможных ситуаций приводит к переводу триггера в соответствующее состояние. Таким образом, на выходных шинах регистра 3 в каждый тактовый момент появляется двоичный код остатка по модулю p1 от поступившего к этому моменту на вход формирователя остатков 2 двоичного числа. В момент считывания последнего (высшего) разряда числа на выходных шинах регистра 3 появляется код остатка по модулю p1 от числа  В тот же момент регистр 4-5 сдвига обнуляется, и на выходе многовходового элемента «И-НЕ» 4-4 появляется импульс «конец считывания», который поступает на другой вход элемента 4-8 «И-НЕ», прекращая тем самым прохождение тактовых импульсов на тактовый вход регистра 4-5 сдвига и через элемент 4-9 «ИЛИ» на соответствующий вход блока 4-6, приводя в нулевое состояние его регистр множимого. В следующий тактовый момент, пройдя элемент 4-1 задержки, данный импульс поступает на счетный вход счетчика 4-12 числа элементов и на другие входы элементов 4-2 «И», открывая их и обеспечивая считывание с выходных шин регистра 3 в параллельном коде остатка

В тот же момент регистр 4-5 сдвига обнуляется, и на выходе многовходового элемента «И-НЕ» 4-4 появляется импульс «конец считывания», который поступает на другой вход элемента 4-8 «И-НЕ», прекращая тем самым прохождение тактовых импульсов на тактовый вход регистра 4-5 сдвига и через элемент 4-9 «ИЛИ» на соответствующий вход блока 4-6, приводя в нулевое состояние его регистр множимого. В следующий тактовый момент, пройдя элемент 4-1 задержки, данный импульс поступает на счетный вход счетчика 4-12 числа элементов и на другие входы элементов 4-2 «И», открывая их и обеспечивая считывание с выходных шин регистра 3 в параллельном коде остатка  по модулю p1 от числа A1 на третьи выходы кодов остатков и на входы записи множимого числа в регистр блока 4-6 умножения в следующий тактовый момент. Пройдя элемент 4-3 задержки, данный импульс проходит через элемент 4-7 «И-НЕ» на вход «начало умножения» блока 4-6 умножения, обеспечивая умножение множимого числа

по модулю p1 от числа A1 на третьи выходы кодов остатков и на входы записи множимого числа в регистр блока 4-6 умножения в следующий тактовый момент. Пройдя элемент 4-3 задержки, данный импульс проходит через элемент 4-7 «И-НЕ» на вход «начало умножения» блока 4-6 умножения, обеспечивая умножение множимого числа  на множитель Θx. Результат умножения - число

на множитель Θx. Результат умножения - число  записывается в регистр 4-5 сдвига.

записывается в регистр 4-5 сдвига.

Затем повторяется цикл операций, описанный ранее для числа A2, и на выходных третьих шинах образующего мультипликатора 4 появляется код остатка, который в блоке 4-6 умножается на Θх, и в регистр 4-5 сдвига записывается следующий результат  . Затем цикл операций повторяется и так далее. Таким образом, на третьей группе выходов образующего мультипликатора 4 появляется последовательность параллельных двоичных кодов остатков

. Затем цикл операций повторяется и так далее. Таким образом, на третьей группе выходов образующего мультипликатора 4 появляется последовательность параллельных двоичных кодов остатков  представляющая собой последовательность мультипликативной группы GF(p1) или, так называемую, УЧКП-1).

представляющая собой последовательность мультипликативной группы GF(p1) или, так называемую, УЧКП-1).

Работа БФМГ-1 по формированию ЭЧ (кодов остатков) aj(κ) УЧКП-1, описанная выше, является идентичной работе БФМГ-2 по формированию ЭЧ bi(μ) УЧКП-2.

С первым тактовым импульсом от первого выхода БФСС ДЧС 13 (см. фиг. 8б)) первые восьмиразрядные двоичные коды остатков  и

и  поступают одновременно по первым и вторым входам БЦПС 11 соответственно, схема электрическая функциональная которого представлена на фиг. 4. При этом восьмиразрядный двоичный код остатка

поступают одновременно по первым и вторым входам БЦПС 11 соответственно, схема электрическая функциональная которого представлена на фиг. 4. При этом восьмиразрядный двоичный код остатка  параллельно поступает на прямые входы «А» восьми одноразрядных параллельных сумматоров по модулю 11-3.1, 11-3.2, …, 11-3.8 ДПС 11-3, а на их входы «В» - восьмиразрядный двоичный код остатка

параллельно поступает на прямые входы «А» восьми одноразрядных параллельных сумматоров по модулю 11-3.1, 11-3.2, …, 11-3.8 ДПС 11-3, а на их входы «В» - восьмиразрядный двоичный код остатка  С первым и последующим тактовыми импульсами от первого выхода БФСС ДЧС 13 на входы «М» девяти одноразрядных параллельных сумматоров по модулю 11-3.1, 11-3.2, …, 11-3.9 будет поступать девятиразрядный двоичный «код модуля числа», считываемый с МБР 14-17 и 14-19, находящиеся в режиме «считывания информации». При этом на входы «А» и «В» одноразрядного параллельного сумматора по модулю 11-3.9 ДПС 11-3, как и на вход «Ph» (где h∈N) первого одноразрядного сумматора по модулю 11-3.1, с выхода инвертора 11-2 поступает «логический ноль», а на вход PMh первого одноразрядного параллельного сумматора по модулю 11-18 поступает «логическая единица». Таким образом, на первой группе выходов БЦПС 11 появится результат суммирования кодов остатков

С первым и последующим тактовыми импульсами от первого выхода БФСС ДЧС 13 на входы «М» девяти одноразрядных параллельных сумматоров по модулю 11-3.1, 11-3.2, …, 11-3.9 будет поступать девятиразрядный двоичный «код модуля числа», считываемый с МБР 14-17 и 14-19, находящиеся в режиме «считывания информации». При этом на входы «А» и «В» одноразрядного параллельного сумматора по модулю 11-3.9 ДПС 11-3, как и на вход «Ph» (где h∈N) первого одноразрядного сумматора по модулю 11-3.1, с выхода инвертора 11-2 поступает «логический ноль», а на вход PMh первого одноразрядного параллельного сумматора по модулю 11-18 поступает «логическая единица». Таким образом, на первой группе выходов БЦПС 11 появится результат суммирования кодов остатков  и

и  по соответствующему «коду модуля числа» - ЭЧ ДК ПУЧКП АТ

по соответствующему «коду модуля числа» - ЭЧ ДК ПУЧКП АТ  формируемой ДК ПУЧКП АТ

формируемой ДК ПУЧКП АТ  Кроме этого восьмиразрядный двоичный код остатка

Кроме этого восьмиразрядный двоичный код остатка  параллельно поступает и на третьи входы регистров сдвигающих 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, последовательно перезаписываемый из триггера в триггер по фронту с каждым тактовым импульсом от выхода 1 БФСС ДЧС, что соответствующим образом происходит и с восьмиразрядным двоичным кодом остатка

параллельно поступает и на третьи входы регистров сдвигающих 11-1.1, 11-1.3, 11-1.5, 11-1.7, 11-1.9, 11-1.11, 11-1.13, 11-1.15, последовательно перезаписываемый из триггера в триггер по фронту с каждым тактовым импульсом от выхода 1 БФСС ДЧС, что соответствующим образом происходит и с восьмиразрядным двоичным кодом остатка  поступающего на третьи входы регистров сдвигающих 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15.

поступающего на третьи входы регистров сдвигающих 11-4.1, 11-4.3, 11-4.5, 11-4.7, 11-4.9, 11-4.11, 11-4.13, 11-4.15.

Поступление кодов остатков  в восьмиразрядном двоичном коде на первые входы ДПС 11-3 с первого образующего мультипликатора 4 продолжается до тех пор, пока счетчик 4-12 числа элементов, на первый (счетный) вход которого поступают импульсы «момент считывания

в восьмиразрядном двоичном коде на первые входы ДПС 11-3 с первого образующего мультипликатора 4 продолжается до тех пор, пока счетчик 4-12 числа элементов, на первый (счетный) вход которого поступают импульсы «момент считывания  », не переполнится и не выдаст импульс переполнения «конец формирования», поступающий на выход 4 и через элемент 4-9 «ИЛИ» на соответствующий вход блока 4-6 умножения, обнуляя его регистр множимого, в котором был к этому моменту записан код последнего остатка, а также через элемент 4-10 задержки на второй вход элемента 4-7 «И-НЕ», запрещая прохождение импульса с выхода элемента 4-3 задержки на вход «начало умножения» блока 4-6 умножения. Таким образом, БФМГ-1, подготавливается к новому циклу вычислений и формирования последовательности кодов остатков

», не переполнится и не выдаст импульс переполнения «конец формирования», поступающий на выход 4 и через элемент 4-9 «ИЛИ» на соответствующий вход блока 4-6 умножения, обнуляя его регистр множимого, в котором был к этому моменту записан код последнего остатка, а также через элемент 4-10 задержки на второй вход элемента 4-7 «И-НЕ», запрещая прохождение импульса с выхода элемента 4-3 задержки на вход «начало умножения» блока 4-6 умножения. Таким образом, БФМГ-1, подготавливается к новому циклу вычислений и формирования последовательности кодов остатков  Аналогичным образом происходит формирование последовательности параллельных восьмиразрядных двоичных кодов остатков

Аналогичным образом происходит формирование последовательности параллельных восьмиразрядных двоичных кодов остатков  на третьих выходах второго образующего мультипликатора 9 БФМГ-2. При этом каждая мультипликативная группа полей GF(p1) и GF(p2) поразрядно запишется в соответствующие группы регистров сдвиговых первого 11-1 и второго 11-4 узла хранения кодов остатков.

на третьих выходах второго образующего мультипликатора 9 БФМГ-2. При этом каждая мультипликативная группа полей GF(p1) и GF(p2) поразрядно запишется в соответствующие группы регистров сдвиговых первого 11-1 и второго 11-4 узла хранения кодов остатков.

В очередные тактовые моменты от первого выхода БФСС ДЧС 13, вслед за последним восьмиразрядным кодом остатка  на входы «А» восьми одноразрядных параллельных сумматоров по модулю с 11-3.1 по 11-3.8 ДПС 11-3, с выходов мультиплексоров 11-1.2, 11-1.4, 11-1.6, 11-1.8, 11-1.10, 11-1.12, 11-1.14 и 11-1.16, в соответствии с поданными на эти мультиплексоры двоичным восьмиразрядным кодом C0…C7, циклически поэлементно будет поступать мультипликативная группа

на входы «А» восьми одноразрядных параллельных сумматоров по модулю с 11-3.1 по 11-3.8 ДПС 11-3, с выходов мультиплексоров 11-1.2, 11-1.4, 11-1.6, 11-1.8, 11-1.10, 11-1.12, 11-1.14 и 11-1.16, в соответствии с поданными на эти мультиплексоры двоичным восьмиразрядным кодом C0…C7, циклически поэлементно будет поступать мультипликативная группа  в восьмиразрядном двоичном коде начиная с

в восьмиразрядном двоичном коде начиная с  Аналогичная работа будет происходить и с мультипликативной группой

Аналогичная работа будет происходить и с мультипликативной группой  поля GF(p2), ЭЧ которой, начиная с

поля GF(p2), ЭЧ которой, начиная с  будут поступать на входы «В» восьми одноразрядных параллельных сумматоров по модулю. Циклы поступления кодов остатков

будут поступать на входы «В» восьми одноразрядных параллельных сумматоров по модулю. Циклы поступления кодов остатков  поля GF(p1) в восьмиразрядном двоичном коде, так же как кодов остатков

поля GF(p1) в восьмиразрядном двоичном коде, так же как кодов остатков  поля GF(p2) в восьмиразрядном двоичном коде соответственно на первые и третьи входы ДПС 11-3 будут продолжаться до тех пор, пока при последнем тактовом импульсе от ДПКД 13-10 не произойдет одновременного поступления и сложения по модулю кодов остатков

поля GF(p2) в восьмиразрядном двоичном коде соответственно на первые и третьи входы ДПС 11-3 будут продолжаться до тех пор, пока при последнем тактовом импульсе от ДПКД 13-10 не произойдет одновременного поступления и сложения по модулю кодов остатков  и

и

При всех тактовых импульсах от ДПКД 13-10 (число которых равняется длине L формируемой ДК ПУЧКП АТ) все ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  в восьмиразрядном двоичном коде последовательно будут поступают с группы выходов 1 БЦПС (или группы выходов 1 БФ ДК ПУЧКП АТ 12) на входы дешифратора 13-3 БФСС ДЧС 13. Дешифратор 13-3 преобразует двоичный девятиразрядный код каждого ЭЧ

в восьмиразрядном двоичном коде последовательно будут поступают с группы выходов 1 БЦПС (или группы выходов 1 БФ ДК ПУЧКП АТ 12) на входы дешифратора 13-3 БФСС ДЧС 13. Дешифратор 13-3 преобразует двоичный девятиразрядный код каждого ЭЧ  ДК ПУЧКП АТ в сигнал (импульс) только на одном из своих выходов. Этот сигнал (импульс) поступает на управляющие входы распределителя 13-4 и через схему «ИЛИ» 13-6 на первый вход схемы «И» 13-7. При этом на вход АЦП 13-11 с выхода источника дискретной информации 13-8 поступает последовательность информационных импульсов от N-источников сообщений, уплотненных по времени.

ДК ПУЧКП АТ в сигнал (импульс) только на одном из своих выходов. Этот сигнал (импульс) поступает на управляющие входы распределителя 13-4 и через схему «ИЛИ» 13-6 на первый вход схемы «И» 13-7. При этом на вход АЦП 13-11 с выхода источника дискретной информации 13-8 поступает последовательность информационных импульсов от N-источников сообщений, уплотненных по времени.

АЦП 13-11 преобразует длительность информационного импульса в цифровой код, который поступает на группу третьих входов ДПКД 13-10. Причем на первый вход ДПКД 13-10 подаются импульсы от генератора 13-9 тактовых импульсов, а на второй вход - восьмиразрядный двоичный «код числа ЭЧ ДК ПУЧКП АТ». ДПКД 13-10, в соответствии с поступившим на его входы цифровым кодом с выхода АЦП 13-11 и восьмиразрядным двоичным «кодом числа элементов ДК ПУЧКП АТ», изменяет коэффициент деления и выдает последовательность импульсов с измененным в соответствии с числом элементов ДК ПУЧКП АТ периодом их следования. Последовательность импульсов с выхода ДПКД 13-10 является тактовыми импульсами для счетчиков 1 и 6, регистров 3 и 8, и образующих мультипликаторов 4 и 9 блоков 5 и 10 формирования УЧКП-1 и УЧКП-2 соответственно. Также эти импульсы проходят через элемент 13-7 «И», открытый сигналом с выхода элемента 13-6 «ИЛИ», на выходы распределителя 13-4 через его второй вход в такой последовательности, которая определяется номером входа распределителя 13-4, на котором существует сигнал дешифратора 13-3. С соответствующих выходов распределителя 13-4 импульсы в последовательности, соответствующей определенному ЭЧ  ДК ПУЧКП АТ, поступают на первые входы группы ключевых схем 13-2, на вторые входы которых постоянно подаются сигналы с элементов 13-1-n синтезатора частот 13-1, а на третьи - сигнал с выхода источника дискретной информации 13-8. Синтезатор частот 13-1 представляет собой совокупность генераторов высокостабильных частот 13-1-n. Каждому информационному импульсу на выходе источника дискретной информации 13-8 соответствует определенное ЭЧ

ДК ПУЧКП АТ, поступают на первые входы группы ключевых схем 13-2, на вторые входы которых постоянно подаются сигналы с элементов 13-1-n синтезатора частот 13-1, а на третьи - сигнал с выхода источника дискретной информации 13-8. Синтезатор частот 13-1 представляет собой совокупность генераторов высокостабильных частот 13-1-n. Каждому информационному импульсу на выходе источника дискретной информации 13-8 соответствует определенное ЭЧ  ДК ПУЧКП АТ на выходе дешифратора 13-3, и, следовательно, как было указано выше, и определенный порядок распределения импульсов с выхода ДПКД 13-10 по выходам распределителя 13-4.

ДК ПУЧКП АТ на выходе дешифратора 13-3, и, следовательно, как было указано выше, и определенный порядок распределения импульсов с выхода ДПКД 13-10 по выходам распределителя 13-4.

Таким образом, ключевые схемы 13-2-n будут открываться поочередно в порядке, определенном для каждого информационного импульса и соответствующего конкретному ЭЧ  ДК ПУЧКП АТ, пропуская на второй выход через элемент n-входовый элемент 13-5 «ИЛИ» одну из частот гармонических колебаний синтезатора частоты 13-1. Очередность открывания ключевых схем 13-4 определяет структуру ДЧС, соответствующую ДК ПУЧКП АТ

ДК ПУЧКП АТ, пропуская на второй выход через элемент n-входовый элемент 13-5 «ИЛИ» одну из частот гармонических колебаний синтезатора частоты 13-1. Очередность открывания ключевых схем 13-4 определяет структуру ДЧС, соответствующую ДК ПУЧКП АТ  и этот порядок определяется: первообразными элементами Θx и Θy соответственно полей GF(p1) и GF(p2); простыми числами p1, р2 и р3; длительностью информационной посылки Т. Таким образом, каждой определенной информационной посылке будет соответствовать свой определенный сложный сигнал.

и этот порядок определяется: первообразными элементами Θx и Θy соответственно полей GF(p1) и GF(p2); простыми числами p1, р2 и р3; длительностью информационной посылки Т. Таким образом, каждой определенной информационной посылке будет соответствовать свой определенный сложный сигнал.

Устройство формирования систем ДК ПКДЧС может работать в 8 режимах. Количество режимов работы устройства определяется непосредственно работой БФСС ДЧС устройства, которая (как указывалось выше) зависит от длительностей Т поступающих в этот блок информационных посылок, а также ТВС и длин ДК ПУЧКП АТ

В режиме 1.1 (при фиксированных значениях длительностей Т информационных посылок с изменением значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходит изменение последовательности поступления кодов ЭЧ  ДК ПУЧКП АТ

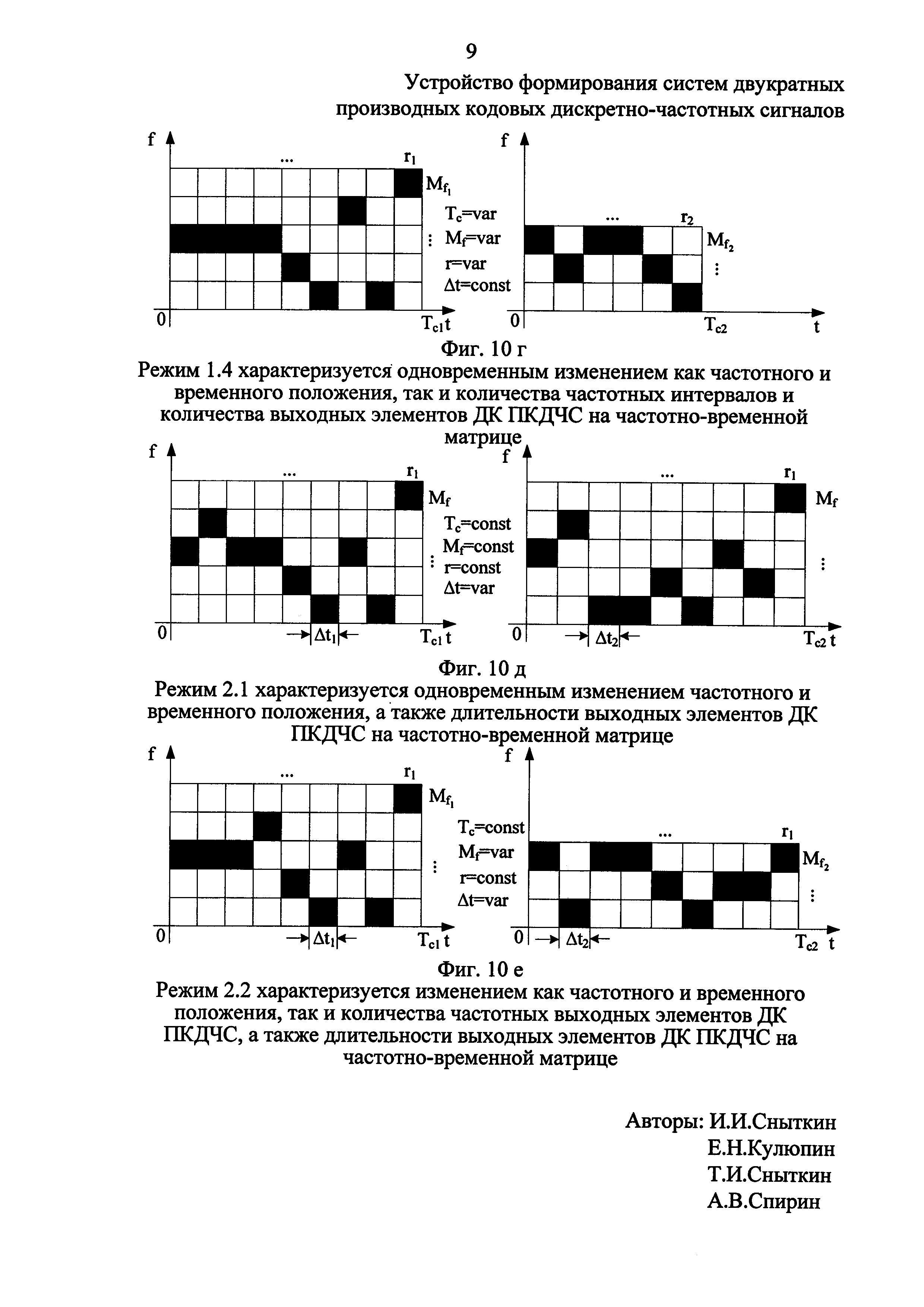

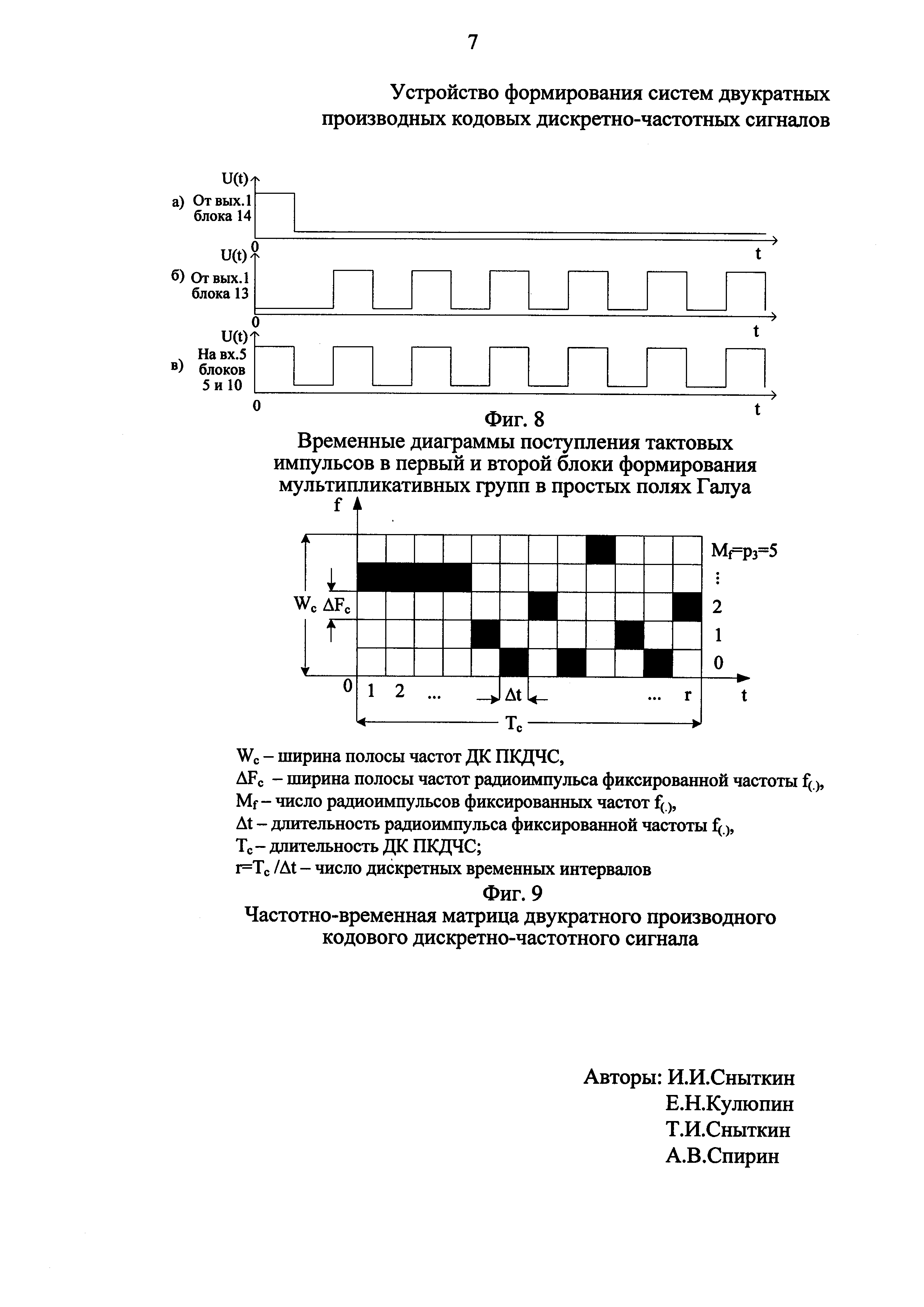

ДК ПУЧКП АТ  фиксированной длины на входы дешифратора 13-3. Это приводит к тому, что управляющие работой распределителя 13-4 сигналы (импульсы) будут появляться на различных выходах дешифратора 13-3, то есть на различных входах распределителя, а это изменяет режим работы распределителя 13-4, который будет распределять импульсы в различных последовательностях, а, следовательно, коммутировать группу схем 13-2 «И» в различной последовательности, что и приведет к изменению частотного и временного положения выходных элементов ДК ПКДЧС на частотно-временной матрице (ЧВМ) (см. фиг. 10а).

фиксированной длины на входы дешифратора 13-3. Это приводит к тому, что управляющие работой распределителя 13-4 сигналы (импульсы) будут появляться на различных выходах дешифратора 13-3, то есть на различных входах распределителя, а это изменяет режим работы распределителя 13-4, который будет распределять импульсы в различных последовательностях, а, следовательно, коммутировать группу схем 13-2 «И» в различной последовательности, что и приведет к изменению частотного и временного положения выходных элементов ДК ПКДЧС на частотно-временной матрице (ЧВМ) (см. фиг. 10а).

В режиме 1.2 (при фиксированных значениях длительностей Т информационных посылок с изменением значений простого числа p3 (в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем с изменением значений простого числа p3 количество значений кодов ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  фиксированной длины, поступающих на входы дешифратора 13-3, будут ограничиваться изменяющимися значениями простого числа p3, что, соответственно, приведет к изменению (увеличению или уменьшению) количества подключаемых распределителем 13-4 схем «И» из группы 13-2 ключевых схем. Следовательно, в данном режиме происходит изменение как частотного и временного положения, так и количества частотных выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10б).

фиксированной длины, поступающих на входы дешифратора 13-3, будут ограничиваться изменяющимися значениями простого числа p3, что, соответственно, приведет к изменению (увеличению или уменьшению) количества подключаемых распределителем 13-4 схем «И» из группы 13-2 ключевых схем. Следовательно, в данном режиме происходит изменение как частотного и временного положения, так и количества частотных выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10б).

В режиме 1.3 (при фиксированных значениях длительностей Т информационных посылок с изменением кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  (в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем в результате изменения кода числа ЭЧ

(в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем в результате изменения кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  изменяются как период следования импульсов от делителя ДПКД 13-10, которые являются тактовыми импульсами для образующих мультипликаторов 4 и 9, счетчиков 1 и 6, регистров 3 и 8, распределителя 13-4 и БЦПС 11 (см. фиг. 8б)), так и коды числа элементов поля GF(p1) и GF(p2), что в целом приводит к уменьшению или увеличению числа ЭЧ

изменяются как период следования импульсов от делителя ДПКД 13-10, которые являются тактовыми импульсами для образующих мультипликаторов 4 и 9, счетчиков 1 и 6, регистров 3 и 8, распределителя 13-4 и БЦПС 11 (см. фиг. 8б)), так и коды числа элементов поля GF(p1) и GF(p2), что в целом приводит к уменьшению или увеличению числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  (или длины ДК ПУЧКП АТ

(или длины ДК ПУЧКП АТ  ), поступающих на входы дешифратора 13-3 с БЦПС 11. В связи с этим, распределитель 13-4 будет подключать большее или меньшее количество схем «И» из группы 13-2 ключевых схем во время фиксированной длительности Т информационной посылки, а, следовательно, в данном режиме происходит изменение как частотного и временного положения, так и количества частотных интервалов выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10в).

), поступающих на входы дешифратора 13-3 с БЦПС 11. В связи с этим, распределитель 13-4 будет подключать большее или меньшее количество схем «И» из группы 13-2 ключевых схем во время фиксированной длительности Т информационной посылки, а, следовательно, в данном режиме происходит изменение как частотного и временного положения, так и количества частотных интервалов выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10в).

В режиме 1.4 (при фиксированных значениях длительностей Т информационных посылок с одновременным изменением кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  и значений простого числа p3 (в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят одновременно процессы, описанные в режимах 1.1, 1.2 и 1.3. Следовательно, в режиме 1.4 происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов и количества выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10г).

и значений простого числа p3 (в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят одновременно процессы, описанные в режимах 1.1, 1.2 и 1.3. Следовательно, в режиме 1.4 происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов и количества выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10г).

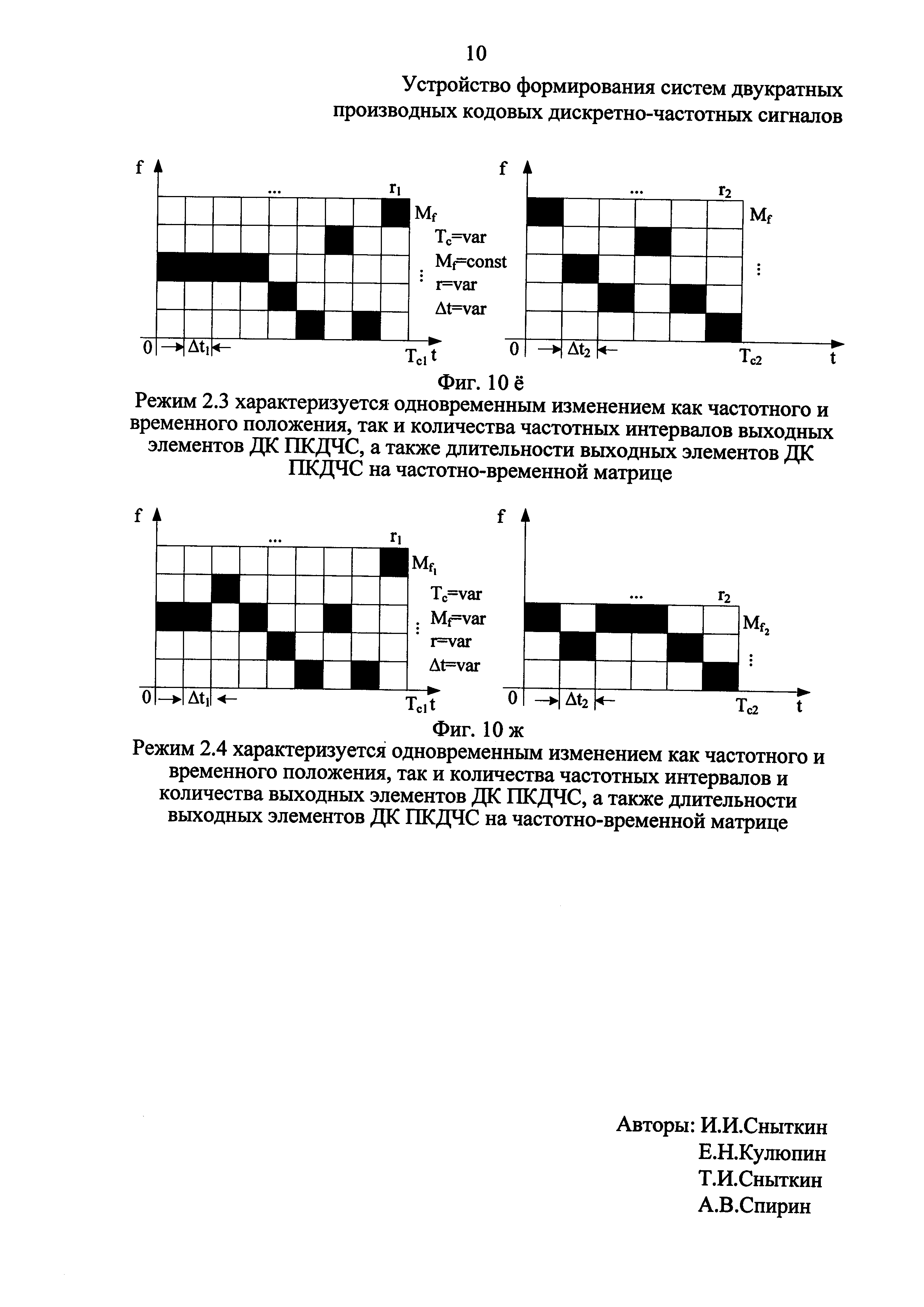

В режиме 2.1 (при изменении длительности Т информационных посылок с изменением значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем в результате изменения длительности Т информационных посылок изменится цифровой код на выходах АЦП 13-11, который является управляющим для ДПКД 13-10. В связи с этим изменится коэффициент деления ДПКД 13-10, а, следовательно, изменится частота следования выходных импульсов ДПКД 13-10. Соответственно изменится фактическое время подключения группы ключевых схем 13-2 «И», и, как следствие, фактическое время генерирования частот синтезатором частот 13-1. Следовательно, в режиме 2.1 происходит одновременное изменение частотного и временного положения выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10д).

В режиме 2.2 (при изменении длительности Т информационных посылок с изменением значений простого числа p3 (в том числе и в случае изменения значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем с изменением значений простого числа p3 количество значений кодов ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  фиксированной длины, поступающих на входы дешифратора 13-3, будут ограничиваться изменяющимися значениями простого числа p3, что, соответственно, приведет к изменению (увеличению или уменьшению) количества подключаемых распределителем 13-4 схем «И» из группы 13-2 ключевых схем. При этом код на выходах АЦП 13-11, при изменении длительности Т информационных посылок, изменит коэффициент деления ДПКД 13-10, что приведет к фактическому изменению времени подключения схем «И» из группы 13-2 ключевых схем, а, следовательно, и фактическое время генерирования частот. Следовательно, в данном режиме происходит одновременное изменение как частотного и временного положения, так и количества частотных выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10е).

фиксированной длины, поступающих на входы дешифратора 13-3, будут ограничиваться изменяющимися значениями простого числа p3, что, соответственно, приведет к изменению (увеличению или уменьшению) количества подключаемых распределителем 13-4 схем «И» из группы 13-2 ключевых схем. При этом код на выходах АЦП 13-11, при изменении длительности Т информационных посылок, изменит коэффициент деления ДПКД 13-10, что приведет к фактическому изменению времени подключения схем «И» из группы 13-2 ключевых схем, а, следовательно, и фактическое время генерирования частот. Следовательно, в данном режиме происходит одновременное изменение как частотного и временного положения, так и количества частотных выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10е).

В режиме 2.3 (при изменении длительности Т информационных посылок с изменением кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  (в том числе при изменении значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем в результате изменения кода числа ЭЧ

(в том числе при изменении значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят процессы, описанные в режиме 1.1, причем в результате изменения кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  изменяются как период следования импульсов от делителя ДПКД 13-10, так и коды числа элементов поля GF(p1) и GF(p2), что в целом приводит к уменьшению или увеличению числа ЭЧ

изменяются как период следования импульсов от делителя ДПКД 13-10, так и коды числа элементов поля GF(p1) и GF(p2), что в целом приводит к уменьшению или увеличению числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  (или длины ДК ПУЧКП АТ

(или длины ДК ПУЧКП АТ  поступающих на входы дешифратора 13-3 от БЦПС 11. В связи с этим, распределитель 13-4 будет подключать большее или меньшее количество схем «И» из группы 13-2 ключевых схем во время изменения длительности Т информационной посылки. Следовательно, в данном режиме происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10ё).

поступающих на входы дешифратора 13-3 от БЦПС 11. В связи с этим, распределитель 13-4 будет подключать большее или меньшее количество схем «И» из группы 13-2 ключевых схем во время изменения длительности Т информационной посылки. Следовательно, в данном режиме происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10ё).

В режиме 2.4 (при изменении длительности Т информационных посылок с одновременным изменением кода числа ЭЧ  ДК ПУЧКП АТ

ДК ПУЧКП АТ  и значений простого числа р3 (в том числе при изменении значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят одновременно процессы, описанные в режимах 2.1, 2.2 и 2.3. Следовательно, в режиме 2.4 происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов и количества выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10ж).

и значений простого числа р3 (в том числе при изменении значений первообразных корней Θx и (или) Θy соответствующих полей GF(p1) и GF(p2)) происходят одновременно процессы, описанные в режимах 2.1, 2.2 и 2.3. Следовательно, в режиме 2.4 происходит одновременное изменение как частотного и временного положения, так и количества частотных интервалов и количества выходных элементов ДК ПКДЧС, а также длительности выходных элементов ДК ПКДЧС на ЧВМ (см. фиг. 10ж).

Технический результат, достигаемый при реализации изобретения, заключается в возможности увеличения количества реализаций баз В сложного сигнала (в виде ДК ПКДЧС) с 23 до 30, то есть В={16, 36, 100, 144, 256, 324, 400, 484, 784, 900, 1296, 1600, 1764, 1936, 2116, 2304, 2704, 3364, 3600, 4356, 4900, 5184, 6084, 6400, 6724, 7056, 8100, 8464, 9216, 10000} одним функционально законченным устройством. Причем реализация таких значений баз В сложного сигнала требует относительно невысоких значений исходных данных (значений простых чисел). Например, для реализации В=900 не требуется более значений простого числа р=31, а достаточно иметь набор простых чисел p1=7 и p2=11. Например, для больших значений баз В=4356 вместо значения простого числа р=67 достаточно набора простых чисел p1=7 и р2=23. Отсюда очевидно, что для формирования сложного сигнала заданной базы потребуется сравнительно небольшой набор значений простых чисел, что соответственно приводит к кратному уменьшению числа ячеек памяти (регистров) для хранения значений простых чисел до 101 включительно. Изобретение также позволяет формировать объем V ансамбля кодовых форм сложного сигнала при фиксированной его длительности в кратное число раз больше, чем длина М-ичной ПСП, на основе которой формируется сложный сигнал, в том числе по сравнению с техническими возможностями прототипа. Например, при длине L=36 ДК ПУЧКП АТ (где p1=19, р2=5) объем ансамблей кодовых форм ДК ПКДЧС равен V=864, тогда как прототип при той же длине М-ичной ПСП (то есть при длине УЧКП  ) формирует объем ансамблей кодовых ДЧС размером V1=36. При таких значениях объемов, например, значение имитостойкости сложного сигнала формируемого изобретением равен Ic=f(V)=log2V=log2(24V1)≈9,7, нежели прототипом - Iпр≈5,1 (то есть Iс≈2⋅Iпр).

) формирует объем ансамблей кодовых ДЧС размером V1=36. При таких значениях объемов, например, значение имитостойкости сложного сигнала формируемого изобретением равен Ic=f(V)=log2V=log2(24V1)≈9,7, нежели прототипом - Iпр≈5,1 (то есть Iс≈2⋅Iпр).

Отсюда очевидно, что предпочтение при решении вопросов о повышении помехоустойчивости, скрытности и имитостойкости следует отдавать предлагаемому устройству.

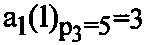

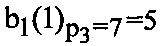

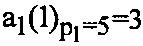

Рассмотрим работу устройства для формирования одной кодовой формы ДК ПУЧКП АТ на примере.

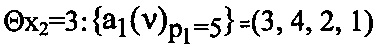

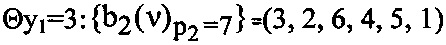

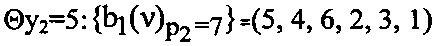

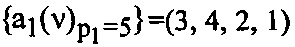

Пусть p1=7, p2=5, а p3=р2=5. Тогда первообразными корнями при выбранных p1 и р2 в GF(11) и GF(13) будут соответственно Θx={2, 3} и Θy={3, 5}.

Справочно: На основе изоморфных преобразований первообразных корней Θx={2, 3} и Θy={3, 5} соответственно в GF(5) и GF(7) системы УЧКП-1 и УЧКП-2 будут иметь следующий вид:

- неинверсная УЧКП-1;

- неинверсная УЧКП-1;

- инверсная УЧКП-1;

- инверсная УЧКП-1;

- неинверсная УЧКП-2;

- неинверсная УЧКП-2;

- инверсная УЧКП-2.

- инверсная УЧКП-2.