Результат интеллектуальной деятельности: МНОГОФУНКЦИОНАЛЬНЫЙ ТОКОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Вид РИД

Изобретение

Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах, устройствах передачи информации и системах связи.

В вычислительных и управляющих системах сегодня широко используются потенциальные логические элементы «И», «ИЛИ», «НЕ» и др., работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующиеся низким и высоким потенциалами [1-47].

Кроме этого, достаточно перспективны цифровые элементы «И», «ИЛИ», «НЕ», «Сравнение x1>x2» и др. с входными и выходными токовыми логическими переменными, на основе которых могут быть реализованы различные спецвычислители и СФ-блоки ЭВМ, работающие на принципах линейной (не булевой) алгебры [48-65].

В монографии [66], а также работах соавтора настоящей заявки [67, 68] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство относится к этому типу цифровых устройств.

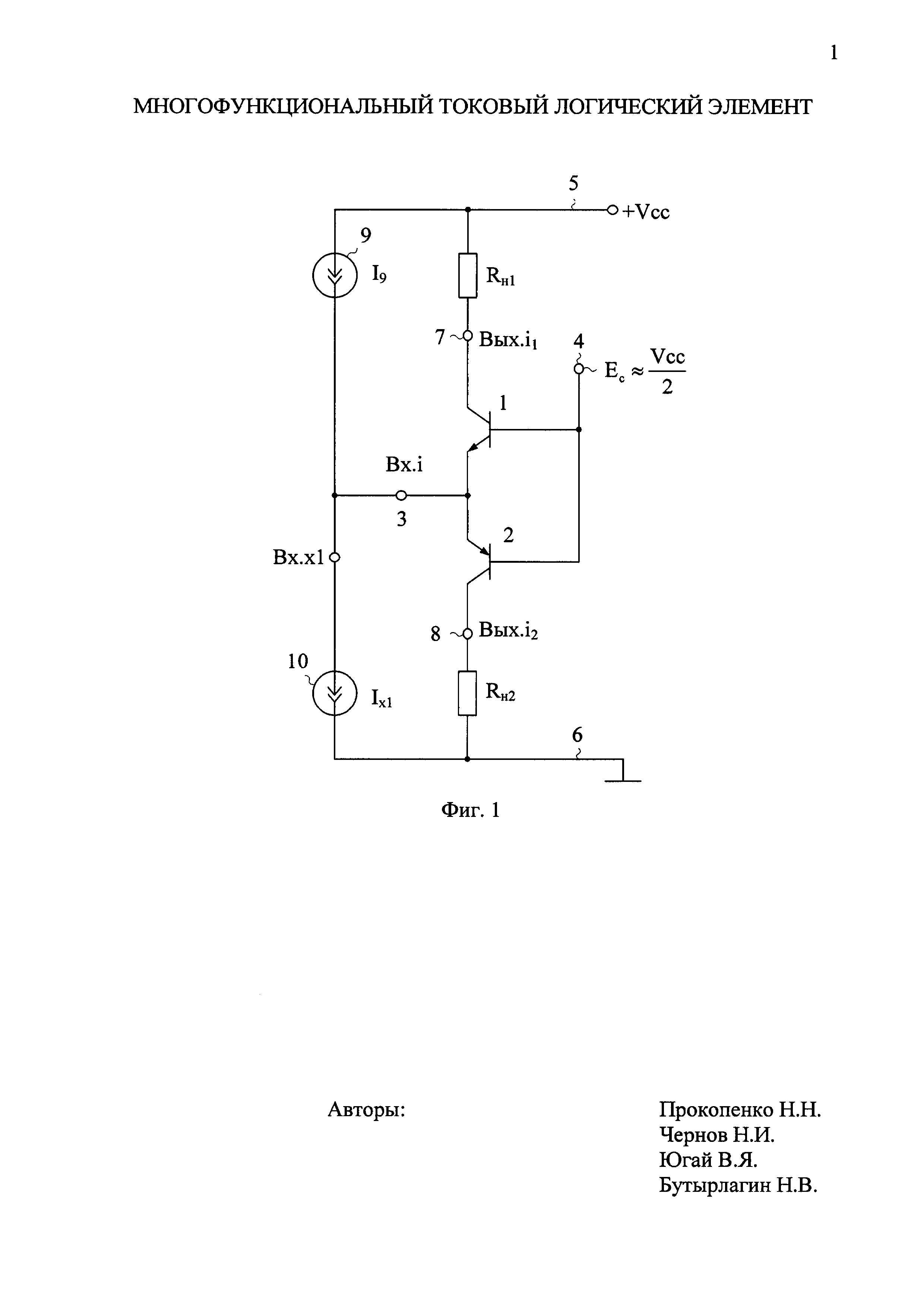

Ближайшим прототипом заявляемого устройства является токовый логический элемент «2И», представленный в патенте RU 2513717. Он содержит (фиг. 1) первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, источник вспомогательного напряжения 4, связанный с базами первого 1 и второго 2 входных транзисторов, первую 5 шину источника питания, к которой подключен коллектор первого 1 входного транзистора, вторую 6 шину источника питания, к которой подключен коллектор второго 2 входного транзистора, первый 7 и второй 8 токовые выходы устройства, первый 9 и второй 10 источники входных токов, связанные с токовым входом 3 устройства. Причем первый 9 источник входного тока в схеме-прототипе включает линейный элемент, реализованный на основе токового зеркала, которое «повторяет» с инверсией сигнал входной логической переменной.

Существенный недостаток известного логического устройства состоит в том, что на его основе не реализуются основные логические функции, соответствующие операциям «НЕ», «ИЛИ», «И», «Сравнение x1>x2» и др.

Основная задача предлагаемого изобретения состоит в создании устройства, которое в рамках одной и той же архитектуры может реализовывать основные логические операции ЭВМ «И», «ИЛИ», «НЕ», «Сравнение x1>x2», а также нормализацию входных токовых логических переменных, т.е. выполнять функции многофункционального токового логического элемента. В конечном итоге это позволяет унифицировать (сделать более универсальной) структуру базового цифрового IP модуля ЭВМ и создать элементную базу вычислительных устройств, работающих на принципах линейной алгебры [67, 68].

Поставленная задача решается тем, что в токовом логическом элементе (фиг. 1), содержащем первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, источник вспомогательного напряжения 4, связанный с базами первого 1 и второго 2 входных транзисторов, первую 5 шину источника питания, к которой подключен коллектор первого 1 входного транзистора, вторую 6 шину источника питания, к которой подключен коллектор второго 2 входного транзистора, первый 7 и второй 8 токовые выходы устройства, первый 9 и второй 10 источники входных токов, связанные с токовым входом 3 устройства, предусмотрены новые элементы и связи - в схему введен компаратор напряжений 11, первый 12 вход которого соединен с объединенными эмиттерами первого 1 и второго 2 входных транзисторов, второй 13 вход связан с источником вспомогательного напряжения 4, а противофазные первый 14 и второй 15 токовые выходы компаратора напряжений 11 связаны с соответствующими первым 7 и вторым 8 токовыми выходами устройства.

На фиг. 1 представлена схема логического элемента-прототипа «2И».

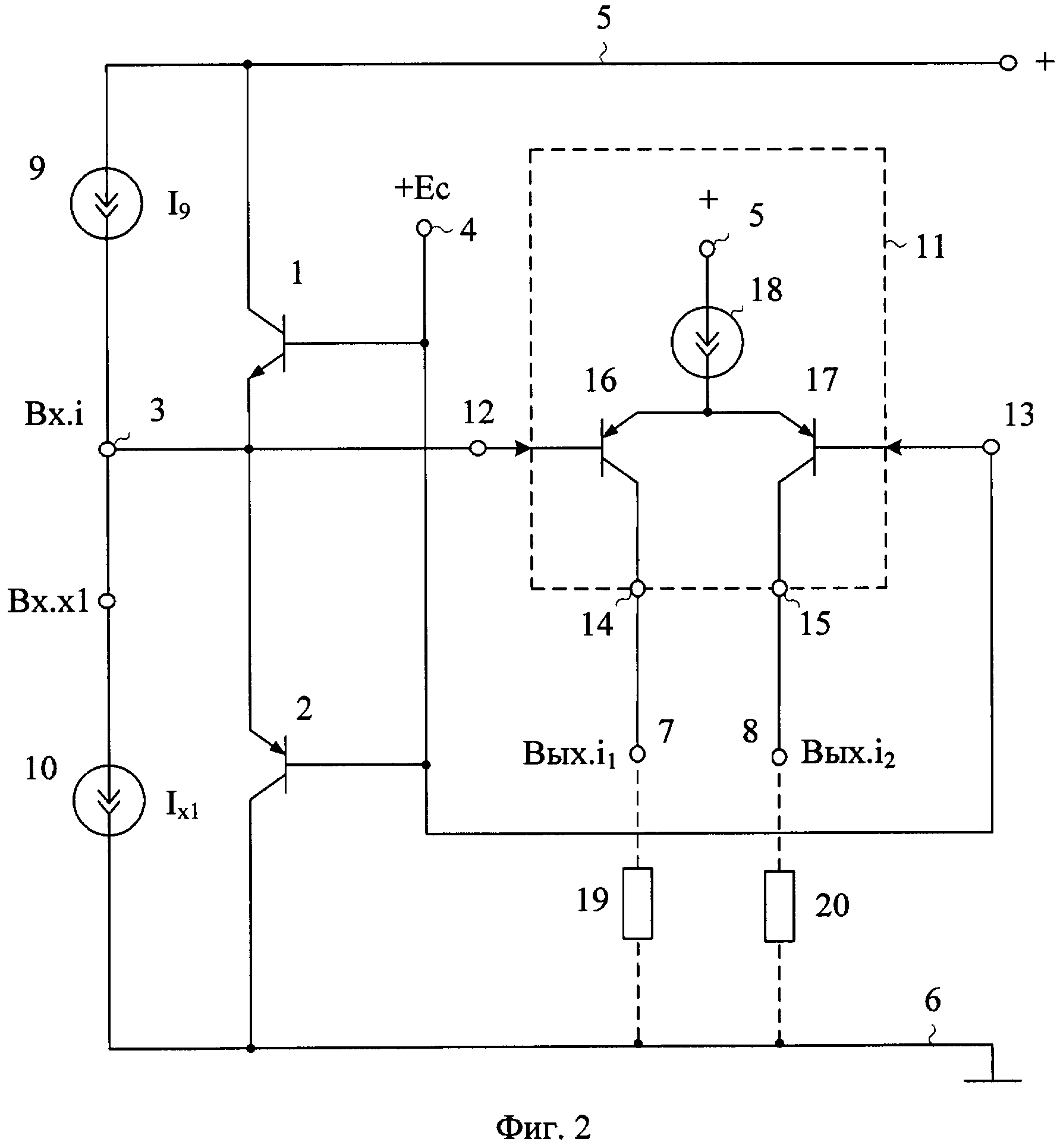

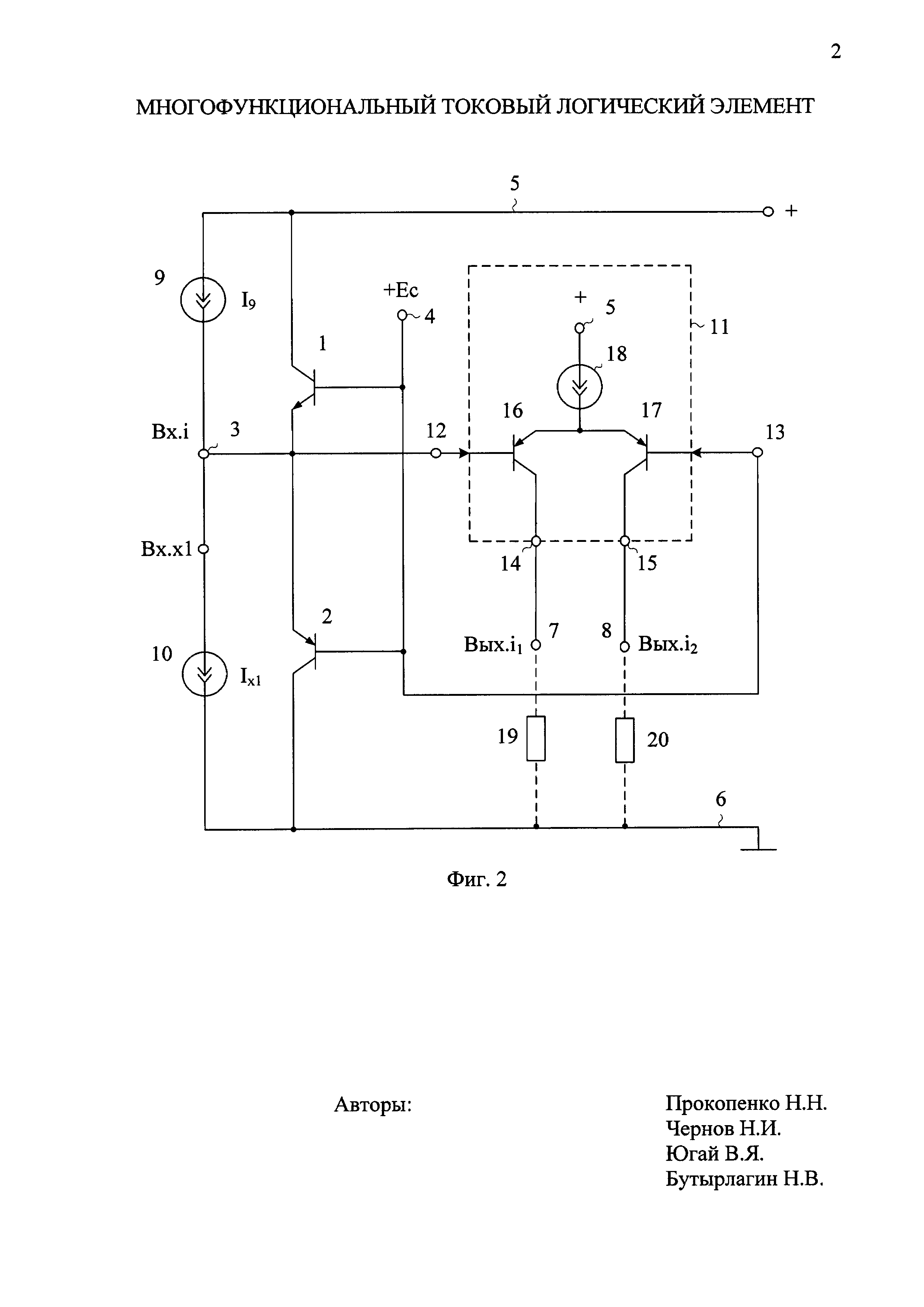

На фиг. 2 представлена схема заявляемого устройства в соответствии с пп. 1, 2, 3 формулы изобретения. При этом п. 2 формулы изобретения характеризует вариант включения токовых выходов 7 и 8 устройства, а п. 3 описывает внутреннюю структуру компаратора напряжения 11.

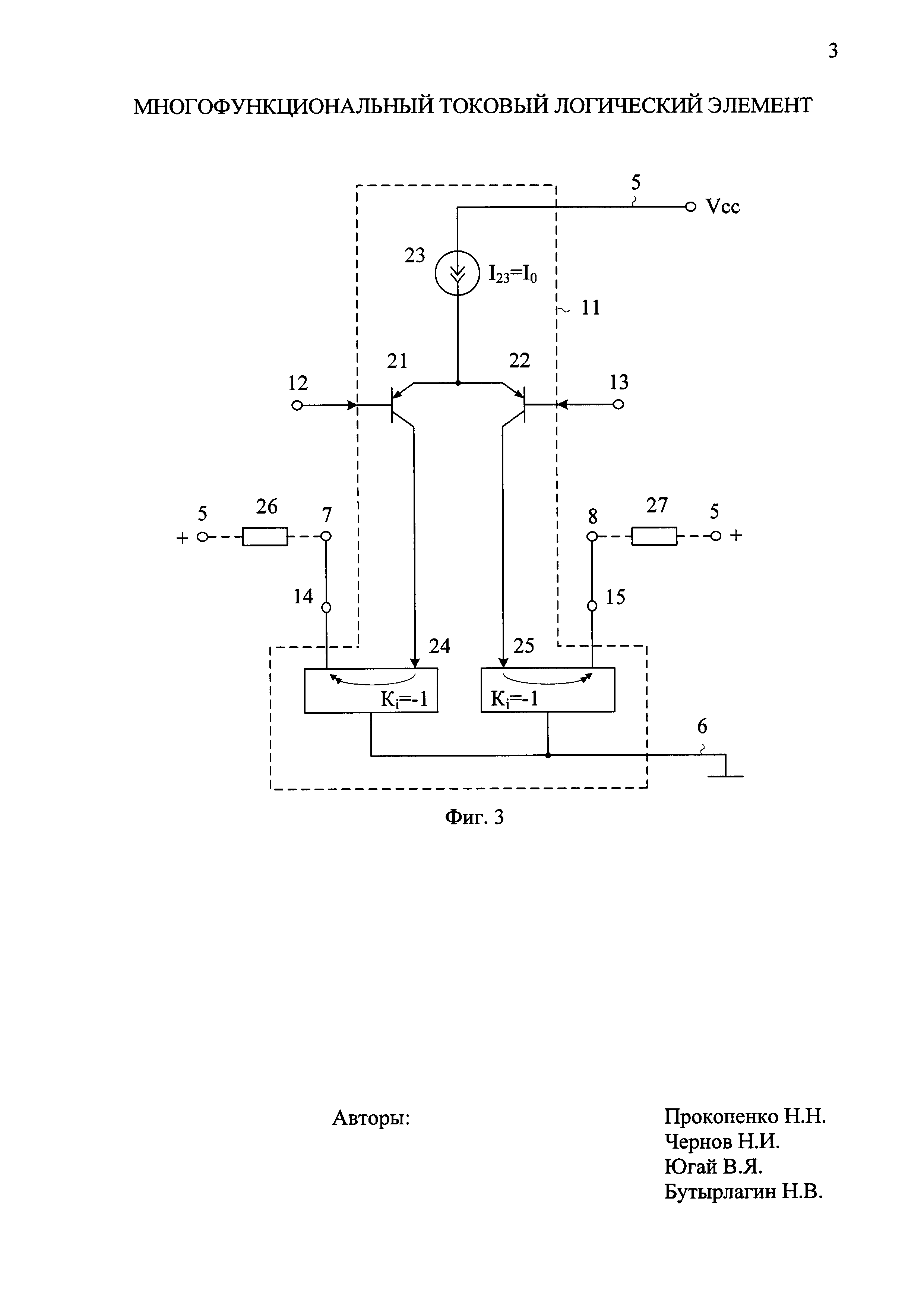

На фиг. 3 представлена другая частная схема компаратора напряжения 11, соответствующая п. 4 формулы изобретения.

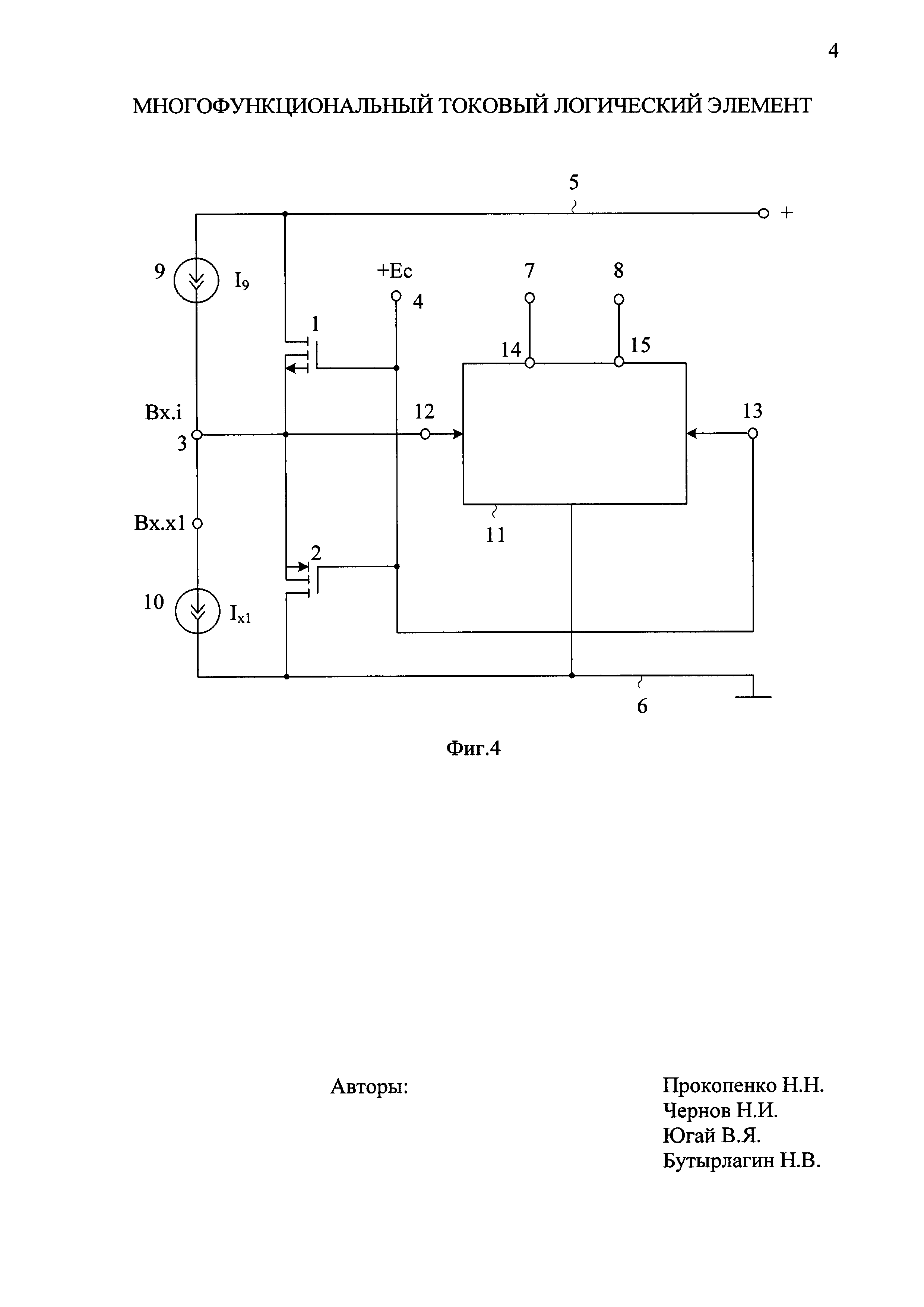

На фиг. 4 показана схема заявляемого устройства в соответствии с п. 5 формулы изобретения.

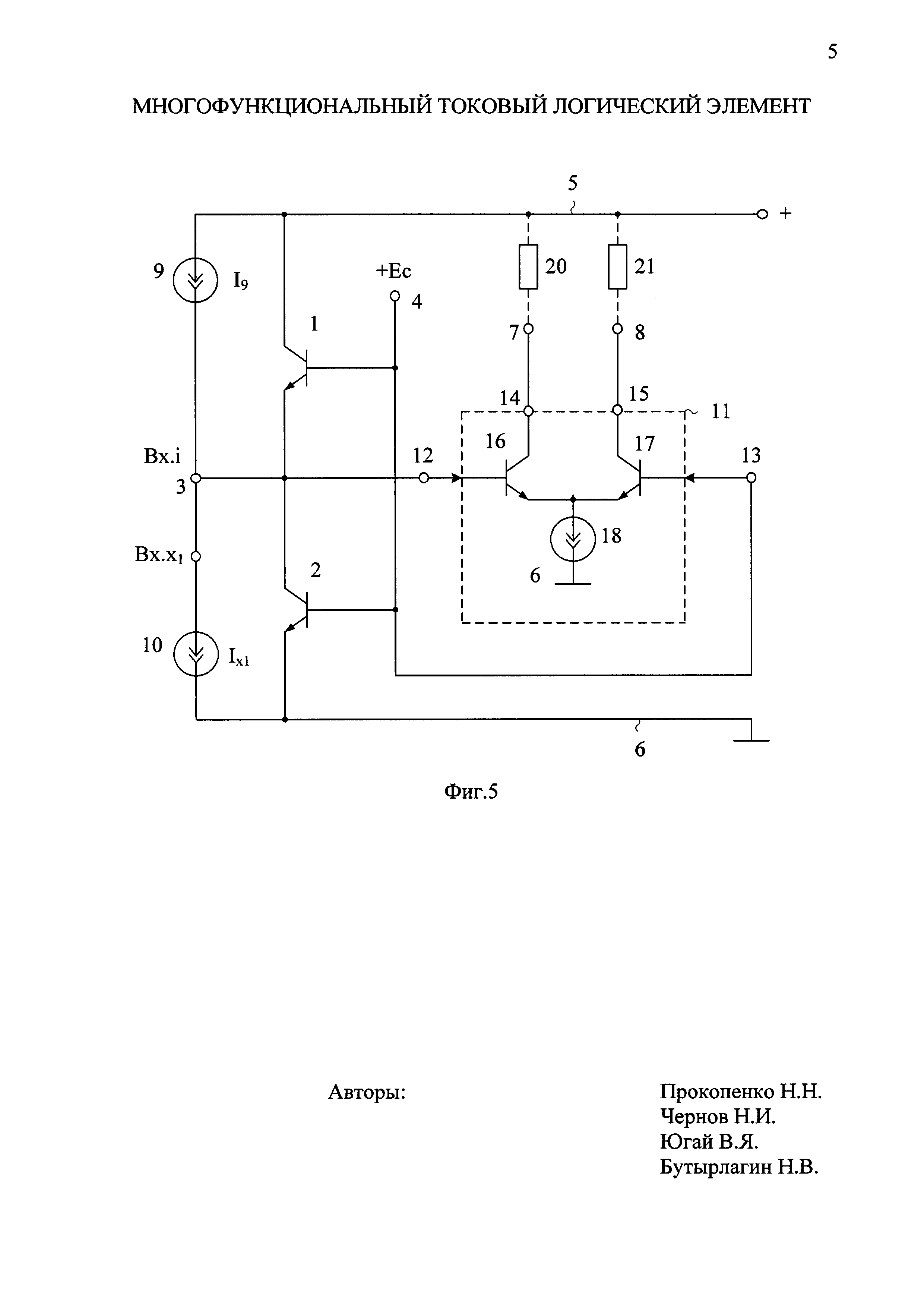

На фиг. 5 показана схема заявляемого устройства в соответствии с п. 6 формулы изобретения.

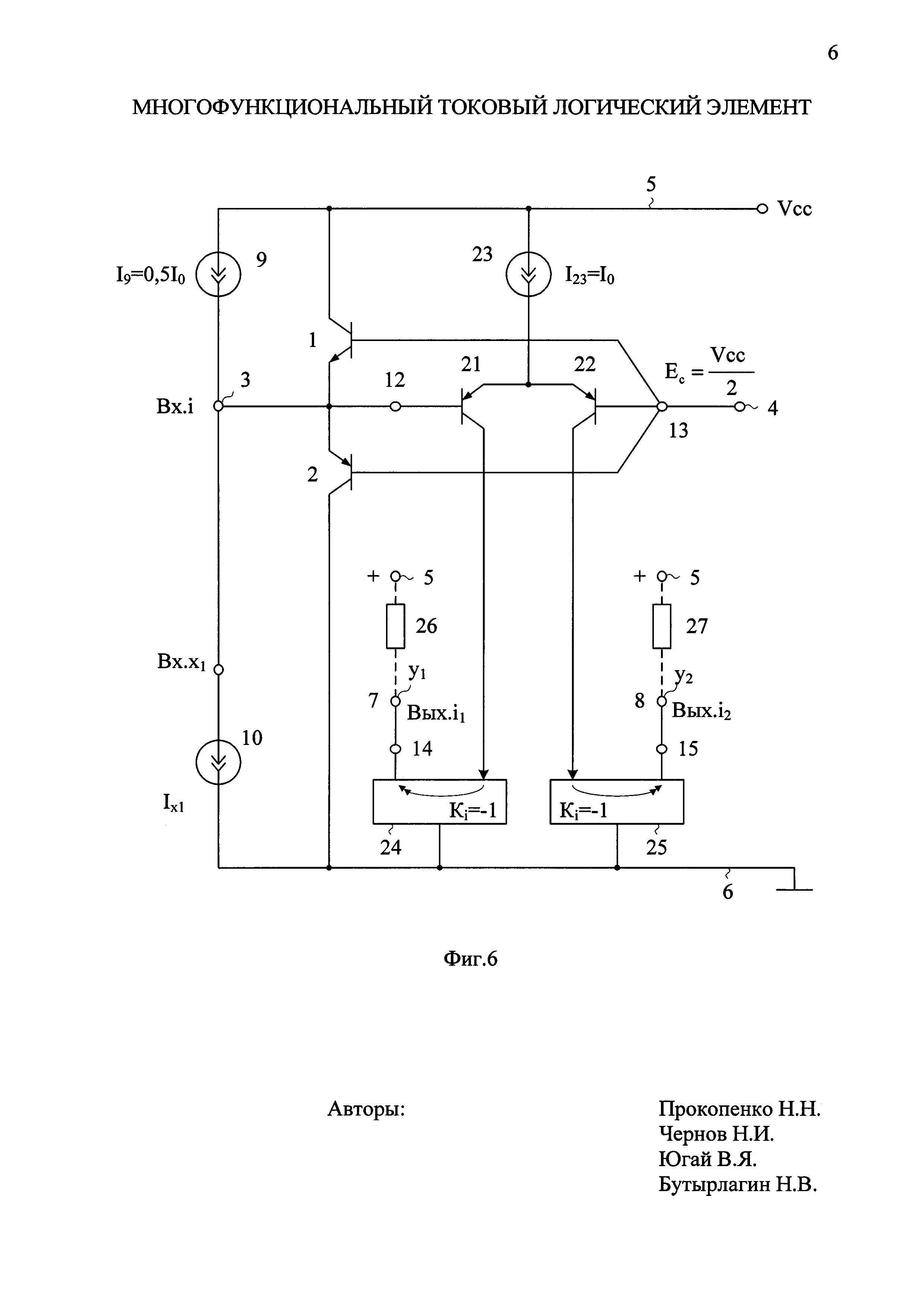

На фиг. 6 показана схема заявляемого устройства в режиме логической операции «НЕ» в соответствии с п. 7 формулы изобретения.

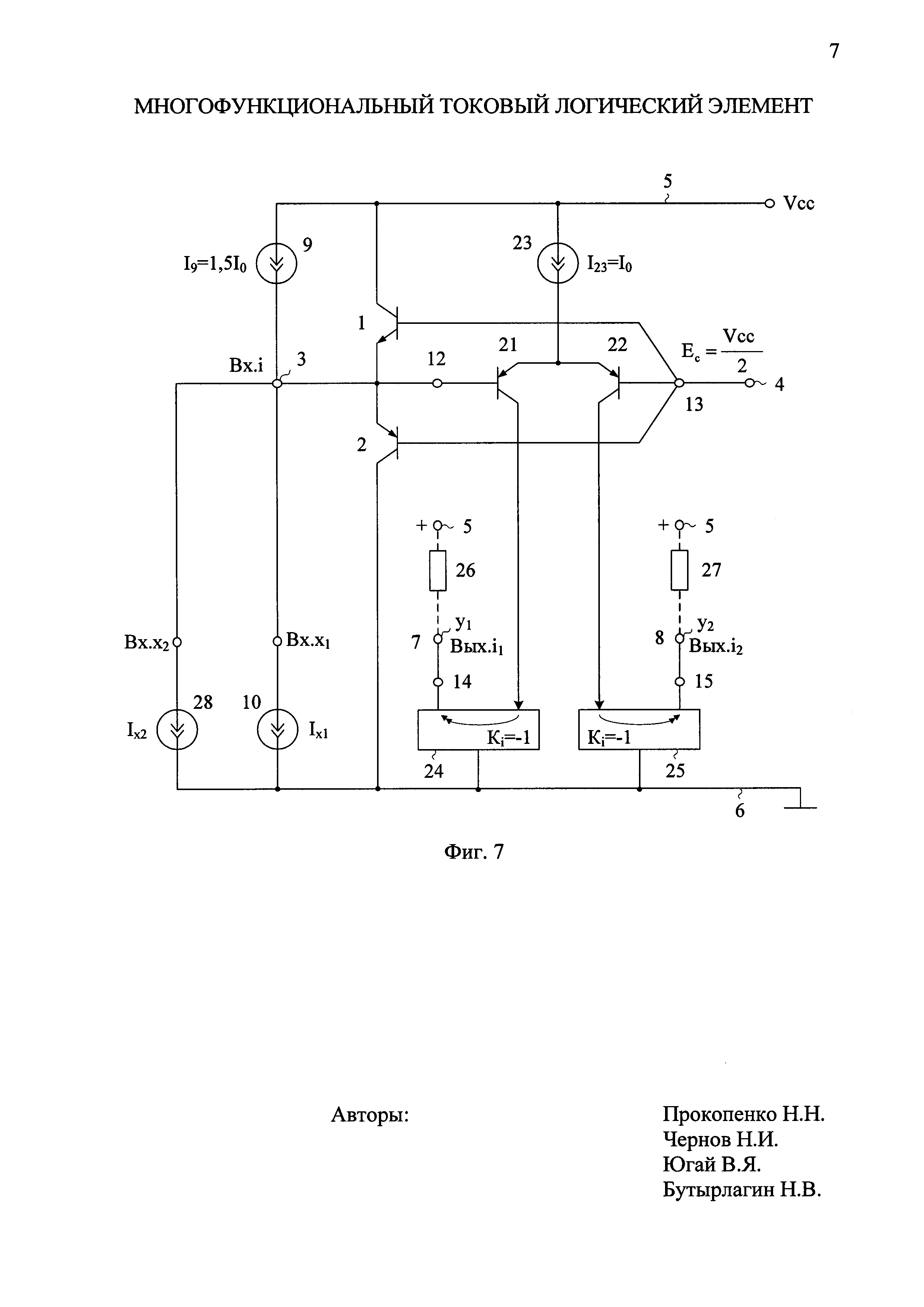

На фиг. 7 показана схема заявляемого устройства в режиме логической операции «И» в соответствии с п. 8 формулы изобретения.

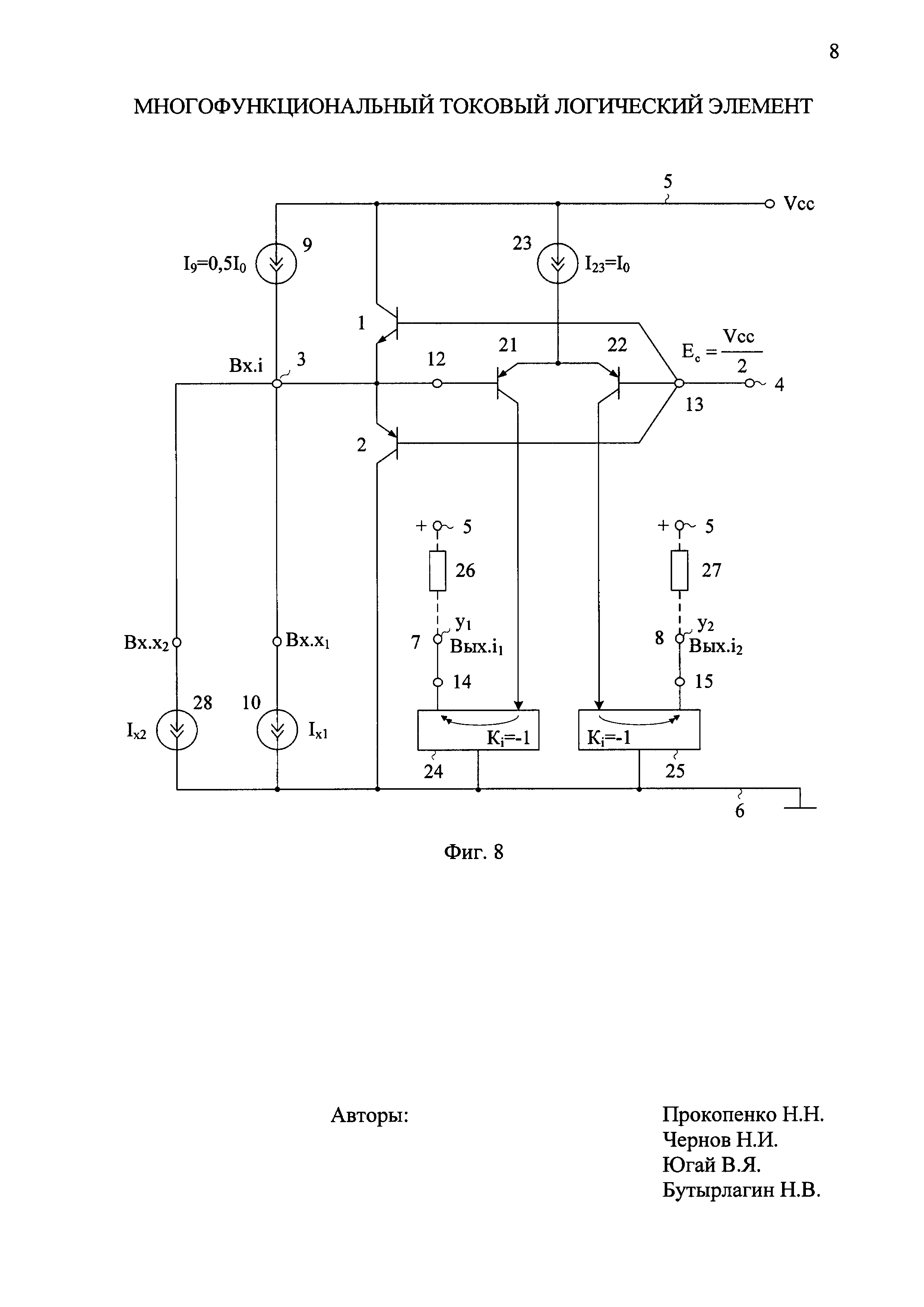

На фиг. 8 показана схема заявляемого устройства в режиме логической операции «ИЛИ» в соответствии с п. 9 формулы изобретения.

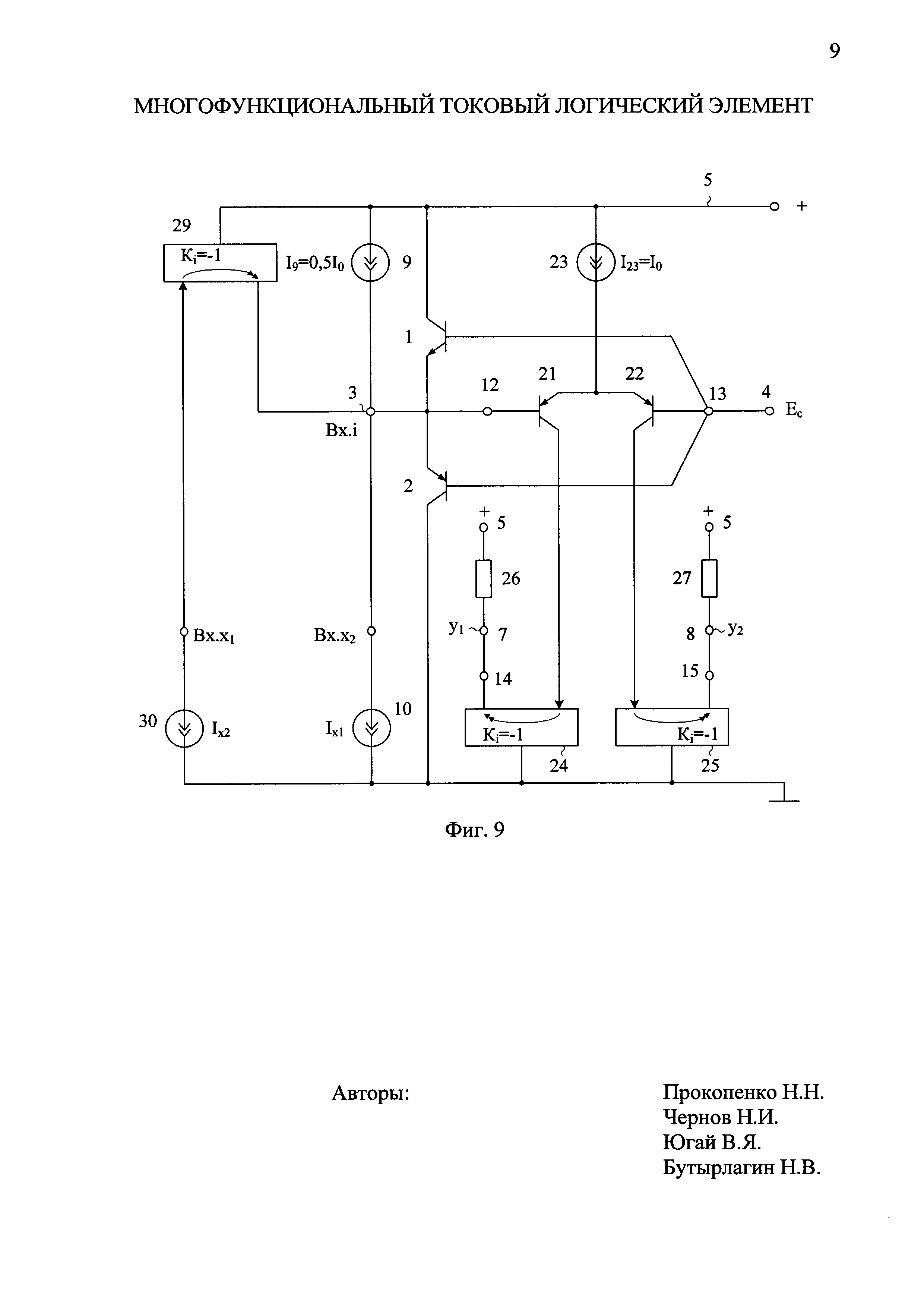

На фиг. 9 показана схема заявляемого устройства в режиме логической операции «Сравнение x1>x2» в соответствии с п. 10 формулы изобретения.

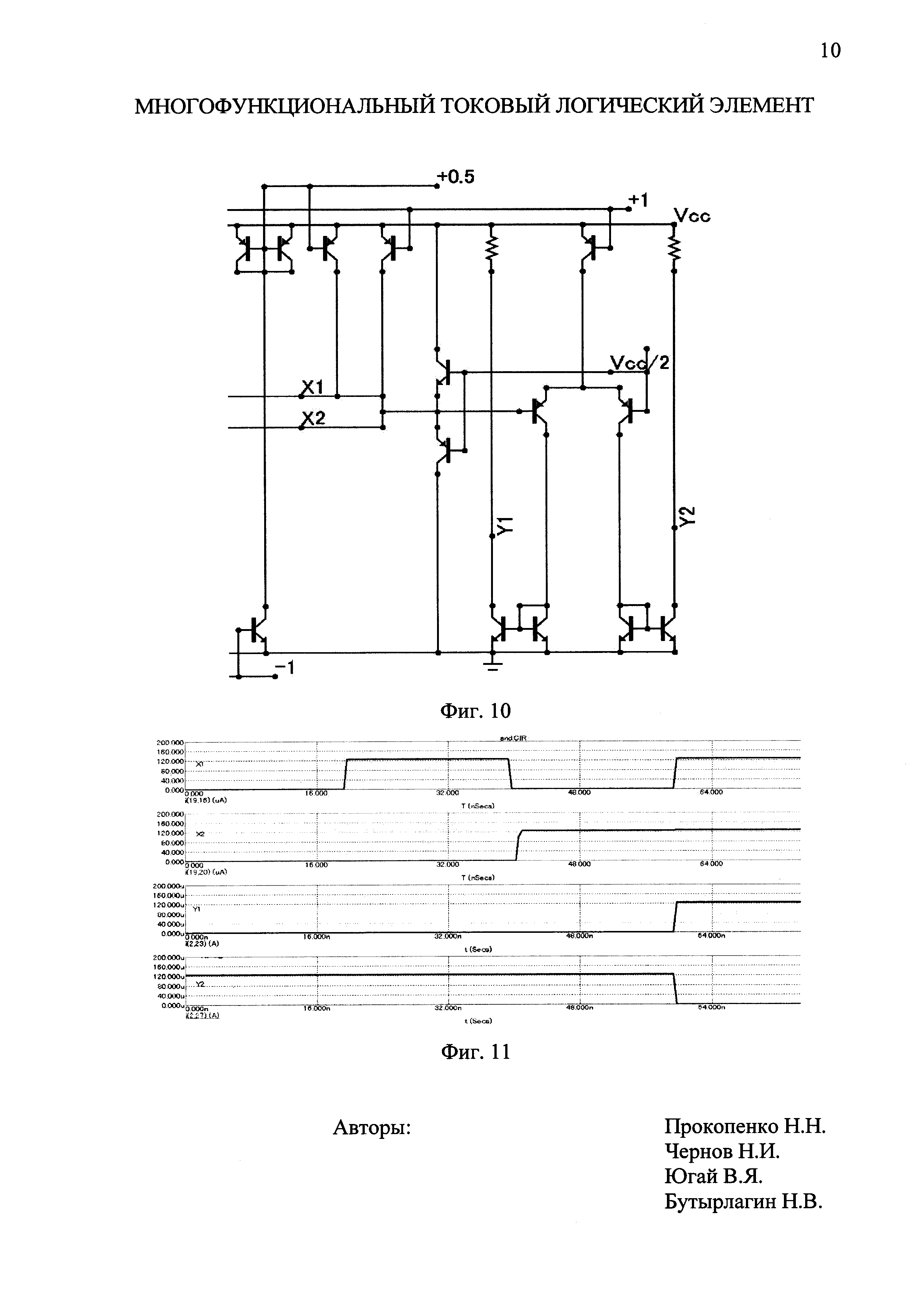

На фиг. 10 показана схема логического элемента «И» в среде компьютерного моделирования, который реализуется на основе заявляемого многофункционального токового логического элемента (фиг. 7), а на фиг. 11 - временная диаграмма его работы.

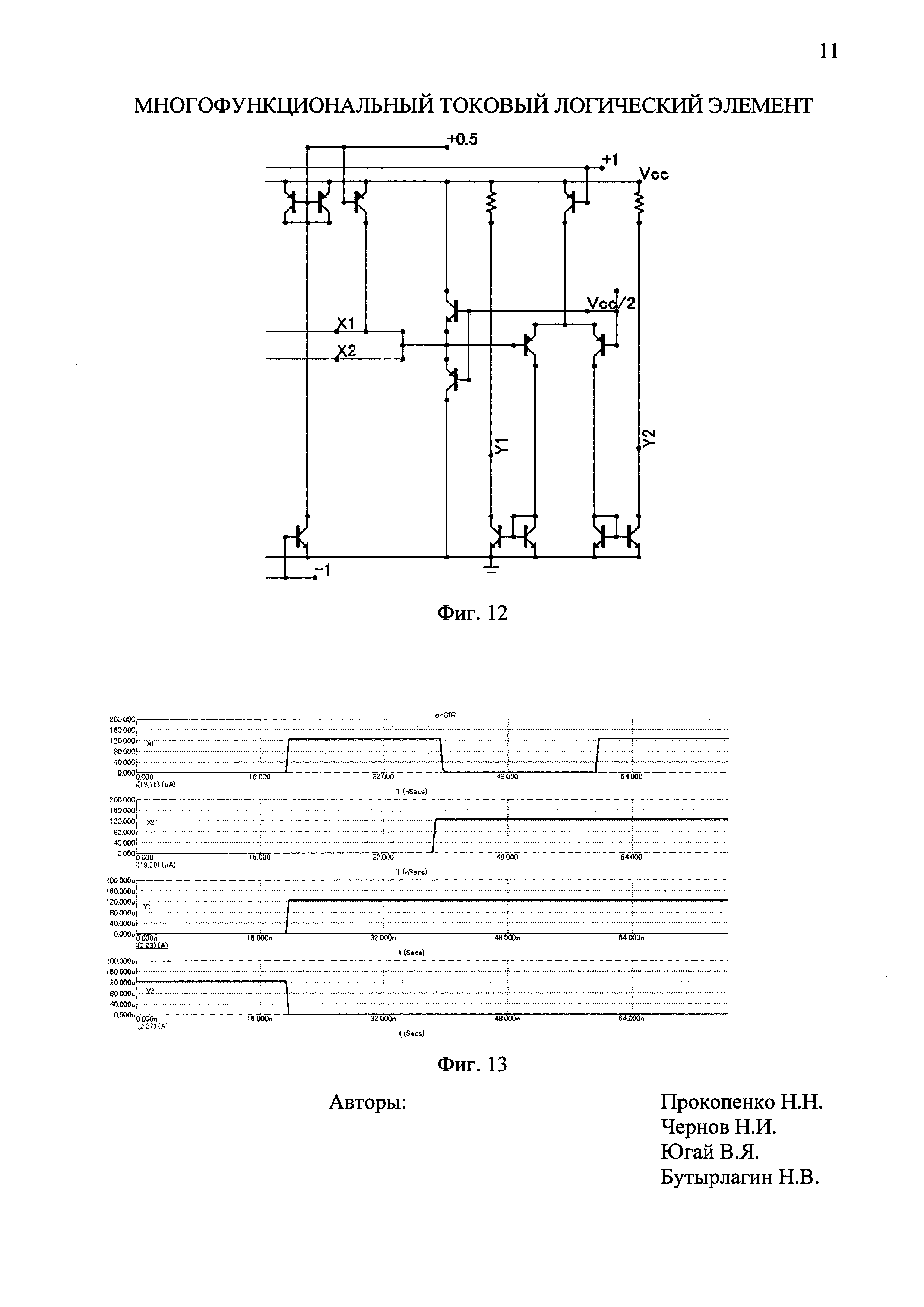

На фиг. 12 показана схема логического элемента «ИЛИ» в среде компьютерного моделирования, реализуемого на основе заявляемого многофункционального токового логического элемента (фиг. 8), а на фиг. 13 - временная диаграмма его работы.

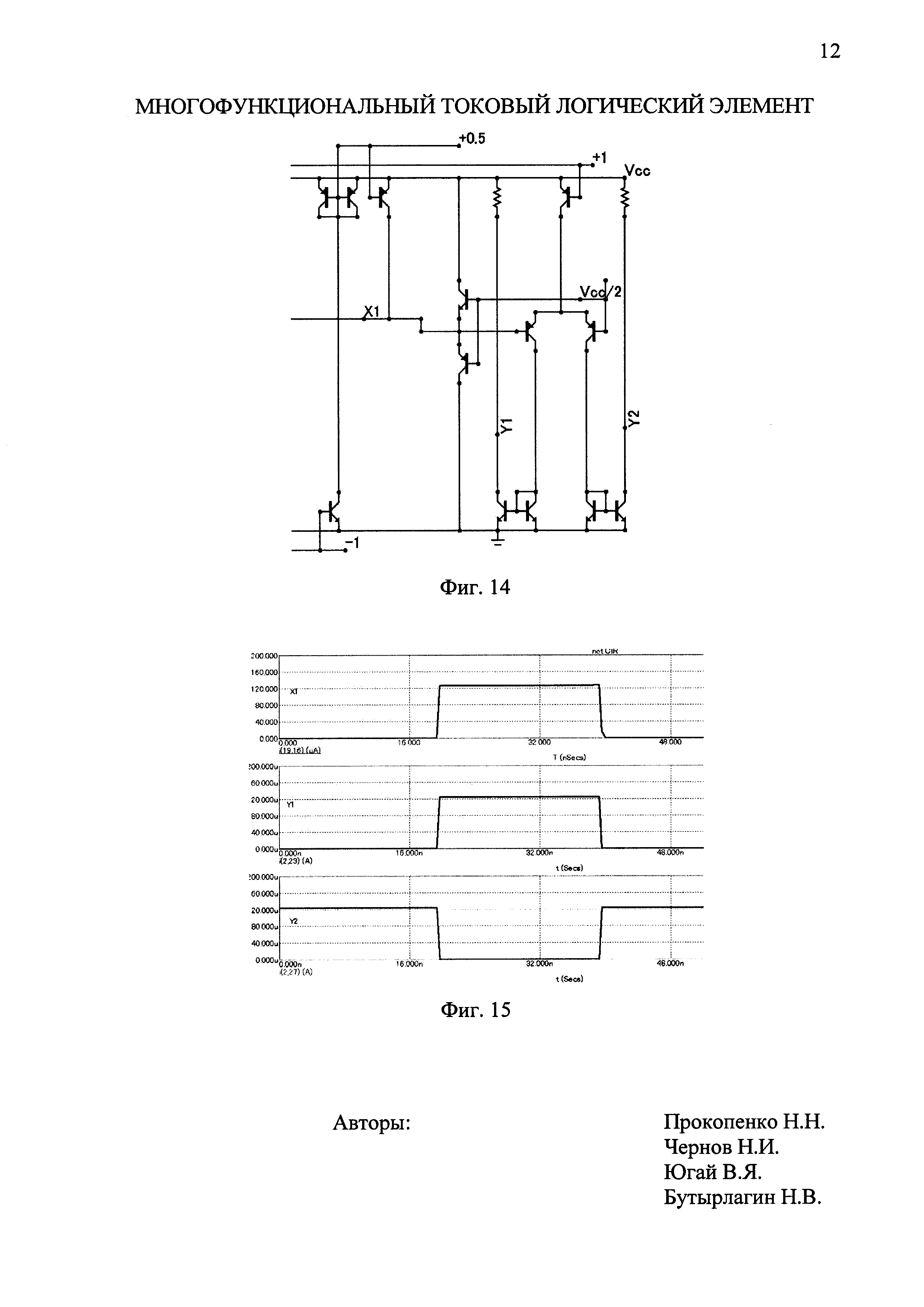

На фиг. 14 показана схема логического элемента «НЕ» в среде компьютерного моделирования, который реализуется на основе заявляемого многофункционального токового логического элемента (фиг. 6), а на фиг. 15 - временная диаграмма его работы.

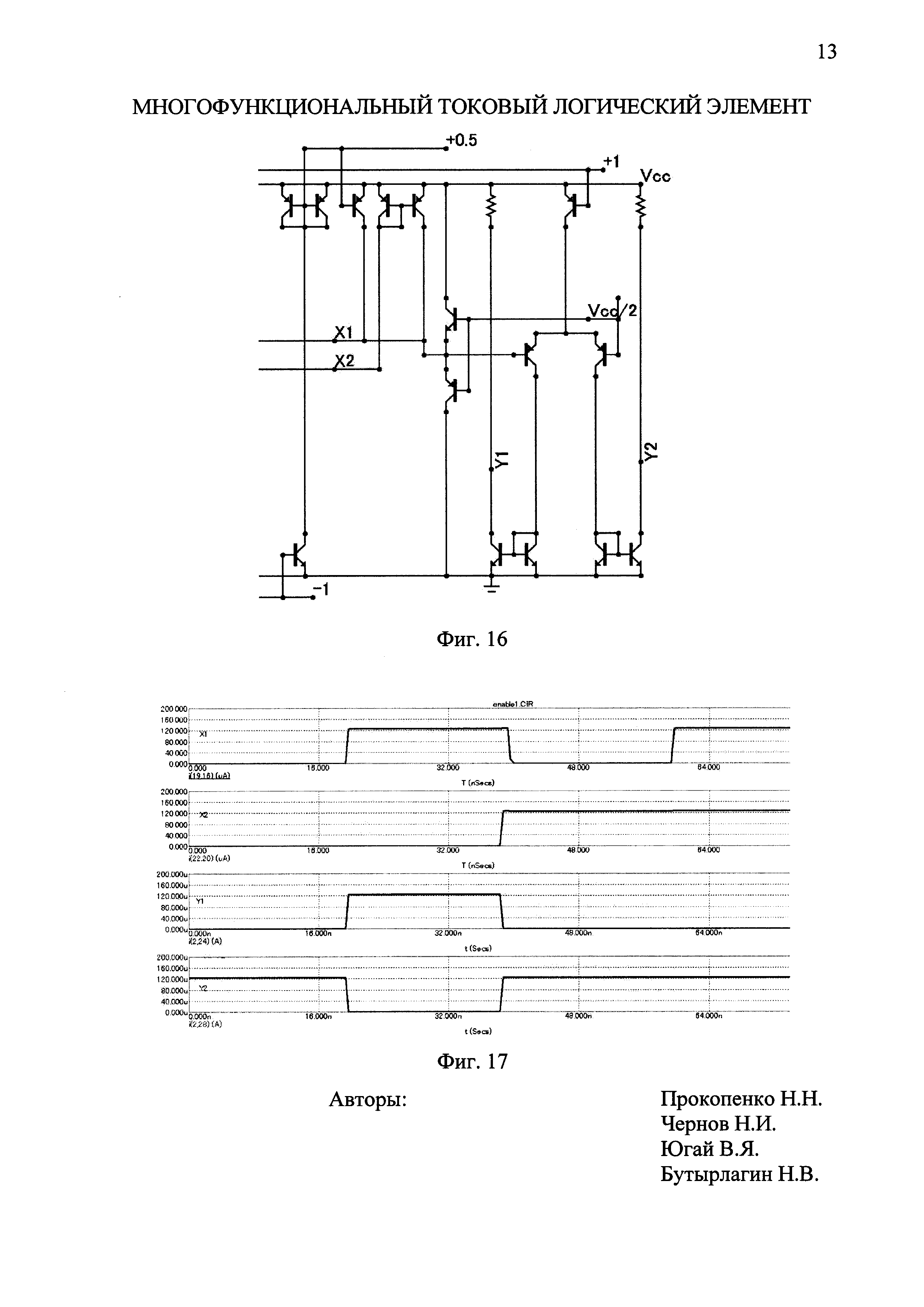

На фиг. 16 показана схема элемента «Логическое сравнение x1>x2» в среде компьютерного моделирования, реализуемого на основе заявляемого многофункционального токового логического элемента фиг. 9, а на фиг. 17 - временная диаграмма его работы.

Многофункциональный токовый логический элемент фиг. 2 содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых объединены и подключены к токовому входу 3 устройства, источник вспомогательного напряжения 4, связанный с базами первого 1 и второго 2 входных транзисторов, первую 5 шину источника питания, к которой подключен коллектор первого 1 входного транзистора, вторую 6 шину источника питания, к которой подключен коллектор второго 2 входного транзистора, первый 7 и второй 8 токовые выходы устройства, первый 9 и второй 10 источники входных токов, связанные с токовым входом 3 устройства. В схему введен компаратор напряжений 11, первый 12 вход которого соединен с объединенными эмиттерами первого 1 и второго 2 входных транзисторов, второй 13 вход связан с источником вспомогательного напряжения 4, а противофазные первый 14 и второй 15 токовые выходы компаратора напряжений 11, связаны с соответствующими первым 7 и вторым 8 токовыми выходами устройства.

На фиг. 2, в соответствии с п. 2 формулы изобретения, первый 7 и второй 8 токовые выходы устройства согласованы со второй 6 шиной источника питания.

На фиг. 2, в соответствии с п. 3 формулы изобретения, компаратор напряжений 11 содержит первый 16 и второй 17 входные транзисторы с объединенными эмиттерами, связанными с источником опорного тока 18, причем база первого 16 входного транзистора соединена с первым 12 входом компаратора напряжений 11, база второго 17 входного транзистора соединена со вторым 13 входом компаратора напряжений 11, коллектор первого 16 входного транзистора соединен с первым 14 токовым выходом компаратора напряжений 11, а коллектор второго 17 входного транзистора соединен со вторым 15 токовым выходом компаратора напряжений 11.

Кроме этого, на фиг. 2 показаны двухполюсники 19 и 20, моделирующие влияние нагрузки, подключаемой к первому 7 и второму 8 токовым выходам устройства.

На фиг. 3, в соответствии с п. 4 формулы изобретения, компаратор напряжений 11 содержит первый 21 и второй 22 входные транзисторы с объединенными эмиттерами, связанными с источником опорного тока 23, причем база первого 21 входного транзистора соединена с первым 12 входом компаратора напряжений 11, база второго 22 входного транзистора соединена со вторым 13 входом компаратора напряжений 11, коллектор первого 21 входного транзистора соединен со входом первого 24 токового зеркала, выход которого связан с первым 14 токовым выходом компаратора напряжений 11, а коллектор второго 22 входного транзистора соединен со входом второго 25 токового зеркала, выход которого связан со вторым 15 токовым выходом компаратора напряжений 11.

Кроме этого, на фиг. 3 показаны двухполюсники 26 и 27, моделирующие влияние нагрузки, подключаемой к первому 7 и второму 8 токовым выходам устройства.

На фиг. 4, в соответствии с п. 5 формулы изобретения, в качестве первого 1 и второго 2 входных транзисторов используются КМОП транзисторы, исток каждого из которых соответствует эмиттеру биполярного транзистора, затвор - базе, а сток - коллектору биполярного транзистора.

На фиг. 5, в соответствии с п. 6 формулы изобретения, первый 7 и второй 8 токовые выходы устройства согласованы с первой 5 шиной источника питания.

На фиг. 6, в соответствии с п. 7 формулы изобретения, ток второго 10 источника входного тока соответствует первой входной логической переменной устройства (x1), а численное значение статического тока первого 9 источника входного тока выбирается на уровне, близком к 0.5I0, где I0 - заданный квант тока, определяющий масштаб изменения первой входной логической переменной (x1). Это позволяет реализовать логическую функцию «НЕ».

На фиг. 7 в качестве компаратора напряжения 11 используется компаратор фиг. 3, а в соответствии с п. 8 формулы изобретения, ток второго 10 источника входного тока соответствует первой входной логической переменной устройства (x1), к токовому входу 3 устройства подключен дополнительный источник входного тока 28, соответствующий второй входной логической переменной (х2) устройства, причем численное значение статического тока первого 9 источника входного тока выбирается на уровне, близком к 1.5I0, где I0 - заданный квант тока, определяющий масштаб изменения первой (x1) и второй (х2) входных логических переменных устройства. Это позволяет реализовать логическую функцию «И».

На фиг. 8, в качестве компаратора напряжения 11 используется компаратор фиг. 3, а в соответствии с п. 9 формулы изобретения, ток второго 10 источника входного тока соответствует первой входной логической переменной (x1) устройства, к токовому входу 3 устройства подключен дополнительный источник входного тока 28, соответствующий второй входной логической переменной (х2) устройства, причем численное значение статического тока первого 9 источника входного тока выбирается на уровне, близком к 0.5I0, где I0 - заданный квант тока, определяющий масштаб изменения первой (x1) и второй (х2) входных логических переменных устройства. Это позволяет реализовать логическую функцию «ИЛИ».

На фиг. 9, в качестве компаратора напряжения 11 используется компаратор фиг. 3, а в соответствии с п. 10 формулы изобретения, ток второго 10 источника входного тока соответствует первой входной логической переменной (x1) устройства, к токовому входу 3 устройства подключен выход дополнительного токового зеркала 29, согласованного с первой 5 шиной источника питания, вход которого связан со вторым 30 дополнительным источником входного тока Ix2, соответствующим второй (х2) логической переменной, причем численное значение статического тока первого 9 источника входного тока выбирается на уровне, близком к 0.5I0 где I0 - заданный квант тока, определяющий масштаб изменения первой (x1) и второй (х2) входных логических переменных устройства при реализации логической функции «Сравнение x1>x2».

Рассмотрим работу многофункционального токового логического элемента на примере анализа схемы, приведенной на фиг. 2.

Входные токовые сигналы I9, Ix1 поступают к токовому входу 3 устройства. Так как ток I9 является втекающим, а ток Ix1 - вытекающим, то в эмиттеры первого 1 и второго 2 входных транзисторов поступает разность этих входных токов.

При неравенстве I9>Ix1 в токовом входе 3 устройства формируется втекающий ток, который будет «уходить» в эмиттер второго 2 входного транзистора, снижая напряжение на первом 12 входе компаратора напряжений 11 до значения Ec-Uбэ2, где Uбэ2 - напряжение открытого эмиттерного перехода второго 2 входного транзистора. Напряжение на втором 13 входе компаратора напряжений 11 постоянно и равно Ес - напряжению вспомогательного источника 4. Поэтому второй 17 входной транзистор компаратора напряжений 11 будет закрыт и его выходной ток (Вых.i2) будет равен нулю, а первый 16 входной транзистор - открыт. При этом ток источника опорного тока 18 компаратора напряжения 11 поступит на первый 7 токовый выход устройства (Вых.i1).

При неравенстве I9<Ix1 в токовом входе 3 устройства формируется вытекающий ток, который будет протекать через эмиттер n-p-n первого 1 входного транзистора, увеличивая напряжение на первом 12 входе компаратора напряжений 11 до значения Ec+Uбэ1, где Uбэ1≈0,7 B - напряжение открытого эмиттерного перехода первого 1 входного транзистора. В этом случае первый 16 и второй 17 входные транзисторы компаратора напряжений 11 переключатся в противоположные состояния и коллекторный ток первого 16 входного транзистора компаратора напряжений 11 будет равен нулю, а второй 17 входной транзистор компаратора напряжения 11 будет передавать на второй 8 токовый выход устройства ток источника опорного тока 18.

Таким образом, в зависимости от соотношения численных значений входных токов I9, Ix1 выходные токи многофункционального логического элемента (токи выходов 7, 8 устройства) принимают одно из двух значений - либо ток источника опорного тока 18 или ноль. Если выходной ток источника опорного тока 18 равен кванту тока, то на одном из выходов 14 и 15 компаратора напряжений 11 формируется стандартный токовый сигнал одного из логических уровней, а на втором его выходе - сигнал инверсного логического уровня. Как будет показано далее, в зависимости от способов формирования входных токовых сигналов токового входа 3 устройства многофункциональный логический элемент может выполнять различные логические функции.

Рассмотренные выше процессы протекают также в других схемах практического использования заявляемого многофункционального токового логического элемента (фиг. 4-9).

Для компенсации возможных погрешностей формирования выходных сигналов в схеме «И» фиг. 10 реализовано соотношение (x1+x2)>1,5I0. Тогда суммарные погрешности входных логических переменных менее 0,5 от кванта тока I0 не влияют на логику работы схемы. В результате, в соответствии с фиг. 11, получаем два выхода: Y1 - конъюнкция, Y2 - конъюнкция с инверсией.

Фактически для компенсации возможных погрешностей формирования выходных сигналов в схеме элемента «ИЛИ» фиг. 12 реализовано соотношение (x1+x2)>0,5I0. Тогда суммарные погрешности входных логических переменных менее 0,5 от кванта тока I0 не влияют на логику работы схемы. В результате, в соответствии с фиг. 13, для схемы фиг. 12 получаем два выхода: Y1 - дизъюнкция, Y2 - дизъюнкция с инверсией.

В схеме логического элемента «НЕ» фиг. 14 для компенсации возможных погрешностей формирования выходных сигналов реализовано соотношение x1<0,5I0. Поэтому погрешность входной логической переменной (x1) менее 0,5 от кванта тока I0 не влияют на логику работы схемы. При этом, в соответствии с фиг. 15, получаем на двух выходах схемы фиг. 14 инверсию и повторение входного сигнала с восстановлением исходных уровней токовых сигналов.

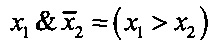

Фактически в схеме «Логического элемента сравнения x1>x2» (фиг. 16) реализовано соотношение (x1+0,5-x2)>0. Поэтому суммарные погрешности входных логических переменных менее 0,5 от кванта тока I0 не влияют на логику работы схемы. На выходах схемы фиг. 16 также получаем функцию  и ее инверсию (фиг. 17).

и ее инверсию (фиг. 17).

Таким образом, заявляемый многофункциональный логический элемент реализует основные операции токового преобразования входных логических переменных («И», «ИЛИ», «НЕ», «x1>x2») и обеспечивает их нормализацию. Причем каждый из названных вариантов логических элементов реализуется за счет изменения уровня тока первого 9 источника входного тока, а также введения в схему дополнительного токового зеркала (для фиг. 9).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 3.508.076, fig. 1.

2. Авторское свидетельство СССР SU 892729.

3. Патентная заявка WO 2004/112247.

4. Патент US 4.001.603.

5. Патент US 4.359.653.

6. Патент US 6.157.693, fig. 5.

7. Патент US 5.216.295.

8. Патент US 3.758.791, fig. 5.

9. Патент US 4.593.211.

10. Патент US 4.347.446.

11. Патент US 4.516.039, fig. 5.

12. Патент US 4.970.416.

13. Патент US 4.605.871, fig. 2.

14. Патент US 4.799.026.

15. Патентная заявка US 2009/0237163 fig. 2.

16. Патент US 4.361.815 fig. 3.

17. Патент US 5.371.476 fig. 1.

18. Патентная заявка US 2006/0006910.

19. Патентная заявка US 2008/0032656 fig. 6.

20. Патент US 3.921.090 fig. 2.

21. Патентная заявка US 2010/0097141 fig. 7.

22. Патент US 4.241.315 fig. 4.

23. Патент US RE 030587.

24. Патент США №3.439.542.

25. Патент США №5.880.639.

26. А.св. СССР №361605.

27. Патент ФРГ №2551068.

28. Патент ФРГ №2620999.

29. Патент США №4.267.519.

30. Патент США №4.783.602.

31. Патент США №4.176.323.

32. Патент US 5.315.176, fig. 1, fig. 2.

33. Патентная заявка US 2007/0018694.

34. Патент US 6.414.519.

35. Патент US 6.566.912.

36. Патент US 6.700.413.

37. Патентная заявка US 2004/0263210.

38. Патент US 6.680.625.

39. Патент SU 1621164.

40. Патент JP 10098374.

41. Патент US 6.573.758.

42. Патент US 5.155.387.

43. Патент US 4.713.790.

44. Патент US 5.608.741.

45. Патент US 4.158.210.

46. Патент US 4.185.210, fig. 2.

47. Патент US 3.040.192, fig. 1.

48. Патент РФ №2506696.

49. Патент РФ №2504074.

50. Патент РФ №2513717.

51. Патент РФ №2514789.

52. Патент РФ №2520416.

53. Патент РФ №2546078.

54. Патент РФ №2546082.

55. Патент РФ №2546085.

56. Патент РФ №2547225.

57. Патент РФ №2547231.

58. Патент РФ №2547233.

59. Патент РФ №2549144.

60. Патент РФ №2549142.

61. Патент РФ №2553070.

62. Патент РФ №2553071.

63. Патент РФ №2554557.

64. Патент РФ №2559705.

65. Патент РФ №2568385.

66. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С. 84-93.

67. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

68. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие Таганрог. - ТРТУ, 2004. - 118 с.