Результат интеллектуальной деятельности: НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления электрических сигналов различных датчиков.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых или биполярных транзисторах [1-15], в т.ч. выполненные на основе несимметричных дифференциальных каскадов [14-16]. Основное достоинство последних - отсутствие классических источников опорного тока, отрицательно влияющих на важнейшие статические и динамические параметры.

Для работы в условиях космического пространства в экспериментальной физике необходимы радиационно-стойкие ОУ с малым напряжением смещения нуля. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач экономически целесообразно с использованием биполярно-полевого технологического процесса [17], обеспечивающего формирование p-канальных полевых (Fet) и высококачественных n-p-n биполярных (BiFet) транзисторов с радиационной стойкостью до 1 Мрад, удовлетворительно работающих при потоке нейтронов до 5⋅1013 н/см2 [18-24]. Однако в таких ОУ при отрицательных температурах t=-100÷-120°C необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [18-20]. Для более низких, в том числе криогенных температур в схемах рекомендуется использовать только полевые транзисторы (Fet, CMOS).

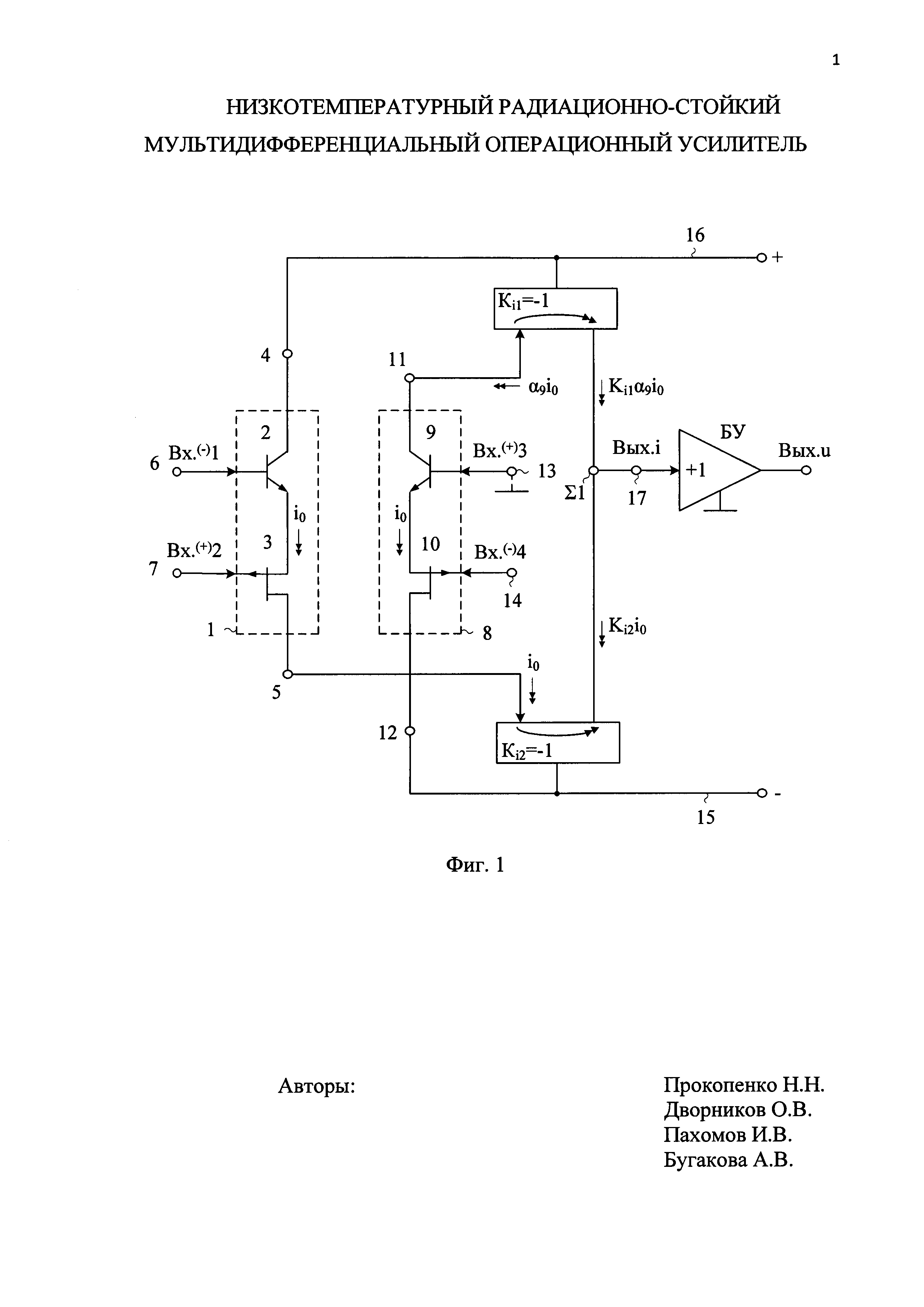

Ближайшим прототипом (фиг. 1) заявляемого устройства является мультидифференциальный операционный усилитель (МОУ), представленный в патенте RU 2523124, фиг. 2. Он содержит (фиг. 1) первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами (эмиттером и истоком), первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первую 15 и вторую 16 шины источника питания, а также выход устройства 17.

Существенный недостаток известного МОУ состоит в том, что он характеризуется повышенным значением напряжения смещения нуля (Uсм). Это обусловлено его архитектурой, а также связано с тем, что в двухканальной архитектуре МОУ-прототипа (фиг. 1) для передачи сигналов используются токовые зеркала, реализуемые на разнотипных транзисторах (n-р-n, p-n-р), имеющих различные коэффициенты усиления по току базы (β), а также неодинаковые напряжения Эрли. В конечном итоге, это увеличивает влияние неидентичности данных токовых зеркал на Uсм.

Основная задача предполагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля МОУ.

Поставленная задача достигается тем, что в мультидифференциальном операционном усилителе фиг. 1, содержащем первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами (эмиттером и истоком), первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первую 15 и вторую 16 шины источника питания, а также выход устройства 17, предусмотрены новые элементы и связи - второй 5 токовый выход первого 1 дифференциального каскада соединен с первой 15 шиной источника питания через первый 18 токостабилизирующий двухполюсник и подключен к эмиттеру первого 19 согласующего транзистора, второй 12 токовый выход второго 8 дифференциального каскада соединен с эмиттером второго 20 согласующего транзистора и через второй 21 токостабилизирующий двухполюсник соединен с первой 15 шиной источника питания, причем базы первого 19 и второго 20 согласующих транзисторов подключены в первому 22 источнику напряжения смещения, первый 4 токовый выход первого 1 дифференциального каскада подключен к эмиттеру первого 23 выходного транзистора и соединен с коллектором второго 20 согласующего транзистора, коллектор первого 23 выходного транзистора соединен с первым 24 входом выходного дифференциального каскада 25, согласованного со второй 16 шиной источника питания, а база соединена с базой второго 26 выходного транзистора и со вторым 27 источником напряжения смещения, причем первый 11 токовый выход второго 8 дифференциального каскада соединен с эмиттером второго 26 выходного транзистора и подключен коллектору первого 19 согласующего транзистора, коллектор второго 26 выходного транзистора связан со вторым 28 входом выходного дифференциального каскада 25, выход которого соединен с выходом устройства 17.

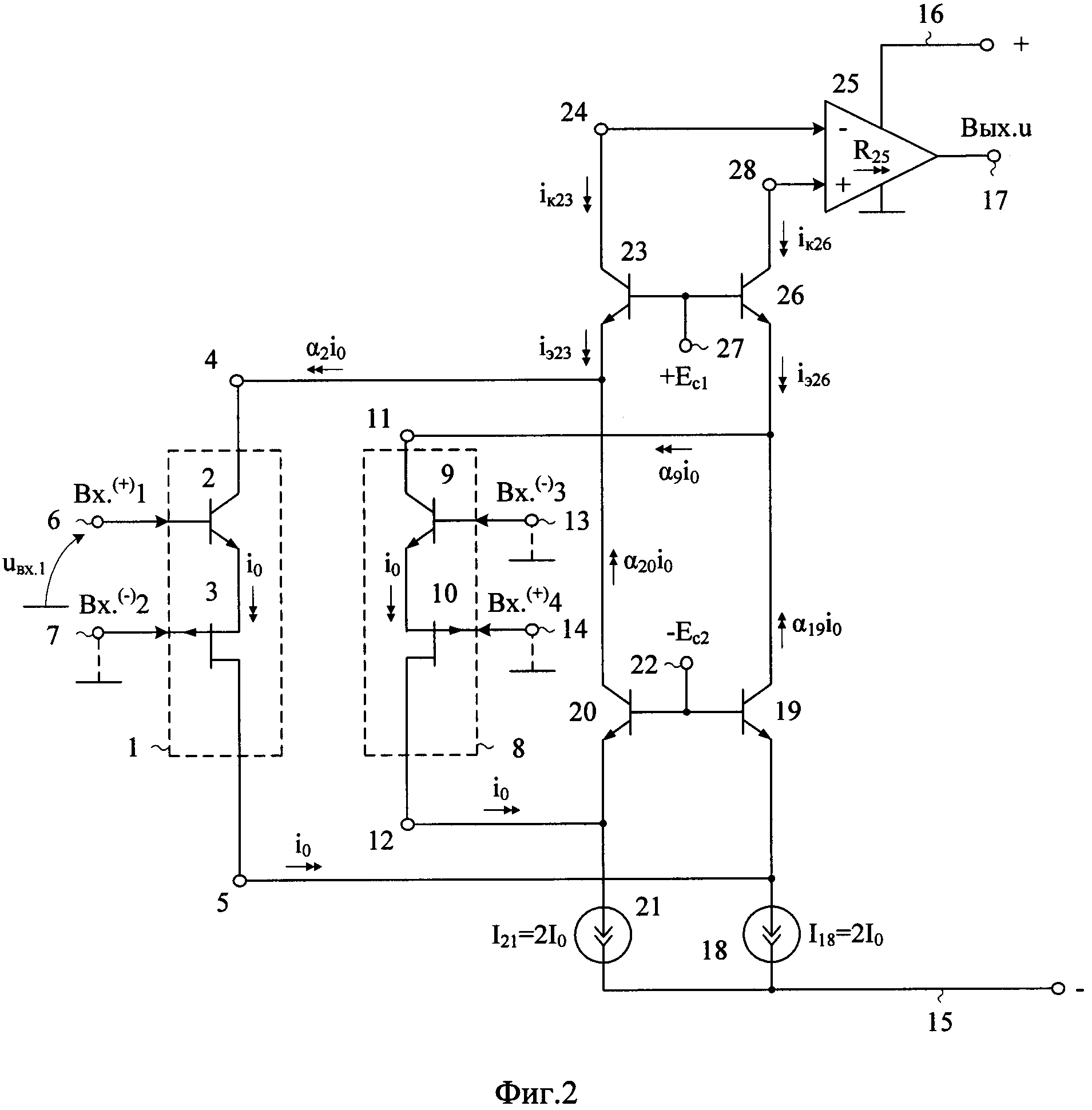

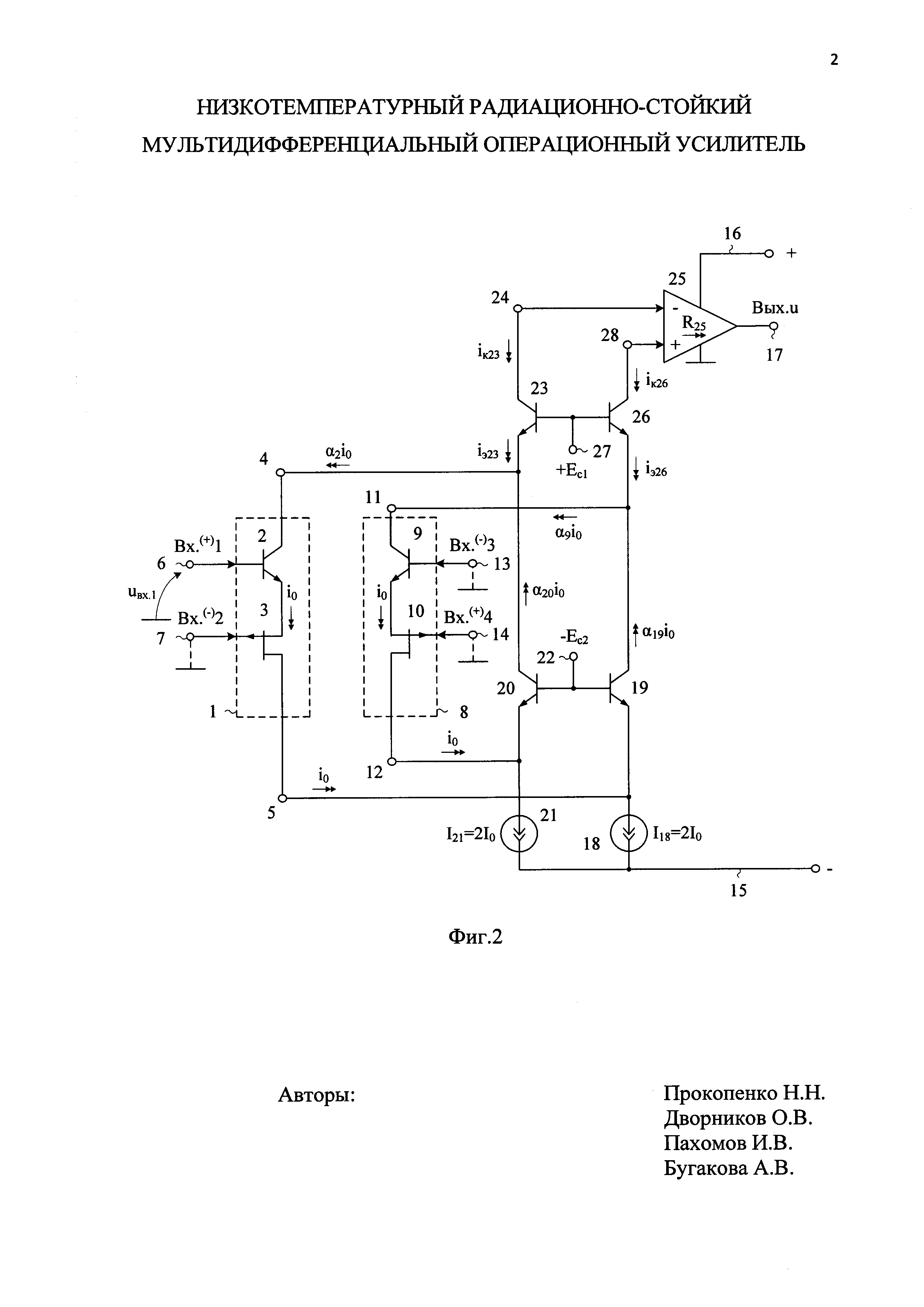

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

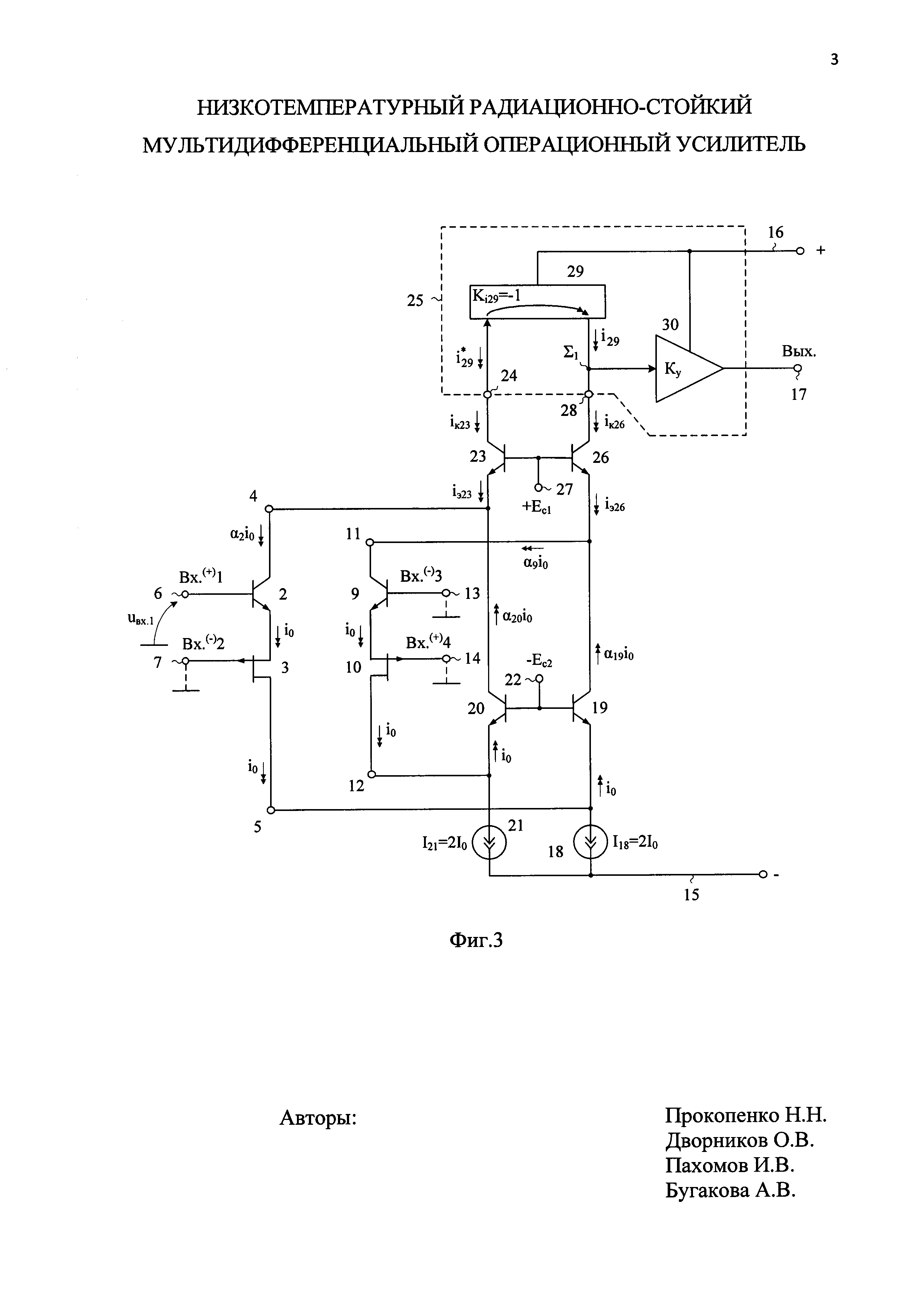

На чертеже фиг. 3 приведена схема заявляемого устройства соответствии с п. 2 формулы изобретения для конкретного выполнения выходного дифференциального каскада 25.

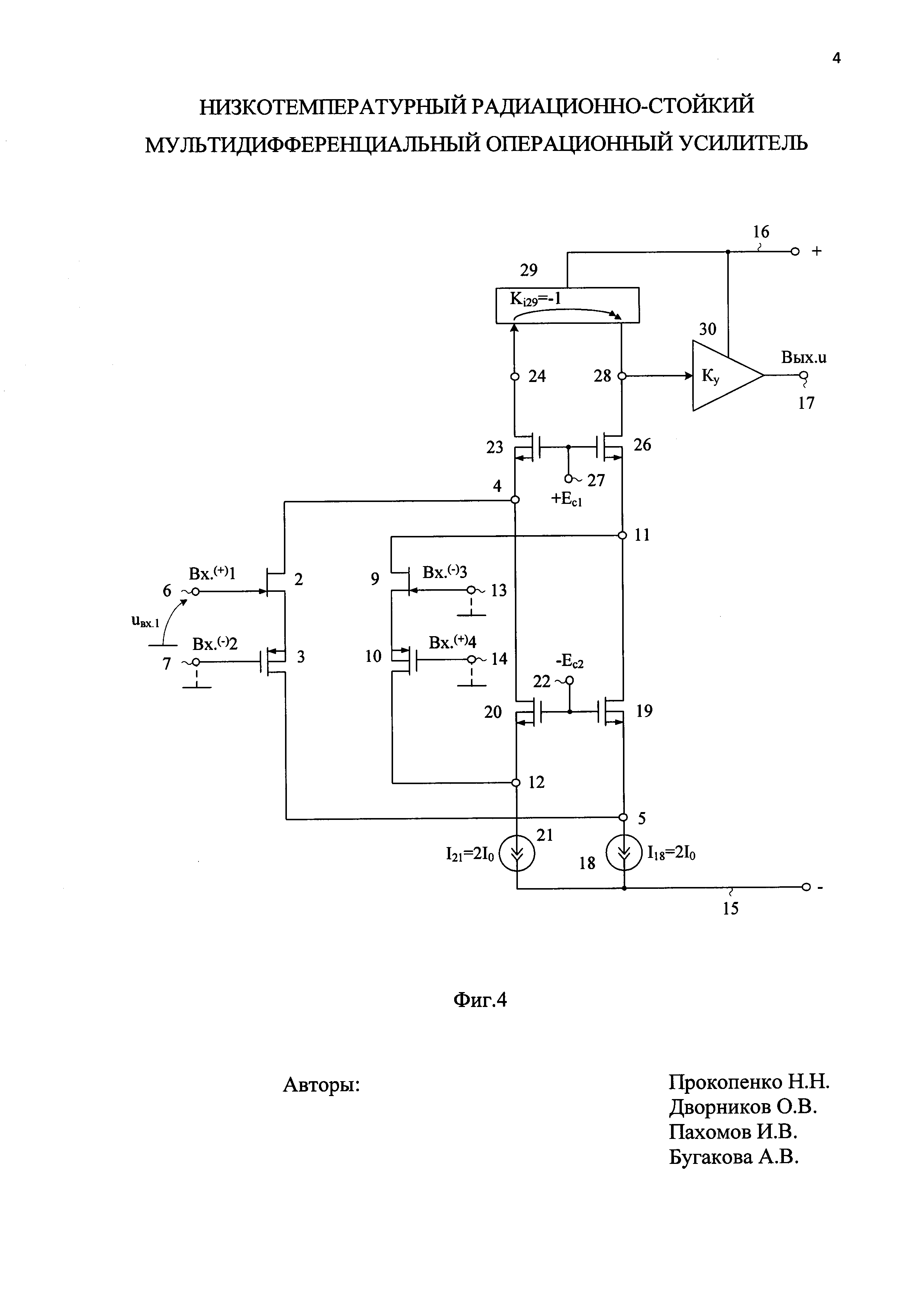

На чертеже фиг. 4 приведена схема заявляемого устройства в соответствии с п. 3 и п. 4 формулы изобретения.

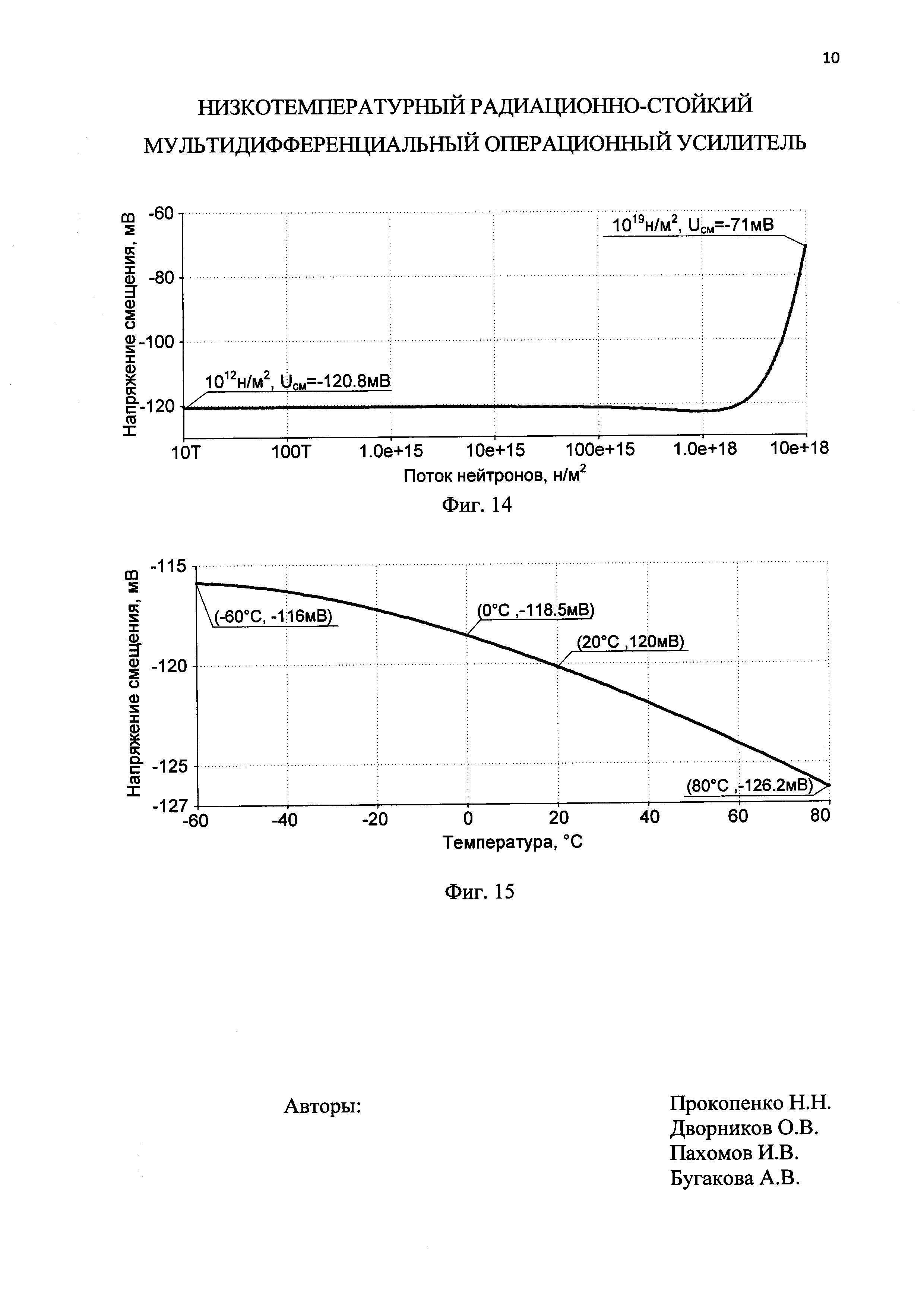

На чертеже фиг. 5 приведена схема заявляемого устройства фиг. 2 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 (ОАО «Интеграл», г. Минск). В данной схеме моделировались амплитудно-частотные характеристики МОУ.

На чертеже фиг. 6 показаны амплитудно-частотные характеристики коэффициента усиления МОУ фиг. 5 со 100% отрицательной обратной связью и без отрицательной обратной связи.

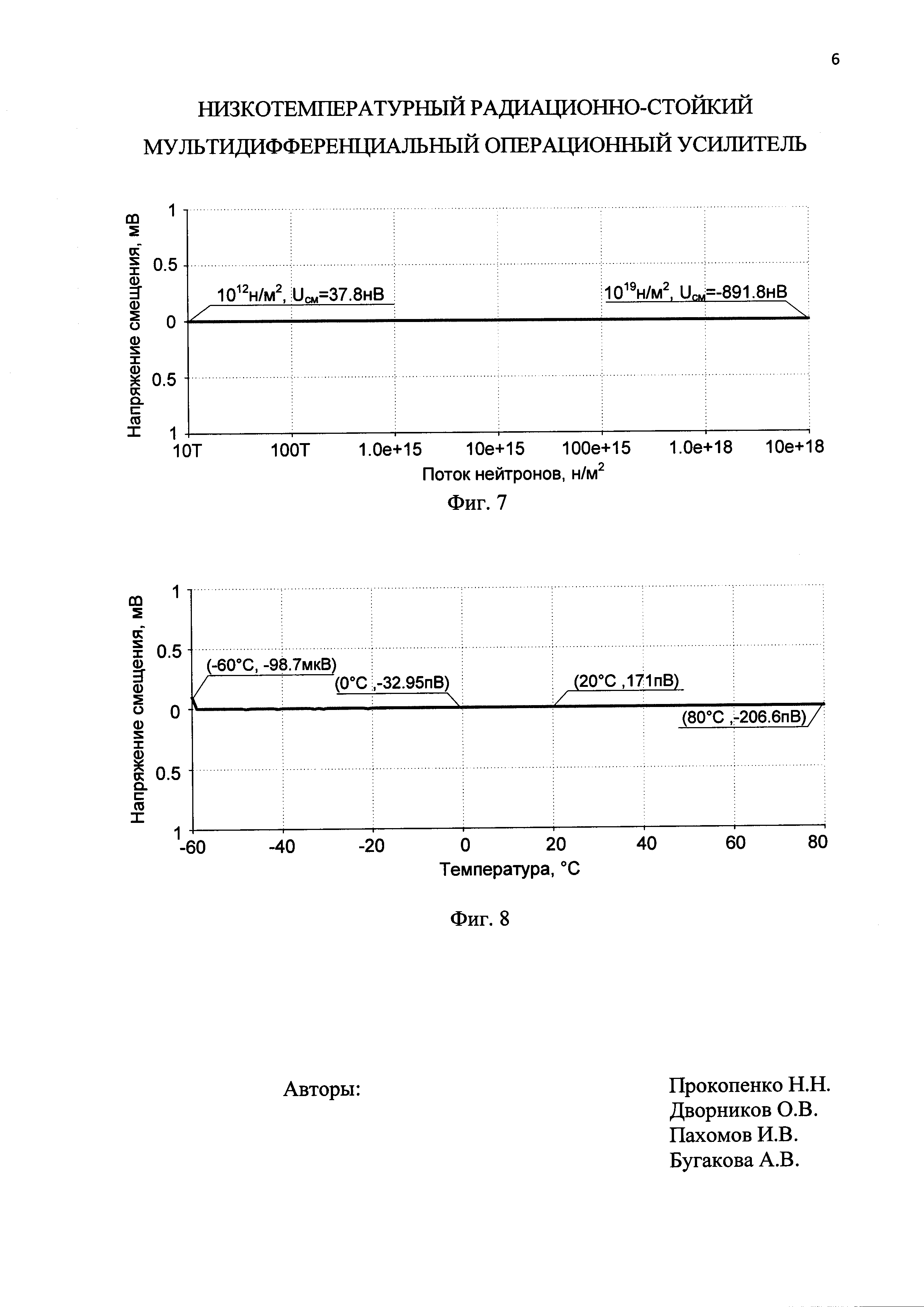

На чертеже фиг. 7 приведена зависимость напряжения смещения нуля МОУ фиг. 5 от потока нейтронов, а на чертеже фиг. 8 - от температуры в диапазоне минус 60 - плюс 80°С (б).

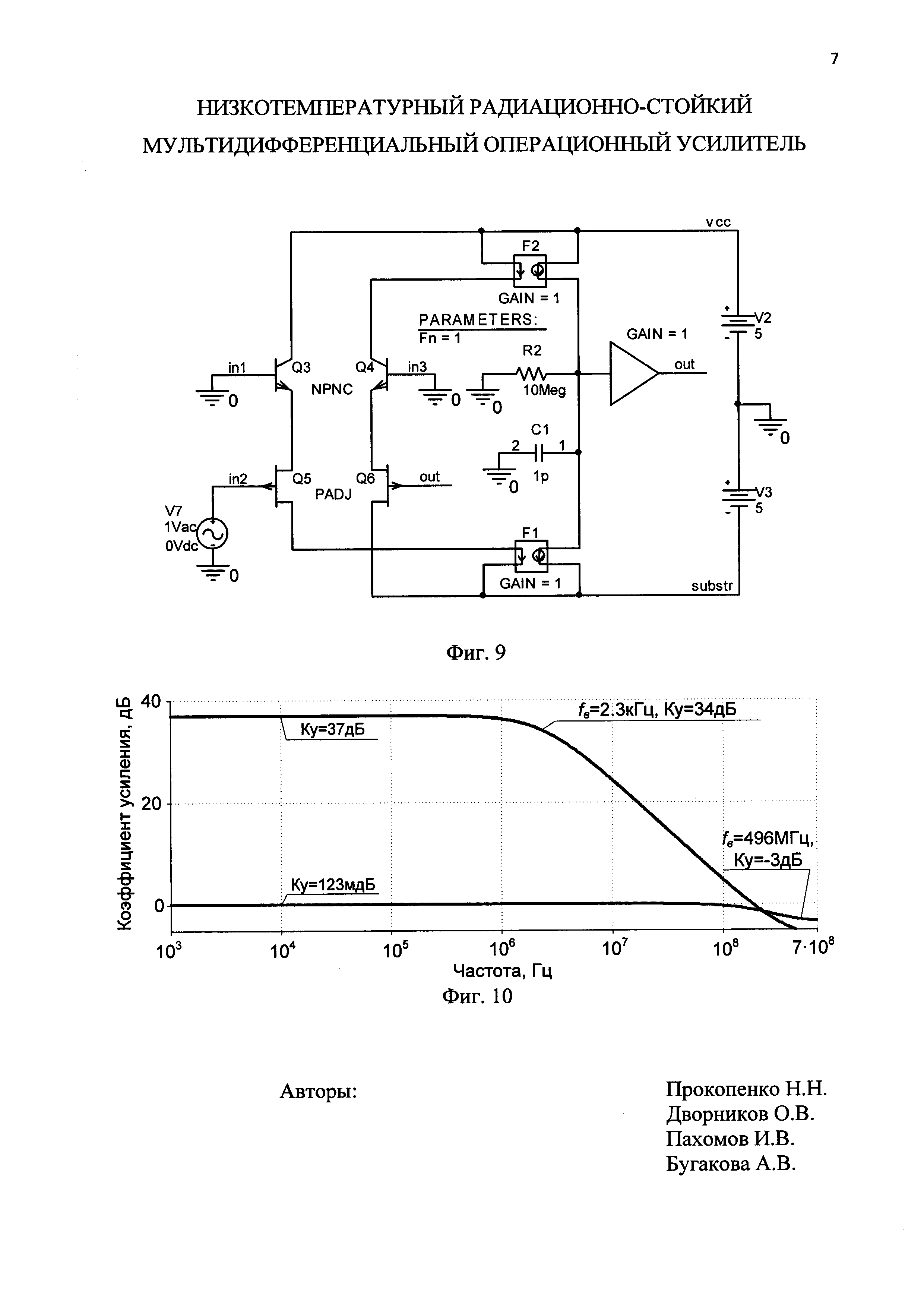

На чертеже фиг. 9 приведена схема известного устройства фиг. 1 (прототипа) в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 (ОАО «Интеграл», г. Минск) для случая, когда коэффициенты передачи токовых зеркал F1 и F2 равны единице (GAIN=1).

На чертеже фиг. 10 показаны амплитудно-частотные характеристики коэффициента усиления МОУ фиг. 9 со 100% отрицательной обратной связью и без отрицательной обратной связи.

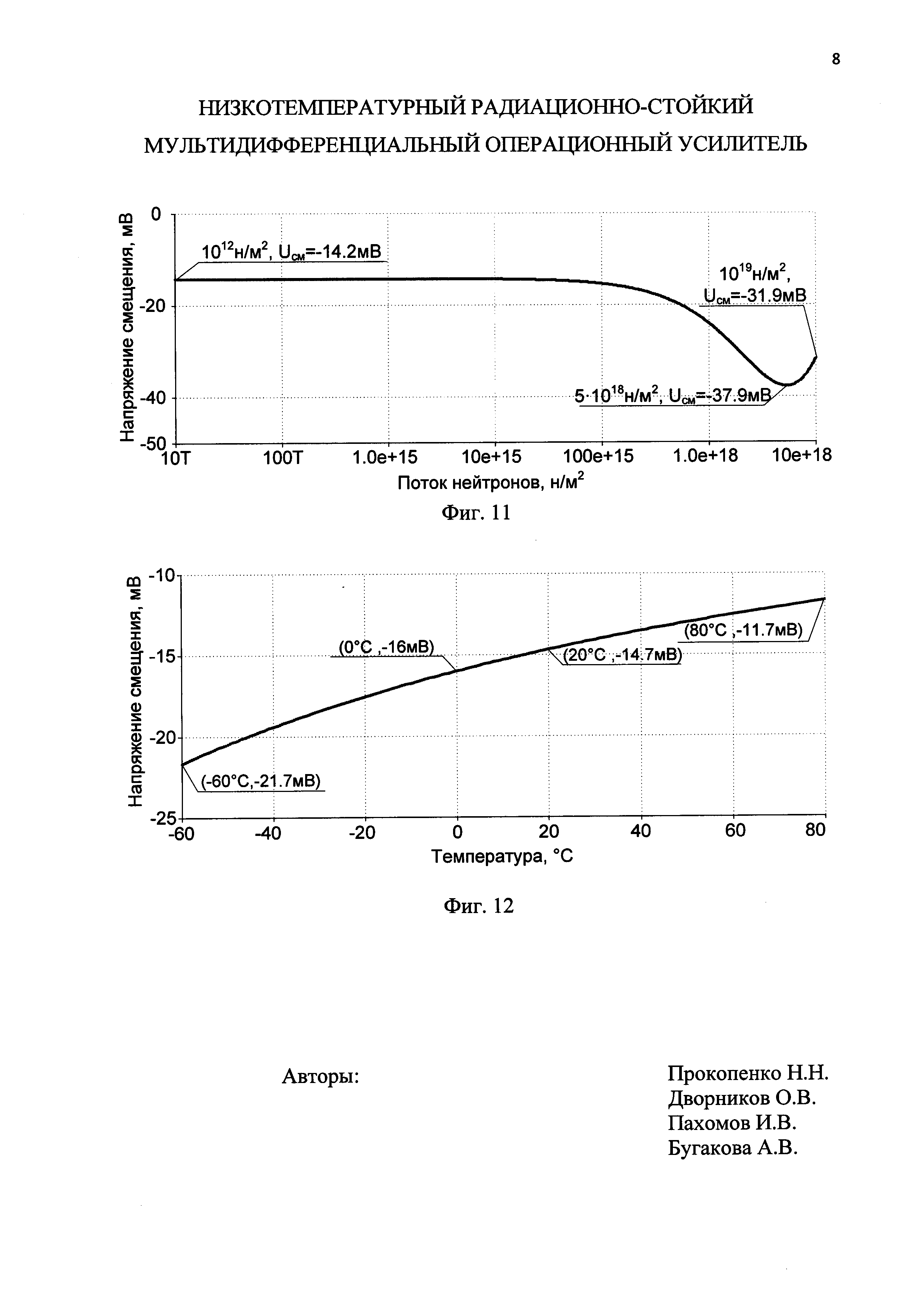

На чертеже фиг. 11 приведена зависимость напряжения смещения нуля МОУ фиг. 9 от потока нейтронов, а на чертеже фиг. 12 - от температуры в диапазоне минус 60 - плюс 80°С (б).

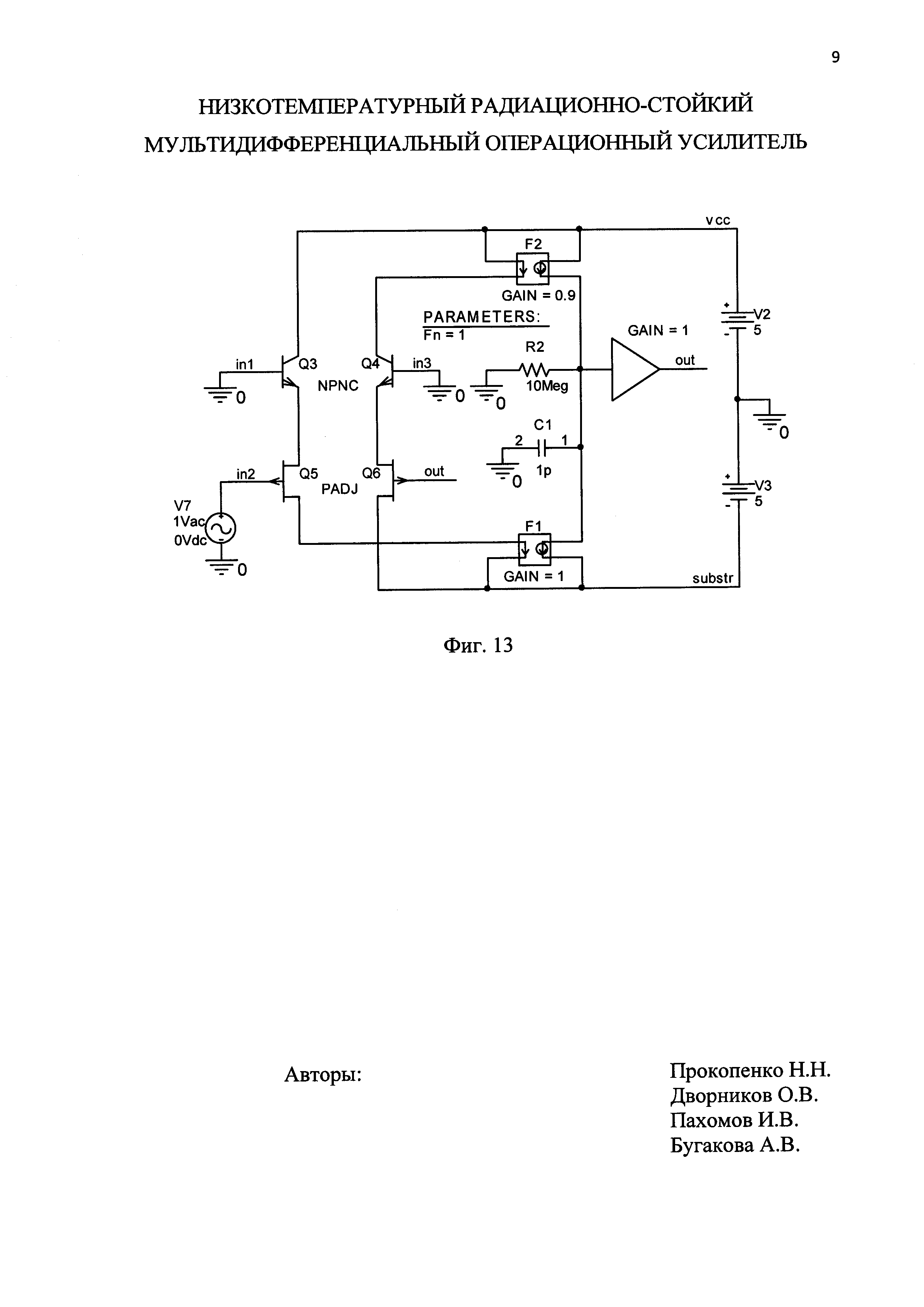

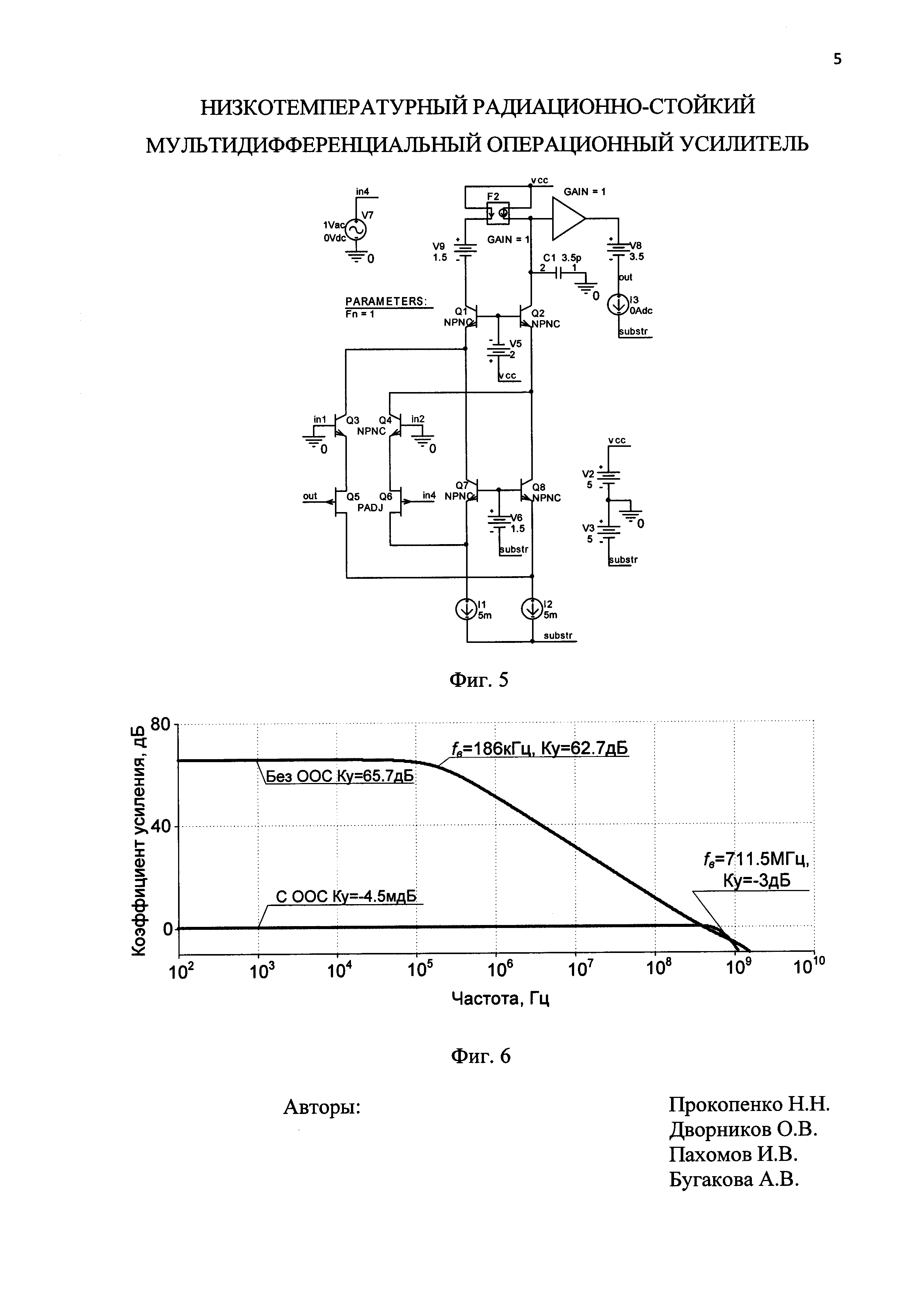

На чертеже фиг. 13 приведена схема известного устройства фиг. 1 (прототипа) в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 (ОАО «Интеграл», г. Минск) для случая, когда коэффициенты передачи токовых зеркал F1 и F2 неодинаковы (для F1 GAIN=1, для F2 GAIN=0.9).

На чертеже фиг. 14 приведена зависимость напряжения смещения нуля МОУ фиг. 13 от потока нейтронов, а на чертеже фиг. 15 - от температуры в диапазоне минус 60 - плюс 80°C (б).

Представленные на чертежах фиг. 7, фиг. 8 (заявляемое устройство), а также фиг. 11, фиг. 12, фиг. 14 и фиг. 15 (МОУ-прототип) графики зависимости напряжения смещения нуля от дестабилизирующих факторов показывают, что систематическая составляющая напряжения смещения нуля предлагаемого МОУ значительно меньше аналогичного параметра МОУ-прототипа.

Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель фиг. 2 содержит первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами (эмиттером и истоком), первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первую 15 и вторую 16 шины источника питания, а также выход устройства 17. Второй 5 токовый выход первого 1 дифференциального каскада соединен с первой 15 шиной источника питания через первый 18 токостабилизирующий двухполюсник и подключен к эмиттеру первого 19 согласующего транзистора, второй 12 токовый выход второго 8 дифференциального каскада соединен с эмиттером второго 20 согласующего транзистора и через второй 21 токостабилизирующий двухполюсник соединен с первой 15 шиной источника питания, причем базы первого 19 и второго 20 согласующих транзисторов подключены в первому 22 источнику напряжения смещения, первый 4 токовый выход первого 1 дифференциального каскада подключен к эмиттеру первого 23 выходного транзистора и соединен с коллектором второго 20 согласующего транзистора, коллектор первого 23 выходного транзистора соединен с первым 24 входом выходного дифференциального каскада 25, согласованного со второй 16 шиной источника питания, а база соединена с базой второго 26 выходного транзистора и со вторым 27 источником напряжения смещения, причем первый 11 токовый выход второго 8 дифференциального каскада соединен с эмиттером второго 26 выходного транзистора и подключен коллектору первого 19 согласующего транзистора, коллектор второго 26 выходного транзистора связан со вторым 28 входом выходного дифференциального каскада 25, выход которого соединен с выходом устройства 17.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, первый 2 входной транзистор первого 1 дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым 4 токовым выходом первого 1 дифференциального каскада, база соединена с первым 6 входом первого 1 дифференциального каскада, причем второй 3 входной транзистор первого 1 дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым 7 входом первого 1 дифференциального каскада, а сток связан со вторым 5 токовым выходом первого 1 дифференциального каскада, первый 9 входной транзистор второго 8 дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым 11 токовым выходом второго 8 дифференциального каскада, база соединена с первым 13 входом второго 8 дифференциального каскада, причем второй 10 входной транзистор второго 8 дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым 14 входом второго 8 дифференциального каскада, а сток связан со вторым 12 токовым выходом второго 8 дифференциального каскада.

Кроме этого, на чертеже фиг. 3 выходной дифференциальный каскад 25 реализован на основе токового зеркала 29 и буферного усилителя 30, согласованных со второй 16 шиной источника питания.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, первый 2 входной транзистор первого 1 дифференциального каскада и первый 9 входной транзистор второго 8 дифференциального каскада выполнены как полевые транзисторы с управляющим pn-переходом, а второй 3 входной транзистор первого 1 дифференциального каскада и второй 10 входной транзистор второго 8 дифференциального каскада выполнены как полевые КМОП-транзисторы, причем исток каждого из полевых транзисторов соответствует эмиттеру биполярного транзистора, сток - коллектору биполярного транзистора, а затвор - базе биполярного транзистора.

Кроме этого, на чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, первый 23 и второй 26 выходные транзисторы, а также первый 19 и второй 20 согласующие транзисторы выполнены как КМОП-транзисторы, стоки которых соответствует коллектору биполярных транзисторов, затвор эквивалентен базе, а исток эмиттеру биполярного транзистора.

Рассмотрим зависимость напряжения смещения нуля схемы фиг. 3 от параметров элементов.

При нулевом входном напряжении (первый 6 и второй 7 входы первого 1 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада связаны с общей шиной) воздействие температуры (или радиации) вызывает изменение токов истоков второго 3 входного транзистора первого 1 дифференциального каскада и второго 10 входного транзистора второго 8 дифференциального каскада на некоторую величину i0, связанную с дрейфом их входных характеристик. Приращения i0 передаются в коллекторные цепи первого 2 входного транзистора первого 1 дифференциального каскада и первого 9 входного транзистора второго 8 дифференциального каскада, а также в эмиттерные и коллекторные цепи первого 19 и второго 20 согласующих транзисторов. Поэтому, эмиттерные токи первого 23 и второго 26 выходных транзисторов:

где

,

,  ,

,

,

,  ,

,

где αij≈1 - коэффициент передачи по току эмиттера ij-транзистора.

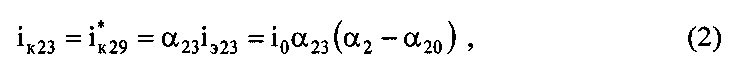

После преобразования формулы (1) можно найти изменения коллекторных токов

Из формул (2) и (3) следует важный вывод - при идентичных коэффициентах α2=α20, α9=α19 приращения i0, вызванные дестабилизирующими факторами, не передаются в выходную цепь МОУ (выходной дифференциальный каскад 25), которая в этом случае может иметь асимметрию в коэффициентах усиления по току. В МОУ-прототипе фиг. 1 данный эффект отсутствует.

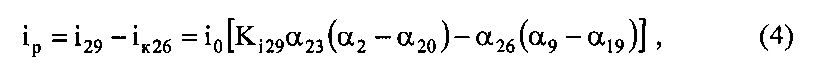

Определим Uсм в заявляемом МОУ фиг. 3 при асимметрии в коэффициентах передачи токов выходного дифференциального каскада 25.

Для высокоимпедансного узла Σ1 при нулевом входном токе буферного усилителя 30 можно записать следующие уравнения для схемы фиг. 3:

где i29, Ki29≈1 - выходной ток и коэффициент передачи по току токового зеркала 29;

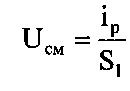

ip - разностный ток в высокоимпедансном узле Σ1, определяющий напряжение смещения нуля (Uсм) МОУ:

,

,

где S1≈2S3 - крутизна преобразования входного напряжения МОУ (напряжения между первым 6 и вторым 7 входами первого 1 дифференциального каскада) в выходной ток высокоимпедансного узла Σ1;

S3 - крутизна стокозатворной характеристики второго 3 входного полевого транзистора первого 1 дифференциального каскада.

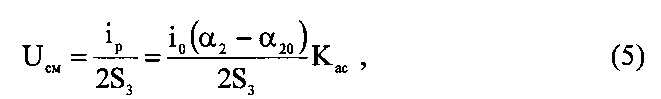

Если предположить, что α9-α19=α2-α20, Ki29≈1, i23≈1, то из (4) можно найти, что напряжение смещения нуля (с учетом асимметрии выходного дифференциального каскада 25) определяется уравнением:

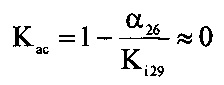

где  - коэффициент асимметрии выходного дифференциального каскада 25.

- коэффициент асимметрии выходного дифференциального каскада 25.

Последние уравнения показывают, что при α2=α3 асимметрия выходного дифференциального каскада 25 не влияет на Uсм.

В МОУ-прототипе фиг. 1 напряжение смещения нуля

где  - коэффициент асимметрии выходной цепи МОУ-прототипа фиг. 1;

- коэффициент асимметрии выходной цепи МОУ-прототипа фиг. 1;

Ki1, Ki2 - коэффициенты передачи по току выходных токовых зеркал на различных (n-p-n и p-n-р) транзисторах, причем Ki1≠ Ki2.

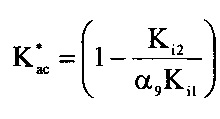

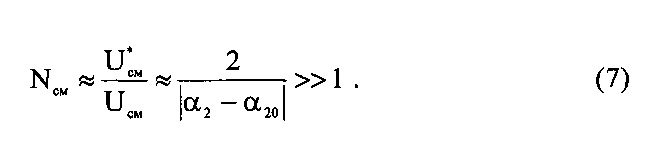

Если считать, что  , то из (5) и (6) можно найти, что в заявляемом МОУ фиг. 3 напряжение смещения нуля уменьшается в Nсм-раз, где

, то из (5) и (6) можно найти, что в заявляемом МОУ фиг. 3 напряжение смещения нуля уменьшается в Nсм-раз, где

Если в схеме фиг. 3 использовать только полевые транзисторы (см., например, фиг. 4), то в этом случае α2=1, α20=1, α9=1, α19=1 и, как следствие, температурные и радиационные изменения статического режима первого 2 и второго 3 входных транзисторов первого 1 дифференциального каскада и первого 9 и второго 10 входных транзисторов второго 8 дифференциального каскада не будут влиять на рассмотренную систематическую составляющую Uсм.

Для работы предлагаемого МОУ в диапазоне более низких, в т.ч. криогенных, температур целесообразно исключать биполярные транзисторы, что реализуется в схеме фиг. 4.

Таким образом, заявляемое устройство характеризуется более высокими значениями параметров, характеризующими его прецизионность, и имеет потенциальные возможности работы при низких температурах с одновременным воздействием радиации [18-21].

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №4.596.958, fig. 2.

2. Патент US №4.901.031, fig. 3.

3. Патент US №5.291.149, fig. 4.

4. Патент US №4.357.578, fig. 1.

5. Патент US №3.703.650, fig. 1.

6. Патент US №2.070.768, fig. 1.

7. Патент US №2.571.579, fig. 4.

8. Патент US №3.873.933, fig. 2.

9. Патент US №7.202.738, fig. 10.

10. Патент US №4.198.610, fig. 3.

11. Патент US №6.407.537, fig. 1.

12. Патент US №4.667.165, fig. 3

13. Патентная заявка US 2010/0117735, fig. 2.

14. Патент РФ 2523124.

15. Патент РФ 2517699.

16. Prokopenko, N.N. The Radiation-Hardened Differential Stages and Op Amps without Classical Reference Current Source / N.N. Prokopenko, O.V. Dvornikov, I.V. Pakhomov and N.V. Butyrlagin // 2015 Conference on Radiation Effects on Components and Systems (RADECS), September 14th-18th, 2015, Moscow, Russia. DOI: 10.1109/RADECS.2015.7365681.

17. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

18. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 1/O. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №4. С. 44-49.

19. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №5. С. 24-28.

20. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 3 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №6. С. 34-39.

21. Dvornikov, О.V. Specialized Integral Microcircuit of the Amplifier of Photosignals / О.V. Dvornikov, V.A. Chekhovskii, V.L. Dyatlov, and N.N. Prokopenko // Russian Microelectronics, 2015, Vol. 44, No. 3, pp. 197-202. (ISSN 1063-7397). DOI: 10.1134/S1063739715020031.

22. Dvornikov, О.V. An Integrated Circuit of a Universal Comparator / О.V. Dvornikov, V.A. Chekhovskii, V.L. Dyatlov, and N.N. Prokopenko // Instruments and Experimental Techniques, 2015, Vol. 58, No. 3, pp. 483-487. DOI: 10.1134/S0020441215030197.

23. Dvornikov, О.V. An integrated circuit for silicon photomultipliers tubes / O.V. Dvornikov, V.A. Tchekhovsi, V.L. Dyatlov, and N.N. Prokopenko // Instruments and Experimental Techniques, vol. 57, no. 1, pp. 40-44, Feb. 2014. WOS: 000331640100007, JCR 2013 Impact Factor - 0.349 DOI: 10.1134/S0020441214010047.

24. Dvornikov, О.V. Influence of Ionizing Radiation on the Parameters of an Operational Amplifier Based on Complementary Bipolar Transistors / О.V. Dvornikov, V.A. Tchekhovski, V.L. Dziatlau, and N.N. Prokopenko // Russian Microelectronics, 2016, Vol. 45, No. 1, pp. 54-62. (ISSN 1063-7397). DOI: 10.1134/S1063739716010030.