Результат интеллектуальной деятельности: СПОСОБ ЗАПИСИ ДАННЫХ И СИСТЕМА ПАМЯТИ

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Варианты осуществления настоящего изобретения относятся к компьютерным технологиям, в частности к способу записи данных и системе памяти.

УРОВЕНЬ ТЕХНИКИ

Существующая система памяти, главным образом, включает в себя контроллер памяти (MC), устройство памяти и подобное. Контроллер памяти и устройство памяти осуществляют обмен данными посредством использования протокола удвоенной скорости передачи данных (DDR). Контроллер памяти записывает данные в устройство памяти способом пакетной (пакет) записи, и размер блока данных, в который осуществляется одна пакетная запись, является шириной шины данных памяти; кэш (кэш) и система памяти осуществляют обмен данными в единице строки кэша (строка кэша), и размер данных, считываемых или записываемых всякий раз, является размером одной строки кэша у кэша последнего уровня (LLC) в кэше. Вследствие этого контроллеру памяти требуется осуществлять несколько последовательных пакетных записей, чтобы записать данные одной строки кэша в устройство памяти, при этом число последовательных пакетных записей именуется длиной пакета (BL).

В протоколе DDR3, BL, как правило, равна 8, и размер блока данных в одной пакетной записи используется в качестве степени разбиения, чтобы разделить одну строку кэша на несколько блоков данных. Например, если размер одной строки кэша у LLC составляет 64 байта и ширина шины данных памяти составляет 64 бита, когда данные пакетной записи появляются на шине данных, контроллеру памяти требуется выполнить восемь пакетных записей в последовательных четырех тактовых циклах, чтобы записать данные одной строки кэша у LLC в устройство памяти. Тем не менее, фактически, когда данные одной строки кэша у LLC записываются в устройство памяти, многие блоки данных не изменяются. Во время процесса записи существует возможность того, что недостоверные данные (неизмененные данные) записываются в устройство памяти в некоторых пакетных записях. В результате, скорость записи достоверных данных (измененные данные) низкая, и запись большого объема недостоверных данных ведет к увеличению энергопотребления системы памяти, тем самым уменьшая эффективность системы памяти.

В технологии BC4 (burst chop 4), поддерживаемой посредством протокола DDR3, когда контроллер памяти записывает данные в устройство памяти, всего четыре пакетные записи происходят в двух последовательных тактовых циклах, и отсутствует пакетная запись в последующих двух тактовых циклах, чтобы записать первую половину или вторую половину данных одной строки кэша в устройство памяти. Во время данного процесса в рамках первых двух тактовых циклов, также возможно, что при способе записи, при котором не учитывается, изменились или нет данные в блоке данных, недостоверные данные записываются в устройство памяти в некоторых пакетных записях. В результате, скорость записи достоверных данных низкая, и запись большого объема недостоверных данных ведет к увеличению энергопотребления системы памяти, тем самым уменьшая эффективность системы памяти.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Варианты осуществления настоящего изобретения предоставляют способ записи данных и систему памяти, при этом различают, изменились ли данные в блоке данных строки кэша, и запись выполняется только по измененному блоку данных, так что достигаются цели, связанные с тем, чтобы быстро записывать достоверные данные, уменьшать энергопотребление системы памяти и повышать эффективность системы памяти.

В соответствии с первым аспектом, вариант осуществления настоящего изобретения предоставляет способ записи данных, который применяется к системе памяти, включающей в себя, по меньшей мере, контроллер памяти и устройство памяти, и включает в себя этапы, на которых:

принимают посредством контроллера памяти информацию изменения, отправленную посредством кэша, при этом информация изменения является информацией, которая генерируется после того, как кэш делит первую что-будет-записана строку кэша строка кэша у кэша последнего уровня (LLC) на, по меньшей мере, два блока данных, и которая используется, чтобы указать, изменились ли данные в каждом из, по меньшей мере, двух блоков данных; и

применительно к каждому неизмененному блоку данных, в котором данные не изменились, как указывается посредством информации изменения, пропускают отправку посредством контроллера памяти в соответствии с информацией изменения адреса столбца, соответствующего каждому неизмененному блоку данных, и данных, соответствующих каждому неизмененному блоку данных, к устройству памяти; и применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, отправляют посредством контроллера памяти в соответствии с информацией изменения адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти; и

записывают посредством устройства памяти в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данные длины пакета в каждый измененный блок данных, при этом длина пакета равна числу из, по меньшей мере, двух блоков данных.

В первом возможном варианте реализации первого аспекта, этап, на котором: применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, отправляют посредством контроллера памяти в соответствии с информацией изменения адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти, включает в себя этап, на котором:

если число измененных блоков данных первой что-будет-записана строки кэша равно длине пакета, отправляют посредством контроллера памяти адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти; и

этап, на котором записывают посредством устройства памяти в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данные длины пакета в каждый измененный блок данных, включает в себя этап, на котором:

выполняют посредством устройства памяти в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, запись данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша.

Во втором возможном варианте реализации первого аспекта, этап, на котором: применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, отправляют посредством контроллера памяти в соответствии с информацией изменения адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти, включает в себя этап, на котором:

если число измененных блоков данных первой что-будет-записана строки кэша меньше длины пакета, отправляют адрес столбца и данные, соответствующие каждому измененному блоку данных первой что-будет-записана строки кэша, и адрес столбца и данные, соответствующие каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша к устройству памяти, при этом сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше либо равна длине пакета; и

этап, на котором записывают посредством устройства памяти в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данные длины пакета в каждый измененный блок данных, включает в себя этап, на котором:

выполняют посредством устройства памяти в соответствии с каждым адресом столбца первой что-будет-записана строки кэша и каждым адресом столбца, по меньшей мере, одной второй что-будет-записана строки кэша, запись данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша и каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша, при этом вторая что-будет-записана строка кэша является что-будет-записана строкой кэша за исключением первой что-будет-записана строки кэша в LLC.

Со ссылкой на второй возможный вариант реализации первого аспекта, в третьем возможном варианте реализации первого аспекта первая что-будет-записана строка кэша и, по меньшей мере, одна вторая что-будет-записана строка кэша, находятся в одном и том же ряду одного и того же Банка группы хранения, и отсутствует команда чтения того же самого ряда в LLC.

Со ссылкой на первый аспект или любой из с первого по третий возможные варианты реализации первого аспекта, в четвертом возможном варианте реализации первого аспекта этап, на котором записывают посредством устройства памяти в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данные длины пакета в каждый измененный блок данных, включает в себя этап, на котором:

когда буферы адреса столбца, число которых равно длине пакета, и дешифраторы столбца, число которых равно длине пакета, размещаются в устройстве памяти, выполняют запись данных по каждому измененному блоку данных посредством использования независимого буфера адреса столбца и независимого дешифратора столбца.

В соответствии со вторым аспектом, вариант осуществления настоящего изобретения предоставляет систему памяти, включающую в себя, по меньшей мере, контроллер памяти и устройство памяти, при этом:

контроллер памяти выполнен с возможностью: приема информации изменения, отправленной посредством кэша, при этом информация изменения является информацией, которая генерируется после того, как кэш делит первую что-будет-записана строку кэша строка кэша у кэша последнего уровня (LLC) на, по меньшей мере, два блока данных, и которая используется, чтобы указать, изменились ли данные в каждом из, по меньшей мере, двух блоков данных; применительно к каждому неизмененному блоку данных, в котором данные не изменились, как указывается посредством информации изменения, пропуска отправки в соответствии с информацией изменения адреса столбца, соответствующего каждому неизмененному блоку данных, и данных, соответствующих каждому неизмененному блоку данных, к устройству памяти; и применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, отправки в соответствии с информацией изменения адреса столбца, соответствующего каждому измененному блоку данных, и данных, соответствующих каждому измененному блоку данных, к устройству памяти; и

устройство памяти выполнено с возможностью записи в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данных длины пакета в каждый измененный блок данных, при этом длина пакета равна числу из, по меньшей мере, двух блоков данных.

В первом возможном варианте реализации второго аспекта, контроллер памяти выполнен с возможностью: если число измененных блоков данных первой что-будет-записана строки кэша равно длине пакета, отправки адреса столбца, соответствующего каждому измененному блоку данных, и данных, соответствующих каждому измененному блоку данных, к устройству памяти; и

устройство памяти выполнено с возможностью выполнения в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, записи данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша.

Во втором возможном варианте реализации второго аспекта, контроллер памяти выполнен с возможностью: если число измененных блоков данных первой что-будет-записана строки кэша меньше длины пакета, отправки адреса столбца и данных, соответствующих каждому измененному блоку данных первой что-будет-записана строки кэша, и адреса столбца и данных, соответствующих каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша к устройству памяти, при этом сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше, либо равна длине пакета; и

устройство памяти выполнено с возможностью выполнения в соответствии с каждым адресом столбца первой что-будет-записана строки кэша и каждым адресом столбца, по меньшей мере, одной второй что-будет-записана строки кэша, записи данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша и каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша, при этом вторая что-будет-записана строка кэша является что-будет-записана строкой кэша за исключением первой что-будет-записана строки кэша в LLC.

Со ссылкой на второй возможный вариант реализации второго аспекта, в третьем возможном варианте реализации второго аспекта первая что-будет-записана строка кэша и, по меньшей мере, одна вторая что-будет-записана строка кэша находятся в одном и том же ряду одного и того же Банка группы хранения, и отсутствует команда чтения того же самого ряда в LLC.

Со ссылкой на второй аспект или первый, второй, или третий возможные варианты реализации второго аспекта, в четвертом возможном варианте реализации второго аспекта, когда буферы адреса столбца, число которых равно длине пакета, и дешифраторы столбца, число которых равно длине пакета, размещаются в устройстве памяти, запись данных выполняется по каждому измененному блоку данных посредством использования независимого буфера адреса столбца и независимого дешифратора столбца.

В способе записи данных и системе памяти, предоставленных в вариантах осуществления настоящего изобретения, контроллер памяти отправляет в соответствии с информацией изменения, отправленной посредством кэша, адрес столбца и данные к устройству памяти только применительно к блоку данных, в котором данные изменились, так что устройство памяти выполняет запись данных по каждому измененному блоку данных и не выполняет запись по блоку данных, у которого данные не изменились. Вследствие этого достигаются цели, связанные с тем, чтобы быстро записывать достоверные данные, уменьшать энергопотребление системы памяти и повышать эффективность системы памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Чтобы описать технические решения в вариантах осуществления настоящего изобретения или в известном уровне техники более понятно, нижеследующее кратко представляет сопроводительные чертежи, требуемые для описания вариантов осуществления или известного уровня техники.

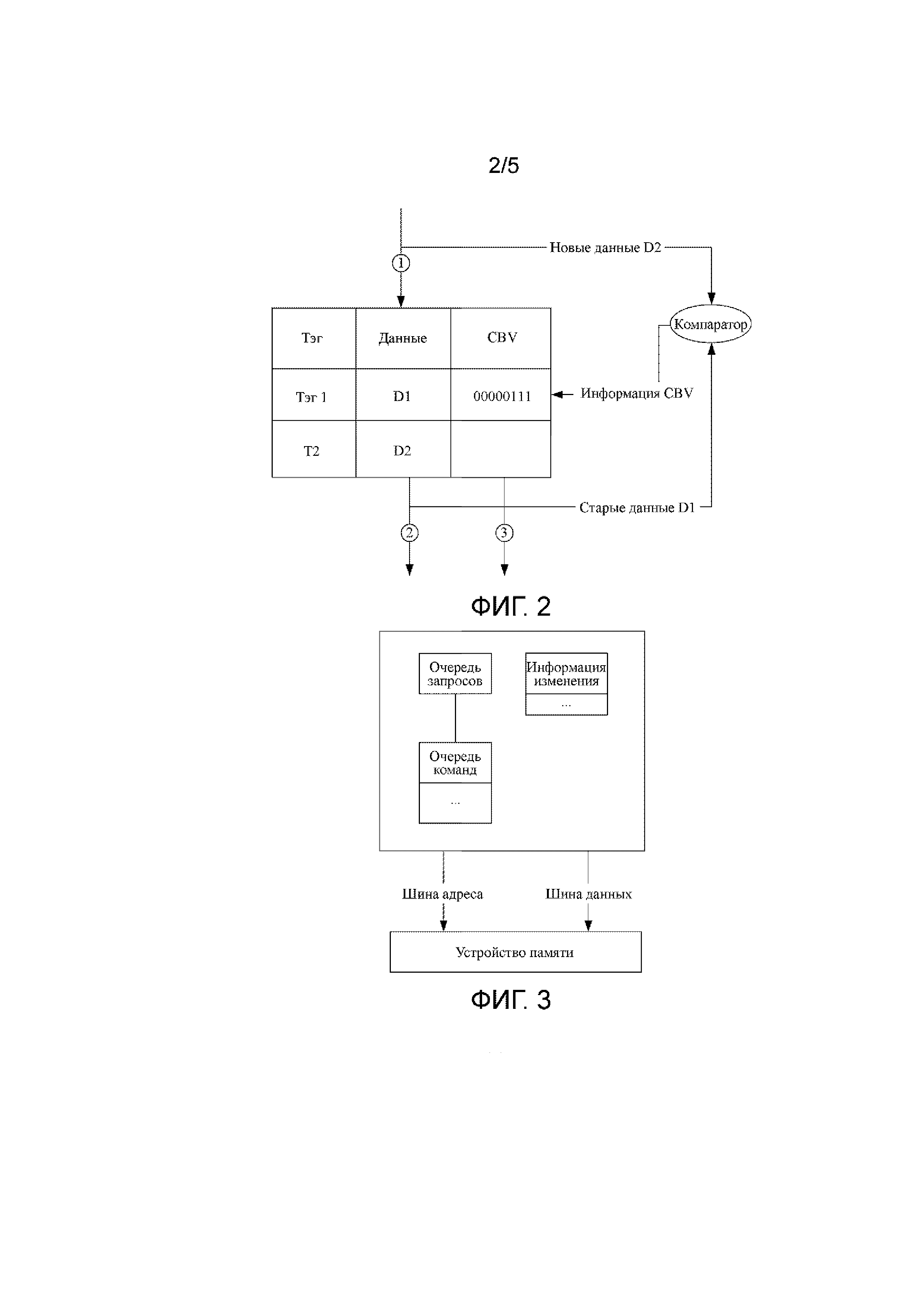

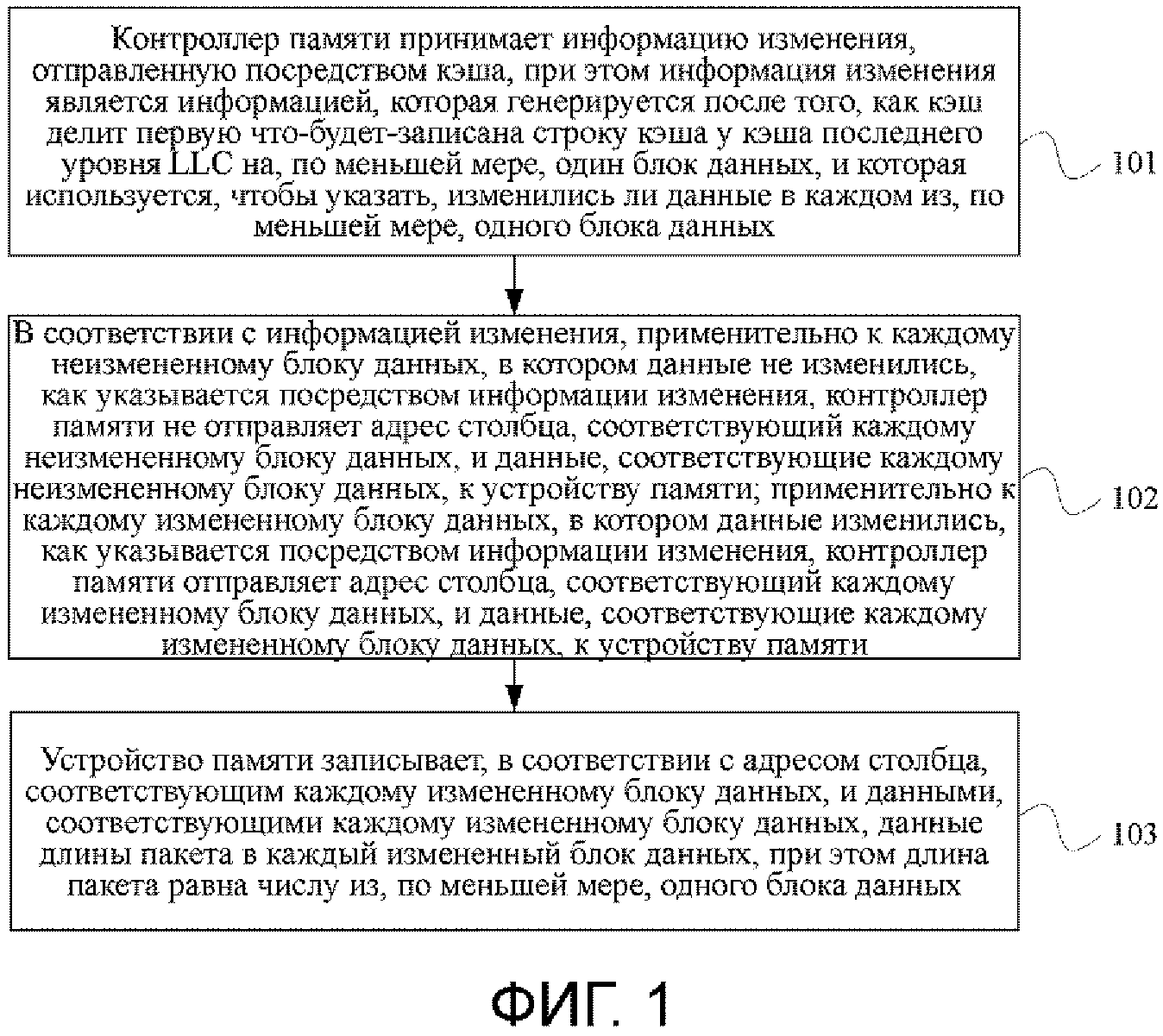

Фиг. 1 является блок-схемой способа записи данных в соответствии с настоящим изобретением;

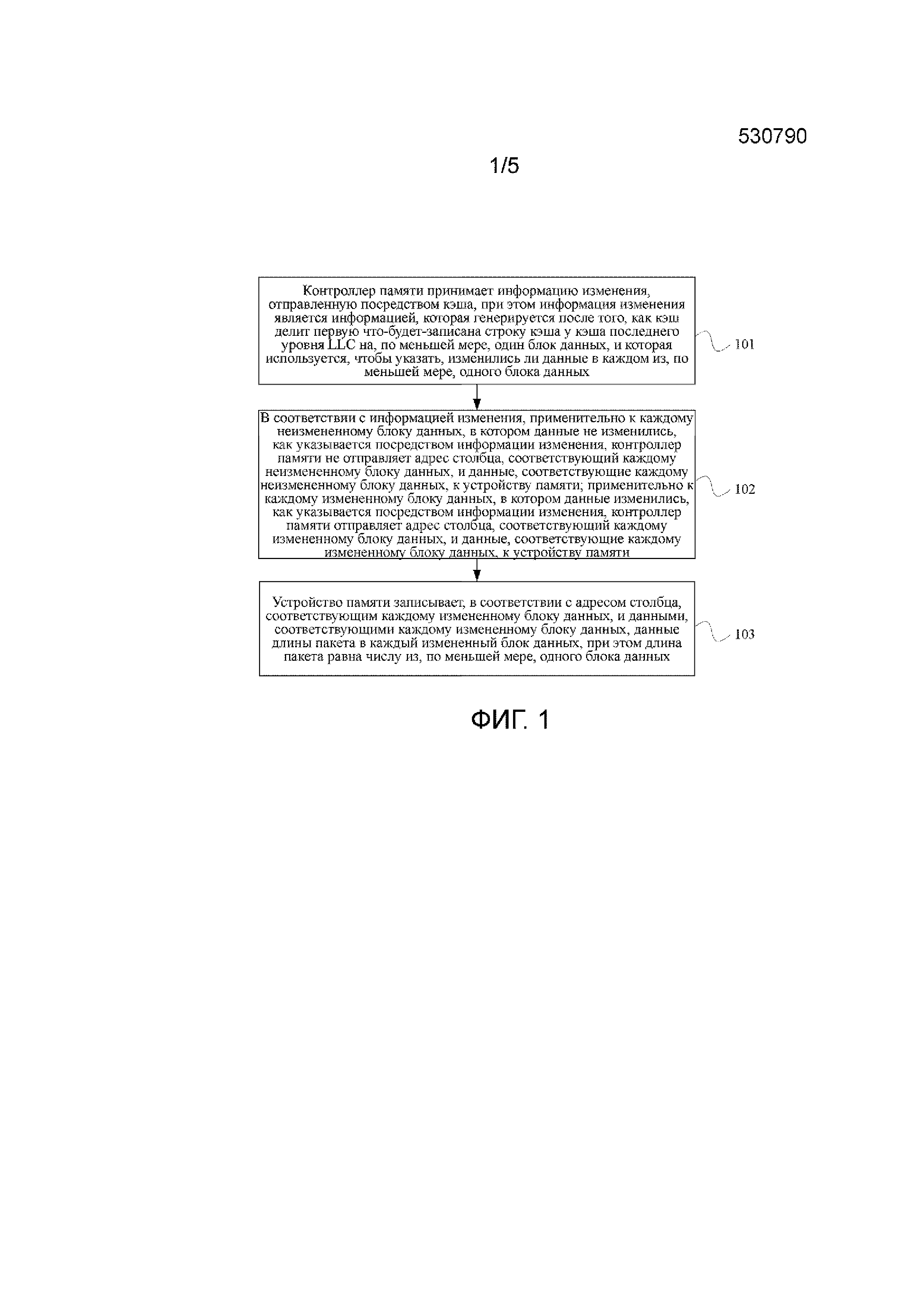

Фиг. 2 является принципиальной схемой, показывающей работу LLC в способе записи данных в соответствии с настоящим изобретением;

Фиг. 3 является принципиальной схемой, показывающей работу контроллера памяти в способе записи данных в соответствии с настоящим изобретением;

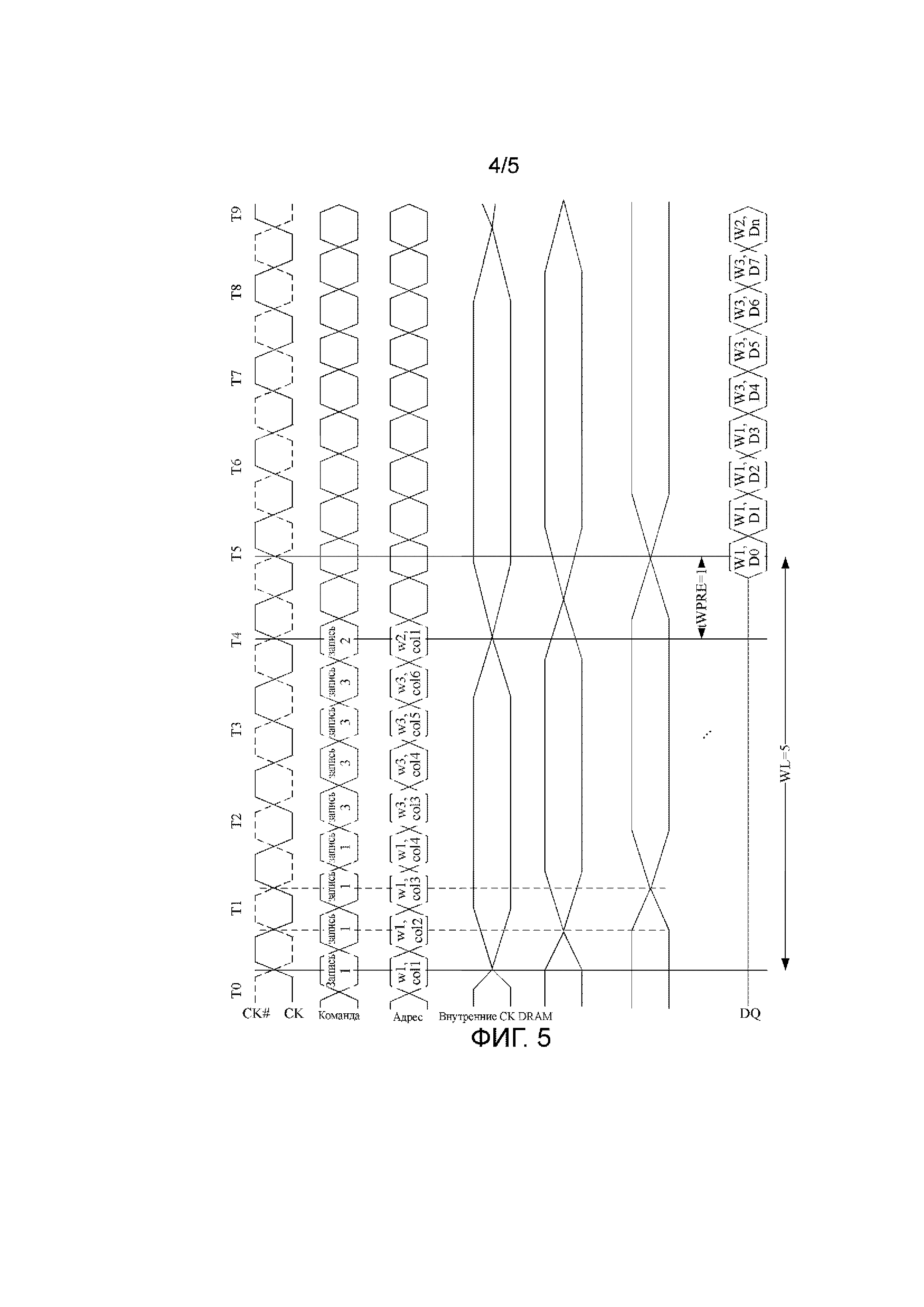

Фиг. 4 является принципиальной схемой, показывающей работу устройства памяти в способе записи данных в соответствии с настоящим изобретением;

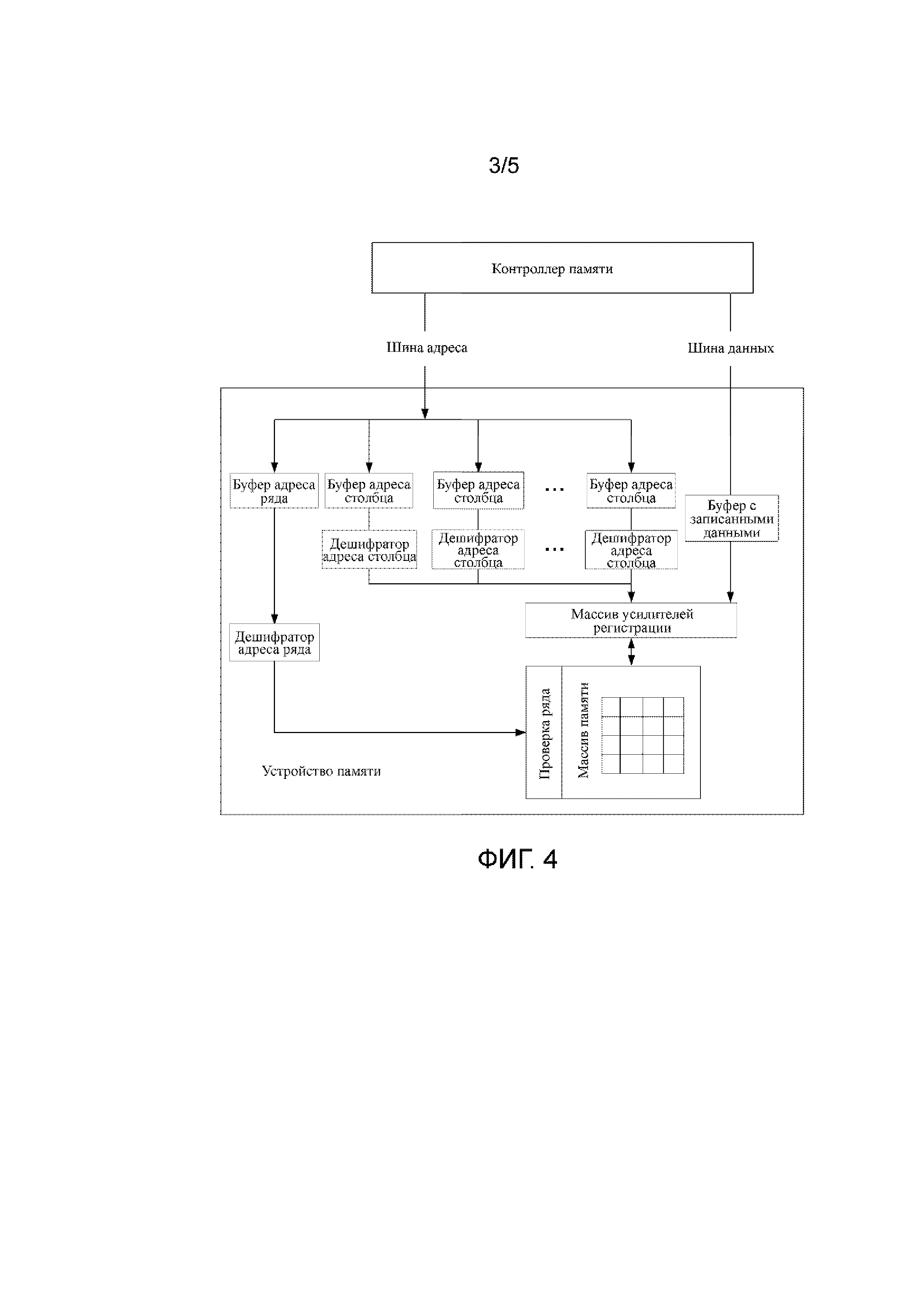

Фиг. 5 является циклограммой объединения команд записи в способе записи данных в соответствии с настоящим изобретением; и

Фиг. 6 является принципиальной структурной схемой системы памяти в соответствии с настоящим изобретением.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Чтобы сделать более понятными цели, технические решения и преимущества вариантов осуществления настоящего изобретения, нижеследующее четко и полно описывает технические решения в вариантах осуществления настоящего изобретения со ссылкой на сопроводительные чертежи в вариантах осуществления настоящего изобретения.

Фиг. 1 является блок-схемой способа записи данных в соответствии с Вариантом 1 Осуществления настоящего изобретения. Данный вариант осуществления применяется к сценарию, при котором данные записываются в системе памяти, включающей в себя, по меньшей мере, контроллер памяти и устройство памяти. В частности, данный вариант осуществления включает в себя следующие этапы:

101. Контроллер памяти принимает информацию изменения, отправленную посредством кэша, при этом информация изменения является информацией, которая генерируется после того, как кэш делит первую что-будет-записана строку кэша строка кэша у кэша последнего уровня (LLC) на, по меньшей мере, один блок данных, и которая используется, чтобы указать, изменились ли данные в каждом из, по меньшей мере, одного блока данных.

Кэш располагается между центральным модулем обработки (центральный модуль обработки, CPU) и системой памяти большой емкости и имеет относительно высокую скорость доступа. На данном этапе кэш делит первую что-будет-записана строку кэша строка кэша у кэша последнего уровня (LLC) на, по меньшей мере, один блок данных, и добавляет один бит флага к каждому из, по меньшей мере, одного блока данных, при этом бит флага указывает, изменились ли данные в блоке данных, одной строке кэша требуется несколько битов флага, и несколько битов флага каждой строки кэша составляют информацию изменения, указывающую на то, изменились ли данные в каждом из, по меньшей мере, одного блока данных строки кэша. Например, одна строка кэша делится на несколько блоков данных посредством использования ширины шины данных памяти в качестве степени разбиения, и один бит флага, представленный посредством 0 или 1, добавляется к каждому из нескольких блоков данных, при этом 0 указывает на то, что данные в блоке данных не изменились, т.е. значение блока данных не изменилось; и 1 указывает на то, что данные в блоке данных изменились, т.е. значение блока данных изменилось. Биты флага каждой строки кэша составляют вектор измененного блока (вектор измененного блока, CVB), т.е. информацию изменения, строки кэша. В частности, предполагая, что размер одной строки кэша составляет 64 байта и ширина шины данных памяти составляет 64 бита, одна строка кэша может быть разделена на восемь блоков данных, и длина пакета BL является равной 8, т.е. размер одного CBV составляет восемь бит.

Фиг. 2 является принципиальной схемой, показывающей работу LLC в способе записи данных в соответствии с настоящим изобретением. Как показано на Фиг. 2, когда кэш верхнего уровня кэша записывает данные в одну строку кэша у LLC, кэш верхнего уровня сначала считывает старые данные (старые данные) в строке кэша и сравнивает старые данные с что-будут-записаны данными (новыми данными); если данные в одном блоке данных не изменились, кэш верхнего уровня устанавливает бит флага данного блока данных в 0; если данные изменились, кэш верхнего уровня устанавливает бит флага данного блока данных в 1. Когда LLC записывает данные строки кэша в систему памяти, информация CBV, соответствующая строке кэша, пересылается к контроллеру памяти в системе памяти, и контроллер памяти принимает информацию CBV, т.е. принимает соответствующую информацию изменения. Взяв в качестве примера блок данных, тэгом которого является Тэг1, кэш верхнего уровня исполняет следующие этапы: (1) при записи данных в строку кэша у LLC считывает старые данные D1 в блоке данных, сначала сравнивает D1 с что-будут-записаны данными D2 посредством использования компаратора и записывает результат сравнения в CBV. Подобным образом, кэш верхнего уровня считывает данные других блоков данных в строке кэша, сравнивает данные с новыми данными, которые будут записаны в эти блоки данных, и записывает результат сравнения каждого из других блоков данных в CBV, чтобы получить информацию CBV данной строки кэша, т.е. информацию изменения. Когда LLC исполняет следующий этап: (2) записывает данные в систему памяти, т.е. отправляет запрос записи к системе памяти, чтобы записать данные, LLC одновременно исполняет следующий этап: (3) отправляет информацию изменения что-будет-записана строки кэша к системе памяти.

102. В соответствии с информацией изменения, применительно к каждому неизмененному блоку данных, в котором данные не изменились, как указывается посредством информации изменения, контроллер памяти не отправляет адрес столбца, соответствующий каждому неизмененному блоку данных, и данные, соответствующие каждому неизмененному блоку данных, к устройству памяти; применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, контроллер памяти отправляет адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти.

На данном этапе, контроллер памяти в системе памяти определяет в соответствии с принятой информацией изменения, требуется ли выполнить запись по каждому блоку первой что-будет-записана строки кэша. В частности, обратимся к Фиг. 3.

Фиг. 3 является принципиальной схемой, показывающей работу контроллера памяти в способе записи данных в соответствии с настоящим изобретением. Обращаясь к Фиг. 3, контроллер памяти в системе памяти включает в себя очередь запросов (очередь транзакций), очередь команд (очередь команд) и подобное. Запрос записи у LLC сначала помещается в очередь запросов, контроллер памяти преобразует запрос записи в конкретную команду для оперирования устройством памяти и сохраняет команду в очереди команд. Контроллер памяти определяет в соответствии с информацией изменения первой что-будет-записана строки кэша, требуется ли выполнять запись по каждому из, по меньшей мере, одного блока данных первой что-будет-записана строки кэша. В частности, применительно к неизмененному блоку данных, в котором данные не изменились, пакетная запись не выполняется; применительно к измененному блоку данных, в котором данные изменились, адрес столбца и данные, соответствующие измененному блоку данных, отправляются к контроллеру памяти каждый такт посредством использования шины адреса, шины данных и подобного. Так как данные передаются как по переднему фронту, так и заднему фронту одного тактового цикла в технологии DDR, а частота данных шины данных соответствует удвоенной тактовой частоте шины данных, то каждый такт является половиной тактового цикла.

103. Устройство памяти записывает в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данные длины пакета в каждый измененный блок данных, при этом длина пакета равна числу из, по меньшей мере, одного блока данных.

Как правило, число блоков данных, на которые делится первая что-будет-записана строка кэша, является числом последовательных пакетных записей. На данном этапе, устройство памяти выполняет запись данных дины пакета по каждому измененному блоку данных в соответствии с каждым принятым адресом столбца и каждым фрагментом принятых данных.

Опционально, в сравнении с тем, что одно устройство памяти имеет только один буфер адреса столбца и один дешифратор столбца в известном уровне техники, устройство памяти в данном варианте осуществления включает в себя несколько буферов адреса столбца и несколько дешифраторов столбца. Фиг. 4 является принципиальной схемой, показывающей работу устройства памяти в способе записи данных в соответствии с настоящим изобретением. Обращаясь к Фиг. 4, в данном варианте осуществления устройство памяти включает в себя буфер адреса ряда (буфер адреса ряда), дешифратор адреса ряда (дешифратор ряда), буферы адреса столбца (буфер адреса столбца), число которых равно длине пакета, дешифраторы адреса столбца (дешифратор столбца), число которых равно длине пакета, массив усилителей регистрации (массив усилителей регистрации, SAA), массив памяти (массив памяти), буфер с записанными данными (данные в буфере) и подобное. Применительно к каждому измененному блоку данных, устройство памяти выполняет запись данных посредством использования независимого буфера адреса столбца и независимого дешифратора столбца. Всякий раз, когда записываются данные, несколько адресов столбца, отправленные посредством контроллера памяти, сохраняются в разных буферах адреса столбца и одновременно дешифруются посредством использования разных дешифраторов столбца, выбираются разные столбцы в SAA, данные записываются в эти выбранные столбцы, и в заключении данные в SAA записываются в массив памяти.

В способе записи данных, предоставленном в данном варианте осуществления настоящего изобретения, контроллер памяти отправляет в соответствии с информацией изменения, отправленной посредством кэша, адрес столбца и данные к устройству памяти только применительно к блоку данных, в котором данные изменились, так что устройство памяти выполняет запись данных по каждому измененному блоку данных и не выполняет запись по блоку данных, в котором данные не изменились. Вследствие этого достигаются цели, связанные с тем, чтобы быстро записывать достоверные данные, уменьшать энергопотребление системы памяти и повышать эффективность системы памяти.

Опционально, в вышеупомянутом Варианте 1 Осуществления контроллер памяти определяет в соответствии с информацией изменения, требуется ли выполнять запись по каждому из, по меньшей мере, одного блока данных. Применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, если число измененных блоков данных первой что-будет-записана строки кэша равно длине пакета, контроллер памяти отправляет адрес столбца, соответствующий каждому измененному блоку данных, и данные, соответствующие каждому измененному блоку данных, к устройству памяти. Соответственно устройство памяти выполняет в соответствии с каждым адресом столбца запись данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша.

В частности, кэш делит первую что-будет-записана строку кэша у LLC на, по меньшей мере, один блок данных и выполняет одну пакетную запись по каждому из, по меньшей мере, одного блока данных, при этом число блоков данных, полученных после разделения, является числом пакетных записей, т.е. длиной пакета. В данном варианте осуществления, если число измененных блоков данных равно длине пакета, т.е. данные во всех блоках данных, полученных после разделения, изменились, информация изменения, принятая посредством контроллера памяти, указывает на то, что данные во всех блоках данных строки кэша изменились. В данном случае применительно к каждому из, по меньшей мере, одного блока данных первой что-будет-записана строки кэша контроллер памяти отправляет адрес столбца и данные, соответствующие блоку данных, к устройству памяти; устройство памяти сохраняет несколько принятых адресов столбца в разных буферах адреса столбца, выполняет дешифрование одновременно посредством использования разных дешифраторов столбца, выбирает разные столбцы в SAA, записывает данные в эти выбранные столбцы и в заключении записывает данные в SAA в массив памяти. Например, первая что-будет-записана строка кэша делится на восемь блоков данных посредством использования ширины шины данных памяти в качестве степени разбиения, и данные во всех восьми блоках данных изменились. Вследствие этого контроллер памяти отправляет восемь адресов столбца и соответствующие данные устройству памяти. Восемь буферов адреса столбца и восемь дешифраторов столбца размещены в устройстве памяти, каждый буфер адреса столбца хранит один адрес столбца, и дешифраторы, соответствующие адресам столбца, выполняют дешифрование одновременно.

Опционально, в вышеупомянутом Варианте 1 Осуществления контроллер памяти определяет в соответствии с информацией изменения, требуется ли выполнить запись по каждому блоку данных. Применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, если число измененных блоков данных первой что-будет-записана строки кэша меньше длины пакета, контроллер памяти отправляет адрес столбца и данные, соответствующие каждому измененному блоку данных первой что-будет-записана строки кэша, и адрес столбца и данные, соответствующие каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша к устройству памяти. Сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше либо равна длине пакета. Соответственно устройство памяти выполняет в соответствии с каждым адресом столбца первой что-будет-записана строки кэша и каждым адресом столбца, по меньшей мере, одной второй что-будет-записана строки кэша, запись данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша и каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша, при этом вторая что-будет-записана строка кэша является что-будет-записана строкой кэша за исключением первой что-будет-записана строки кэша в LLC.

Как правило, кэш делит первую что-будет-записана строку кэша у LLC на, по меньшей мере, один блок данных и выполняет одну пакетную запись по каждому из, по меньшей мере, одного блока данных, при этом число блоков данных, полученных после разделения, является числом пакетных записей, т.е. длиной пакета. В данном варианте осуществления, если число измененных блоков данных меньше длины пакета, то изменились данные только в некоторых блоках данных из блоков данных, полученных после разделения. В данном случае при выполнении планирования команды контроллер памяти объединяет команды записи и совершает несколько записей в тактовом цикле одной фиксированной длины пакета способом объединения команд записи, тем самым предотвращая пустую трату тактового цикла, уменьшая энергопотребление системы памяти и повышая эффективность системы памяти.

В частности, запросы записи, которые отправляются посредством LLC к контроллеру памяти и используются, чтобы запросить те данные размера записываемой строки кэша, сначала сохраняются в очереди запросов, и контроллер памяти преобразует эти запросы записи в команды записи для оперирования устройством памяти и сохраняет команды записи в очереди команд. Когда устройство памяти отправляет команду записи первой что-будет-записана строки кэша, если контроллер памяти обнаруживает в соответствии с информацией изменения первой что-будет-записана строки кэша, что число измененных блоков данных строки кэша меньше длины пакета, команда записи, соответствующая, по меньшей мере, одной второй что-будет-записана строки кэша, выбирается из очереди команд. Сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше, либо равна длине пакета. В пакетных записях, число которых равно BL, контроллер памяти отправляет адрес столбца и данные, соответствующие одному измененному блоку данных первой что-будет-записана строки кэша, к устройству памяти каждый такт; после того как адреса столбца и данные, соответствующие измененным блокам данных первой что-будет-записана строки кэша отправлены, контроллер памяти последовательно продолжает отправлять адрес столбца и данные, соответствующие одному измененному блоку данных второй что-будет-записана строки кэша к устройству памяти каждый такт, и повторяет данный процесс до тех пор, пока данные не записываются в блоки данных, число которых равно BL, или до тех пор, пока не могут быть найдены команды записи, которые могут быть объединены, в очереди команд, т.е. число блоков данных, в которые данные записываются, меньше BL.

Следует отметить, что если число измененных блоков данных первой что-будет-записана строки кэша меньше длины пакета, и требуется объединить команду записи, соответствующую первой что-будет-записана строке кэша, и команду записи, соответствующую, по меньшей мере, одной второй что-будет-записана строке кэша, во время процесса записи данных, должны быть выполнены следующие условия: сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше, либо равна длине пакета, при этом первая что-будет-записана строка кэша и, по меньшей мере, одна вторая что-будет-записана строка кэша соответствуют командам записи, которые могут быть объединены. В дополнение, требуется чтобы команды записи дополнительно отвечали следующему условию: первая что-будет-записана строка кэша и, по меньшей мере, одна вторая что-будет-записана строка кэша находятся в одном и том же ряду одного и того же Банка группы хранения, и отсутствует команда чтения того же самого ряда в LLC. Т.е. команда записи, соответствующая первой что-будет-записана строке кэша, и команды записи, соответствующие, по меньшей мере, одной второй что-будет-записана строке кэша, используются для записи в одном и том же ряду одного и того же Банка группы хранения, и отсутствует запрос чтения того же самого ряда в командах записи, соответствующих, по меньшей мере, одной второй что-будет-записана строке кэша. В данном случае, обращаясь к Фиг. 4, устройство памяти дополнительно включает в себя модуль проверки ряда (проверка ряда), которая выполнена с возможностью проверки того, используются ли команды записи для выполнения записи данных в одном и том же ряду одного и того же Банка группы хранения.

В частности, предполагается, что размер одной строки кэша у LLC составляет 64 байта, ширина шины данных памяти составляет 64 бита, и длина пакета BL равна 8. Таблица 1 показывает информацию касательно команд в очереди команд контроллера памяти: три команды записи используются для оперирования одним и тем же Банком, команды записи Запись 1 и Запись 3 используются для записи в ряд Ряд1, а команда записи Запись 2 используется для записи в ряд Ряд2.

|

Как может быть видно из Таблицы 1, Запись 1 и Запись 3 используются для записи в один и тот же ряд; CBV, а именно информация изменения указывает на то, что сумма числа измененных блоков данных строки кэша, соответствующей Записи 1, и числа измененных блоков данных строки кэша, соответствующей Записи 3 (показаны заштрихованными в Таблице 1), равна 8. Вследствие этого объединение команд записи выполняется для Записи 1 и Записи 3; контроллер памяти планирует Запись 2 после завершения планирования Записи 1 и Записи 3. В частности, обратимся к Фиг. 5.

Фиг. 5 является циклограммой объединения команд записи в способе записи данных в соответствии с настоящим изобретением. Как показано на Фиг. 5, в первых четырех тактах, т.е. передних фронтах и задних фронтах тактовых циклов T0 и T1, контроллер памяти отправляет Запись 1 и адрес столбца col1, col2, col3, и col4; в последующих четырех тактах, т.е. передних фронтах и задних фронтах тактовых циклов T2 и T3, контроллер памяти отправляет Запись3 и адреса столбца col3, col4, col5 и col6. Затем контроллер памяти отправляет адреса столбца, соответствующие Записи 2. В момент T5 данные Dn пакетной записи появляются по шине данных, и выполняются восемь пакетных записей, так что измененные блоки данных строки кэша, соответствующей Записи 1, и строки кэша, соответствующей Записи 3, записываются в устройство памяти. Col1 указывает адрес столбца, соответствующий первому блоку данных из восьми блоков данных строки кэша, соответствующей Записи 1, а D1 указывает данные, соответствующие первому блоку данных, а остальное может быть выведено по аналогии.

Следует отметить, что в вышеприведенном варианте осуществления настоящее изобретение подробно описано посредством использования примера, в котором объединяются две команды записи Запись 1 и Запись 3 и сумма числа измененных блоков данных строки кэша, соответствующей Записи 1, и числа измененных блоков данных строки кэша, соответствующей Записи 3, равна BL. Тем не менее настоящее изобретение этим не ограничивается. В другом возможном варианте реализации может быть объединено несколько команд записи. Например, если сумма числа измененных блоков данных строки кэша, соответствующей Записи 1, и числа измененных блоков данных строки кэша, соответствующей Записи 3, меньше BL, другие команды записи, которые могут быть объединены, могут быть выбраны из очереди команд. В дополнение, если сумма чисел измененных блоков данных строк кэша, соответствующих всем командам записи, которые могут быть объединены, в очереди команд меньше BL, выполняются пакетные записи, число которых равно BL, и некоторые тактовые циклы в пакетных записях, число которых равно BL или некоторые такты тактового цикла являются незанятыми. В дополнение, Фиг. 5 показывает только три тактовые частоты памяти (внутренние CK) динамической памяти с произвольным доступом (динамическая память с произвольным доступом, DRAM). Фактически, присутствует суммарно восемь тактовых частот памяти.

Фиг. 6 является принципиальной структурной схемой системы памяти в соответствии с настоящим изобретением и является вариантом осуществления аппаратуры, соответствующим варианту осуществления настоящего изобретения на Фиг. 1; вследствие этого конкретный процесс реализации здесь вновь не описывается. В частности, система 100 памяти в данном варианте осуществления включает в себя, по меньшей мере, контроллер 10 памяти и устройство 11 памяти.

В частности, контроллер 10 памяти выполнен с возможностью: приема информации изменения, отправленной посредством кэша, при этом информация изменения является информацией, которая генерируется после того, как кэш делит первую что-будет-записана строку кэша строка кэша у кэша последнего уровня (LLC) на, по меньшей мере, один блок данных, и которая используется, чтобы указать, изменились ли данные в каждом блоке данных; применительно к каждому неизмененному блоку данных, в котором данные не изменились, как указывается посредством информации изменения, пропуска отправки в соответствии с информацией изменения адреса столбца, соответствующего каждому неизмененному блоку данных, и данных, соответствующих каждому неизмененному блоку данных, к устройству памяти; и применительно к каждому измененному блоку данных, в котором данные изменились, как указывается посредством информации изменения, отправки в соответствии с информацией изменения адреса столбца, соответствующего каждому измененному блоку данных, и данных, соответствующих каждому измененному блоку данных, к устройству памяти; и

устройство 11 памяти, выполнено с возможностью записи в соответствии с адресом столбца, соответствующим каждому измененному блоку данных, и данными, соответствующими каждому измененному блоку данных, данных длины пакета в каждый измененный блок данных, при этом длина пакета равна числу из, по меньшей мере, одного блока данных.

Кроме того, контроллер 10 памяти выполнен с возможностью: если число измененных блоков данных первой что-будет-записана строки кэша равно длине пакета, отправки адреса столбца, соответствующего каждому измененному блоку данных, и данных, соответствующих каждому измененному блоку данных, к устройству 11 памяти.

Устройство 10 памяти выполнено с возможностью выполнения в соответствии с каждым адресом столбца записи данных длины пакета длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша.

Кроме того, контроллер 10 памяти выполнен с возможностью: если число измененных блоков данных первой что-будет-записана строки кэша меньше длины пакета, отправки адреса столбца и данных, соответствующих каждому измененному блоку данных первой что-будет-записана строки кэша, и адреса столбца и данных, соответствующих каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша к устройству памяти, при этом сумма числа измененных блоков данных, по меньшей мере, одной второй что-будет-записана строки кэша и числа измененных блоков данных первой что-будет-записана строки кэша меньше, либо равна длине пакета; и

устройство 11 памяти выполнено с возможностью выполнения в соответствии с каждым адресом столбца первой что-будет-записана строки кэша и каждым адресом столбца, по меньшей мере, одной второй что-будет-записана строки кэша, записи данных длины пакета по каждому измененному блоку данных первой что-будет-записана строки кэша и каждому измененному блоку данных, по меньшей мере, одной второй что-будет-записана строки кэша, при этом вторая что-будет-записана строка кэша является что-будет-записана строкой кэша за исключением первой что-будет-записана строки кэша в LLC.

Кроме того, первая что-будет-записана строка кэша и, по меньшей мере, одна вторая что-будет-записана строка кэша, находятся в одном и том же ряду одного и того же Банка группы хранения, и отсутствует команда чтения того же самого ряда в LLC.

Кроме того, когда буферы адреса столбца, число которых равно длине пакета, и дешифраторы столбца, число которых равно длине пакета, размещаются в устройстве 11 памяти, где количество равно длине пакета, запись данных выполняется по каждому измененному блоку данных посредством использования независимого буфера адреса столбца и независимого дешифратора столбца.

Специалистам в соответствующей области техники может быть понятно, что все или некоторые из этапов вариантов осуществления способа могут быть реализованы посредством программы, выдающей инструкции соответствующему аппаратному обеспечению. Программа может быть сохранена на машиночитаемом запоминающем носителе информации. При работе программы выполняются этапы вариантов осуществления способа. Вышеупомянутый запоминающий носитель информации включает в себя: любой носитель информации, который может хранить программный код, такой как ROM, RAM, магнитный диск или оптический диск.

В заключении, следует отметить, что вышеупомянутые варианты осуществления предназначены лишь для описания технических решений настоящего изобретения, а не для ограничения настоящего изобретения. Несмотря на то, что настоящее изобретение подробно описывается со ссылкой на вышеупомянутые варианты осуществления, специалисты в соответствующей области должны понимать, что они по-прежнему могут сделать модификации в отношении технических решений, описанных в вышеупомянутых вариантах осуществления, или сделать эквивалентные замеры в отношении некоторых или всех их технических признаков, не отступая от объема технических решений вариантов осуществления настоящего изобретения.