Результат интеллектуальной деятельности: МУЛЬТИПЛЕКСОР ПОТЕНЦИАЛЬНЫХ СИГНАЛОВ ДАТЧИКОВ

Вид РИД

Изобретение

Изобретение относится к области радиоэлектроники и вычислительной техники и может быть использовано в качестве прецизионного устройства коммутации и преобразования аналоговых электрических сигналов датчиков различной физической природы.

Аналоговые мультиплексоры (AM) являются неотъемлемым элементом современных многоканальных систем сбора информации от большого количества датчиков и их последующего аналого-цифрового преобразования.

В современной радиоэлектронной аппаратуре и датчиковых системах находят применение аналоговые мультиплексоры, выполненные на основе дифференциальных каскадов с коммутируемой общей эмиттерной или коллекторной цепями [1-18]. На их основе реализуются аналого-цифровые устройства, обеспечивающие формирование выходного напряжения, пропорционального одному из выбранных (на заданном отрезке времени) входных напряжений, что обеспечивается последовательным «включением» («выключением») входных дифференциальных каскадов (переведением их в режим микротоков).

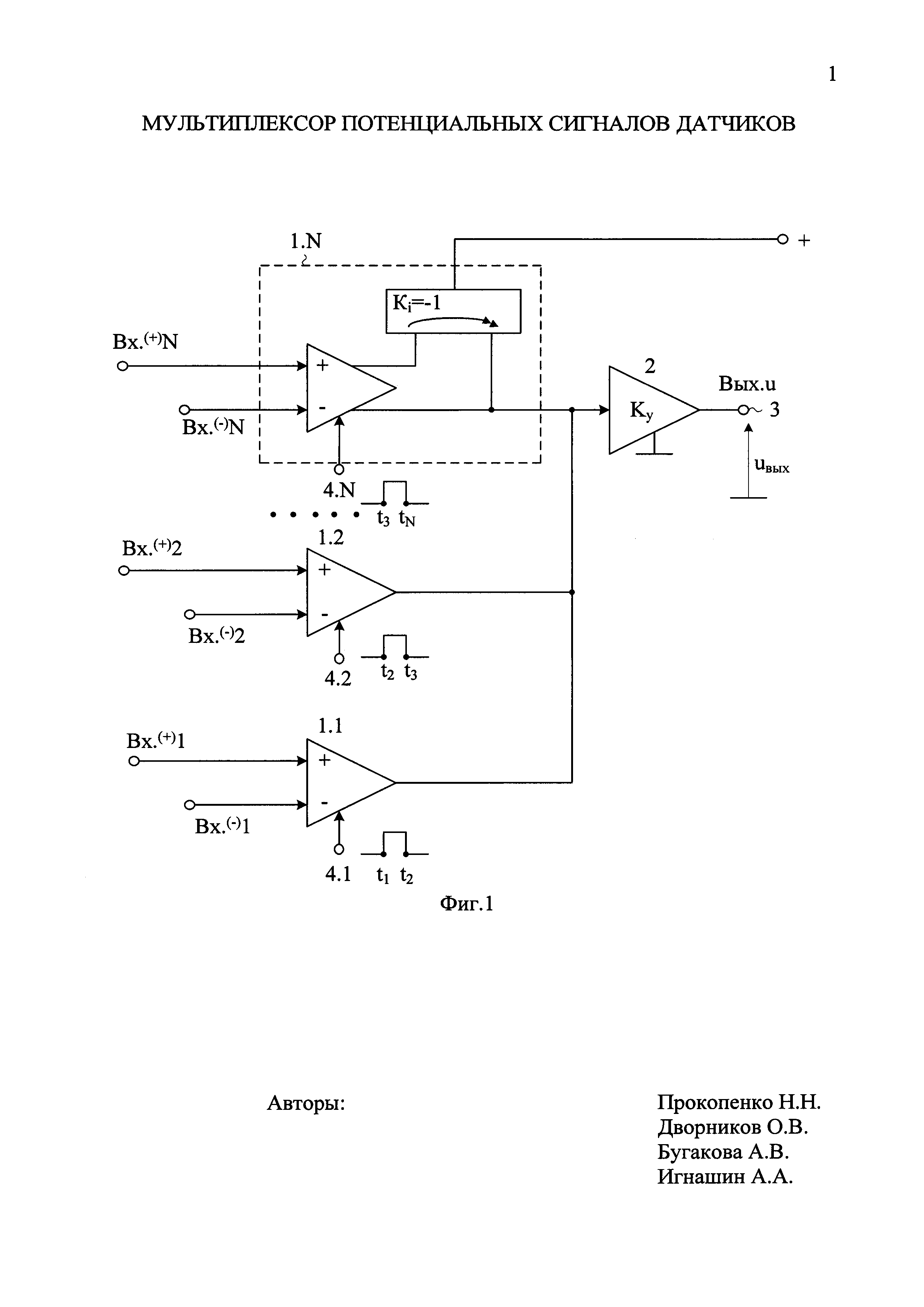

Ближайшим прототипом (фиг. 1) заявляемого устройства является мультиплексор потенциальных сигналов датчиков, представленный в патентной заявке US 2009/0206929. Он содержит (фиг. 1) первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входные дифференциальные каскады, каждый из которых имеет инвертирующий и неинвертирующий входы, связанные с соответствующими источниками потенциальных сигналов, и токовые выходы, связанные с входом выходного буферного усилителя (2), имеющего потенциальный выход (3), причем каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад снабжен логическим потенциальным входом (4.1), (4.2), (…), (4.N) для включения / выключения данного входного дифференциального каскада.

Существенный недостаток устройства-прототипа состоит в том, что оно, выполняя функции мультиплексора аналоговых сигналов, не обеспечивает алгебраическое суммирование входных напряжений, а также не позволяет коммутировать входные дифференциальные и недифференциальные сигналы с инверсией их фазы.

Основная задача предлагаемого изобретения состоит в расширении функциональных возможностей мультиплексора - реализации на его основе не только режима последовательного во времени преобразования входных потенциальных сигналов в выходное напряжение устройства, но и в обеспечении алгебраического суммирования входных дифференциальных и недифференциальных напряжений, а также изменения их фазы в процессе мультиплексирования.

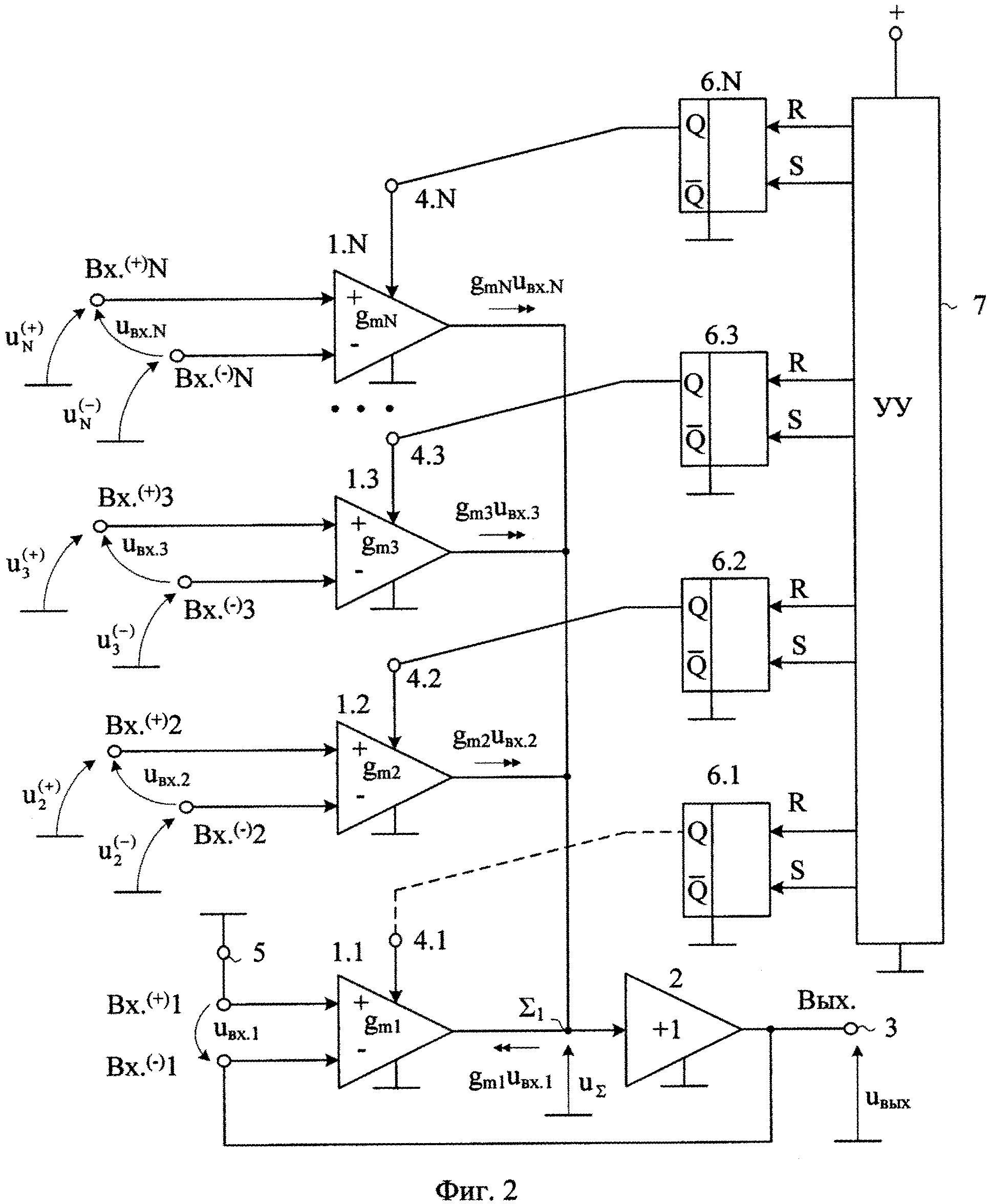

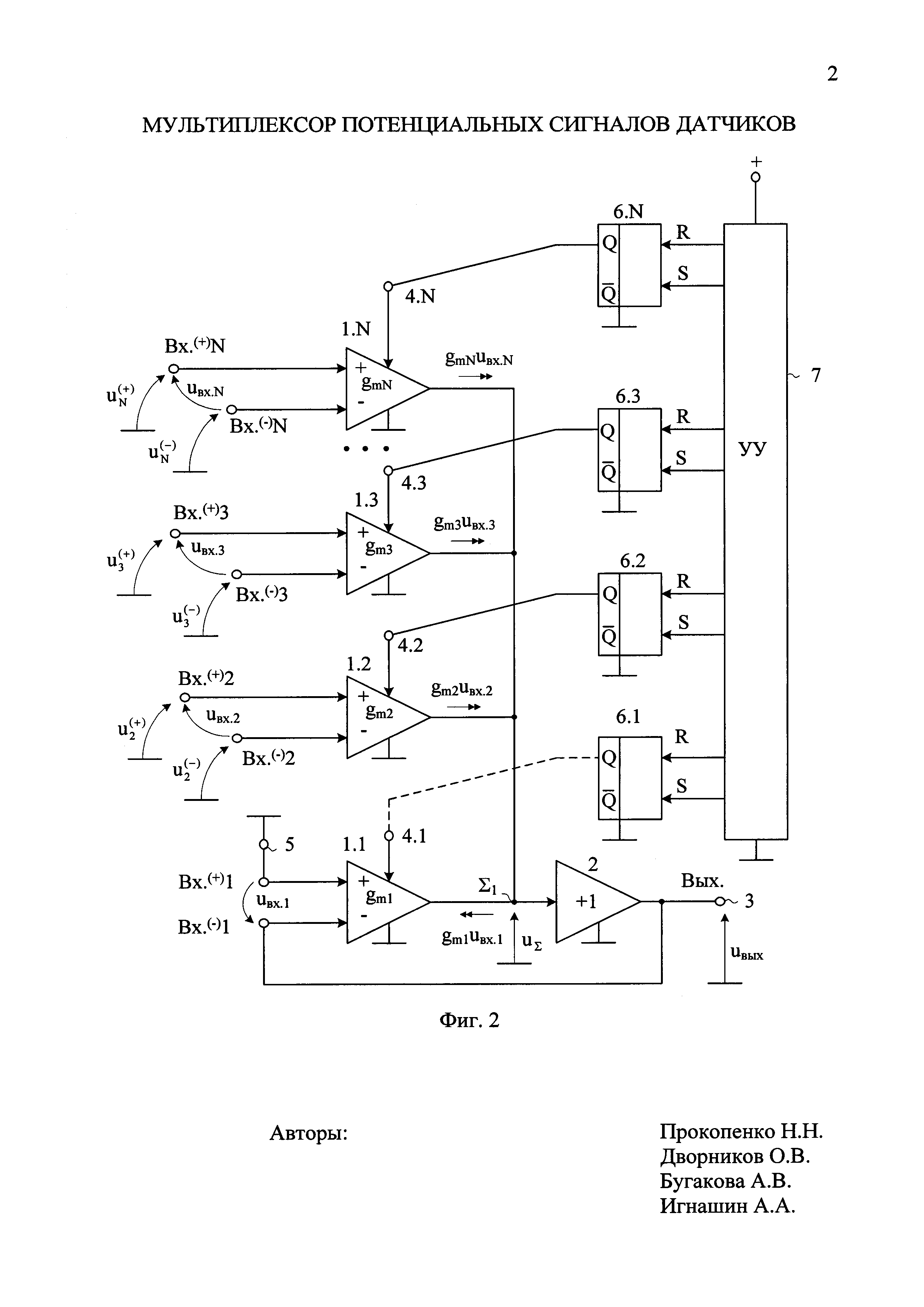

Поставленная задача достигается тем, что в мультиплексоре потенциальных сигналов датчиков фиг. 1, содержащем первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входные дифференциальные каскады, каждый из которых имеет инвертирующий и неинвертирующий входы, связанные с соответствующими источниками потенциальных сигналов, и токовые выходы, связанные с входом выходного буферного усилителя (2), имеющего потенциальный выход (3), причем каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад снабжен логическим потенциальным входом (4.1), (4.2), (…), (4.N) для включения/выключения данного входного дифференциального каскада, предусмотрены новые элементы и связи - каждый из N входных дифференциальных каскадов (1.1), (1.2), (1.3), (…), (1.N) имеет диапазон линейной работы по дифференциальному входу, превышающий максимальную амплитуду его входного дифференциального напряжения, потенциальный выход (3) выходного буферного усилителя (2) соединен с инвертирующим входом первого (1.1) входного дифференциального каскада, неинвертирующий вход которого связан с общей шиной источника питания (5), причем каждый логический потенциальный вход (4.1), (4.2), (4.3), (…), (4.N) включения/выключения каждого входного дифференциального каскада (1.1), (1.2), (1.3), (…), (1.N) связан с выходом соответствующих первого (6.1), второго (6.2), третьего (6.3) и N-го (6.N) триггеров, входы управления состоянием которых соединены с выходами цифрового управляющего устройства (7).

На фиг. 1 показана схема мультиплексора-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

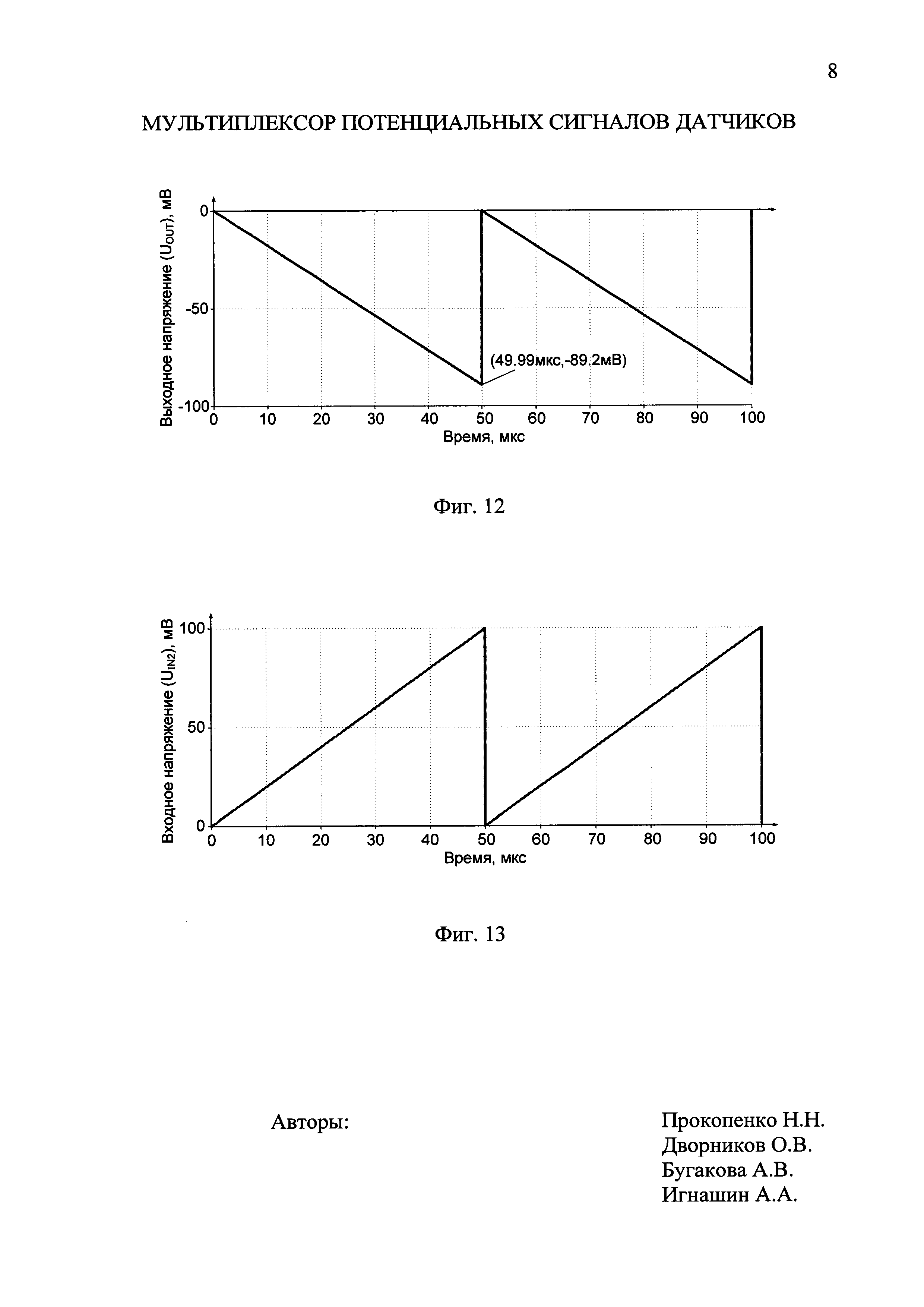

На фиг. 3 показана проходная характеристика первого (1.1), второго (1.2), третьего (1.3) и N-ого (1.N) входных дифференциальных каскадов (ДК) заявляемого устройства, которая дает определение - что такое диапазон линейной работы входных ДК.

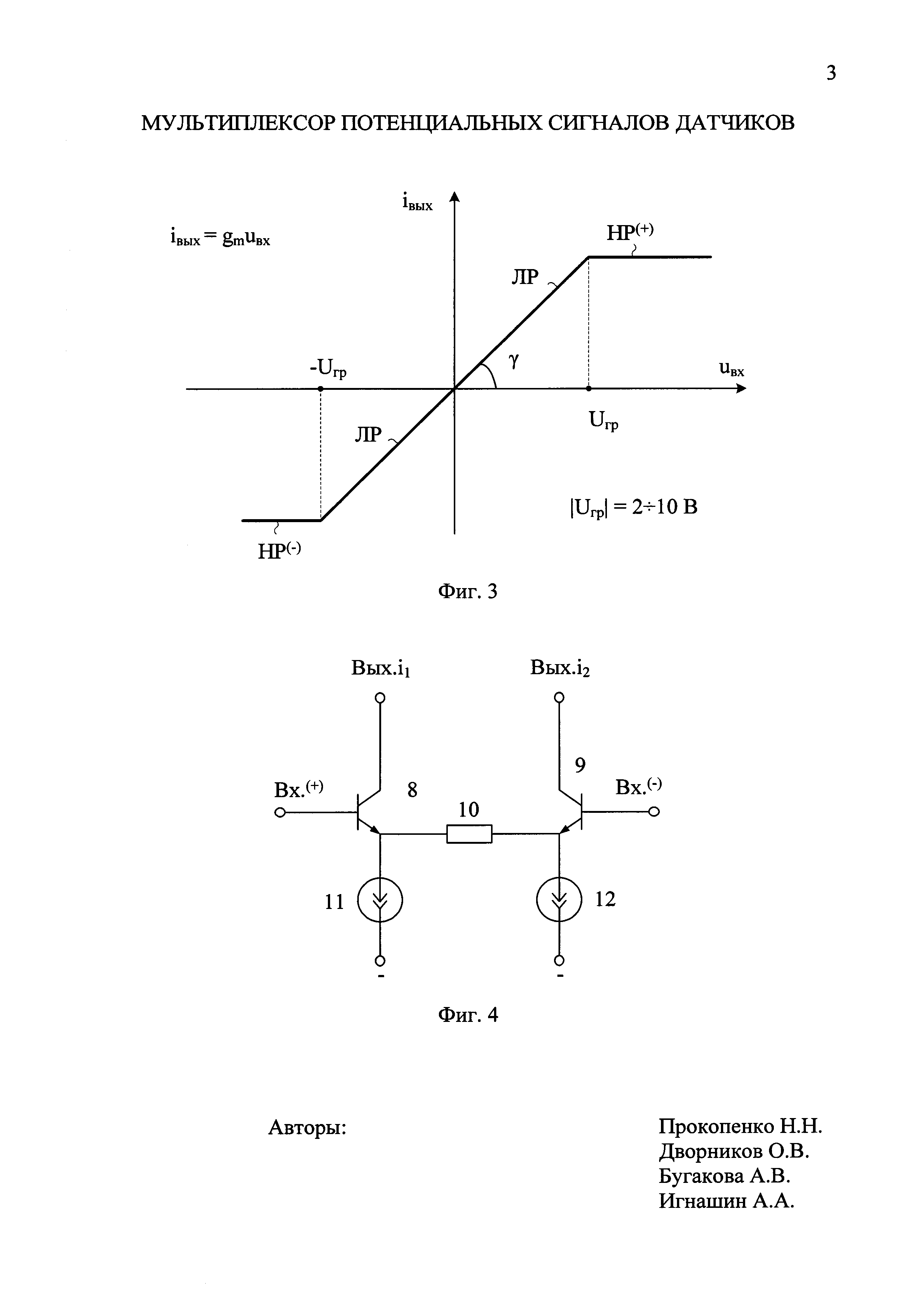

На фиг. 4 представлена одна из возможных структур входного дифференциального каскада (1.1), (1.2), (1.3), (…), (1.N) AM фиг. 2 на биполярных транзисторах. На полевых транзисторах схема ДК реализуется аналогично.

На фиг. 5 приведена схема входного дифференциального каскада (1.1), (1.2), (1.3), (…), (1.N) AM фиг. 2 с расширенным диапазоном линейной работы, что обеспечивается введением специальных цепей нелинейной коррекции [20].

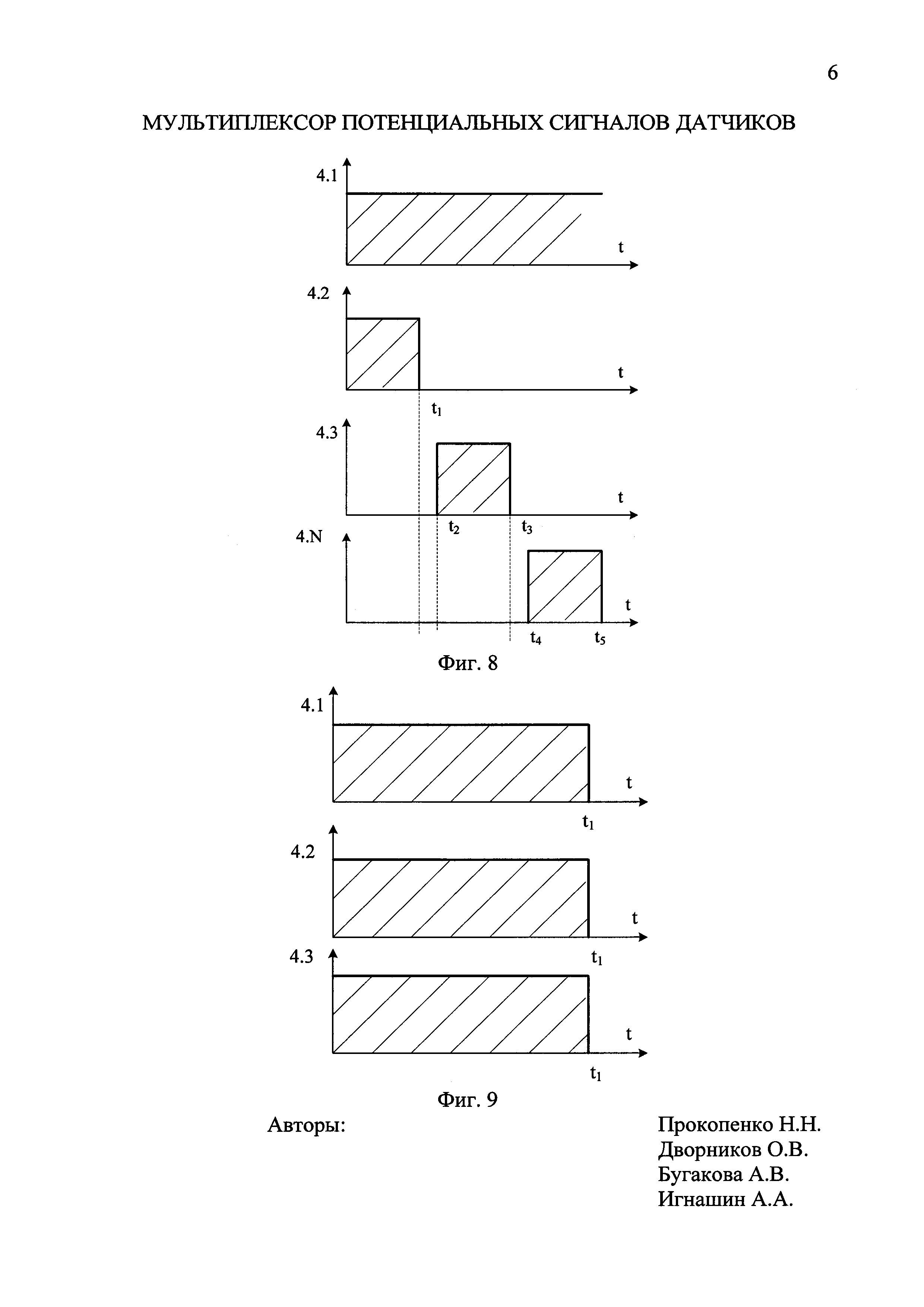

На фиг. 6 приведен первый вариант построения входного дифференциального каскада AM фиг. 2 с цепью его включения/выключения логическим сигналом, который подается на каждый логический потенциальный вход (4.1), (4.2), (4.3), (…), (4.N) включения/выключения каждого входного ДК.

На фиг. 7 приведен второй вариант построения входного дифференциального каскада [позиции (1.1), (1.2), (1.3), (…), (1.N)] AM фиг. 2 с цепью его включения/выключения логическим сигналом, который подается на каждый логический потенциальный вход (4.1), (4.2), (4.3), (…), (4.N) включения/выключения каждого входного ДК.

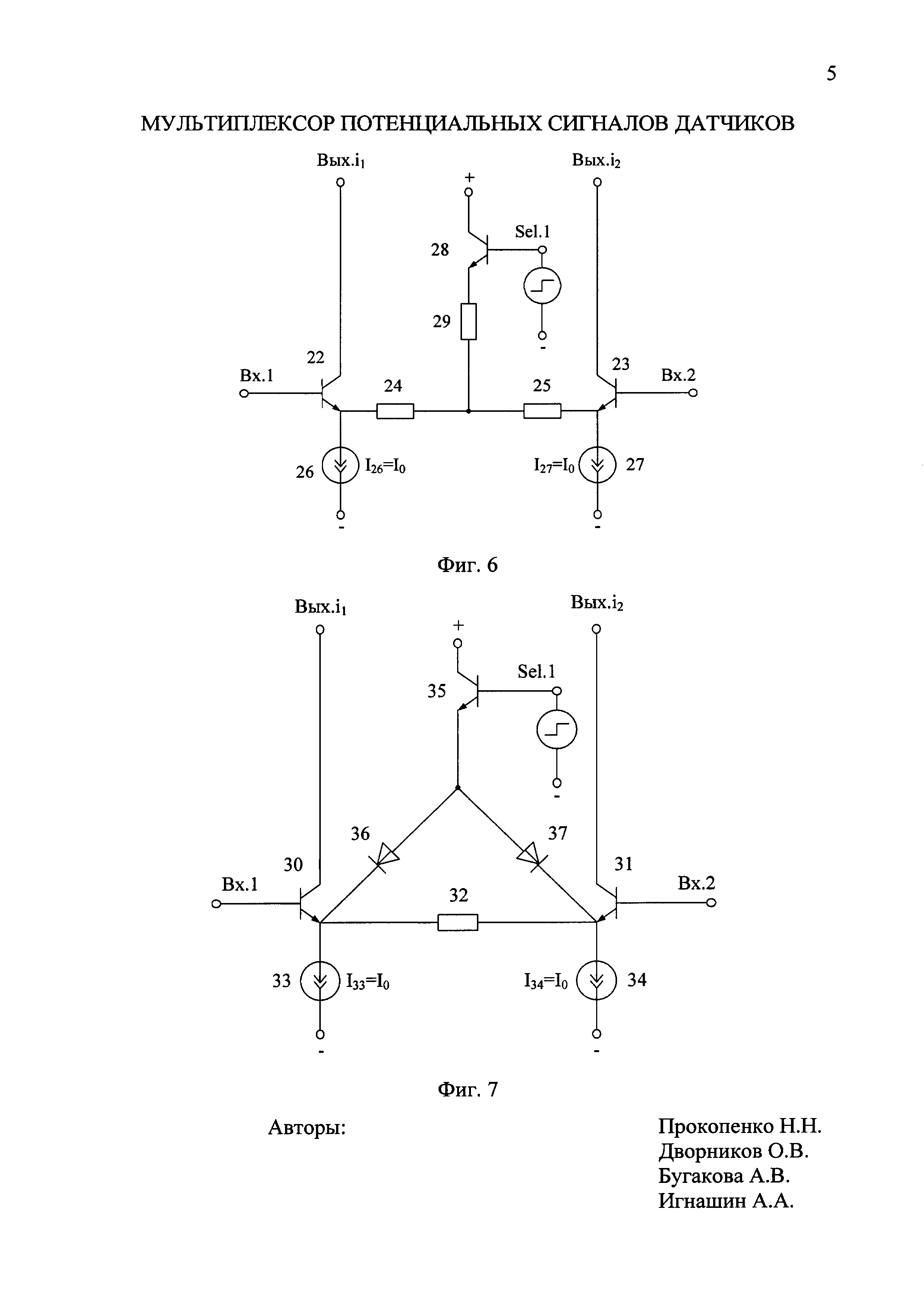

На фиг. 8 показаны временные диаграммы логических сигналов, подаваемых на логические потенциальные входы (4.1), (4.2), (…), (4.N) для включения/выключения входных дифференциальных каскадов (1.1), (1.2), (1.3), (…), (l.N) AM фиг. 2 заявляемого устройства. При этом обеспечивается первый режим работы AM - последовательное по времени мультиплексирование входных сигналов выбранных входных дифференциальных каскадов (их передача на выход устройства 3).

На фиг. 9 показаны временные диаграммы логических сигналов, подаваемых на логические потенциальные входы (4.1), (4.2), (4.3) для включения/выключения входных дифференциальных каскадов (1.1), (1.2), (1.3), (…), (1.N) AM фиг. 2, при которых обеспечивается второй режим работы AM - алгебраическое суммирование сигналов, присутствующих на входах соответствующих входных дифференциальных каскадов (1.2) и (1.3). Следует заметить, что на данной временной диаграмме, в отличие от фиг. 8, обеспечивается включение соответствующих дифференциальных каскадов (1.2) и (1.3) на все время работы мультиплексора (на интервале (0÷t1). В ином случае (фиг. 8), режим алгебраического суммирования не реализуется.

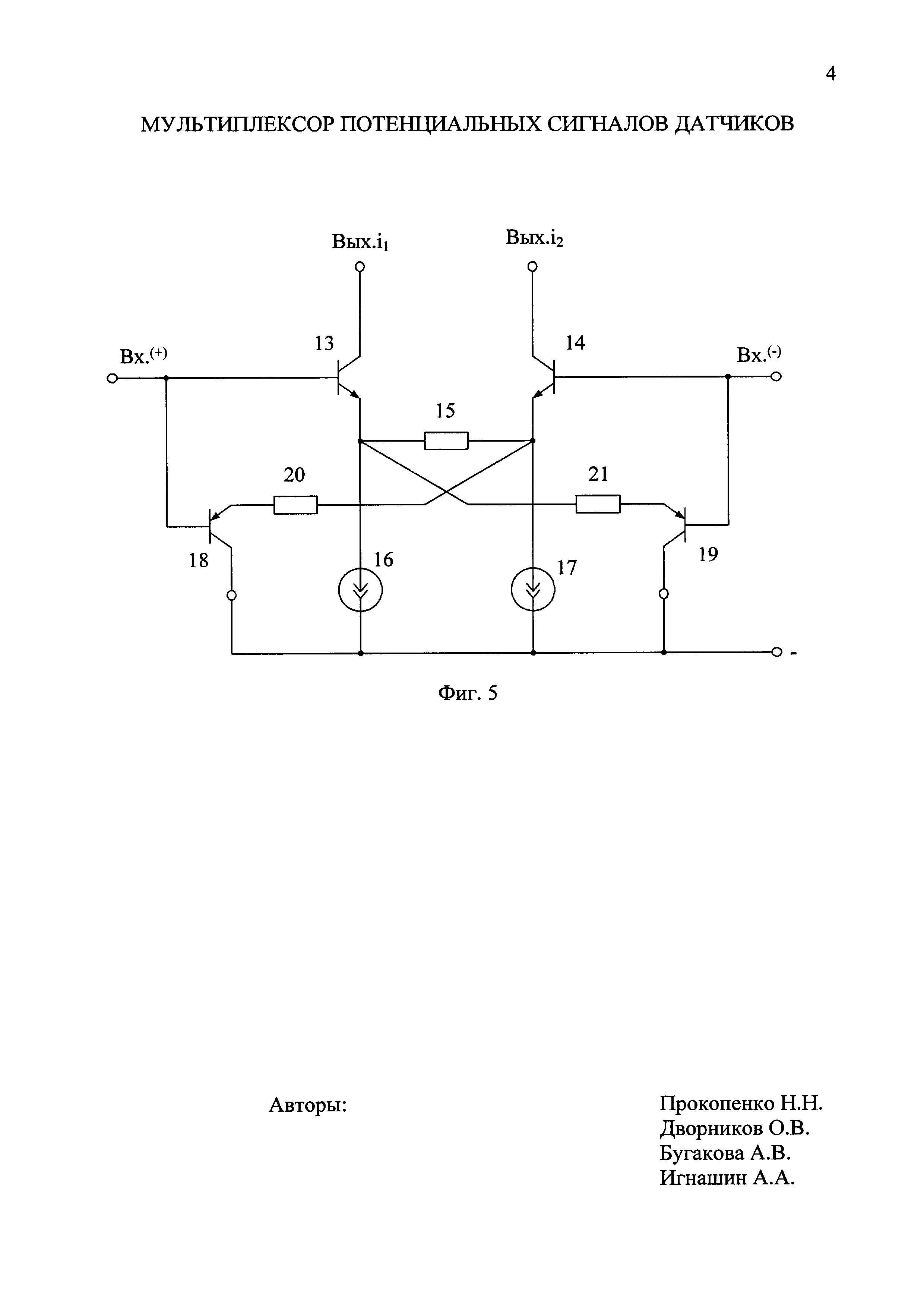

На фиг. 10 приведена схема устройства фиг. 2 в среде PSpice, для случая, когда в нем используется только три входных дифференциальных каскада (1.1), (1.2), (1.3) AM фиг. 2, а на инвертирующий вход IN1 подается входной пилообразный сигнал с амплитудой 100 мВ.

На фиг. 11 показана временная диаграмма входного напряжения в схеме фиг. 10, подаваемого на инвертирующий вход IN1 с амплитудой 100 мВ.

На фиг. 12 показана временная диаграмма выходного напряжения при входном напряжении, соответствующим фиг. 11. Из данного графика следует, что фаза выходного напряжения заявляемого устройства в этом случае противоположна фазе входного напряжения.

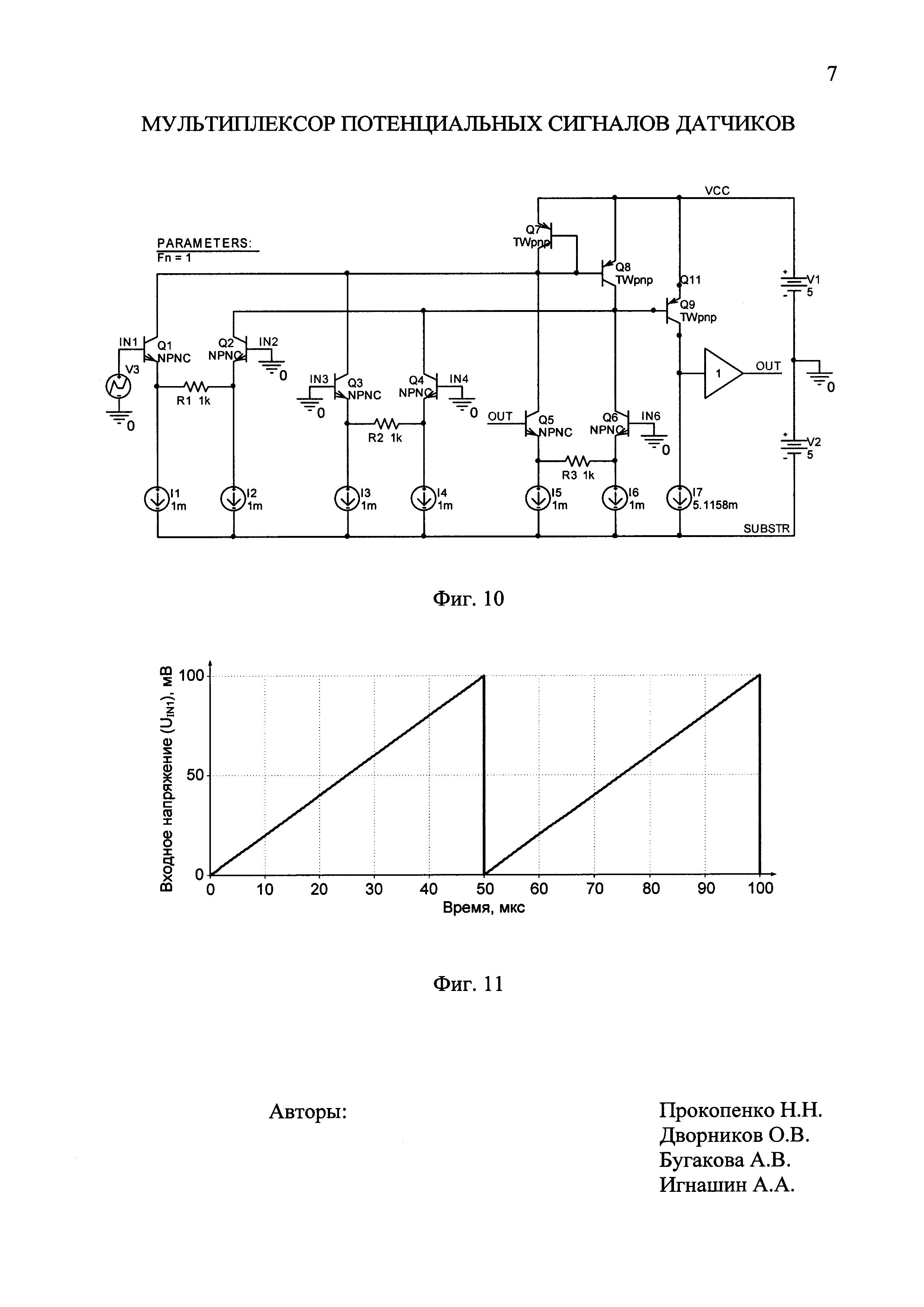

На фиг. 13 показана временная диаграмма входного напряжения в схеме фиг. 10, подаваемого на неинвертирующий вход IN2 соответствующего «включенного» входного дифференциального каскада (Q1, Q2, R1, I1, I2).

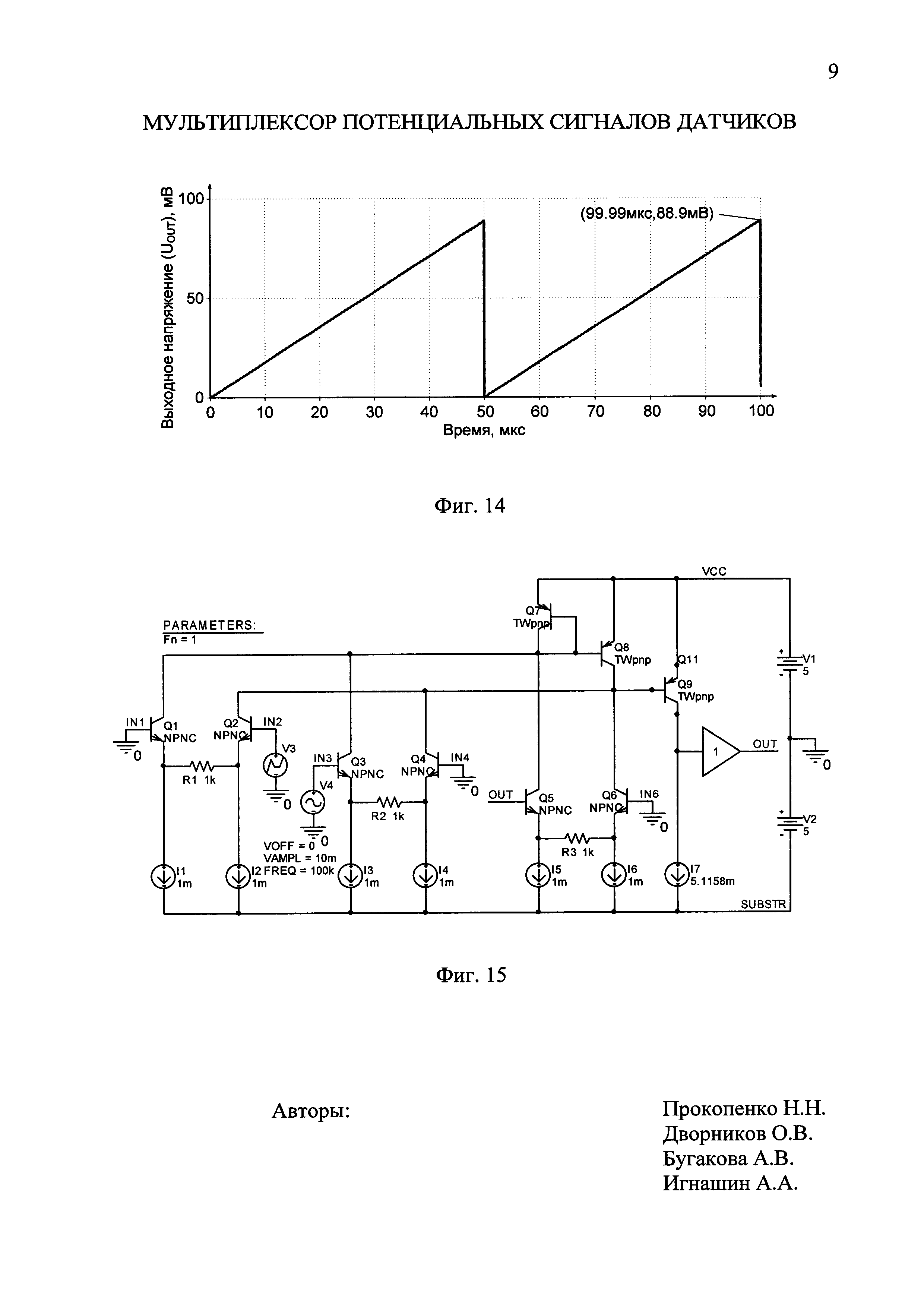

На фиг. 14 показана временная диаграмма выходного напряжения устройства фиг. 10 при входном напряжении, соответствующем фиг. 13. Из данного графика следует, что фаза выходного напряжения заявляемого устройства в этом случае совпадает с фазой входного напряжения.

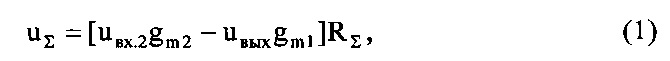

На фиг. 15 представлена схема заявляемого устройства фиг. 2 в среде PSpice в режиме алгебраического суммирования двух недифференциальных напряжений, одно из которых имеет пилообразную форму с амплитудой 100 мВ, а второе - синусоидальный сигнал с амплитудой Vamp1=10 MB, f=100 кГц.

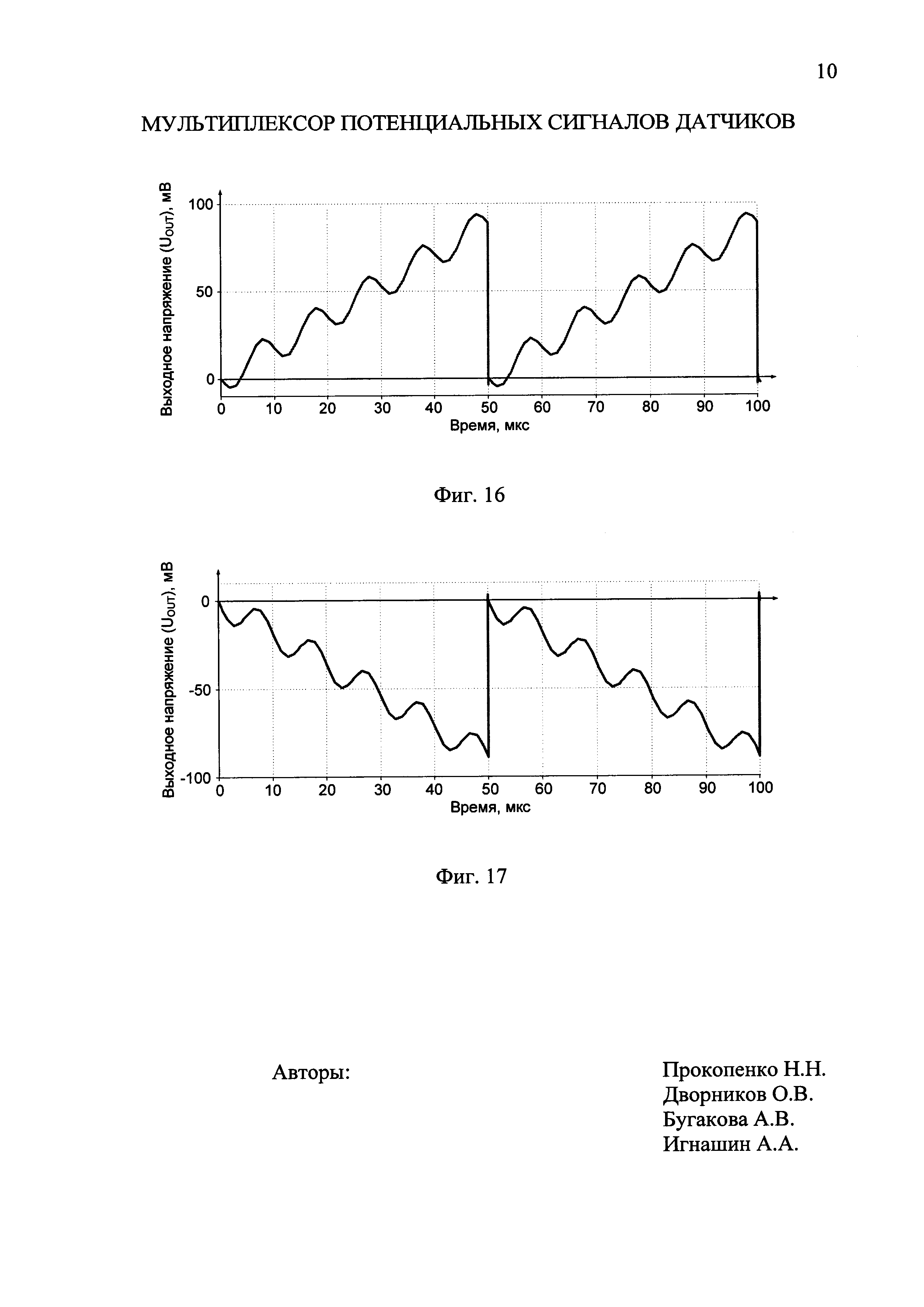

На фиг. 16 показана временная диаграмма выходного напряжения схемы фиг. 15 при пилообразном и синусоидальном входных сигналов без их инверсии.

На фиг. 17 показана временная диаграмма выходного напряжения схемы фиг. 15 при пилообразном и синусоидальном входных сигналов с инверсией их фазы.

Мультиплексор потенциальных сигналов датчиков фиг. 2 содержит первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входные дифференциальные каскады, каждый из которых имеет инвертирующий и неинвертирующий входы, связанные с соответствующими источниками потенциальных сигналов, и токовые выходы, связанные с входом выходного буферного усилителя (2), имеющего потенциальный выход (3), причем каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад снабжен логическим потенциальным входом (4.1), (4.2), (…), (4.N) для включения/выключения данного входного дифференциального каскада. Каждый из N входных дифференциальных каскадов (1.1), (1.2), (1.3), (1.N) имеет диапазон линейной работы по дифференциальному входу, превышающий максимальную амплитуду его входного дифференциального напряжения. Потенциальный выход (3) выходного буферного усилителя (2) соединен с инвертирующим входом первого (1.1) входного дифференциального каскада, неинвертирующий вход которого связан с общей шиной источника питания (5), причем каждый логический потенциальный вход (4.1), (4.2), (4.3), (…), (4.N) включения/выключения каждого входного дифференциального каскада (1.1), (1.2), (1.3), (…), (1.N) связан с выходом соответствующих первого (6.1), второго (6.2), третьего (6.3) и N-го (6.N) триггеров, входы управления состоянием которых соединены с выходами цифрового управляющего устройства (7).

На фиг. 4 каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад реализован на основе входных транзисторов (8) и (9), резистора местной отрицательной обратной связи (10) и источников опорного тока (11) и (12).

На фиг. 5 каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад реализован на основе входных транзисторов (13) и (14), резистора местной отрицательной обратной связи (15), источников опорного тока (16) и (17), транзисторов цепи нелинейной коррекции (18) и (19) и вспомогательных резисторов (20) и (21).

В схеме фиг. 6 каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад реализован на основе входных транзисторов (22) и (23), резисторов местной отрицательной обратной связи (24) и (25), источников опорного тока (26) и (27), транзистора (28) и резистора (29) цепи коммутации.

В схеме фиг. 7 каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад реализован на основе входных транзисторов (30) и (31), резистора местной отрицательной обратной связи (32), источников опорного тока (33), (34), транзистора (35) и диодов (36), (37) цепи коммутации.

Рассмотрим работу заявляемого устройства фиг. 2.

Схема фиг.2 может работать в двух основных режимах.

Первый режим - режим мультиплексора, при котором цифровое управляющее устройство (7) формирует импульсные сигналы триггерам (6.1), (6.2), (....), (6.N) (фиг. 8), при которых в схеме фиг. 2 обеспечивается последовательное во времени включение только одного из N входных дифференциальных каскадов (1.1), (1.2), (1.3), (…), (1.N). При этом выходное напряжение устройства на момент включения i-го входного дифференциального каскада, равно входному дифференциальному напряжению этого i-го входного дифференциального каскада.

Важно заметить, что в первом режиме в схеме фиг. 2 происходит формирование выходного напряжения, пропорционального входному дифференциальному напряжению в течение всего отрезка времени, в пределах которого i-й входной дифференциальный каскад находится во включенном состоянии (фиг. 8).

Рассмотрим случай, когда на заданном интервале времени включены только первый (1.1) и второй (1.2) входные ДК, что обеспечивается установкой соответствующих состояний RS триггеров (6.1), (6.2), (6.3), (…), (6.N). На основании второго закона Кирхгофа для схемы фиг. 2 можно определить напряжение в высокоимпедансном узле ∑1

где gm1=gm2 - проводимости передачи входных дифференциальных каскадов (1.1), (1.2);

R2 - эквивалентное сопротивление в высокоимпедансном узле ∑1.

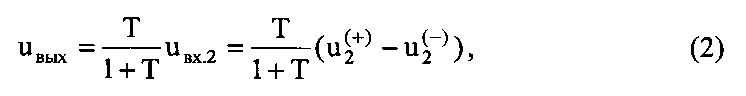

После преобразований (1) можно получить, что

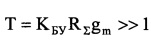

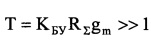

где  - петлевое усиление;

- петлевое усиление;

KБУ - коэффициент передачи выходного буферного усилителя 2.

Учитывая, что Т>>1, из (2) можно найти, что рассматриваемый режиме (фиг. 8) заявляемый мультиплексор (фиг. 2) обеспечивает выходной сигнал, равный разности напряжений

Второй режим работы устройства фиг. 2 - прецизионное алгебраическое суммирование избранных входных напряжений, что обеспечивается включением с помощью управляющего устройства 7 избранного количества входных дифференциальных каскадов (1.1, 1.2, 1.3, … 1.N).

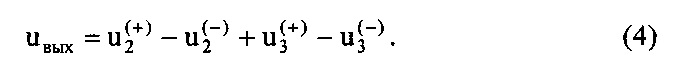

Так, например, если «включены» первый (1.1), второй (1.2), третий (1.3) входные дифференциальные каскады, то выходное напряжение заявляемого устройства

Покажем это аналитически на примере анализа данного состояния мультиплексора, которое устанавливается за счет формирования управляющих импульсных сигналов на R (S) входы первого (6.1), второго (6.2), третьего (6.3) и N-го (6.N) триггеров в схеме фиг. 2.

На основании второго закона Кирхгофа можно определить напряжение в высокоимпедансном узле ∑1

где gm1=gm2=gm3=gm - проводимости передачи входных дифференциальных каскадов (1.1), (1.2), (1.3);

R∑ - эквивалентное сопротивление в высокоимпедансном узле ∑1.

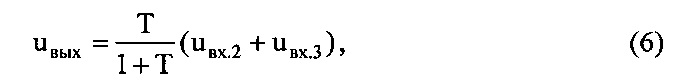

После преобразований (5) можно получить, что

где  - петлевое усиление;

- петлевое усиление;

KБУ - коэффициент передачи выходного буферного усилителя 2.

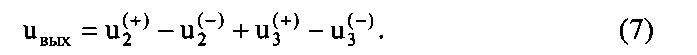

Учитывая, что Т>>1, из (6) можно найти, что в режиме алгебраического суммирования входных сигналов заявляемый мультиплексор фиг. 2 обеспечивает выходной сигнал, равный разности входных напряжений дифференциальных каскадов (1.2) и (1.3)

Уравнение (7) совпадает с (4).

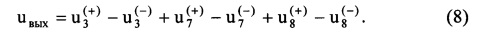

При других сочетаниях «включенных» входных дифференциальных каскадов в схеме фиг. 2 обеспечивается алгебраическое суммирование других входных напряжений. Так, например, при включении второго (1.2) и третьего (1.3), седьмого (1.7) и восьмого (1.8) входных дифференциальных каскадов

Если в первом режиме работы AM фиг. 2 нужно обеспечить последовательную передачу на выход устройства (3) недифференциальных напряжений  , затем -

, затем -  , а потом

, а потом  , то в схеме фиг. 2 нужно соответствующим образом соединить входы

, то в схеме фиг. 2 нужно соответствующим образом соединить входы  ,

,  ,

,  с общей шиной (4), а затем последовательно во времени подать логические сигналы включения третьего (1.3), седьмого (1.7) и восьмого (1.8) входных дифференциальных каскадов (фиг. 8).

с общей шиной (4), а затем последовательно во времени подать логические сигналы включения третьего (1.3), седьмого (1.7) и восьмого (1.8) входных дифференциальных каскадов (фиг. 8).

Таким образом, заявляемое устройство фиг. 2 является многофункциональным программируемым аналоговым процессором, который обеспечивает следующие операции преобразования потенциальных сигналов датчиков:

1. Неинвертирующее мультиплексирование входных недифференциальных напряжений ( ,

,  ,

,  и т.д.);

и т.д.);

2. Мультиплексирование входных дифференциальных напряжений (uвх.1, uвх.2, uвх.N);

3. Инвертирующее мультиплексирование входных недифференциальных напряжений ( ,

,  , и т.д.);

, и т.д.);

4. Мультиплексирование входных дифференциальных и недифференциальных сигналов (uвх.2,  ,

,  и т.д.);

и т.д.);

5. Алгебраическое суммирование выбранных дифференциальных и недифференциальных сигналов (uвх.2,  ,

,  и т.д.).

и т.д.).

Мультиплексор-прототип реализует только одну из пяти вышеназванных операций преобразования сигналов - неинвертирующее мультиплексирование входных недифференциальных напряжений без изменения их фазы. Это значительно сужает области его практического использования.

Дополнительным преимуществом заявляемого устройства является повышенная помехозащищенность от синфазных помех, что обусловлено возможностью коммутации входных дифференциальных сигналов. В АМ-прототипе это невозможно.

Следует заметить, что все указанные выше качества в заявляемом AM реализуются только в том случае, если каждый из входных дифференциальных каскадов (1.1), (1.2), (1.3), (…), (1.N) имеет широкий диапазон активной работы (фиг. 3) [17, 18]. Такое качество может быть получено на практике за счет введения в каждый классический входной дифференциальный каскад достаточно высокоомного резистора местной отрицательной обратной связи (10) (фиг. 4) либо применением нелинейных корректирующих (фиг. 5) цепей [18].

Таким образом, заявляемый мультиплексор имеет расширенные функциональные возможности, более высокую помехозащищенность, обеспечивает несколько режимов мультиплексирования входных напряжений, а также решает проблему алгебраического суммирования выбранных дифференциальных и недифференцальных сигналов. Это является его существенным преимуществом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Заявка на патент US 2009/0206929.

2. Патент US 5.352.987.

3. Патент US 4.905.238.

4. Патент US 7.151.409 fig. 3.

5. Патент US 3.916.215.

6. Патент US 6.583.668 fig. 4.

7. Патент US 4.177.432 fig. 1.

8. Заявка на патент WO 2000/013310.

9. Патент US 6.489.845.

10. Патент US 5.801.571.

11. Патент US 5.189.312.

12. Патент US 4.963.767.

13. Патент US 4.835.771.

14. Патент US 3.535.458.

15. Патент US 4.191.856.

16. Патент US 6.492.798.

17. Патент US 7.212.062.

18. Патент US 6.531.910.

19. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

20. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

Мультиплексор потенциальных сигналов датчиков, содержащий первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входные дифференциальные каскады, каждый из которых имеет инвертирующий и неинвертирующий входы, связанные с соответствующими источниками потенциальных сигналов, и токовые выходы, связанные с входом выходного буферного усилителя (2), имеющего потенциальный выход (3), причем каждый первый (1.1), второй (1.2), третий (1.3) и N-ый (1.N) входной дифференциальный каскад снабжен логическим потенциальным входом (4.1), (4.2), (…), (4.N) для включения/выключения данного входного дифференциального каскада, отличающийся тем, что каждый из N входных дифференциальных каскадов (1.1), (1.2), (1.3), …, (1.N) имеет диапазон линейной работы по дифференциальному входу, превышающий максимальную амплитуду его входного дифференциального напряжения, потенциальный выход (3) выходного буферного усилителя (2) соединен с инвертирующим входом первого (1.1) входного дифференциального каскада, неинвертирующий вход которого связан с общей шиной источника питания (5), причем каждый логический потенциальный вход (4.1), (4.2), (4.3), (…), (4.N) включения/выключения каждого входного дифференциального каскада (1.1), (1.2), (1.3), (…), (1.N) связан с выходом соответствующих первого (6.1), второго (6.2), третьего (6.3) и N-го (6.N) триггеров, входы управления состоянием которых соединены с выходами цифрового управляющего устройства (7).