Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ

Вид РИД

Изобретение

Изобретение относится к области электроники, измерительной техники и может быть использовано в качестве прецизионного устройства усиления сигналов различных датчиков.

В современной информационно-измерительной технике, приборостроении, датчиковых системах, различных аналого-цифровых интерфейсах находят широкое применение дифференциальные (ДУ) и операционные (ОУ) усилители на полевых транзисторах с управляющим p-n-переходом [11-13], которые обеспечивают усиление дифференциального сигнала (ud) и повышенное ослабление синфазной составляющей входных напряжений (uc) в диапазоне низких температур [14-16]. При этом для повышения линейности ДУ в его схему вводится резистор местной отрицательной обратной связи (R0=1-10 кОм), что существенно ухудшает один из важнейших параметров ДУ - коэффициент ослабления входного синфазного сигнала (Кос.сф).

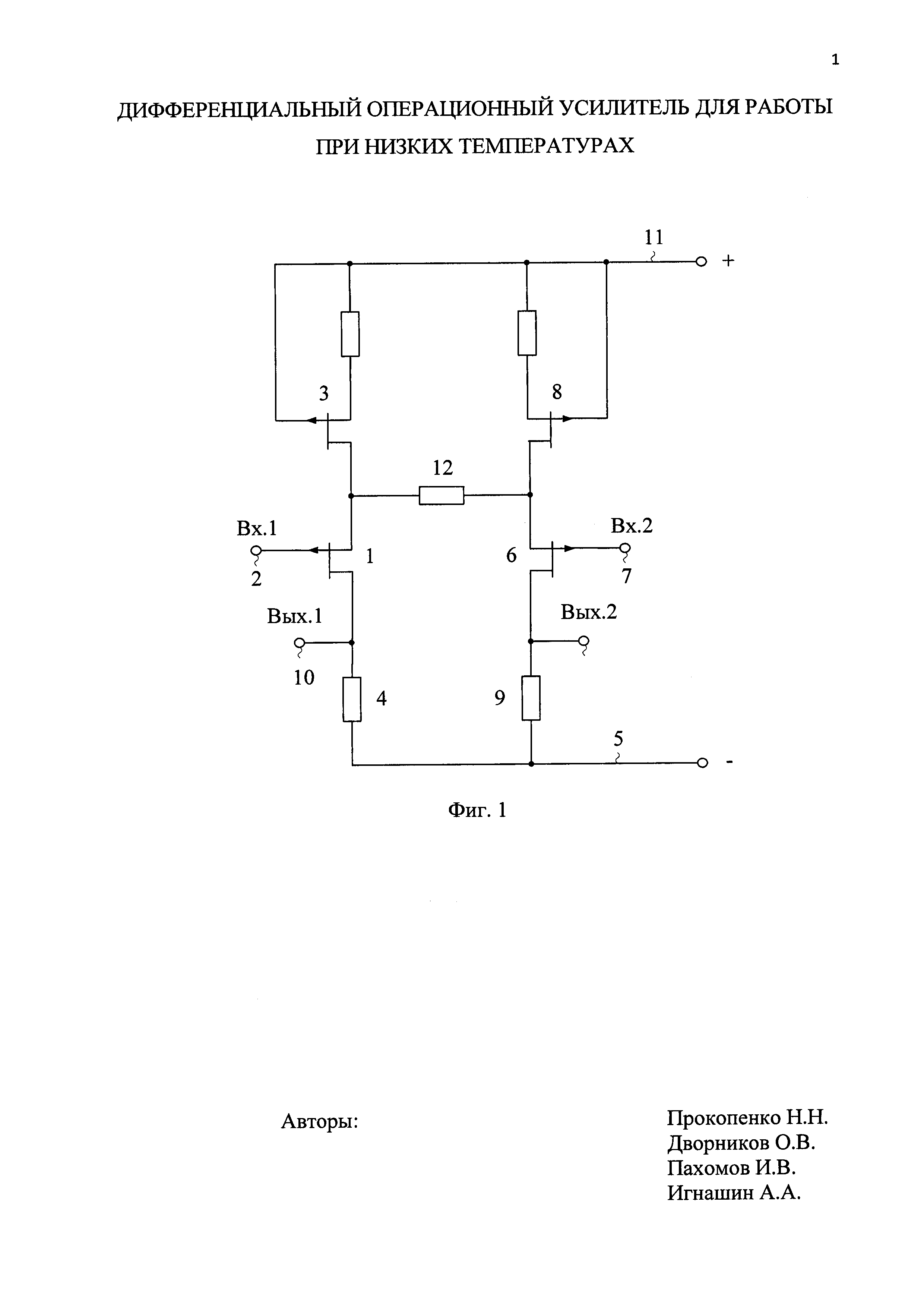

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель по патенту RU 25713299 (рис. 1, рис. 2). Он содержит (фиг. 1) первый 1 входной полевой транзистор, затвор которого соединен с первым 2 входом устройства, исток подключен к стоку первого 3 вспомогательного транзистора, а сток через первый 4 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 7 входом устройства, исток подключен к стоку второго 8 вспомогательного транзистора, а сток через второй 9 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, первый 10 выход устройства, вторую 11 шину источника питания, первый 12 резистор отрицательной обратной связи, включенный между истоками первого 1 и второго 6 входных полевых транзисторов.

Существенный недостаток известного ОУ состоит в том, что в связи с применением JFet полевых транзисторов, удовлетворительно работающих при криогенных температурах, он имеет невысокий коэффициент ослабления входного синфазного сигнала.

Основная задача предлагаемого изобретения состоит в повышении коэффициента ослабления входного синфазного сигнала.

Поставленная задача достигается тем, что в усилителе фиг. 1, содержащем первый 1 входной полевой транзистор, затвор которого соединен с первым 2 входом устройства, исток подключен к стоку первого 3 вспомогательного транзистора, а сток через первый 4 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 7 входом устройства, исток подключен к стоку второго 8 вспомогательного транзистора, а сток через второй 9 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, первый 10 выход устройства, вторую 11 шину источника питания, первый 12 резистор отрицательной обратной связи, включенный между истоками первого 1 и второго 6 входных полевых транзисторов, предусмотрены новые элементы и связи - затвор первого 3 вспомогательного транзистора подключен к эмиттеру первого 13 выходного транзистора, затвор второго 8 вспомогательного транзистора соединен с эмиттером второго 14 выходного транзистора, исток первого 3 вспомогательного транзистора связан с эмиттером первого 13 выходного транзистора, исток второго 8 вспомогательного транзистора связан с эмиттером второго 14 выходного транзистора, база которого соединена с базой первого 13 выходного транзистора и подключена к первой 15 цепи смещения потенциалов, сток первого 1 входного транзистора соединен с эмиттером первого 16 дополнительного транзистора, сток второго 6 входного транзистора соединен с эмиттером второго 17 дополнительного транзистора, база которого подключена к базе первого 16 дополнительного транзистора и соединена со второй 18 цепью смещения потенциалов, коллектор первого 16 дополнительного транзистора связан с эмиттером первого 13 выходного транзистора, коллектор второго 17 дополнительного транзистора соединен с эмиттером второго 14 выходного транзистора, причем коллекторы первого 13 и второго 14 выходных транзисторов связаны с соответствующими первым 19 и вторым 20 входами выходного дифференциального каскада 21, согласованного со второй 11 шиной источника питания, выход которого соединен с выходом устройства 10.

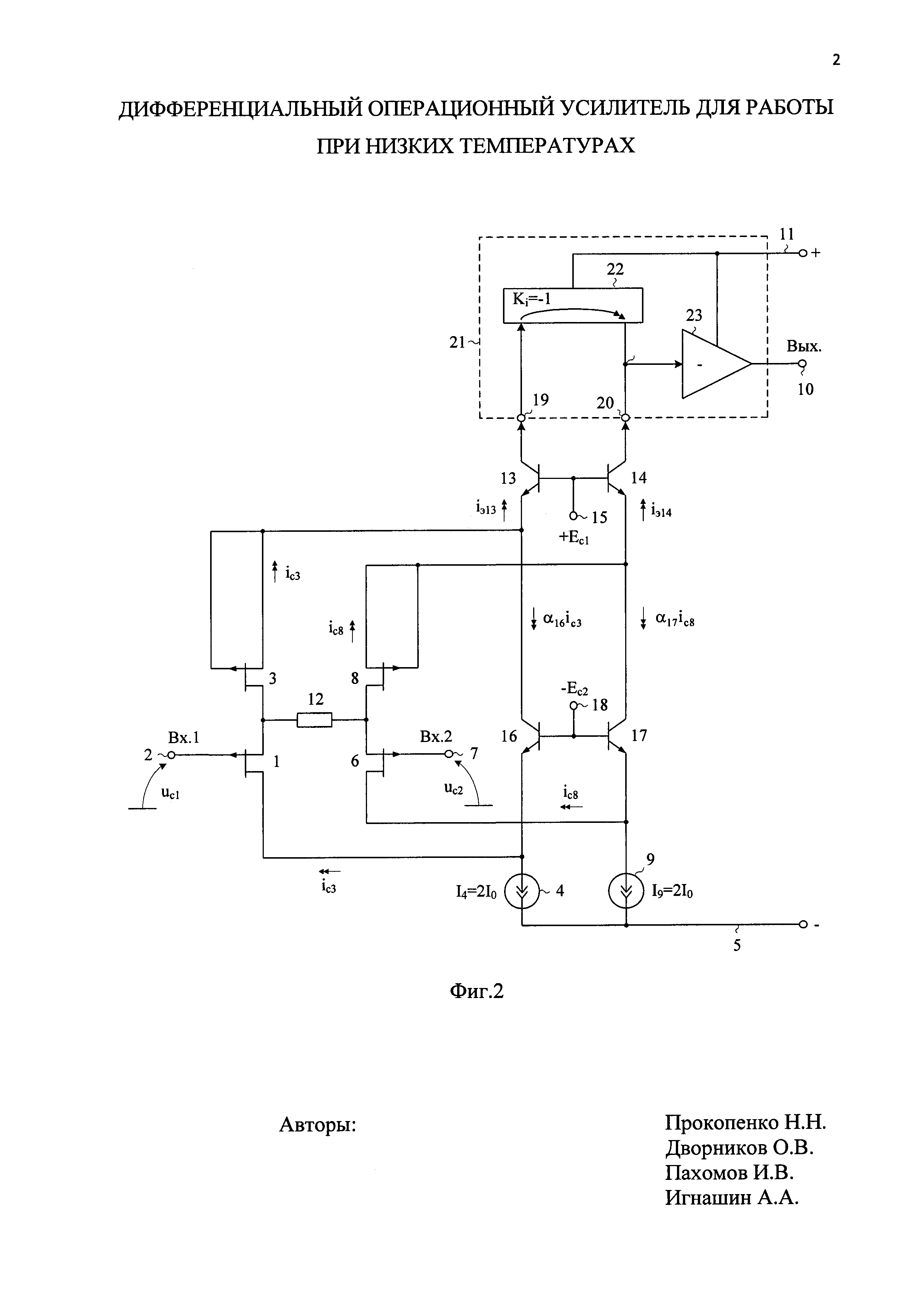

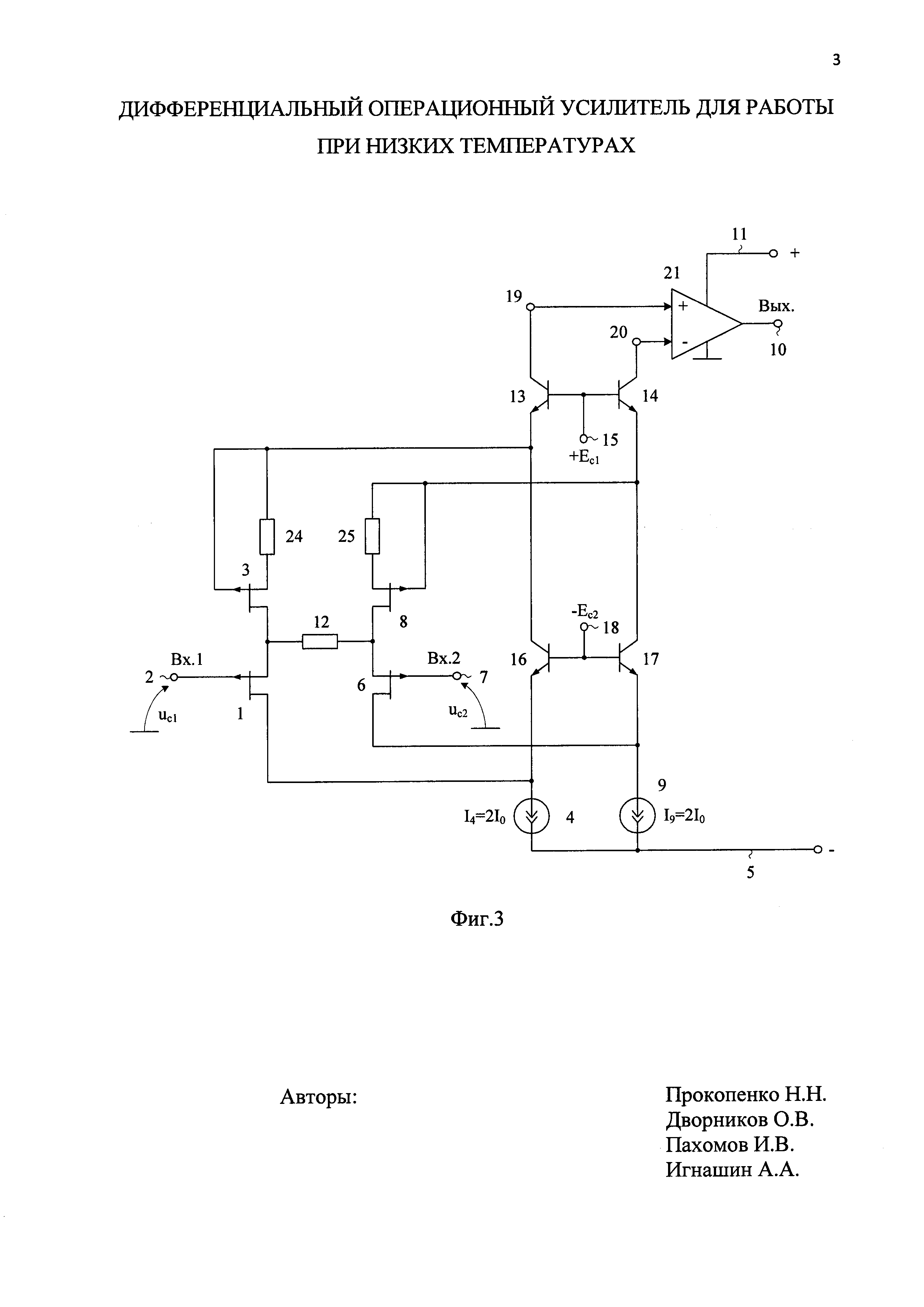

На фиг. 1 показана схема усилителя-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

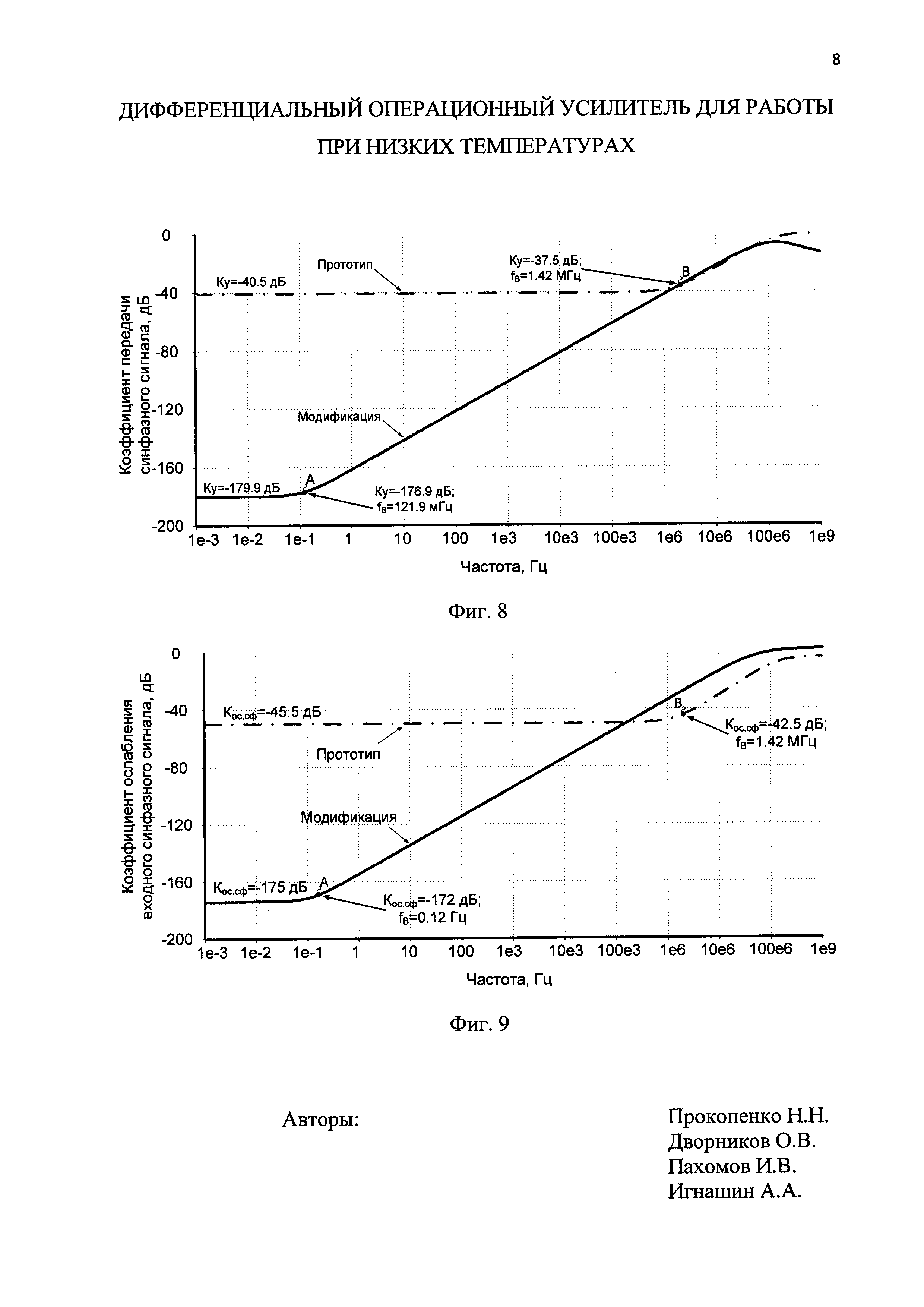

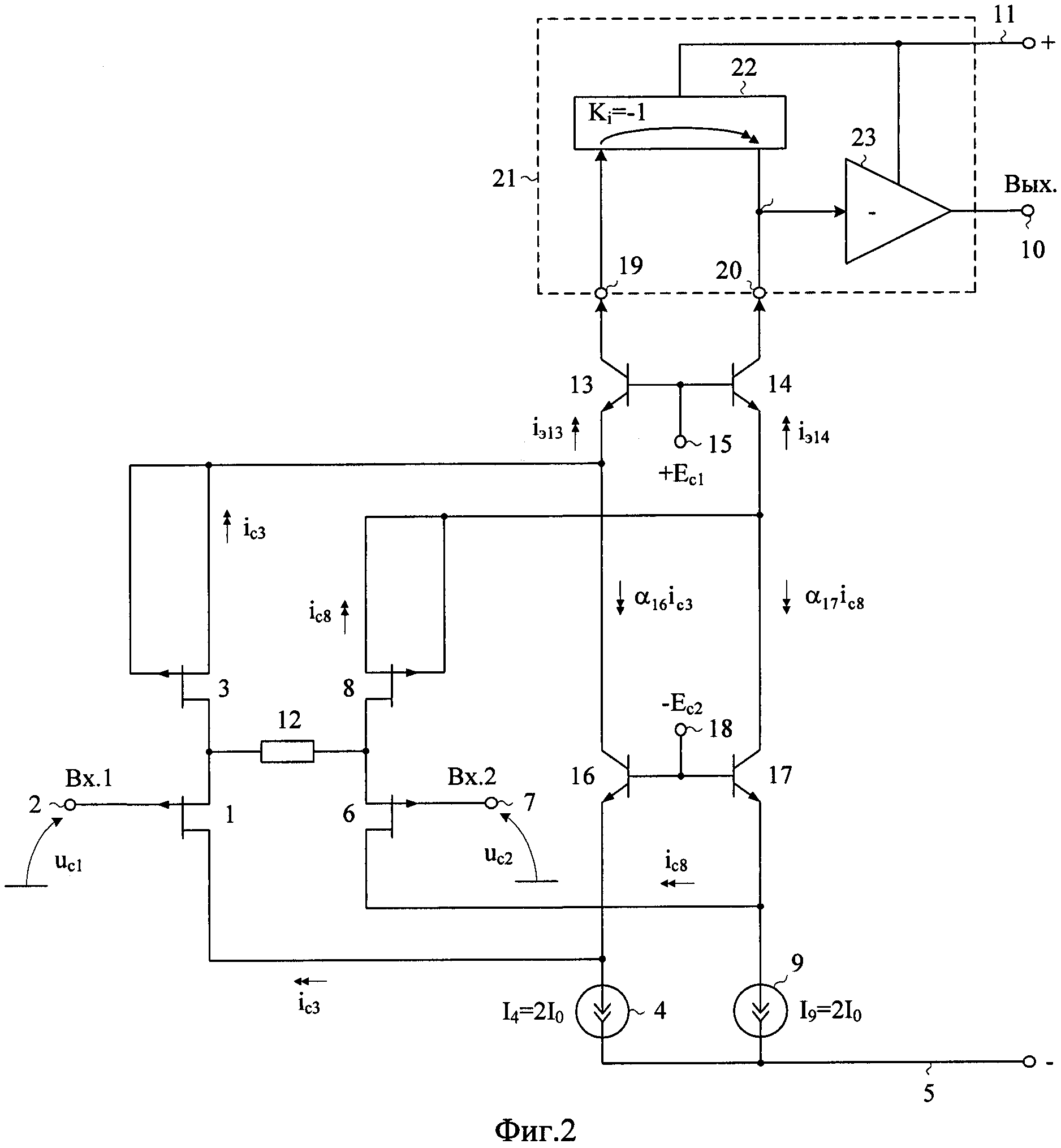

На фиг. 3 приведена схема заявляемого устройства в соответствии с п. 2, а на фиг. 4 в соответствии с п. 3 формулы изобретения.

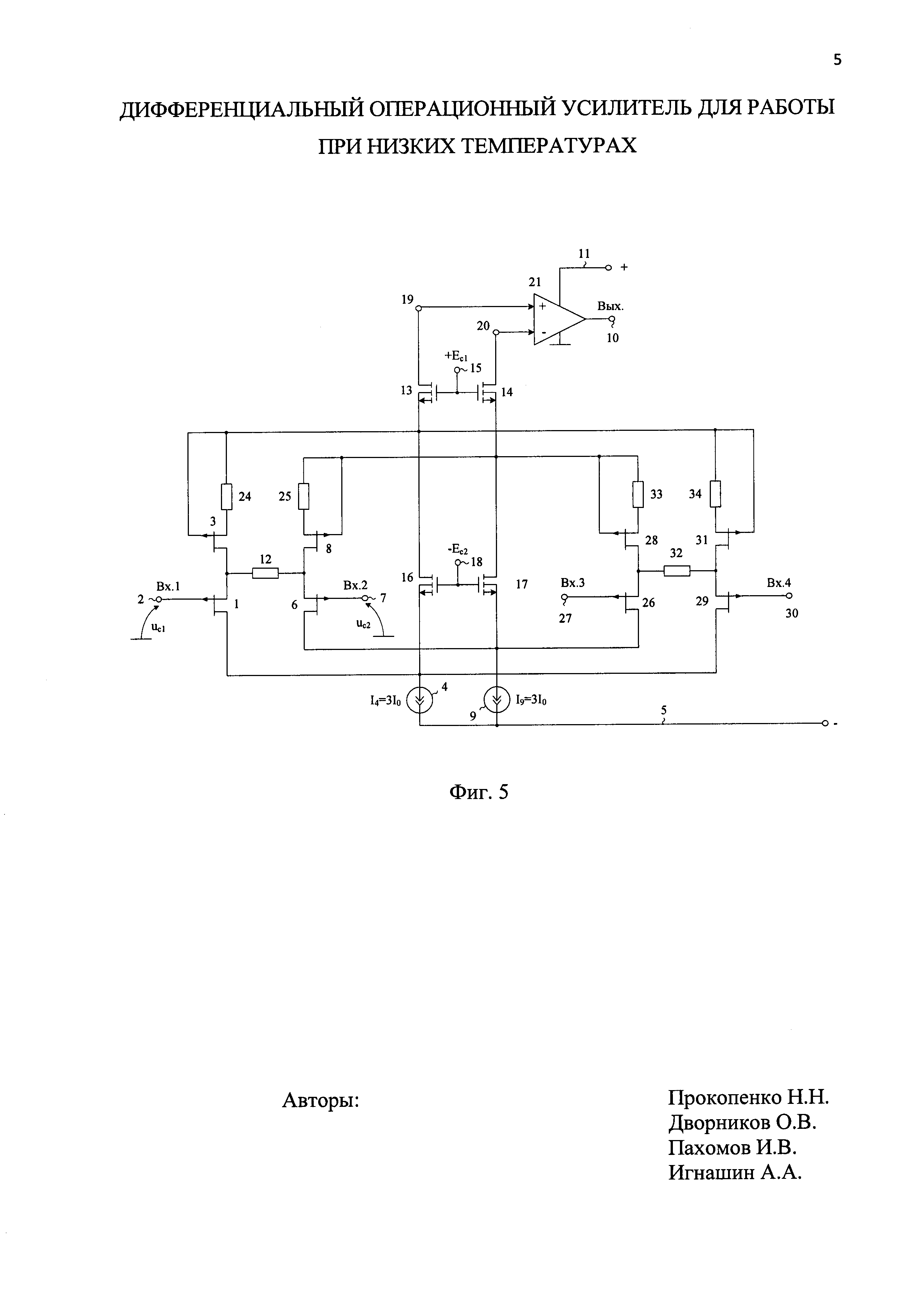

На фиг. 5 представлена схема заявляемого устройства в соответствии с п. 4 формулы изобретения.

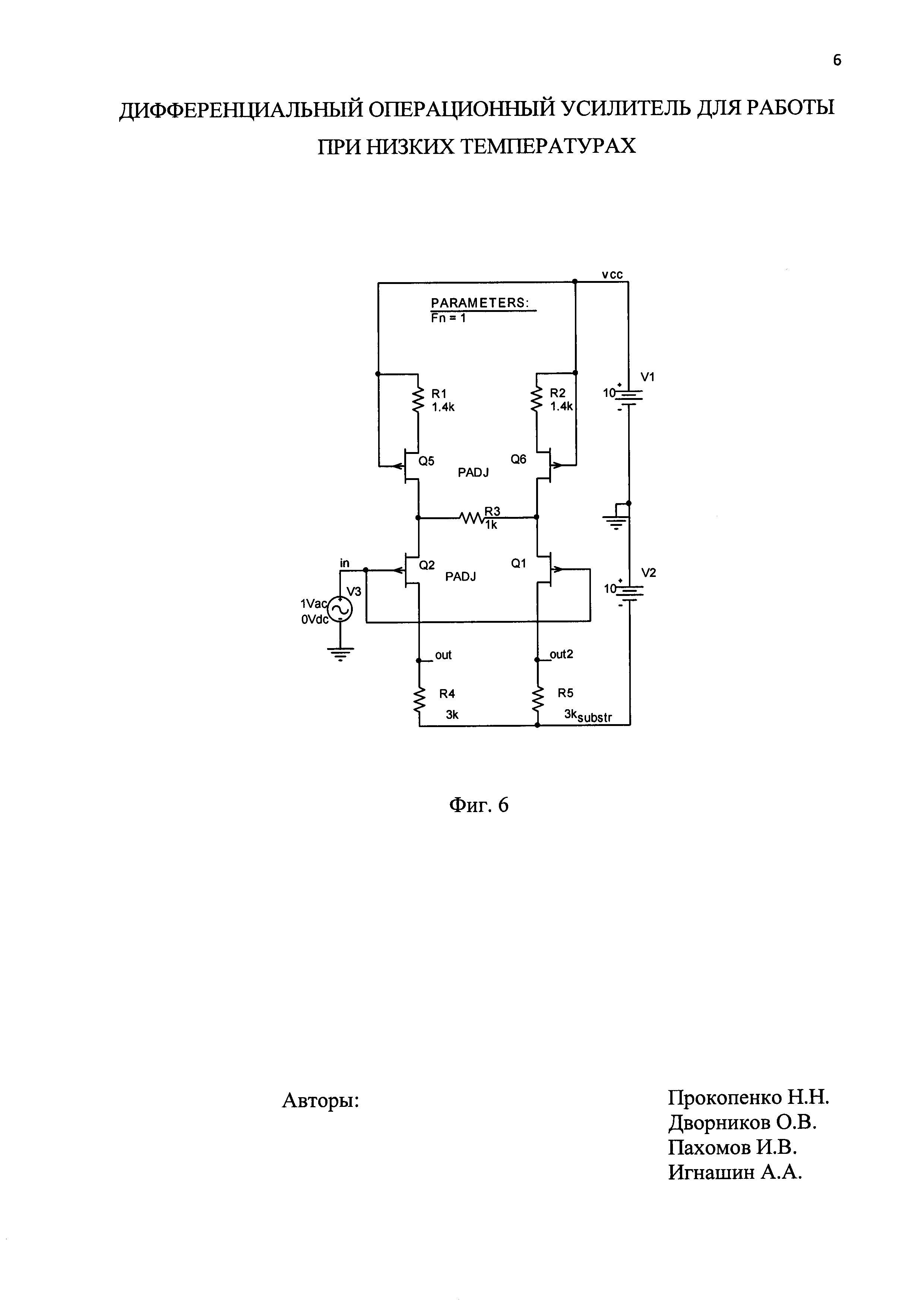

На фиг. 6 представлена схема усилителя-прототипа фиг. 1 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г.Минск) для определения его коэффициента передачи входного синфазного сигнала от объединенных входов (V3) на выход (out).

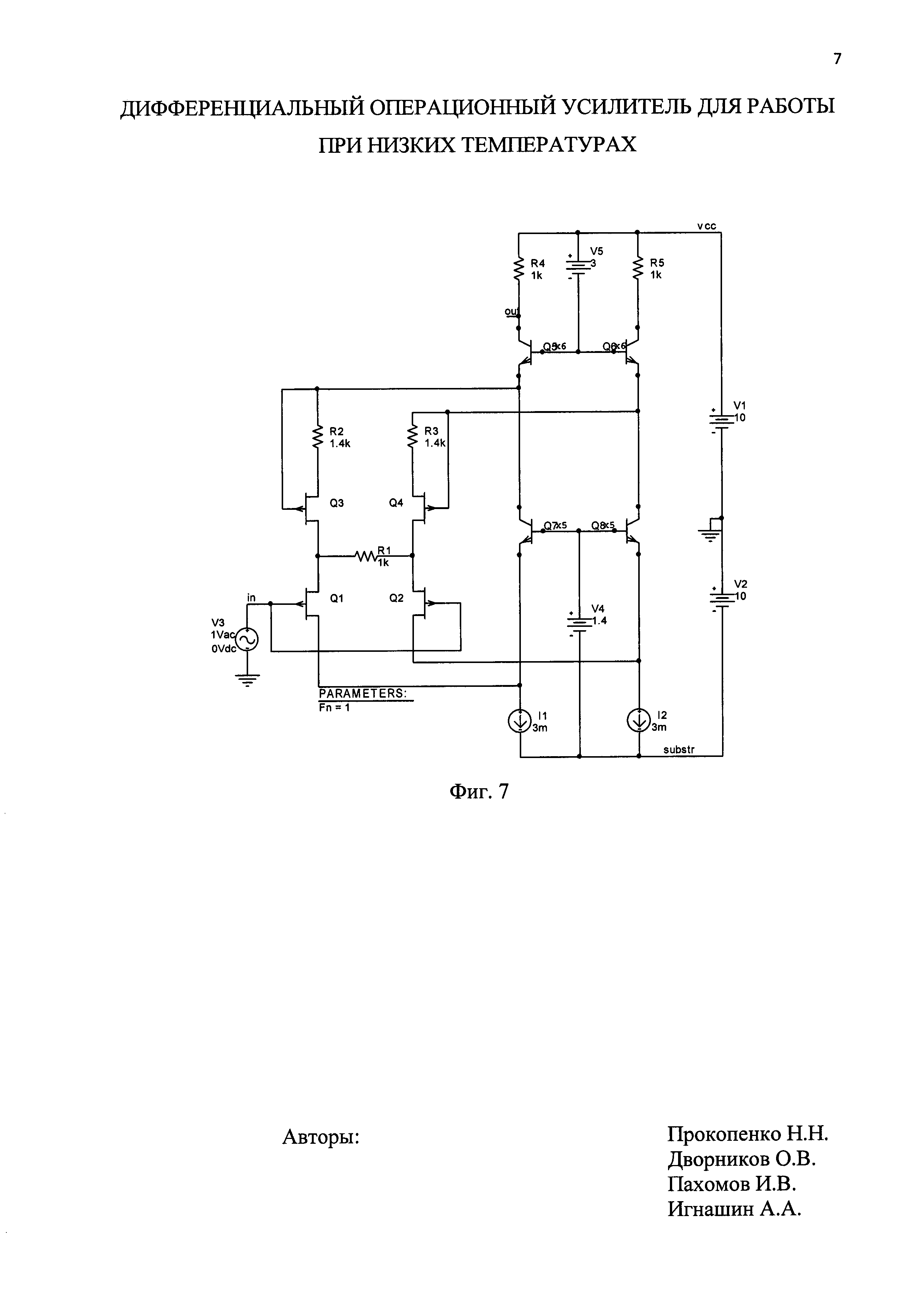

На фиг. 7 представлена схема заявляемого устройства фиг. 3 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск) для определения его коэффициента передачи входного синфазного сигнала от объединенных входов (V3) на выход (out).

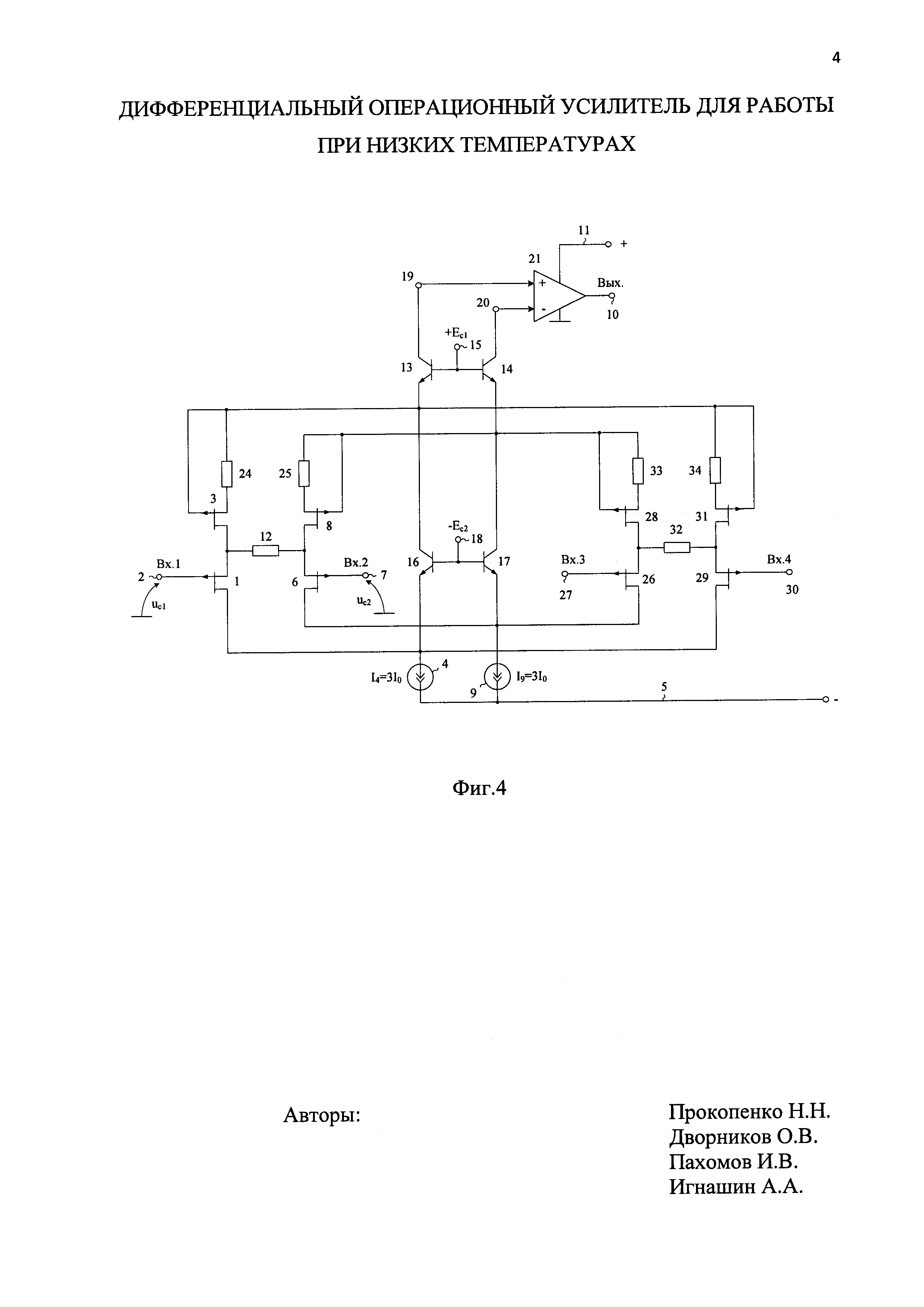

На фиг. 8 показана частотная зависимость коэффициента передачи входного синфазного сигнала в сравниваемых усилителях (фиг. 6 и фиг. 7).

На фиг. 9 показана частотная зависимость коэффициента ослабления входного синфазного сигнала известного (фиг.6) и заявляемого устройств (фиг. 7).

Дифференциальный операционный усилитель для работы при низких температурах фиг. 2 содержит первый 1 входной полевой транзистор, затвор которого соединен с первым 2 входом устройства, исток подключен к стоку первого 3 вспомогательного транзистора, а сток через первый 4 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 7 входом устройства, исток подключен к стоку второго 8 вспомогательного транзистора, а сток через второй 9 токостабилизирующий двухполюсник соединен с первой 5 шиной источника питания, первый 10 выход устройства, вторую 11 шину источника питания, первый 12 резистор отрицательной обратной связи, включенный между истоками первого 1 и второго 6 входных полевых транзисторов. В схему введены новые элементы и связи между ними - затвор первого 3 вспомогательного транзистора подключен к эмиттеру первого 13 выходного транзистора, затвор второго 8 вспомогательного транзистора соединен с эмиттером второго 14 выходного транзистора, исток первого 3 вспомогательного транзистора связан с эмиттером первого 13 выходного транзистора, исток второго 8 вспомогательного транзистора связан с эмиттером второго 14 выходного транзистора, база которого соединена с базой первого 13 выходного транзистора и подключена к первой 15 цепи смещения потенциалов, сток первого 1 входного транзистора соединен с эмиттером первого 16 дополнительного транзистора, сток второго 6 входного транзистора соединен с эмиттером второго 17 дополнительного транзистора, база которого подключена к базе первого 16 дополнительного транзистора и соединена со второй 18 цепью смещения потенциалов, коллектор первого 16 дополнительного транзистора связан с эмиттером первого 13 выходного транзистора, коллектор второго 17 дополнительного транзистора соединен с эмиттером второго 14 выходного транзистора, причем коллекторы первого 13 и второго 14 выходных транзисторов связаны с соответствующими первым 19 и вторым 20 входами выходного дифференциального каскада 21, согласованного со второй 11 шиной источника питания, выход которого соединен с выходом устройства 10.

На фиг. 2 выходной дифференциальный каскад 21 содержит (в частном случае) токовое зеркало 22 и буферный усилитель 23, согласованные со второй 11 шиной источника питания. Причем выход буферного усилителя 23 подключен к выходу устройства 10.

В соответствии с п. 2 формулы изобретения на фиг. 3 исток первого 3 вспомогательного транзистора связан с эмиттером первого 13 выходного транзистора через первый 24 дополнительный резистор, а исток второго 8 вспомогательного транзистора связан с эмиттером второго 14 выходного транзистора через второй 25 дополнительный резистор.

В соответствии с п. 3 формулы изобретения, в схему фиг. 4 введены третий 26 входной полевой транзистор, затвор которого соединен с третьим 27 входом устройства, сток подключен к эмиттеру второго 17 дополнительного транзистора, исток соединен со стоком третьего 28 вспомогательного транзистора, затвор введенного в схему четвертого 29 входного полевого транзистора соединен с четвертым 30 входом устройства, сток подключен к первому 16 дополнительному транзистору, исток соединен со стоком четвертого 31 вспомогательного транзистора, между истоками третьего 26 входного полевого транзистора и стоком четвертого 29 входного полевого транзистора включен второй 32 резистор отрицательной обратной связи, затвор третьего 28 вспомогательного транзистора соединен с эмиттером второго 14 выходного транзистора, затвор четвертого 31 вспомогательного транзистора соединен с эмиттером первого 13 выходного транзистора, исток третьего 28 вспомогательного транзистора соединен с эмиттером второго 14 выходного транзистора через третий 33 дополнительный резистор, а исток четвертого 31 вспомогательного транзистора соединен с эмиттером первого 13 выходного транзистора через четвертый 34 дополнительный резистор.

В соответствии с п. 4 формулы изобретения на фиг. 5 в качестве первого 13 выходного транзистора, второго 14 выходного транзистора, первого 16 дополнительного транзистора, второго 17 дополнительного транзистора используются соответствующие полевые транзисторы, затвор каждого из которых соответствует базе биполярного транзистора, исток - эмиттеру биполярного транзистора, а сток - коллектору биполярного транзистора.

Рассмотрим работу ОУ фиг. 2.

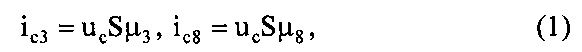

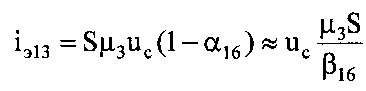

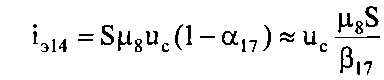

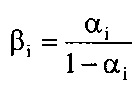

При изменении входного синфазного сигнала на первом 2 и втором 7 входах устройства uc=uc1=uc2 изменяются токи стоков первого 3 (ic3) и второго 8 (ic8) вспомогательных транзисторов:

где S=S3=S8 - крутизна стокозатворной характеристики первого 3 и второго 8 вспомогательных транзисторов;

μ3, μ8=10-2÷10-3 - коэффициент внутренней обратной связи первого 3 и второго 8 вспомогательных транзисторов в схеме с общим затвором.

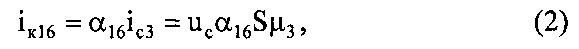

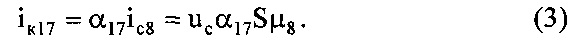

Приращения токов ic3, ic8 передаются через первый 1 и второй 6 входные полевые транзисторы в эмиттерные, а затем в коллекторные цепи первого 16 и второго 17 дополнительных транзисторов:

В результате, изменения токов в эмиттерах первого 13 и второго 14 выходных транзисторов определяются формулами

,

,

.

.

где  - коэффициент усиления по току базы первого 16 и второго 17 дополнительных транзисторов.

- коэффициент усиления по току базы первого 16 и второго 17 дополнительных транзисторов.

Как следствие, токи ошибки первого 19 и второго 20 входов дифференциального каскада 21 в заявляемом усилителе существенно (в β раз) уменьшаются. При прочих равных условиях (например, при асимметрии входов выходного каскада 21 или применении в его структуре неидентичных резисторов нагрузки) это улучшает К ос.сф. Данный вывод подтверждается графиками фиг. 8, фиг. 9, которые показывают, что предлагаемое устройство обеспечивает более глубокое ослабление входных синфазных сигналов.

Таким образом, в сравнении с прототипом заявляемое устройство является более прецизионным при работе с синфазными сигналами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Patent US 5.648.743, fig. 3.

2. Patent US 4.538.155, fig. 2.

Схемы с входными ПТ

3. Patent US 4.596.958, fig. 2.

4. Patent US 4.537.578, fig. 1.

5. Patent US 8.169.263, fig. 5.

6. Patent US 7.2020.738, fig. 7, fig. 11.

7. Patent US 4.198.610, fig. 4.

8. Patent US 6.407.537, fig. 1.

9. Patent US 5.367.271, fig. 2.

10. Патент РФ 2070768, фиг. 1.

11. Патент РФ 2571399, фиг. 2.

12. Патент РФ 2571578, фиг. 3.

13. Патент US 2008/0088374.

14. Дворников О.В. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 1 / О.В. Дворников, В.А. Чеховский Н.Н., В.Л. Дятлов, Н.Н. Прокопенко. Современная электроника №4. 2015. С. 44-49.

15. Дворников О.В. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О.В. Дворников, В.А. Чеховский Н.Н., В.Л. Дятлов, Н.Н. Прокопенко. Современная электроника №5. 2015. С. 24-28.

16. Дворников О.В. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 3/ О.В. Дворников, В.А. Чеховский Н.Н., В.Л. Дятлов, Н.Н. Прокопенко. Современная электроника №6. 2015. С. 34-39.