Результат интеллектуальной деятельности: ПРОЦЕССОР, СПОСОБ, СИСТЕМА И ИЗДЕЛИЕ ДЛЯ ВЕКТОРНОГО ИНДЕКСИРОВАННОГО ДОСТУПА К ПАМЯТИ ПЛЮС АРИФМЕТИЧЕСКОЙ И/ИЛИ ЛОГИЧЕСКОЙ ОПЕРАЦИИ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, в основном, относятся к микропроцессорам. В частности, варианты осуществления, описанные в данном документе, в основном, относятся к микропроцессорам, обеспечивающим доступ к памяти в ответ на инструкции.

Уровень техники

Процессоры обычно используются для выполнения инструкций для доступа к системной памяти. Например, процессоры могут выполнять инструкции загрузки для загрузки или считывания данных из системной памяти и/или инструкции сохранения для хранения или записи данных в системной памяти.

Некоторые процессоры используются для выполнения векторных индексированных инструкций загрузки (например, для загрузки векторных элементов с использованием векторных индексов). Эти векторные индексированные инструкции загрузки также упоминаются в данной области техники как векторные инструкции сбора или просто gather-инструкции. Intel® справочник по программированию по усовершенствованному вектору расширения, справочный номер документа 319433-011, опубликовано в июне 2011, описывает несколько векторных gather-инструкций (VGATHER). Примеры включают в себя VGATHERDPD, VGATHERQPD, VGATHERDPS, VGATHERQPS, VPGATHERDD, VPGATHERQD, VPGATHERDQ и VPGATHERQQ. Эти инструкции сбора могут использоваться для сбора или загрузки множества элементов данных из памяти с использованием множества соответствующих индексов памяти.

Некоторые процессоры используются для выполнения векторных индексированных инструкций для сохранения данных (например, сохранить векторные элементы с использованием векторных индексов). Эти векторные индексированные инструкции на сохранение данных также упоминаются в данной области техники, как векторные инструкции разброса или просто scatter-инструкции. Intel® справочник по программированию по архитектуре расширения набора инструкций, справочный номер документа 319433-015, опубликован в июле 2013, описывает несколько векторных scatter-инструкций (VSCATTER). Эти инструкции разброса могут использоваться для разнесенияпо разным участкам памяти или хранения нескольких элементов данных из исходного операнда в системную память, используя множество соответствующих индексов памяти.

Краткое описание чертежей

Изобретение описывается со ссылкой на прилагаемые чертежи, иллюстрирующие варианты осуществления, а именно:

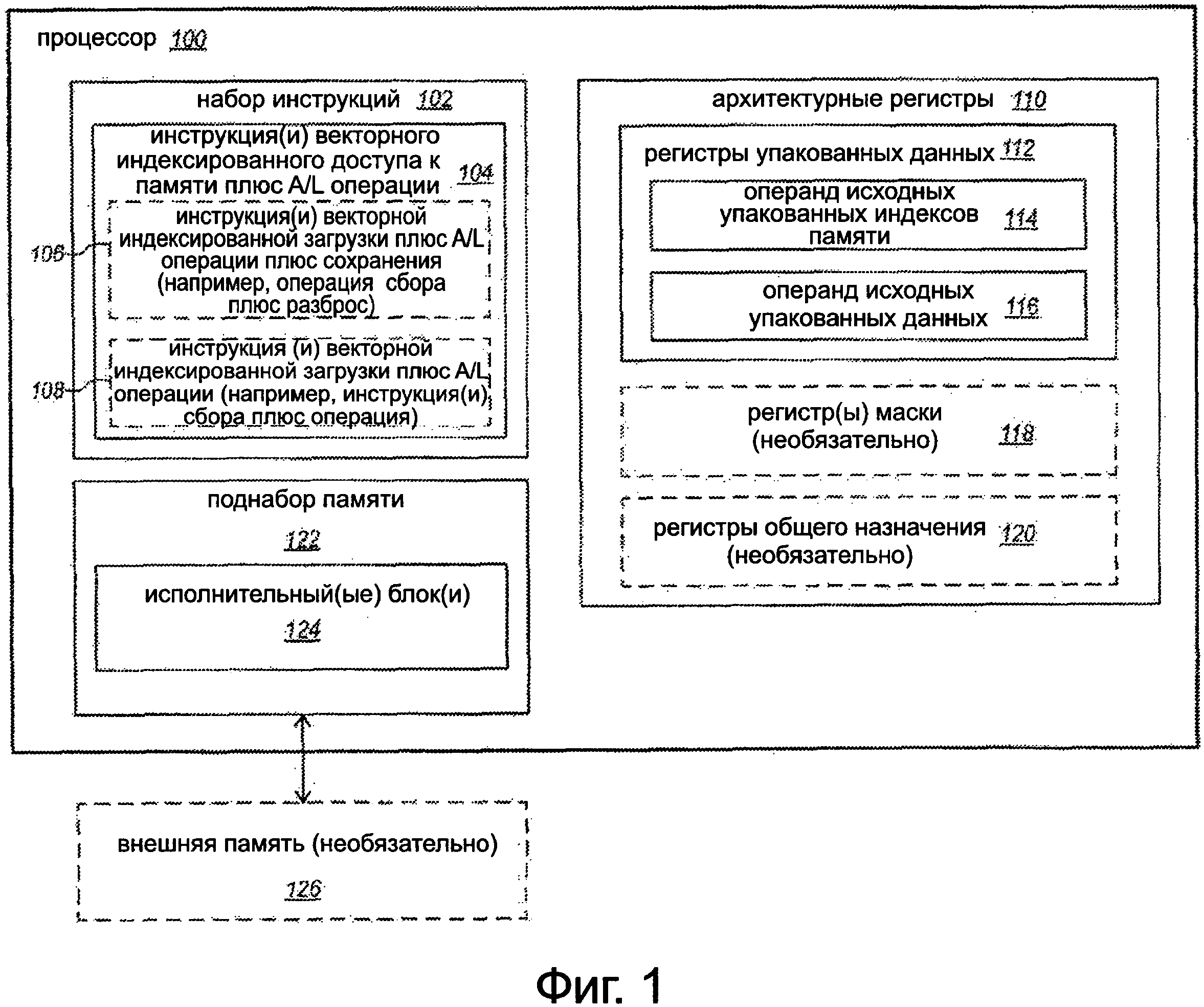

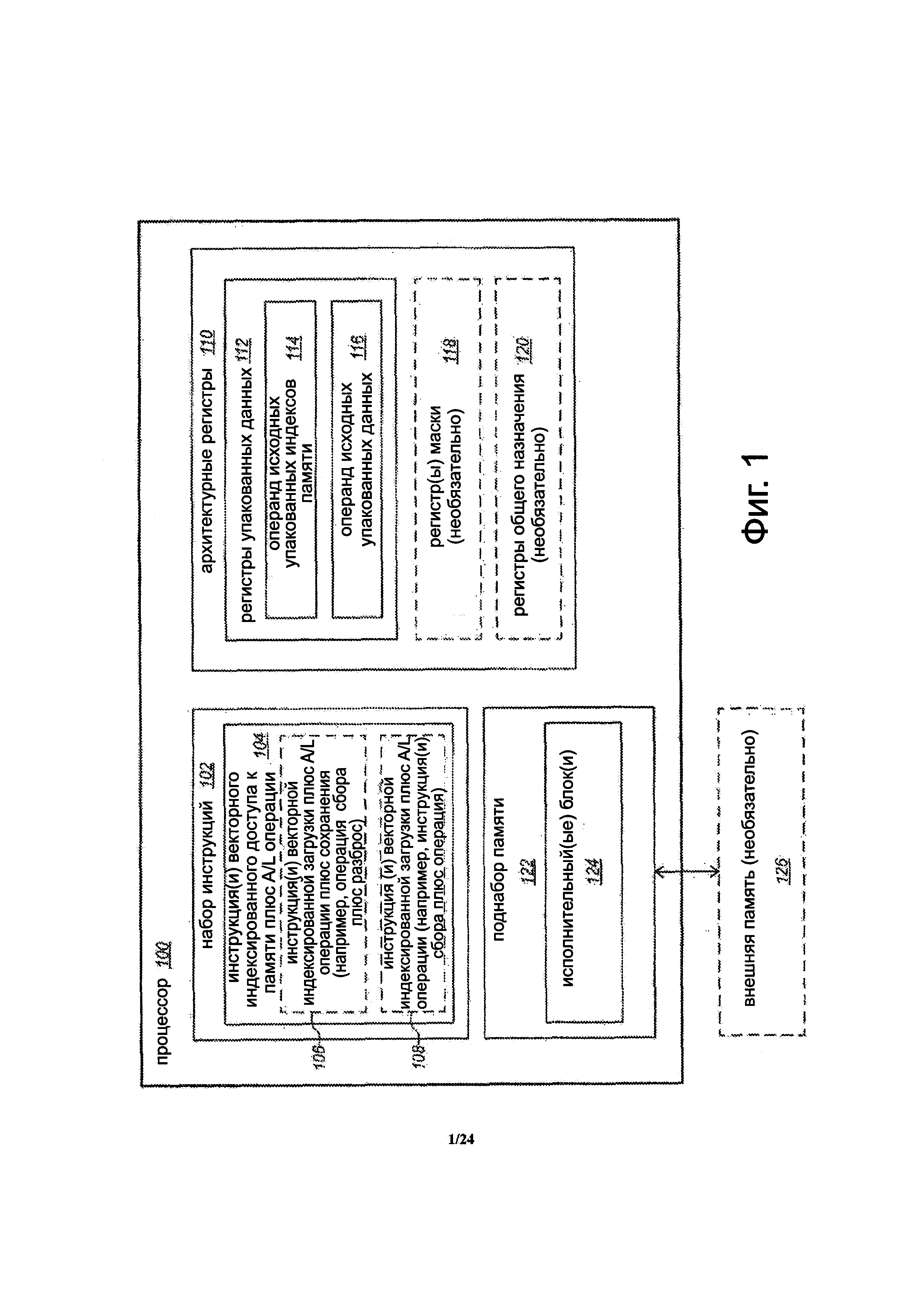

Фиг. 1 представляет собой блок-схему варианта осуществления процессора, который выполнен с возможностью выполнять одну или более инструкций векторного индексированного доступа к памяти плюс арифметическую и/или логическую операцию.

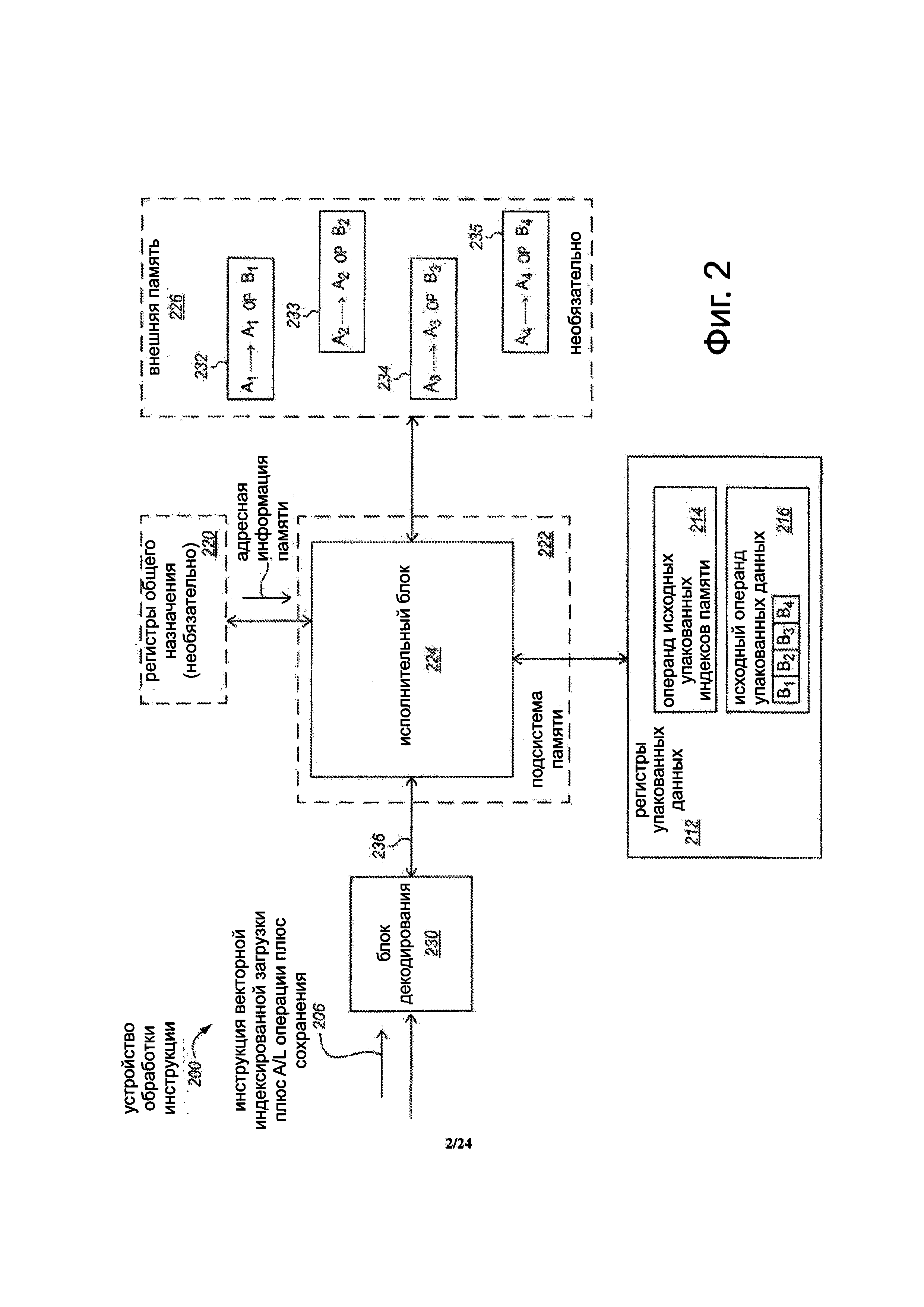

Фиг. 2 представляет блок-схему варианта осуществления устройства обработки инструкции, которое выполнено с возможностью выполнять одну или более инструкций векторного индексированного доступа к памяти плюс арифметическую и/или логическую операцию.

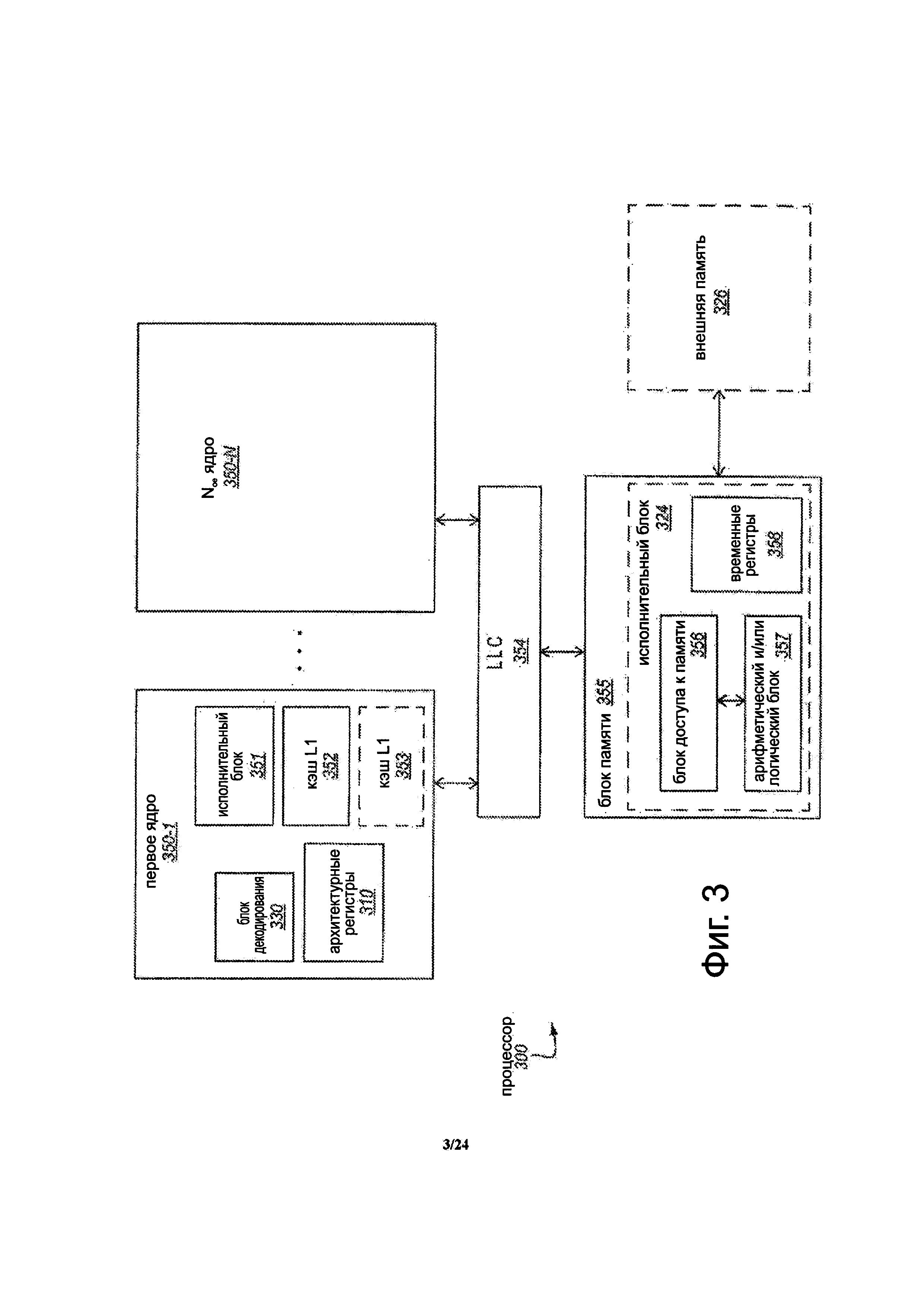

Фиг. 3 представляет собой блок-схему, иллюстрирующую один вариант осуществления структуры расположения исполнительного блока в процессоре.

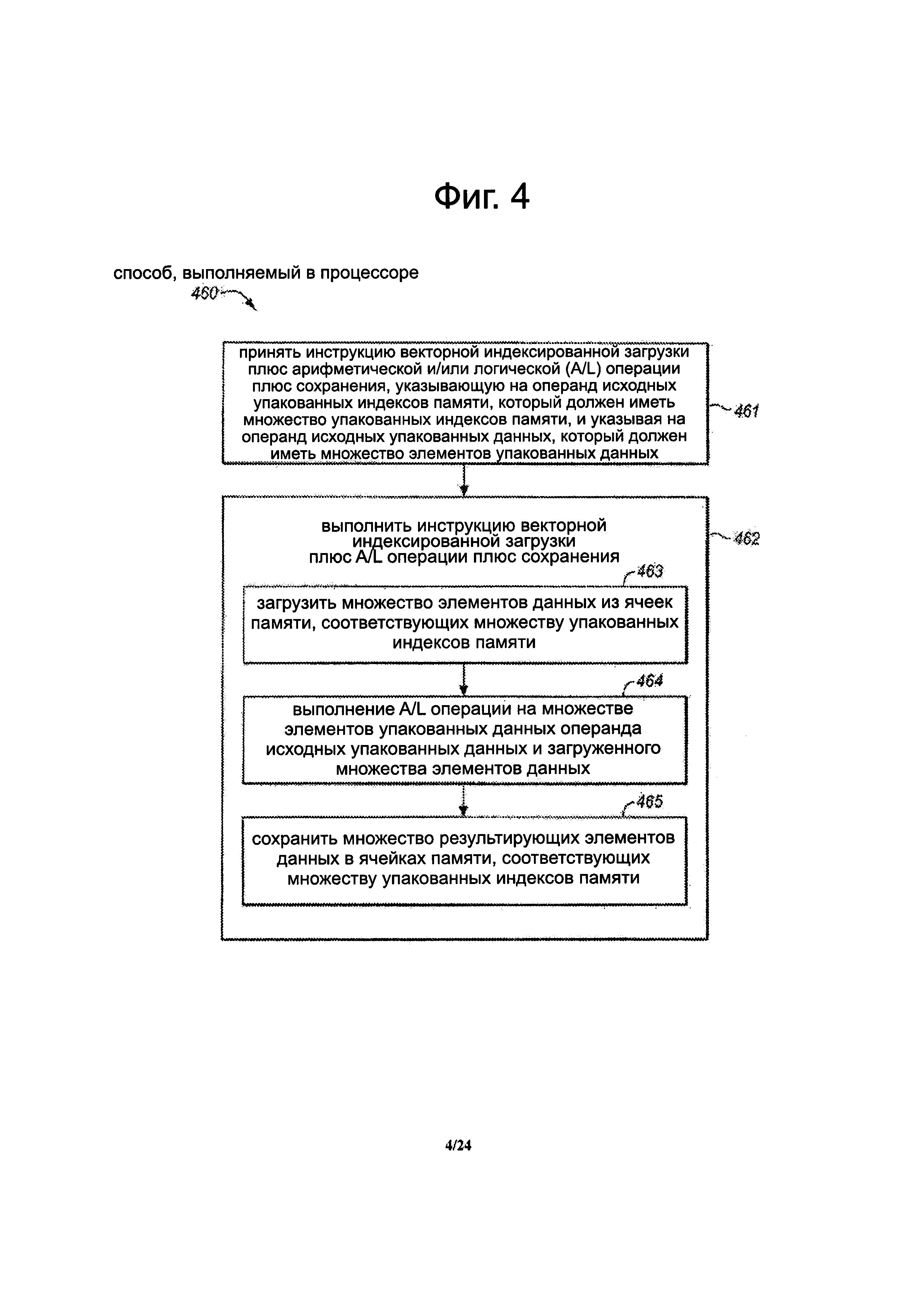

Фиг. 4 является блок-схемой алгоритма варианта осуществления способа обработки варианта осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс хранение.

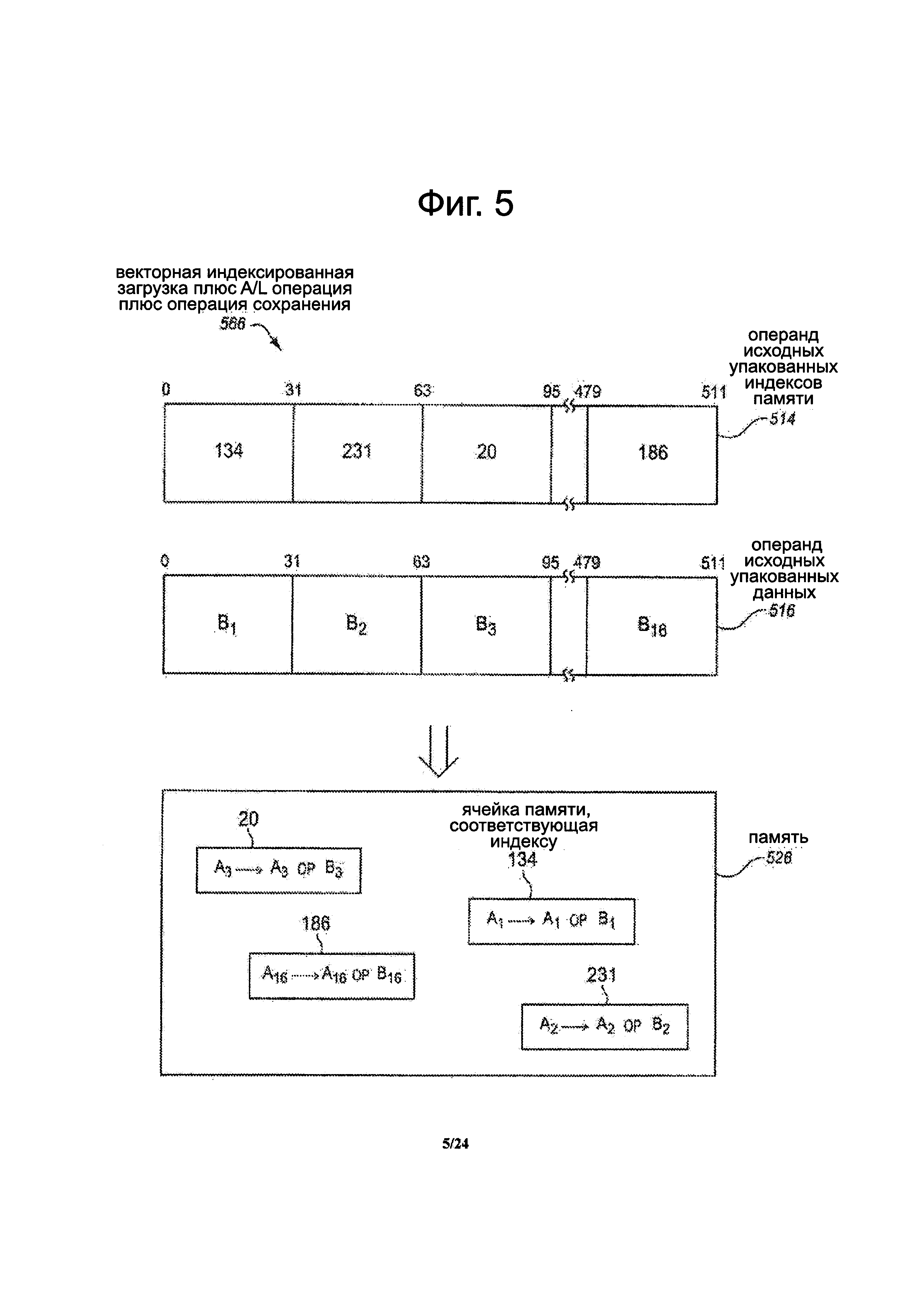

Фиг. 5 представляет собой блок-схему, иллюстрирующую вариант осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс операции сохранения.

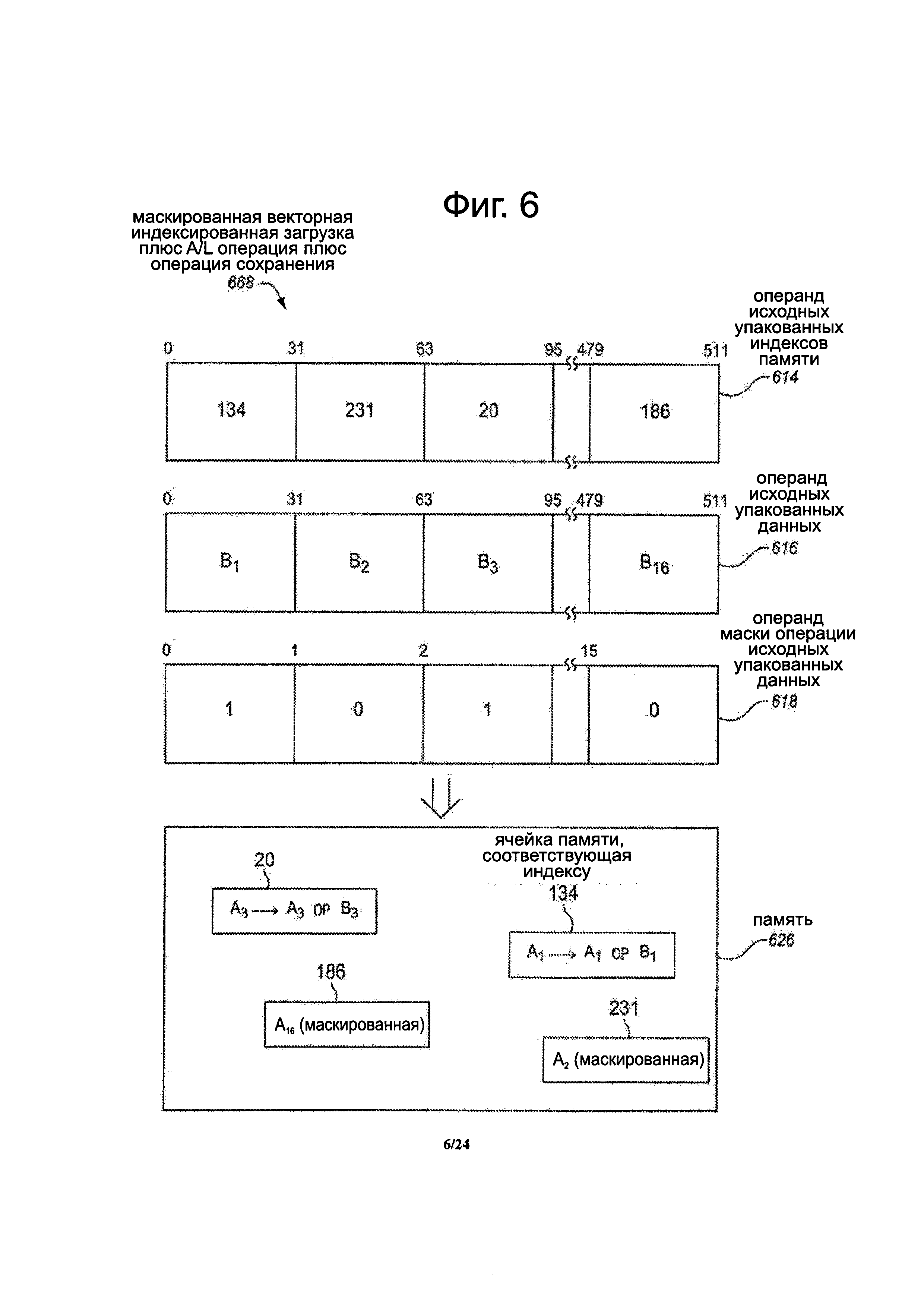

Фиг. 6 представляет собой блок-схему, иллюстрирующую вариант осуществления замаскированной векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс операции сохранения.

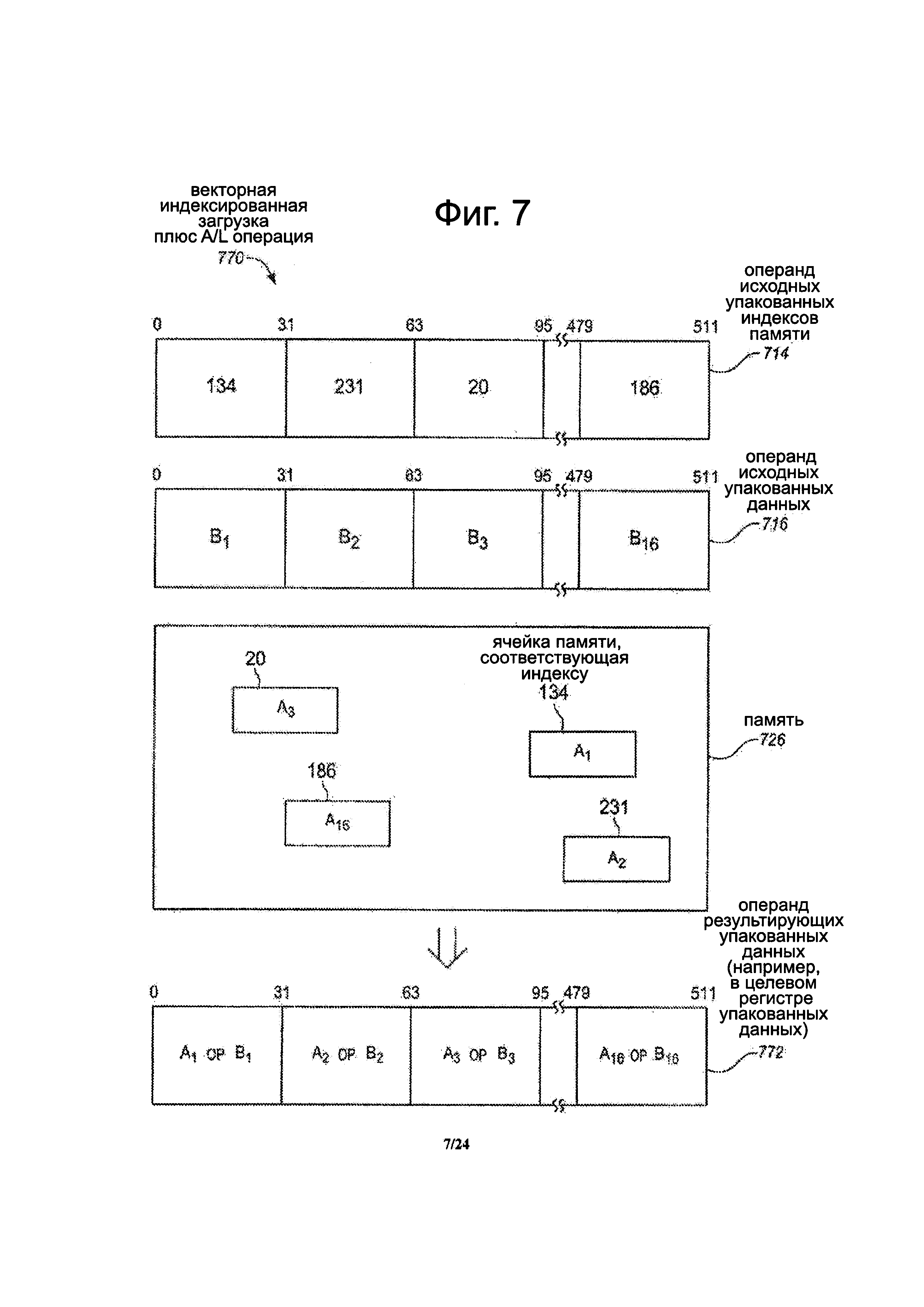

Фиг. 7 представляет блок-схему, иллюстрирующую вариант осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции.

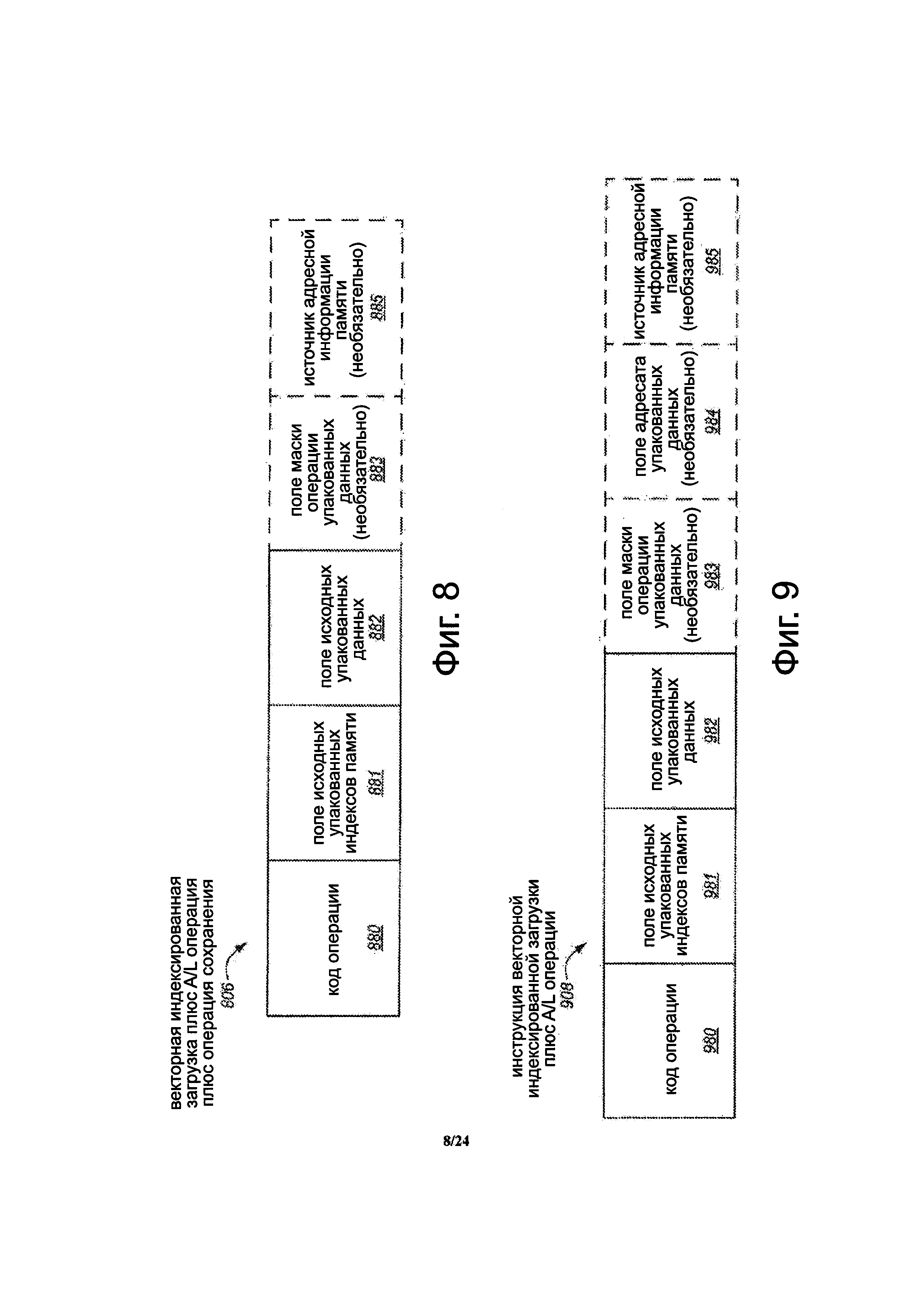

Фиг. 8 является блок-схемой варианта осуществления формата для векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс инструкции сохранения.

Фиг. 9 является блок-схемой варианта осуществления формата для векторной индексированной инструкции загрузки плюс арифметической и/или логической операции.

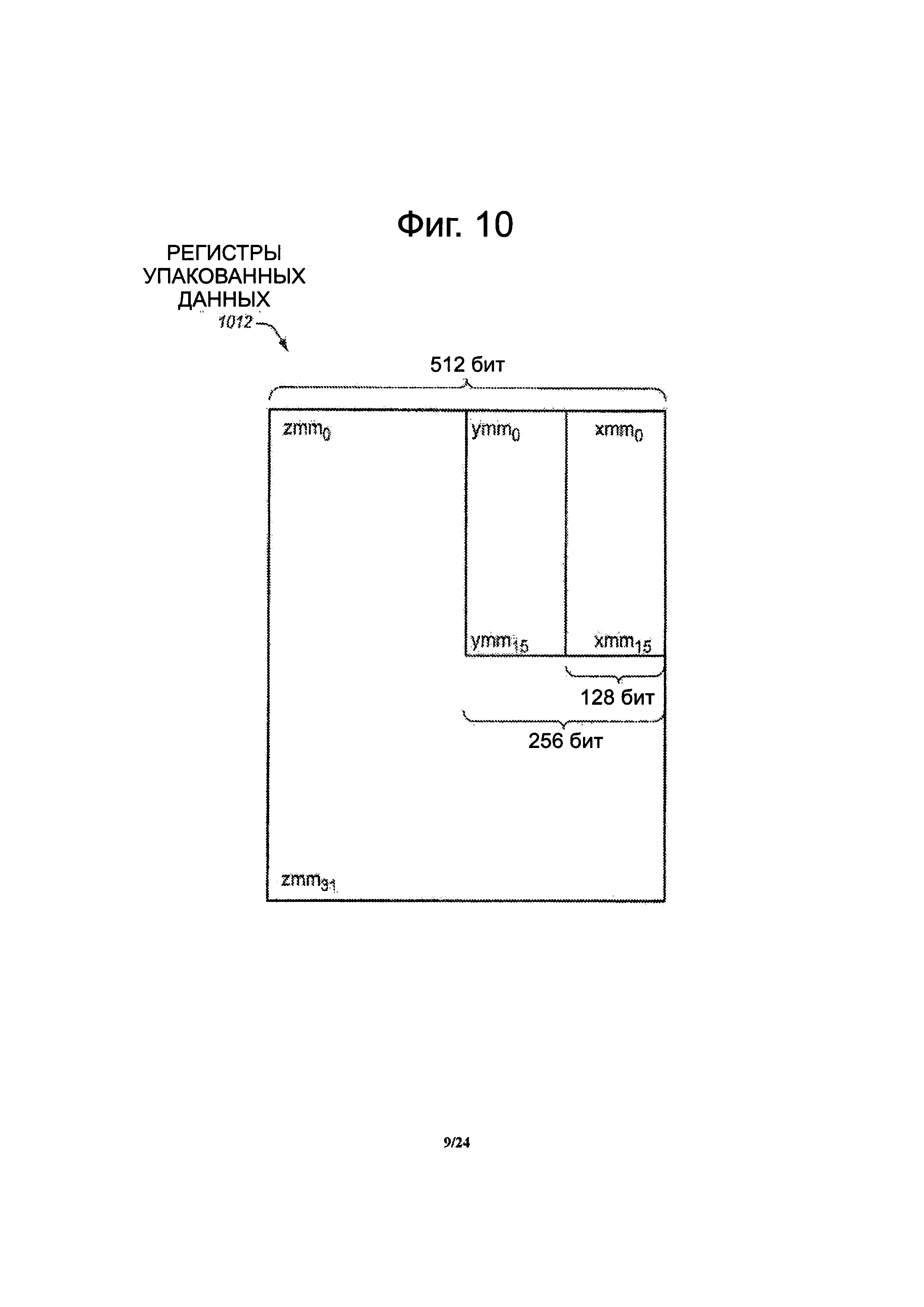

Фиг. 10 представляет собой блок-схему примера варианта осуществления конкретного подходящего набора упакованных данных регистров.

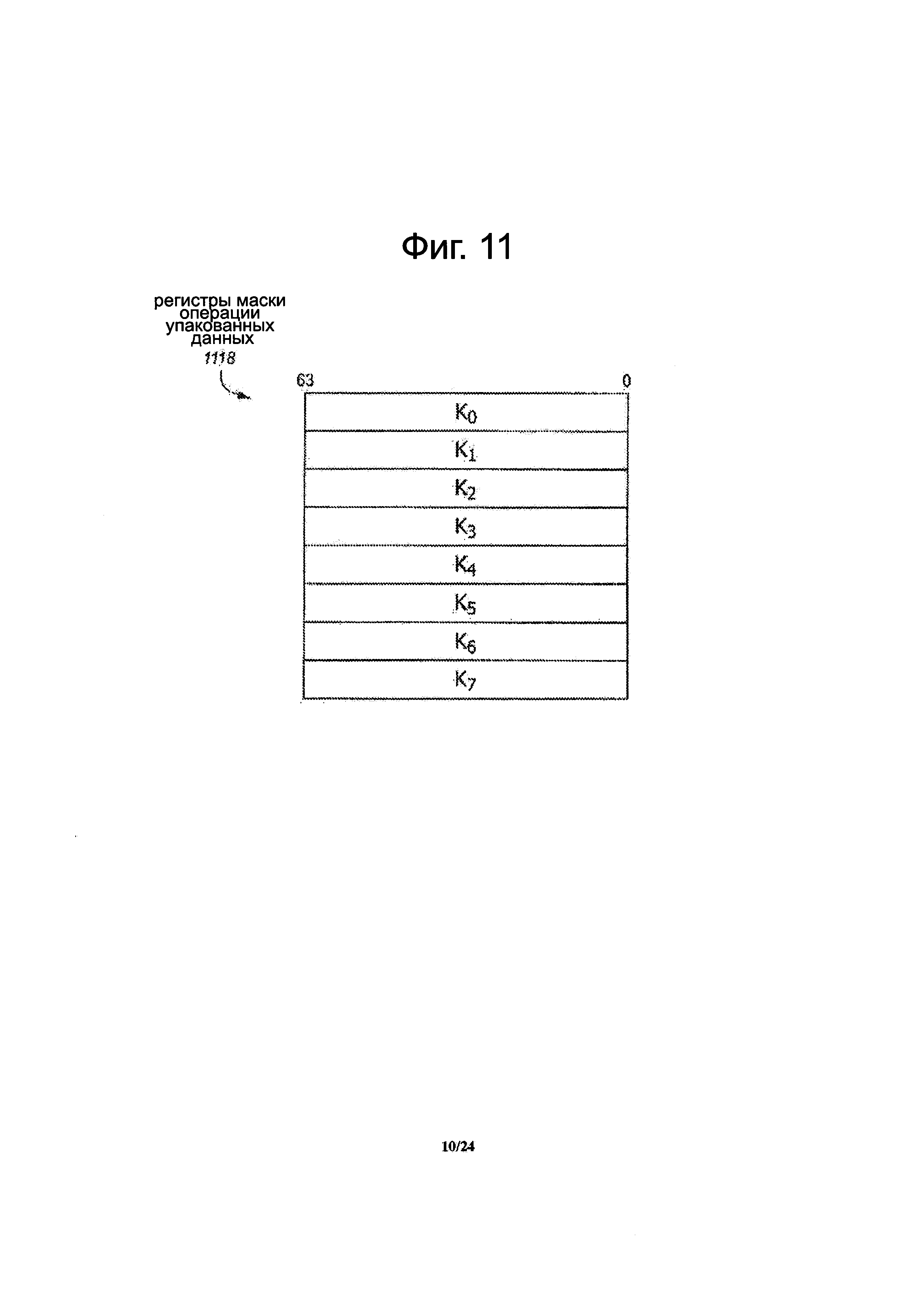

Фиг. 11 представляет собой блок-схему примера варианта осуществления конкретного подходящего набора упакованных данных операции маскирования регистров.

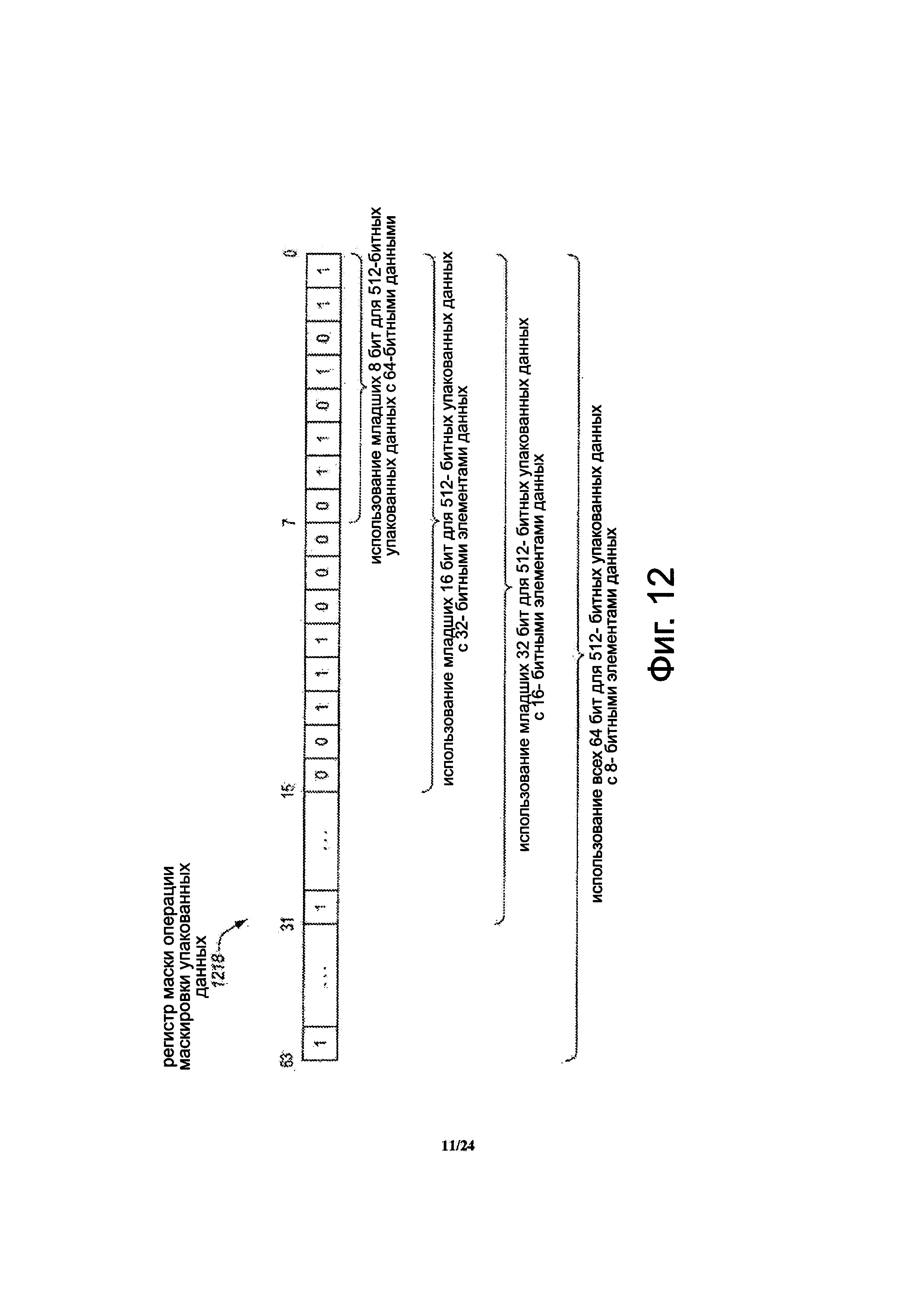

Фиг. 12 является схемой, иллюстрирующей пример варианта осуществления конкретных подходящих 64-разрядных упакованных данных операции маскирования регистров.

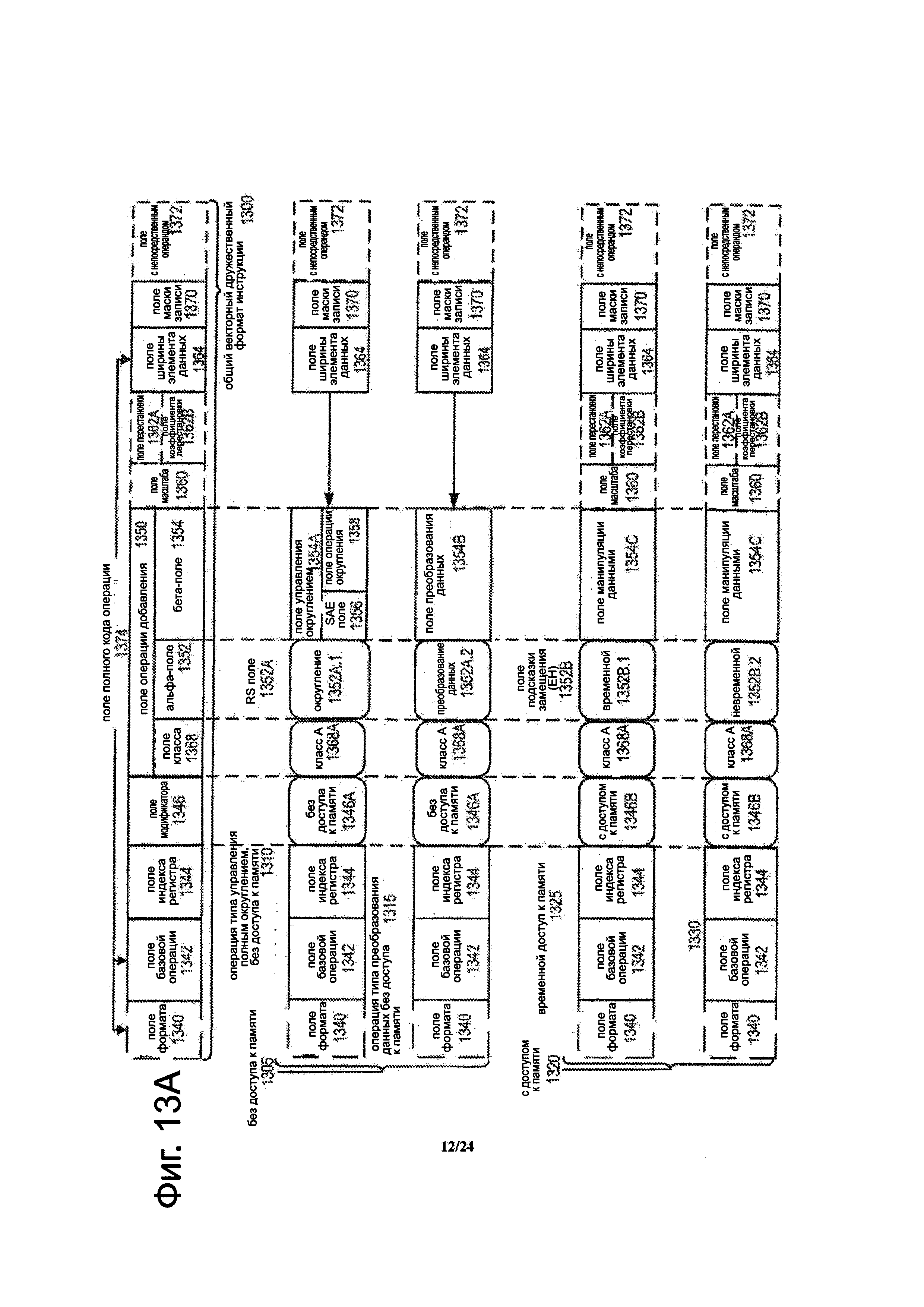

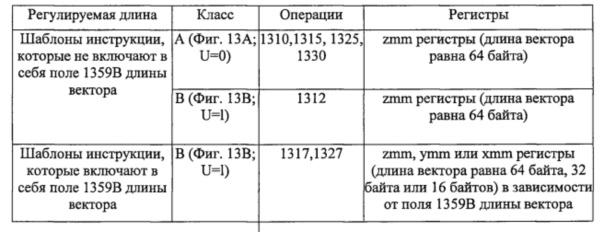

Фиг. 13А является блок-схемой, иллюстрирующей универсальный векторный дружественный формат инструкции и шаблоны инструкции класса А согласно вариантам осуществления изобретения.

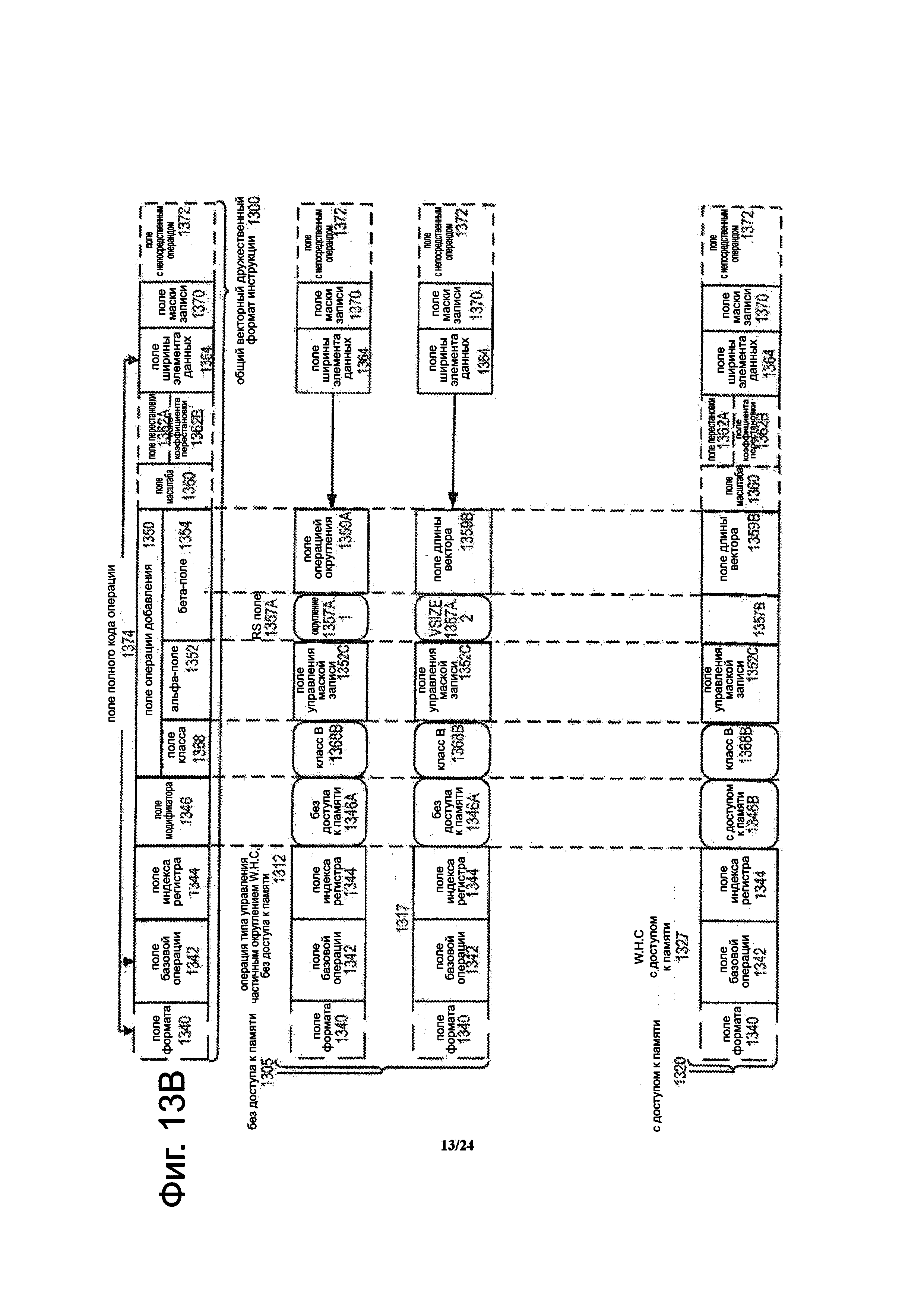

Фиг. 13В является блок-схемой, иллюстрирующей универсальный векторный дружественный формат инструкции и шаблоны инструкции класса В согласно вариантам осуществления изобретения.

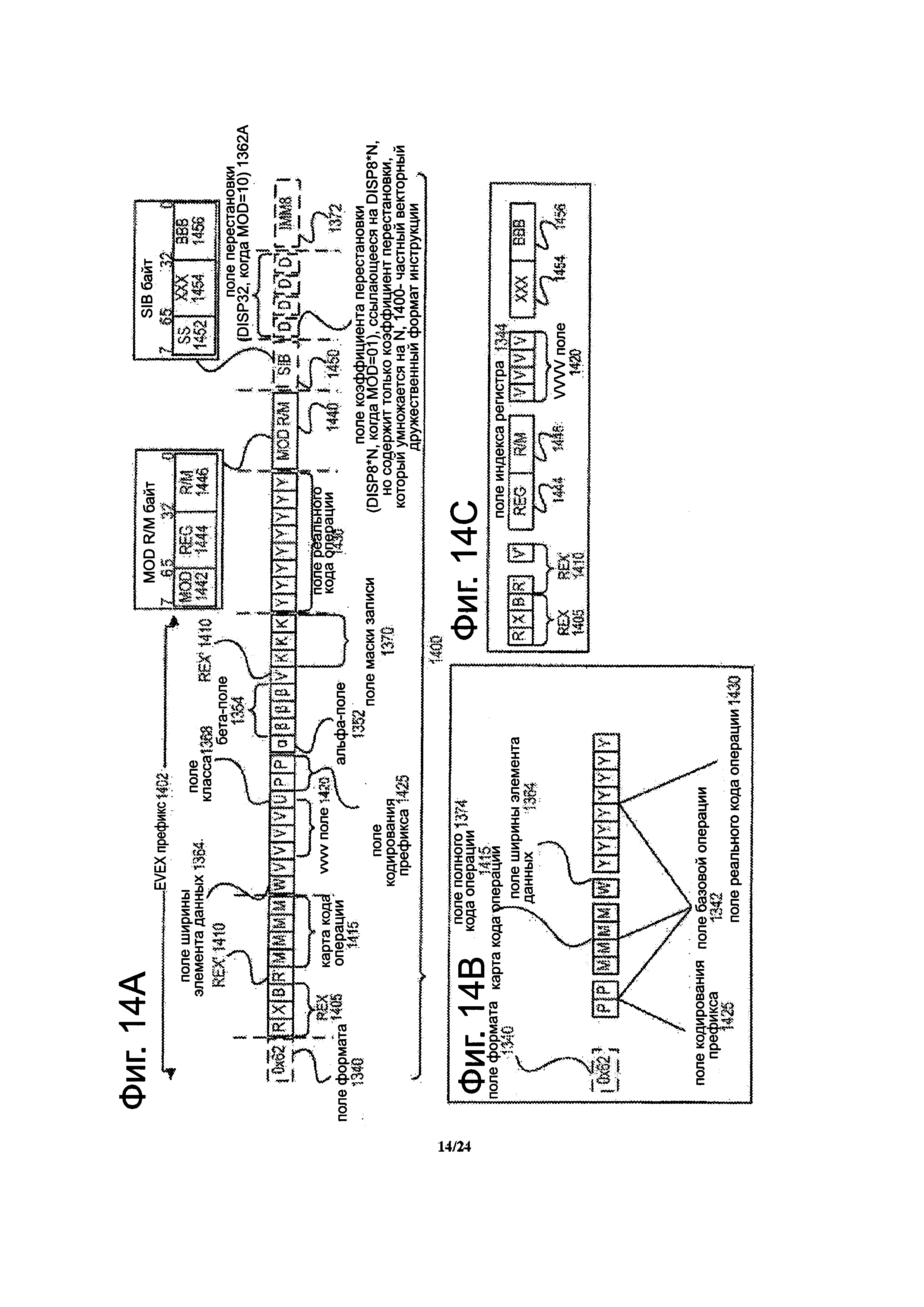

Фиг. 14А представляет собой блок-схему, иллюстрирующую примерный конкретный векторный дружественный формат инструкции согласно вариантам осуществления изобретения.

Фиг. 14В является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие полное поле кода операции согласно одному варианту осуществления изобретения.

Фиг. 14С является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие поле индекса регистра согласно одному варианту осуществления изобретения.

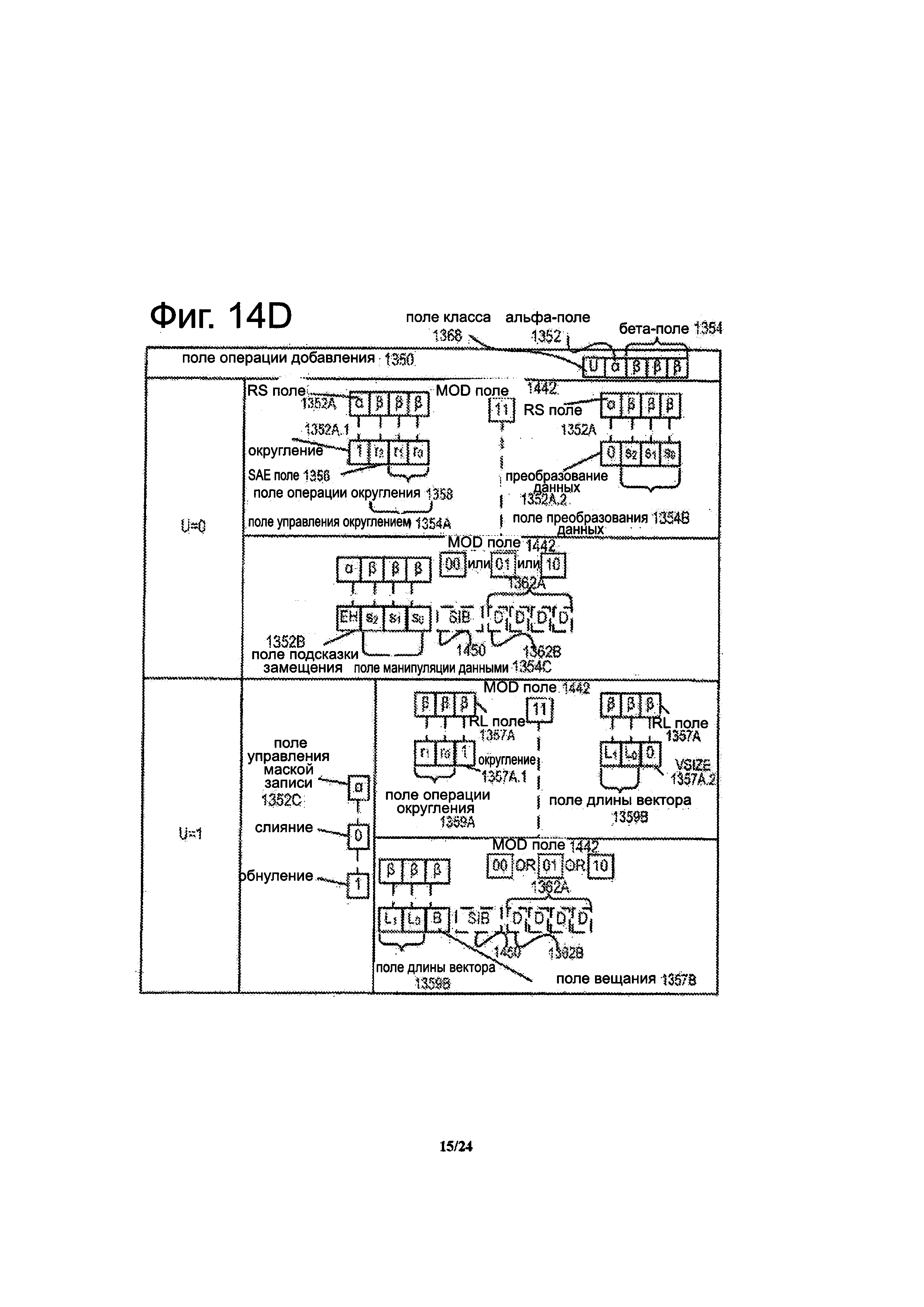

Фиг. 14D является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие поле операции приращения согласно одному варианту осуществления изобретения.

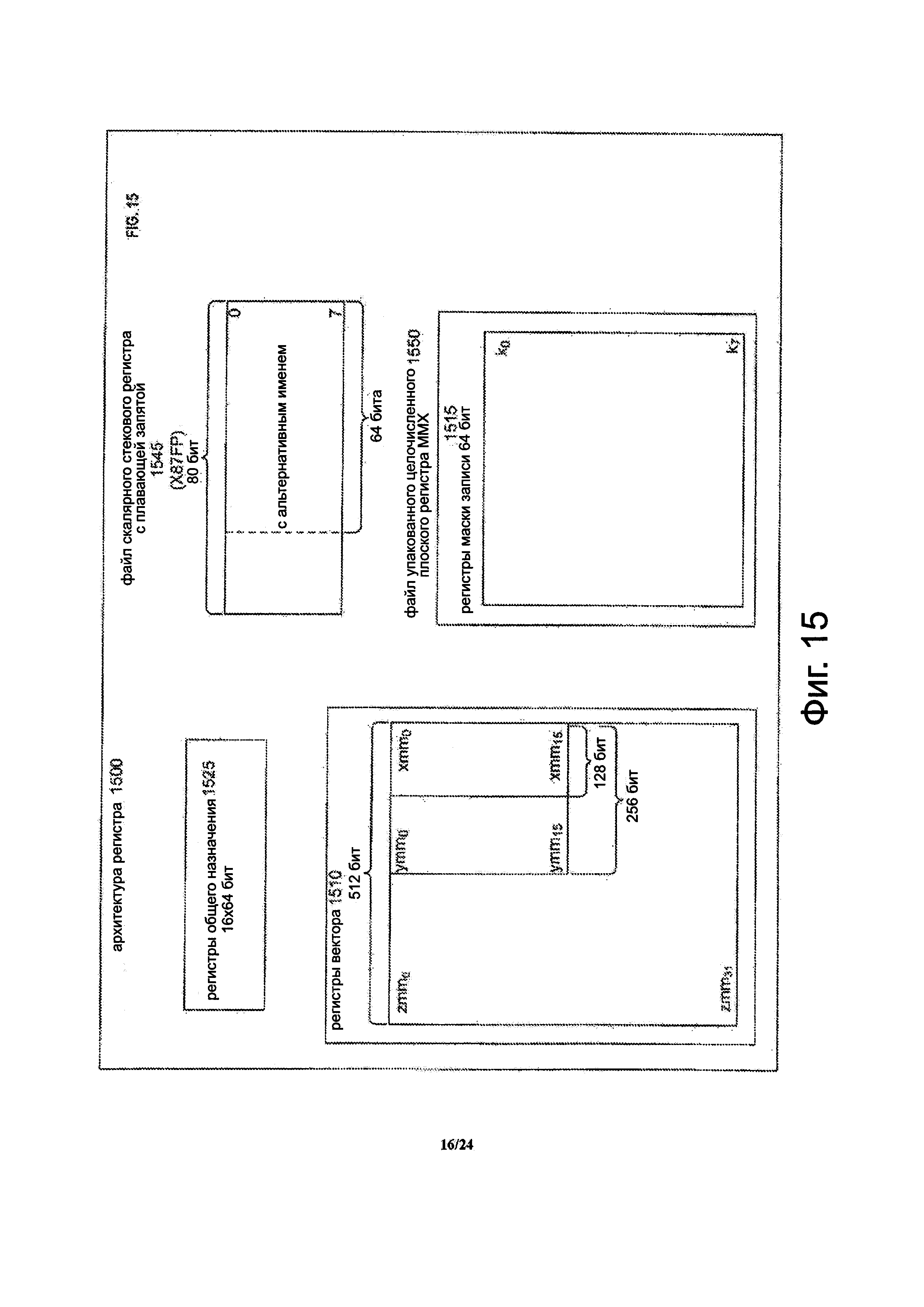

Фиг. 15 представляет блок-схему архитектуры регистра согласно одному варианту осуществления изобретения.

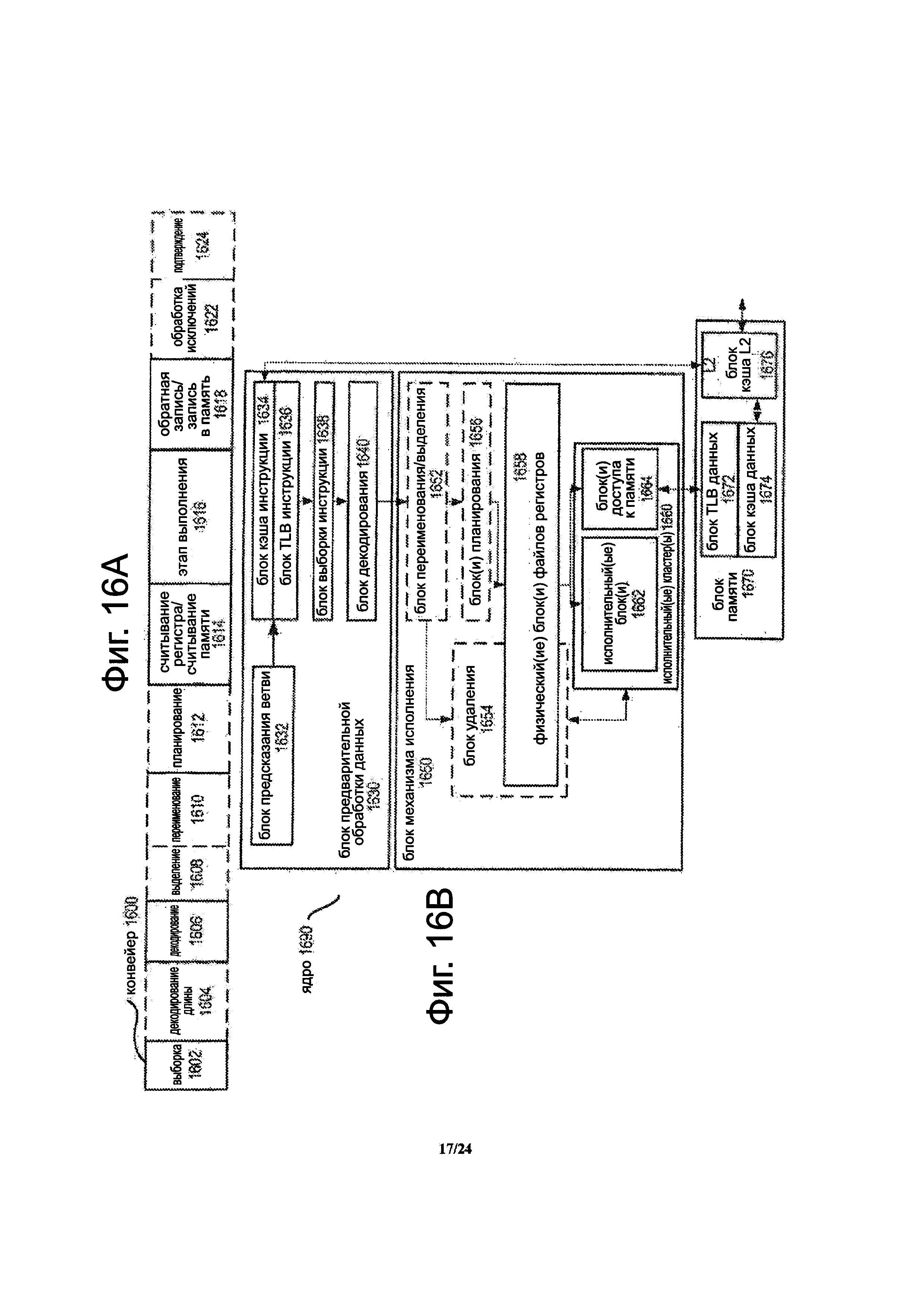

Фиг. 16А представляет собой блок-схему, иллюстрирующую оба примерный упорядоченный конвейер и примерный порядок переименования регистров, конвейер с изменением выполнения последовательности команд согласно вариантам осуществления изобретения.

Фиг. 16В показывает ядро процессора, включающее в себя блок предварительной обработки данных, соединенный с блоком механизма исполнения, и оба соединены с блоком памяти.

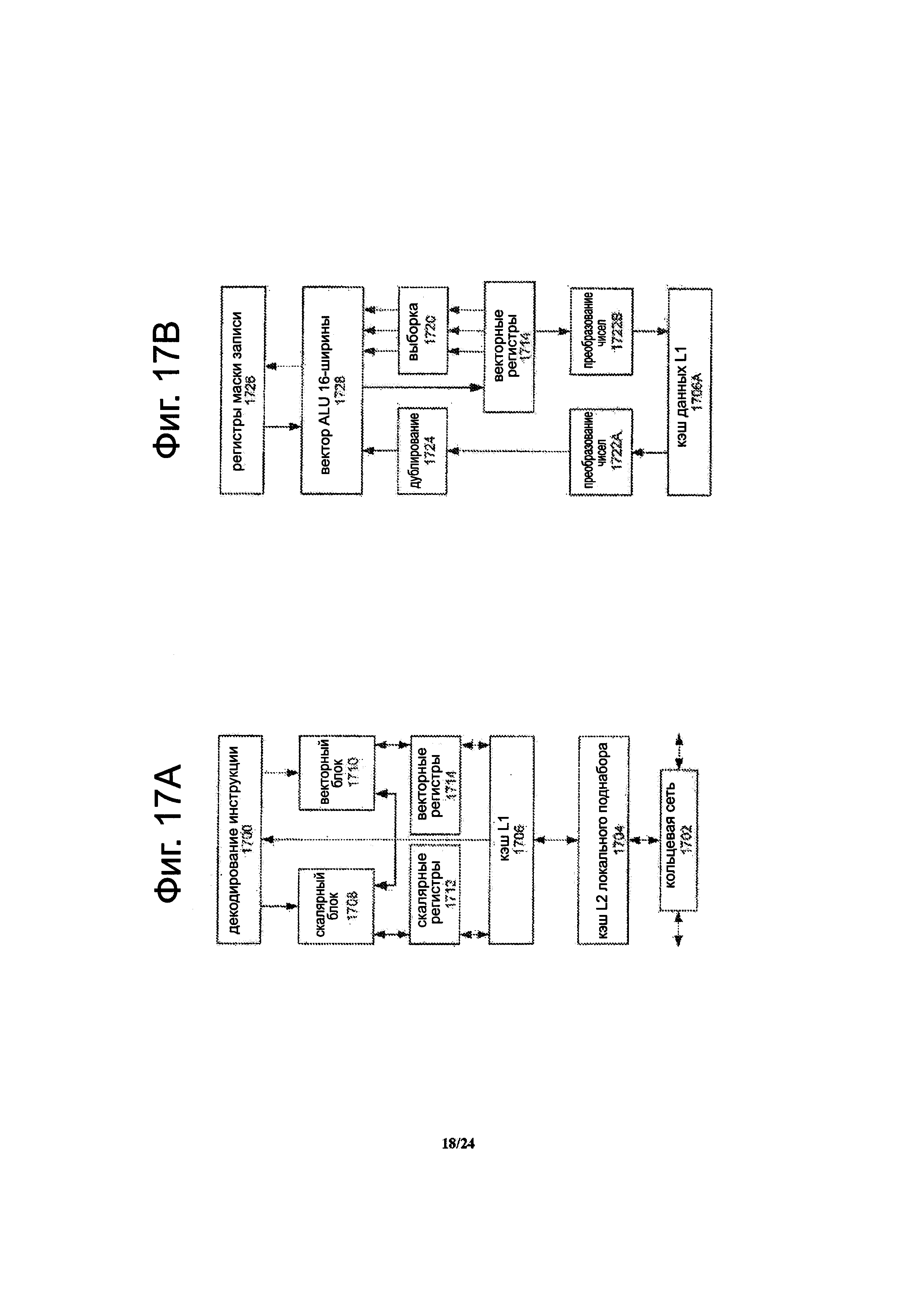

Фиг. 17А является блок-схемой одноядерного процессора, подключенного к накристальному межсетевому соединению и с ее локальным подмножеством кэша уровня 2 (L2), согласно вариантам осуществления изобретения.

Фиг.17В представляет собой развернутый вид части ядра процессора, показанного на фиг. 17А, согласно вариантам осуществления изобретения.

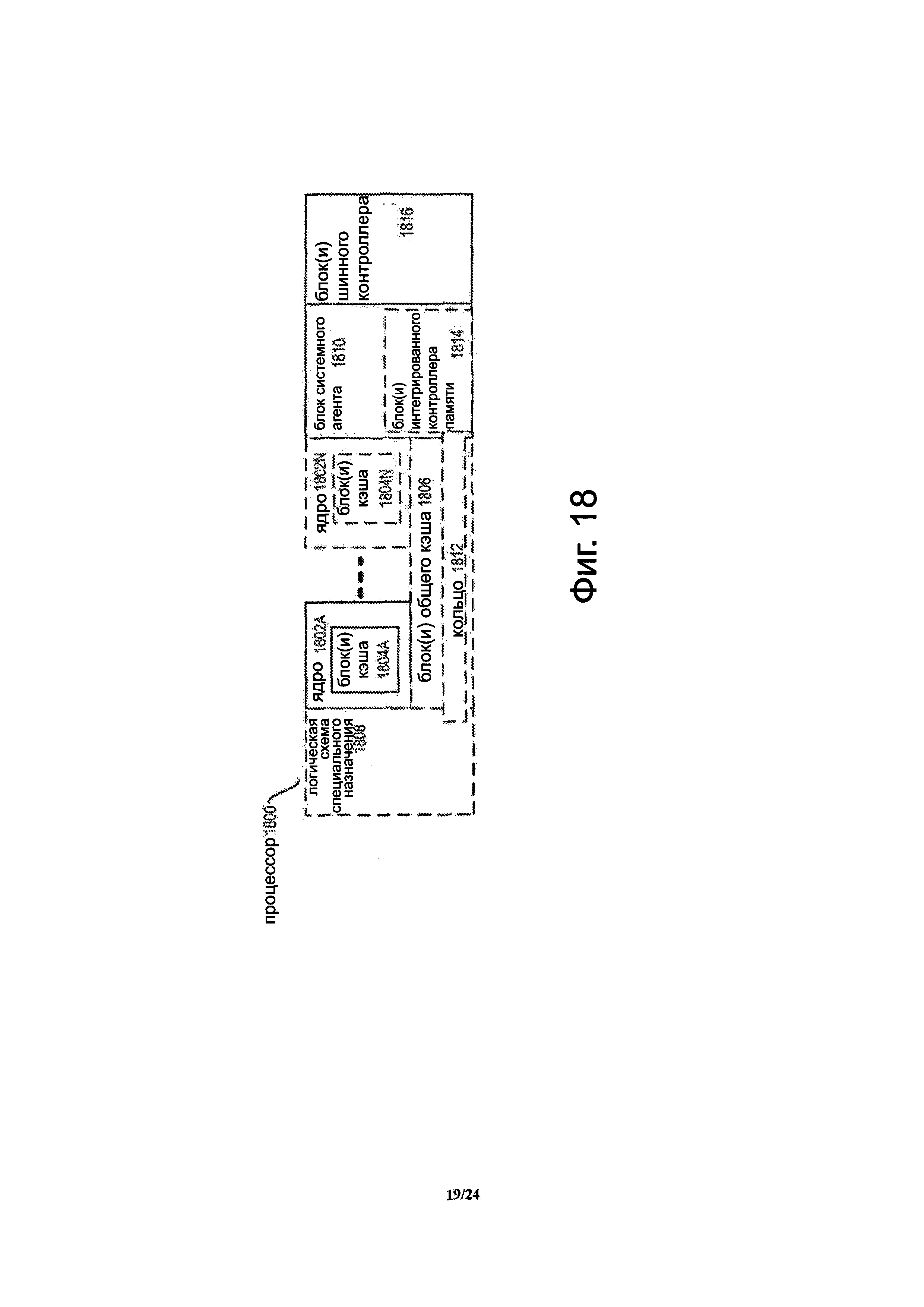

Фиг. 18 представляет собой блок-схему процессора, который может иметь более одного ядра, может иметь интегрированный контроллер памяти и может иметь интегрированный графический блок согласно вариантам осуществления изобретения.

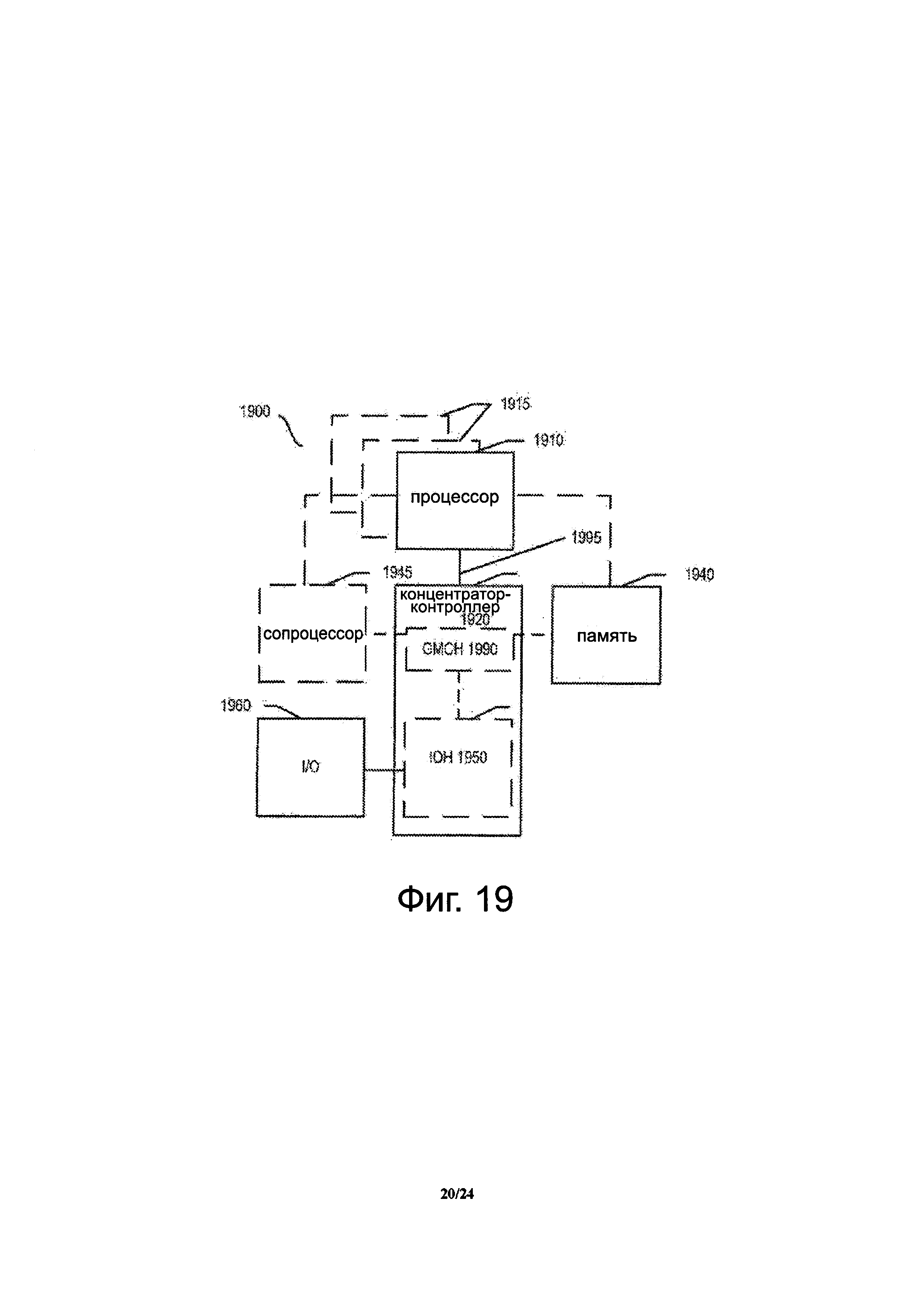

Фиг. 19 показывает блок-схему системы в соответствии с одним вариантом осуществления настоящего изобретения.

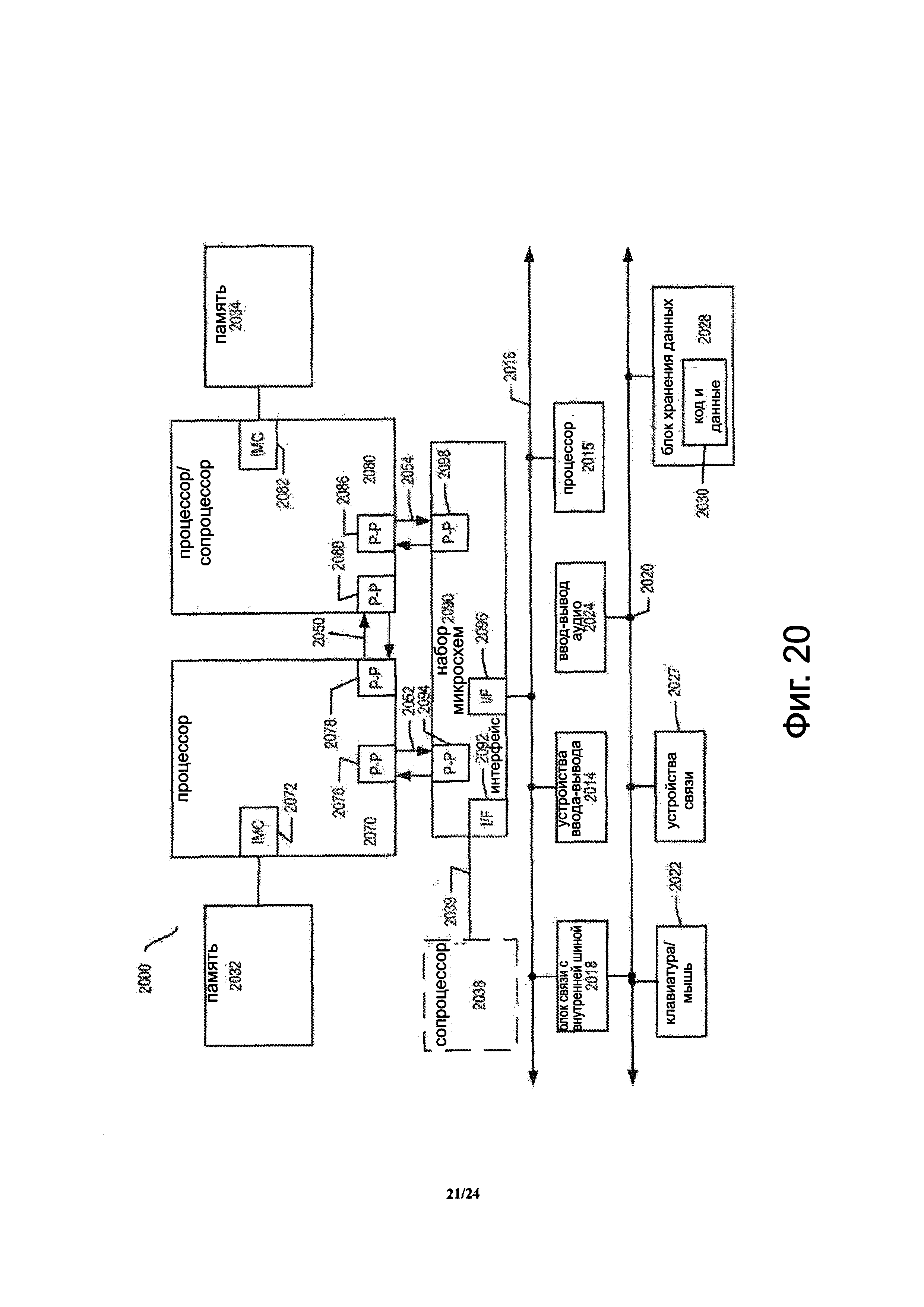

Фиг. 20 показывает блок-схему первого более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

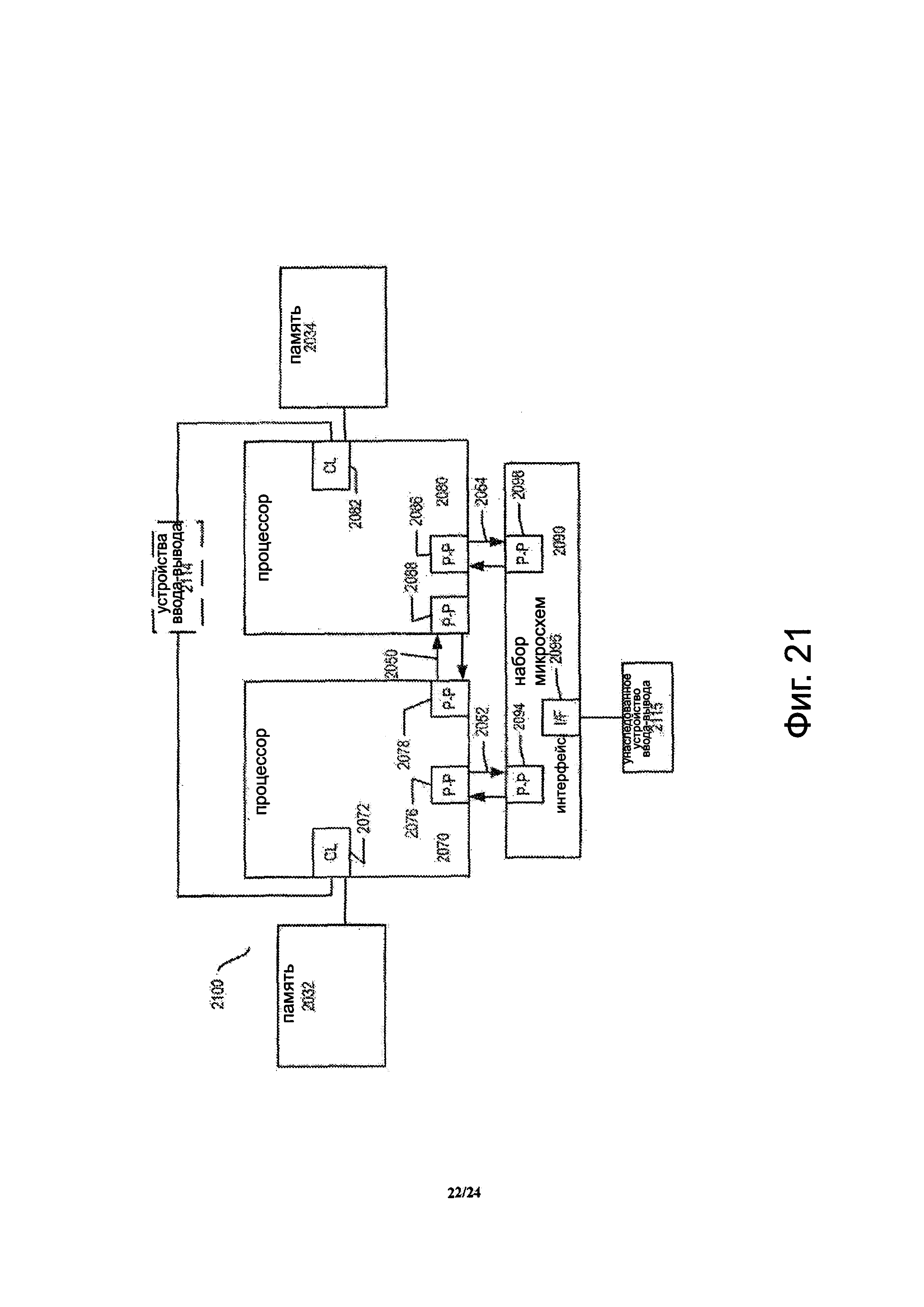

Фиг. 21 показывает блок-схему второго более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

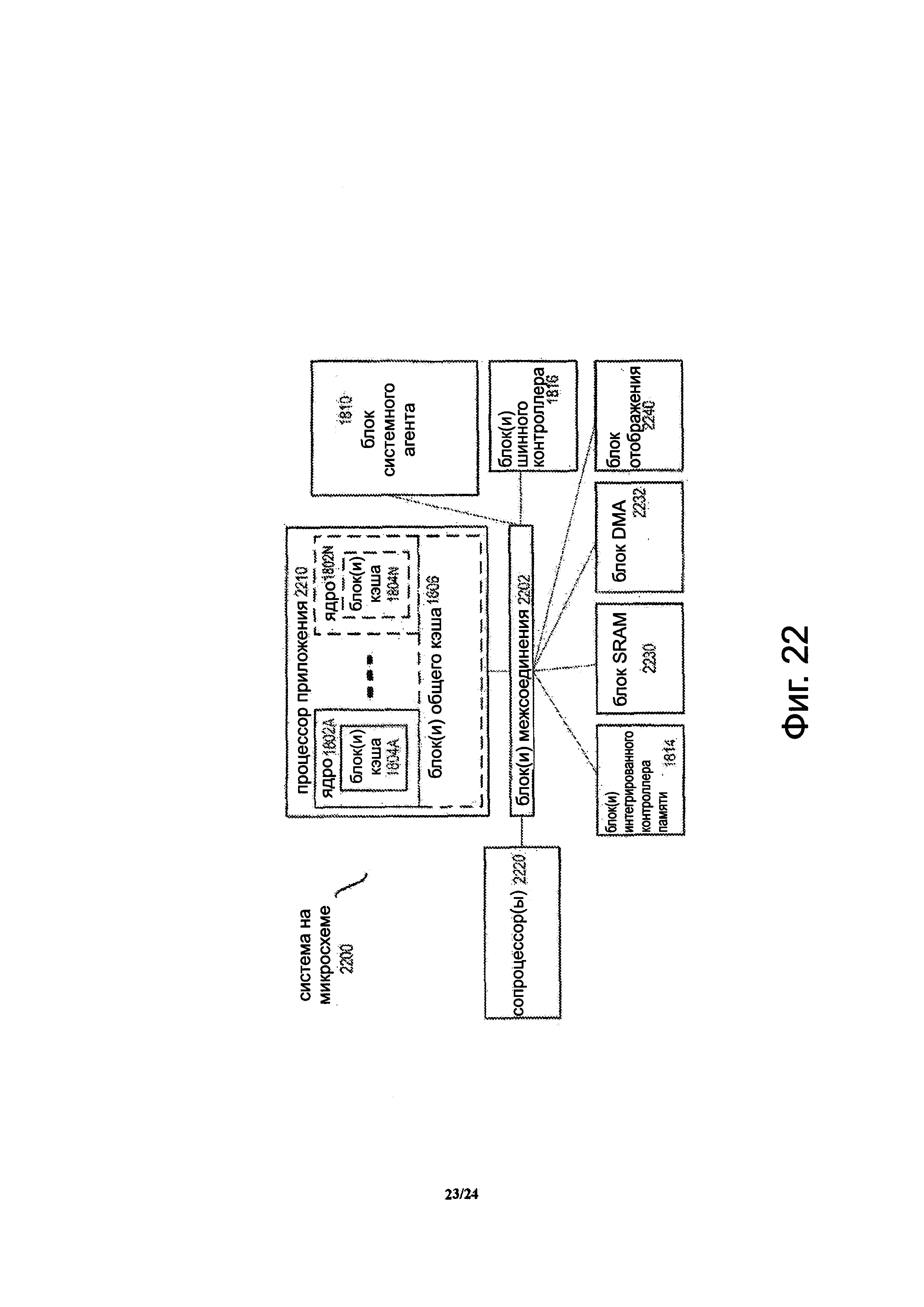

Фиг. 22 показывает блок-схему SoC в соответствии с вариантом осуществления настоящего изобретения.

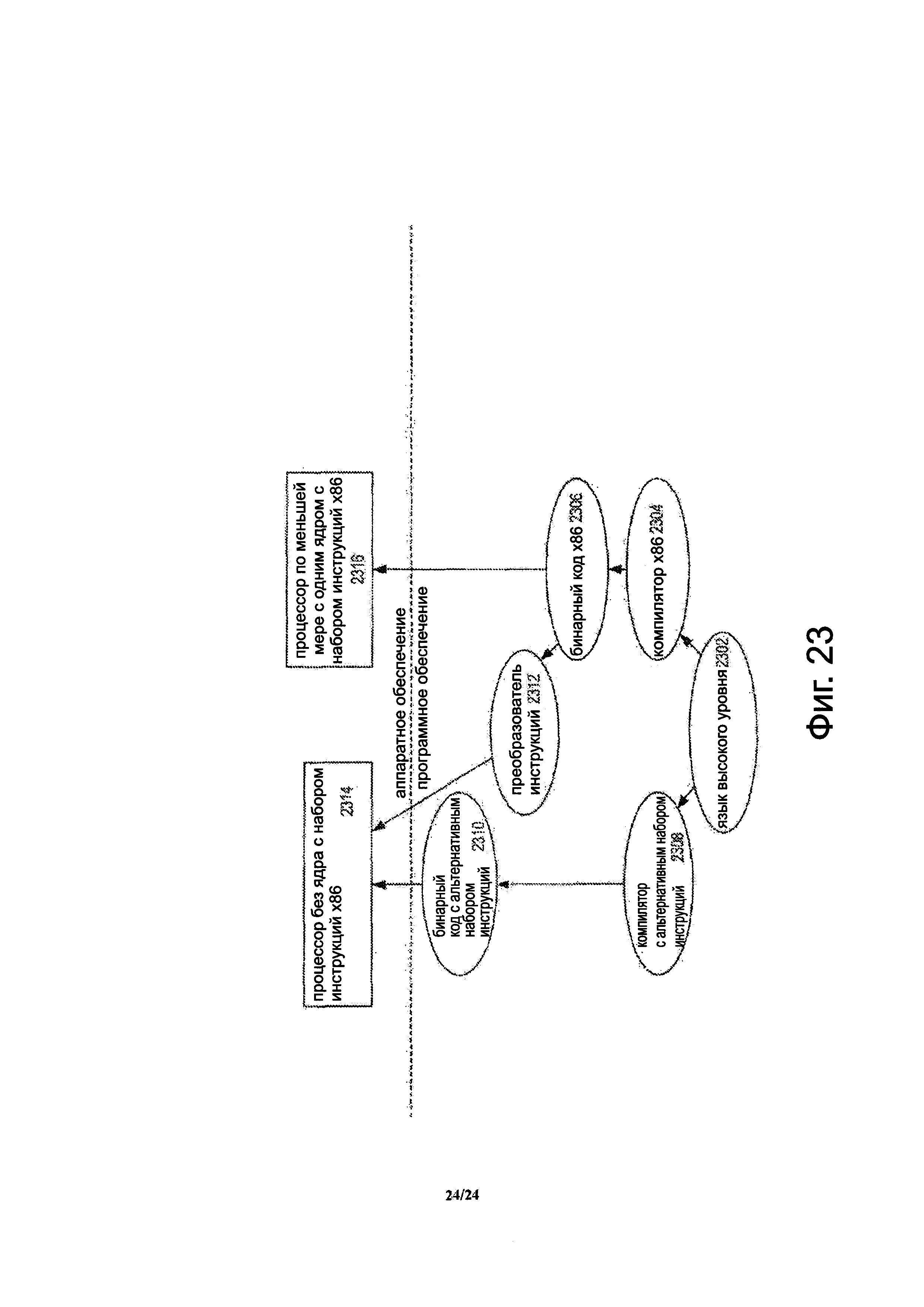

Фиг. 23 представляет собой блок-схему, на которой представлена сравнительная информация относительно использования преобразователя инструкций для преобразования двоичных инструкций в исходном наборе инструкций в двоичные инструкции в целевом наборе инструкций согласно вариантам осуществления изобретения.

Подробное описание вариантов осуществления

Приведенное в настоящем документе описание относится к инструкциям векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции, процессорам для исполнения таких инструкций, способам, выполняемых процессорами при обработке или выполнении таких инструкций, и системам, включающие в себя один или более процессоров для обработки или выполнения таких инструкций. В следующем описании приводятся многочисленные конкретные подробные детали (напр., конкретные инструкции операций, форматы данных, конфигурации процессора, детали микроархитектуры, системные конфигурации, форматы команд, последовательности операций и др.). Впрочем, варианты осуществления могут быть реализованы на практике без этих конкретных деталей. В других случаях известные схемы, структуры и способы не были подробно проиллюстрированы, чтобы не усложнять понимание описания.

Фиг. 1 представляет собой блок-схему варианта осуществления процессора 100, выполненный с возможностью реализовывать или выполнять одну или более инструкций 104 векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции. Процессор соединен с возможной внешней памятью 126 (например, динамическая память с произвольным доступом (DRAM), флэш-память, другие системы памяти и др.). Память 126 показана, как возможная, потому что в некоторых вариантах осуществления процессор 100 описывается без памяти 126.

В некоторых вариантах осуществления процессор может быть процессором общего назначения (например, настольный, ноутбук, планшет, КПК, сотовый телефон как вычислительные устройства). В качестве альтернативы, процессор может быть специализированным процессором. Примеры подходящих специализированных процессоров включают в себя, но не ограничиваясь этим, графические процессоры, сетевые процессоры, коммуникационные процессоры, криптографические процессоры, сопроцессоры и цифровые сигнальные процессоры (DSPs), что представляет собой только несколько примеров. Процессор может быть любым из различных процессоров со сложным набором команд (CISC), различных процессоров с сокращенным набором команд (RISC), различных процессоров со сверх длинным командным словом (VLIW), различных их гибридных вариаций или других типов процессоров целиком.

Процессор включает в себя архитектурно-видимые или архитектурные регистры 110. Термин архитектурные регистры часто используется в данной области техники для обозначения тех регистров, которые видимы для программного обеспечения (например, программатор) и/или регистры, указанные инструкциями набора инструкций для идентификации операндов. Эти архитектурные регистры противопоставляются другим неархитектурным или неархитектурно видимым регистрам в данной микроархитектуре (например, регистры временного запоминания используются инструкциями и др.). Для простоты, эти архитектурные регистры будут часто упоминаться в данном документе просто как регистры. Регистры, как правило, представляют местоположения хранения данных на кристальном процессоре. Регистры могут быть реализованы по-разному в разных микроархитектурах, используя известные технологии, и не ограничиваются каким-либо конкретным типом схемы. Примеры подходящих типов регистров включают в себя, но не ограничиваются этим, выделенные физические регистры, динамически выделенные физические регистры, используя переименование регистров и их комбинации. Иллюстрированные регистры включают в себя набор векторных или упакованных данных регистров 112, каждый выполнен с возможностью хранить векторные или упакованные данные. В некоторых вариантах осуществления регистры могут также возможно включать в себя упакованные данные операции маскировки регистров 118, хотя это не обязательно. В некоторых вариантах осуществления регистры могут также включать в себя регистры 120 общего назначения, хотя это не обязательно.

Процессор имеет набор 102 инструкций. Набор инструкций включает в себя набор инструкций, которые поддерживаются процессором. Инструкции из набора команд представляют собой инструкции языка ассемблера, инструкции машинного уровня, макроинструкции или инструкции для выполнения процессором, в отличие от микроинструкций, микро-ops или инструкции, которые являются результатом декодирования макроинструкций посредством блока декодирования и предоставляются для выполнения в исполнительный блок. Набор инструкций включает в себя одну или более инструкций 104 векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции. Каждая одна или более инструкций векторного индексированного доступа к памяти плюс A/L операции выполнена с возможностью вызывать процессор выполнить операцию векторного индексированного доступа к памяти совместно с векторной A/L операцией.

В некоторых вариантах осуществления одна или более инструкций 104 векторного индексированного доступа к памяти плюс A/L операции может возможно включать в себя одну или более инструкций 106 векторной индексированной загрузки плюс A/L операции плюс операции сохранения (например, одну или более gather-плюс A/L операции плюс scatter-инструкции). Для примера, в некоторых вариантах осуществления инструкция 106 векторной индексированной загрузки плюс A/L операции плюс операции сохранения (например, инструкция gather-плюс A/L операции плюс scatter-инструкция) может быть выполнена с возможностью вызывать процессор собирать элементы данных из ячеек памяти во внешней памяти 126, указанные исходным операндом 114 упакованных индексов памяти, выполнять A/L операции на собранных элементах данных и элементов данных исходного операнда 116 упакованных данных, и разбрасывать полученные элементы данных в ячейках памяти во внешней памяти 126, указанные исходным операндом 114 упакованных индексов памяти.

В некоторых вариантах осуществления, одна или более инструкции 104 векторного индексированного доступа к памяти плюс A/L операции может возможно включать в себя одну или более инструкций 108 векторной индексированной загрузки плюс A/L операции (например, одну или более gather-инструкции плюс A/L операции). Для примера, в некоторых вариантах осуществления, инструкция 108 векторной индексированной загрузки плюс A/L операции (например, gather-инструкция плюс A/L операции) может быть выполнена с возможностью вызывать процессор собирать элементы данных из ячеек памяти во внешней памяти 126, указанными исходным операндом 114 упакованных индексов памяти, выполнять A/L операцию на собранных элементах данных и элементах данных исходного операнда 116 упакованных данных, и сохранение полученных элементов данных, как результат упаковки данных, на местах хранения процессора (например, в одном или более упакованных данных регистров).

Различные типы векторных A/L операций пригодны для инструкций 104. Некоторые примеры подходящих A/L операций включают в себя, но не ограничиваются этим, векторные или упакованные операции сложения, операции вычитания, операции умножения, операции деления, операции умножения-сложения, операции сдвига, операции поворота, операции логики И, операции логики ИЛИ, операции логики НЕТ, операции логики И-НЕТ, операции осреднения, операции максимизации, операции минимизации и операции сравнения, что представляет собой только некоторые из возможных примеров. В различных вариантах осуществления, могут использоваться в любом месте от одной инструкции 104 векторного индексированного доступа к памяти плюс A/L операции до многих таких разных инструкций. Например, может быть несколько или много gather-инструкций плюс операция плюс scatter-инструкций для различных типов A/L операций (например, добавление, умножение, сдвиг и др.) и/или несколько или много gather-инструкций плюс различные типы A/L операций.

В некоторых вариантах осуществления, инструкции 104 могут возможно указывать на упакованные данные операции маскировки операнда в маскированных регистрах 118, хотя это не обязательно. Упакованные данных операции маскировки операндов и упакованные данные операции маскированных регистров будут дополнительно рассмотрены ниже. В некоторых вариантах осуществления, инструкции 104 могут возможно указывать на (например, неявно указывать) регистр 120 общего назначения (например, один, имеющий базовый адрес или другую адресную информацию памяти), хотя это не обязательно. Альтернативно, адресная информация памяти может быть предоставлена иным способом.

Процессор также включает в себя один или несколько исполнительных блоков 124. Исполнительный блок(и) выполнен с возможностью реализовывать или выполнять инструкцию(и) 104 векторного индексированного доступа к памяти плюс A/L операции. Примеры подходящих исполнительных блоков включают в себя, но не ограничены этим, блоки доступа к памяти, исполнительные блоки памяти, блоки сбора данных, блоки разброса данных, арифметические и/или логические блоки (ALUs) и тому подобное, и их комбинации. В некоторых вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять сбор или разброс данных или другую операцию векторного индексированного доступа к памяти) может быть модифицирован, чтобы включать в себя арифметический и/или логический блок или схему. В других вариантах осуществления исполнительный блок памяти (или другие блоки, способные осуществлять сбор или разброс данных или другую операцию векторного индексированного доступа к памяти) могут быть соединены с A/L блоком или схемой. В некоторых вариантах осуществления один или несколько исполнительных блоков 124 могут быть включены в состав подсистемы 122 памяти, которая используется для доступа к внешней памяти 126.

Фиг. 2 представляет собой блок-схему варианта осуществления устройства 200 обработки инструкции. В некоторых вариантах осуществления, устройство 200 обработки инструкции может быть, или может быть включено в состав, процессора 100, показанного на фиг. 1. Признаки и детали, описанные выше, для процессора 100 могут также возможно применяться к устройству 200 обработки инструкции. Альтернативно, устройство 200 обработки инструкции может быть, или может быть включено в состав, аналогичным или другим процессором, чем процессор 100. Кроме того, процессор 100 может включать в себя аналогичное или иное устройство обработки инструкции, чем устройство 200 обработки инструкции.

Устройство 200 обработки инструкции соединено к возможной внешней памяти 226 (например, динамической памяти с произвольным доступом (DRAM), флэш-памяти, другим системам памяти и др.). Например, устройство обработки инструкции и внешняя память могут быть соединены посредством шины или других межсоединений на печатной плате, через набор микросхем или другим образом, известным в данной области техники. Внешняя память отображается как возможная, потому что некоторые варианты осуществления относятся к устройству обработки инструкции без внешней памяти (например, перед установкой процессора в систему).

Устройство 200 обработки инструкции может принимать инструкцию 206 векторной индексированной загрузки плюс A/L операции плюс сохранения. Например, инструкция может быть принята из блока доставки инструкции, очереди команд, памяти и т.д. В некоторых вариантах осуществления, инструкция 206 может представлять собой инструкцию сбора плюс A/L операции плюс разброса. Инструкция 206 может четко определять (например, через один или более битов или поле) или иным образом (например, неявно указывать, указывать косвенно посредством эмуляции сопоставления регистра и др.) указывать исходный операнд 214 упакованных индексов памяти, имеющий множество упакованных индексов памяти. Каждый индекс памяти в исходном операнде упакованных индексов памяти может указывать на соответствующее место в памяти во внешней памяти 226. В некоторых вариантах осуществления индексы памяти могут быть 16-бит, 32-бит или 64-битными индексами памяти, хотя объем изобретения этим не ограничен. В некоторых вариантах осуществления, инструкция 206 может также явно указывать (например, через один или более битов или поле) или иным образом (например, неявно указывать, указывать косвенно через эмуляцию сопоставление регистров и др.) указывать исходный операнд 216 упакованных данных, имеющий множество элементов упакованных данных.

Устройство включает в себя набор регистров 212 упакованных данных. Регистры упакованных данных могут представлять собой архитектурные регистры. Регистры могут быть реализованы по-разному в различных микроархитектурах, используя известные технологии, и не ограничиваются каким-либо конкретным типом схемы. Примеры подходящих типов регистров включают в себя, но не ограничиваются этим, выделенные физические регистры, динамически выделенные физические регистры, используя переименование регистров, и их комбинации. Как показано, в некоторых вариантах осуществления исходный операнд 214 упакованных индексов памяти и исходный операнд 216 упакованных данных могут храниться в регистрах упакованных данных. Например, инструкция 206 может иметь одно или более полей или набор битов, чтобы указать эти регистры упакованных данных в качестве исходных операндов. Альтернативно, в других местах хранения может возможно использоваться для одного или более из этих операндов.

Устройство 200 обработки инструкции включает в себя блок декодирования инструкций или декодер 230. В некоторых вариантах осуществления блок декодирования может располагаться в ядре. Блок декодирования может принимать и декодировать машинные инструкции более высокого уровня или макроинструкции (например, инструкция 206) и выводить одну или более микроинструкций низкого уровня, микрокод точки входа, микроинструкции или другие низкоуровневые инструкции или управляющие сигналы 236, что соответствуют и/или получают из исходной инструкции более высокого уровня. Одна или более низкоуровневых инструкций или управляющие сигналы могут выполнять операцию инструкции более высокого уровня в рамках одной или более низкоуровневой операции (например, уровня схемы или на аппаратном уровне). Блок декодирования может быть реализован с помощью различных механизмов, включающие в себя, но не ограничиваясь этим, памяти микрокода только для чтения (ROMs), справочные таблицы, аппаратные реализации, программируемые логические матрицы (PLAs) и другие механизмы, известные в данной области техники. В других вариантах осуществления, вместо блока декодирования могут быть использованы эмулятор инструкций, переводчик, интерпретатор или другие логические блоки преобразования инструкции (например, реализованные в программном обеспечении, аппаратных средствах, микропрограммном обеспечении или их комбинациях). В еще других вариантах осуществления может быть использована комбинация логических блоков преобразования инструкции (например, модуль эмуляции) и блока декодирования. Некоторые или все логические блоки преобразования инструкций могут потенциально быть размещены вне кристалла от остальной части устройства обработки инструкций, например, на отдельном кристалле и/или памяти.

Обращаясь снова к фиг. 2, один или несколько исполнительных блоков 224 соединены с блоком 230 декодирования, регистрами 212 упакованных данных и с внешней памятью 226. В некоторых вариантах осуществления один или несколько исполнительных блоков могут также возможно быть соединены с регистрами 220 общего назначения, которые могут возможно использоваться для хранения базового адреса и/или другой адресной информации памяти для преобразования индексов памяти в адреса памяти. Альтернативно, адресная информация памяти может быть предоставлена иным образом.

Исполнительный блок выполнен с возможностью, в ответ на и/или как результат инструкции 206 векторной индексированной загрузки плюс A/L операции плюс сохранения (например, в ответ на один или более управляющих сигналов 236 декодированный или иным образом преобразованный из инструкции 206, или в ответ на один или более управляющий сигнал 236 декодированный из одной или более инструкций, используемый для эмуляции инструкция 206) выполнять операцию векторной индексированной загрузки плюс A/L операцию плюс операцию сохранения. Операция загрузки, A/L операция и операция сохранения могут все представлять собой векторные операции. В некоторых вариантах осуществления, операция может включать в себя процессорный сбор данных или иной способ загрузки множества элементов данных из потенциально несмежных ячейках памяти во внешней памяти 226, обозначаемой соответствующими индексами памяти исходного операнда 214 упакованных индексов памяти, выполнения A/L операцию на собранных или загруженных элементах данных и ассоциированных элементах данных исходного операнда 216 упакованных данных, и разброс или иной способ сохранения результирующих элементов данных в соответствующих ячейках памяти во внешней памяти 226, указанные соответствующими индексами памяти исходного операнда 214 упакованных индексов памяти.

В иллюстрируемом примере варианта осуществления, первая ячейка 232 памяти изначально включает в себя элемент А1 данных, вторая ячейка 233 памяти изначально включает в себя элемент А2 данных, третья ячейка 234 памяти изначально включает в себя элемент A3 данных и четвертая ячейка 235 памяти изначально включает в себя элемент А4 данных. Каждая из этих ячеек памяти соответственно может соответствовать с первого по четвертый индексы памяти исходного операнда 214 упакованных индексов памяти. Исходный операнд 216 упакованных данных включает в себя соответствующие элементы B1, В2, В3 и В4 данных. В результате выполнения инструкции, элемент А1 данных в первой ячейке 232 памяти может быть перезаписан с А1 посредством операции (ОР) на В1, элемент А2 данных во второй ячейке 233 памяти может быть перезаписан с А2 OP В2, элемент A3 данных в третьей ячейке 234 памяти может быть перезаписан с A3 ОР В3 и данные А4 элемента в четвертой ячейке 235 памяти может быть перезаписан с А4 OP В4. В этом примерном варианте осуществления, операция (ОР) может представлять собой любую подходящую операцию "вертикального" типа упакованных данных, например, упакованное сложение, упакованное вычитание, упакованное умножение, упакованное деление, упакованное умножение-сложение, упакованный сдвиг (например, сдвиг А1 на В1, сдвиг А2 на В2 и т.д.), упакованный поворот (например, поворот А1 на В1, поворот А2 на В2 и т.д.), упакованная логическая И, упакованная логическая ИЛИ, упакованная логическая НЕ, упакованная логическая И-НЕТ, упакованные усреднения, упакованная максимизация, упакованная минимизация, упакованное сравнение или тому подобное. Хотя в этом примере "вертикальные" операции будут использоваться в операции, выполняемой на паре соответствующих элементов данных (например, элементов данных в соответствующих позициях битов в операндах), и "вертикальный" тип операции не требуется. В других вариантах осуществления, другие виды операций могут быть выполнены, такие как, например, "горизонтальный" тип операции, часть "горизонтальной" операции, часть "вертикальной" операции, операции с участием более чем просто один элемент данных и т.д.

Примеры подходящих исполнительных блоков включают в себя, но не ограничены этим, блоки доступа к памяти, исполнительные блоки памяти, блоки сбора данных, блоки разброса данных, арифметические и/или логические блоки (ALUs) и тому подобное, и их комбинации. В некоторых вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять операцию сбора и/или разброса и/или другие операции векторного индексированного доступа к памяти), может быть изменен, чтобы включать в себя арифметический и/или логический блок или схему. В других вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять операцию сбора и/или разброса и/или другие операции векторного индексированного доступа к памяти) может быть соединен с арифметическим и/или логическим блоком или схемой. Один или несколько исполнительных блоков и/или устройство может содержать специфическую или конкретную логику (например, схему, транзисторы или другие аппаратные средства, потенциально объединенные с программным обеспечением и/или аппаратно-программным обеспечением), выполненную с возможностью выполнять и/или обрабатывать инструкцию 206. В некоторых вариантах осуществления один или несколько исполнительных блоков могут включать в себя, по меньшей мере, некоторые транзисторы, интегральную схему, часть интегральной схемы или другую схему или оборудование.

В некоторых вариантах осуществления, один или несколько исполнительных блоков 224 могут быть включены в состав подсистемы 222 памяти, которая используется для доступа к внешней памяти 226, хотя это не обязательно. Как будет рассмотрено дополнительно ниже, как правило, чем ближе один или несколько исполнительных блоков 224 к внешней памяти 226, тем выше эффективность. Например, это может быть отчасти из-за не необходимости хранить данные на одном или более высоком уровне кэша и/или нет необходимости передавать данные по межсоединению всем, вплоть до самого высокого уровня кэша и/или в ядро.

С целью упрощения описания, была проиллюстрирована простая структура устройства 200 обработки инструкции, хотя устройство обработки инструкции может возможно включать в себя один или более других компонентов. Примеры таких обычных компонентов включают в себя, но не ограничиваются ими, блок выборки инструкций, блок планирования инструкции, блок предсказания ветви, кэш данных и инструкции, буферы предыстории преобразования данных (TLB), буферы предварительной выборки, очереди микроинструкции, устройства, задающие последовательность микроинструкций, блоки шинного интерфейса, блок удаления/подтверждения, блок переименования регистра и другие компоненты, обычно используемые в процессорах. Кроме того, варианты осуществления могут иметь несколько ядер, логические процессоры или блок механизма исполнения, имеющие тот же или другой набор инструкций и/или ISA. Есть множество различных комбинаций и конфигураций таких компонентов в процессорах и варианты осуществления не ограничиваются какой-либо конкретной такой комбинацией или конфигурацией.

В некоторых вариантах осуществления, операция может быть выполнена посредством исполнительного блока, находящегося за пределами ядер (например, с помощью исполнительного блока, расположенного с и/или непосредственно последнего уровня кэша, предпоследнего уровня кэша или одного из последних уровней кэша. В некоторых вариантах осуществления, операция может быть выполнена с помощью исполнительного блока на данных, поставленных или полученных из последнего уровня кэша, предпоследнего уровня кэша или одного из последних уровней кэша. В некоторых вариантах осуществления один или несколько исполнительных блоков 224 могут быть логически развернуты на том же уровне иерархии памяти, как последний уровень кэшпамяти (или один из самых низких уровней кэш-памяти), в противоположность логическому развертыванию одного или нескольких исполнительных блоков 224 на высшем уровне кэша (или один из самых высоких уровней кэша). Обычно, чем выше уровень кэша между высоким уровнем кэша и уровнем иерархии памяти, на котором работает один или несколько исполнительных блоков, тем выше эффективность. В некоторых вариантах осуществления, операция может быть выполнена над данными, которые обходят все или, по меньшей мере, один или более высоких уровней кэша, что выше, чем кэш, из которого данные предоставляются (например, последний уровень кэша). В таких вариантах осуществления, собранные или иным образом загруженные данные, не должны передаваться ни в какой-либо более высокий уровень кэша и/или в ядро, до обработки и затем разбросаны или иным образом сохранены обратно в памяти. Целесообразно, избегая необходимости хранить эти данные на более высоких уровнях кэша, способствует освобождению пространства на более высоких уровнях кэша. Это освобожденное пространство может использоваться для хранения других данных, которые могут помочь улучшить производительность. Более того, в некоторых вариантах осуществления, операция может быть выполнена на данных, содержащихся в регистрах временного запоминания, в отличие архитектурных регистров. Это может помочь освободить архитектурные регистры так, чтобы они были доступны для использования другими инструкциями. Это может также помочь улучшить производительность (например, помогая уменьшить подкачку данных в регистрах и др.). Более того, может быть также уменьшена полоса пропускания соединения и/или других ресурсов, которые иным образом были бы необходимы для передачи данных на самый высокий или более высокий уровень кэша и/или в ядро. Такая ширина полосы пропускания соединения и/или иные ресурсы могут быть использованы для других целей, которые также могут помочь повысить производительность.

Фиг. 3 представляет собой блок-схему, иллюстрирующую один вариант осуществления расположения исполнительного блока 324 в процессоре 300. Процессор включает в себя один или более ядер 350. На чертеже, процессор включает в себя первое ядро 350-1, возможно N-e ядро 350-N, где N может представлять собой любое подходящее количества ядер. Первое ядро включает в себя блок 330 декодирования, который может быть аналогичен блокам декодирования, описанными в данном документе, и может декодировать инструкцию векторного индексированного доступа к памяти плюс A/L операции. Первое ядро также включает в себя исполнительный блок 351. Ядро также включает в себя архитектурные регистры 310, которые могут быть указаны инструкциями, выполненными первым ядром. Первое ядро дополнительно включает в себя кэш 352 первого уровня (L1) и возможно кэш 353 второго уровня (L2). Энное ядро может возможно быть схожим или таким же, как первой ядро, хотя это не обязательно. Процессор также включает в себя кэш 354 последнего уровня (LLC), соединенный с ядрами. Процессор также включает в себя блок 355 памяти, соединенный с LLC и ядрами. Блок памяти соединен с внешней памятью 326.

В некоторых вариантах осуществления блок памяти может включать в себя исполнительный блок, используемый для выполнения или реализации инструкции векторного индексированного доступа к памяти плюс A/L операции. Исполнительный блок включает в себя блок 356 доступа к памяти, который выполнен с возможностью выполнять операцию векторного индексированного доступа к памяти (например, операцию сбора и/или операцию разброса). Исполнительный блок также включает в себя блок 357 A/L, соединенный с блоком доступа к памяти. Блок A/L может быть выполнен с возможностью выполнить A/L операцию на данных, к которым разрешен доступ (например, загруженные векторные данные с помощью индексов). Блок 356 доступа к памяти и блок 357 A/L могут взаимодействовать или работать вместе, чтобы выполнять вариант реализации инструкции векторного индексированного доступа к памяти плюс A/L операции. В некоторых вариантах осуществления исполнительный блок 324 может выполнять операции над данными, загруженными из внешней памяти 326 перед загрузкой в LLC, будучи загруженными в LLC, или на данных, полученных из LLC после загрузки в LLC. В некоторых вариантах осуществления исполнительный блок 324 может выполнять операции над данными, которые отсутствуют в ядре 350, L1 кэш 352 или кэш L2 353. В некоторых вариантах осуществления исполнительный блок может включать в себя регистры 358 временного запоминания для содействия в выполнении этих инструкций. Например, регистры временного запоминания могут использоваться для хранения загруженных данных и/или промежуточных или временных данных, сгенерированных при выполнении инструкции. Использование таких регистров временного запоминания помогает избежать необходимости занимать архитектурные регистры 310.

Фиг. 4 представляет собой блок-схему варианта осуществления способа 460 обработки варианта осуществления инструкции векторной индексированной загрузки плюс A/L операции плюс операции сохранения. В различных вариантах осуществления способ может быть выполнен процессором общего назначения, процессором специального назначения или другим устройством обработки инструкций или цифровым логическим устройством. В некоторых вариантах осуществления, операции и/или способ, показанный на фиг. 4, могут быть выполнены посредством и/или в любых устройствах, показанных на фиг. 1-3. Компоненты, признаки и конкретные возможные детали, описанные в настоящем документе для устройства, показанного на фиг. 1-3, также возможно применяются к операциям и/или способу, показанному на фиг. 4. Альтернативно, операции и/или способ на фиг. 4 могут быть выполнены посредством и/или в пределах аналогичного или другого процессора или устройства. Кроме того, устройство, показанное на любом из фиг. 1-3, может выполнять такие же операции и/или способы, схожие или отличающиеся от фиг. 4.

Способ включает в себя прием инструкции векторной индексированной загрузки плюс A/L операции плюс сохранение, на этапе 461. В различных аспектах, инструкция может быть принята посредством процессора, устройством обработки инструкции или их частью (например, блок выборки инструкции, блок декодирования, модуль преобразования инструкции и др.). В различных аспектах, инструкция может быть принята из внешнего источника (например, из DRAM, диска, межсоединения и т.д.) или из внутреннего источника (например, из кэша команд, из блока выборки и др.). В некоторых вариантах осуществления, инструкция может указывать или иным образом указывать исходный операнд упакованных индексов памяти, который должен иметь множество упакованных индексов памяти. В некоторых вариантах осуществления, инструкция может указать или иным образом указать исходный операнд упакованных данных, который должен иметь множество упакованных элементов данных.

Способ включает в себя выполнение инструкции векторной индексированной загрузки плюс A/L операции плюс сохранения, на этапе 462. В некоторых вариантах осуществления это может включать в себя загрузку множества элементов данных из ячеек памяти, соответствующих множеству упакованных индексов памяти, на этапе 463, выполнение A/L операции на множестве упакованных элементов данных исходного операнда упакованных данных и множества загруженных элементов данных, на этапе 464, и хранить множество результирующих элементов данных в ячейках памяти, соответствующих множеству упакованных индексов памяти, на этапе 465. Те же индексы, используемые для операции загрузки, могут также использоваться для операции сохранения.

Иллюстрированный способ включает в себя архитектурно видимые операции (например, видимое программное обеспечение и/или программатор). В других вариантах осуществления способ может возможно включать одну или более микроархитектурные операции. Например, инструкция может быть извлечена, расшифрована, запланирована с изменением последовательности выполнения команд, исходные операнды могут быть доступны, исполнительный блок может быть выполнен с возможностью выполнять микроархитектурные операции для реализации операций инструкции (например, в упакованные данные могут быть сохранены из кэша в регистре временного хранения, упакованные данные могут быть получены из регистра временного хранения, результирующие упакованные данные могут быть сохранены из регистра временного хранения обратно в кэше или памяти и др.) и т.д.

Фиг. 5 представляет блок-схему, иллюстрирующую вариант осуществления операции 566 векторной индексированной загрузки плюс A/L операции плюс сохранения, которая может выполняться в ответ на вариант осуществления инструкции векторной индексированной загрузки плюс A/L операции плюс сохранение. В некоторых вариантах осуществления инструкция может представлять собой инструкцию сбора плюс AIL операции плюс операции разброса.

Инструкция может указать или иным образом указать на исходный операнд 514 упакованных индексов памяти, имеющий множество упакованных индексов памяти. В иллюстрируемом варианте осуществления исходный операнд упакованных индексов памяти является 512-бит шириной и содержит шестнадцать 32-разрядных индексов памяти, хотя объем изобретения не ограничен. В иллюстрируемом примере значения индексов памяти равны, от наименее значимой позиции (слева) к самой значимой позиции (справа), 134 бит [31:0], 231 бит [63:32], 20 бит [95:64] и 186 бит [511:480]. Очевидно, что эти значения являются только иллюстративными примерами. Главное, что есть значения, которые указывают или соответствуют различным ячейкам памяти. Альтернативно, другие размеры индексов памяти, которые возможно могут быть использованы, такие как, например, 16-битные индексы памяти, 64-разрядные индексы памяти или другие размерности индексов памяти известны в данной области техники. Кроме того, в других вариантах осуществления исходный операнд упакованных индексов памяти может иметь любую другую приемлемую ширину, кроме 512-бит, такую как, например, 64-бит, 128-бит, 256-бит или 1024 бит.

Инструкция может также указывать или иным образом указать на исходный операнд 516 упакованных данных, имеющее множество упакованных элементов данных. В показанном варианте исходный операнд упакованных данных является также 512-бит шириной и содержит шестнадцать 32-разрядных элементов данных, хотя объем изобретения этим не ограничен. В иллюстрируемом примере, значения данных элементов, от наименее значимой позиции (слева) до самой значимой позиции (справа), В1 бит [31:0], В2 бит [63:32], ВЗ бит [95:64] до В16 бит [511:480]. В качестве альтернативы, другие размеры элементов данных могут возможно использоваться, такие как, например, 8-разрядные элементы данных, 16-разрядные элементы данных, 64-разрядные элементы данных или другие размеры элементов данных, известные в данной области техники. Кроме того, в других вариантах осуществления исходный операнд упакованных данных может иметь любую другую ширину, кроме 512-бит, такую как, например, 64-бит, 128-бит, 256-бит или 1024 бита. Отсутствует требование к битовой ширине индексов памяти, которые должны совпадать с битовой шириной элементов данных. Часто, число элементов данных будет таким же, как количество индексов памяти, хотя этого не требуется в зависимости от конкретного типа операции.

Операция векторной индексированной загрузки, A/L операции и операции сохранения может быть выполнена в ответ на и/или в результате реализации маскированной инструкции. Операция может собрать или иным образом загрузить элементы данных из ячейки памяти в память, в соответствии с указанием соответствующих индексов памяти исходного операнда упакованных индексов памяти. Каждый индекс памяти может указывать соответствующую ячейку памяти и/или элемент данных, хранящийся в ней. Например, в показанном варианте осуществления, индекс 134 памяти может указывать на ячейку памяти, в которой хранится элемента А1 данных, индекс 231 памяти может указывать на ячейку памяти, в которой хранится элемент А2 данных, индекс 20 памяти может указывать на ячейку памяти, в которой хранится элемент A3 данных и так далее вплоть до индекса 186 памяти, указывающий на ячейку памяти, в которой хранится элемент А16 данных. A/L операция (ОР) может быть выполнена на собранных или иным образом загруженных элементах данных и элементах данных исходного операнда 516 упакованных данных. Полученные элементы данных (т.е. те, которые возникают в результате совершения операции) могут быть разбросаны или иным образом сохранены обратно в соответствующие ячейки памяти, указанные индексами памяти исходного операнда упакованных индексов памяти. В некоторых вариантах осуществления, в зависимости от конкретной инструкции операции, результирующие элементы данных могут быть такого же размера, что и элементы данных исходного операнда упакованных данных (например, 32-разрядные элементы данных). Альтернативно, результирующие элементы данных могут быть больше или меньше, чем элементы данных исходного операнда упакованных данных, такие как, например, 8-бит, 16-бит, 64-бит, и т.д.

В показанном варианте осуществления, для простоты описания, выполняется вертикальный тип операции для генерирования первого результирующего элемента данных, равного A1 OP В1, второго результирующего элемента данных, равного А2 ОР В2, третьего результирующего элемента данных, равного A3 ОР В3 и четвертого результирующего элемента данных, равного А16 ОР В16. Хотя термин "равный" был использован, очевидно, что насыщение может возможно быть выполнено, чтобы насытить значения до максимального или минимального значения. Любая из ранее упомянутых вертикальных операций, описанных в данном документе, может быть использована (например, упакованное сложение, упакованная разность, упакованное произведение, упакованный сдвиг, упакованный поворот, различные типы логических операций (например, И, ИЛИ, НЕ, И-НЕ и др.). Например, в случае операции упакованного сложения, результирующие элементы данных могут включать в себя A1+B1, А2+В2, А3+В3 до А16+В16. В качестве другого примера, в случае операции упакованного сдвига, результирующие элементы данных могут включать в себя А1 со сдвигом на шаг сдвига в B1, А2 сдвинут на шаг сдвига в В2 и так далее. В других вариантах осуществления другие виды операций, такие как, например, операции горизонтального типа, операции части вертикального типа и горизонтального типа, операции с участием более чем двух элементов данных или тому подобное, может быть возможно выполнено. Как показано на чертеже, значение А1 в ячейке памяти, соответствующее индексу 134 памяти, может быть перезаписано значением A1 OP В1, значение А2 в ячейке памяти, соответствующее индексу 231 памяти, может быть перезаписано со значением А2 OP В2, значение A3 в ячейке памяти, соответствующее индексу 20 памяти, может быть перезаписано значением A3 ОР В3 и значение А16 в ячейке памяти, соответствующее индексу 186 памяти, может быть перезаписано со значением А16 ОР В16.

Фиг. 6 представляет собой блок-схему, иллюстрирующую вариант выполнения операции 668 векторной маскированной индексированной загрузки плюс A/L операции плюс операции сохранения, которая может выполняться в ответ на реализацию инструкции маскированной векторной индексированной загрузки плюс A/L операции плюс сохранение. В некоторых вариантах осуществления инструкция может представлять собой инструкцию маскированной операции сбора плюс A/L операции плюс операции разброса. Маскированная операция и маскированная инструкция, показанные на фиг. 6, имеют определенные сходства с незамаскированной операцией и незамаскированной инструкцией, показанной на фиг. 5. Чтобы не усложнять описание, различные и/или дополнительные характеристики для маскированной операции/инструкции на фиг. 6 будут в первую очередь описаны без повторения всех похожих или общих характеристик по отношению к незамаскированной операции/инструкции, показанной на фиг. 5. Однако, следует отметить, что ранее описанные характеристики немаскированной операции/инструкции, показанные на фиг. 5, также возможно применимы к фиг. 6, если не оговорено иначе или иным образом является очевидным.

Инструкция может указать или иным образом указать на исходный операнд 614 упакованных индексов памяти, имеющий множество упакованные индексов памяти. Инструкция может также указывать или иным образом указать на исходный операнд 616 упакованных данных, имеющий множество упакованных элементов данных. Каждый из них может быть схожим или таким же, как те ранее описано на фиг. 5, и может иметь одинаковые вариации и альтернативы.

В некоторых вариантах осуществления, маскированная инструкция также может указывать или иным образом указывать на исходный операнд 618 замаскированной операции упакованных данных. Исходный операнд замаскированной операции упакованных данных может представлять собой предикативный операнд или операндом условного управления, который выполнен с возможностью маскировать, предсказывать или условно управлять или или нет соответствующий набор операций, ассоциированный с инструкцией, которая должна быть выполнена, и/или сохранять соответствующий результат. Операция маскировки упакованных данных может также упоминаться здесь как операция маскировки, предикат маскировки или просто маскировка. В некоторых вариантах осуществления, маскировка или предикация могут быть на каждом уровне детализации элемента данных так, что операции на различных элементах данных могут быть предсказаны или условно управляемы отдельно и/или независимо от других. Маскировка может включать в себя множество маскированных элементов, предикат элементов или условно управляемые элементы. В одном аспекте, маскированные элементы могут быть включены в состав взаимно однозначных отображений с соответствующими исходными элементам данных и/или результирующими элементами данных. В некоторых вариантах осуществления, каждый маскированный элемент может быть одним битом маски. Значение каждого отдельного бита маски может управлять или нет соответствующим набором операций, ассоциированным с инструкцией, которая должна выполняться на соответствующих элементах данных, и/или нет соответствующий результат будет сохранен в целевой ячейке памяти. Согласно одному возможному правилу, каждый бит маски может иметь первое значение (например, может быть установлен в двоичную 1), чтобы позволить соответствующему набору операций быть выполненному, и разрешить соответствующему результирующему элементу данных хранится в соответствующей целевой ячейке памяти, или может иметь второе значение (например, может быть сброшено в двоичный 0), чтобы не позволить соответствующему набору операций быть выполненному и/или не разрешить соответствующему результирующему элементу данных сохранится в соответствующей ячейке памяти.

Как показано, в случае исходного операнда 614 упакованных индексов памяти, имеющий 512-битную ширину, и имеющий шестнадцать 32-разрядных индексов памяти, исходный операнд 618 маскировочной операции упакованных данных может иметь 16-битную ширину, в которой каждый бит представляет собой бит маски. Каждый бит маски может соответствовать индексу памяти в соответствующей позиции и/или может соответствовать результирующему элементу данных, который должен быть сохранен в соответствующей ячейке памяти, на которую указывает индекс памяти. На чертеже соответствующие позиции вертикально выровнены относительно друг друга. В других вариантах осуществления, когда есть более или менее результирующих элементов данных, может быть больше или меньше битов маски. Например, маска может иметь ширину в битах равную количеству индексов памяти в исходных упакованных индексах 614 памяти (например, четыре, восемь, тридцать два, шестьдесят четыре и т.д.). В иллюстрируемом примере, биты маски от младшего значащего бита (слева) к старшему биту (справа) являются 1, 0, 1, … 0. Это лишь один показательный пример. Согласно иллюстрированному правилу, значение бита маски двоичного 0 представляет собой отсутствие маскировки результирующего элемента и/или набора операций, которые не должны выполняться, в то время как значение бита маски двоичной 1 указывает на немаскированный результирующий элемент и/или набор операций, которые будут выполняться. Для каждого незамаскированного элемента выполняется соответствующая операция векторной индексированной загрузки, A/L операция и операция сохранения. В отличие от них, для каждого маскируемого элемента, соответствующая операция векторной индексированной загрузки, A/L операция и операция сохранения не выполняется, или если они выполняются, ассоциированный результат не должен храниться в ассоциированной ячейки памяти. Часто, есть преимущества, которые заключаются в том, что даже при неисполнении операции маскировки, такой как, например, возможность избежать ошибок (например, ошибки страниц) при выполнении операции, они не должны выполняться.

Маскированная операция векторной индексированной загрузки, A/L операция и операция сохранения могут быть выполнены в ответ на и/или в результате реализации маскированной инструкции. В некоторых вариантах осуществления набор операций (например, операции загрузки, A/L и сохранения) могут или не могут быть выполнены на соответствующих элементах данных с учетом, которые подвергнуты условному управлению битов маски. В некоторых вариантах осуществления элементы данных могут быть выборочно собраны или иным образом загружены из соответствующих ячеек памяти, указанные соответствующими индексами памяти только тогда, когда соответствующие биты маски не замаскированы (например, установлена двоичная 1). Элементы данных, соответствующие битам маски маскированной операции упакованных данных операции (например, сброшенные до двоичного 0), не могут быть загружены. Затем, A/L операция (ОР) может быть выборочно выполнена только на нагруженных элементах данных и соответствующих элементах данных исходного операнда 616 упакованных данных. Затем, полученные элементы данных могут быть селективно разбросаны или иным образом сохранены обратно в соответствующие ячейки памяти, указанные индексами памяти, только тогда, когда соответствующие биты маски не замаскированы (например, установка двоичной 1).

В иллюстрируемом примере, поскольку биты маски на битовых позициях [0] и [2] исходной маскированной операции упакованных данных не маскируются (например, значение двоичной 1), то значение А1 в ячейке памяти, соответствующей индексу 134 памяти, может быть перезаписано значением A1 OP В1, и значение A3 в ячейке памяти, соответствующей индексу 20 памяти, может быть перезаписано значением A3 ОР В3. В показанном варианте осуществления, для простоты описания, выполняется только операция вертикального типа. Любая из ранее описанных операций вертикального типа является подходящей. В других вариантах осуществления, операции горизонтального типа, часть операций вертикального типа часть операций горизонтального типа, операции с участием более чем двух элементов данных или тому подобное, может быть выполнена вместо этого.

В иллюстрируемом примере, поскольку биты маски на битовых позициях [1] и [15] маски скрыты (например, сброс на двоичный 0), то результаты набора операций, ассоциированные с инструкцией, не хранятся в ячейках памяти, обозначенные соответствующими индексами памяти. Скорее, в некоторых случаях, эти ячейки памяти могут удерживать или сохранять их прежние значения до инструкции (например, не могут быть изменены посредством инструкции). Как показано на чертеже, ячейка памяти, ассоциированная с индексом 231 памяти, может сохранить начальное значение А1, и ячейка памяти, ассоциированная с индексом 186 памяти, может сохранить первоначальное значение А16. Альтернативно, нули или другие заданные значения могут храниться в маскированных ячейках памяти.

Фиг. 7 представляет собой блок-схему, иллюстрирующую вариант осуществления операции 770 векторной индексированной загрузки плюс A/L операции, которые могут выполняться в ответ на реализацию инструкции векторной индексированной загрузки плюс A/L операции. В некоторых вариантах осуществления инструкции могут представлять собой инструкцию сбора плюс A/L операции. Операция и инструкция, показанные на фиг. 7, имеют определенные сходства с операцией и инструкцией, показной на фиг. 5. Чтобы избежать усложнений описания, различные и/или дополнительные характеристики операции/инструкции на фиг. 7 будет описаны без повторения всех похожих или общих характеристик относительно операции/инструкции на фиг. 5. Однако, следует отметить, что описанные ранее характеристики операции/инструкции на фиг. 5 также возможно применяются к фиг. 7, если не указано иное или очевидное.

Инструкция может указать или иным образом указать исходный операнд 714 упакованных индексов памяти, имеющий множество упакованных индексов памяти. Инструкция может также указывать или иным образом указать исходный операнд 716 упакованных данных, имеющий множество упакованных элементов данных. Каждый из них может быть схожим или таким же, как ранее описанные на фиг. 5, и может иметь одинаковые вариации и альтернативы.

Векторная индексированная загрузка плюс A/L операция могут быть выполнены в ответ на и/или в результате реализации инструкции. Операция может собирать или иным образом загружать элементы данных из ячеек памяти, указанных соответствующими индексами памяти исходного операнда 714 упакованных индексов памяти. Например, в иллюстрируемом варианте осуществления элемент А1 данных может быть собран из ячейки памяти, указанной индексом 134 памяти, элемент А2 данных может быть собран из ячейки памяти, указанной индексом 231 памяти, элемент A3 данных может быть собран из ячейки памяти, указанной индексом 20 памяти и так далее до элемента А16 данных, собранного из ячейки памяти, указанной индексом 186 памяти. Затем, A/L операция (ОР) может быть выполнена на собранных или иным образом загруженных элементах данных и соответствующих элементах данных исходного операнда упакованных данных. Это может генерировать множество результирующих элементов данных.

В отличие от операции/инструкции на фиг. 5, в этом варианте осуществления результирующие элементы данных не могут быть разбросаны или иным образом сохранены обратно в памяти 726. Скорее, полученные элементы данных могут храниться в результирующем операнде упакованных данных в области хранения, которая находится на кристалле или в процессоре. Например, в некоторых вариантах осуществления, результирующие элементы данных могут храниться в результирующих упакованных данных в регистре упакованных данных процессора. В некоторых вариантах осуществления, инструкция может иметь поле или набор битов для явного указания регистра упакованных данных. Альтернативно, регистр упакованных данных может возможно быть неявно указан инструкцией. В других вариантах осуществления, регистры для временного хранения могут использоваться для хранения результирующих упакованных данных.

В показанном варианте осуществления, для простоты описания, выполняется операция вертикального типа для генерирования первого результирующего элемента данных, равного A1 OP В1, второго результирующего элемента данных, равного А2 ОР В2, третьего результирующего элемента данных, равного A3 ОР В3 и шестнадцатого результирующего элемента данных, равного А16 ОР В16. Любая из ранее упомянутых операций вертикального типа, описанная в данном документе, может использоваться. В других вариантах осуществления другие виды операций, такие как, например, операции горизонтального типа, часть операции вертикального типа и часть операции горизонтального типа, операции с участием более чем двух элементов данных или тому подобное могут возможно выполняться. Результирующие элементы данных хранятся в результирующем операнде 772 упакованных данных (например, в регистре упакованных данных). Как показано, первый результирующий элемент данных хранится в битах [31:0], второй результирующий элемент данных хранится в битах [63:32], третий результирующий элемент данных хранится в битах [95:64] и шестнадцатый результирующий элемент данных хранится в битах [511:480]. В других вариантах осуществления, в зависимости от конкретной операции инструкции, результирующий элемент данных может быть больше или меньше элементов данных исходного операнда упакованных данных, такие как, например, 8-бит, 16-бит, 64-бит и т.д.

Фиг. 7 показывает вариант осуществления немаскированной операции/инструкции. Другие варианты осуществления могут включать в себя соответствующие маскируемые операции/инструкции. Маски и маскирование может быть выполнено, по существу, как описано выше со ссылкой на фиг. 6, за исключением того, что результаты будут сохранены или не сохранены в результирующих упакованных данных 772 вместо памяти 726. Характеристики маски и маскировки, ранее описанные со ссылкой на фиг. 6, могут также применяться к данной инструкции/операции.

В различных вариантах осуществления операции, описанные на любом из чертежей с 5 по 7, могут быть выполнены устройством, описанном на любом из чертежей с 1 по 3. Компоненты, признаки и конкретные возможные детали, описанные в настоящем документе для устройства, описанного на любом чертеже с 1 по 3, могут также возможно применяться к операциям на любом из чертежей с 5 по 7. Альтернативно, операции на любом чертеже с 5 по 7 могут быть выполнены посредством и/или в пределах аналогичного или иного устройства, чем те, которые описаны на чертежах с 1 по 3. Кроме того, устройство, описанное со ссылкой на любой чертеж с 1 по 3, может выполнять операции, которые аналогичны или отличаются от описанных на чертежах с 5 по 7. Операции, описанные на любом чертеже с 5 по 7, могут также выполняться как часть способа, описанного на фиг. 4. Альтернативно, способ на фиг. 4 может выполнять аналогичные или разные операции, чем те, которые описаны со ссылкой на фигуры 5-7.

Инструкции, описанные в настоящем документе, являются инструкциями общего назначения, и могут быть использованы для различных целей. Для дополнительной иллюстрации определенных понятий, рассмотрим следующий подробный пример. Рассмотрим следующий цикл:

FOR I=1, N

DATA [INDEX [I]] = DATA [INDEX [I]] + COUNT

Без инструкций, описанных в настоящем документе, такие циклы могут быть закодированы в инструкции x86 следующим образом:

MOV ZMM2, [INDEX+RSI]

GATHERDPS ZMM1, [DATA + ZMM2 * SCALE]

ADDPS ZMM1, ZMM1, ZMM3

SCATTERDPS [DATA + ZMM2 * SCALE], ZMM1

Впрочем, в варианте осуществления инструкции сбора плюс упакованного сложения плюс разброса, такие циклы могут быть закодированы более кратко следующим образом:

MOV ZMM2, [INDEX+RSI]

GATADDSCATDPS [DATA + ZMM2 * SCALE], ZMM3

Преимущественно, данный пример иллюстрирует, что инструкция сбора плюс упакованное сложение плюс разброс может помочь устранить или уменьшить некоторые инструкции, которые могут помочь увеличить плотность кода и увеличить производительность. Более того, прирост производительности может также быть получен от сокращения служебных сигналов при генерации адреса и обработки загрузки/сохранения для каждого элемента. Как уже говорилось выше, фактический прирост производительности может зависеть от местоположения блока или схемы, в которой реализуется инструкция в конвейере. Как правило, чем ближе реализуется инструкция к памяти или, наоборот, чем дальше от наивысшего уровня кэша в системе, тем будет получен выше прирост производительности. Как уже упоминалось выше, это может быть связано, частично, для того, чтобы избежать необходимости хранить данные, ассоциированные с исполнением инструкции на самом высоком или более высоком уровне кэша, избегая необходимости передавать данные на межсоединение с самым высоким или более высоким уровнем кэша и др.

Фиг. 8 является блок-схемой варианта осуществления формата для инструкции 806 векторной индексированной загрузки плюс A/L операции плюс сохранения. Инструкция включает в себя код операции либо опкод 880. Опкод может представлять собой множество битов или одно или нескольких полей, которые выполнены с возможностью идентифицировать выполняемый тип инструкции и/или операции. Инструкция также включает в себя исходное поле 881 упакованных индексов памяти, которое предназначено для указания исходного операнда упакованных индексов памяти. Инструкция также включает в себя исходное поле 882 упакованных данных, которое предназначено для указания исходного операнда упакованных данных. В некоторых вариантах осуществления, инструкция может также возможно включать в себя исходное поле 883 операции маскировки упакованных данных, которое предназначено для указания исходной операции маскировки упакованных данных. В некоторых вариантах осуществления, инструкция может также возможно включать в себя исходное поле 885 адресной информации памяти для указания источника (например, регистр общего назначения), имеющего базовый адрес или другую адресную информацию. Альтернативно, инструкция может косвенно указывать на регистр или другой источник, имеющий такую адресную информацию памяти.

Фиг. 9 является блок-схемой варианта осуществления формата инструкции 908 векторной индексированной загрузки плюс A/L операции. Инструкция включает в себя код операции либо опкод 980. Код операции может представлять множество битов или одно или нескольких полей, которые предназначены для определения типа инструкции и/или операции. Инструкция также включает в себя исходное поле 981 упакованных индексов памяти, которое предназначено для указания исходного операнда упакованных индексов памяти. Инструкция также включает в себя исходное поле 982 упакованных данных, предназначенное для указания исходного операнда упакованных данных. В некоторых вариантах осуществления, инструкция может также возможно включать в себя исходное поле 983 операции маскировки упакованных данных, предназначенное для указания источника операции маскировки упакованных данных. Инструкции могут также возможно включать в себя поле 984 адресата упакованных данных, предназначенное для указания назначенной области хранения упакованных данных. В некоторых вариантах осуществления, назначенная область хранения упакованных данных может быть регистром упакованных данных или другой областью хранения на кристалле или в процессоре. В некоторых вариантах осуществления, инструкция может также возможно включать в себя поле 985 источника адресной информации памяти для указания источника (например, регистра общего назначения), имеющего базовый адрес памяти или другую адресную информацию. Альтернативно, инструкция может косвенно указывать на регистр или другой источник, имеющий такую адресную информацию памяти.

Как показано на фигурах 8-9, каждое из различных полей может включать в себя набор битов, достаточный для указания адреса регистра или в другой области хранения, которое имеет операнды. Биты полей могут быть непрерывными и/или фрагментированными. В других вариантах осуществления, одно или более различные поля могут быть неявными для инструкции (например, неявно обозначается опкодом инструкции) вместо того, чтобы явно указать посредством поля. Альтернативные варианты осуществления могут добавить дополнительные поля или опустить некоторые поля. Дополнительно, показанный порядок/расположения полей не является обязательным. Скорее, поля могут быть переупорядочены, некоторые поля могут перекрываться и др.

В некоторых вариантах осуществления формат команды может соответствовать EVEX кодированию или формату инструкции, хотя это не обязательно. EVEX кодирование будет рассмотрен ниже. В одном варианте осуществления два унаследованных префикса могут использоваться для переопределения управления 62. Например, префикс F2 может подразумевать использование форматирования операции загрузки и VSIB. В одном варианте осуществления этот префикс F2 может быть использован для инструкции векторной индексированной загрузки плюс A/L операции, как раскрыто в данном описании. Префикс F3 может подразумевать использование форматирования операции сохранения и VSIB. В одном варианте осуществления этот префикс F3 может быть использован для инструкции векторной индексированной загрузки плюс A/L операции плюс сохранение, как раскрыто в данном описании. Например, для VADDPS кодирования:

EVEX.U1.NDS.512.0F.WO 58 /r VADDPS zmm1, {k1}, zmm2, [rax]

Инструкция сбора плюс упакованное сложение может быть выражена как:

F2.EVEX.U1.NDS.512.0F.W0 58/r и VGATHERADDPS zmm1, {k1}, zmm2, [rax+zmm3 *scale]

Инструкция сбора плюс упакованное сложение плюс разброс может быть выражена как:

F3.EVEX.U1.HCP.512.0F. W0 58 /r и VGATSCATADDPS [rax+zmm3*scale] {k1}, zmm1, zmm2

zmm1, zmm2 и zmm3 относятся к 512-битным регистрам упакованных данных, {k1} представляет собой 64-разрядный регистр маски. Rax представляет собой целое число регистров общего назначения, используемые для удержания адресной информации памяти. Эти примеры являются просто иллюстративными примерами подходящих кодировок. Объем изобретения не ограничивается этими кодировками.

Для дополнительной иллюстрации определенных понятий, рассмотрим несколько примеров подходящих форматов упакованных данных. 128-битный формат упакованного слова является 128-битной шириной и включает в себя восемь 16-разрядных элементов данных слова. 128-битный формат упакованного двойного слова является 128 битами и содержит четыре 32-битные элементы данных двойного слова. 128-разрядный формат 846 упакованного учетверенного слова является 128 битами и содержит два 64-разрядных элемента данных учетверенного слова. 256-битный формат упакованного слова является 256-битной шириной и включает в себя шестнадцать 16-разрядных элементов данных слова. 256-битный формат 850 двойного слова является 256 битами и включает в себя восемь 32-битных элемента данных двойного слова. 256-разрядный формат упакованного учетверенного слова является 256 битами и включает в себя четыре 64-разрядных элемента данных учетверенного слова. 512-битный формат упакованного слова представляет собой 512-битовую ширину и включает в себя тридцать два 16-разрядных элементов данных слова. 512-битный формат упакованного двойного слова представляет собой 512-бит и содержит шестнадцать 32-битных элемента данных двойного слова. 512-битный формат упакованного учетверенного слова представляет собой 512-бит и включает в себя восемь 64-битных элементов данных учетверенного слова. Другие форматы упакованных данных могут включать в себя форматы упакованных 32-бит с плавающей точкой одинарной точности или форматы упакованные 64-битные двойной точности с плавающей точкой. Любой другой размер элемента данных (например, более широкие или более узкие), пригодный для инструкций сбора и/или разброса, также подходят. Кроме того, более широкие или более узкие ширины упакованных данных также подходят, такие как, например, 64-разрядные упакованные данные, 1024-разрядные упакованные данные и др. Как правило, число элементов упакованных данных равно размеру в битах упакованных данных, разделенного на размер в битах элементов упакованных данных.

Фиг. 10 представляет блок-схему примера варианта осуществления конкретного подходящего набора регистров 1012 упакованных данных. Иллюстрированные регистры упакованных данных включают в себя тридцать два 512-разрядных регистров упакованных данных или векторных регистров. Эти тридцать два 512-разрядных регистры обозначены как с ZMM0 по ZMM31. В показанном варианте осуществления 256-биты младшего разряда нижних шестнадцать из этих регистров, а именно ZMM0 по ZMM15 имеют псевдоним или накладываются на соответствующие 256-битные регистры упакованных данных или векторные регистры, обозначенные как YMM0-YMM15, хотя это не обязательно. Кроме того, в показанном варианте осуществления 128-биты младшего разряда YMM0-YMM15 имеют псевдоним или накладываются на соответствующие 128-разрядные регистры упакованных данных или векторные регистры, обозначенные как ХММ0-ХММ1, хотя это также не требуется. 512-битные регистры с ZMM0 по ZMM31 выполнены с возможностью удерживать 512-разрядные упакованные данные, 256-битные упакованные данные или 128-разрядные упакованные данные. 256-битные регистры с YMM0-YMM15 выполнены с возможностью удерживать 256-битные упакованные данные или 128-разрядные упакованные данные. 128-битные регистры от ХММ0-ХММ1 выпилены с возможностью удерживать 128-битные упакованные данные. Каждый из регистров может использоваться для хранения упакованных данных с плавающей запятой или целочисленных упакованных данных. Другие размеры элемента данных поддерживаются, включая в себя, по меньшей мере, 8-битный байт данных, 16-битное слово данных, 32-битное двойное слово, данные с плавающей точкой одинарной точности, 64-разрядное учетверенное слово и данные с плавающей точкой двойной точности. Альтернативные варианты осуществления подходящих регистров упакованных данных могут включать в себя разное количество регистров, различные размеры регистров, может или не может задавать псевдоним большим регистрам на малых регистрах и может или не может также использоваться для данных с плавающей запятой.

Фиг. 11 представляет блок-схему примера варианта осуществления конкретного подходящего набора регистров 1118 маскированных упакованных данных. Каждый из регистров маскированных упакованных данных может использоваться для хранения маскированных упакованных данных. В иллюстрируемом варианте осуществления выполнения набор включает в себя восемь регистров упакованных данных операции маскировки, обозначенных как с k0 по k7. Альтернативные варианты осуществления могут включать в себя либо меньше чем восемь (например, два, четыре, шесть и т.д.) или больше, чем восемь (напр., шестнадцать, двадцать, тридцать два и т.д.) регистров упакованных данных операции маскировки. В показанном варианте осуществления, каждый из регистров упакованных данных операции маскировки является 64-битным. В альтернативных вариантах осуществления, величины ширин регистров упакованных данных операции маскировки могут быть либо шире, чем 64-бит (например, 80-бит, 128-бит и др.) или уже, чем 64-бит (например, 8-бит, 16-бит, 32-бит и т.д.). Например, инструкция может использовать три бита (например, 3-битовое поле) для кодирования или указания любого из восьми регистров с k0 по k7 упакованных данных операции маскировки. В альтернативных вариантах осуществления, либо меньшее или большее число битов может быть использовано, когда есть меньше или больше регистров упакованных данных операции маскировки, соответственно.

Фиг. 12 представляет собой схему, иллюстрирующую пример конкретного пригодного 64-разрядного регистра 1218 упакованных данных операции маскировки, и иллюстрирующую, что число битов, используемых как упакованные данные операции маскировки и/или для маскировки, зависит от ширины упакованных данных и ширины элемента данных. Иллюстрированный регистр маски является 64-битным, хотя как говорилось выше, это не требуется. Как правило, когда используется один бит управления для маскировки элемента, то число битов, используемых для маскировки, равно ширине упакованных данных в битах, деленной на ширину элемента упакованных данных в битах. Для дополнительной иллюстрации рассмотрим несколько возможных примеров вариантов осуществления. Только 8-бит, например, только младшие 8 бит могут быть использованы для 256-разрядных упакованных данных, имеющие 32-разрядные элементы данных. Только 16-бит, например, только младшие 16-бит могут быть использованы либо для 512-битных упакованных данных, имеющие 32-разрядные элементы данных. Только 32-бит, например, только младшие 32-бита могут использоваться либо для 1024-разрядных упакованных данных, имеющие 32-разрядные элементы данных. Все 64-биты могут быть использованы для 1024-разрядных упакованных данных, имеющие 16-разрядные элементы данных.

Как было описано выше, векторные операции вертикального типа были выделены для облегчения иллюстрации и описания, хотя объем изобретения этим не ограничен. Любой из вариантов осуществления, описанный здесь, использующий векторные операции вертикального типа, может быть изменен для другой векторной операции невертикального типа (например, часть вертикального и часть горизонтального типа операции, операции на более чем паре соответствующих элементов вертикально расположенных данных и др.).

В других вариантах осуществления, вместо инструкции, использующие одну арифметическую и/или логическую операцию (например, операцию упакованного умножения или упакованного сложения), вариант осуществления инструкции может включать в себя несколько различных арифметических и/или логических операций, которые будут выполняться последовательно. Например, после того, как операция векторной индексированной загрузки, первая арифметическая и/или логическая операция могут быть выполнены, как описано здесь в другом месте, затем вторая арифметическая и/или логическая операция может возможно выполняться, используя результат первой арифметической и/или логической операции и потенциально другие данные, и затем результаты второй арифметической и/или логической операции могут быть сохранены в памяти.

Компоненты, признаки и детали, описанные для любых фигур 3 и 5-12, могут также возможно использоваться в любых чертежах 1-2 и 4. Кроме того, компоненты, признаки и детали, описанные в настоящем документе для любого устройства, могут также возможно использоваться в любом из способов, описанных в данном документе, который в вариантах осуществления может быть выполнен посредством и/или с таким устройством.

Набор инструкций включает в себя один или несколько форматов инструкции. Данный формат инструкции определяет различные поля (число битов, расположение битов) для указания, среди прочего, операции (опкод), которые должны быть выполнены, и операнд(ы), на которых данная операция может быть выполнена. Некоторые форматы инструкций дополнительно подвергаются дальнейшей разбивке для определения шаблонов инструкций (или подформатов). Например, шаблоны инструкции заданного формата инструкции могут быть определены для различных подмножеств полей формата инструкции (полей расположенных, как правило, в том же порядке, но, по меньшей мере, некоторые имеют различные битовые позиции, поскольку есть меньше полей) и/или определенное заданное поле должно интерпретироваться иначе. Таким образом, каждая инструкция ISA выражается, используя данный формат инструкции (и, если определен заданный один из шаблонов инструкций формата инструкции) и включает в себя поля для указания операции и операндов. Например, примерная инструкция ADD имеет конкретный опкод и формат инструкции, который включает в себя поле кода операции, чтобы указать, что код операции и поля операнда для выбора операндов (источник 1 / адресат и источник 2); и появление инструкции ADD в потоке инструкций будет иметь конкретный контент в полях операнда для выбора конкретных операндов. Набор SIMD расширений, упомянутых в векторных расширениях набора команд (AVX) (AVX1 и AVX2), и с использованием схемы кодирования векторных расширений (VEX), был выпущен и/или опубликован (см., например, справочник Intel® 64 и IA-32 разработчиков архитектуры программного обеспечения, октябрь 2011 г.; и см. справочник по программированию Intel® Векторные расширения набора команд, июнь 2011).

Форматы иллюстративной инструкции

Варианты осуществления инструкции(й), описанные здесь, могут быть реализованы в разных форматах. Кроме того, далее приводится подробное описание иллюстративной системы, архитектуры и конвейера. Варианты осуществления инструкции(й) могут быть выполнены на таких системах, архитектурах и конвейерах, но не ограничиваются ими.

Общий векторный дружественный формат инструкции

Векторный дружественный формат инструкции представляет собой формат инструкции, который подходит для векторных инструкций (например, есть определенные поля для векторных операций). Описанные варианты осуществления, в которых как векторные, так и скалярные операции поддерживаются посредством векторного дружественного формата инструкции, альтернативные варианты осуществления используют только векторные операции векторного дружественного формата инструкции.

Фигуры 13А-13В являются блок-схемами, иллюстрирующие общий векторный дружественный формат инструкции и шаблоны инструкции согласно вариантам осуществления изобретения. Фиг. 13А показывает блок-схему, иллюстрирующую общий векторный дружественный формат инструкции и шаблоны инструкции класса А согласно вариантам осуществления изобретения; фиг. 13В показывает блок-схему, иллюстрирующую общий векторный дружественный формат инструкции и шаблоны инструкции класса В согласно вариантам осуществления изобретения. В частности, общий векторный дружественный формат инструкции 1300, для которого определяются шаблоны инструкции класса А и класса В, оба включают в себя шаблоны инструкции без доступа 1305 к памяти и шаблоны инструкции с доступом 1320 к памяти 1320. Термин общий в контексте векторного дружественного формата инструкции относится к формату инструкции, не будучи привязанным к какому-либо конкретному набору инструкций.