Результат интеллектуальной деятельности: ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Вид РИД

Изобретение

Перекрестные ссылки на родственные заявки

Данная заявка основана и притязает на приоритет предварительной заявки на патент США № 61/804548, поданной 22 марта 2013 года, и заявки на патент США №14/014183, поданной 29 августа 2013 года, содержимое которых полностью включено в данный документ путем ссылки.

Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к полупроводниковому запоминающему устройству.

Уровень техники

В полупроводниковом запоминающем устройстве, таком как SDRAM, доступ выполняется, например, посредством ввода адреса строки вместе с командой активации и ввода адреса столбца вместе с командой считывания/командой записи. Тем не менее, в последние годы размер адресов (число битов) увеличивается по мере того, как возрастает емкость хранения полупроводникового запоминающего устройства.

Краткое описание чертежей

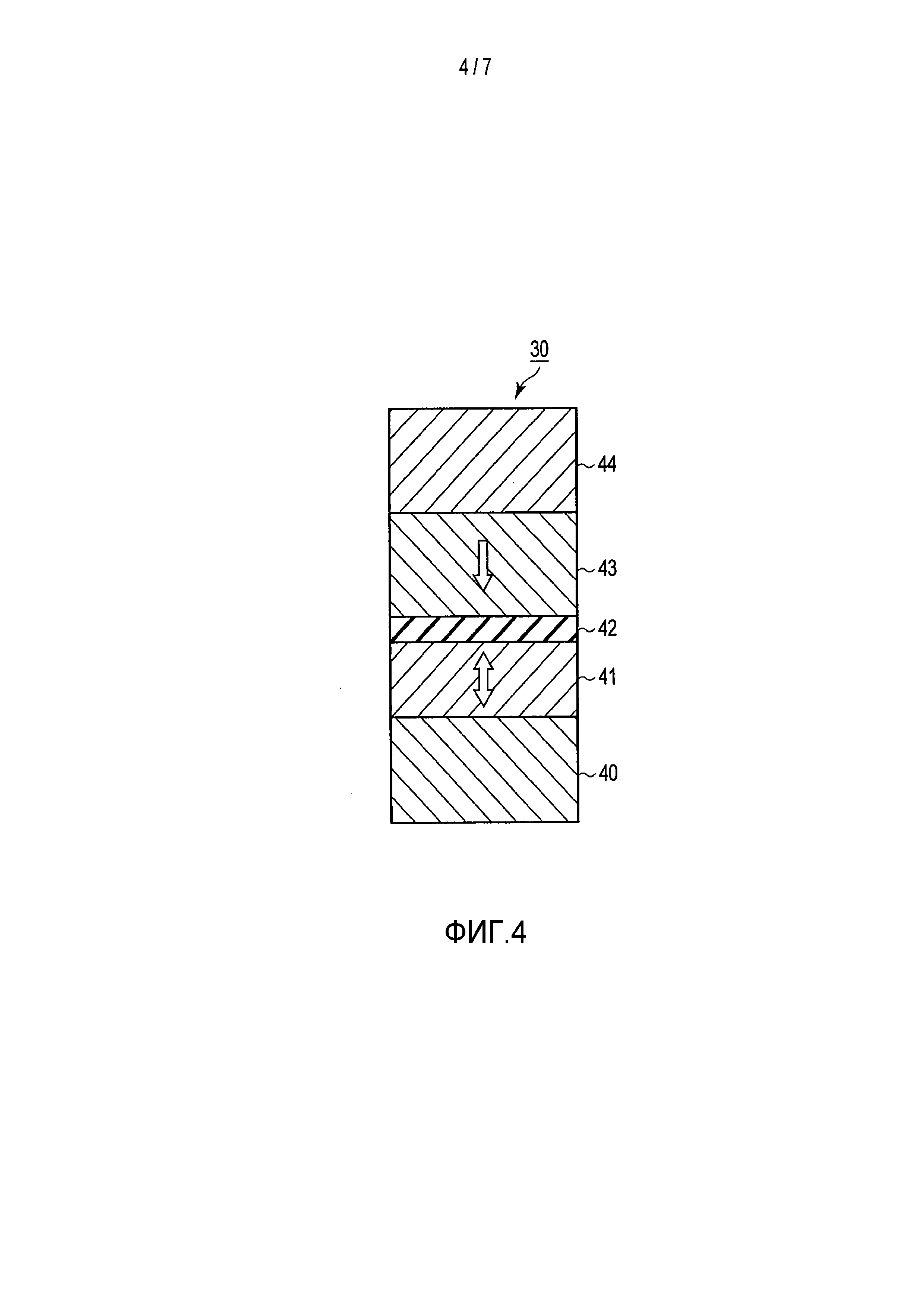

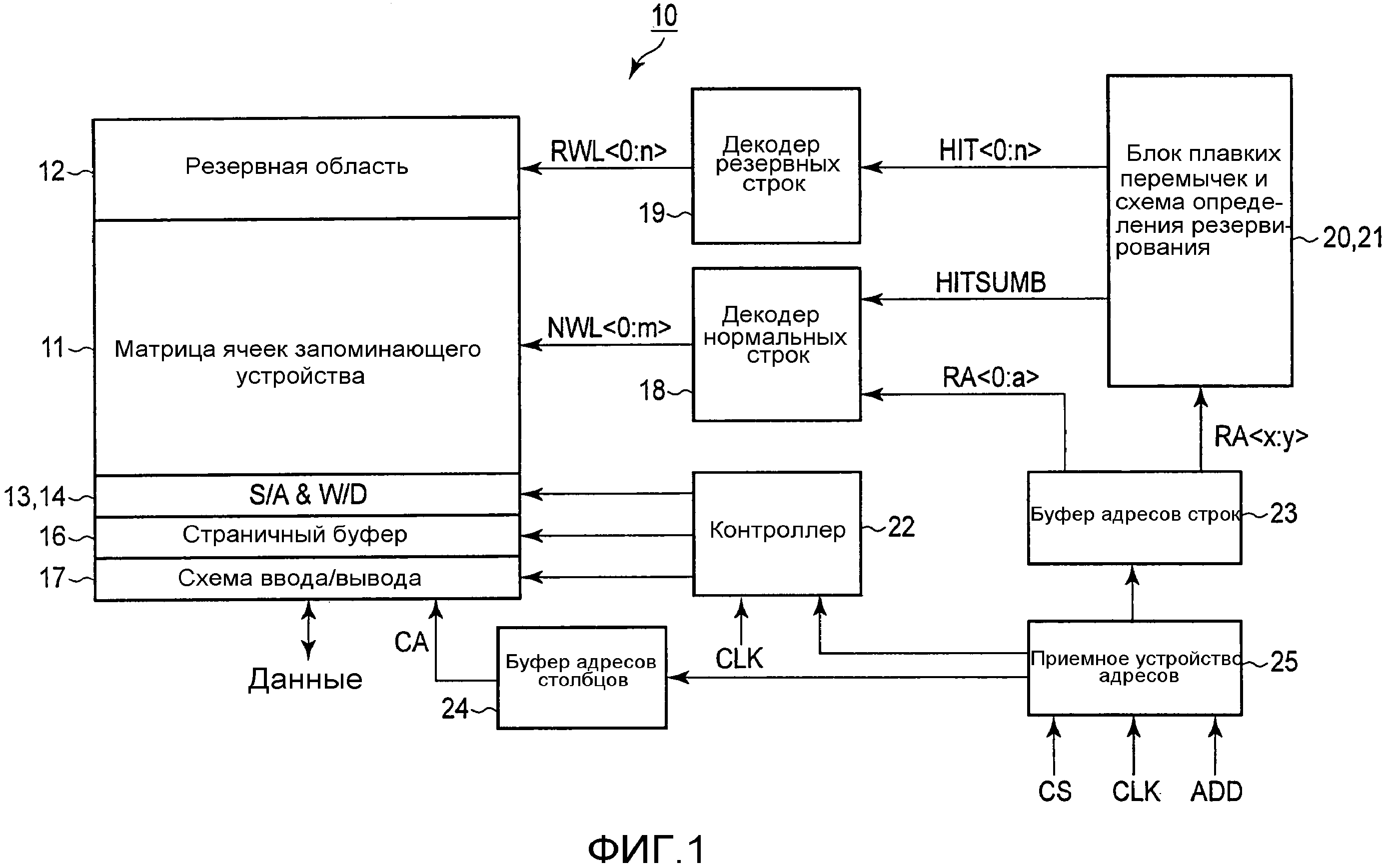

Фиг. 1 является блок-схемой MRAM согласно первому варианту осуществления;

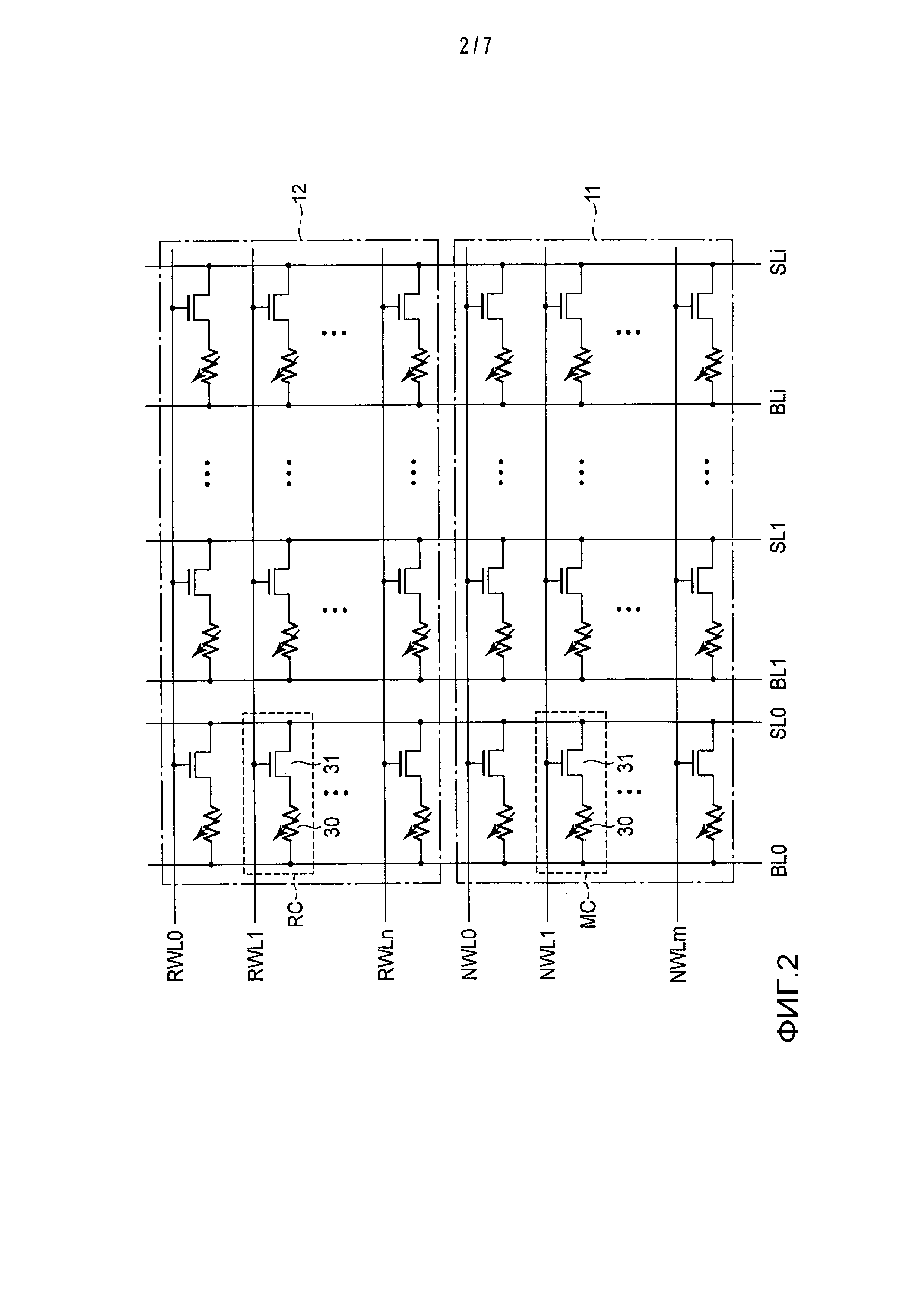

Фиг. 2 является принципиальной схемой матрицы ячеек запоминающего устройства и резервной области;

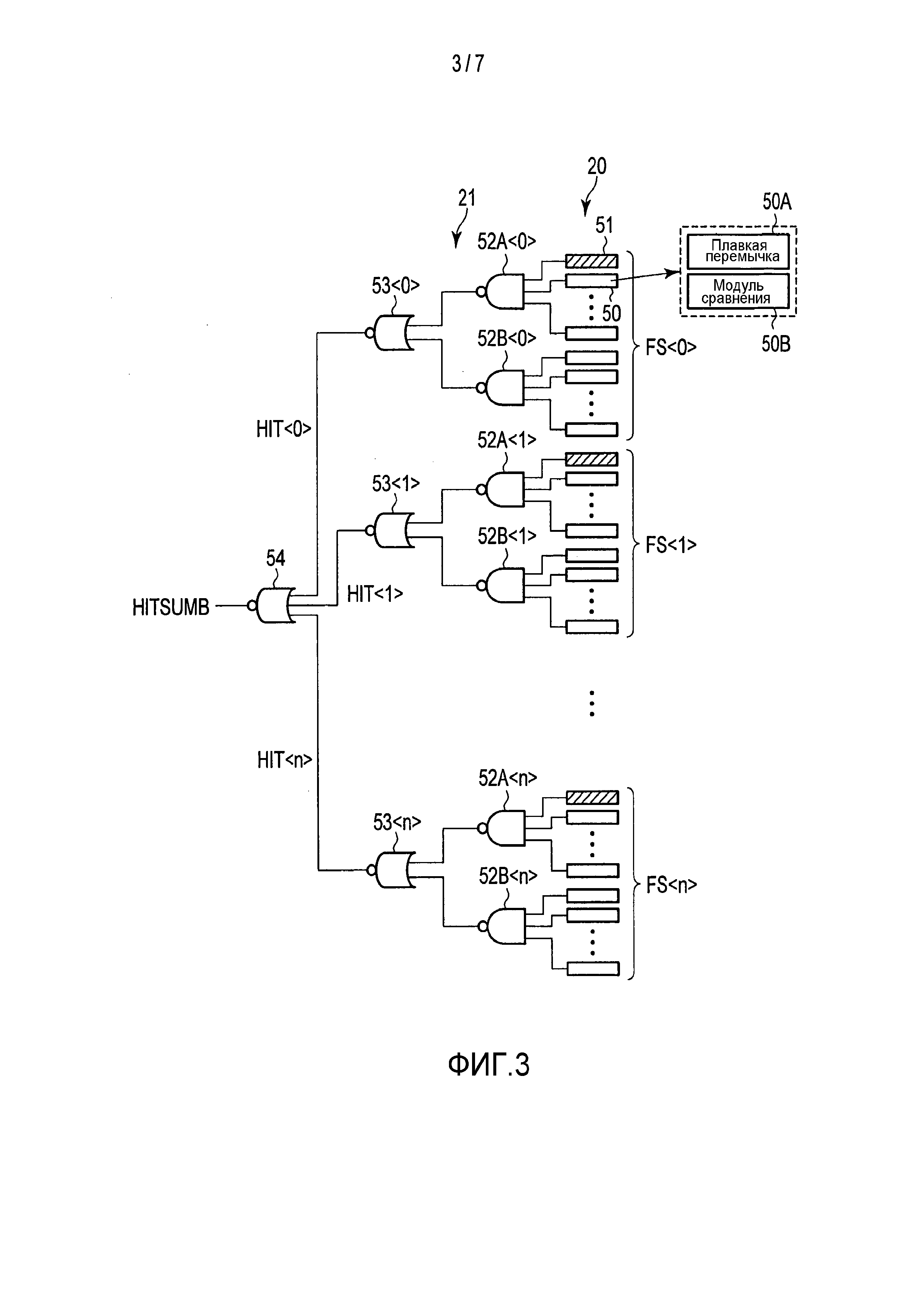

Фиг. 3 является принципиальной схемой блока плавких перемычек и схемы определения резервирования;

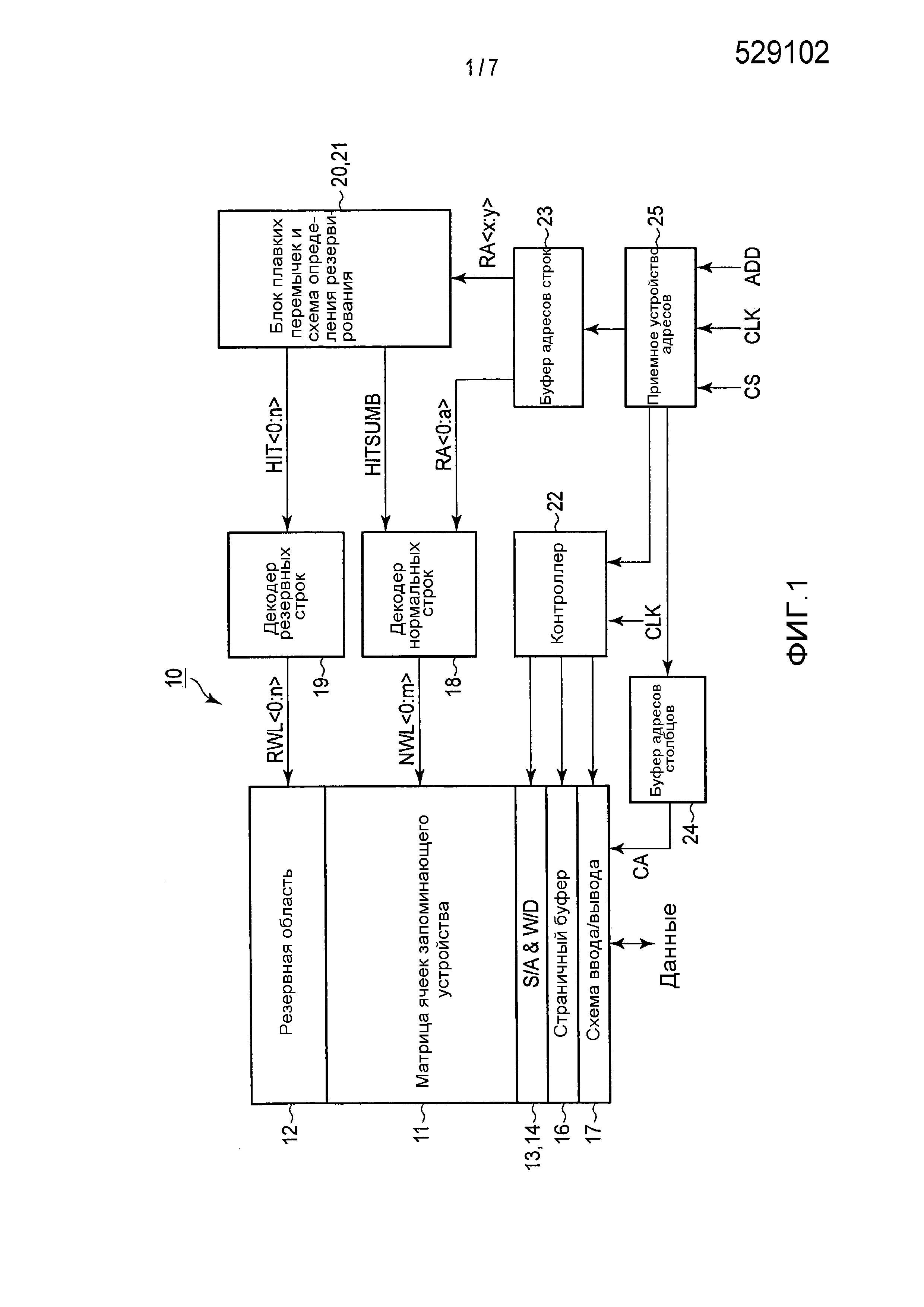

Фиг. 4 является видом в поперечном сечении MTJ-элемента;

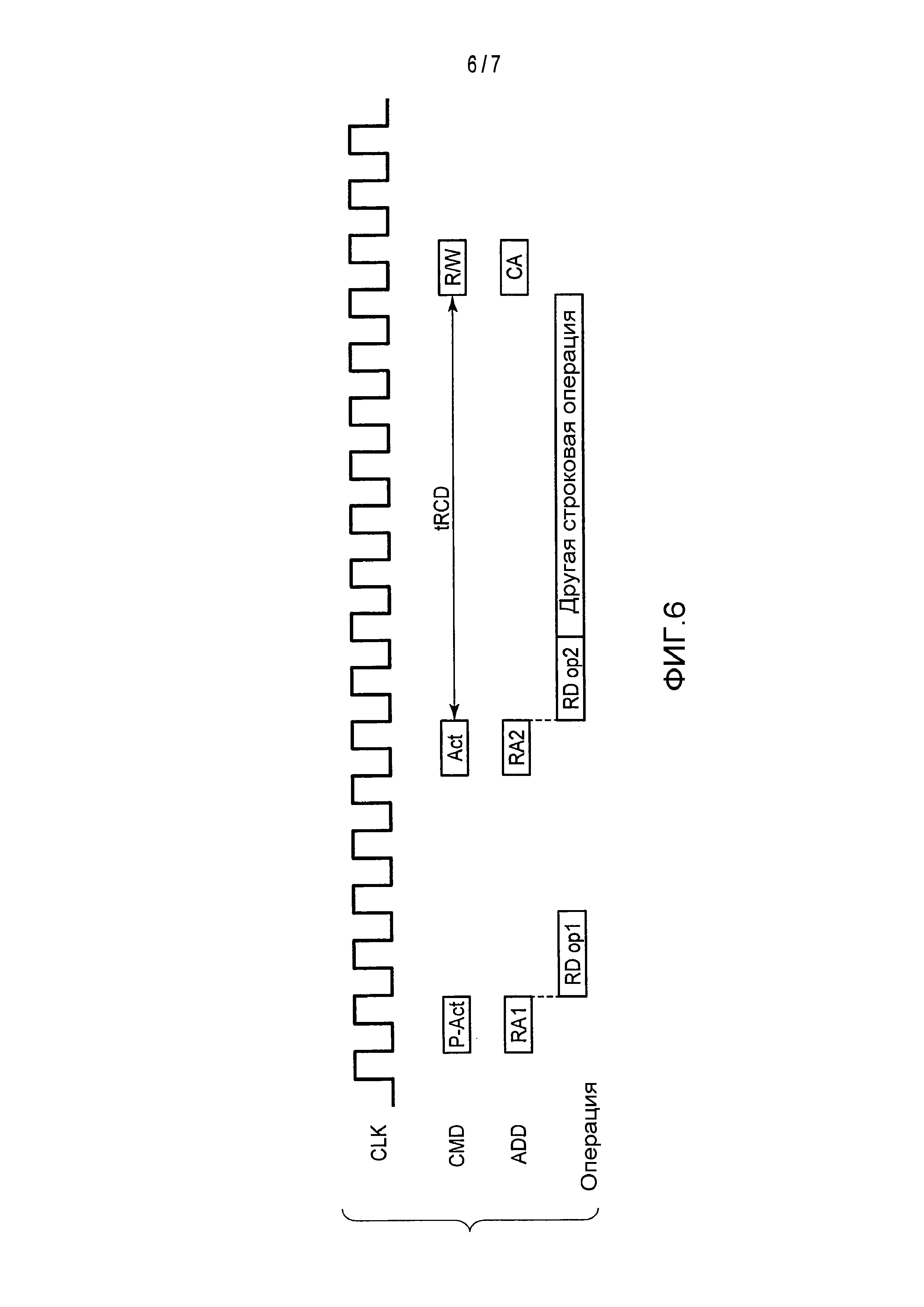

Фиг. 5 является временной диаграммой, показывающей работу MRAM;

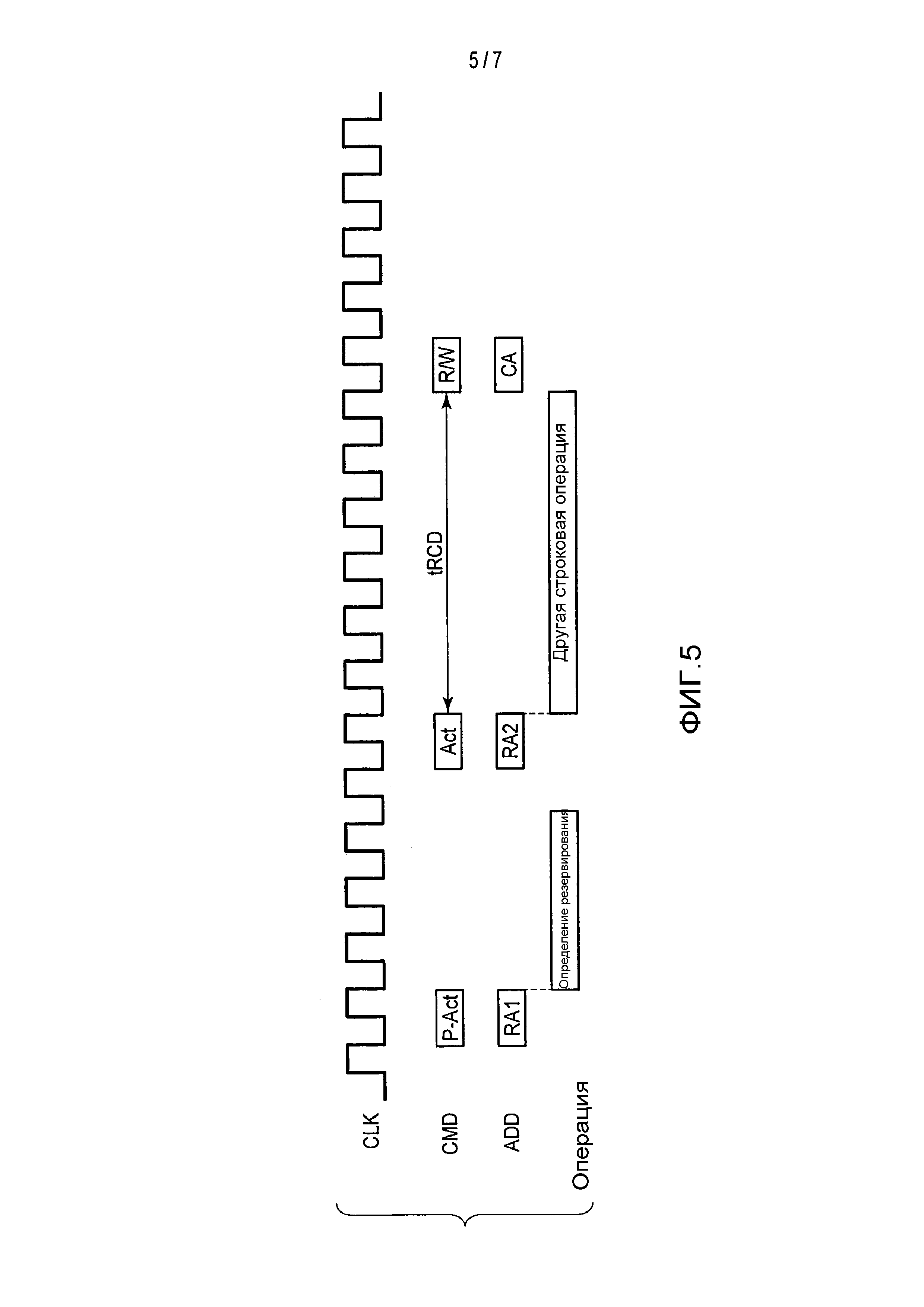

Фиг. 6 является временной диаграммой, показывающей работу MRAM согласно второму варианту осуществления; и

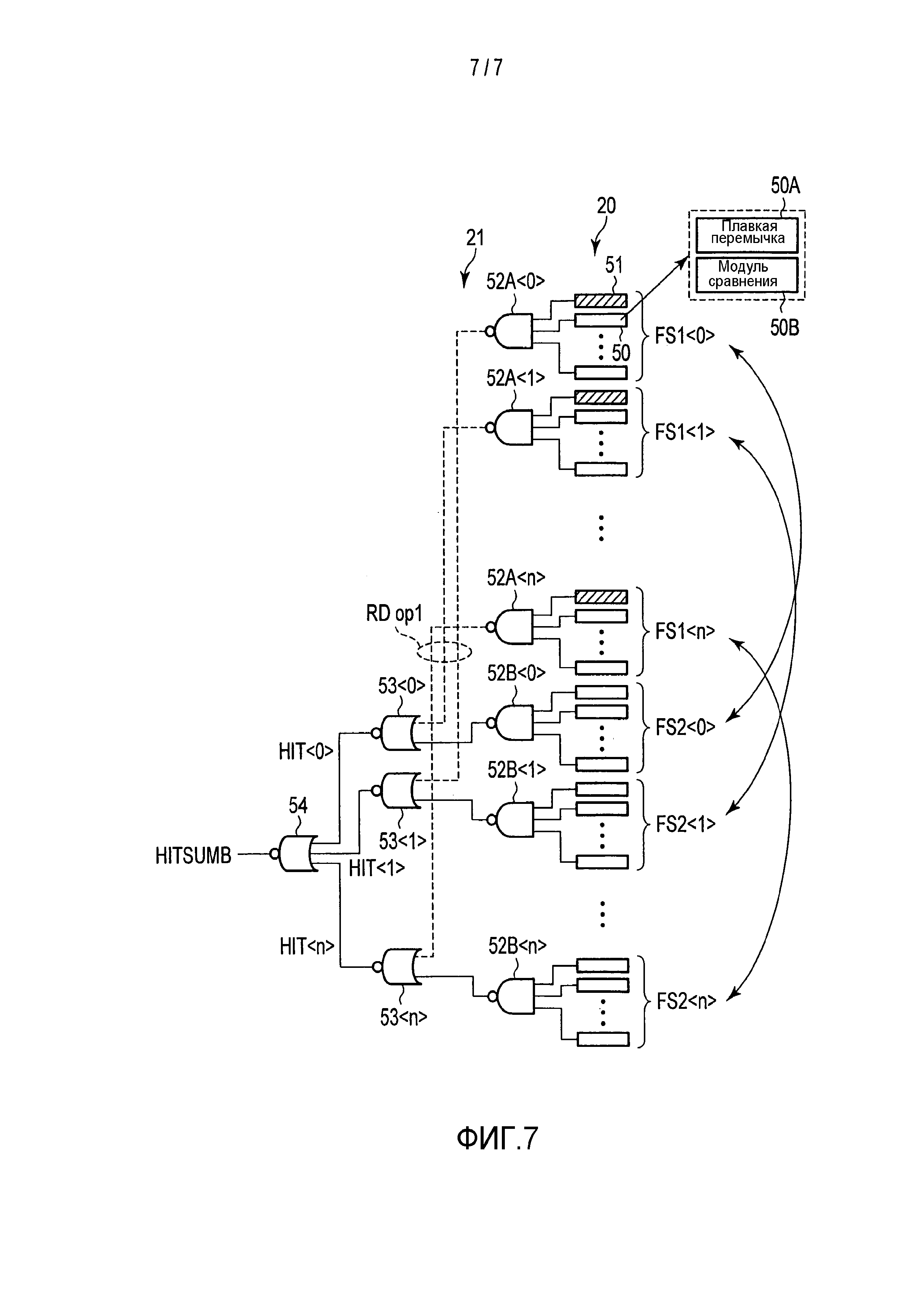

Фиг. 7 является принципиальной схемой блока плавких перемычек и схемы определения резервирования.

Подробное описание изобретения

В общем, согласно одному варианту осуществления, предусмотрено полупроводниковое запоминающее устройство, содержащее:

матрицу ячеек запоминающего устройства, содержащую ячейки запоминающего устройства;

резервную область, содержащую резервные ячейки, которые используются вместо сбойных ячеек в матрице ячеек запоминающего устройства;

первые числовые шины, подключенные к матрице ячеек запоминающего устройства;

вторые числовые шины, подключенные к резервной области;

первый декодер строк, выполненный с возможностью осуществлять выбор из первых числовых шин на основе адреса строки;

схему определения, выполненную с возможностью определять, требуется ли или нет операция замены резервной областью на основе резервного адреса, включенного в адрес строки; и

второй декодер строк, выполненный с возможностью осуществлять выбор из вторых числовых шин на основе результата определения посредством схемы определения,

при этом адрес строки включает в себя первый адрес строки и второй адрес строки, вводимые по порядку способом разделения времени, и

первый адрес строки включает в себя весь резервный адрес.

Ниже описываются варианты осуществления настоящего изобретения со ссылкой на чертежи. В нижеприведенном описании компоненты с одними и теми же функциями и конфигурациями обозначаются посредством одних и тех же ссылочных позиций, и дублированные описания предоставляются только при необходимости.

Варианты осуществления описываются ниже с рассмотрением MRAM (магнитного оперативного запоминающего устройства) в качестве примера полупроводникового запоминающего устройства.

Первый вариант осуществления

1. Конфигурация MRAM

1-1. Общая конфигурация MRAM

Фиг. 1 является блок-схемой MRAM 10 согласно первому варианту осуществления. MRAM 10 содержит матрицу 11 ячеек запоминающего устройства, резервную область 12, усилитель 13 считывания (S/A), служащий в качестве схемы считывания, формирователь 14 сигналов записи (W/D), служащий в качестве схемы записи, схему 15 ECC (проверки и коррекции ошибок), страничный буфер 16 (P/B), схему 17 ввода-вывода, декодер 18 нормальных строк, декодер 19 резервных строк, блок 20 плавких перемычек, служащий в качестве модуля хранения адресов сбоев, схему 21 определения резервирования, контроллер 22, буфер 23 адресов строк, буфер 24 адресов столбцов и приемное устройство 25 адресов.

Матрица 11 ячеек запоминающего устройства содержит множество ячеек запоминающего устройства, размещаемых в матрице. Матрица 11 ячеек запоминающего устройства содержит множество числовых шин (нормальных числовых шин) NWL<0:m>, множество разрядных шин и множество истоковых шин, расположенных в ней. Одна числовая шина NWL и одна пара из разрядной шины и истоковой шины подключаются к одной ячейке запоминающего устройства.

Резервная область 12 предоставляется с возможностью восстанавливать сбойные ячейки запоминающего устройства, возникающие в матрице 11 ячеек запоминающего устройства. Резервная область 12 имеет меньшую емкость хранения, чем матрица 11 ячеек запоминающего устройства, но имеет конфигурацию, идентичную конфигурации матрицы 11 ячеек запоминающего устройства. Иными словами, резервная область 12 содержит множество резервных ячеек, размещаемых в матрице. Каждая из резервных ячеек имеет конфигурацию, идентичную конфигурации ячейки запоминающего устройства. Резервная область 12 содержит множество числовых шин (резервных числовых шин) RWL<0:n>, размещенных в ней, и множество разрядных шин и истоковых шин, размещенных в ней, которые являются общими для матрицы 11 ячеек запоминающего устройства. Одна числовая шина RWL и одна пара из разрядной шины и истоковой шины подключаются к одной резервной ячейке. Резервная область 12 заменяется матрицей 11 ячеек запоминающего устройства в единицах одной строки (группы ячеек запоминающего устройства, подключенных к одной числовой шине RWL) или множества строк.

Приемное устройство 25 адресов принимает адрес ADD, синхросигнал CLK и сигнал CS выбора кристалла из внешней схемы. Адрес ADD включает в себя адрес RA строки и адрес CA столбца. Адрес ADD и сигнал CS выбора кристалла отправляются в контроллер 22. Адрес RA строки отправляется в буфер 23 адресов строк. Адрес CA столбца отправляется в буфер 24 адресов столбцов.

Буфер 24 адресов столбцов принимает адрес CA столбца из приемного устройства 25 адресов. Буфер 24 адресов столбцов отправляет адрес CA столбца в усилитель 13 считывания, формирователь 14 сигналов записи, страничный буфер 16 и схему 17 ввода-вывода.

Буфер 23 адресов строк принимает адрес RA строки из приемного устройства 25 адресов. Буфер 23 адресов строк отправляет адрес RA<0:a> строки в декодер 18 нормальных строк и отправляет адрес RA<x:y> резервной строки в схему 21 определения резервирования. Адрес RA<x:y> резервной строки содержит часть адреса RA<0:a> строки.

Декодер 18 нормальных строк подключается к множеству числовых шин NWL<0:m>, расположенных в матрице 11 ячеек запоминающего устройства. Декодер 18 нормальных строк выбирает любую из множества числовых шин NWL<0:m> на основе адреса RA<0:a> строки.

Декодер 19 резервных строк подключается к множеству числовых шин RWL<0:n>, расположенных в резервной области 12. Декодер 19 резервных строк выбирает любую из множества числовых шин RWL<0:n> на основе сигнала HIT<0:n>, отправленного из схемы 21 определения резервирования.

Блок 20 плавких перемычек сохраняет адреса (адреса сбоев) для использования при идентификации числовых шин, подключенных к сбойным ячейкам запоминающего устройства, возникающим в матрице 11 ячеек запоминающего устройства. Блок 20 плавких перемычек содержит множество элементов-плавких перемычек, выполненных с возможностью сохранять адреса сбоев. Ниже описывается конкретная конфигурация блока 20 плавких перемычек.

Схема 21 определения резервирования сравнивает адрес RA<x:y> резервной строки с каждым из адресов сбоев, сохраненных в блоке 20 плавких перемычек, чтобы формировать сигнал HIT<0:n> и сигнал HITSUMB в качестве результата сравнения. Сигнал HIT<0:n> отправляется в схему 21 определения резервирования. Сигнал HITSUMB отправляется в декодер 18 нормальных строк. Ниже описывается конкретная конфигурация схемы 21 определения резервирования.

Усилитель 13 считывания подключается ко множеству разрядных шин. Например, в случае схемы определения напряжения, усилитель 13 считывания сравнивает опорное напряжение с напряжением ячейки, приложенным к выбранной ячейке запоминающего устройства через соответствующую разрядную шину BL, чтобы определять и усиливать данные в выбранной ячейке запоминающего устройства. Формирователь 14 сигналов записи подключается ко множеству разрядных шин и множеству истоковых шин. Формирователь 14 сигналов записи записывает данные в выбранную ячейку запоминающего устройства через надлежащую разрядную шину и истоковую шину.

Страничный буфер 16 запоминает записываемые данные, отправленные из схемы 17 ввода-вывода, и считываемые данные, отправленные из усилителя 13 считывания.

Схема 17 ввода-вывода подключается к внешней схеме, чтобы выполнять процесс вывода и приема данных в/из внешней схемы. Схема 17 ввода-вывода отправляет входные данные, принятые из внешней схемы, в страничный буфер в качестве записываемых данных. Схема 17 ввода-вывода выводит считываемые данные, принятые из страничного буфера 16, во внешнюю схему в качестве выходных данных.

Контроллер 22 интегрально управляет работой MRAM 10. Контроллер 22 принимает синхросигнал CLK из внешней схемы. Контроллер 22 подает различные управляющие сигналы в усилитель 13 считывания, формирователь 14 сигналов записи, страничный буфер 16 и схему 17 ввода-вывода, чтобы управлять операциями этих схем.

1-2. Конфигурация матрицы ячеек запоминающего устройства и резервной области

Далее описывается конфигурация матрицы 11 ячеек запоминающего устройства и резервной области 12. Фиг. 2 является принципиальной схемой матрицы 11 ячеек запоминающего устройства и резервной области 12. Матрица 11 ячеек запоминающего устройства содержит множество ячеек MC запоминающего устройства, размещаемых в матрице. Матрица 11 ячеек запоминающего устройства содержит множество числовых шин NWL<0:m>, множество разрядных шин BL<0:i> и множество истоковых шин SL<0:i>. Ячейка MC запоминающего устройства подключается к одной числовой шине NWL и одной паре из разрядной шины BL и истоковой шине SL.

Ячейка MC запоминающего устройства содержит элемент 30 с магниторезистивным эффектом (элемент с MTJ (магнитным туннельным переходом)) и транзистор 31 выбора. Транзистор 31 выбора содержит, например, MOSFET-транзистор с каналом n-типа. Один конец MTJ-элемента 30 подключается к соответствующей разрядной шине BL. Другой конец MTJ-элемента 30 подключается к стоку транзистора 31 выбора. Затвор транзистора 31 выбора подключается к соответствующей числовой шине NWL. Исток транзистора 31 выбора подключается к соответствующей истоковой шине SL.

Резервная область 12 содержит множество резервных ячеек RC, размещаемых в матрице. Резервная область 12 содержит множество числовых шин RWL<0:n>, множество разрядных шин BL<0:i> и множество истоковых шин SL<0:i>. Резервная ячейка RC подключается к одной числовой шине RWL и одной паре из разрядной шины BL и истоковой шине SL. Резервная ячейка RC имеет конфигурацию, идентичную конфигурации ячейки MC запоминающего устройства.

1-3. Конфигурация блока плавких перемычек и схемы определения резервирования

Далее описывается пример конфигурации блока 20 плавких перемычек и схемы 21 определения резервирования. Фиг. 3 является принципиальной схемой блока 20 плавких перемычек и схемы 21 определения резервирования.

Блок 20 плавких перемычек содержит множество наборов FS<0:n> плавких перемычек, соответствующих множеству числовых шин RWL<0:n>. Каждый из наборов FS плавких перемычек содержит множество модулей 50 плавких перемычек, соответствующих числу битов в адресе RA<x:y> резервной строки и одном модуле 51 разрешения использования плавких перемычек. Каждый из модулей 50 плавких перемычек содержит элемент-плавкую перемычку 50A и модуль 50B сравнения. Элемент-плавкая перемычка 50A представляет собой, например, выжигаемую лазером плавкую перемычку (выжигаемую электричеством плавкую перемычку). Модуль 51 разрешения использования плавких перемычек также имеет конфигурацию, идентичную конфигурации модуля 50 плавких перемычек.

Модуль 51 разрешения использования плавких перемычек используется для того, чтобы определять, следует ли или нет использовать набор FS плавких перемычек, включающий в себя этот модуль 51 разрешения использования плавких перемычек. Информация, указывающая, следует ли или нет использовать набор FS плавких перемычек, программируется в элементе-плавкой перемычке в модуле 51 разрешения использования плавких перемычек. Модуль 51 разрешения использования плавких перемычек выполнен с возможностью выводить H-уровень, если набор FS плавких перемычек должен использоваться.

Адрес (адрес сбоя) для использования при идентификации числовой шине, подключенной к сбойной ячейке запоминающего устройства, включенной в матрицу 11 ячеек запоминающего устройства (т.е. одной из числовых шин в матрице 11 ячеек запоминающего устройства, которая должна быть заменена резервной областью 12), программируется в каждом из множества элементов-плавких перемычек 50A, включенных во множество модулей 50 плавких перемычек в каждом наборе FS плавких перемычек. Модуль 50 плавких перемычек (в частности, модуль 50B сравнения) сравнивает непосредственно бит адреса, введенный в модуль 50 плавких перемычек, с битом, сохраненным в элементе-плавкой перемычке 50A. Если бит адреса совпадает с сохраненным битом, модуль 50 плавких перемычек выводит H-уровень.

Схема 21 определения резервирования содержит множество (например, два) логических элементов 52А и 52B "НЕ-И", подключенных к каждому набору FS плавких перемычек, и логический элемент 53 "НЕ-ИЛИ", подключенный к выводам логических элементов 52А и 52B "НЕ-И". Схема 21 определения резервирования дополнительно содержит логический элемент 54 "НЕ-ИЛИ", подключенный к выводам множества логических элементов 53 <0:n> "НЕ-ИЛИ", соответствующих множеству числовых шин RWL<0:n>.

Если адрес сбоя, сохраненный в наборе FS<0> плавких перемычек, совпадает с адресом RA<x:y> резервной строки, схема 21 определения резервирования подтверждает сигнал HIT<0> (выводит H-уровень). Сигнал HIT<1:n> работает аналогично сигналу HIT<0>. Сигнал HIT<0:n> отправляется в декодер 19 резервных строк. В завершение, активируется резервная числовая шина RWL<α>, соответствующая подтвержденному сигналу HIT<α>.

Кроме того, если какой-либо из сигналов HIT<0:n> подтвержден, схема 21 определения резервирования подтверждает сигнал HITSUMB (выводит L-уровень). Сигнал HITSUMB отправляется в декодер 18 нормальных строк. Сигнал HITSUMB с L-уровнем означает, что операция замены резервной областью 12 должна выполняться. Следовательно, если сигнал HITSUMB имеет L-уровень, декодер 18 нормальных строк работает с возможностью не допускать активации числовой шине NWL<0:m>.

1-4. Структура MTJ-элемента

Далее описывается пример структуры MTJ-элемента 30. Фиг. 4 является видом в сечении MTJ-элемента 30. MTJ-элемент содержит нижний электрод 40, запоминающий слой 41 (также называемый "свободным слоем"), немагнитный слой 42 (туннельный барьерный слой), опорный слой 43 (также называемый "фиксированным слоем") и верхний электрод 44, уложенные в этом порядке. Порядок, в котором уложены запоминающий слой 41 и опорный слой 43, может быть изменен на противоположный.

Запоминающий слой 41 и опорный слой 43 формируются из ферромагнитного материала. Используемый туннельный барьерный слой 42 представляет собой, например, изоляционный материал, такой как MGO.

Каждый из запоминающего слоя 41 и опорного слоя 43 имеет перпендикулярную магнитную анизотропию и направление простого намагничивания, равное перпендикулярному направлению. Запоминающий слой 41 и опорный слой 43 имеют направление намагничивания, равное направлению в плоскости.

Запоминающий слой 41 имеет переменное направление намагничивания (направление намагничивания инвертируется). Опорный слой 43 имеет неизменяемое направление намагничивания (направление намагничивания является фиксированным). Опорный слой 43 задается с возможностью иметь энергию перпендикулярной магнитной анизотропии, в определенной степени превышающую энергию перпендикулярной магнитной анизотропии запоминающего слоя 41. Магнитная анизотропия может задаваться посредством регулирования состава материалов или толщин пленки. Ток инверсии направления намагничивания в запоминающем слое 41 уменьшается, как описано выше, таким образом, что ток инверсии направления намагничивания в опорном слое превышает ток инверсии направления намагничивания в запоминающем слое 41. Таким образом, результирующий MTJ-элемент 30 содержит запоминающий слой 41 с направлением намагничивания, которое является переменным относительно предварительно определенного тока записи, и опорный слой 43 с направлением намагничивания, которое является неизменяемым относительно предварительно определенного тока записи.

Настоящий вариант осуществления использует схему записи с переносом спина, в которой ток записи проходит непосредственно через MTJ-элемент 30, чтобы управлять состоянием намагничивания MTJ-элемента 30. MTJ-элемент 30 может быть переведен в состояние с низким сопротивлением или в состояние с высоким сопротивлением в зависимости от того, находится корреляция между намагничиванием в запоминающем слое 41 и намагничиванием в опорном слое 43 в параллельном состоянии или в антипараллельном состоянии.

Когда ток записи, вытекающий из запоминающего слоя 41 к опорному слою 43, проходит через MTJ-элемент 30, корреляция между намагничиванием в запоминающем слое 41 и намагничиванием в опорном слое 43 переводится в параллельное состояние. В параллельном состоянии MTJ-элемент 30 имеет наименьшее значение сопротивления и задается в состояние с низким сопротивлением. Состояние с низким сопротивлением MTJ-элемента 30 задается, например, в качестве данных в "0".

С другой стороны, когда ток записи, вытекающий из опорного слоя 43 к запоминающему слою 41, проходит через MTJ-элемент 30, корреляция между намагничиванием в запоминающем слое 41 и намагничиванием в опорном слое 43 переводится в антипараллельное состояние. В антипараллельном состоянии MTJ-элемент 30 имеет наибольшее значение сопротивления и задается в состояние с высоким сопротивлением. Состояние с высоким сопротивлением MTJ-элемента 30 задается, например, в качестве данных в "1".

Таким образом, MTJ-элемент 30 может использоваться в качестве запоминающего элемента, который может сохранять 1-битовые данные (двоичные данные). Назначение состояния сопротивления и данные для MTJ-элемента 30 могут быть необязательно заданы.

Данные считываются из MTJ-элемента 30 посредством приложения тока считывания к MTJ-элементу 30 и определения значения сопротивления MTJ-элемента 30 на основе тока считывания, протекающего через MTJ-элемент 30 в ходе приложения напряжения считывания. Ток считывания задается равным значению, в определенной степени меньшему порогового значения, за рамками которого намагничивание инвертируется посредством переноса спина.

2. Работа

Далее описывается работа MRAM 10, имеющего такую конфигурацию, как описано выше. Фиг. 5 является временной диаграммой, показывающей работу MRAM 10. MRAM 10 работает в синхронизме с синхросигналом CLK, отправленным из внешней схемы.

Когда емкость хранения матрицы 11 ячеек запоминающего устройства растет, чтобы увеличивать число строк, которое может указываться посредством адреса RA строки в операции считывания данных и операции записи данных, число битов в адресе RA строки, соответственно, увеличивается. Таким образом, в настоящем варианте осуществления, адрес RA строки для использования при выборе из строк (числовых шин) в матрице 11 ячеек запоминающего устройства разделен на первый адрес RA1 строки и второй адрес RA2 строки, которые отдельно вводятся в MRAM 10 из внешней схемы. Иными словами, первый адрес RA1 строки и второй адрес RA2 строки вводятся из внешней схемы в MRAM 10 в этом порядке способом разделения времени.

Кроме того, в настоящем варианте осуществления, если первый адрес RA1 строки принимается, выполняется операция определения резервирования, и после этого принимается второй адрес RA2 строки. Когда получается весь адрес RA<0:a> строки, выполняются операции, отличные от операции определения резервирования, которые используют адрес RA строки. Таким образом, первый адрес RA1 строки выполнен с возможностью включать в себя адрес RA<x:y> резервной строки. Второй адрес RA2 строки содержит весь адрес RA<0:a> строки за исключением первого адреса RA1 строки.

Во-первых, контроллер 22 принимает команду P-Act предварительной активации, и буфер 23 адресов строк принимает первый адрес RA1 строки из внешней схемы. Команда P-Act предварительной активации вводится до команды Act активации, описанной ниже, и используется для того, чтобы вводить первый адрес RA1 строки в MRAM 10. Затем, буфер 23 адресов строк отправляет первый адрес RA1 строки в блок 20 плавких перемычек и схему 21 определения резервирования.

Затем, блок 20 плавких перемычек и схема 21 определения резервирования выполняют операцию определения резервирования для определения того, совпадает или нет адрес сбоя, сохраненный в наборе FS плавких перемычек, с адресом RA<x:y> резервной строки, включенным в первый адрес RA1 строки. В частности, каждый набор FS плавких перемычек сравнивает адрес сбоя, сохраненный в элементах-плавких перемычках, с адресом RA<x:y> резервной строки. Если адреса совпадают, набор FS плавких перемычек выводит сигнал HIT с H-уровнем, а если адреса не совпадают, набор FS плавких перемычек выводит сигнал HIT с L-уровнем. Сигнал HIT отправляется в декодер 19 резервных строк.

Кроме того, если какой-либо из сигналов HIT<0:n> имеет H-уровень, схема 21 определения резервирования выводит сигнал HITSUMB с L-уровнем. Если все сигналы HIT<0:n> имеют L-уровень, т.е. замена резервной областью 12 не выполняется, резервная область 12 выводит сигнал HITSUMB с H-уровнем. Сигнал HITSUMB отправляется в декодер 18 нормальных строк.

Затем, контроллер 22 принимает команду Act активации из внешней схемы. Буфер 23 адресов строк принимает второй адрес RA2 строки из внешней схемы. Команда Act активации дает возможность выполнения процесса активации одной (выбранной числовой шине) из множества числовых шин в выбранном банке и считывания данных из матрицы 11 ячеек запоминающего устройства в страничный буфер 16. Фактически, одно MRAM 10, показанное на фиг. 1, соответствует одному банку, и множество банков монтируются на подложке, чтобы формировать энергонезависимое запоминающее устройство. В это время получается весь адрес RA<0:a> строки, содержащий первый адрес RA1 строки и второй адрес RA2 строки. Адрес RA<0:a> строки затем отправляется из буфера 23 адресов строк в декодер 18 нормальных строк.

Затем, при условии, что сигнал HITSUMB имеет H-уровень, декодер 18 нормальных строк использует адрес RA<0:a> строки для того, чтобы активировать одну из числовых шин NWL<0:m>. Если выбранная числовая шина является сбойной (сигнал HITSUMB имеет L-уровень), числовая шина заменяется резервной областью 12. В частности, декодер 19 резервирования активирует одну из числовых шин RWL<0:n> на основе сигнала HIT<0:n>. Затем, усилитель 13 считывания считывает данные из матрицы 11 ячеек запоминающего устройства. Считываемые данные записываются в страничный буфер 16 через ECC-схему 15.

Затем, контроллер 22 принимает команду считывания или команду записи (R/W) из внешней схемы. Буфер 24 адресов столбцов принимает адрес CA столбца из внешней схемы. После этого контроллер 22 выполняет операцию считывания или операцию записи для столбца, обозначенного посредством адреса CA столбца.

Преимущества

Как подробно описано выше, первый вариант осуществления заключается в следующем. Первый адрес RA1 строки и второй адрес RA2 строки, включенные в адрес RA строки, вводятся в MRAM 10 в этом порядке способом разделения времени. Первый адрес RA1 строки, который вводится раньше, выполнен с возможностью включать в себя весь резервный адрес, связанный с операцией замены при резервировании. Затем операция замены при резервировании начинается сразу после приема первого адреса RA1 строки.

Таким образом, первый вариант осуществления дает возможность выполнения операции определения резервирования до того, как принимается команда Act активации, обеспечивая явное уменьшение времени, требуемого для определения резервирования. Это обеспечивает уменьшение времени tRCD задержки (задержки RAS-CAS) от приема команды Act активации до приема команды считывания или команды записи, за счет этого повышая скорость работы MRAM 10.

Второй вариант осуществления

Согласно второму варианту осуществления, адрес RA строки для использования при выборе из строк (числовых шин) в матрице 11 ячеек запоминающего устройства разделен на первый адрес RA1 строки и второй адрес RA2 строки. Первый адрес RA1 строки и второй адрес RA2 строки отдельно вводятся в MRAM 10 из внешней схемы. Иными словами, первый адрес RA1 строки и второй адрес RA2 строки вводятся из внешней схемы в MRAM 10 в этом порядке способом разделения времени.

Кроме того, согласно настоящему варианту осуществления, первый адрес RA1 строки выполнен с возможностью включать в себя часть адреса RA<x:y> резервной строки. Второй адрес RA2 строки содержит весь адрес RA<0:a> строки за исключением первого адреса RA1 строки. Иными словами, второй адрес RA2 строки также включает в себя часть адреса RA<x:y> резервной строки. После того как первый адрес RA1 строки принимается, выполняется часть операции определения резервирования. Затем, после приема второго адреса RA2 строки для того, чтобы получать весь адрес RA<0:a> строки, MRAM выполняет всю оставшуюся часть операции определения резервирования и операций, отличных от операции определения резервирования, которые используют адрес RA строки.

Фиг. 6 является временной диаграммой, показывающей работу MRAM 10 согласно второму варианту осуществления. Во-первых, контроллер 22 принимает команду P-Act предварительной активации из внешней схемы, и буфер 23 адресов строк принимает первый адрес RA1 строки из внешней схемы. Затем буфер 23 адресов строк отправляет первый адрес RA1 строки в блок 20 плавких перемычек и схему 21 определения резервирования.

Затем блок 20 плавких перемычек и схема 21 определения резервирования выполняют операцию определения резервирования для определения того, совпадает или нет адрес сбоя, сохраненный в наборе FS плавких перемычек, с частью адреса RA<x:y> резервной строки, включенного в первый адрес RA1 строки, т.е. блок 20 плавких перемычек и схема 21 определения резервирования выполняют часть операции определения резервирования ("PD op1" на фиг. 6).

Затем контроллер 22 принимает команду Act активации из внешней схемы. Буфер 23 адресов строк принимает второй адрес RA2 строки из внешней схемы. В это время весь адрес RA<0:a> строки, содержащий первый адрес RA1 строки и второй адрес RA2 строки, получается и отправляется из буфера 23 адресов строк в декодер 18 нормальных строк. Кроме того, вся оставшаяся часть адреса RA<x:y> резервной строки отправляется из буфера 23 адресов строк в блок 20 плавких перемычек и схему 21 определения резервирования.

Затем блок 20 плавких перемычек и схема 21 определения резервирования используют адрес RA<x:y> резервной строки для того, чтобы выполнять всю оставшуюся часть операции определения резервирования ("RD op2" на фиг. 6).

Затем декодер 18 нормальных строк использует адрес RA<0:a> строки для того, чтобы активировать выбранную числовую шину. Если выбранная числовая шина является сбойной, числовая шина заменена резервной областью 12. После этого усилитель 13 считывания считывает данные из матрицы 11 ячеек запоминающего устройства, и считываемые данные записываются в страничный буфер 16 через ECC-схему 15. Последующая работа является идентичной соответствующей работе в первом варианте осуществления.

Пример конфигурации блока 20 плавких перемычек и схемы 21 определения резервирования

Далее описывается пример конфигурации блока 20 плавких перемычек и схемы 21 определения резервирования. Фиг. 7 является принципиальной схемой блока 20 плавких перемычек и схемы 21 определения резервирования. Часть схемы по фиг. 7 соответствует критическому пути для операции определения резервирования. Уменьшение времени, требуемого для обработки в части схемы, является важным.

В настоящем варианте осуществления, первые наборы FS1<0:n> плавких перемычек из наборов FS<0:n> плавких перемычек, которые соответствуют адресу резервной строки (части адреса RA<x:y> резервной строки), включенному в первый адрес RA1 строки, совместно размещаются на коротком расстоянии друг от друга. Кроме того, вторые наборы FS2<0:n> плавких перемычек в наборах FS<0:n> плавких перемычек, которые соответствуют адресу резервной строки (всей оставшейся части адреса RA<x:y> резервной строки), включенному во второй адрес RA2 строки, совместно размещаются на коротком расстоянии друг от друга. Кроме того, первые наборы FS1<0:n> плавких перемычек, соответствующие первому адресу RA1 строки, который вводится раньше и заключает в себе относительно достаточное количество времени для вычисления, размещаются на удалении от схемы (логического элемента 53 <0:n> "НЕ-ИЛИ"), выполненной с возможностью вычислять сигнал HIT<0:n>, и схемы (логического элемента 54 "НЕ-ИЛИ"), выполненной с возможностью вычислять сигнал HITSUMB. Вторые наборы FS2<0:n> плавких перемычек, соответствующие второму адресу RA1 строки, который вводится позднее, размещаются ближе к логическому элементу 53 <0:n> "НЕ-ИЛИ" и логическому элементу 54 "НЕ-ИЛИ", чем первые наборы FS1<0:n> плавких перемычек.

Таким образом, когда вводится второй адрес RA2 строки, операция определения резервирования ("RD op1" на фиг. 7), связанная с первым адресом RA1 строки, уже завершена. Следовательно, операция определения резервирования ("RD op2" на фиг. 6), выполняемая после ввода команды Act активации, представляет собой арифметический процесс, связанный только со вторыми наборами FS плавких перемычек, размещаемыми близко к логическому элементу 54 "НЕ-ИЛИ". Это обеспечивает уменьшение времени, требуемого для операции определения резервирования, выполняемой после ввода команды Act активации.

Преимущества

Как подробно описано выше, согласно второму варианту осуществления, первый адрес RA1 строки и второй адрес RA2 строки, включенные в адрес RA строки, вводятся в MRAM 10 в этом порядке способом разделения времени. Первый адрес RA1 строки, который вводится раньше, выполнен с возможностью включать в себя часть резервного адреса, связанную с операцией замены при резервировании. Затем операция определения резервирования начинается сразу после приема первого адреса RA1 строки.

Таким образом, второй вариант осуществления дает возможность выполнения части операции определения резервирования до того, как принимается команда Act активации, обеспечивая явное уменьшение времени, требуемого для определения резервирования. Это обеспечивает уменьшение времени tRCD задержки, за счет этого повышая скорость работы MRAM 10.

Кроме того, первые наборы FS1<0:n> плавких перемычек, соответствующие первому адресу RA1 строки, размещаются на удалении от схемы, выполненной с возможностью вычислять сигнал HIT<0:n>, и схемы, выполненной с возможностью вычислять сигнал HITSUMB. Арифметический процесс, связанный с первыми наборами FS1<0:n> плавких перемычек, выполняется раньше. Это обеспечивает дополнительное уменьшение времени, требуемого для операции определения резервирования, связанной со вторым адресом RA2 строки, который вводится позднее.

Каждый из вышеописанных вариантов осуществления выполнен с возможностью разделять целый адрес RA строки на два адреса и вводить адреса способом разделения времени. Тем не менее, варианты осуществления не ограничены этой конфигурацией. Целый адрес строки может быть разделен на три или более адреса, которые затем вводятся способом разделения времени. В связи с этим адрес резервной строки может быть разделен на два или более адреса перед вводом.

Кроме того, каждый из вышеописанных вариантов осуществления рассматривает MRAM в качестве примера полупроводникового запоминающего устройства. Тем не менее, варианты осуществления не ограничены MRAM, а являются применимыми к любому другому запоминающему устройству, такому как SDRAM (синхронное DRAM).

Хотя описаны конкретные варианты осуществления, эти варианты осуществления представлены только в качестве примера и не имеют намерение ограничивать объем изобретения. Фактически, новые варианты осуществления, описанные в данном документе, могут быть осуществлены во множестве других форм; кроме того, различные пропуски, подстановки и изменения в форме вариантов осуществления, описанных в данном документе, могут осуществляться без отступления от сущности изобретения. Прилагаемая формула изобретения и ее эквиваленты имеют намерение охватывать такие формы и модификации, как попадающие в пределы объема и сущности изобретения.