Результат интеллектуальной деятельности: ГЕНЕРАТОР СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Изобретение относится к области вычислительной техники и может быть использовано автономно или в комплексе для вычисления ортогонального базиса положительно определенной симметрической матрицы, который может быть использован для передачи информации в системе цифровой радиосвязи с множественным доступом с кодовым разделением каналов (CDMA - code division multiply access), например, в системе сотовой связи 3 и 4 поколения, радиоканальной системе охраны, навигационном аппаратно-программном комплексе.

Уровень техники

Известен генератор дискретных базисных функций (Генератор функций Уолша: пат. №1501019 А2 СССР, МПК G06F 1/02), содержащий два счетчика, группу элементов И и группу сумматоров по модулю два, а также многовходовый сумматор по модулю два.

Недостатком известного генератора, как и других генераторов функций Уолша, генераторов функций Хаара являются узкие функциональные возможности, заключающиеся в том, что число базисных функций не может быть отличным от 2m (где m - натуральное число).

Кроме этого, указанные генераторы имеют малый набор значений периодов генерируемых функций и малое число значений базисных функций.

Известно также устройство для операций над матрицами (Устройство для операций над матрицами: пат. №1443003 А1 СССР, МПК G06F 15/347), содержащее N2 операционных блоков, N-1 элементов задержки и распределитель импульсов.

Однако известное устройство осуществляет только решение систем линейных уравнений и обращение матриц. Это устройство обладает ограниченными функциональными возможностями, поскольку не может генерировать дискретные базисные функции.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство генерации ортогональных кодов (Генератор функций Попенко-Турко: пат. №1753464 А1 СССР, МПК G06F1/02), предназначенное для вычисления ортогонального базиса положительно определенной симметрической матрицы с действительными положительными коэффициентами, принадлежащими интервалу (0; 1).

Недостатками генератора функций Попенко-Турко является отсутствие автоматического поступления входных данных, а также отсутствие возможности стохастического формирования ансамблей ортогональных кодов различной структуры.

Раскрытие изобретения

Техническим результатом изобретения является автоматизация процесса формирования исходных данных и обеспечение стохастического формирования систем стохастических ортогональных кодов.

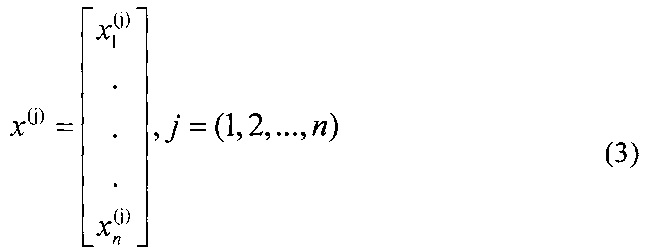

Генератор функций Попенко-Турко вычисляет ортогональный базис для матрицы вида

Для положительно определенной симметрической матрицы это будет означать:

1) любой коэффициент матрицы вида (1) удовлетворяет условию aij>0, i, j ∈ [1, n];

2) соблюдается свойство симметричности для коэффициентов матрицы, не принадлежащих главной диагонали aij= aji, i, j ∈ [1, n], i≠j.

Для формирования матрицы вида (1) необходимо ввести лишь элементы верхней или нижней треугольной матрицы. Формула расчета количества элементов треугольной матрицы порядка n для получения квадратной матрицы вида (1) порядка n выглядит так:

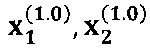

Если действительная матрица А=[aij], i, j ∈ [1, n] - симметрическая и положительно определенная порядка n вида (1), то собственные векторы этой матрицы

могут быть взяты действительными и они удовлетворяют условиям ортогональности [Демидович Б.П., Марон И.А. Основы вычислительной математики. М.: Наука, 1970].

Таким образом, положительно определенная симметрическая матрица имеет n собственных векторов.

Для спектрального анализа сигналов используется сравнительно небольшое количество полных и ортогональных систем базисных функций. При этом наиболее эффективно разложение сигналов по системам кусочно-постоянных функций, например функций Уолша. Поскольку собственные векторы действительной симметрической матрицы, соответствующие различным собственным значениям, ортогональны между собой, то в качестве системы базисных функций может быть использован ортогональный базис, состоящий из собственных векторов симметрической матрицы вида (1).

Предлагаемый генератор стохастических ортогональных кодов имеет расширенную область применения, заключающуюся в генерировании стохастических ортогональных дискретных базисных функций, число которых может быть отлично от 2m (m - натуральное число), имеющих широкий набор значений периодов генерируемых функций и большое число значений базисных функций за счет автоматизации присвоения входных псевдослучайных значений симметрической матрицы вида (1).

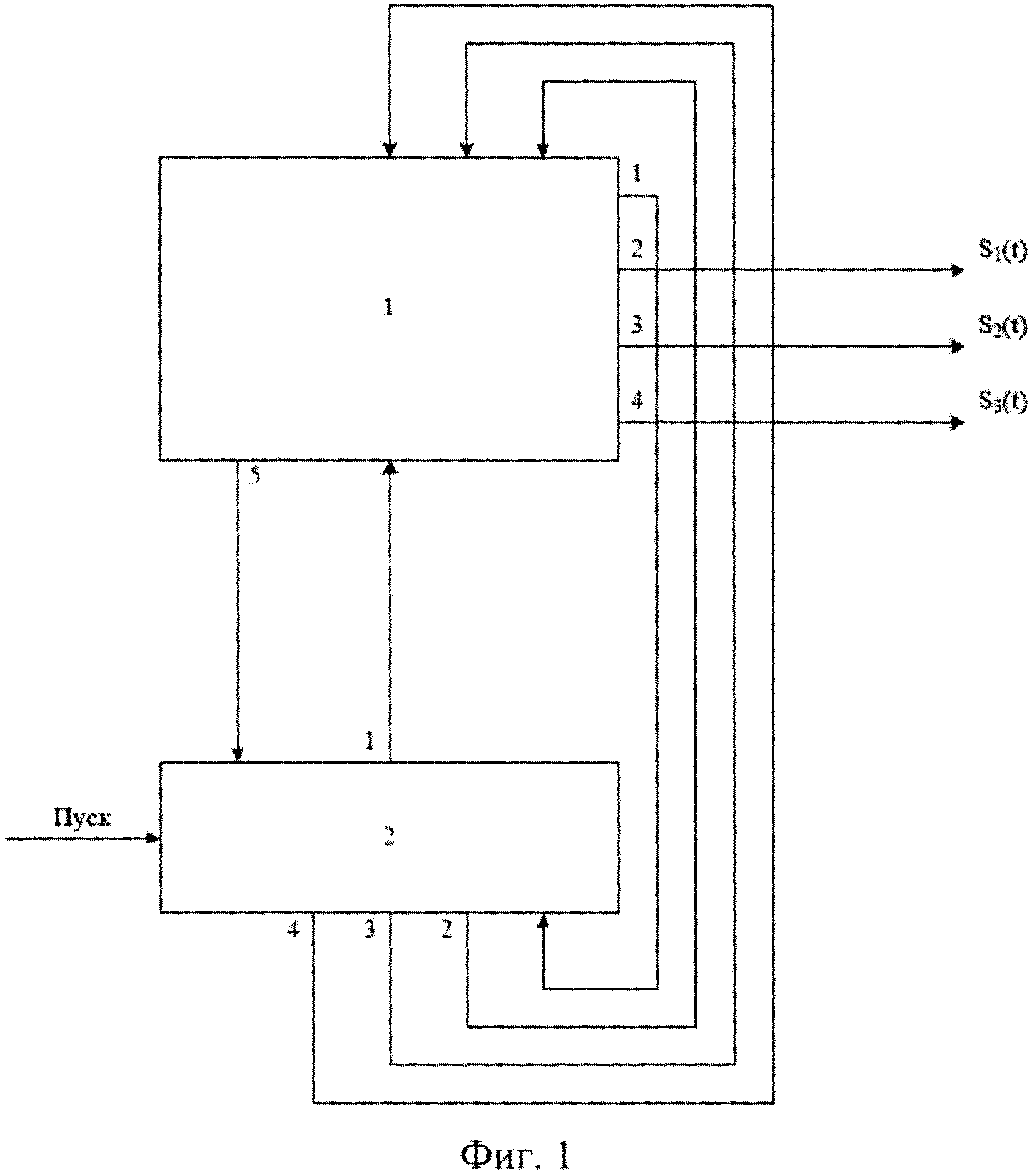

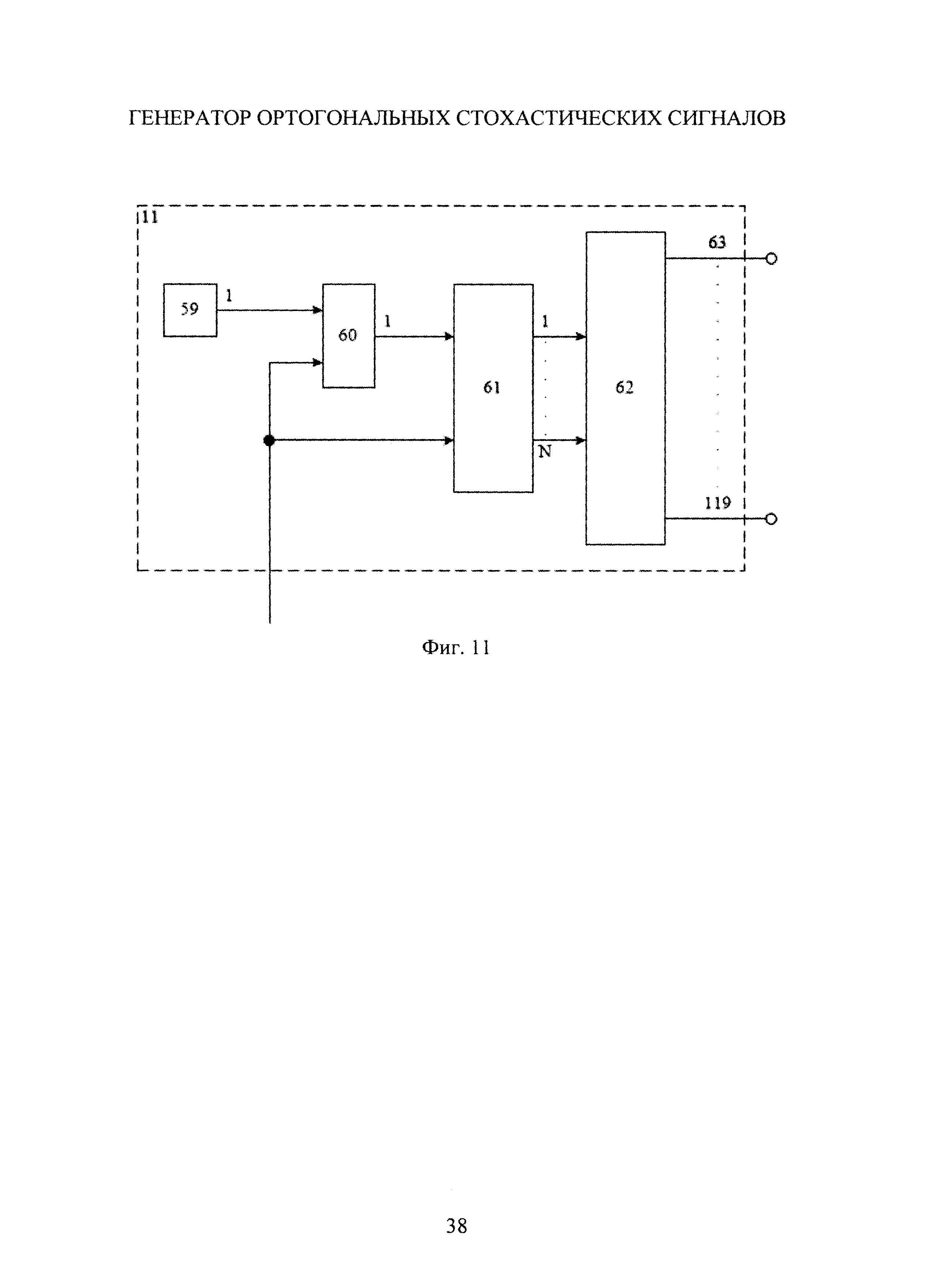

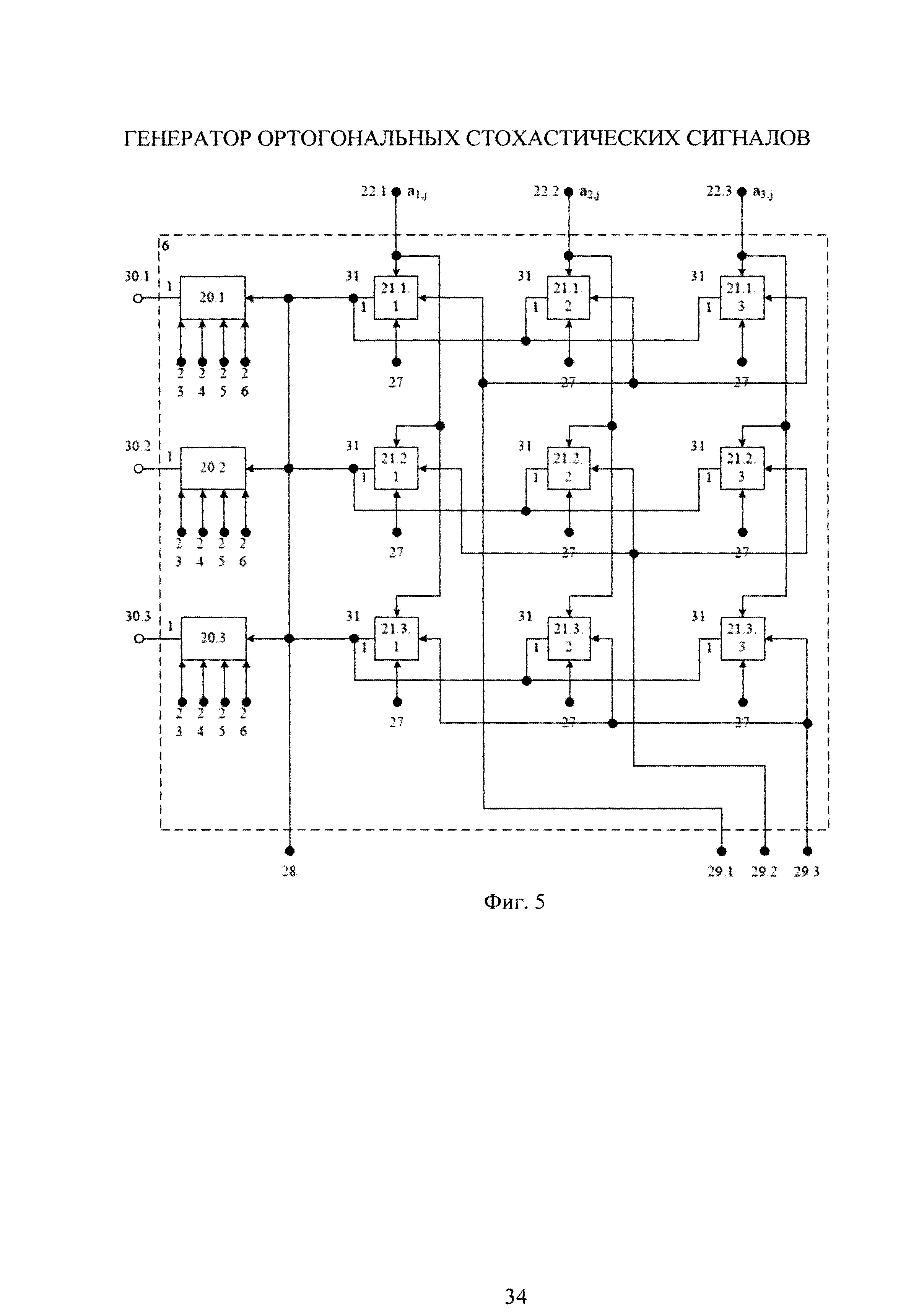

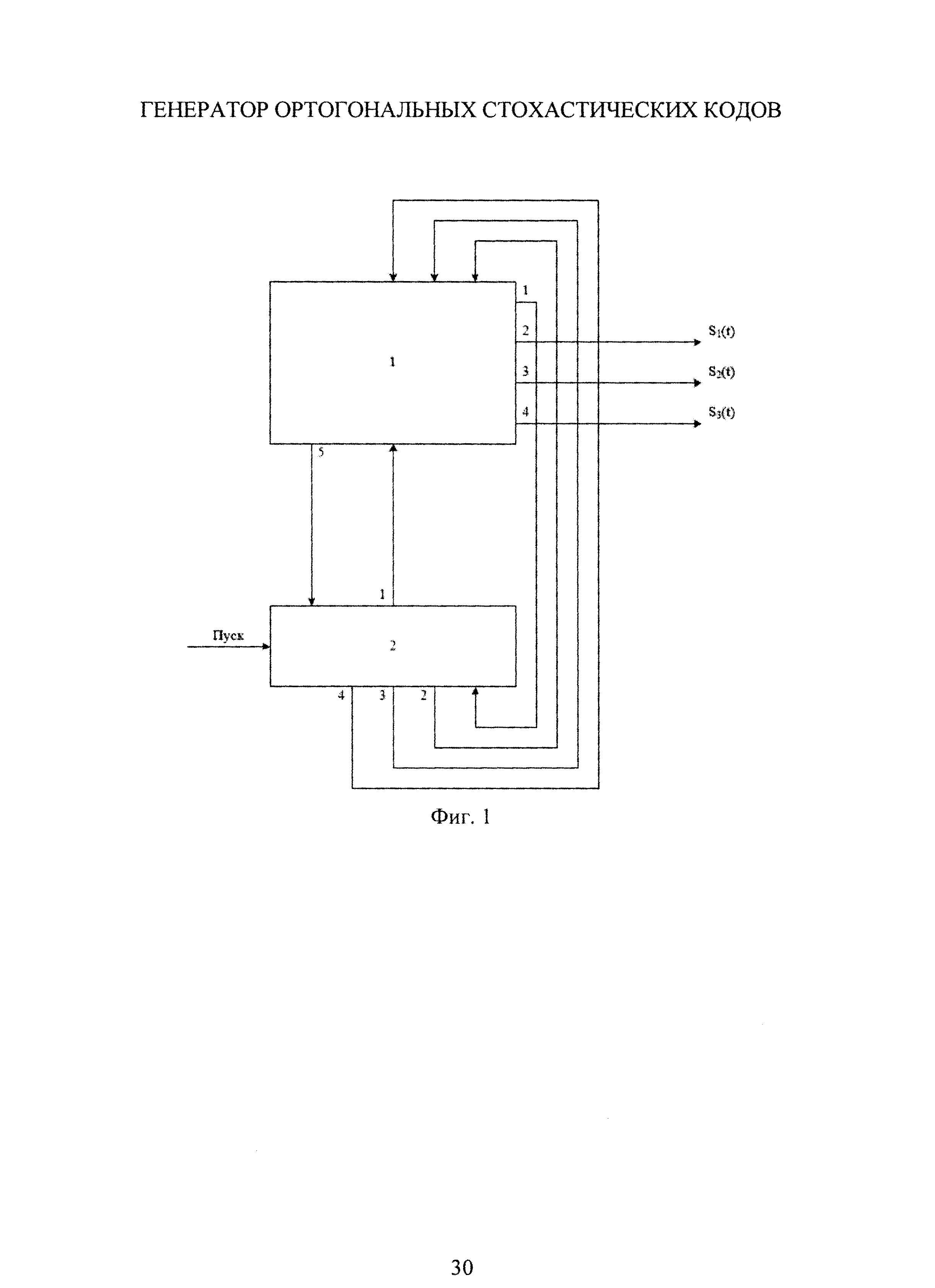

Технический результат достигается с помощью того, что в функциональную схему генератора 1 функций Попенко-Турко (ГФПТ), состоящего из блоков 3.1.1-3.1.3, 3.2.1-3.2.3, 3.3.1-3.3.3 вычислителя, состоящих из первого сумматора-накопителя 17, умножителя 18, сумматора 19, блоков 4.1.1, 4.1.2, 4.2.1 элементов И, блоков 5.1.1, 5.1.2, 5.2.1 деления, первого блока 6 памяти, состоящего из блоков 20.1-20.3 формирования коэффициентов системы линейных уравнений, элементов 21.1.1-21.1.3, 21.2.1-21.2.3, 21.3.1-21.3.3 памяти, первого двухразрядного разряда регистра 7 сдвига, второго двухразрядного разряда регистра 7 сдвига, операционных блоков 8.1.1, 8.1.2, 8.2.1, 8.2.2, причем операционные блоки 8.1.1 и 8.1.2 состоят из входного 44 регистра, блока 45 деления, операционные блоки 8.2.1 и 8.2.2 состоят из регистра 47 второго сомножителя, выходного 48 регистра, вычитателя 49, умножителя 50, регистра 51 первого сомножителя, второго блока 9 памяти, состоящего из блоков 20.4-20.6 формирования коэффициентов системы линейных уравнений, причем каждый из блоков 20.1-20.6 формирования коэффициентов системы линейных уравнений состоит из регистра 40 памяти, умножителя 41, управляемого 42 инвертора, второго сумматора - накопителя 43, элементов 32.1.1-32.1.3, 32.2.1-32.2.3, 32.3.1-32.3.3 памяти, элемента 10.1 задержки, состоящего из регистров 55 и 56, блока 11 синхронизации, состоящего из генератора 59 синхроимпульсов, элемента 60 И, счетчика 61 тактов, блока 62 памяти микрокоманд, первого разряда трехразрядного регистра 12 сдвига, второго разряда трехразрядного регистра 12 сдвига, третьего разряда трехразрядного регистра 12 сдвига, введен блок 2 стохастического формирования коэффициентов симметрической матрицы (блок СФКСМ), состоящий из микроконтроллера 13, генератора 14 псевдослучайных чисел (ПСЧ), блока 15 накопителя, блоков 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 N-разрядного (N-разрядность генерируемых генератором 14 ПСЧ псевдослучайных коэффициентов матрицы) оперативного запоминающего устройства (ОЗУ), причем

первый выход ГФПТ 1 подключен ко второму входу блока 2 СФКСМ, второй выход ГФПТ 1 выводит компоненты первого собственного вектора,

первый выход блока 3.1.1 вычислителя подключен к третьему входу блока 3.1.2 вычислителя, который подключен ко второму входу сумматора 19, входящего в состав блока 3.1.2 вычислителя, второй выход блока 3.1.1 вычислителя подключен к первому входу блока 3.2.1 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.2.1 вычислителя,

первый выход блока 3.1.2 вычислителя подключен к третьему входу блока 3.1.3 вычислителя, который подключен ко второму входу сумматора 19, входящего в состав блока 3.1.3 вычислителя, второй выход блока 3.1.2 вычислителя подключен к первому входу блока 3.2.2 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.2.2 вычислителя,

первый выход блока 3.1.3 вычислителя подключен к первому входу блока 5.1.1 деления, второй выход блока 3.1.3 вычислителя подключен к первому входу блока 3.2.3 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.2.3 вычислителя,

первый вход блока 3.2.1 вычислителя подключен к третьему входу блока 3.2.2 вычислителя, который подключен ко второму входу сумматора 19, входящего в состав блока 3.2.2 вычислителя, второй выход блока 3.2.1 подключен к первому входу блока 3.3.1 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.3.1 вычислителя,

первый выход блока 3.2.2 вычислителя подключен к третьему входу блока 3.2.3 вычислителя, который подключен ко второму входу сумматора 19, который входит в состав блока 3.2.3 вычислителя, и первому входу блока 5.2.1 деления, второй выход блока 3.2.2 вычислителя подключен к первому входу блока 3.3.2 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.3.2 вычислителя,

первый выход блока 3.2.3 вычислителя подключен к первому входу блока 5.1.2 деления, второй выход блока 3.2.3 подключен к первому входу блока 3.3.3 вычислителя, который подключен ко второму входу умножителя 18, входящего в состав блока 3.3.3 вычислителя,

первый выход блока 3.3.1 вычислителя подключен к третьему входу блока 3.3.2 вычислителя, который подключен ко второму входу сумматора 19, входящего в состав блока 3.3.2 вычислителя, второй выход блока 3.3.1 подключен к информационному входу 33.1 второго блока 9 памяти, который подключен к первому входу элементов 32.1.1, 32.2.1, 32.3.1 памяти, входящих в состав второго блока 9 памяти,

первый выход блока 3.3.2 вычислителя подключен к третьему входу блока 3.3.3 вычислителя, который подключен ко второму входу сумматора 19, входящего в состав блока 3.3.3 вычислителя, второй выход блока 3.3.2 подключен к информационному входу 33.2 второго блока 9 памяти, который подключен к первому входу элементов 32.1.2, 32.2.2, 32.3.2 памяти, входящих в состав второго блока 9 памяти,

первый выход блока 3.3.3 вычислителя подключен ко второму входу блока 5.1.1 деления и ко второму входу блока 5.1.2 деления, второй выход блока 3.3.3 вычислителя подключен к информационному входу 33.3. второго блока 9 памяти, который подключен к первому входу элементов 32.1.3, 32.2.3, 32.3.3 памяти, входящих в состав второго блока 9 памяти,

первый выход блока 4.1.1 элементов И подключен к первому входу блока 3.2.1 вычислителя,

первый выход блока 4.1.2 элементов И подключен к первому входу блока 3.3.2 вычислителя,

первый выход блока 4.2.1 элементов И подключен к первому входу блока 3.2.1 вычислителя,

первый выход блока 5.1.1 деления подключен к первому входу блока 4.1.1 элементов И,

первый выход блока 5.1.2 деления подключен к первому входу блока 4.1.2 элементов И,

первый выход блока 5.2.1 деления подключен к первому входу блока 4.2.1 элементов И,

первый выход первого блока 6 памяти является информационным выходом 30.1 первого блока 6 памяти и подключен ко вторым входам блоков 3.1.1, 3.1.2, 3.1.3 вычислителя, которые подключены к первому входу первого сумматора-накопителя 17, входящего в состав блоков вычислителя 3.1.1, 3.1.2, 3.1.3, второй выход первого блока 6 памяти является информационным выходом 30.2 первого блока 6 памяти и подключен ко вторым входам блока 3.2.1 вычислителя, блока 3.2.2 вычислителя и блока 3.2.3 вычислителя, которые подключены к первому входу первого сумматора-накопителя 17, входящего в состав блоков вычислителя 3.2.1, 3.2.2, 3.2.3, третий выход первого блока 6 памяти является информационным выходом 30.3 первого блока 6 памяти и подключен ко вторым входам блока 3.3.1 вычислителя, блока 3.3.2 вычислителя и блока 3.3.3 вычислителя, которые подключены к первому входу первого сумматора-накопителя 17, входящего в состав блоков вычислителя 3.3.1, 3.3.2, 3.3.3,

первый выход первого разряда двухразрядного регистра 7 сдвига подключен ко второму входу блока 4.2.1 элементов И,

первый выход второго разряда двухразрядного регистра 7 сдвига подключен ко второму входу блока 4.1.1 элементов И и второму входу блока 4.1.2 элементов И,

первый выход операционного блока 8.1.1 подключен к первому входу операционного блока 8.2.1, который подключен к первому входу регистра 47 второго сомножителя, входящего в состав операционного блока 8.2.1,

первый выход операционного блока 8.1.2 подключен к информационному входу 33.3 второго блока 9 памяти, который подключен к первому входу элементов 32.1.3, 32.2.3, 32.3.3 памяти, входящих в состав второго блока 9 памяти, второй выход операционного блока 8.1.2 подключен к первому входу операционного блока 8.2.2, который подключен к первому входу регистра 47 второго сомножителя, входящего в состав операционного блока 8.2.2,

первый выход операционного блока 8.2.1 подключен ко второму входу операционного блока 8.1.2, который подключен к первому входу входного 44 регистра и второму входу блока 45 деления, входящих в состав операционного блока 8.1.2, второй выход операционного блока 8.2.1 подключен к первому входу элемента 10.1 задержки,

первый выход операционного блока 8.2.2 подключен к информационному входу 33.2 второго блока 9 памяти, который подключен к первому входу элементов 32.1.2, 32.2.2, 32.3.2 памяти, входящих в состав второго блока 9 памяти,

первый выход второго блока 9 памяти является информационным выходом 38.1 второго блока 9 памяти и выводит элементы первого собственного вектора ортогонального базиса матрицы А вида (1), а также подключен к дополнительному информационному входу 28 первого блока 6 памяти, который подключен к первым входам блоков 20.1-20.3 формирования коэффициентов СЛУ в составе первого блока 6 памяти, и второму входу операционного блока 8.1.1, который подключен к первому входу входного 44 регистра и второму входу блока 45 деления, входящих в состав операционного блока 8.1.1,

второй выход второго блока 9 памяти является информационным выходом 38.2 второго блока 9 памяти и выводит элементы второго собственного вектора ортогонального базиса матрицы А вида (1), а также подключен к третьему входу операционного блока 8.2.1, который подключен к первому входу регистра 51 первого сомножителя и второму входу вычитателя 49, входящих в состав операционного блока 8.2.1,

третий выход второго блока 9 памяти является информационным выходом 38.3 второго блока 9 памяти и выводит элементы третьего собственного вектора ортогонального базиса матрицы А вида (1),

первый выход элемента 10.1 задержки подключен к третьему входу операционного блока 8.2.2, который подключен к первому входу регистра 51 первого сомножителя и второму входу вычитателя 49, входящих в состав операционного блока 8.2.2,

выход 63 блока 11 синхронизации подключен к управляющему входу 46 операционного блока 8.1.1; выход 64 блока 11 синхронизации подключен к управляющему входу 54 операционного блока 8.2.1; выход 65 блока 11 синхронизации подключен к входу 46 операционного блока 8.1.2; выход 66 блока 11 синхронизации подключен к входу 54 операционного блока 8.2.2; выход 67 блока 11 синхронизации подключен к управляющим входам 53 операционных блоков 8.2.1, 8.2.2, к управляющим входам 52 операционных блоков 8.2.1, 8.2.2, к синхровходам 57 и 58 блока 10.1 задержки; выход 68 блока 11 синхронизации подключен к первому (тактовому) входу двухразрядного регистра 7 сдвига; выход 69 блока 11 синхронизации подключен к управляющей шине 29.1 первого блока 6 памяти, подключенной ко вторым входам элементов 21.1.1-21.1.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.1.1-16.1.3 ОЗУ; выход 70 блока 11 синхронизации подключен к управляющей шине 29.2 первого блока 6 памяти, подключенной ко вторым входам элементов 21.2.1-21.2.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.2.1-16.2.3 ОЗУ; выход 71 блока 11 синхронизации подключен к управляющей шине 29.3 первого блока 6 памяти, подключенной ко вторым входам элементов 21.3.1-21.3.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.3.1-16.3.3 ОЗУ; выход 72 блока 11 синхронизации подключен к управляющей шине 35.1 блока 11 памяти, подключенной ко вторым входам элементов 32.1.1-32.1.3 памяти в составе второго блока 9 памяти; выход 73 блока 11 синхронизации подключен к управляющей шине 36.1 второго блока 9 памяти, подключенной ко вторым входам элементов 32.2.1-32.2.2 памяти в составе второго блока 9 памяти; выход 74 блока 11 синхронизации подключен к шине 36.2 второго блока 9 памяти, подключенной ко второму входу элемента 32.2.3 памяти в составе второго блока 9 памяти; выход 75 блока 11 синхронизации подключен к шине 37.1 второго блока 9 памяти, подключенной ко второму входу элемента 32.3.1 памяти в составе второго блока 9 памяти; выход 76 блока 11 синхронизации подключен к шине 37.2 второго блока 9 памяти, подключенной ко вторым входам элементов памяти 32.3.2-32.3.3 памяти в составе второго блока 9 памяти; выходы 77-80 блока 11 синхронизации подключены к управляющим входам блока 20.1, входящего в состав первого блока 6 памяти; выходы 81-84 блока 11 синхронизации подключены к управляющим входам блока 20.2, входящего в состав первого блока 6 памяти; выходы 85-88 блока 11 синхронизации подключены к управляющим входам блока 20.3, входящего в состав первого блока 6 памяти; выходы 89-92 блока 11 синхронизации подключены к управляющим входам блока 20.4, входящего в состав второго блока 9 памяти; выходы 93-96 блока 11 синхронизации подключены к управляющим входам блока 20.5, входящего в состав второго блока 9 памяти; выходы 97-100 блока 11 синхронизации подключены к управляющим входам блока 20.6, входящего в состав второго блока 9 памяти; выходы 101-109 блока 11 синхронизации подключен к управляющим входам 27 считывания элементов 21 памяти, входящих в состав первого блока 6 памяти; выходы 110-118 блока 11 синхронизации подключены к управляющим входам 34 считывания элементов 32.1.1-32.1.3, 30.2.1-32.2.3, 32.3.1-32.3.3 памяти, входящих в состав второго блока 9 памяти; выход 119 блока 11 синхронизации подключен к первому (тактовому) входу трехразрядного трехразрядного регистра 12 сдвига,

первый выход первого разряда трехразрядного регистра 12 сдвига подключен к входам 34 управления считыванием элементов памяти 32.1.1, 32.2.1, 32.3.1 второго блока 9 памяти,

первый выход второго разряда трехразрядного регистра 12 сдвига подключен к входам 34 управления считыванием элементов памяти 32.1.2, 32.2.2, 32.3.2 второго блока 9 памяти,

первый выход третьего разряда трехразрядного регистра 12 сдвига подключен к входам 34 управления считыванием элементов памяти 32.1.3, 32.2.3, 32.3.3 второго блока 9 памяти, второй выход третьего разряда трехразрядного регистра 12 сдвига подключен к первому входу микроконтроллера 13,

первый выход микроконтроллера 13 подключен к первому входу генератора 14 ПСЧ, второй выход микроконтроллера 13 подключен ко второму входу блока 15 накопителя, к первым входам управления записью блоков 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ и первому входу блока 11 синхронизации, третий выход микроконтроллера 13 подключен к первому входу блока 15 накопителя,

первый выход генератора 14 ПСЧ подключен к третьему входу блока 15 накопителя, первый выход блока 15 накопителя подключен к третьему информационному входу блока 16.1.1 ОЗУ, второй выход блока 15 накопителя подключен к третьему (информационному) входу блоков 16.1.2 и 16.2.1 ОЗУ, третий выход блока 15 накопителя подключен к третьему (информационному) входу блоков 16.1.3 и 16.3.1 ОЗУ, четвертый выход блока 15 накопителя подключен к третьему (информационному) входу блока 16.2.2 ОЗУ, пятый выход блока 15 накопителя подключен к третьему (информационному) входу блоков 16.2.3 и 16.3.2 ОЗУ, шестой выход блока 15 накопителя подключен к третьему (информационному) входу блока 16.3.3 ОЗУ,

первый выход блока 16.1.1 ОЗУ подключен по общей для блоков 16.1.1, 16.2.1, 16.3.1 ОЗУ N-разрядной шине (N-разрядность псевдослучайных коэффициентов симметрической матрицы) к информационному входу 22.1 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.1, 21.2.1, 21.3.1, входящим в состав первого блока 6 памяти,

первый выход блока 16.1.2 ОЗУ подключен по общей для блоков 16.1.2, 16.2.2, 16.3.2 ОЗУ N-разрядной шине к информационному входу 22.2 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.2, 21.2.2, 21.3.2, входящим в состав первого блока 6 памяти,

первый выход блока 16.1.3 ОЗУ подключен по общей для блоков 16.1.3, 16.2.3, 16.3.3 ОЗУ N-разрядной шине к информационному входу 22.3 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.3, 21.2.3, 21.3.3, входящим в состав первого блока 6 памяти,

первый выход блока 16.2.1 ОЗУ подключен по общей для блоков 16.1.1, 16.2.1, 16.3.1 ОЗУ N-разрядной шине к информационному входу 22.1 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.1, 21.2.1, 21.3.1, входящим в состав первого блока 6 памяти,

первый выход блока 16.2.2 ОЗУ подключен по общей для блоков 16.1.2, 16.2.2, 16.3.2 ОЗУ N-разрядной шине к информационному входу 22.2 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.2, 21.2.2, 21.3.2, входящим в состав первого блока 6 памяти,

первый выход блока 16.2.3 ОЗУ подключен по общей для блоков 16.1.3, 16.2.3, 16.3.3 ОЗУ N-разрядной шине к информационному входу 22.3 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.3, 21.2.3, 21.3.3, входящим в состав первого блока 6 памяти,

первый выход блока 16.3.1 ОЗУ подключен по общей для блоков 16.1.1, 16.2.1, 16.3.1 ОЗУ N-разрядной шине к информационному входу 22.1 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.1, 21.2.1, 21.3.1, входящим в состав первого блока 6 памяти,

первый выход блока 16.3.2 ОЗУ подключен по общей для блоков 16.1.2, 16.2.2, 16.3.2 ОЗУ N-разрядной шине к информационному входу 22.2 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.2, 21.2.2, 21.3.2, входящим в состав первого блока 6 памяти,

первый выход блока 16.3.3 ОЗУ подключен по общей для блоков 16.1.3, 16.2.3, 16.3.3 ОЗУ N-разрядной шине к информационному входу 22.3 первого блока 6 памяти, который подключен к первым входам элементов памяти 21.1.3, 21.2.3, 21.3.3, входящим в состав первого блока 6 памяти,

первый выход первого сумматора - накопителя 17 подключен к первому входу умножителя 18,

первый выход умножителя 18 подключен к первому входу сумматора 19,

первый выход сумматора 19 в случае, если сумматор 19 входит в состав блока 3.1.1 вычислителя, подключен к третьему входу блока 3.1.2 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.1.2 вычислителя; в случае, если сумматор 19 входит в состав блока 3.1.2 вычислителя, первый выход сумматора 19 подключен к третьему входу блока 3.1.3 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.1.3 вычислителя; в случае, если сумматор 19 входит в состав блока 3.1.3 вычислителя, первый выход сумматора 19 подключен к первому входу блока 5.1.1 деления; в случае, если сумматор 19 входит в состав блока 3.2.1 вычислителя, первый выход сумматора 19 подключен к третьему входу блока 3.2.2 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.2.2 вычислителя; в случае, если сумматор 19 входит в состав блока 3.2.2 вычислителя, первый выход сумматора 19 подключен к первому входу блока 5.2.1 деления и к третьему входу блока 3.2.3 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.2.3 вычислителя; в случае, если сумматор 19 входит в состав блока 3.2.3 вычислителя, первый выход сумматора 19 подключен к первому входу блока 5.1.2 деления; в случае, если сумматор 19 входит в состав блока 3.3.1 вычислителя, первый выход сумматора 19 подключен к третьему входу блока 3.3.2 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.3.2 вычислителя; в случае, если сумматор 19 входит в состав блока 3.3.2 вычислителя, первый выход сумматора 19 подключен к третьему входу блока 3.3.3 вычислителя, подключенному ко второму входу сумматора 19 в составе блока 3.3.3 вычислителя; в случае, если сумматор 19 входит в состав блока 3.3.3 вычислителя, первый выход сумматора 19 подключен ко второму входу блока 5.1.1 деления и второму входу блока 5.1.2 деления,

первый выход блока 20.1 формирования коэффициентов системы линейных уравнений (СЛУ) подключен к информационному выходу 30.1 первого блока 6 памяти, подключенному ко вторым входам блоков 3.1.1, 3.1.2, 3.1.3 вычислителя, которые подключены к первому входу первого сумматора-накопителя 17 в составе блоков 3.1.1, 3.1.2, 3.1.3 вычислителя,

первый выход блока 20.2 формирования коэффициентов СЛУ подключен к информационному выходу 30.2 первого блока 6 памяти, подключенному ко вторым входам блоков 3.2.1, 3.2.2, 3.2.3 вычислителя, которые подключены к первому входу первого сумматора - накопителя 17 в составе блоков 3.2.1, 3.2.2, 3.2.3 вычислителя,

первый выход блока 20.3 формирования коэффициентов СЛУ подключен к информационному выходу 30.3 первого блока 6 памяти, подключенному ко вторым входам блоков 3.3.1, 3.3.2, 3.3.3 вычислителя, которые подключены к первому входу первого сумматора - накопителя 17 в составе блоков 3.3.1, 3.3.2, 3.3.3 вычислителя,

первый выход блока 20.4 формирования коэффициентов СЛУ подключен к информационному выходу 38.1 второго блока 9 памяти, который подключен к второму выходу ГФПТ 1 и выводит элементы первого собственного вектора ортогонального базиса матрицы А вида (1), а также подключен к дополнительному информационному входу 28 первого блока 6 памяти, который подключен к первым входам блоков 20.1-20.3 формирования коэффициентов СЛУ в составе первого блока 6 памяти, и второму входу операционного блока 8.1.1, который подключен к первому входу входного 44 регистра и второму входу блока 45 деления, входящих в состав операционного блока 8.1.1,

первый выход блока 20.5 формирования коэффициентов СЛУ подключен к информационному выходу 38.2 второго блока 9 памяти, который подключен к третьему выходу ГФПТ 1 и выводит элементы второго собственного вектора ортогонального базиса матрицы А вида (1), а также подключен к третьему входу операционного блока 8.2.1, который подключен к первому входу регистра 51 первого сомножителя и второму входу вычитателя 49, входящих в состав операционного блока 8.2.1,

первый выход блока 20.6 формирования коэффициентов СЛУ подключен к информационному выходу 38.3 второго блока 9 памяти, который подключен к четвертому выходу ГФПТ 1 и выводит элементы третьего собственного вектора ортогонального базиса матрицы А вида (1),

первые выходы элементов 21.1.1-21.1.3 памяти подключены к информационным выходам 31 элементов памяти, каждый из которых подключен к первому входу блока 20.1 формирования коэффициентов СЛУ,

первые выходы элементов 21.2.1-21.2.3 памяти подключены к информационным выходам 31 элементов памяти, каждый из которых подключен к первому входу блока 20.2 формирования коэффициентов СЛУ,

первые выходы элементов 21.3.1-21.3.3 памяти подключены к информационным выходам 31 элементов памяти, каждый из которых подключен к первому входу блока 20.3 формирования коэффициентов СЛУ,

первые выходы элементов 32.1.1-32.1.3 памяти подключены к информационным выходам 39 элементов памяти, каждый из которых подключен к первому входу блока 20.4 формирования коэффициентов СЛУ,

первые выходы элементов 32.2.1-32.2.3 памяти подключены к информационным выходам 39 элементов памяти, каждый из которых подключен к первому входу блока 20.5 формирования коэффициентов СЛУ,

первые выходы элементов 32.3.1-32.3.3 памяти подключены к информационным выходам 39 элементов памяти, каждый из которых подключен к первому входу блока 20.6 формирования коэффициентов СЛУ,

первый выход регистра 40 памяти подключен к первому входу умножителя 41,

первый выход умножителя 41 подключен к первому входу управляемого инвертора 42,

первый выход управляемого инвертора 42 подключен к первому входу второго сумматора-накопителя 43,

первый выход второго сумматора-накопителя 43, в том случае, если сумматор-накопитель 43 входит в состав блоков 20.1-20.3 формирования коэффициентов СЛУ, подключен соответственно к информационным выходам 30.1-30.3 первого блока 6 памяти; в том случае, если сумматор-накопитель 43 входит в состав блоков 20.4-20.6 формирования коэффициентов СЛУ, первый выход второго сумматора-накопителя 43 подключен соответственно к информационным выходам 38.1-38.3 второго блока 9 памяти,

первый выход входного 44 регистра подключен к первому входу блока 45 деления,

первый выход блока 45 деления в том случае, если блок 45 деления входит в состав операционного блока 8.1.1, подключен к первому входу операционного блока 8.2.1, который подключен к первому входу регистра 47 второго сомножителя в состав е операционного блока 8.2.1; в случае, если блок 45 деления входит в состав операционного блока 8.1.2, первый выход блока 45 деления подключен к первому входу операционного блока 8.2.2, который подключен к первому входу регистра 47 второго сомножителя в составе операционного блока 8.2.2, и к информационному входу 33.3 второго блока 9 памяти, который подключен к первым выходам элементов 32.1.3, 32.2.3, 32.3.3 памяти второго блока 9 памяти,

первый выход регистра 47 второго сомножителя подключен к первому входу умножителя 50 и, в случае, если регистр 47 сдвига входит в состав операционного блока 8.2.1, подключен к первому входу элемента 10.1 задержки, который подключен к первому входу регистра 56 в составе элемента 10.1 задержки,

первый выход выходного 48 регистра в том случае, если он входит в состав операционного блока 8.2.1, подключен ко второму входу операционного блока 8.1.2, который подключен ко второму входу блока 45 деления и первому входу входного 44 регистра в составе операционного блока 8.1.2; в том случае, если выходной 48 регистр входит в состав операционного блока 8.2.2, первый выход выходного 48 регистра подключен к информационному входу 33.2, который подключен к первым выходам элементов 32.1.2, 32.2.2, 32.3.2 памяти второго блока 9 памяти,

первый выход вычитателя 49 подключен к первому входу выходного 48 регистра,

первый выход умножителя 50 подключен к первому входу вычитателя 49, первый выход регистра 51 первого сомножителя подключен ко второму входу умножителя 50,

первый выход регистра 55 подключен к третьему входу операционного блока 8.2.2, который подключен к первому входу регистра 51 первого сомножителя и второму входу вычитателя 49 в составе операционного блока 8.2.2,

первый выход регистра 56 подключен к первому входу регистра 55, первый выход генератора 59 синхроимпульсов подключен к первому входу элемента 60 И,

первый выход элемента 60 И подключен к первому входу счетчика 61 тактов,

выходы 1…N счетчика 61 тактов подключены к входам 1…N блока 62 памяти микрокоманд,

выход 63 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющему входу 46 операционного блока 8.1.1; выход 64 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющему входу 54 операционного блока 8.2.1; выход 65 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к входу 46 операционного блока 8.1.2; выход 66 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к входу 54 операционного блока 8.2.2; выход 67 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющим входам 53 операционных блоков 8.2.1, 8.2.2, к управляющим входам 52 операционных блоков 8.2.1, 8.2.2, к синхровходам 57 и 58 блока 10.1 задержки; выход 68 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к первому (тактовому) входу двухразрядного регистра 7 сдвига; выход 69 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющей шине 29.1 первого блока 6 памяти, подключенной ко вторым входам элементов 21.1.1-21.1.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.1.1-16.1.3 ОЗУ; выход 70 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющей шине 29.2 первого блока 6 памяти, подключенной ко вторым входам элементов 21.2.1-21.2.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.2.1-16.2.3 ОЗУ; выход 71 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющей шине 29.3 первого блока 6 памяти, подключенной ко вторым входам элементов 21.3.1-21.3.3 памяти в составе первого блока 6 памяти, и к первому выходу ГФПТ 1, который подключен к второму входу блока 2 СФКСМ, подключенному к входам 2 управления считыванием блоков 16.3.1-16.3.3 ОЗУ; выход 72 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющей шине 35.1 второго блока 9 памяти, подключенной ко вторым входам элементов 32.1.1-32.1.3 памяти в составе второго блока 9 памяти; выход 73 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к управляющей шине 36.1 второго блока 9 памяти, подключенной ко вторым входам элементов 32.2.1-32.2.2 памяти в составе второго блока 9 памяти; выход 74 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к шине 36.2 блока 9памяти, подключенной ко второму входу элемента 32.2.3 памяти в составе второго блока 9 памяти; выход 75 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к шине 37.1 второго блока 9 памяти, подключенной ко второму входу элемента 32.3.1 памяти в составе второго блока 9 памяти; выход 76 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к шине 37.2 второго блока 9 памяти, подключенной ко вторым входам элементов 32.3.2-32.3.3 памяти в составе второго блока 9 памяти; выходы 77-80 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.1, входящего в состав первого блока 6 памяти; выходы 81-84 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.2, входящего в состав первого блока 6 памяти; выходы 85-88 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.3, входящего в состав первого блока 6 памяти; выходы 89-92 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.4, входящего в состав второго блока 9 памяти; выходы 93-96 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.5, входящего в состав второго блока 9 памяти; выходы 97-100 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам блока 20.6, входящего в состав второго блока 9 памяти; выходы 101-109 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам 27 считывания элементов 21.1.1-21.1.3, 21.2.1-21.2.3, 21.3.1-21.3.3 памяти, входящих в состав первого блока 6 памяти; выходы 110-118 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключены к управляющим входам 34 считывания элементов 32.1.1-32.1.3, 32.2.1-32.2.3, 32.3.1-32.3.3 памяти, входящих в состав второго блока 9 памяти; выход 119 блока 62 памяти микрокоманд в составе блока 11 синхронизации подключен к первому (тактовому) входу трехразрядного трехразрядного регистра 12 сдвига.

В генераторе функций Попенко-Турко убрана обратная связь в трехразрядном регистре 12, который обеспечивает вывод из второго блока 9 памяти дискретных базисных функций (ортогонального базиса матрицы вида (1)) S1(t), S2(t), S3(t), для предотвращения цикличности вывода элементов S1(t), S2(t), S3(t).

Краткое писание чертежей

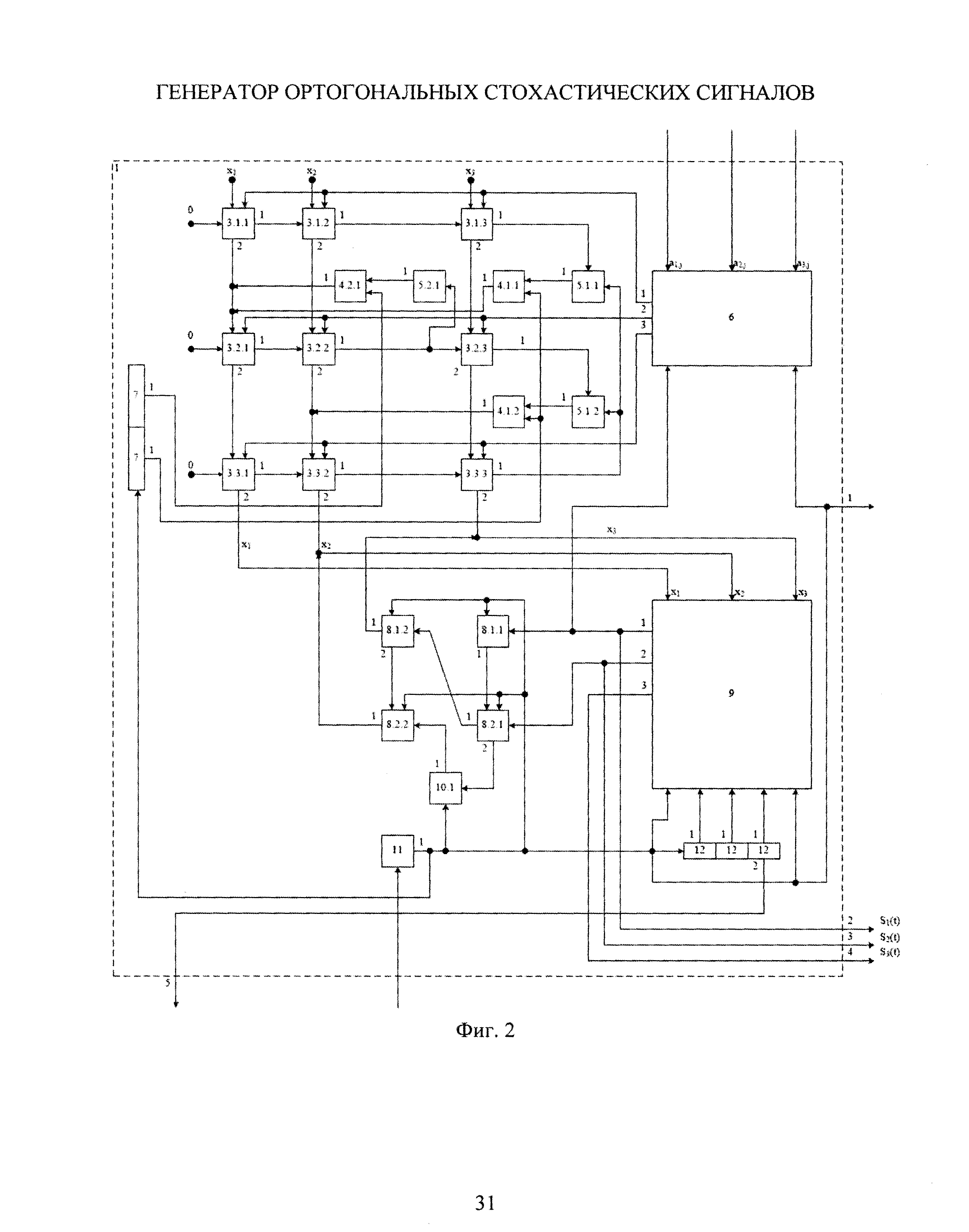

На фиг. 1 представлена схема генератора стохастических ортогональных кодов.

На фиг. 2 представлена функциональная схема генератора 1 функций Попенко-Турко.

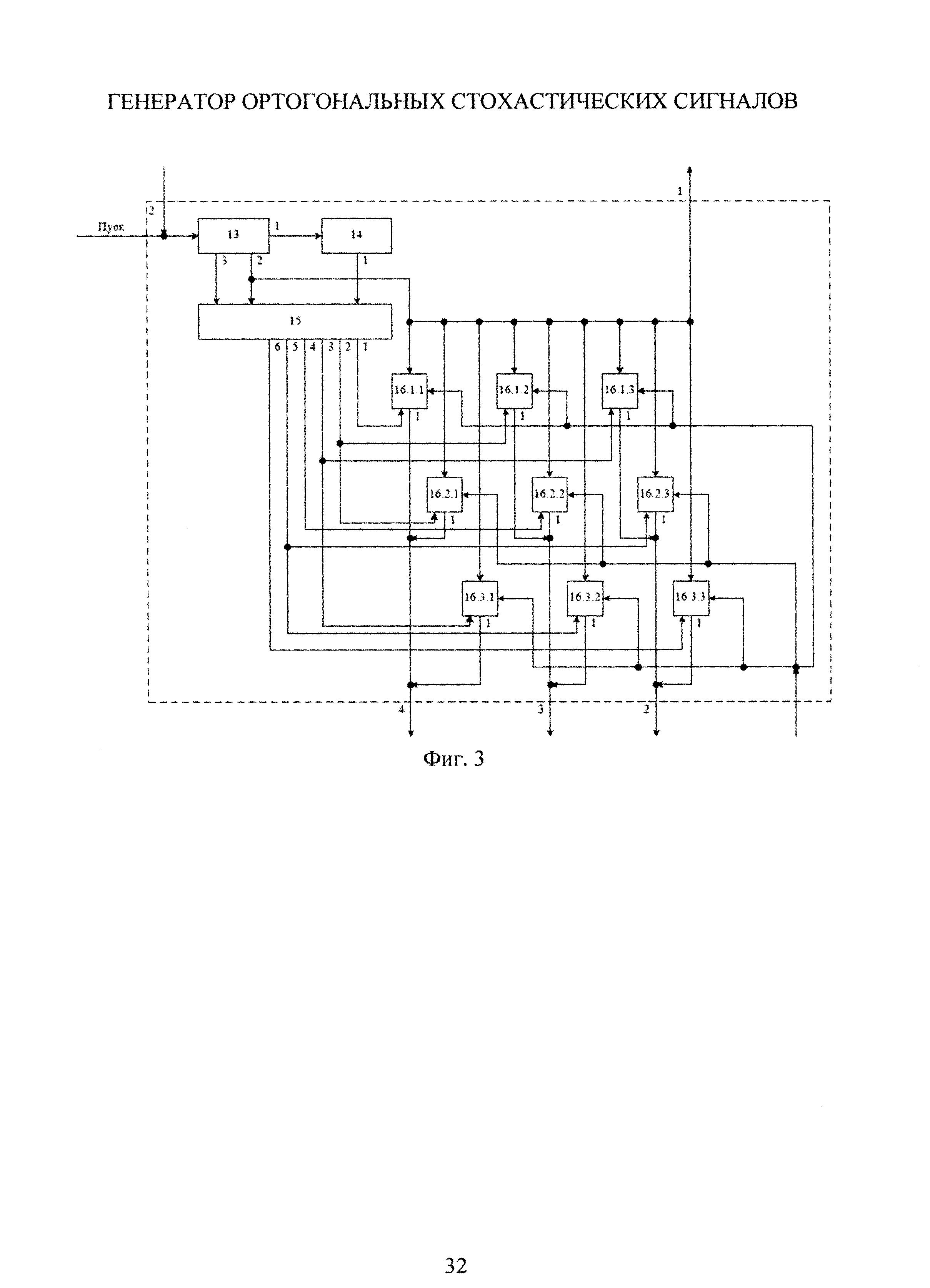

На фиг. 3 представлена функциональная схема блока 2 стохастического формирования коэффициентов симметрической матрицы.

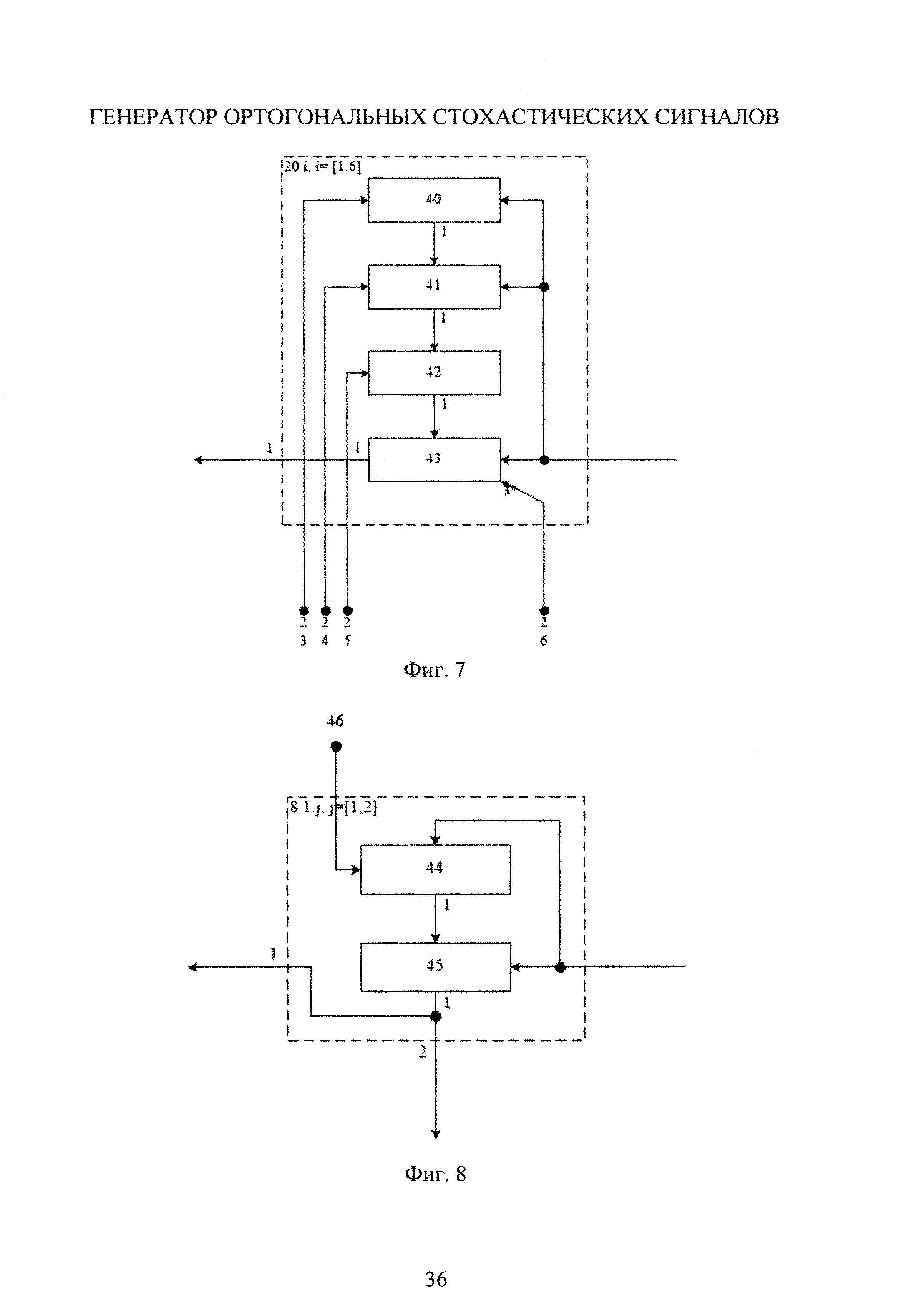

На фиг. 4 представлена функциональная схема вычислителя 3.i.j (i=1, 2, 3; j=1, 2, 3).

На фиг. 5 представлена функциональная схема первого блока 6 памяти.

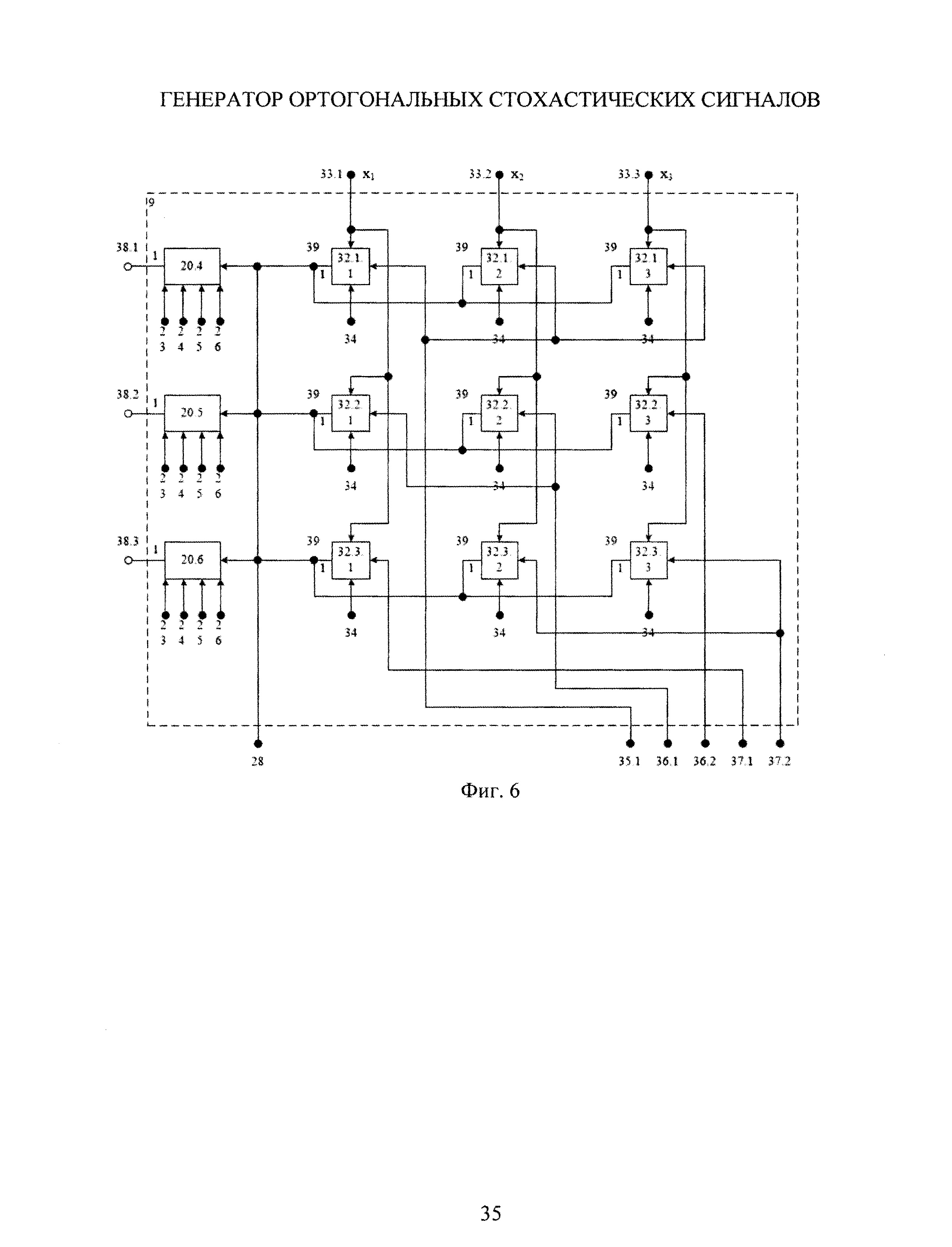

На фиг. 6 представлена функциональная схема второго блока 9 памяти.

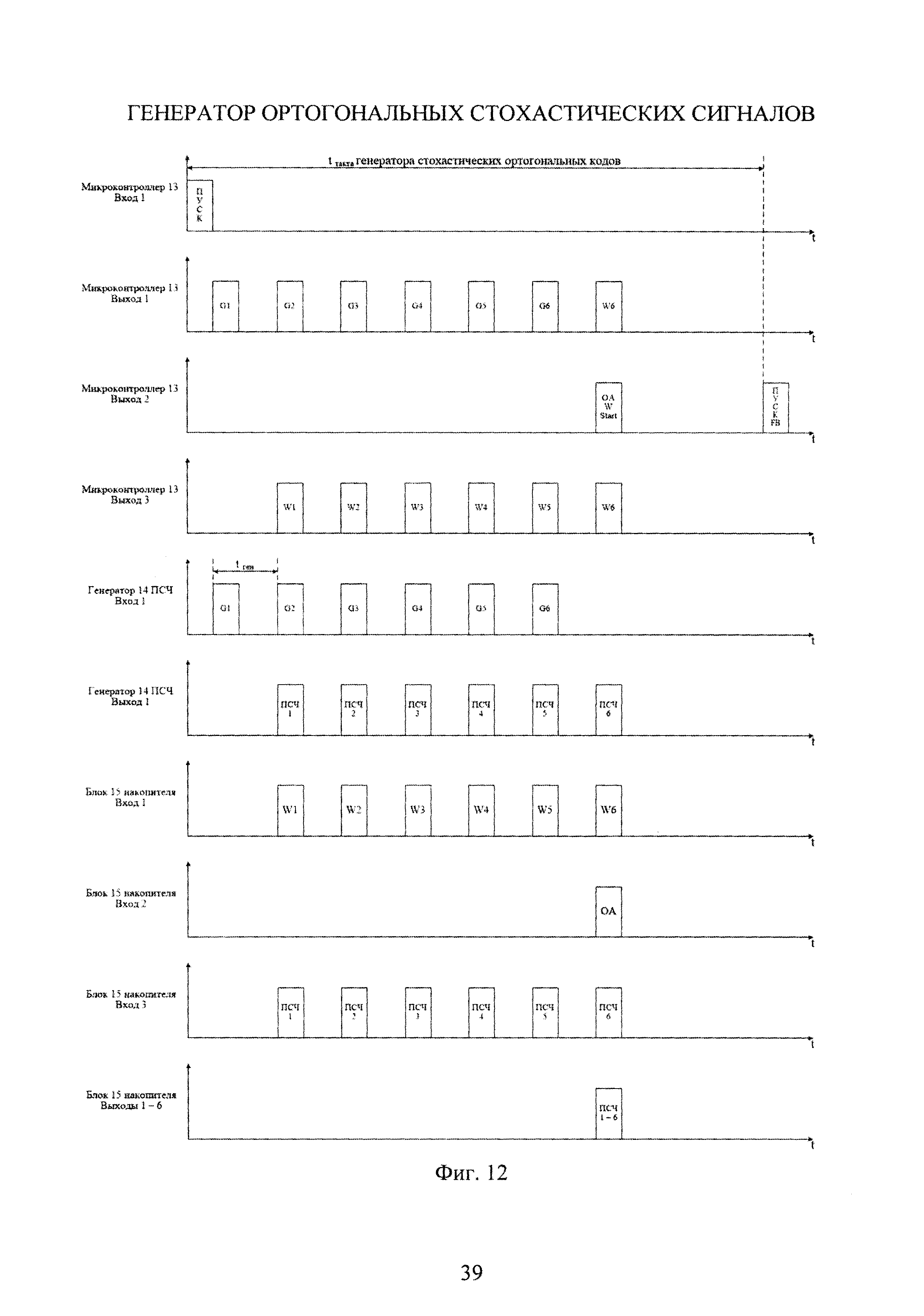

На фиг. 7 представлена функциональная схема блока 20.i (i=1, 2, 3, 4, 5, 6) формирования коэффициентов системы линейных уравнений.

На фиг. 8 представлена функциональная схема операционного блока 8.1.j (j=1, 2).

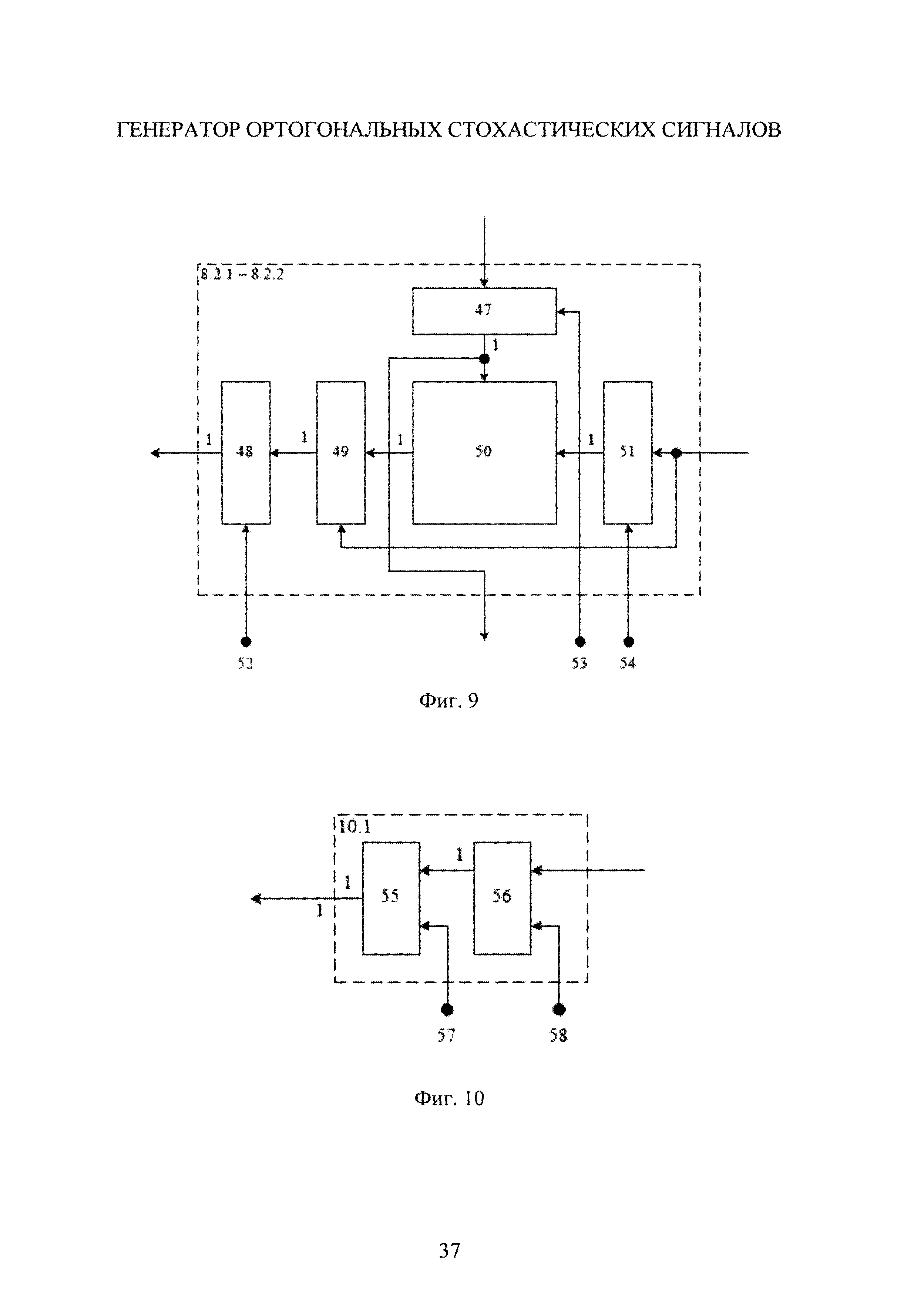

На фиг. 9 представлена функциональная схема операционного блока 8.2.j (j=1, 2).

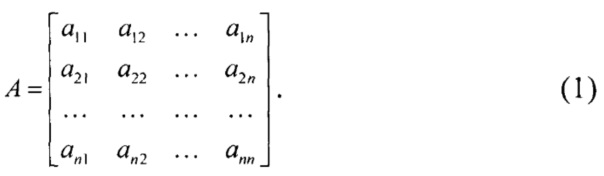

На фиг. 10 представлена функциональная схема элемента 10.1 задержки.

На фиг. 11 представлена функциональная схема блока 11 синхронизации.

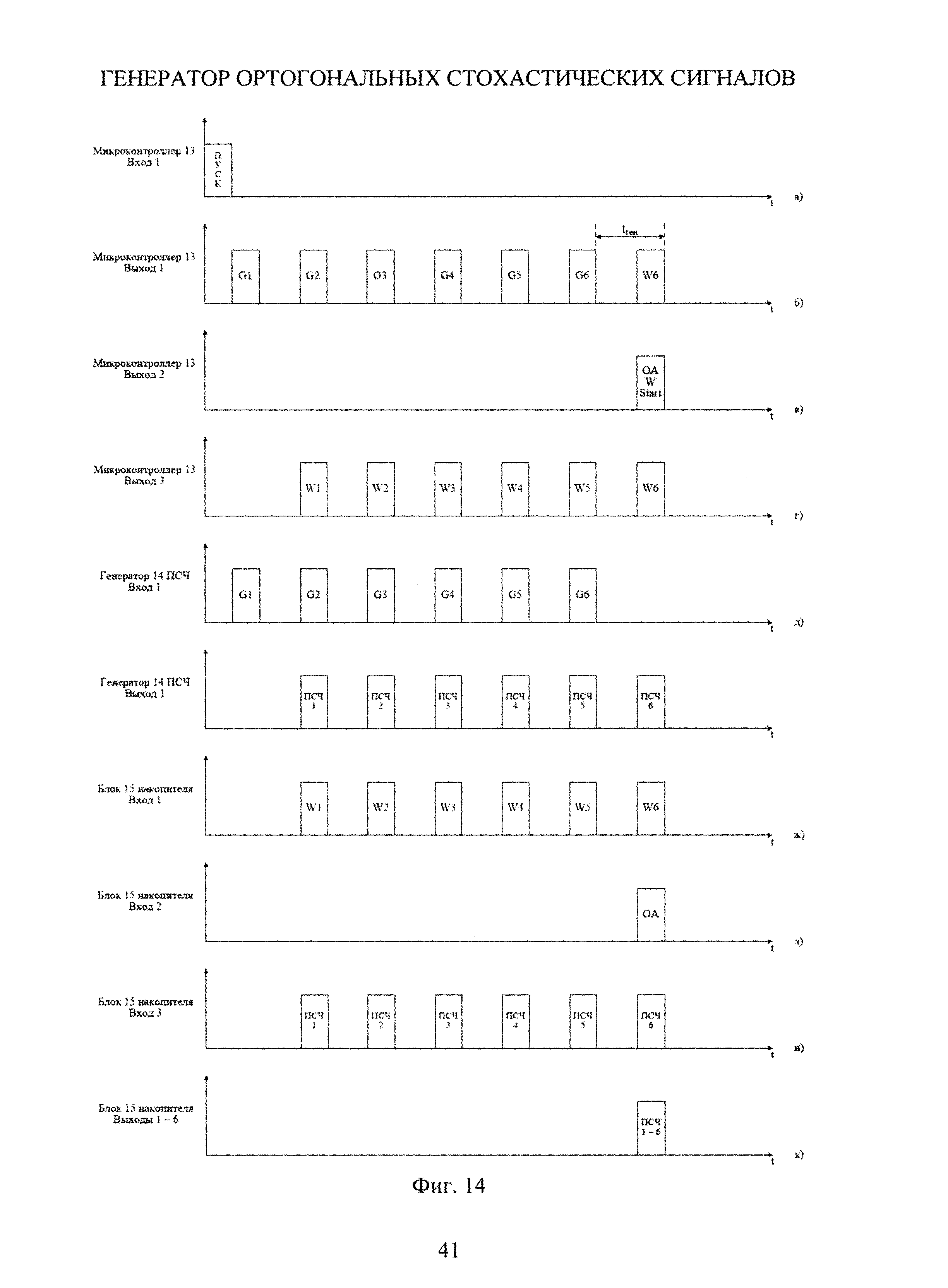

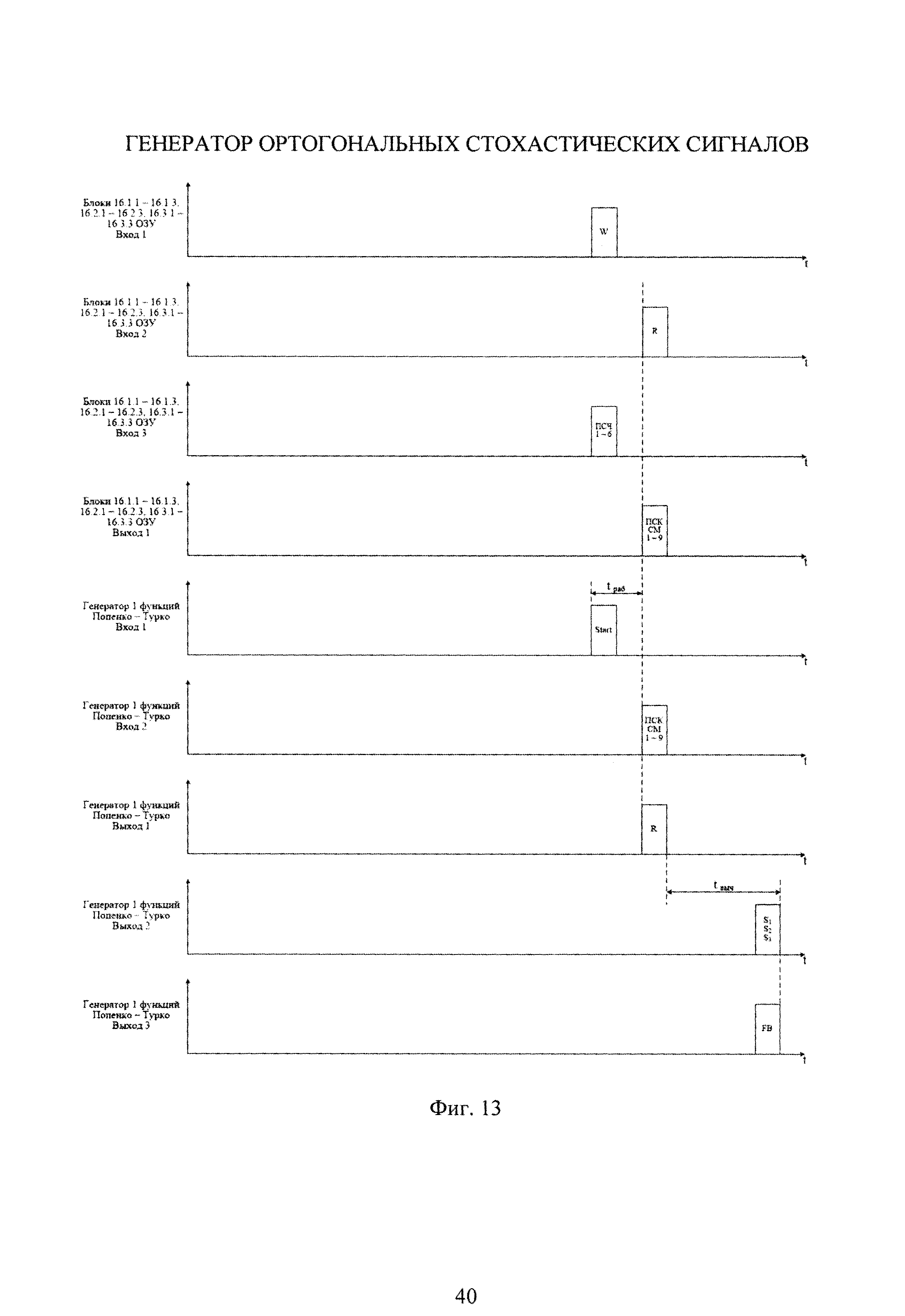

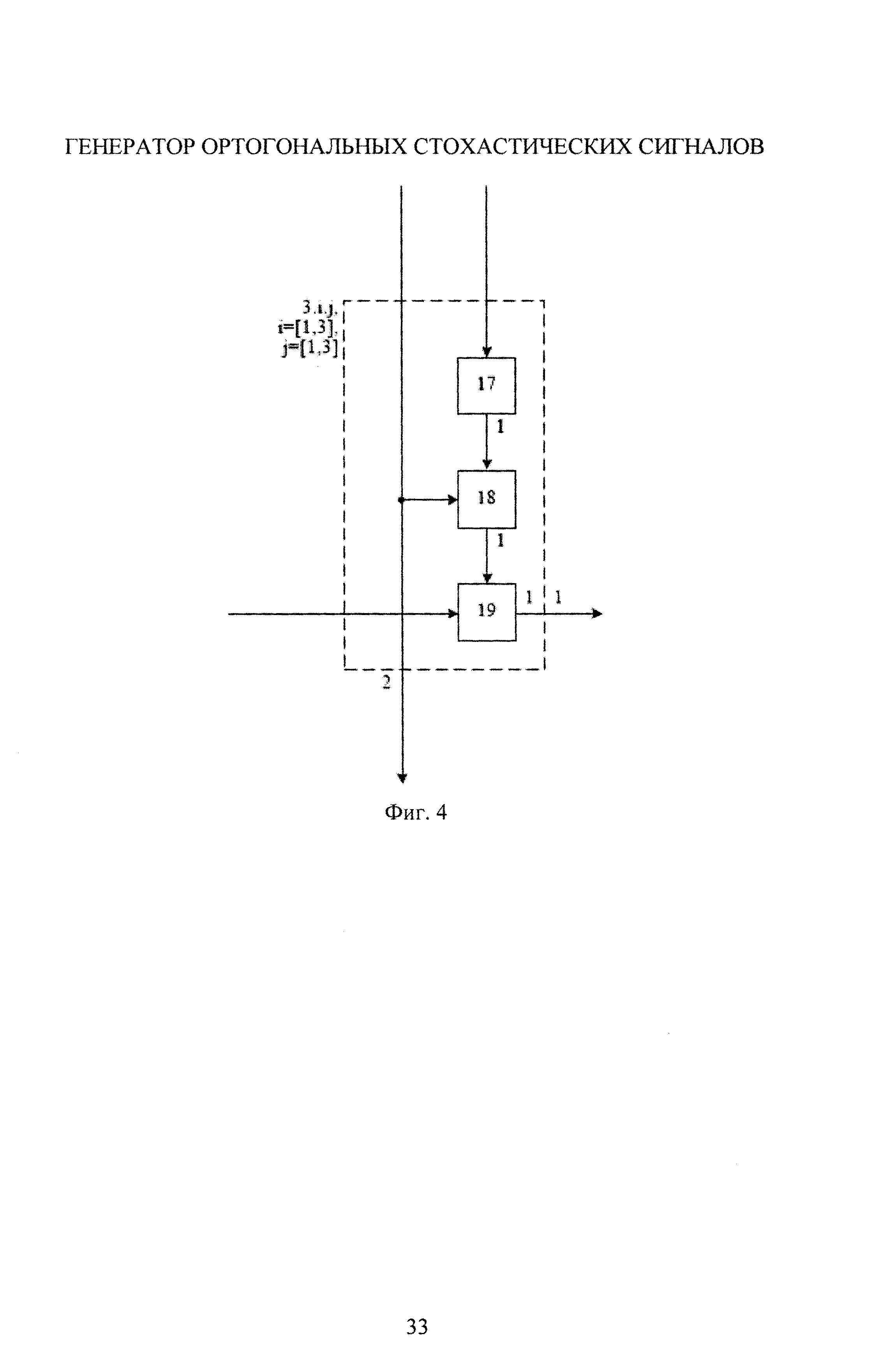

На фиг. 12-13 представлены временные диаграммы выходов блоков заявляемого генератора стохастических ортогональных сигналов.

На фиг. 14 представлена иллюстрация процесса формирования симметрической матрицы. Описание обозначений приводится в осуществлении изобретения.

Осуществление изобретения

Процедуру задания начальных псевдослучайных значений коэффициентов симметрической положительно определенной действительной матрицы для работы ГФПТ 1 осуществляют микроконтроллер 13, генератор 14 псевдослучайных чисел (ПСЧ), блок 15 накопителя и блоки 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 N-разрядного оперативного запоминающего устройства (ОЗУ), где N-разрядность генерируемых генератором 14 ПСЧ значений. Формирование симметрической матрицы порядка n происходит в блоках 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 N-разрядного ОЗУ из верхней треугольной матрицы того же порядка n, исходя из свойства симметричности (1). В рассматриваемом случае порядок матрицы равен 3, исходя из (2) число коэффициентов равно 6.

Устройство работает следующим образом.

После поступления от пользователя команды «Пуск» на первый вход блока 2 СФКСМ, микроконтроллер 13 с первого выхода подает на первый вход генератора 14 ПСЧ команду на генерацию очередного псевдослучайного числа (ПСЧ). Генератор 14 ПСЧ с первого выхода передает ПСЧ на третий вход блока 15 накопителя. По прошествии определенного времени, необходимого генератору 14 ПСЧ на выработку очередного ПСЧ, равное tген (записывается предварительно в память микроконтроллера 13), микроконтроллер 13 одновременно с третьего выхода подает команду на первый вход блока 15 накопителя на запоминание выработанного генератором 14 ПСЧ значения и с первого выхода подает на первый вход генератора 14 ПСЧ команду на генерацию ПСЧ. Всего одновременная подача команд на генератор 14 ПСЧ и блок 15 накопителя повторяется 6 раз. Вышеописанный процесс иллюстрируется на фиг. 14.

На фиг. 14 а) показана команда «Пуск», являющаяся командой на начало работы генератора стохастических ортогональных сигналов. Как будет показано ниже, роль этой команды после первого запуска универсального генератора будет выполнять импульс обратной связи (на фиг. 10 - команда ПУСК FB) с второго выхода третьего разряда трехразрядного регистра 12 сдвига.

На фиг. 14 б) показаны команды, выдаваемые микроконтроллером 13 генератору 14 ПСЧ на генерацию ПСЧ, они обозначены как GN, N - порядковый номер ПСЧ, N ∈ [1, 6].

На фиг. 14 в) показана команда микроконтроллера 13, адресованная одновременно нескольким блокам: команда OA на одновременный вывод всех хранимых в блоке 15 накопителя значений ПСЧ, команда W блокам 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ на запись передаваемым блоком 15 накопителя значениям ПСЧ, команда Start на запуск блока 11 синхронизации.

На фиг. 14 г) показаны команды микроконтроллера 13 блоку 15 накопителя на запись очередного ПСЧ, они обозначены как WN, N - порядковый номер ПСЧ, N ∈ [1, 6].

После того, как микроконтроллер 13 с первого выхода подает команду G1 на первый вход генератора 14 ПСЧ, в дальнейшем команды G2-G6 подаются по прошествии времени tген, необходимого генератору 14 ПСЧ на генерацию ПСЧ. Команды W1-W5 подаются одновременно с командами G2-G6, команда W6 подается одновременно с командой с второго выхода микроконтроллера 13. Таким образом, процесс формирования симметрической матрицы занимает 7 тактов работы микроконтроллера 13.

На фиг. 14 д) показаны команды G1-G6, подаваемые с первого выхода микроконтроллера 13 на первый вход генератора 14 ПСЧ.

На фиг. 14 е) показаны ПСЧ1-ПСЧ6, генерируемые генератором 14 ПСЧ по командам микроконтроллера 13 и с первого выхода передаваемые на третий вход блока 15 накопителя.

На фиг. 14 ж) показаны команды W1-W6, подаваемые микроконтроллером 13 с третьего выхода на первый вход блока 15 накопителя.

На фиг. 14 з) показана команда OA, подаваемая микроконтроллером 13 с второго выхода на второй вход блока 15 накопителя для одновременного вывода всех хранимых в накопителе значений ПСЧ из выходов 1-6 блока 15 накопителя.

На фиг. 14 и) показаны значения ПСЧ1-ПСЧ6, подаваемые с первого выхода генератора 14 ПСЧ на третий вход блока 15 накопителя.

На фиг. 14 к) показан одновременный вывод значений ПСЧ1-ПСЧ6 с соответствующих выходов 1-6 блока 15 накопителя на входы 3 (информационные) блоков 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ, формирующих симметрическую матрицу А вида (1).

Каждый из блоков 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ представляет собой N-разрядный элемент памяти, на первый вход микроконтроллером 13 подается управляющий импульс разрешения записи значения ПСЧ (на фиг. 14 - команда W), на второй вход блоком 11 синхронизации подается управляющий импульс считывания (на фиг. 13 - команда R), на третий вход блоком 15 накопителя подается N-разрядное значение ПСЧ.

Блоки 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ связаны таким образом, чтобы сформировать квадратную симметрическую матрицу А вида (1) из элементов верхней треугольной матрицы с количеством элементов, определяемым (2). Таким образом, генератором 14 ПСЧ последовательно формируется шесть ПСЧ, которые записываются следующим образом: ПСЧ1 запоминается блоком 16.1.1 ОЗУ, ПСЧ2 запоминается блоками 16.1.2 и 16.2.1 ОЗУ, ПСЧЗ запоминается блоками 16.1.3 и 16.3.1 ОЗУ, ПСЧ4 запоминается блоком 16.2.2 ОЗУ, ПСЧ5 запоминается блоками 16.2.3 и 16.3.2 ОЗУ, ПСЧ6 запоминается блоком 16.3.3 ОЗУ.

После поступления команды запуска одновременно на второй вход элемента 60 И и на второй вход счетчика 61 тактов на первый вход счетчика 61 тактов через элемент 60 И начинают поступать импульсы с первого выхода генератора 59 синхроимпульсов. В соответствием с алгоритмом работы счетчик тактов 61 с выходов 1-N управляет работой блока 62 памяти микрокоманд.

Блок 11 синхронизации управляет работой блоков, составляющих функционал ГФПТ 1, а также чтением информации, хранящейся в блоках 16.1.1-16.1.3, 16.2.1-16.2.3, 16.3.1-16.3.3 ОЗУ. Для вычисления ансамбля стохастических ортогональных кодов (ортогонального базиса собственных секторов симметрической матрицы А вида (1)) необходимо записать псевдослучайные коэффициенты симметрической матрицы А (ПСК СМ) вида (1) в блок 6 памяти в составе ГФПТ 1.

Поскольку формирование системы дискретных базисных функций (ортогонального базиса собственных секторов симметрической матрицы А вида (1)) осуществляется аналогично для любых симметрических положительно определенных матриц любой размерности, то для примера рассмотрим формирование системы, состоящей из трех дискретных базисных функций.

Для записи ПСК СМ в элементы 21.1.1-21.1.3, 21.2.1-21.2.3, 21.3.1-21.3.3 памяти блок 11 синхронизации с выходов 69-71 последовательно подает команды, а именно: команда с выхода 69 одновременно подается на вторые входы блоков 16.1.1, 16.1.2, 16.1.3 ОЗУ для вывода хранящихся в них значений ПСК СМ, передаваемых блоками 16.1.1, 16.1.2, 16.1.3 ОЗУ с первых выходов на информационные входы 22.1, 22.2, 20.3 первого блока 6 памяти, и на вход 29.1 первого блока 6 памяти, управляющий записью элементов 21.1.1, 21.1.2, 21.1.3 памяти в составе первого блока 6 памяти, для записи переданных на информационные входы 22.1, 22.2, 22.3 первого блока 6 памяти значений ПСК СМ; команда с выхода 70 одновременно подается на вторые входы блоков 16.2.1, 16.2.2, 16.2.3 ОЗУ для вывода хранящихся в них значений ПСК СМ, передаваемых блоками 16.2.1, 16.2.2, 16.2.3 ОЗУ с первых выходов на информационные входы 22.1, 22.2, 22.3 первого блока 6 памяти, и на вход 29.2 первого блока 6 памяти, управляющий записью элементов 21.2.1, 21.2.2, 21.2.3 памяти в составе первого блока 6 памяти, для записи переданных на информационные входы 22.1, 22.2, 22.3 первого блока 6 памяти значений ПСК СМ; команда из выхода 71 одновременно подается на вторые входы блоков 16.3.1, 16.3.2, 16.3.3 ОЗУ для вывода хранящихся в них значений ПСК СМ, передаваемых блоками 16.3.1, 16.3.2, 16.3.3 ОЗУ с первых выходов на информационные входы 22.1, 22.2, 22.3 первого блока 6 памяти, и на вход 29.3 первого блока 6 памяти, управляющий записью элементов 21.3.1, 21.3.2, 21.3.3 памяти в составе первого блока 6 памяти, для записи переданных на информационные входы 22.1, 22.2, 22.3 первого блока 6 памяти значений ПСК СМ.

После этого считается, что исходные данные (ПСК СМ) записаны в блок 6 памяти. После записи исходных данных генератор стохастических ортогональных кодов работает следующим образом.

Пусть исходная действительная симметрическая положительно определенная матрица А имеет вид (1).

Предположим, что генератор 14 ПСЧ сформировал следующие псевдослучайные коэффициенты симметрической матрицы А вида (1), так что она имеет вид:

В исходном состоянии элементы матрицы А (5) записаны в элементах 21.1.1-21.1.3, 21.2.1-21.2.3, 21.3.1-21.3.3 памяти блока 6, в регистре 7 сдвига записан код вида «10…0» (для рассматриваемого случая - «10»), причем «1» записана в первом разряде регистра 7 сдвига. Вычисление 1-го собственного значения и соответствующего ему собственного вектора будет осуществляться в течение времени нахождения «1» в i-м (i=[1; 3]) разряде регистра 7 сдвига, поэтому период поступления тактовых импульсов с выхода 68 на тактовый вход регистра 7 сдвига равен времени сходимости итерационного процесса и вычисления оставшейся части компонент собственного вектора.

В течение первого периода работы генератора «1» с выхода первого двухразрядного разряда регистра 7 сдвига поступает на входы вторых сомножителей блоков элементов И 4.1.1 и 4.1.2. На вход второго сомножителя блока 4.2.1 поступает «0» с выхода второго двухразрядного разряда регистра 7 сдвига, в результате на выходе блока 4.2.1 формируется «0».

С поступлением последовательности синхроимпульсов с выходов 101-109 на управляющие входы 27 считывания элементов 21.1.1-21.1.3, 21.2.1-21.2.3, 21.3.1-21.3.3 памяти в составе первого блока 6 памяти значения элементов матрицы А (5) последовательно поступают на входы сумматоров-накопителей 17 в составе блоков 3.1.1-3.1.3, 3.2.1-3.2.3, 3.3.1-3.3.3 вычислителей и запоминаются в них. Накопление в сумматорах-накопителях 17 осуществляется каждый раз при подаче на их вход нового слагаемого.

На входы вторых сомножителей блоков 18 умножения всех столбцов матрицы блоков 3.1.1-3.1.3, 3.2.1-3.2.3, 3.3.1-3.3.3 вычислителей, кроме последнего, подаются произвольные сигналы  . На входах вторых сомножителей блоков 18 умножения блоков 3.1.3, 3.2.3, 3.3.3 вычислителей последнего столбца присутствует сигнал «1».

. На входах вторых сомножителей блоков 18 умножения блоков 3.1.3, 3.2.3, 3.3.3 вычислителей последнего столбца присутствует сигнал «1».

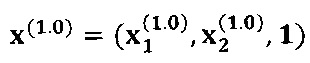

Следовательно, для реализации итерационной процедуры отыскания собственного числа λ1 матрицы А (5) в качестве начального приближения выбирается вектор  .

.

На выходе сумматора 19 последнего блока 3.3.3 вычислителя последней строки матрицы при этом образуется сигнал

который является первым приближением собственного числа λ1.

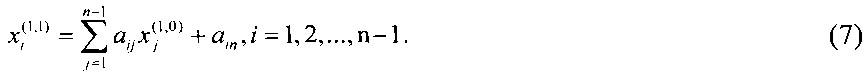

На выходе сумматора 19 последнего вычислителя 3.3.i i-й строки (i=1, …, n-1) образуется сигнал

Этот сигнал является i-м компонентом первого ненормированного приближения первого собственного вектора матрицы А (5)

.

.

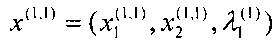

Нормирование первого приближения первого вектора осуществляется путем деления всех его компонентов на величину последнего компонента  . Так как в результате нормирования последняя компонента равна 1, то ее деление не производится и «1» поступает на входы вторых сомножителей всех блоков 18 умножения последнего столбца матрицы блоков 3.1.3, 3.2.3, 3.3.3 вычислителей. Нормирование остальных компонент осуществляется при помощи блоков деления 5.1.1 и 5.1.2 путем деления компонент на величину последней компоненты

. Так как в результате нормирования последняя компонента равна 1, то ее деление не производится и «1» поступает на входы вторых сомножителей всех блоков 18 умножения последнего столбца матрицы блоков 3.1.3, 3.2.3, 3.3.3 вычислителей. Нормирование остальных компонент осуществляется при помощи блоков деления 5.1.1 и 5.1.2 путем деления компонент на величину последней компоненты  .

.

Сигнал с выхода блока 5.1.1 деления через блок 4.1.1 элементов И поступает на входы вторых сомножителей блоков 18 умножения блоков вычислителей 3.2.1 и 3.3.1, т.е. блоков 3.2.1, 3.3.1 вычислителей первого столбца матрицы. Сигнал с выхода блока 5.1.2 деления через блок 4.1.2 элементов И поступает на вход второго сомножителя блока 18 умножения вычислителя 3.3.2, т.е. блока 3.3.2 вычислителя второго столбца матрицы. Таким образом, в соответствии с соотношением

после окончания первой итерации на выходах блоков 3.3.1, 3.3.2, 3.3.3 вычислителей присутствуют сигналы, соответствующие компонентам первого нормированного приближения первого собственного вектора

.

.

Затем итерационный процесс повторяется и после окончания второй итерации на выходах блоков 3.3.1, 3.3.2, 3.3.3 вычислителей присутствуют сигналы, соответствующие компонентам второго нормированного приближения первого собственного вектора

.

.

Повторение итераций будет осуществляться до полной сходимости итерационного процесса. В результате на выходах блоков 3.3.1, 3.3.2, 3.3.3 вычислителей присутствуют сигналы, соответствующие компонентам нормированного первого собственного вектора

.

.

а на выходе сумматора 19 вычислителя 3.3.3 присутствует сигнал, соответствующий собственному значению λ1.

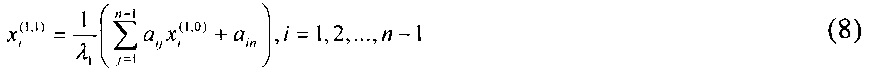

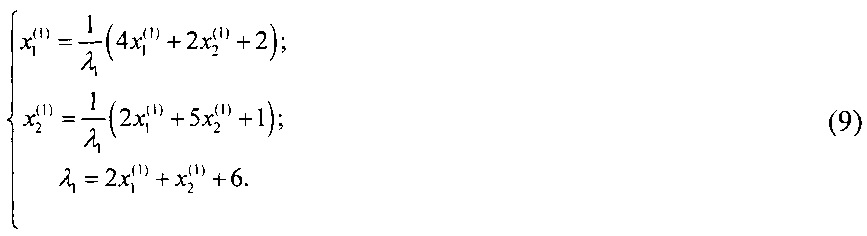

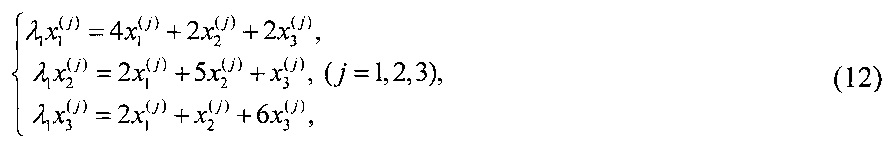

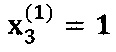

Таким образом, для матрицы А (5) система уравнений, решаемая методом итерации, в соответствии с соотношениями (6) и (7) следующая:

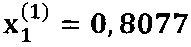

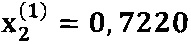

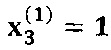

После реализации сходимости итерационного процесса на выходах блоков 3.3.1, 3.3.2, 3.3.3 вычислителей будут получены значения компонент первого собственного вектора  ,

,  ,

,  , а на выходе сумматора 19 вычислителя 3.3.3 будет получено значение λ1=8,3874.

, а на выходе сумматора 19 вычислителя 3.3.3 будет получено значение λ1=8,3874.

По окончании времени, необходимого для реализации сходимости итерационного процесса, импульс с выхода 72 поступит на вход 35.1 второго блока 9 памяти и компоненты первого собственного вектора окажутся записанными в элементах 32.1.1, 32.1.2, 32.1.3 памяти. В следующий момент времени на тактовый вход регистра 7 сдвига поступает тактовый импульс с выхода 68, под воздействием которого «1» из первого двухразрядного разряда регистра 7 сдвига сдвигается во второй разряд.

Таким образом, «1» с выхода второго двухразрядного разряда регистра 7 сдвига поступает на вход второго сомножителя блока 4.2.1 элементов И. На входы вторых сомножителей блоков 4.1.1 и 4.1.2 элементов И поступает «0» с выхода первого двухразрядного разряда регистра 7 сдвига, в результате на выходах блоков 4.1.1 и 4.1.2 элементов И формируется «0».

Для определения второго собственного значения и компонент  ,

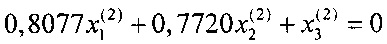

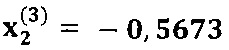

,  второго собственного вектора необходимо методом итерации решить систему уравнений

второго собственного вектора необходимо методом итерации решить систему уравнений

Для матрицы А (5) вторая система уравнений, решаемая методом итерации, определяется из условия ортогональности векторов х(1) и х(2) (4). Так как

,

,

то

Подставляя это выражение в систему вида

и полагая  , получим

, получим

Система (13) решается методом итерации, но для этого нужно предварительно сформировать коэффициенты  (10). Для этого используются коэффициенты aij, записанные в блоке 4 памяти.

(10). Для этого используются коэффициенты aij, записанные в блоке 4 памяти.

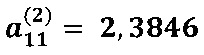

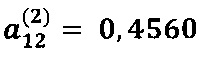

При формировании коэффициента  с выхода 110 на вход 34 считывания элемента 32.1.1 памяти в составе второго блока 9 памяти поступает импульс, и значение 0,8077 через второй сумматор-накопитель 43 блока 20.4 поступает на дополнительный информационный вход 28 первого блока 6 памяти и после поступления импульса с выхода 77 на вход 23 блока 20.1 записывается в регистре 40 памяти. Затем импульс с выхода 103 поступает на вход 27 считывания элемента 21.1.3 памяти в составе первого блока 6 памяти и значение 2 после поступления импульса с выхода 78 на вход 24 блока 20.1 перемножается в блоке 41 умножения со значением 0,8077. После поступления импульсов с выхода 79 на вход 25, с выхода 80 на вход 26 блока 20.1 с его выхода значение - 1,6154 поступает на вход сумматора-накопителя 17 в составе блока 3.1.1 вычислителя, в котором до этого хранилось значение 4, в результате чего в нем станет храниться значение

с выхода 110 на вход 34 считывания элемента 32.1.1 памяти в составе второго блока 9 памяти поступает импульс, и значение 0,8077 через второй сумматор-накопитель 43 блока 20.4 поступает на дополнительный информационный вход 28 первого блока 6 памяти и после поступления импульса с выхода 77 на вход 23 блока 20.1 записывается в регистре 40 памяти. Затем импульс с выхода 103 поступает на вход 27 считывания элемента 21.1.3 памяти в составе первого блока 6 памяти и значение 2 после поступления импульса с выхода 78 на вход 24 блока 20.1 перемножается в блоке 41 умножения со значением 0,8077. После поступления импульсов с выхода 79 на вход 25, с выхода 80 на вход 26 блока 20.1 с его выхода значение - 1,6154 поступает на вход сумматора-накопителя 17 в составе блока 3.1.1 вычислителя, в котором до этого хранилось значение 4, в результате чего в нем станет храниться значение  .

.

Аналогичным образом формируются значения  ,

,  ,

,  , которые будут храниться в сумматорах-накопителях 17 блоков 3.1.2, 3.2.1, 3.2.2 вычислителей соответственно.

, которые будут храниться в сумматорах-накопителях 17 блоков 3.1.2, 3.2.1, 3.2.2 вычислителей соответственно.

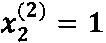

После подачи на входы вторых сомножителей блоков 18 умножения в составе блоков 3.1.1 и 3.2.1 вычислителей произвольного сигнала  , а на входы вторых сомножителей блоков 18 умножения в составе блоков 3.1.2 и 3.2.2 вычислителей сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 5.2.1 делителя, а соответственно на выходе блока 3.2.1 вычислителя будет получено значение

, а на входы вторых сомножителей блоков 18 умножения в составе блоков 3.1.2 и 3.2.2 вычислителей сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 5.2.1 делителя, а соответственно на выходе блока 3.2.1 вычислителя будет получено значение  , на выходе блока 3.2.2 вычислителя будет присутствовать сигнал

, на выходе блока 3.2.2 вычислителя будет присутствовать сигнал  , а на выходе сумматора 19 будет присутствовать значение λ2=4,4867.

, а на выходе сумматора 19 будет присутствовать значение λ2=4,4867.

По окончании времени, необходимого для реализации сходимости итерационного процесса, импульс с выхода 73 поступит на вход 36.1 второго блока 9 памяти и компоненты  и

и  второго собственного вектора окажутся записанными в элементах 32.2.1 и 32.2.2 памяти в составе второго блока 9 памяти.

второго собственного вектора окажутся записанными в элементах 32.2.1 и 32.2.2 памяти в составе второго блока 9 памяти.

Компонента  определяется из соотношения (11), т.е. уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения с одним неизвестным или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 8.1.1, 8.1.2, 8.2.1, 8.2.2, элемент 10.1 задержки, блок 11 синхронизации. В нем выполняется обработка матрицы размерности N×М (N=1,2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности N×1 свободных членов.

определяется из соотношения (11), т.е. уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения с одним неизвестным или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 8.1.1, 8.1.2, 8.2.1, 8.2.2, элемент 10.1 задержки, блок 11 синхронизации. В нем выполняется обработка матрицы размерности N×М (N=1,2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности N×1 свободных членов.

Таким образом, например, для решения системы из двух линейных уравнений на входы устройства будет поступать матрица В вида

где В11, В12, В21, В22 - коэффициенты при неизвестных, а В13, В23 - свободные члены.

Элементы матрицы В поступают на входы операционных блоков 8 построчно со сдвигом на один такт под воздействием синхроимпульсов с выходов блока 11 синхронизации, т.е. первая строка поступает на первый вход операционного блока 8.1.1, начиная с первого такта, вторая строка поступает на первый вход операционного блока 8.2.1, начиная с второго такта, и т.д. На выходах операционных блоков 8.i.j (j=n, i=1, …, n) получается семейство решений системы линейных уравнений.

Таким образом, решения системы из двух уравнений получаются на выходах операционных блоков 8.1.2 и 8.2.2. Решение уравнения с одним неизвестным - на выходе операционного блока 8.1.1.

Следовательно, при вычислении значения  будет задействован только операционный блок 8.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 20.4 в составе второго блока 9 памяти.

будет задействован только операционный блок 8.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 20.4 в составе второго блока 9 памяти.

В соответствии с (11) коэффициент при неизвестном  будет сформирован следующим образом. С выхода 92 на вход 26 блока 20.4 формирования коэффициентов СЛУ второго блока 9 памяти поступает «1», в результате чего через второй сумматор-накопитель 43 блока 20.4 формирования коэффициентов СЛУ она поступает на вход операционного блока 8.1.1.

будет сформирован следующим образом. С выхода 92 на вход 26 блока 20.4 формирования коэффициентов СЛУ второго блока 9 памяти поступает «1», в результате чего через второй сумматор-накопитель 43 блока 20.4 формирования коэффициентов СЛУ она поступает на вход операционного блока 8.1.1.

Затем вычисляется свободный член в соответствии с (11). Синхроимпульс с выхода 111 блока 11 синхронизации поступает на вход 34 считывания элемента 32.1.1 памяти в составе второго блока 9 памяти, с выхода 89 блока 11 синхронизации - на синхровход 23 блока 20.4 формирования коэффициентов СЛУ и значение  записывается в регистр 40 памяти блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 113 блока 11 синхронизации поступает на вход 34 считывания элемента 32.2.1 памяти в составе второго блока 9 памяти, с выхода 90 блока 11 синхронизации - на синхровход 24 блока 20.4 формирования коэффициентов СЛУ и значение

записывается в регистр 40 памяти блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 113 блока 11 синхронизации поступает на вход 34 считывания элемента 32.2.1 памяти в составе второго блока 9 памяти, с выхода 90 блока 11 синхронизации - на синхровход 24 блока 20.4 формирования коэффициентов СЛУ и значение  перемножается с

перемножается с  в блоке 41 перемножения блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 91 блока 11 синхронизации поступает на синхровход 25 блока 20.4 формирования коэффициентов СЛУ и результат перемножения

в блоке 41 перемножения блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 91 блока 11 синхронизации поступает на синхровход 25 блока 20.4 формирования коэффициентов СЛУ и результат перемножения  инвертируется в управляемом инверторе 42 блока 20.4 формирования коэффициентов СЛУ, после чего значение -

инвертируется в управляемом инверторе 42 блока 20.4 формирования коэффициентов СЛУ, после чего значение -  поступает на вход сумматора-накопителя 43 блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 111 блока 11 синхронизации поступает на вход 34 считывания элемента 32.1.2 в составе второго блока 9 памяти, с выхода 89 блока 11 синхронизации на синхровход 23 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение

поступает на вход сумматора-накопителя 43 блока 20.4 формирования коэффициентов СЛУ. Синхроимпульс с выхода 111 блока 11 синхронизации поступает на вход 34 считывания элемента 32.1.2 в составе второго блока 9 памяти, с выхода 89 блока 11 синхронизации на синхровход 23 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение  записывается в регистр 40 памяти блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 114 блока 11 синхронизации поступает на вход 34 считывания элемента 32.2.2 памяти в составе второго блока 9 памяти, с выхода 90 блока 11 синхронизации на синхровход 24 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение

записывается в регистр 40 памяти блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 114 блока 11 синхронизации поступает на вход 34 считывания элемента 32.2.2 памяти в составе второго блока 9 памяти, с выхода 90 блока 11 синхронизации на синхровход 24 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение  перемножается с

перемножается с  в блоке 41 перемножения блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 91 блока 11 синхронизации поступает на синхровход 25 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и результат перемножения

в блоке 41 перемножения блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 91 блока 11 синхронизации поступает на синхровход 25 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и результат перемножения  инвертируется в управляемом инверторе 42 блока 20.4 формирования коэффициентов СЛУ, после чего значение

инвертируется в управляемом инверторе 42 блока 20.4 формирования коэффициентов СЛУ, после чего значение  поступает на вход сумматора-накопителя 43 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 92 блока 11 синхронизации поступает на вход 26 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение, находящееся в сумматоре-накопителе 43 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти, поступает на вход операционного блока 8.1.1.

поступает на вход сумматора-накопителя 43 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти. Синхроимпульс с выхода 92 блока 11 синхронизации поступает на вход 26 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти и значение, находящееся в сумматоре-накопителе 43 блока 20.4 формирования коэффициентов СЛУ в составе второго блока 9 памяти, поступает на вход операционного блока 8.1.1.

Значение  с выхода операционного блока 8.1.2 поступает на информационный вход 33.3 второго блока 9 памяти и с поступлением синхроимпульса с выхода 74 блока 11 синхронизации на вход 36.2 оказывается записанным в элементе 32.2.3 в составе второго блока 9 памяти.

с выхода операционного блока 8.1.2 поступает на информационный вход 33.3 второго блока 9 памяти и с поступлением синхроимпульса с выхода 74 блока 11 синхронизации на вход 36.2 оказывается записанным в элементе 32.2.3 в составе второго блока 9 памяти.

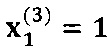

Таким образом, в элементах 32.2.1, 32.2.2, 32.2.3 второго блока 9 памяти будут записаны компоненты второго собственного вектора матрицы А (5):  ,

,  ,

,  .

.

По окончании времени, необходимого для вычисления компонент второго собственного вектора, с выхода 68 блока 11 синхронизации на тактовый вход регистра 7 сдвига поступает тактовый импульс, в результате чего второй разряд регистра 7 сдвига обнуляется. Так как на вход второго сомножителя блока 4.2.1 элементов И поступает «0» с выхода второго разряда регистра 7, то на выходе блока 4.2.1 элементов И формируется «0».

Вычисление компонент третьего собственного вектора производится следующим образом. На входы вторых сомножителей блоков 18 умножения блоков 3.1.1, 3.2.1, 3.3.1 вычислителей подается сигнал «1». С выхода блока 3.3.1 вычислителя значение  поступает на информационный вход 33.1 второго блока 9 памяти. С поступлением синхроимпульса с выхода 75 блока 11 синхронизации на вход 37.1 второго блока 9 памяти значение

поступает на информационный вход 33.1 второго блока 9 памяти. С поступлением синхроимпульса с выхода 75 блока 11 синхронизации на вход 37.1 второго блока 9 памяти значение  записывается в элемент 32.3.1 памяти в составе второго блока 9 памяти.

записывается в элемент 32.3.1 памяти в составе второго блока 9 памяти.

После этого осуществляется вычисление компонент  и

и  с использованием соотношений ортогональности:

с использованием соотношений ортогональности:

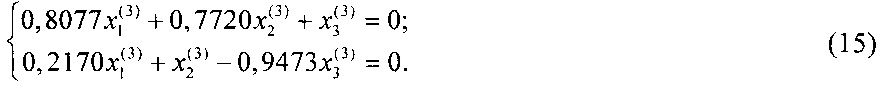

Так как значение  вычислено и записано в элементе 32.3.1 памяти в составе второго блока 9 памяти, то систему уравнений (15) можно представить в виде

вычислено и записано в элементе 32.3.1 памяти в составе второго блока 9 памяти, то систему уравнений (15) можно представить в виде

Эта система линейных уравнений легко решается методом Гаусса-Жордана. Поскольку коэффициенты при неизвестных и свободные члены записаны в блоке 9 памяти, то уравнение (16) решается следующим образом.

При поступлении синхроимпульса с выхода 111 блока 11 синхронизации на вход 34 считывания элемента 33.1.2 памяти второго блока 9 памяти значение 0,7720 считывается с него и при поступлении синхроимпульса с выхода 92 блока 11 синхронизации на вход 26 блока 20.4 формирования коэффициентов СЛУ второго блока 9 памяти через второй сумматор-накопитель 43 блока 20.4 формирования коэффициентов СЛУ значение 0,7720 поступает на вход операционного блока 8.1.1.

При поступлении синхроимпульса с выхода 114 блока 11 синхронизации на вход 34 считывания элемента 32.2.2 памяти второго блока 9 памяти значение «1» считывается с него и при поступлении синхроимпульса с выхода 96 блока 11 синхронизации на вход 26 блока 20.5 формирования коэффициентов СЛУ в составе второго блока 9 памяти через второй сумматор-накопитель 43 блока 20.5 формирования коэффициентов СЛУ значение «1» поступает на вход операционного блока 8.2.1.

Аналогичным образом считываются значения «1» из блока 32.1.3 памяти в составе второго блока 9 памяти и значение -0,9473 из блока 32.2.3 памяти в составе второго блока 9 памяти и поступает на входы операционных блоков 8.1.1 и 8.2.1. Аналогично считываются значения 0,8077 и 0,2170 и после инвертирования в управляемых инверторах 42 блоков 20.4 и 20.5 формирования коэффициентов СЛУ поступают на входы операционных блоков 8.1.1 и 8.2.1 соответственно.

В соответствии с алгоритмом работы операционных блоков 8 на выходах блоков 8.1.2 и 8.2.2 будут сформированы соответственно значения  и

и  , поступающие на входы 33.2 и 33.3 соответственно второго блока 9 памяти.

, поступающие на входы 33.2 и 33.3 соответственно второго блока 9 памяти.

С поступлением синхроимпульса с выхода 76 блока 11 синхронизации на вход 37.2 второго блока 9 памяти значение - 0,5673 окажется записанным в элементе 32.3.2 памяти, а значение - 0,3698 - в элементе 32.3.3 памяти.

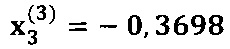

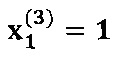

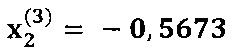

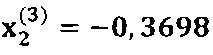

Таким образом, в элементах 32.3.1, 32.3.2 и 32.3.3 будут записаны компоненты третьего собственного вектора матрицы А (5):  ,

,  ,

,  . На этом процесс вычисления компонент собственных векторов матрицы А (5) заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

. На этом процесс вычисления компонент собственных векторов матрицы А (5) заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

В дальнейшем синхроимпульсы с выхода 119 блока 1 синхронизации поступают на тактовый вход трехразрядного регистра 12 сдвига. С остальных выходов блока 11 синхронизации синхроимпульсы не подаются.

В регистре 12 сдвига перед началом работы генератора функций был записан код вида «10…0» (для рассматриваемого случая - «100»), причем «1» записана в первом разряде трехразрядного регистра 12 сдвига. На тактовый вход трехразрядного регистра 12 сдвига поступает последовательность импульсов с выхода 119 блока 11 синхронизации, «1», перемещаясь из разряда в разряд трехразрядного регистра 12 сдвига, управляет формированием дискретных базисных функций на выходах генератора, так как выходы разрядов трехразрядного регистра 12 сдвига подключены к входам 34 считывания элементов 32.1.1-32.1.3, 32.2.1-32.2.3, 32.3.1-32.3.3 памяти второго блока 9 памяти. При этом первый разряд трехразрядного регистра 12 сдвига подключен к входам 34 считывания элементов 32.1.1, 32.2.1, 32.3.1. второй разряд - к входам 34 считывания элементов 32.2.1, 32.2.2, 32.3.2, третий разряд - к входам 34 считывания элементов 32.1.3, 32.2.3, 32.3.3. Таким образом, на выходах второго блока 9 памяти будет формироваться, периодически повторяясь, система кусочно-постоянных дискретных базисных функций (ансамбля стохастических ортогональных кодов) S1(t), S2(t), S3(t):

S1(t)=(0,8077; 0,7720; 1),

S2(t)=(0; 2170; 1; -0,9473),

S3(t)=(1; -0,5673; -0,3698).

В дальнейшем в случае формирования генератором 14 ПСЧ других псевдослучайных чисел, используемых в качестве псевдослучайных коэффициентов для формирования действительной симметрической положительно определенной матрицы, и записи этих коэффициентов в блок 6 памяти на выходах генератора стохастических ортогональных кодов формируется другая система дискретных базисных функций.

При увеличении размерности исходных матриц число дискретных базисных функций увеличивается. При этом значения периодов генерируемых функций и число значений базисных функций имеют весьма широкий набор, что позволяет повысить точность решения задач обобщенного спектрального анализа и синтеза путем лучшего согласования длины периода обрабатываемого сигнала с длиной периода базисных функций и представления сигнала малым числом коэффициентов преобразования по системе базисных функций.

Когда третий разряд регистра 12 подает команду с 1 выхода на входы 34 считывания элементов 32.1.3, 32.2.3, 32.3.3, с второго выхода он подает команду на формирование очередного набора коэффициентов симметрической матрицы вида (1) на первый вход микроконтроллера 13. Таким образом реализуется возможность автоматизации процесса формирования входных данных.

После поступления команды на первый вход микроконтроллер 13 с первого выхода подает команду на первый вход генератора 14 ПСЧ, который генерирует новый набор псевдослучайных коэффициентов верхней треугольной матрицы для формирования матрицы вида (1), что обеспечивает формирование на выходах 38.1-38.3 второго блока 9 памяти системы стохастических ортогональных кодов, соответствующей заданным коэффициентам симметрической матрицы вида (1).

В дальнейшем в процессе формирования генератором 14 ПСЧ набора коэффициентов матрицы вида (1) на выходе заявляемого устройства также будут формироваться соответствующие им системы стохастических ортогональных кодов.

Генератор стохастических ортогональных функций, содержащий генератор функций Попенко-Турко, содержащего матрицу вычислителей, с первой по (Р-1)-й группы блоков элементов И (Р - порядок квадратной матрицы коэффициентов), с второй по (Р-1)-ю группы блоков деления, первый блок памяти, двухразрядный регистр сдвига, матрицу операционных блоков, второй блок памяти, с первого по (Р-2)-й элементы задержки, блок синхронизации, трехразрядный регистр сдвига, причем выход вычислителя i-й строки (i=1, Р-1, Р - порядок квадратной матрицы коэффициентов) матрицы вычислителей соединены с первым информационным входом соответствующего вычислителя (i+1)-й строки матрицы вычислителей, второй выход вычислителя i-гo столбца матрицы вычислителей соединен со вторым информационным входом соответствующего вычислителя (i+1)-го столбца матрицы вычислителей, к вторым информационным входам вычислителей первого столбца матрицы вычислителей подается логический ноль, второй выход вычислителя (i+1)-й строки (i+1)-го столбца матрицы соединен с входами делителя блоков деления (Р-i)-й группы, вход делимого j-го блока деления (j=1, Р-i) i-й группы соединен с вторым выходом вычислителя j-й строки (Р-i+1)-го столбца матрицы, выход j-го блока деления i-й группы соединен с первым входом элементов И j-го блока i-й группы, вторые входы блоков элементов И i-й группы соединены с выходом i-го разряда двухразрядного регистра сдвига, выходы блока синхронизации соединены соответственно с тактовыми входами операционных блоков матрицы, с тактовыми входами с первого по (Р-2)-й элементов задержки, с входом разрешения сдвига двухразрядного регистра сдвига, с входами разрешения записи первого блока памяти, с входами разрешения записи второго блока памяти, с тактовыми входами первого и второго блоков памяти, с входами разрешения считывания первого и второго блоков памяти и с входом разрешения сдвига трехразрядного регистра сдвига, выходы j-x блоков элементов И с первой по (Р-1)-ю группы соединены с первым информационным входом вычислителя (j+1)-й строки j-го столбца матрицы, выходы вычислителей последней строки матрицы соединены с соответствующими информационными входами второго блока памяти, первый информационный вход операционного блока i-й строки первого столбца матрицы соединен с i-м выходом второго блока памяти, первые выходы операционных блоков i-й строки S-x (S=i, Р-1, Р - порядок квадратной матрицы коэффициентов) столбцов матрицы соединены с (Р-i+1)-м информационным входом группы второго блока памяти, первый информационный вход операционного блока К-й (К=1, Р-2, Р - порядок квадратной матрицы коэффициентов) строки М-го (М=2, Р-1, Р - порядок квадратной матрицы коэффициентов) столбца матрицы соединен с первым выходом операционного блока (К+1)-й строки (M-1)-го столбца матрицы, первый информационный вход операционного блока (Р-2)-й строки М-го столбца матрицы подключен к выходу М-го элемента задержки, информационный вход которого подключен к второму выходу операционного блока (Р-1)-й строки (M-1)-го столбца матрицы, второй информационный вход операционного блока М-й строки i-го столбца матрицы подключен к второму выходу операционного блока (М-1)-й строки i-го столбца матрицы, входы значения компонент исходной матрицы генератора функций Попенко-Турко соединены соответственно с информационными входами группы первого блока памяти, выходы которого соединены с третьими информационными входами вычислителей соответствующих строк матрицы, К-й выход второго блока памяти соединен с (К-М)-м дополнительным информационным входом группы первого блока памяти, выходы разрядов трехразрядного регистра сдвига соединены с соответствующими входами разрешения считывания второго блока памяти, выходы которого являются выходами группы генератора, отличающийся тем, что, с целью автоматизации процесса формирования исходных данных и обеспечения формирования систем стохастических ортогональных кодов, введен блок стохастического формирования коэффициентов симметрической матрицы, содержащий микроконтроллер, генератор псевдослучайных чисел, блок накопителя, блоки оперативного запоминающего устройства (ОЗУ), причем первый выход микроконтроллера подключен к первому входу генератора ПСЧ, второй выход микроконтроллера подключен к второму входу блока накопителя, первым управляющим записью входам блоков ОЗУ и первому входу блока синхронизации, третий выход микроконтроллера подключен к первому входу блока накопителя, первый выход генератора ПСЧ подключен к третьему входу блока накопителя, выходы блока накопителя подключены к третьим информационным входам блоков ОЗУ таким образом, чтобы из коэффициентов в виде набора ПСЧ верхней треугольной матрицы была получена симметрическая матрица, второй выход третьего разряда регистра сдвига подключен к первому входу микроконтроллера, выходы блока синхронизации, управляющие записью псевдослучайных коэффициентов симметрической матрицы в столбцы элементов первого блока памяти, подключены к соответствующим управляющим входам соответствующих столбцов блоков ОЗУ, информационные выходы блоков ОЗУ каждого столбца по общей для каждого из столбцов блоков ОЗУ шине подключены к соответствующим информационным входам первого блока памяти.