Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ

Вид РИД

Изобретение

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых или биполярных транзисторах, выполненные на основе дифференциального каскада с симметричной активной нагрузкой в виде источников опорного тока [1-16]. Их основное достоинство - повышенный коэффициент усиления по напряжению, который обеспечивается двумя каскадами усиления.

Для работы в условиях космического пространства, в экспериментальной физике необходимы радиационно стойкие ОУ с повышенным коэффициентом усиления по напряжению и максимальными амплитудами выходного напряжения (Um(+), Um(-)), близкими к напряжению питания. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [17], обеспечивающего формирование p-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [17].

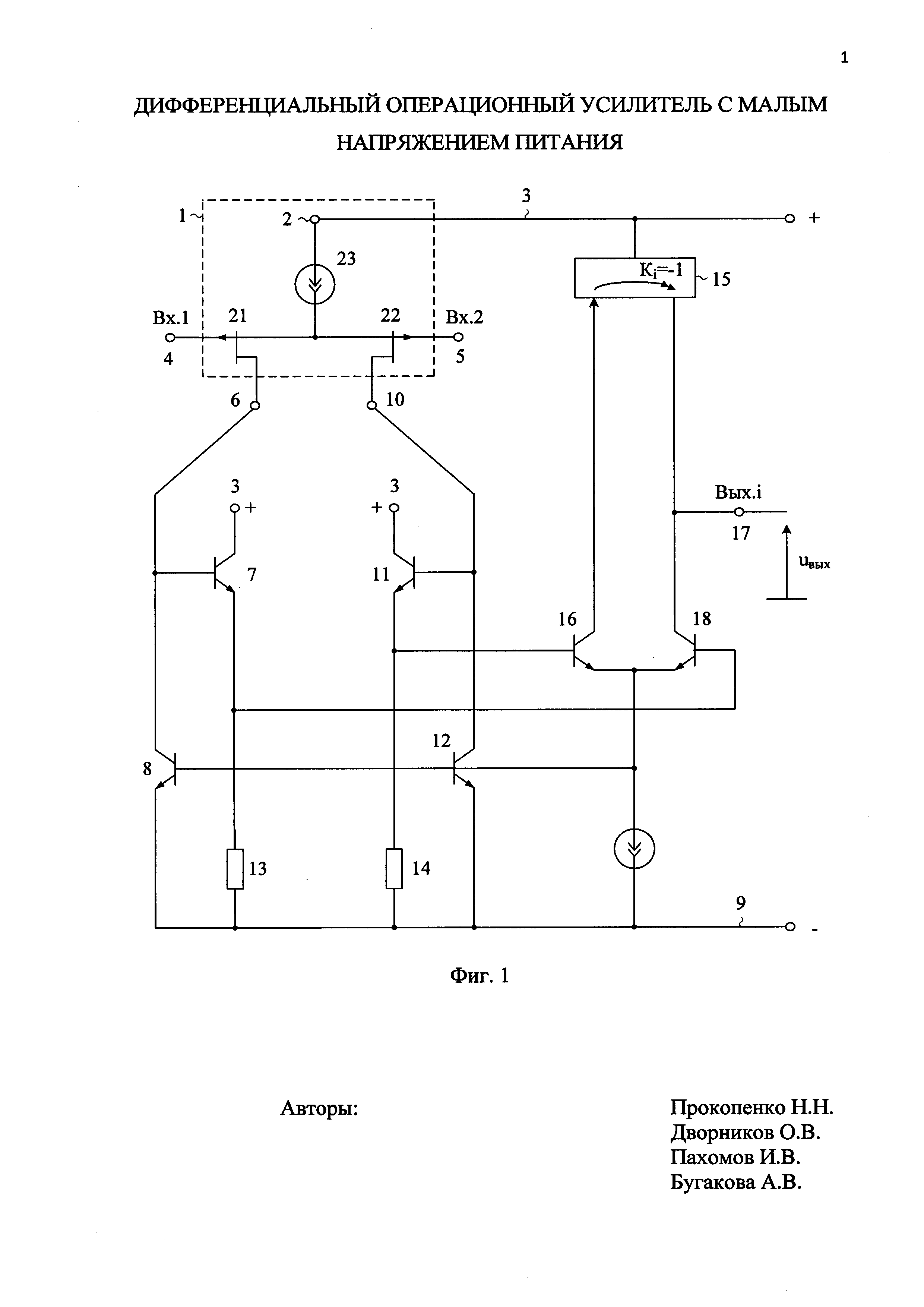

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, опубликованный в статье S. Groner «А new audio amplifier topology with push-pull transimpedance stage - Part 1: Introduction)), fig. 3.; EETimes Connecting the Global Electronic Community 29.08.2012, http://www.eetimes.com/document.asp?doc_id=1279853&page_number=3.

Он содержит (фиг. 1) входной дифференциальный каскад 1, общая цепь питания которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 основные входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 вспомогательного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 вспомогательного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, эмиттер первого 7 вспомогательного транзистора связан со второй 9 шиной источника питания через первый 13 токостабилизирующий двухполюсник, эмиттер второго 11 вспомогательного транзистора связан со второй 9 шиной источника питания через второй 14 токостабилизирующий двухполюсник, причем коллекторы первого 7 и второго 11 вспомогательных транзисторов связаны с первой 3 шиной источника питания, цепь динамической нагрузки 15, согласованную с первой 3 шиной источника питания, вход которой связан с коллектором первого 16 выходного транзистора, а выход связан с токовым выходом устройства 17 и коллектором второго 18 выходного транзистора, причем база первого 16 выходного транзистора подключена к эмиттеру второго 11 вспомогательного транзистора, а база второго 18 выходного транзистора подключена к эмиттеру первого 7 вспомогательного транзистора.

Существенный недостаток известного ОУ состоит в том, что в нем не обеспечивается широкий диапазон изменения выходного напряжения, что особенно проявляется при низковольтном питании (2,5÷5 В). Кроме этого ОУ-прототип не может применяться в схемах инвертирующих усилителей и алгебраических сумматоров нескольких сигналов без резисторов обратной связи. В конечном итоге это снижает универсальность известного ОУ, который может применяться только в традиционных схемах включения.

Основная задача предлагаемого изобретения состоит в расширении диапазона изменения выходного напряжения ОУ до уровней, близких к напряжениям на положительной 3 и отрицательной 9 шинах питания.

Дополнительная задача - расширение функциональных возможностей ОУ, касающихся перспективных схем его инвертирующего и неинвертирующего включения, в т.ч. без резисторов обратной связи.

Поставленные задачи достигаются тем, что в дифференциальном операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1, общая цепь питания которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 основные входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 вспомогательного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 вспомогательного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, эмиттер первого 7 вспомогательного транзистора связан со второй 9 шиной источника питания через первый 13 токостабилизирующий двухполюсник, эмиттер второго 11 вспомогательного транзистора связан со второй 9 шиной источника питания через второй 14 токостабилизирующий двухполюсник, причем коллекторы первого 7 и второго 11 вспомогательных транзисторов связаны с первой 3 шиной источника питания, цепь динамической нагрузки 15, согласованную с первой 3 шиной источника питания, вход которой связан с коллектором первого 16 выходного транзистора, а выход связан с токовым выходом устройства 17 и коллектором второго 18 выходного транзистора, причем база первого 16 выходного транзистора подключена к эмиттеру второго 11 вспомогательного транзистора, а база второго 18 выходного транзистора подключена к эмиттеру первого 7 вспомогательного транзистора, предусмотрены новые элементы и связи - между эмиттерами первого 7 и второго 11 вспомогательных транзисторов включены последовательно соединенные первый 19 и второй 20 дополнительные резисторы, общий узел которых связан с объединенными базами первого 8 транзистора первого источника опорного тока и второго 12 транзистора второго источника опорного тока, причем эмиттер первого 16 выходного транзистора подключен ко второй 9 шине источника питания, а эмиттер второго 18 выходного транзистора связан со второй 9 шиной источника питания.

Чертежи

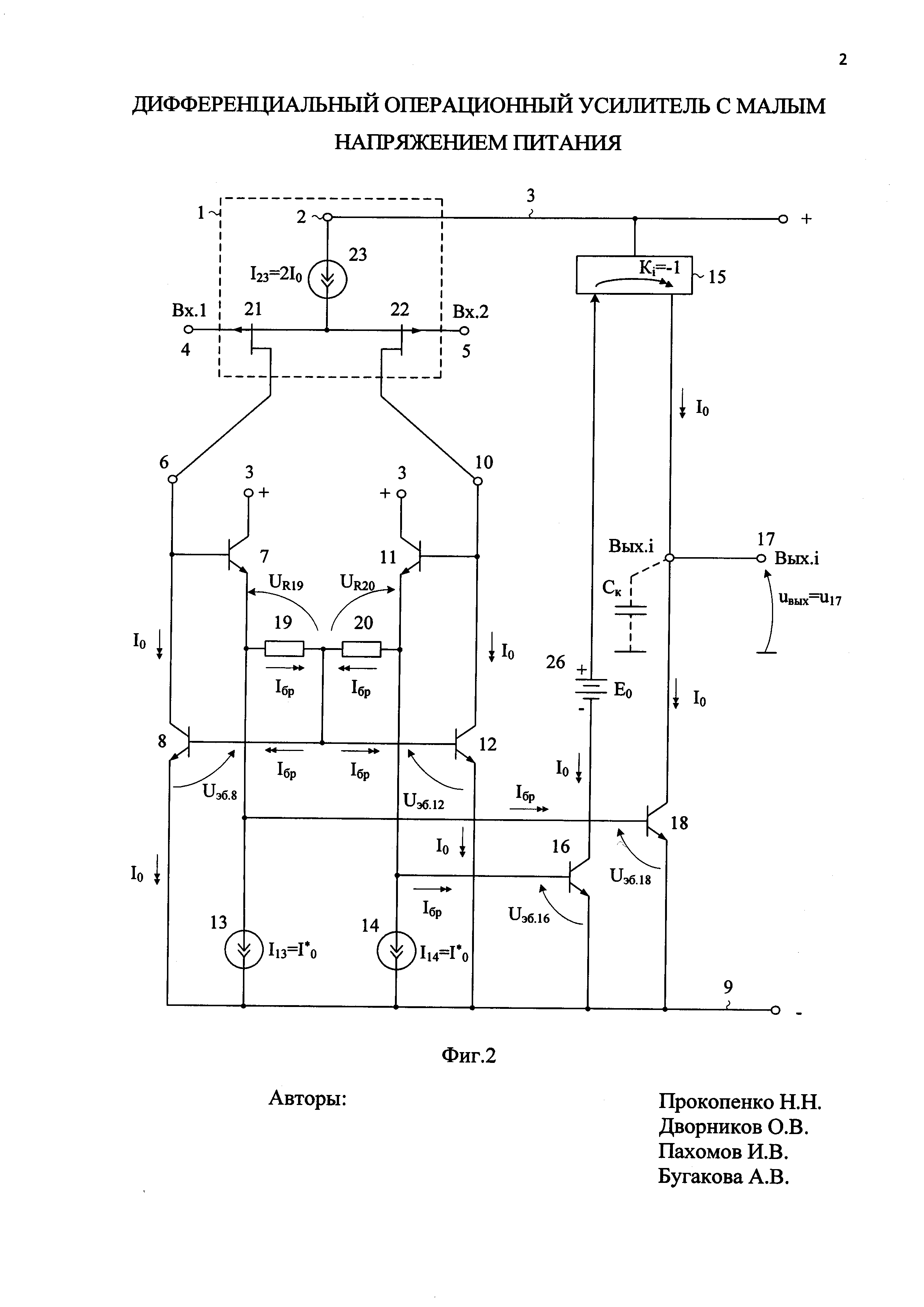

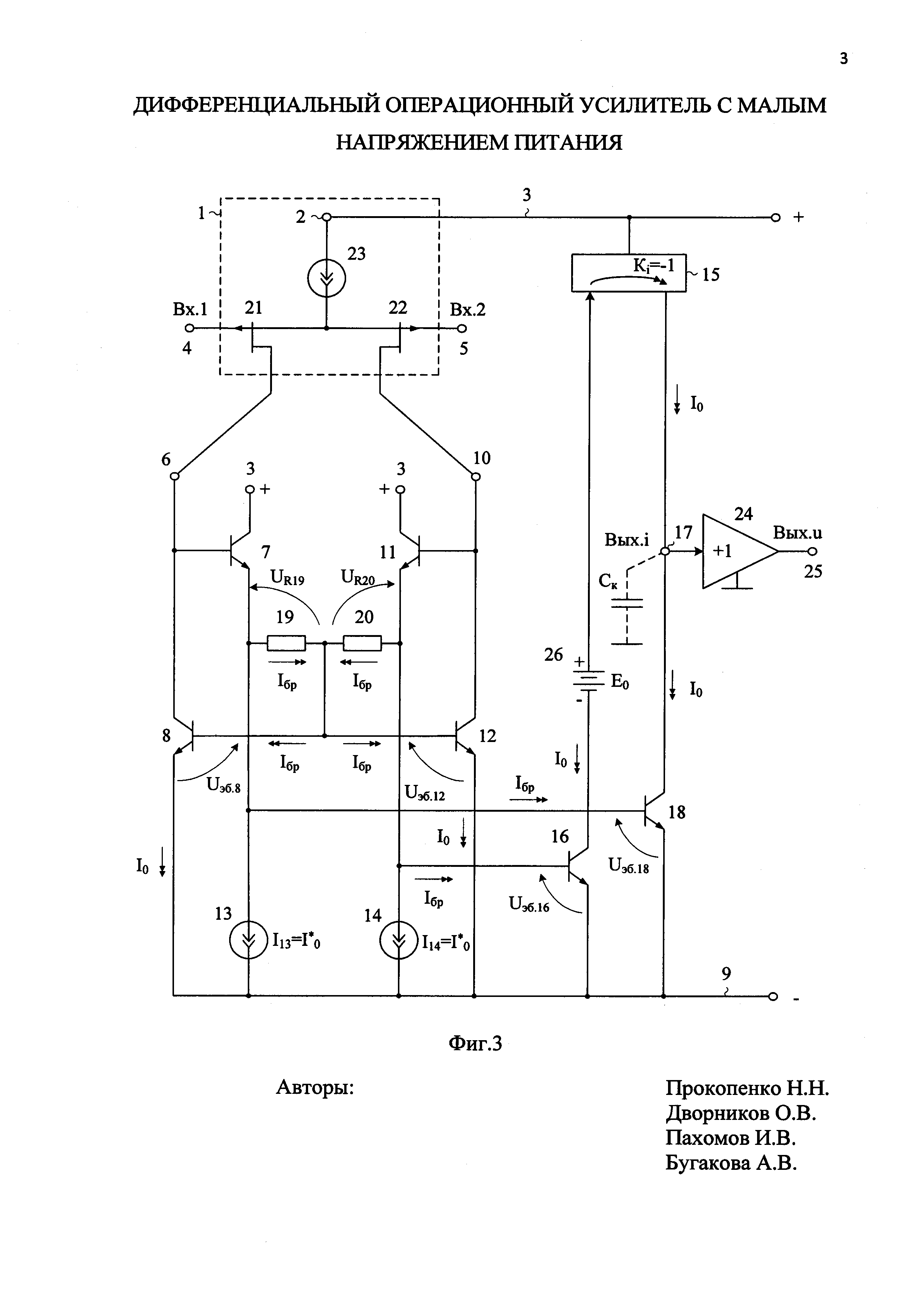

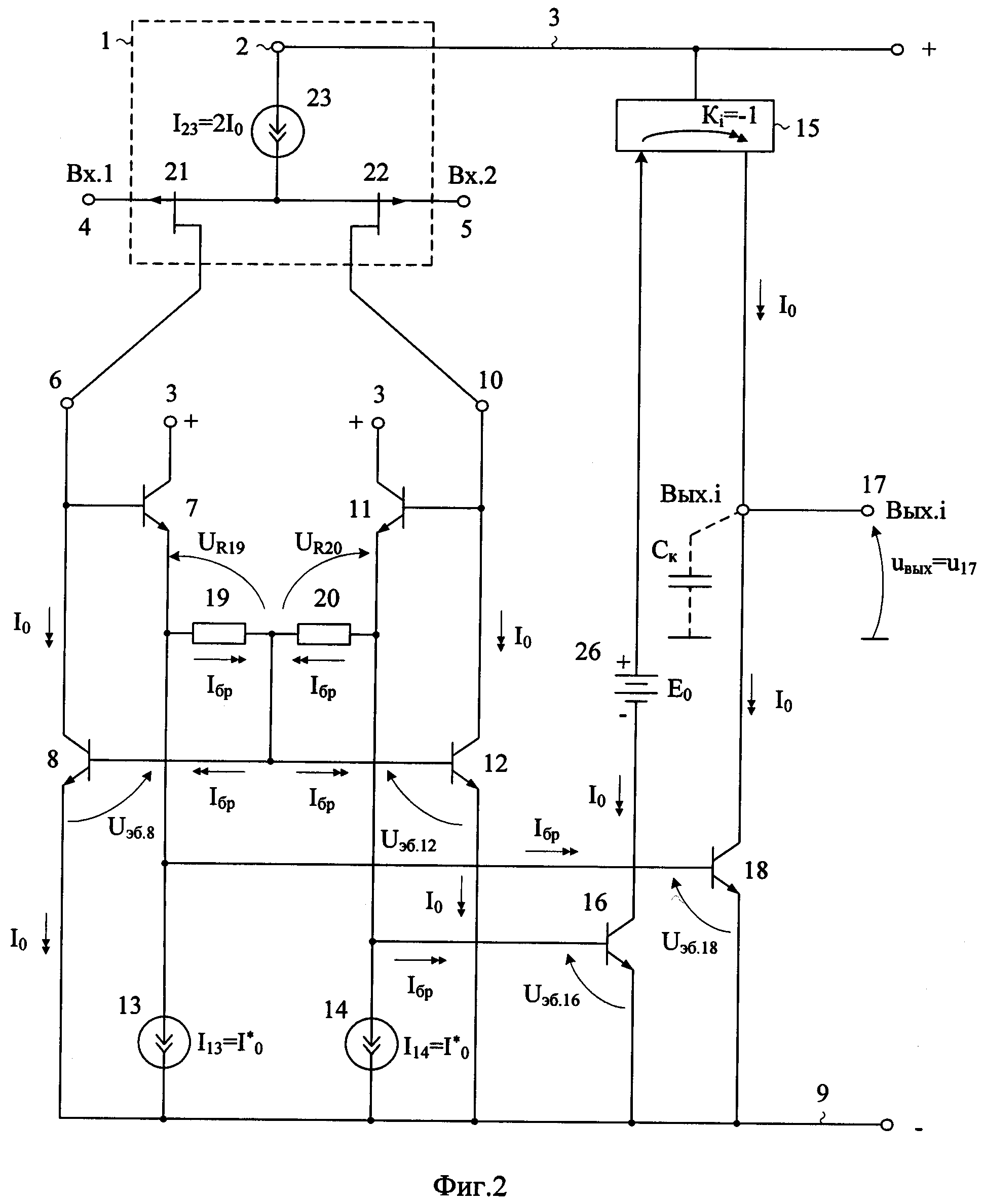

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

На фиг. 3 приведена схема фиг. 2, в которой предусмотрен выходной буферный усилитель 24, обеспечивающий низкоомный (потенциальный) выход устройства 25.

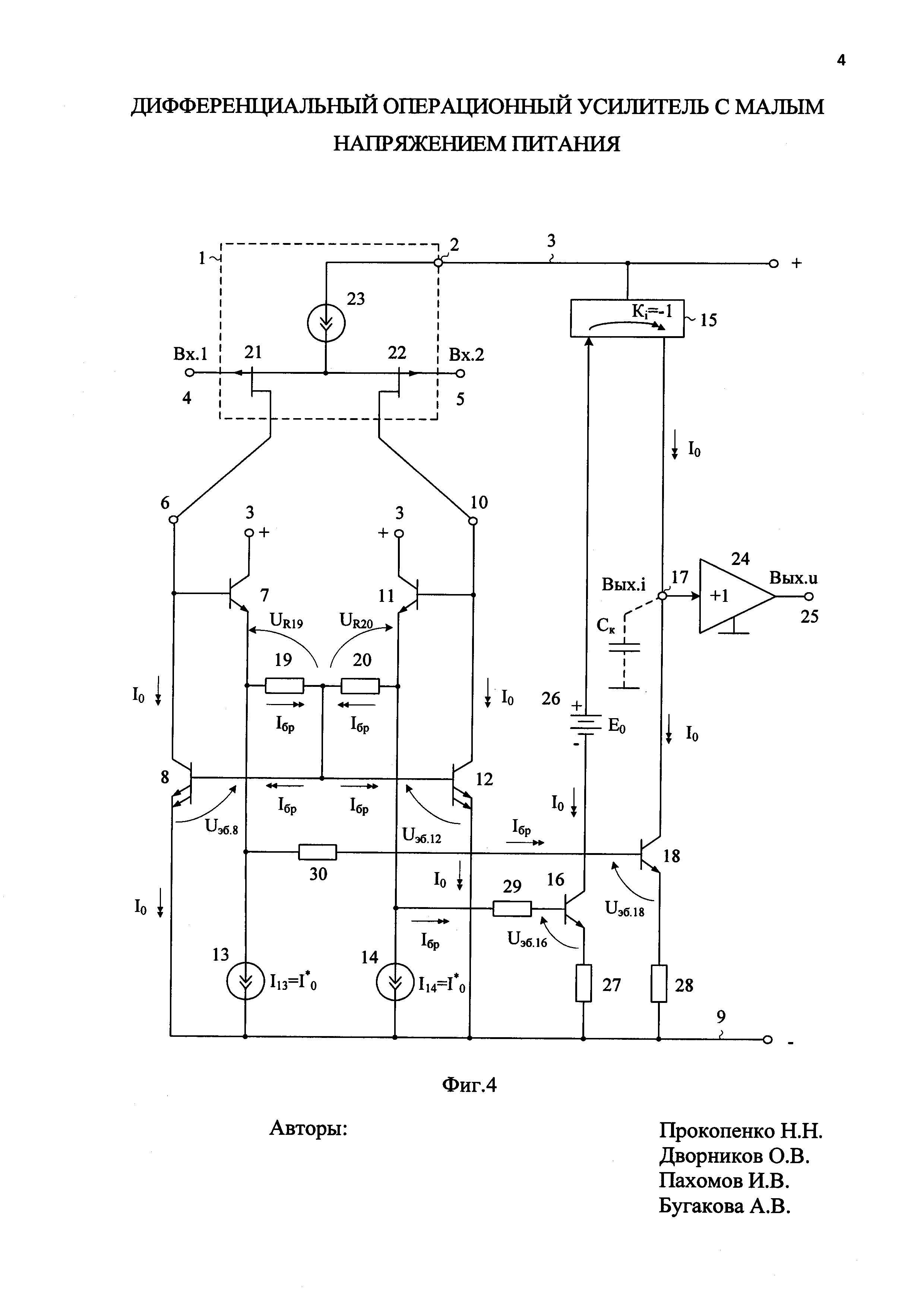

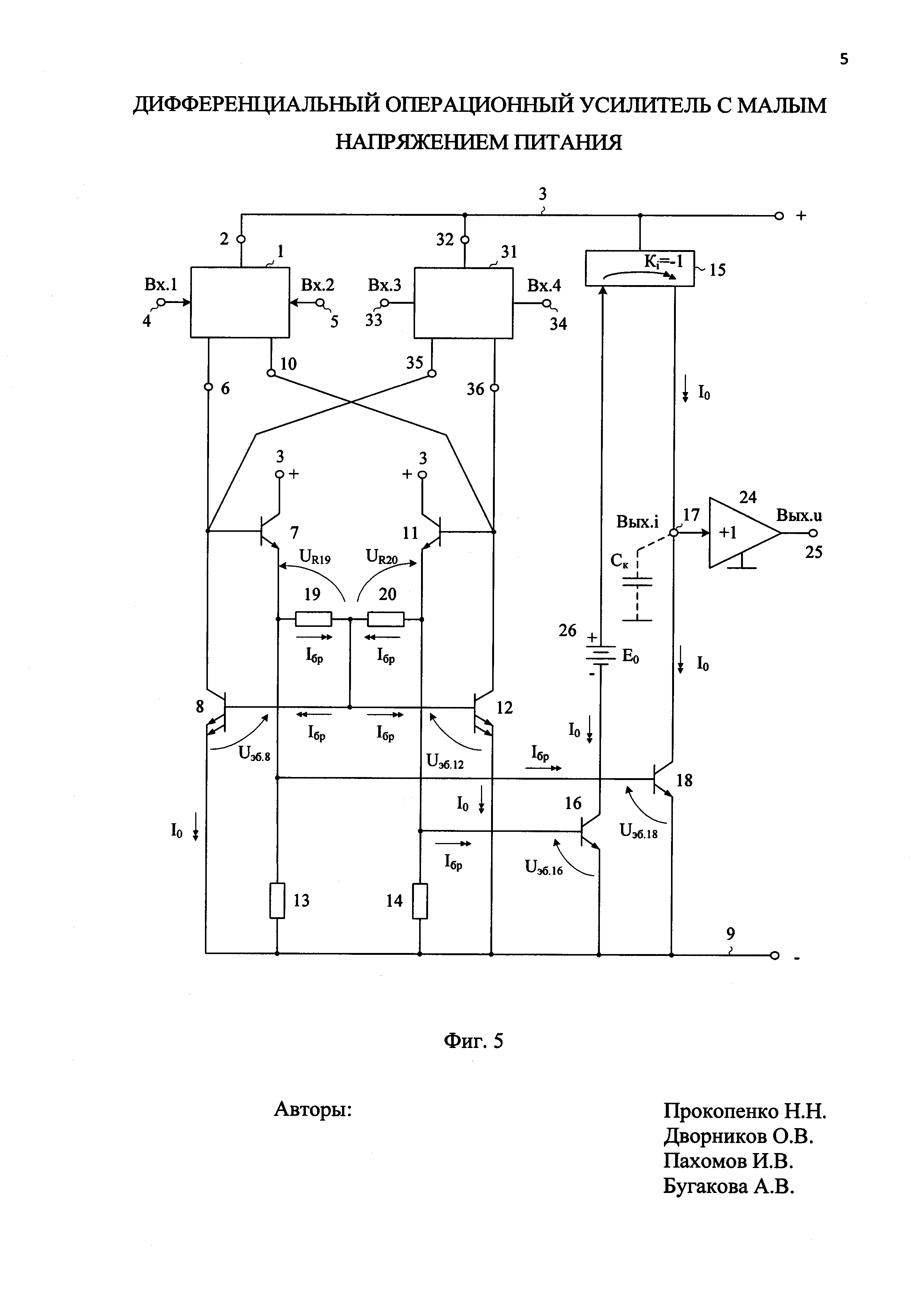

На чертеже фиг. 4 приведена схема заявляемого устройства в соответствии с п. 2 и п. 3, а на фиг. 5 - п. 4 формулы изобретения.

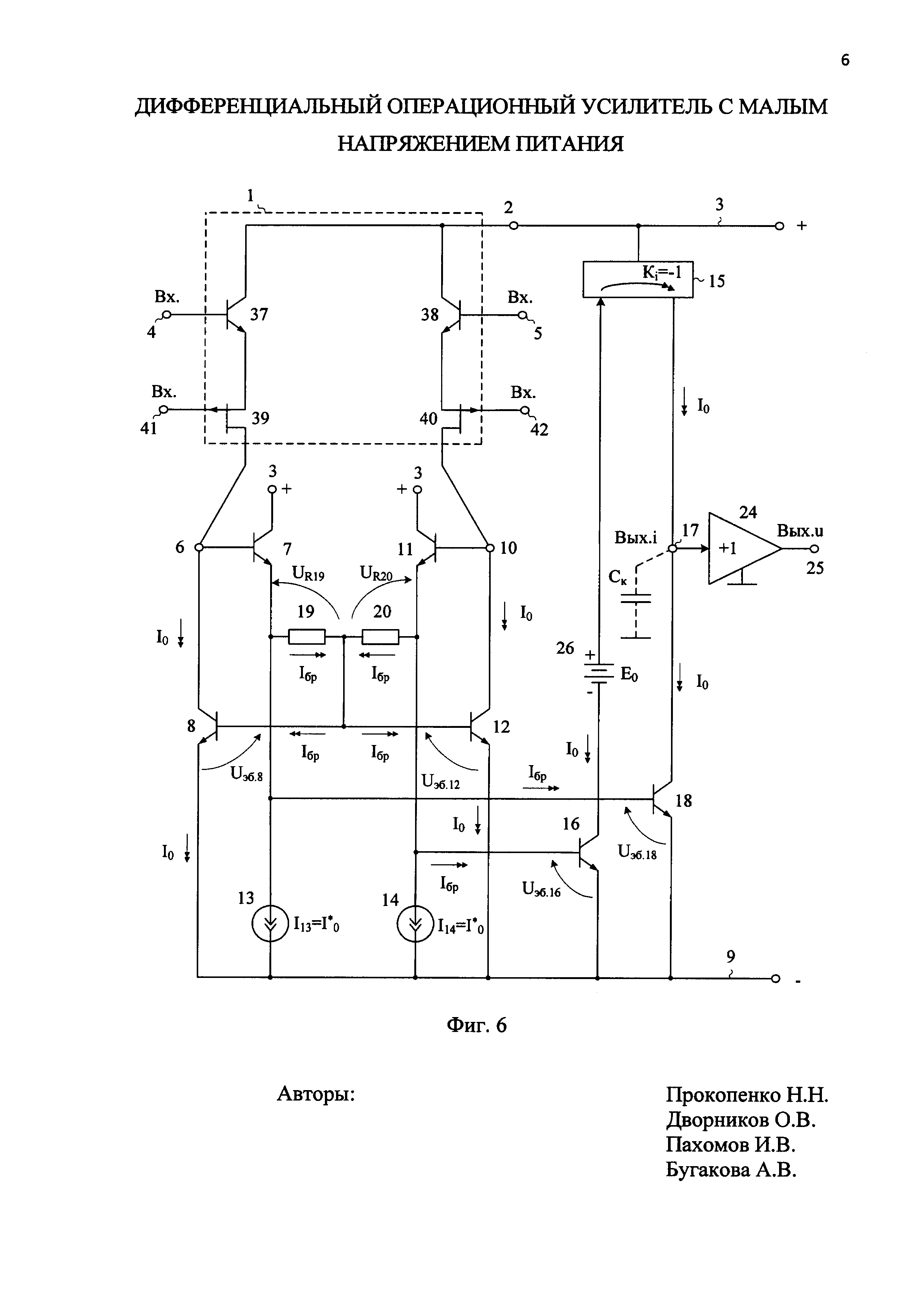

На фиг. 6 представлена схема заявляемого устройства в соответствии с п. 5 формулы изобретения.

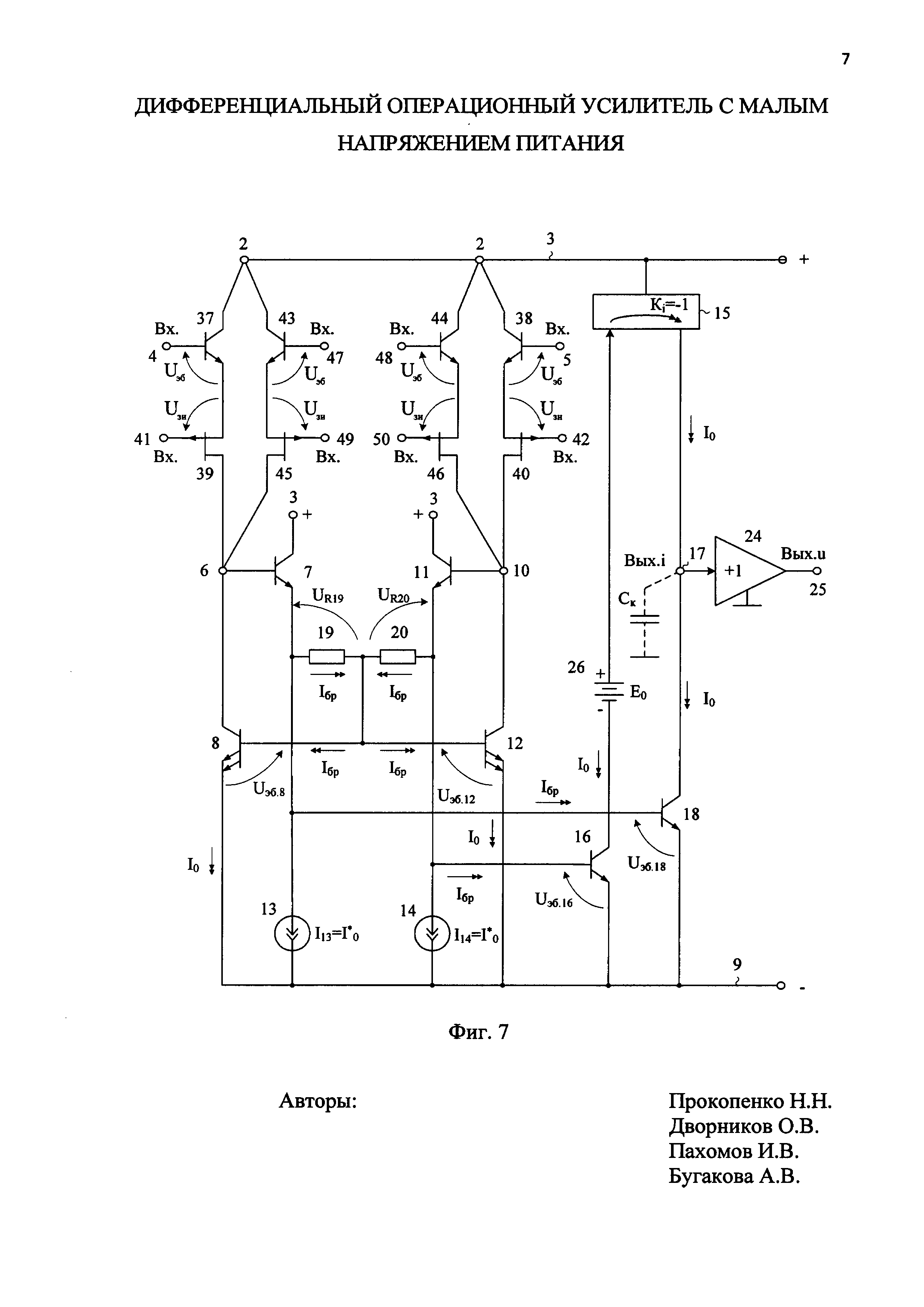

На фиг. 7 представлена схема заявляемого устройства в соответствии с п. 6 формулы изобретения.

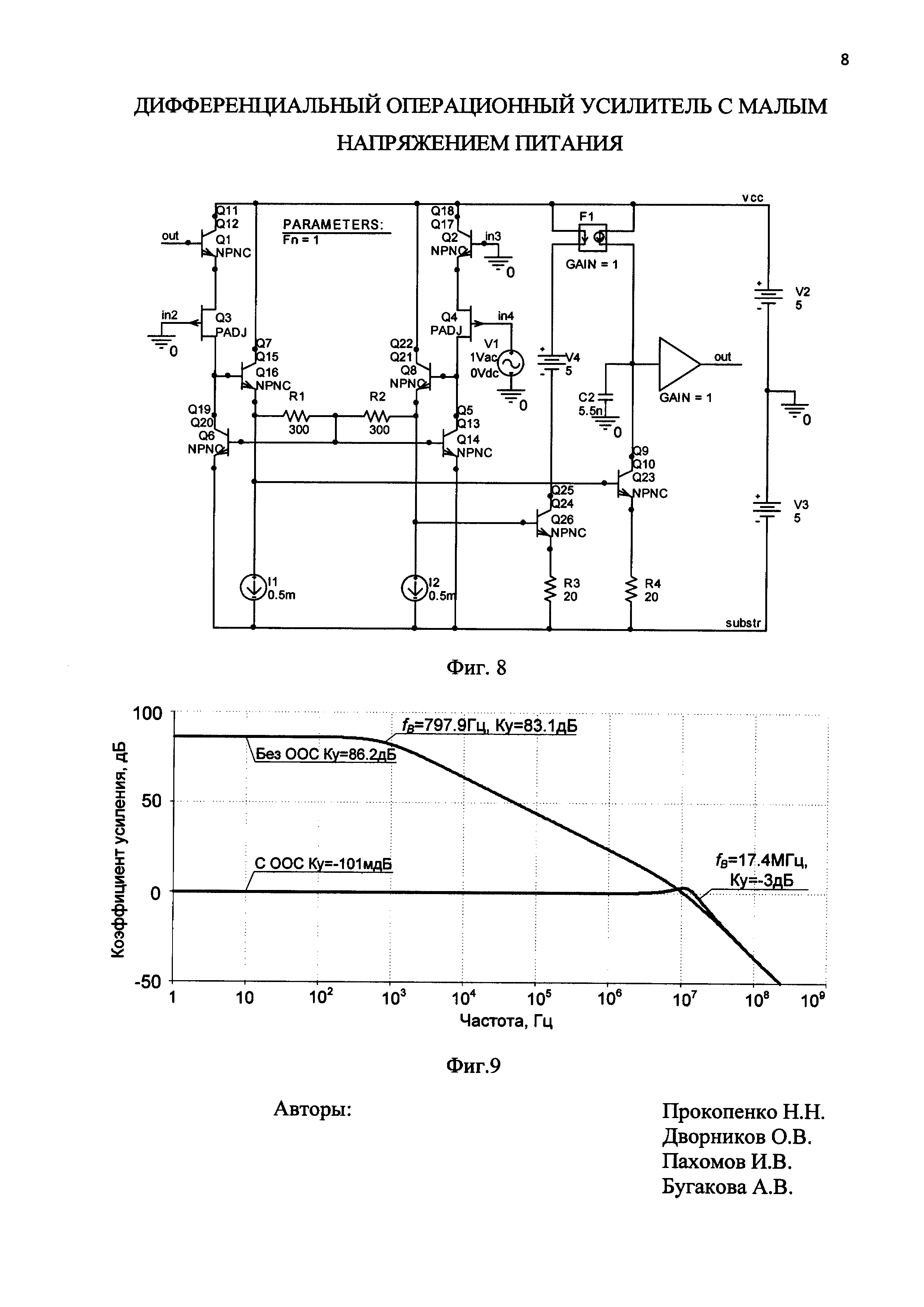

На фиг. 8 приведена схема заявляемого устройства фиг. 6 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск) для случая его инвертирующего включения с отрицательной обратной связью, которая вводится на базу транзистора Q1.

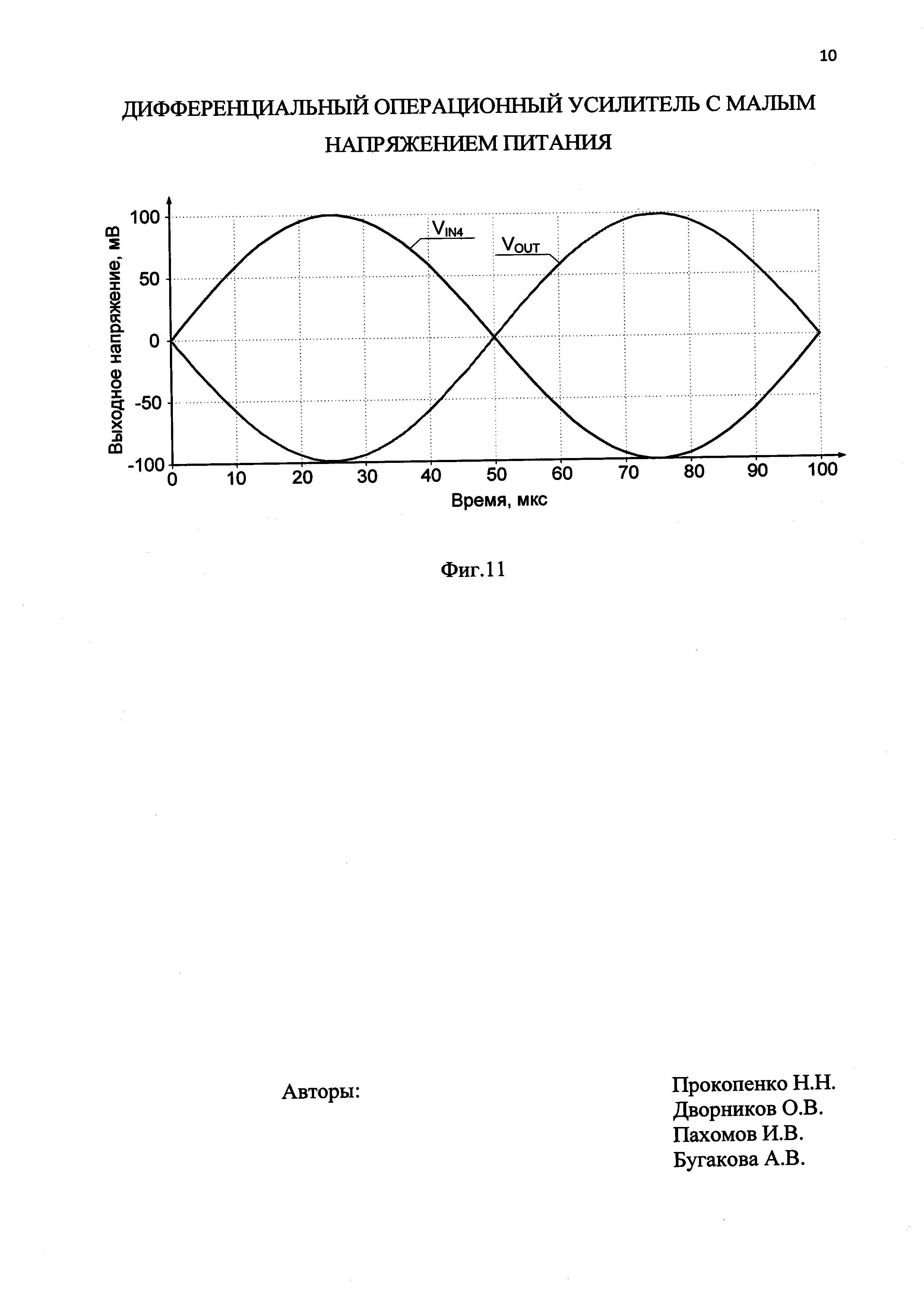

На фиг. 9 показаны амплитудно-частотные характеристики операционного усилителя фиг. 8 без отрицательной обратной связи и со 100% отрицательной обратной связью (ООС).

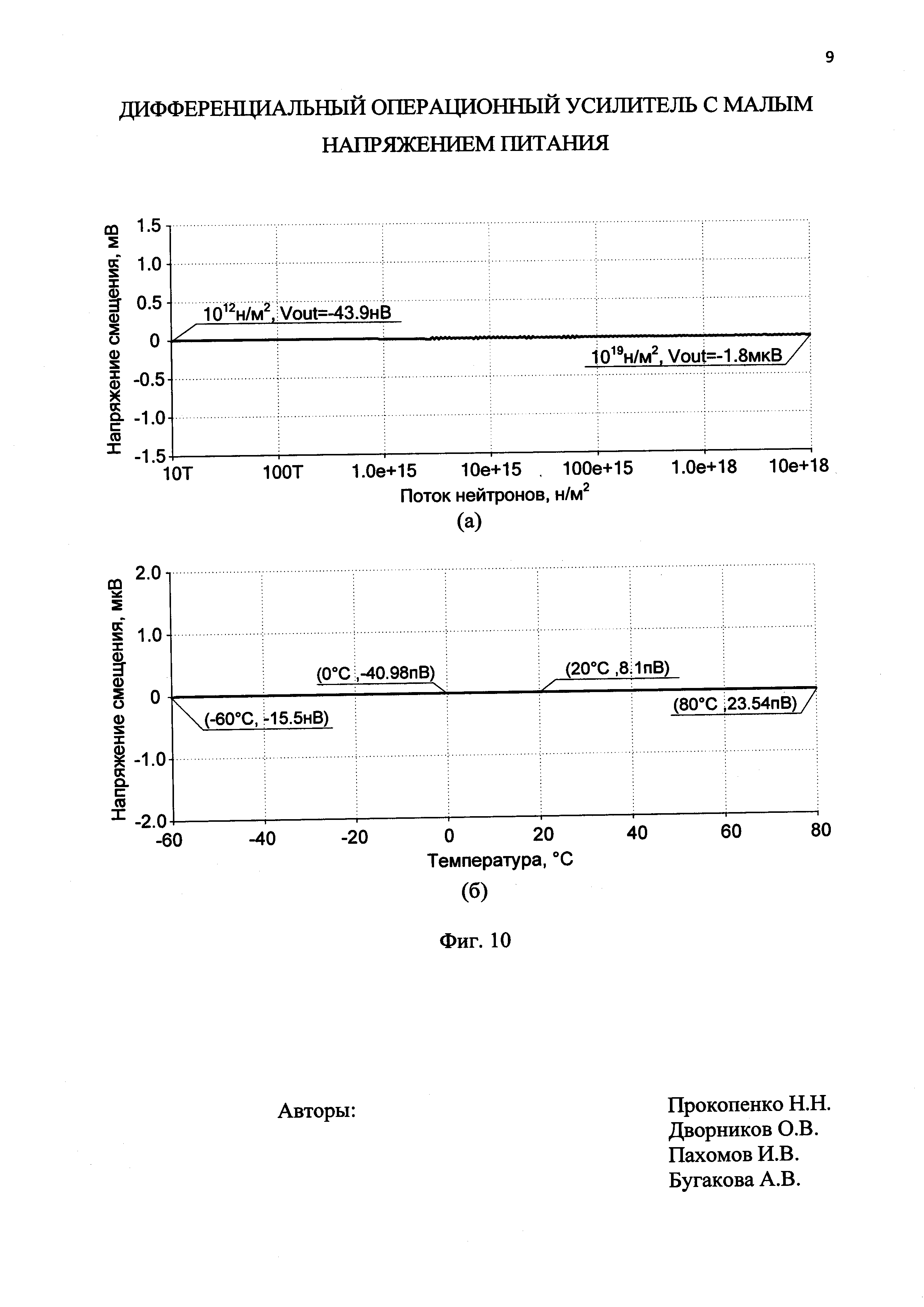

На фиг. 10 приведена зависимость напряжения смещения нуля ОУ фиг. 8 от потока нейтронов (а) и температуры в диапазоне минус 60-80°С (б).

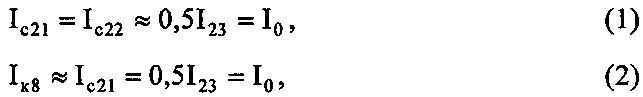

На фиг. 11 приведены временные характеристики входного и выходного синусоидального напряжения схемы фиг. 8, которые показывают, что выходное напряжение заявляемого устройства противофазно его входному напряжению, а его коэффициент передачи Kу≈-1. На основе классических схем ОУ, в т.ч. ОУ-прототипа, такие устройства без резисторов обратной связи не реализуются.

Дифференциальный операционный усилитель с малым напряжением питания фиг. 2 содержит входной дифференциальный каскад 1, общая цепь питания которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 основные входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с базой первого 7 вспомогательного транзистора и коллектором первого 8 транзистора первого источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с базой второго 11 вспомогательного транзистора и коллектором второго 12 транзистора второго источника опорного тока, эмиттер которого связан со второй 9 шиной источника питания, эмиттер первого 7 вспомогательного транзистора связан со второй 9 шиной источника питания через первый 13 токостабилизирующий двухполюсник, эмиттер второго 11 вспомогательного транзистора связан со второй 9 шиной источника питания через второй 14 токостабилизирующий двухполюсник, причем коллекторы первого 7 и второго 11 вспомогательных транзисторов связаны с первой 3 шиной источника питания, цепь динамической нагрузки 15, согласованную с первой 3 шиной источника питания, вход которой связан с коллектором первого 16 выходного транзистора, а выход связан с токовым выходом устройства 17 и коллектором второго 18 выходного транзистора, причем база первого 16 выходного транзистора подключена к эмиттеру второго 11 вспомогательного транзистора, а база второго 18 выходного транзистора подключена к эмиттеру первого 7 вспомогательного транзистора. В схеме между эмиттерами первого 7 и второго 11 вспомогательных транзисторов включены последовательно соединенные первый 19 и второй 20 дополнительные резисторы, общий узел которых связан с объединенными базами первого 8 транзистора первого источника опорного тока и второго 12 транзистора второго источника опорного тока, причем эмиттер первого 16 выходного транзистора подключен ко второй 9 шине источника питания, а эмиттер второго 18 выходного транзистора связан со второй 9 шиной источника питания.

В схемах фиг. 2 и фиг. 3 входной дифференциальный каскад выполнен в частном случае на основе полевых транзисторов 21, 22 и источнике опорного тока 23. В некоторых схемах включения ОУ фиг. 3 может быть предусмотрен буферный усилитель 24, вход которого связан с токовым выходом устройства 17, а выход 25 является потенциальным выходом устройства. Для уменьшения влияния напряжения Эрли транзистора 16 на напряжение смещения нуля в схему введен источник опорного напряжения 26, который может быть выполнен в виде стабилитрона, резистора или цепочки прямосмещенных p-n-переходов. Коррекция амплитудно-частотной характеристик ОУ может осуществляться с помощью корректирующего конденсатора Ск.

Статический ток токостабилизирующих двухполюсников 13 и 14  может быть значительно меньше, чем ток I0.

может быть значительно меньше, чем ток I0.

В качестве токового зеркала 15 могут использоваться классические токовые зеркала на биполярных и полевых транзисторах [16, 17].

На фиг. 4, в соответствии с п. 2 формулы изобретения, эмиттер первого 16 выходного транзистора, подключен ко второй 9 шине источника питания через первый 21 согласующий резистор, а эмиттер второго 18 выходного транзистора связан со второй 9 шиной источника питания через второй 22 согласующий резистор.

Кроме этого, в соответствии с п. 3 формулы изобретения, здесь база первого 16 выходного транзистора связана с эмиттером первого 7 вспомогательного транзистора через третий 29 согласующий резистор, а база второго 18 выходного транзистора соединена с эмиттером второго 11 вспомогательного транзистора через четвертый 30 согласующий резистор.

В ряде случаев транзисторы 8 и 12 могут выполняться в виде многоэмиттерных транзисторов, что может улучшить согласование статического режима транзисторов 8 (12) и 18 (16).

На фиг. 5, в соответствии с п. 4 формулы изобретения, в схему введен дополнительный входной дифференциальный каскад 31, общая цепь питания которого 32 связана с первой 3 шиной источника питания, имеющий первый 33 и второй 34 дополнительные входы, причем первый 35 токовый выход дополнительного входного дифференциального каскада 31 связан с базой первого 7 вспомогательного транзистора, а второй 36 токовый выход дополнительного входного дифференциального каскада 31 связан с базой второго 11 вспомогательного транзистора.

На фиг. 5 токостабилизирующие двухполюсники 13 и 14 выполнены в частном случае на основе резисторов. В качестве дополнительного входного дифференциального каскада 31 могут применяться такие же схемы, как и в качестве входного дифференциального каскада 1 (см., например, фиг. 2).

На основе схемы фиг. 5 реализуется широкий класс новых аналоговых устройств, в которых дополнительный инвертирующий вход используется для введения общей отрицательной обратной связи, а входы 4, 5 - для подачи входных сигналов. При этом схема фиг. 5 по входам 4, 5 является дифференциальным усилителем.

На фиг. 6, в соответствии с п. 5 формулы изобретения, входной дифференциальный каскад 1 выполнен на основе первого 37 и второго 38 биполярных транзисторов, а также первого 39 и второго 40 полевых транзисторов с управляющим p-n-переходом, причем коллекторы первого 37 и второго 38 биполярных транзисторов соединены с общей цепью питания 2 входного дифференциального каскада 1 и связаны с первой 3 шиной источника питания, база первого 37 биполярного транзистора соединена с первым 4 основным входом входного дифференциального каскада 1, база второго 38 биполярного транзистора соединена со вторым 5 основным входом входного дифференциального каскада 1, эмиттер первого 37 биполярного транзистора соединен с истоком первого 39 полевого транзистора с управляющим p-n переходом, эмиттер второго 38 биполярного транзистора соединен с истоком второго 40 полевого транзистора с управляющим p-n-переходом, сток первого 39 полевого транзистора с управляющим p-n-переходом связан с первым 6 токовым выходом входного дифференциального каскада 1, сток второго 40 полевого транзистора с управляющим p-n-переходом соединен со вторым 10 токовым выходом входного дифференциального каскада 1, затвор первого 39 полевого транзистора с управляющим p-n-переходом связан с третьим 41 основным входом входного дифференциального каскада 1, затвор второго 40 полевого транзистора с управляющим p-n-переходом связан с четвертым 42 основным входом входного дифференциального каскада 1.

Особенность схемы фиг. 6 состоит в том, что вход 42 может использоваться для введения отрицательной обратной связи, а входы 4, 5 и 41 - для подачи входных сигналов, что качественно отличает заявляемый ОУ от классических аналогов.

На фиг. 7, в соответствии с п. 6 формулы изобретения, в схему входного дифференциального каскада 1 введены третий 43 и четвертый 44 биполярные транзисторы, а также третий 45 и четвертый 46 полевые транзисторы с управляющим p-n-переходом, причем коллекторы третьего 43 и четвертого 44 биполярных транзисторов соединены с общей цепью питания 2 входного дифференциального каскада 1 и связаны с первой 3 шиной источника питания, база третьего 43 биполярного транзистора соединена с пятым 47 основным входом входного дифференциального каскада 1, база четвертого 44 биполярного транзистора соединена с шестым 48 основным входом входного дифференциального каскада 1, эмиттер третьего 43 биполярного транзистора соединен с истоком третьего 45 полевого транзистора с управляющим p-n-переходом, эмиттер четвертого 44 биполярного транзистора соединен с истоком четвертого 46 полевого транзистора с управляющим p-n-переходом, сток третьего 45 полевого транзистора с управляющим p-n-переходом связан с первым 6 токовым выходом входного дифференциального каскада 1, сток четвертого 46 полевого транзистора с управляющим p-n-переходом соединен со вторым 10 токовым выходом входного дифференциального каскада 1, затвор третьего 45 полевого транзистора с управляющим p-n-переходом связан с седьмым 49 основным входом входного дифференциального каскада 1, затвор четвертого 46 полевого транзистора с управляющим p-n-переходом связан с восьмым 50 основным входом входного дифференциального каскада 1.

Таким образом, схема фиг. 7 имеет 8 входов, из них 4 - инвертирующих и 4 - неинвертирующих. Отрицательная обратная связь с выхода 25 может подаваться на один из инвертирующих входов устройства, а входные сигналы - на семь других входов. Это значительно расширяет функциональные возможности заявляемого устройства, позволяет реализовывать на его основе как инвертирующие, так и неинвертирующие аналоговые сумматоры семи или менее входных сигналов.

Рассмотрим работу ОУ фиг. 2.

Статический режим транзисторов схемы фиг. 2 устанавливается источником опорного тока 23 входного дифференциального каскада 1 (I23=2I0). При этом токи стока (Ici) и токи коллекторов (Iкi) транзисторов схемы определяются уравнениями:

где Iс21, Iс22 - токи стока полевых транзисторов 21 и 22;

I0 - некоторый заданный опорный ток, например, I0=1 мА;

Iк8, Iк12 - токи коллекторов первого 8 и второго 12 транзисторов первого и второго источников опорного тока симметричной активной нагрузки.

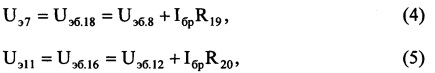

Статическое напряжение на эмиттере транзисторов 7 и 11 относительно второй 9 шины источника питания отличается от напряжений эмиттер-база транзисторов 8 и 12 на сравнительно небольшую величину:

где Iбр - ток базы транзисторов 8 и 12. Причем при I0=1 мА

где β=100÷500 - коэффициент усиления по току базы биполярных транзисторов.

Если выбрать сопротивления резисторов 19 и 20 сравнительно малым (например, 300-500 Ом), то при β≥100 из последних формул можно найти, что напряжение эмиттер-база выходных транзисторов 16 и 18

Uэб.18≈Uэб.8, Uэб.16≈Uэб.12.

Как следствие, в предлагаемой схеме ОУ токи коллекторов транзисторов 16 и 18 равны токам коллекторов транзисторов 8 и 12, которые определяются током I23 входного дифференциального каскада 1.

В том случае, когда резисторы 19 и 20 выбираются сравнительно высокоомными, может потребоваться введение низкоомных резисторов 27 и 28 или резисторов 29 и 30 (фиг. 4). Кроме этого в этом случае возможно также применение в качестве транзисторов 8 и 12 многоэмиттерных транзисторов (например, так как это сделано на чертеже фиг. 3).

Таким образом, в предлагаемой схеме ОУ обеспечивается достаточно стабильный статический режим по току всех активных элементов, который устанавливается единственным источником опорного тока I23 входного дифференциального каскада 1.

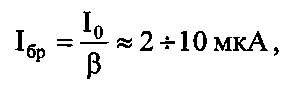

Максимальная амплитуда отрицательного выходного напряжения ОУ фиг. 2 (Um(-)) определяется по следующей формуле:

где Uкэ18.min≈0 - минимальное напряжение коллектор-эмиттер транзистора 18;

Е9(-) - напряжение на второй 9 шине источника питания.

Таким образом, в предлагаемой схеме Um(-)≈E9(-). В ОУ-прототипе фиг. 1 это напряжение на 0,8 В меньше Е9(-), что весьма существенно при малых Е9(-) (2,5-5 В).

С другой стороны, максимальная амплитуда положительного выходного напряжения ОУ фиг. 2 (при типовом построении токового зеркала 15) равна напряжению на первой 3 шине источника питания Um(+)≈E3(+). Следовательно, схема фиг. 2 обеспечивает так называемый rail-to-rail выход (от шины питания 9 до шины питания 3).

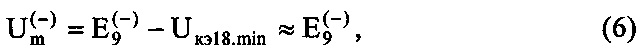

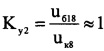

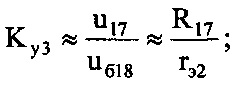

Усиление ОУ фиг. 3 без отрицательной обратной связи при единичном коэффициенте передачи токового зеркала 15 определяется формулой

где Kу1, Kу2≈1, Kу3, KБУ≈1 - коэффициенты передачи по напряжению первого, второго, третьего и четвертого каскадов ОУ.

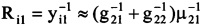

Причем

где uк8 - напряжение на коллекторе транзистора 8,

u45 - напряжение между входами 4 и 5,

gm1 - крутизна входного дифференциального каскада 1;

у6 - эквивалентная проводимость в цепи токового выхода 6;

- коэффициент передачи эмиттерного повторителя на транзисторе 7,

- коэффициент передачи эмиттерного повторителя на транзисторе 7,

uб18 - напряжение на базе транзистора 18;

KБУ≈1 - коэффициент передачи буферного усилителя 24;

R17 - эквивалентное сопротивление в цепи токового выхода ОУ 17;

rэi - сопротивление прямосмещенного эмиттерного p-n-перехода i-го транзистора.

При этом в формуле (8) эквивалентная проводимость в высокоимпедансном узле 6:

у6=уi7+уi8+уi1,

где уi7 - входная проводимость транзистора 7 по цепи базы;

уi8 - выходная проводимость транзистора 8 по цепи коллектора;

уi1 - выходная проводимость дифференциального каскада 1 по цепи токового выхода 6.

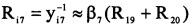

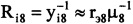

Причем

,

,  ,

,

где μi=10-3÷10-4 - коэффициент внутренней обратной связи i-го транзистора схемы с общей базой 8 (общим затвором, 21);

β7 - коэффициент усиления по току базы транзистора 7;

,

,  - крутизна стокозатворной характеристики полевых транзисторов 21 и 22;

- крутизна стокозатворной характеристики полевых транзисторов 21 и 22;

R19, R20 - сопротивления первого 19 и второго 20 дополнительного резисторов.

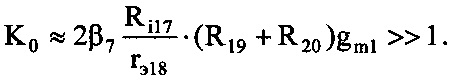

Если пренебречь внутренней обратной связью транзисторов схемы и считать, что выходное сопротивление входного дифференциального каскада 1 относительно токового выхода 6 удовлетворяет условию Ri1>>β7 (R19+R20), то общий коэффициент усиления ОУ

Как показывает компьютерное моделирование схемы фиг. 8, соответствующей схеме фиг. 6, численные значения K0 лежат в пределах 80÷100 дБ, что достаточно для многих применений ОУ.

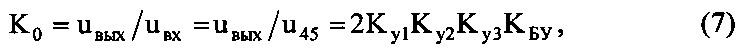

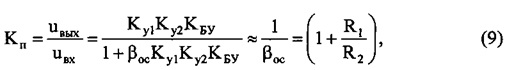

При введении отрицательной обратной связи в схеме фиг. 8, соответствующей фиг. 6, с выхода ОУ 25 на вход 4 модуль коэффициента передачи по напряжению, подаваемому на вход 42 (фиг. 8)

где βoc=R2(R1+R2)-1 - коэффициент передачи четырехполюсника отрицательной обратной связи (в частном случае, при R1=0 βoc=1).

При этом усилитель фиг. 8 является инвертирующим, а его коэффициент передачи по напряжению определяется отношением резисторов в цепи обратной связи R1 и R2 (на схеме фиг. 8 - не показаны).

Графики фиг. 9 показывают, что предлагаемый ОУ имеет (при идентичных транзисторах) достаточно малые значения систематической составляющей напряжения смещения нуля при воздействии температуры и радиации. Данные графики показывают предельные возможности заявляемых ОУ.

Таким образом, заявляемое устройство имеет на 0,8 В более широкий диапазон изменения выходного напряжения (Um(-)), что достаточно актуально при низковольтном электропитании [Е9=(1.5÷3)В]. Предлагаемые схемы ОУ характеризуются также более широкими функциональными возможностями - на них без резисторов обратной связи реализуются как инвертирующие так и неинвертирующие решающие усилители.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7.411.451, fig. 2.

2. Патент US 3.614.645, fig. 1, fig. 2.

3. Патент US 5736.899, fig. 4.

4. Патент US 5.132.640, fig. 4.

5. Патент JP 61-140210, fig. 1, fig. 2, fig. 3, fig. 7.

6. Патент US 6.175.226.

7. Патент US 4.596.960, fig. 2.

8. Патент US 4.271.394.

9. Патент US 4.359.693, fig. 1.

10. Патент US 4.607.232.

11. Патент US 5.963.085, fig. 3.

12. Патент US 6.624.697, fig. 1.

13. Патент DE 1966421, fig. 1.

14. Патент FR 2277461, fig. 1, fig. 3, fig. 4.

15. Патент RU 4.271.394, fig. 3.

16. Операционные усилители / И. Достал; Москва: Пер. с англ., Мир, 1982. - 512 с. (рис. 13.13б, стр. 77).

17. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н., проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.