Результат интеллектуальной деятельности: Способ передачи сообщений между вычислительными устройствами

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Настоящее изобретение относится к вычислительной технике, а конкретнее к способу передачи сообщений между вычислительными устройствами.

Уровень техники

В настоящее время при передаче сообщений посредством технологии Rapid IO значительное количество времени расходуется на обработку прерываний и смену контекста, что особенно существенно при передаче небольших сообщений.

Для передачи сообщений необходимо наличие свободных буферов у получателя. Система, использующая буфера, известна из патентов США №5233701 (опубл. 03.08.1993) и №5870572 (опубл. 09.02.1999). Чтобы обеспечить наличие свободного буфера, требуется специальный протокол, что значительно увеличивает накладные расходы. Попытки же передачи сообщений в отсутствие свободных буферов приводят к значительным потерям времени.

Другой проблемой является защита памяти при прямом доступе к памяти (Direct Memory Access, DMA). Слабо контролируемые ошибки при программировании DMA могут привести к катастрофическим последствиям.

Наиболее близким аналогом можно считать способ межпроцессорной связи, описанный в патенте США №8745291 (опубл. 03.06.2014). Реализующее этот способ устройство содержит для каждого процессора несколько входных и выходных очередей барабанного типа («первый вошел - первый вышел», First-In-First-Out, FIFO).

Раскрытие изобретения

Задача настоящего изобретения состоит в разработке такого способа межпроцессорного обмена, который, расширяя арсенал технических средств, не требовал бы использования дополнительного протокола, что упрощает работу соответствующей системы и повышает надежность функционирования, увеличивая пропускную способность (скорость передачи).

Для решения этой задачи и достижения указанного технического результата в настоящем изобретении предложен способ передачи сообщений между вычислительными устройствами, каждое из которых снабжено запоминающим средством и по меньшей мере одним аппаратным портом для передачи и (или) приема сообщений от по меньшей мере одного другого вычислительного устройства, включающий в себя следующие этапы: формируют в запоминающем средстве каждого из вычислительных устройств по меньшей мере одну входную очередь и (или) по меньшей мере одну выходную очередь, каждая из которых представляет собой упорядоченную последовательность элементов, и каждый из элементов идентифицирует соответствующий буфер в запоминающем средстве соответствующего вычислительного устройства, при этом каждая из выходных очередей предназначена для передачи сообщений через соответствующий аппаратный порт данного вычислительного устройства, а каждая из входных очередей предназначена для приема сообщений через соответствующий аппаратный порт данного вычислительного устройства; логически связывают каждую из сформированных выходных очередей в запоминающем средстве одного вычислительного устройства, именуемого далее устройством-отправителем, с соответствующей из сформированных входных очередей в запоминающем средстве другого вычислительного устройства, именуемого далее устройством-получателем, формируя тем самым однонаправленный канал для передачи сообщений; в устройстве-отправителе: заносят программными средствами в конец выходной очереди идентификатор того из заполненных буферов в запоминающем средстве устройства-отправителя, в который предварительно помещено очередное подлежащее отправке сообщение; последовательно передают аппаратными средствами соответствующему устройству-получателю подлежащие отправке сообщения из тех буферов в запоминающем средстве устройства-отправителя, идентификаторы которых расположены от начала к концу выходной очереди, после чего эти буфера считают свободными и могут быть извлечены программными средствами из выходной очереди; в устройстве-получателе: заносят программными средствами в конец входной очереди идентификатор очередного свободного буфера в запоминающем средстве устройства-получателя, очередное принятое сообщение из которого предварительно обработано; последовательно принимают аппаратными средствами поступающие через соответствующий аппаратный порт переданные от соответствующего устройства-отправителя сообщения, для каждого из которых определяют соответствующую ему входную очередь и помещают это сообщение в очередной свободный буфер соответствующей входной очереди в запоминающем средстве устройства-получателя; извлекают программными средствами очередное из принятых сообщений из того заполненного буфера в запоминающем средстве устройства-получателя, идентификатор которого находится в начале входной очереди, и после того, как очередное сообщение принято, помещают идентификатор этого свободного буфера в конец входной очереди; перестают принимать сообщения через аппаратный порт предназначенные для данной очереди сообщения после исчерпания всех свободных буферов во входной очереди.

Особенность способа по настоящему изобретению состоит в том, что в отсутствие свободных буферов в конкретной входной очереди в устройстве-получателе могут передавать через соответствующий аппаратный порт устройства-получателя уведомление о невозможности приема в данную конкретную входную очередь, после чего могут прекращать передачу сообщений из соответствующей выходной очереди через аппаратный порт устройства-отправителя до появления свободных буферов в соответствующей входной очереди аппаратного порта устройства-получателя, после чего через аппаратный порт устройства-получателя передают уведомление о появлении свободного буфера в данной входной очереди на аппаратный порт устройства-отправителя, который возобновляет передачу сообщений из соответствующей выходной очереди.

Другая особенность способа по настоящему изобретению состоит в том, что при приеме очередного сообщения в устройстве-получателе могут использовать циклический режим, когда по достижении конца входной очереди переходят к ее началу и повторно используют соответствующие буфера.

Еще одна особенность способа по настоящему изобретению состоит в том, что наряду с собственно сообщением могут передавать дополнительную информацию, относящуюся к этому сообщению, при этом идентификатору каждого буфера могут ставить в соответствие отдельную область памяти запоминающего средства устройства-отправителя, содержащую дополнительную информацию.

При этом для каждой из входных и выходных очередей могут указывать диапазон адресов в памяти соответствующего запоминающего средства, где могут располагаться относящиеся к очереди данные, и (или) диапазон адресов в памяти соответствующего запоминающего средства, где могут располагаться соответствующие буфера, диагностировать аппаратными средствами выход за любой из указанных диапазонов адресов при обработке данной очереди и рассматривать такой выход как ошибку.

Еще одна особенность способа по настоящему изобретению состоит в том, что каждую из входных и выходных очередей могут организовывать в виде кольцевых буферов.

Наконец, еще одна особенность способа по настоящему изобретению состоит в том, что каждая из выходных очередей может состоять из первого и второго элементов, при этом в устройстве-отправителе очередное подлежащее отправке сообщение помещают в очередной свободный буфер и заносят его идентификатор во второй из элементов выходной очереди.

Краткое описание чертежей

Изобретение поясняется приложенными чертежами, которые являются чисто иллюстративными и не ограничивают объем данного изобретения.

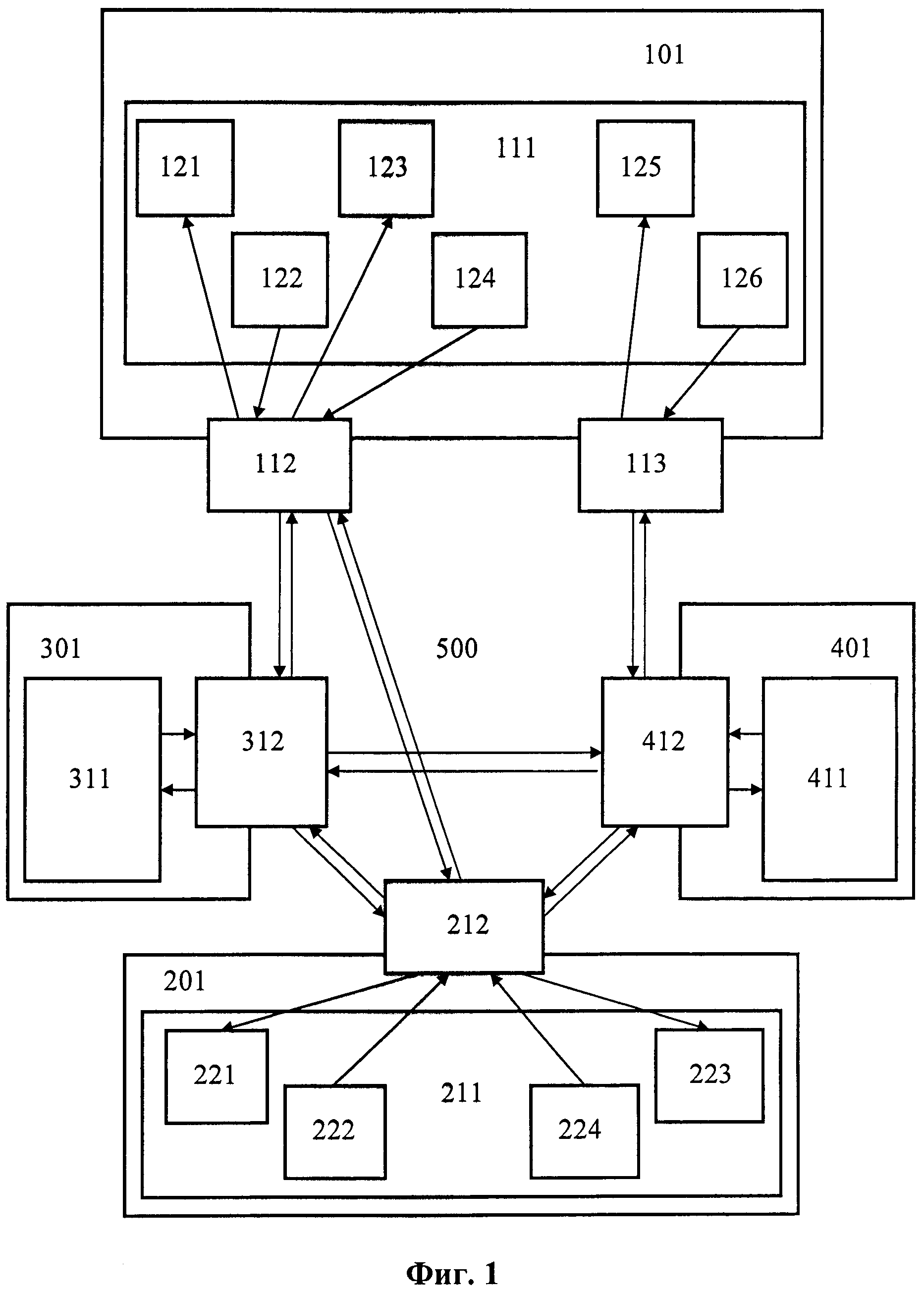

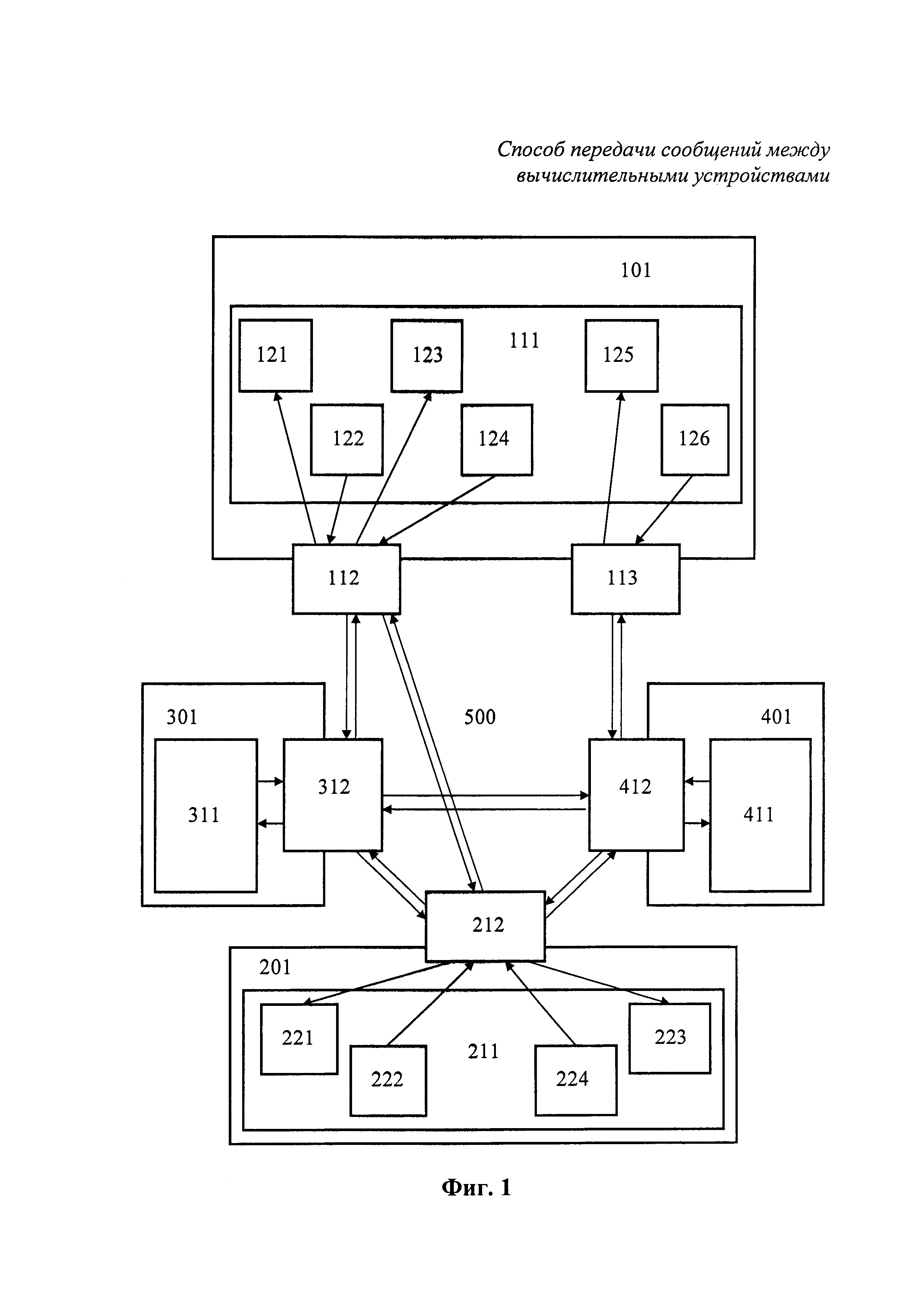

Фиг. 1 схематично показывает связи между отдельными элементами в системе, реализующей способ по настоящему изобретению.

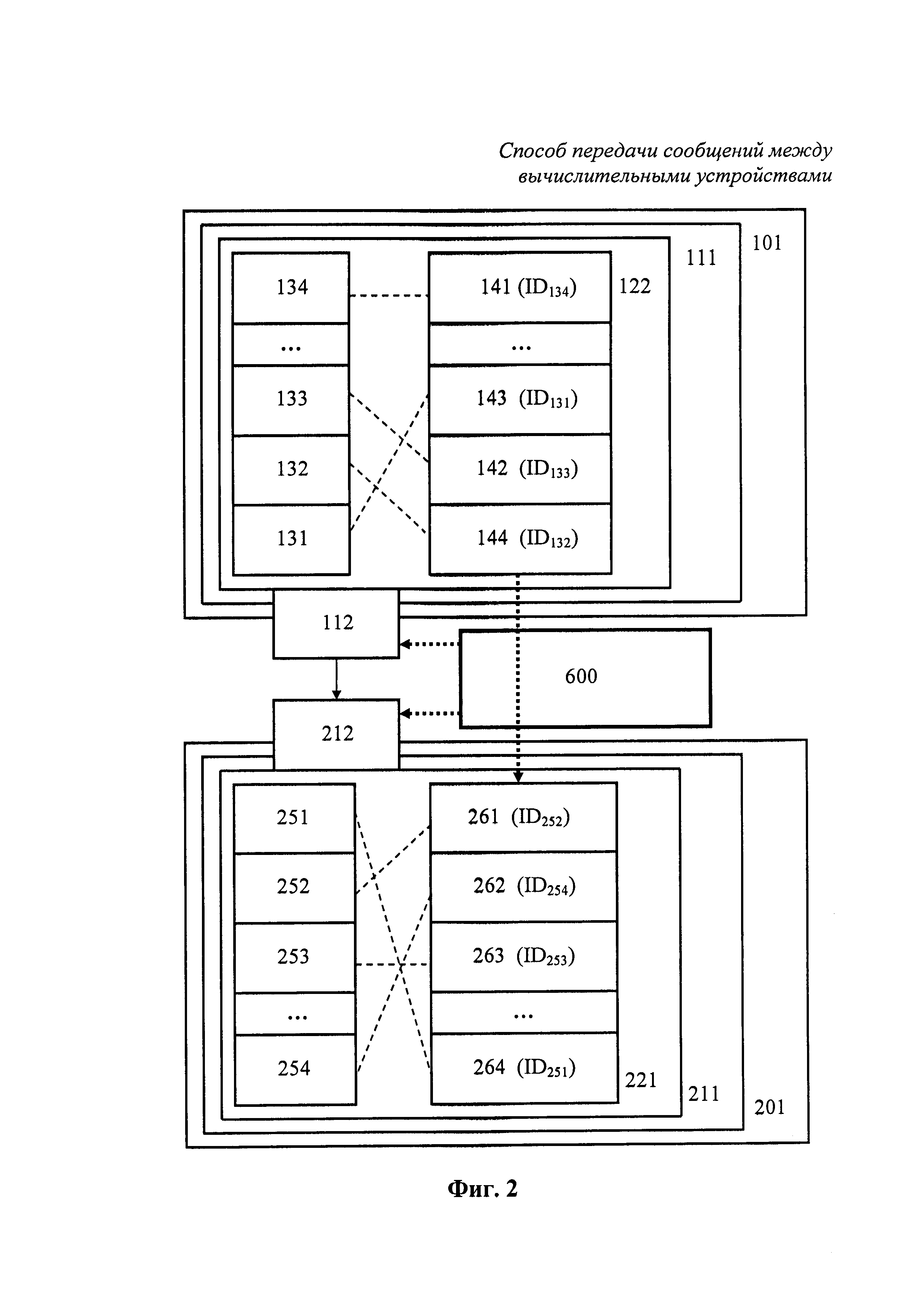

Фиг. 2 схематично показывает взаимодействие отдельных элементов для одного канала.

Подробное описание вариантов осуществления

Способ по настоящему изобретению может осуществляться в системе, проиллюстрированной на Фиг. 1. В этой системе имеется несколько вычислительных устройств, обозначенных на Фиг. 1 ссылочными позициями 101, 201, 301 и 401. Специалистам понятно, что этих устройств может быть как больше, так и меньше показанных (минимум два). Каждое из этих устройств снабжено запоминающим средством, соответственно 111, 211, 311 и 411. В дальнейшем описании термины «запоминающее средство» и «память» используются взаимозаменяемо.

Кроме того, каждое из входящих в систему по Фиг. 1 вычислительных устройств имеет по меньшей мере один аппаратный порт для передачи и (или) приема сообщений от по меньшей мере одного другого вычислительного устройства. На Фиг. 1 первое вычислительное устройство условно показано с двумя аппаратными портами 112 и 113, а вычислительные устройства 201, 301 и 401 имеют каждое по одному аппаратному порту - соответственно 212, 312 и 412. Специалистам понятно, что это всего лишь пример, и у каждого вычислительного устройства может быть иное количество аппаратных портов.

В качестве любого из упомянутых выше вычислительных устройств может использоваться любое известное специалистам либо вновь разработанное средство, способное осуществлять обработку («processing») данных. Например, в качестве такого вычислительного устройства может выступать персональный компьютер, сервер, специализированный компьютер, процессорный модуль и т.п.

Для реализации способа по настоящему изобретению в памяти каждого вычислительного устройства формируют по меньшей мере одну входную очередь и (или) по меньшей мере одну выходную очередь, каждая из которых представляет собой упорядоченную последовательность элементов. На Фиг. 1 входные очереди 121, 123 и 125 и выходные очереди 122, 124 и 126 показаны в памяти 111 первого вычислительного устройства 101, а входные очереди 221 и 223 и выходные очереди 222 и 224 показаны в памяти 211 второго вычислительного устройства 201. В устройствах же 301 и 401 для экономии места ни входные, ни выходные очереди не показаны.

Каждый из элементов в любой очереди идентифицирует соответствующий буфер в запоминающем средстве соответствующего вычислительного устройства (см. далее пояснения к Фиг. 2). Каждая из выходных очередей предназначена для передачи сообщений через соответствующий аппаратный порт данного вычислительного устройства, а каждая из входных очередей предназначена для приема сообщений через соответствующий аппаратный порт данного вычислительного устройства. На Фиг. 1 - исключительно в качестве иллюстративного примера - входные очереди 121 и 123 и выходные очереди 122 и 124 соответствующими стрелками показаны связанными с первым аппаратным портом 112, а входная очередь 125 и выходная очередь 126 (в том же запоминающем средстве 111) показаны связанными со вторым аппаратным портом 113.

Каждая из сформированных выходных очередей в запоминающем средстве одного вычислительного устройства, именуемого далее устройством-отправителем, логически (т.е. программными средствами) связана с соответствующей из сформированных входных очередей в запоминающем средстве другого вычислительного устройства, именуемого далее устройством-получателем. Тем самым между этими очередями формируется однонаправленный канал для передачи сообщений. На Фиг. 1 все эти каналы обозначены ссылочной позицией 500.

На Фиг. 2 для простоты проиллюстрировано формирование одного такого канала - между выходной очередью 122 в памяти 111 первого вычислительного устройства 101 и входной очередью 221 в памяти 211 второго вычислительного устройства 201. На Фиг. 2 в запоминающем средстве 111 первого вычислительного устройства 101 изображены буфера 131-134 и элементы 141-144, образующие упорядоченную последовательность. Каждый элемент этой последовательности идентифицирует один из соответствующих буферов 131-134, что отмечено пунктирными линиями между элементами 141-144 и буферами 131-134, а также указанием в скобках, какой именно из буферов 131-134 идентифицирует тот или иной элемент 141-144.

Аналогично, в запоминающем средстве 211 второго вычислительного устройства 201 входная очередь 221 включает в себя буфера 251-254 и идентифицирующие их элементы 261-264, взаимное соответствие которых показано такими же пунктирными линиями и указаниями в скобках. Следует отметить, что любой из буферов может содержать сообщение или быть пустым.

Выходная очередь 122 связана с первым аппаратным портом 112 в первом вычислительном устройстве 101, а входная очередь 221 связана с аппаратным портом 212 во втором вычислительном устройстве 201. На Фиг. 2 началу выходной очереди 122 соответствует ссылочная позиция 141, а началу входной очереди 221 соответствует ссылочная позиция 261. При этом цепочки буферов 131-134 в выходной очереди 122 и цепочки буферов 251-154 во входной очереди 221 могут начинаться не с первого элемента, показанного на Фиг. 2. Кроме того, на Фиг. 2 ссылочной позицией 600 обозначено программное обеспечение (ПО). Специалистам понятно, что ПО 600 находится в каждом из вычислительных устройств, и на Фиг. 2 оно показано между устройствами лишь условно. Именно ПО 600 формирует канал между аппаратными портами 112 и 212 первого и второго вычислительных устройств 101 и 201. Действие этого ПО условно показано на Фиг. 2 точечными стрелками. Специалистам понятно, что реальная передача сообщений между аппаратными портами вычислительных устройств осуществляется по сети связи, имеющейся между этими вычислительными устройствами. Но для настоящего описания значение имеют логические каналы между соответствующими очередями, сформированные программно. Потоки данных, необходимые для решения конкретных задач, передаются между устройствами по каналам, интерфейс которых может быть выполнен по стандарту ARINC 653.

Эти логические каналы получаются из пары очередей, одна из которых, выходная очередь одного аппаратного порта в устройстве-отправителе (на Фиг. 1 и 2 эта выходная очередь обозначена ссылочной позицией 122) может быть постоянно или временно связана с помощью программного обеспечения 600 с другой, входной очередью другого аппаратного порта в устройстве-получателе (на Фиг. 1 и 2 эта входная очередь обозначена ссылочной позицией 221). Специалистам понятно, что названия «устройство-отправитель» и «устройство-получатель» относятся к конкретному случаю однонаправленной передачи по сформированному логическому каналу. В случае обратной передачи эти названия меняются местами. Отметим, что два порта могут быть связаны несколькими каналами 500, передающими данные как в одном направлении, так и в разных направлениях.

Для передачи конкретного сообщения ПО помещает подлежащее отправке сообщение в свободный буфер, а идентификатор этого буфера - в конец выходной очереди порта в устройстве-отправителе. После отправки этого сообщения аппаратными средствами содержащий его буфер становится свободным и может быть извлечен из выходной очереди посредством ПО и использован для отправки следующего сообщения. Находящиеся в выходной очереди 122 сообщения отправляются соответствующему получателю аппаратными средствами в том порядке, в каком они находятся в очереди, т.е. в порядке записи в выходной очереди идентификаторов 141-144 тех буферов 131-134, в которые помещены подлежащие отправке сообщения. Таким образом, в начале выходной очереди находятся идентификаторы свободных буферов, сообщения из которых уже отправлены, а в конце выходной очереди находятся идентификаторы буферов с сообщениями, подлежащими отправке.

Для приема сообщения в устройстве-получателе ПО помещает один или несколько свободных буферов во входную очередь 221 порта, т.е. записывает в нее идентификаторы этих свободных буферов, которые используются аппаратурой для приема поступающих через порт сообщений. Свободные буфера используются в том порядке, в каком их идентификаторы 261-264 находятся во входной очереди 221, т.е. после ввода принятого сообщения в конкретный буфер для ввода следующего принимаемого сообщения будет использован другой свободный буфер, идентификатор которого стоит во входной очереди после идентификатора только что заполненного буфера. ПО извлекает очередное из принятых сообщений из того заполненного буфера в запоминающем средстве устройства-получателя, идентификатор которого находится в начале его входной очереди, и после того, как это очередное сообщение принято, помещают идентификатор этого свободного буфера в конец входной очереди. Таким образом, в начале входной очереди находятся идентификаторы буферов с принятыми сообщениями, а в конце - идентификаторы свободных буферов. Принятые сообщения считаются находящимися во входной очереди до тех пор, пока они не будут извлечены с помощью ПО. Специалистам понятно, что самый первый элемент очереди извлекается при условии, что в соответствующий буфер уже было принято сообщение.

Если во входной очереди 221 все свободные буфера исчерпаны, в устройстве-получателе 201 перестают принимать предназначенные для этой входной очереди сообщения через тот аппаратный порт 212, с которым соединена упомянутая входная очередь 221. В этом случае через данный аппаратный порт 212 этого устройства-получателя 201 передают к устройству-отправителю 101 уведомление о невозможности приема в данную конкретную входную очередь. После этого из соответствующей выходной очереди 122 через аппаратный порт 112 устройства-отправителя 101 прекращают передачу сообщений до появления свободных буферов в той входной очереди 221 аппаратного порта 212 устройства-получателя 201, откуда поступило отмеченное уведомление. Когда же через этот же аппаратный порт 212 устройства-получателя 201 передают уведомление о появлении свободного буфера в данной входной очереди 221 на аппаратный порт 112 устройства-отправителя 101, этот аппаратный порт 112 возобновляет передачу сообщений из соответствующей выходной очереди 122 устройства-отправителя 101.

В принципе, если во входной очереди все свободные буфера исчерпаны, в устройстве-получателе при приеме очередного сообщения могут использовать циклический режим, когда по достижении конца данной входной очереди переходят к ее началу и повторно используют соответствующие буфера.

Следует указать, что наряду с собственно сообщением может передаваться относящаяся к этому сообщению дополнительная информация. При этом идентификатору каждого буфера, в который может быть записано конкретное сообщение, ставят в соответствие отдельную область памяти запоминающего средства устройства-отправителя, содержащую такую дополнительную информацию. Область памяти, содержащая собственно сообщение (иными словами, буфер), и область памяти, содержащая дополнительную для этого сообщения информацию, могут находиться в несмежных участках памяти. Специалистам понятно, что дополнительная информация может не использоваться, а с другой стороны, она может передаваться даже в отсутствие собственно сообщения.

Специалистам понятно, что каждая из входных и выходных очередей может быть организована в виде кольцевого буфера, как это известно, например, из заявки Японии №06-68040 (опубл. 11.03.1994). С другой стороны, очереди могут быть организованы аналогично тому, как это описано, например, в патенте США №5404485 (опубл. 04.04.1995).

Отметим, что для каждой из входных и выходных очередей может быть указан диапазон адресов в памяти соответствующего запоминающего средства, где могут располагаться относящиеся к очереди данные, и (или) диапазон адресов в памяти соответствующего запоминающего средства, где могут располагаться соответствующие буфера. При обработке данной очереди, т.е. при передаче сообщений из выходной очереди или приеме сообщений во входную очередь аппаратные средства диагностируют выход за любой из указанных диапазонов адресов, и такой выход считается ошибкой.

В частном случае выходные очереди могут быть сформированы всего из двух - первого и второго - элементов. При этом в устройстве-отправителе очередное подлежащее отправке сообщение помещают в очередной свободный буфер и заносят его идентификатор во второй из упомянутых элементов выходной очереди.

Таким образом, способ по настоящему изобретению обеспечивает механизм межпроцессорного обмена, который, расширяя арсенал технических средств, не требует использования дополнительного протокола. Это упрощает работу соответствующей системы и повышает надежность функционирования, увеличивая пропускную способность (скорость передачи).