Результат интеллектуальной деятельности: ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в самосинхронных программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов i=1,n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства является невозможность использования его в энергоэффективных самосинхронных схемах.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1,n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства,

причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-ой группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С. 56-62, Рис. 9, 12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 12.11.12 г.). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: блок вычисления логической функции; 2n входов настройки; n входов переменных; информационный выход; 2n входов настройки подключены к 2n входам настройки блока вычисления логической функции; n входов переменных подключены к n входам переменных блока вычисления логической функции; информационный выход блока вычисления логической функции подключен к информационному выходу устройства; блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1,n транзисторов в группе, группу 2n инверторов настройки; затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных; истоки 2n транзисторов n-й группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки; стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы; транзисторы в группах n-3, n-4…2 соединены аналогично; стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является информационным выходом блока вычисления логической функции.

Недостатком известного устройства, принятого за прототип, является невозможность использования его в энергоэффективных самосинхронных схемах. Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию синхронных схем и не имеют средств индикации завершения переходных процессов. Входные переменные поступают на входные инверторы, на выходе которых образуются инверсии входных сигналов. Это приводит к тому, что, даже введя двойственный канал для вычисления двойственной логической функции (путем инвертирования настроек), нет возможности реализации фазы гашения, так как спейсер (например, нулевой) не может быть создан - отсутствуют средства приведения выходов основного и двойственного каналов в одинаковое состояние. Для реализации спейсера в фазе гашения необходимы дополнительные средства приведения выходов основного и двойственного каналов в одинаковое состояние, отсутствующие в прототипе. Все это вызывает невозможность фиксации завершения переходного процесса, что является ключевым в самосинхронных схемах.

Задачей изобретения является обеспечение возможности индицирования завершения переходного процесса для использования устройства в самосинхронных схемах с парафазными переменными и нулевым спейсером.

Поставленная задача была решена за счет того, что в заявляемое устройство, содержащее блок вычисления логической функции, 2n входов настройки, n входов переменных, информационный выход, причем 2n входов настройки подключены к 2n входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1,n транзисторов в группе, группу 2n инверторов настройки, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-ой группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы, транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства,

согласно изобретению дополнительно введены блок вычисления двойственной логической функции, аналогичный блоку вычисления логической функции, элемент ИЛИ-НЕ, 2n входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации, причем 2n входов инверсной настройки устройства подключены к 2n входам настройки блока вычисления двойственной логической функции, n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции, n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства, причем в блоки вычисления логической функции и двойственной логической функции введены группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт», затворы нечетных транзисторов группы 2n транзисторов инверсной проводимости подключены к соответствующему i-му входу n входов инверсий переменных, затворы четных транзисторов группы 2n транзисторов инверсной проводимости подключены к i-му входу n входов переменных, сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока, исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости, транзисторы в группах n-3, n-4…2 соединены аналогично, исток 2n-го транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт», затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных.

Признаки заявляемого технического решения, отличительные от прототипа: блок вычисления двойственной логической функции, аналогичный блоку вычисления логической функции; элемент ИЛИ-НЕ; 2n входов инверсной настройки; n входов инверсий переменных; инверсный информационный выход; выход индикации;

2n входов инверсной настройки устройства подключены к 2n входам настройки блока вычисления двойственной логической функции; n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции; n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции;

информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ; информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства;

в блоки вычисления логической функции и двойственной логической функции введены группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт»;

затворы каждого нечетного транзистора группы 2n транзисторов инверсной проводимости подключены к соответствующему входу n входов инверсий переменных; затворы каждого четного транзистора группы 2n транзисторов инверсной проводимости подключены к соответствующему входу n входов переменных; сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока; исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости; транзисторы в группах n-3, n-4…2 соединены аналогично; исток 2n-го транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт»;

затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных.

Отличительные признаки в сочетании с известными позволяют обеспечить индицирование завершения переходного процесса для использования устройства в самосинхронных схемах с парафазными переменными и нулевым спейсером.

Введение блока вычисления двойственной логической функции позволяет получить значение двойственной логической функции (на инверсном информационном выходе) путем использования инверсной настройки по соответствующим введенным входам (2n входам инверсной настройки), что необходимо для обеспечения самосинхронного вычисления логических функций.

Введение n входов инверсий переменных позволяет использовать парафазные входные переменные и отдельно управлять четными и нечетными транзисторами (в n группах передающих транзисторов) в блоках вычисления логической функции и двойственной логической функции, что обеспечивает возможность и реализации спейсера.

Введение элемента ИЛИ-НЕ позволяет фиксировать рабочую фазу и выдавать ее на выход индикации, когда блоки вычисления логической функции и двойственной логической функции формируют разные выходные сигналы (01 или 10), и фазу гашения, когда блоки вычисления логической функции и двойственной логической функции формируют разные одинаковые сигналы (0 при нулевом спейсере), что необходимо для обеспечения самосинхронного вычисления логических функций в устройстве.

Введение группы 2n транзисторов инверсной проводимости в блоки вычисления логической функции и двойственной логической функции позволяют реализовать фазу гашения путем подачи на нулевого спейсера (нулевого набора сигналов - инверсных и не инверсных) на n входов переменных и n входов инверсий переменных. В этом случае на затворы всех транзисторов группы 2n транзисторов инверсной проводимости поданы логические нули и все транзисторы открыты, что приводит к подаче логической единицы с выхода дополнительного инвертора на вход выходного инвертора.

Введение дополнительного инвертора позволяет реализовать нулевой спейсер - при активировании затворов всех транзисторов групп 2n транзисторов инверсной проводимости в блоках вычисления логической функции и двойственной логической функции за счет того, что через вход подключения шины «Ноль вольт» на выход дополнительного инвертора подается логическая единица, которая, проходя через все транзисторы групп 2n транзисторов инверсной проводимости, приводит к появлению на входе выходного инвертора логической единицы, а на его выходе - логического нуля. В этом случае неактивны все цепочки в n группах передающих транзисторов (n - число входных переменных по 2i, i=1,n транзисторов в группе) в блоках вычисления логической функции и двойственной логической функции.

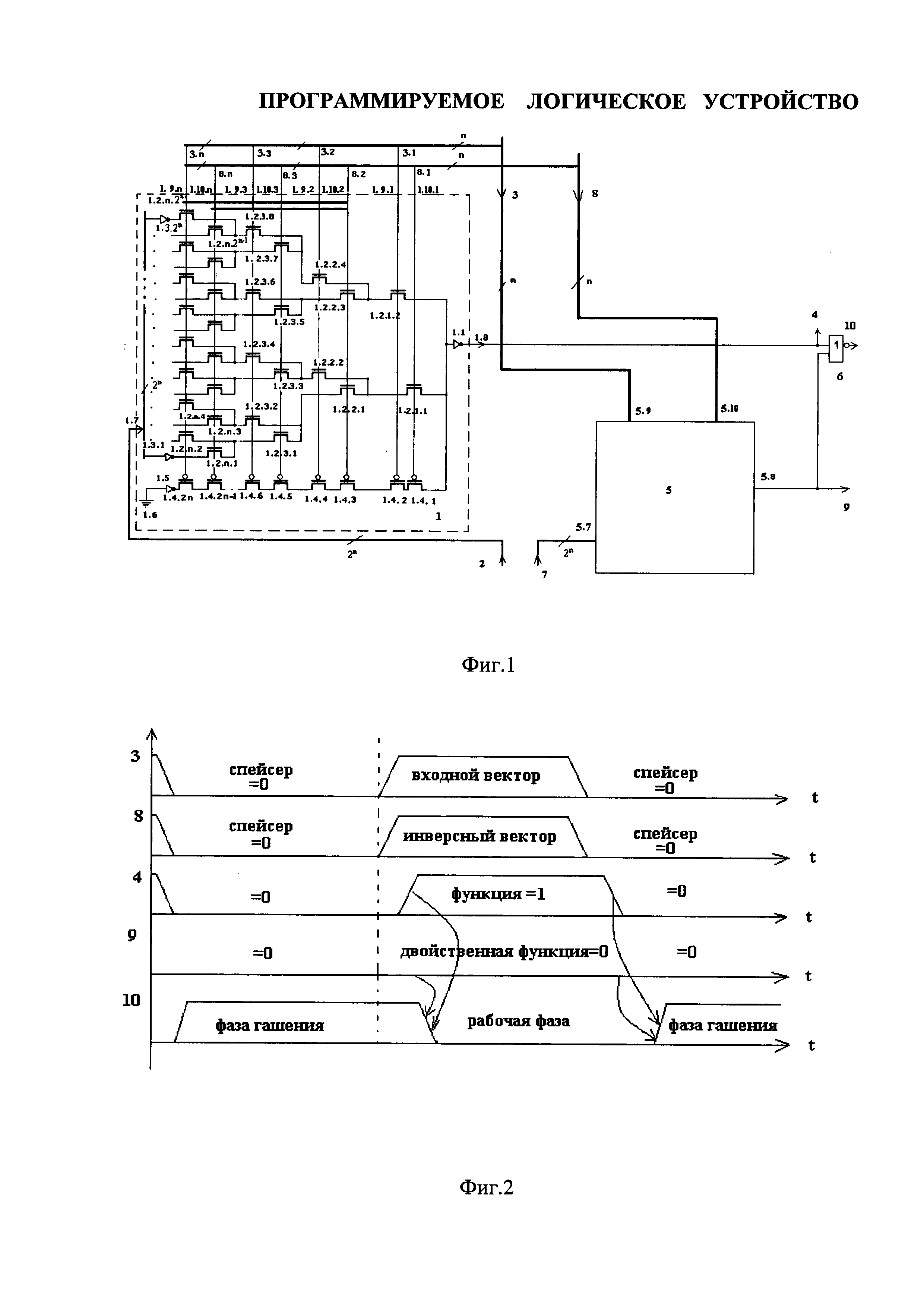

На фиг. 1 изображена схема электрическая принципиальная парафазного программируемого логического устройства для самосинхронных схем.

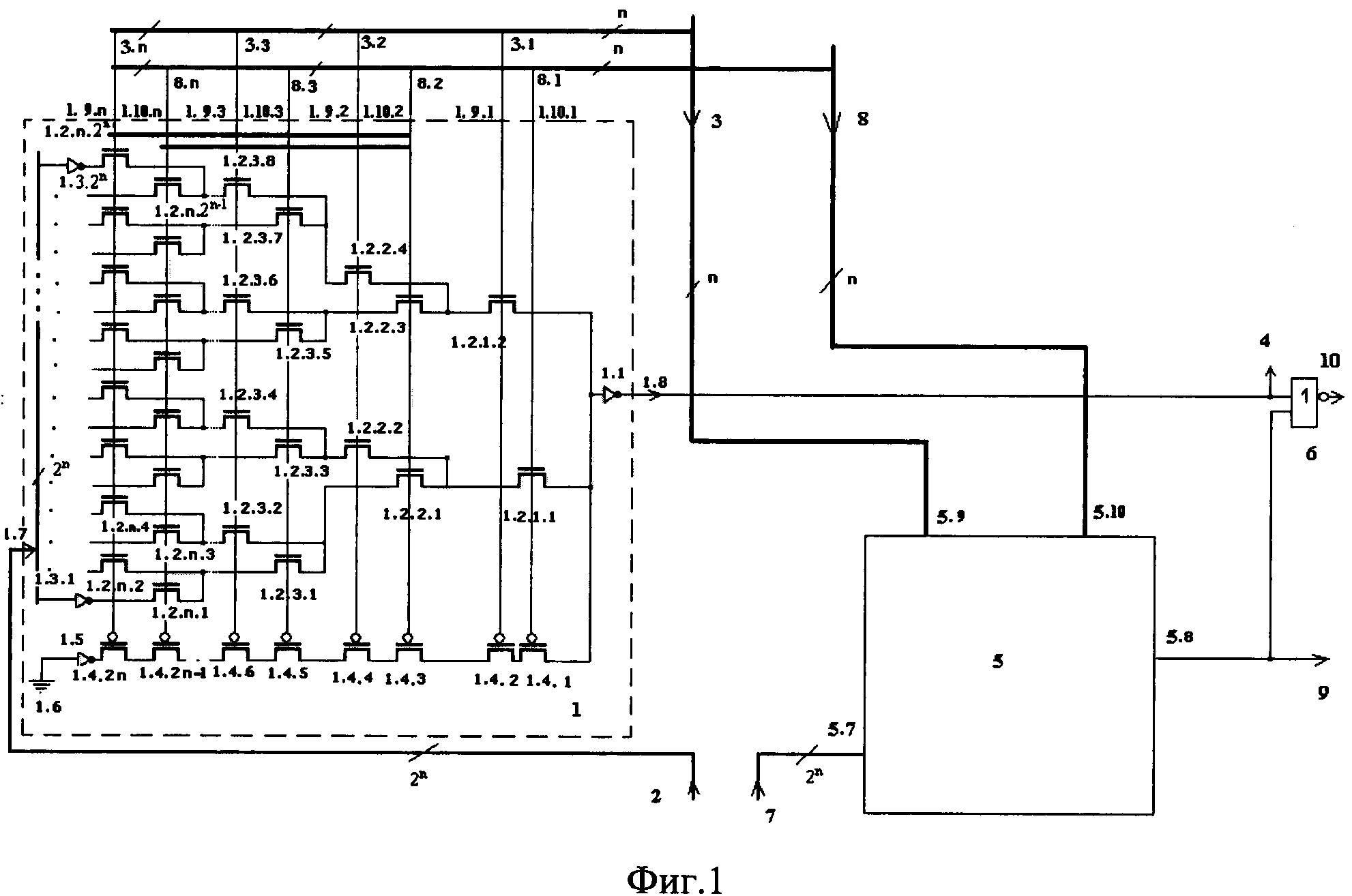

На фиг. 2 изображена временная диаграмма работы парафазного программируемого логического устройства для самосинхронных схем.

Парафазное программируемое логическое устройство для самосинхронных схем (фиг. 1) содержит блок вычисления логической функции 1, 2n входов настройки 2, n входов переменных 3, информационный выход 4, блок вычисления двойственной логической функции 5, элемент ИЛИ-НЕ 6, 2n входов инверсной настройки 7, n входов инверсий переменных 8, инверсный информационный выход 9, выход индикации 10.

Блок вычисления логической функции 1 содержит выходной инвертор 1.1, n групп передающих транзисторов 1.2.i (n - число входных переменных) по 2i, i=1,n транзисторов в группе, группу 2n инверторов настройки 1.3, группу 2n транзисторов инверсной проводимости 1.4, дополнительный инвертор 1.5, вход подключения шины «Ноль вольт» 1.6.

2n входов настройки 2 устройства подключены к 2n входам 1.7 настройки блока вычисления логической функции 1. Информационный выход 1.8 блока вычисления логической функции 1 подключен к информационному выходу 4 устройства.

n входов переменных 3 устройства подключены к n входам 1.9.1-1.9. n переменных блока вычисления логической функции.

Затвор каждого четного транзистора i-й группы передающих транзисторов 1.2 подключен к i-му входу входов n переменных 1.9. Истоки 2n транзисторов n-й группы передающих транзисторов 1.2 подключены к выходам инверторов группы 2n инверторов настройки 1.3, входы которых являются группой 2n входов настройки 1.7 блока вычисления логической функции 1.

Стоки четных и нечетных транзисторов n-й группы передающих транзисторов 1.2 объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы передающих транзисторов 1.2, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы передающих транзисторов 1.2, транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов 1.2.1.2, 1.2.1.1 первой группы передающих транзисторов 1.2 объединены и подключены ко входу выходного инвертора 1.1, информационный выход которого 1.8 является информационным выходом 4 устройства.

Затворы нечетных транзисторов группы 2n транзисторов инверсной проводимости 1.4.1, 1.4.3, 1.4.5 и так далее до 1.4. 2n-1 подключены к соответствующему i-му входу n входов инверсий переменных 8.1…8.n.

Затворы четных транзисторов группы 2n транзисторов инверсной проводимости 1.4.2, 1.4.4, 1.4.6 и так далее до 1.4. 2n подключены к i-му входу n входов переменных 3.1…3.n.

Сток первого транзистора 1.4.1 группы 2n транзисторов инверсной проводимости 1.4 подключен к выходному инвертору 1.1 блока 1, исток первого транзистора 1.4.1 группы 2n транзисторов инверсной проводимости 1.4 подключен к стоку второго транзистора 1.4.2 группы 2n транзисторов инверсной проводимости 1.4, исток которого подключен к стоку третьего транзистора 1.4.3 группы 2n транзисторов инверсной проводимости 1.4 и так далее, исток 2n-го транзистора 1.4.2n группы 2n транзисторов инверсной проводимости 1.4 подключен к выходу дополнительного инвертора 1.5, вход которого подключен к шине «Ноль вольт» 1.6.

Затвор каждого нечетного транзистора i-й группы передающих транзисторов 1.2 i=1,n блока вычисления логической функции 1 подключен к i-му входу n входов инверсий переменных 8.

Блок вычисления двойственной логической функции 5 аналогичен блоку вычисления логической функции 1 и содержит выходной инвертор 5.1, n групп передающих транзисторов 5.2.i (n - число входных переменных) по 2i, i=1,n транзисторов в группе, группу 2n инверторов настройки 5.3, группу 2п транзисторов инверсной проводимости 5.4, дополнительный инвертор 5.5, вход подключения шины «Ноль вольт» 5.6 (на чертеже не показаны 5.1-5.6).

2n входов инверсной настройки 7 устройства подключены к 2n входам настройки 5.7 блока вычисления двойственной логической функции 5.

Информационный выход 1.8 блока вычисления логической функции 1 подключен к первому входу элемента ИЛИ-НЕ 6.

Информационный выход 5.8 блока вычисления двойственной логической функции 5 является инверсным информационным выходом устройства 9 и подключен ко второму входу элемента ИЛИ-НЕ 6, выход которого является выходом индикации устройства 10.

n входов переменных 3 подключены к n входам переменных 5.9 блока вычисления двойственной логической функции 5.

n входов инверсий переменных 8 подключены к n входам инверсий переменных 5.10 блока вычисления двойственной логической функции 5 и блока вычисления логической функции 1.

Парафазное программируемое логическое устройство для самосинхронных схем работает в следующих режимах:

1) Программирования.

2) Двухфазного вычисления логической функции.

1) Программирование. В этом режиме устройство работает аналогично прототипу.

При этом с помощью внешних по отношению к устройству технических средств на 2n входах настройки 2 устанавливаются логические уровни, соответствующие логической функции n переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 2n строк), а на 2n входах инверсной настройки 7 устанавливаются логические уровни, соответствующие инверсной логической функции n переменных.

Так, для реализации функции сложения по модулю два (исключающего ИЛИ) четырех переменных (n=4) x4⊕x3⊕x2⊕x1, где xi - сигнал на входах переменных 3.1, 3.2, 3.3. 3.4 - на настроечных входах 2 (2.1…2.16) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php Дата обращения 12.01.15 г.) - Табл. 1.

На выходах инверторов группы 2n инверторов настройки 1.3.1…1.3. 2n блока 1 устанавливаются значения, инверсные логическим уровням, устанавливаемым на 2n входах настройки 2.

Так для указанного выше примера логической функции входах инверсной настройки 7 (7.1…7.16) устанавливаются следующие логические уровни - Табл. 2.

2) Двухфазное вычисление логической функции

Двухфазное вычисление логической функции обеспечивает фиксацию завершения переходного процесса, что позволяет с использованием дополнительных средств, внешних по отношению к устройству, реализовать самосинхронную обработку информации.

2.1. Фаза гашения

В фазе гашения с помощью внешних по отношению к устройству средств на n входах переменных 3 и n входах инверсий переменных 8 устанавливаются логические нули (спейсер). Это приводит к тому, что в блоках вычисления логической функции 1 (и вычисления двойственной логической функции 5) активируются затворы всех транзисторов групп 2n транзисторов инверсной проводимости 1.4. В то же время затворы всех транзисторов n групп передающих транзисторов 1.2.i неактивны. Это приводит к тому, что логическая единица с выхода дополнительного инвертора 1.5 передается на вход выходного инвертора 1.1, на его выходе 1.8 и на информационном выходе устройства 4 и на инверсном информационном выходе устройства 9 устанавливаются логические нули. Поэтому на выходе элемента ИЛИ-НЕ 6 формируется логическая единица, которая подается на выход индикации 10, сигнализируя внешним средствам о завершении фазы гашения.

2.2. Рабочая фаза

Получив сигнал завершения фазы гашения по выходу индикации 10, внешние по отношению к устройству технические средства устанавливают на n входах переменных 3 и n входах инверсий переменных 8 значения входного вектора и его инверсии - это так называемый парафазный вектор, когда в отличие от прототипа имеется и сигнал и его инверсия.

При этом цепочка транзисторов групп 2n транзисторов инверсной проводимости 1.4 разрывается, так как в каждой паре 2n транзисторов инверсной проводимости 1.4 активен затвор только одного транзистора.

В блоке вычисления логической функции 1 вычисления двойственной логической функции 5 активируется одна из V цепочек в n группах 1.2 передающих транзисторов (четные транзисторы непосредственно с соответствующего входа n переменных 3 (1.9.1, 1.9.2, … 1.9.n), если он равен логической единице, нечетные - с соответствующего входа n инверсий переменных 8, через выходной инвертор 1.1 на выход 1.8 и информационный выход устройства 4 (либо на инверсный информационный выход 9 для блока 5).

Так, при поступлении на входы n переменных 3 инверсий переменных 8 набора 01.10.01.10 (набор №5) «набирается» цепочка «четный транзистор» - «нечетный транзистор» 1.2.4.6-1.2.3.3-1.2.2.2-1.2.1.1 со входа 2.6, на котором установлен логический ноль, через инвертор 1.3.6, через выходной инвертор 1.1 - и на выходе 1.8 блока 1 и на информационном выходе устройства 4 формируется логический ноль: 0⊕1⊕0⊕1=0.

Аналогично вышеописанному на инверсном информационном выходе 9 посредством блока вычисления инверсной логической функции 5 формируется логическая единица.

Это приводит к тому, что на выходе элемента ИЛИ-НЕ 6 формируется логический ноль, которая подается на выход индикации 10, сигнализируя внешним средствам о завершении рабочей фазы и готовности результата вычисления логической функции на выходах 4, 9.

Далее, после приема результата вычислений, снова может следовать фаза гашения, установка нового значения входного вектора на входы 3, 8, далее рабочая фаза и т.д.

При необходимости возможна перенастройка устройства для вычисления другой логической функции и т.д.

Устройство также может работать без фазы гашения, в синхронных схемах. При этом синхронизируется подача входного вектора на входы 3, 8, например, путем записи входного вектора по синхроимпульсу на внешний по отношению к устройству регистр (триггеры), а результаты вычислений на выходах 4, 9, 10 записываются по другому синхроимпульсу на другой внешний по отношению к устройству регистр (триггеры). Результаты на выходах 4, 9, 10 могут быть оценены внешними по отношению к устройству средствами с целью контроля функционирования устройства.

Таким образом, в отличие от прототипа устройство может быть использовано в самосинхронных схемах, работа которых, после настройки на требуемую логическую функцию, состоит их фазы гашения и рабочей фазы.

В фазе гашения с помощью внешних по отношению к устройству технических средств по парафазным входам переменных - n входам переменных 3 и n входам инверсий переменных 8 принимается нулевой набор - спейсер, обеспечивающий одинаковые значения сигналов на информационном выходе 4 и инверсном информационном выходе 9. При этом устанавливается логическая единица на выходе индикации 10, что является сигналом к реализации рабочей фазы, в которой на n входов переменных 3 и n входов инверсий переменных 8 подается парафазный входной вектор, который приводит к формированию разных значений сигналов на информационном выходе 4 и инверсном информационном выходе 9. При этом устанавливается логический ноль на выходе индикации 10, что является сигналом завершения переходного процесса.

Такая работа в составе самосинхронных схем характеризуется большим быстродействием, чем у синхронных схем, так как они работают по реальным задержкам сигналов, и возможностью работы на сверхнизких напряжениях питания, что позволяет использовать устройство в энергоэффективных приложениях.

Программируемое логическое устройство, содержащее блок вычисления логической функции, 2 входов настройки, n входов переменных, информационный выход,причем 2 входов настройки подключены к 2 входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов, n - число входных переменных, по 2, i=1,n транзисторов в группе, группу 2 инверторов настройки, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2 транзисторов n-й группы подключены к выходам инверторов группы 2 инверторов настройки, входы которых являются группой 2 входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2 транзисторов n-2-й группы, транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является информационным выходом блока вычисления логической функции и информационным выходом устройства, отличающееся тем, что в него дополнительно введены блок вычисления двойственной логической функции, аналогичный блоку вычисления логической функции, элемент ИЛИ-НЕ, 2 входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации, причем 2 входов инверсной настройки устройства подключены к 2 входам настройки блока вычисления двойственной логической функции, n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции, n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства, причем в блоки вычисления логической функции и двойственной логической функции введены группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт», затворы нечетных транзисторов группы 2n транзисторов инверсной проводимости подключены к соответствующему i-му входу n входов инверсий переменных, затворы четных транзисторов группы 2n транзисторов инверсной проводимости подключены к i-му входу n входов переменных, сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока, исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости, транзисторы в группах n-3, n-4…2 соединены аналогично, исток 2n-го транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт», затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных.