Результат интеллектуальной деятельности: УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ, СИСТЕМА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ И СПОСОБ ПРОИЗВОДСТВА УСТРОЙСТВА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ

Вид РИД

Изобретение

УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее раскрытие относится к устройству формирования изображений, системам формирования изображений и способам производства устройства формирования изображений.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Было предложено устройство формирования изображений, в котором используются полевые транзисторы с p-n-переходом. В японском выложенном патенте №2007-165736 описывается устройство формирования изображений, включающее в себя множество пикселов. Каждый пиксел включает в себя полевой транзистор с p-n-переходом. В полевом транзисторе с p-n-переходом, описанном в японском выложенном патенте № 2007-165736, область канала расположена между слоями поверхностной области затвора и скрытой области затвора. Область канала соединена с стоковой областью в оконечной части скрытой области затвора.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Согласно первому аспекту настоящего раскрытия, обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости, и с первой по четвертую области затвора второго типа проводимости. Первая область затвора и вторая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Третья область затвора и четвертая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Первая область затвора и третья область затвора расположены в направлении глубины полупроводниковой подложки. Первая область затвора расположена между поверхностью и третьей областью затвора. Вторая область затвора и четвертая область затвора расположены в направлении глубины. Вторая область затвора расположена между поверхностью и четвертой областью затвора. Область канала включает в себя первую область и вторую область. Первая область расположена между первой областью затвора и третьей областью затвора. Вторая область расположена между второй областью затвора и четвертой областью затвора. Истоковая область расположена между первой областью затвора и второй областью затвора. Полупроводниковая область второго типа проводимости расположена между третьей областью затвора и четвертой областью затвора. Полупроводниковая область второго типа проводимости имеет концентрацию примеси, которая ниже, чем концентрация примеси третьей области затвора, и ниже, чем концентрация примеси четвертой области затвора.

[0004] Согласно другому аспекту настоящего раскрытия обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости, и с первой по четвертую области затвора второго типа проводимости. Первая область затвора и вторая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Третья область затвора и четвертая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Первая область затвора и третья область затвора расположены в направлении глубины полупроводниковой подложки. Первая область затвора расположена между поверхностью и третьей областью затвора. Вторая область затвора и четвертая область затвора расположены в направлении глубины. Вторая область затвора расположена между поверхностью и четвертой областью затвора. Область канала включает в себя первую область и вторую область. Первая область расположена между первой областью затвора и третьей областью затвора. Вторая область расположена между второй областью затвора и четвертой областью затвора. Истоковая область расположена между первой областью затвора и второй областью затвора. Полупроводниковая область первого типа проводимости обеспечена таким образом, чтобы продолжаться в пространственном отношении от третьей области затвора до четвертой области затвора.

[0005] Согласно другому аспекту настоящего раскрытия обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости и полупроводниковую область второго типа проводимости. Область канала расположена между полупроводниковой областью и поверхностью полупроводниковой подложки. По меньшей мере, часть истоковой области расположена между областью канала и поверхностью. Полупроводниковая область включает в себя первую часть, вторую часть и третью часть. Концентрация примеси первой части ниже, чем концентрация примеси второй части и ниже чем концентрация примеси третьей части. Первая часть расположена между второй частью и третьей частью. Ортогональная проекция первой части на плоскость, параллельную поверхности, накладывается на ортогональную проекцию истоковой области на плоскости.

[0006] Согласно другому аспекту настоящего раскрытия, обеспечена система формирования изображений. Система формирования изображений включает в себя устройство формирования изображений, описанное выше, и блок обработки сигналов, сконфигурированный для обработки сигнала, выведенного из устройства формирования изображений.

[0007] Кроме того, отличительные признаки настоящего раскрытия станут очевидны из последующего описания иллюстративных вариантов осуществления со ссылкой на сопроводительные чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

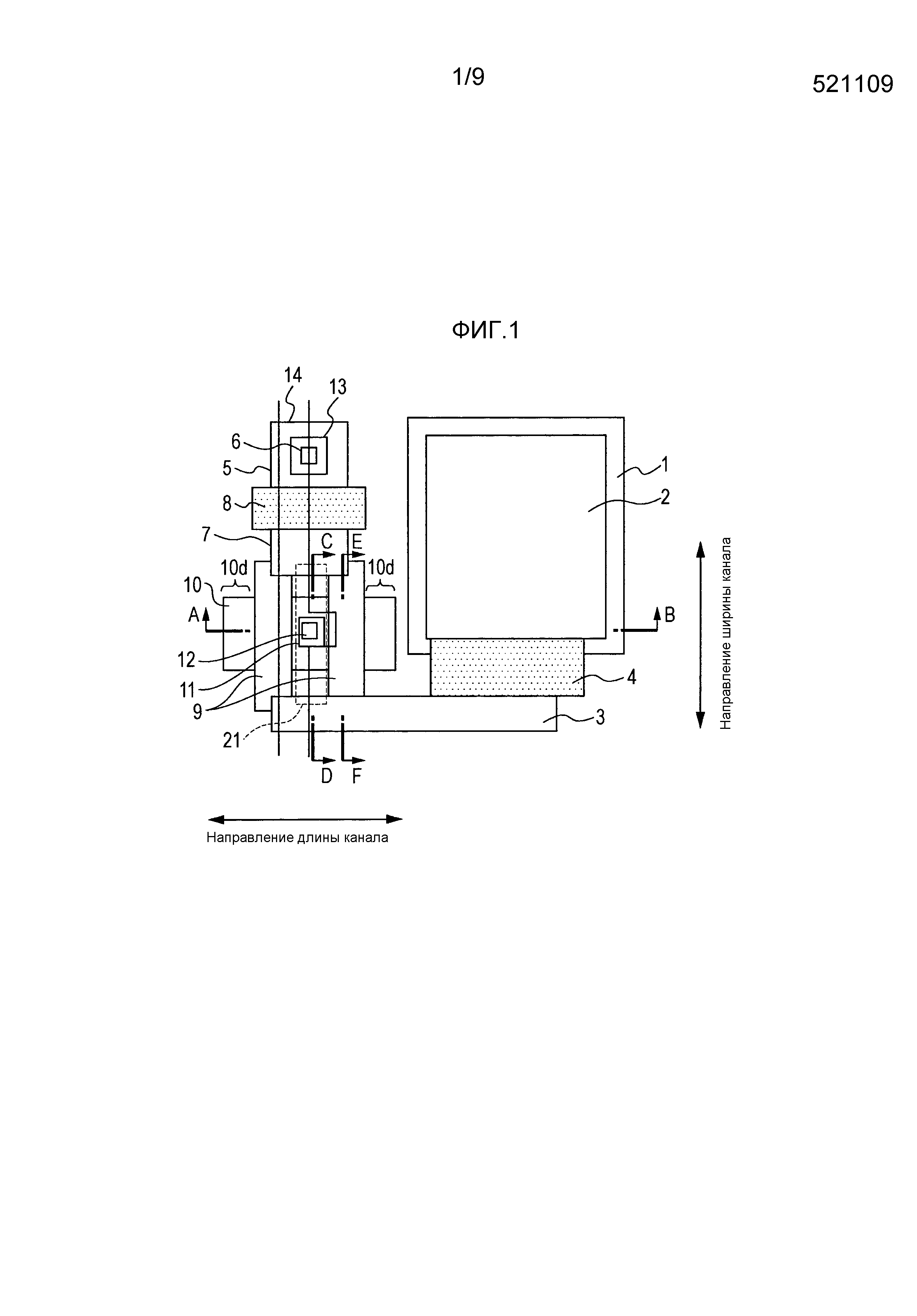

[0008] Фиг. 1 изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений.

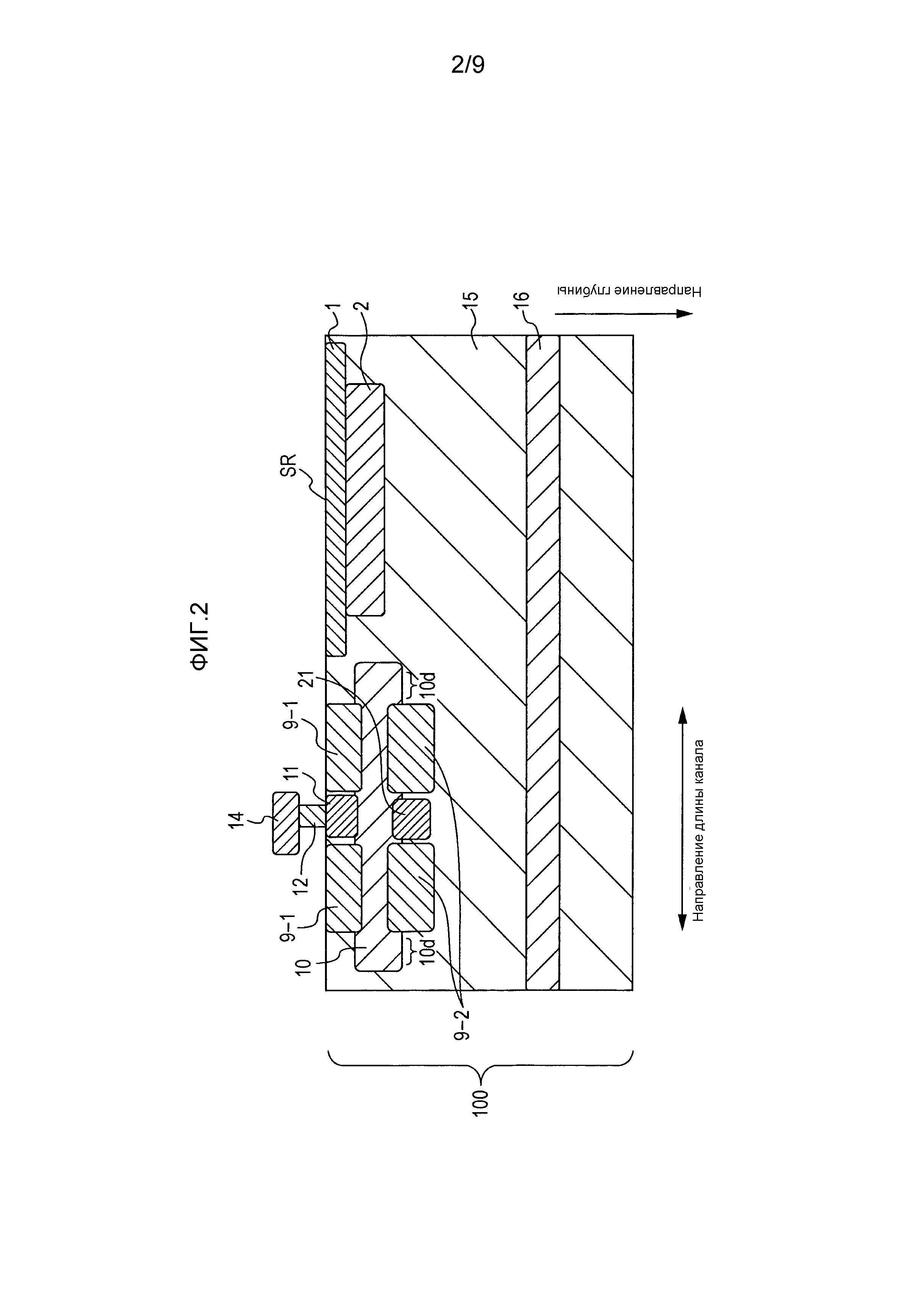

[0009] Фиг. 2 изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

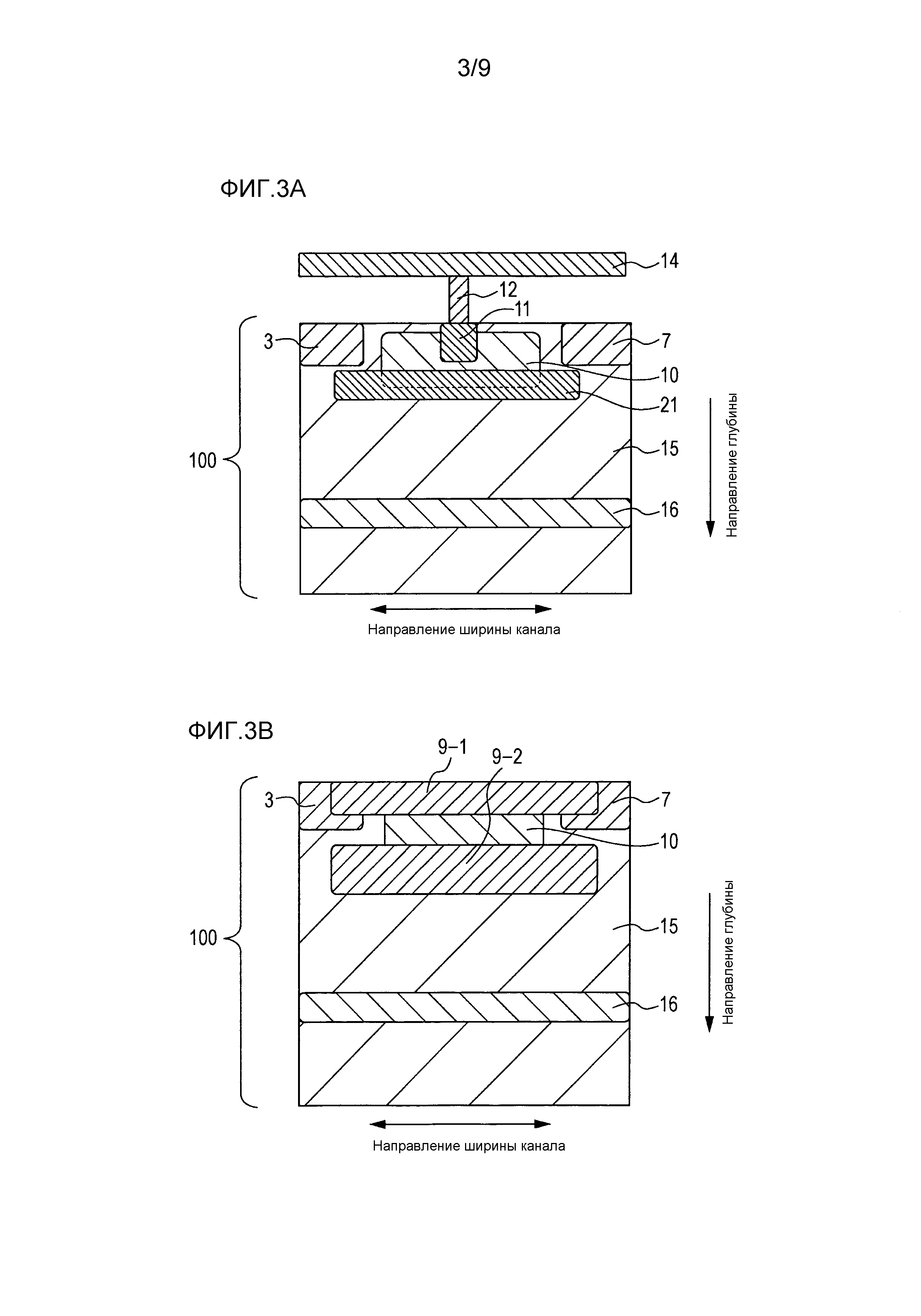

[0010] Фиг. 3A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0011] Фиг. 3B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0012] Фиг. 4A-4C изображают графические представления, используемые для объяснения способа производства устройства формирования изображений.

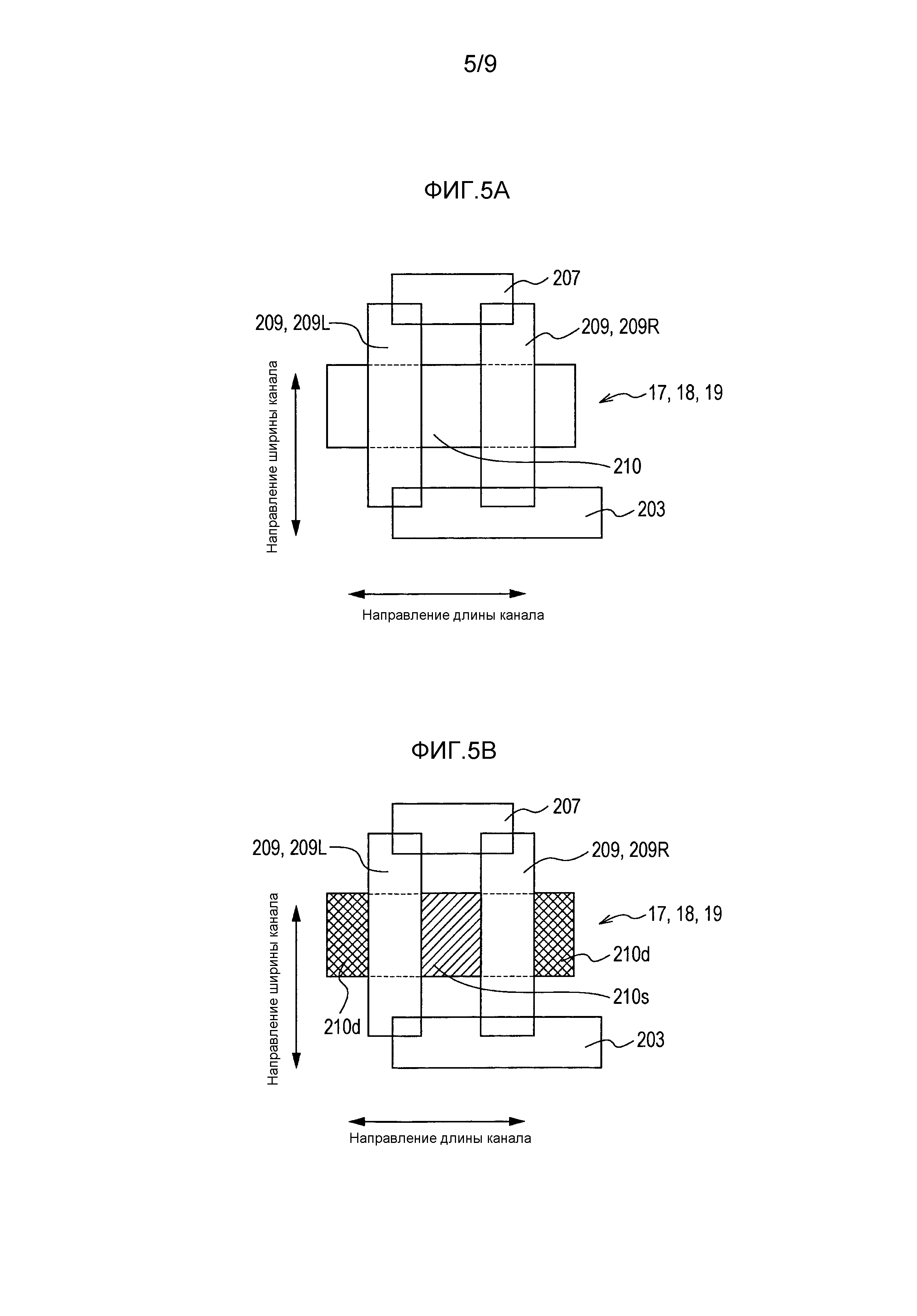

[0013] Фиг. 5A-5B изображают графические представления, схематично иллюстрирующие маски, используемые при производстве устройства формирования изображений.

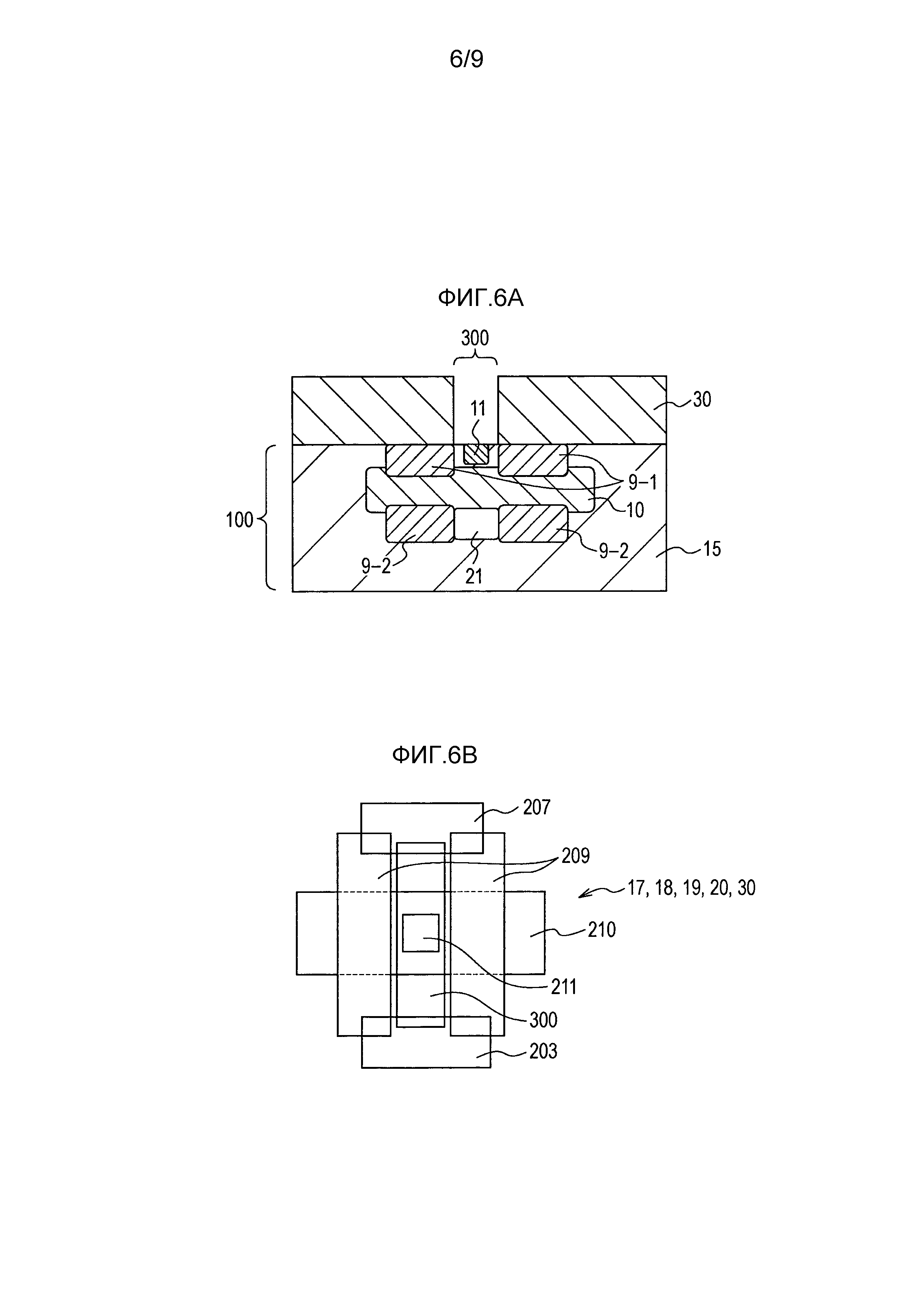

[0014] Фиг. 6A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0015] Фиг. 6B изображает графическое представление, схематично иллюстрирующее маски, используемые при производстве устройства формирования изображений.

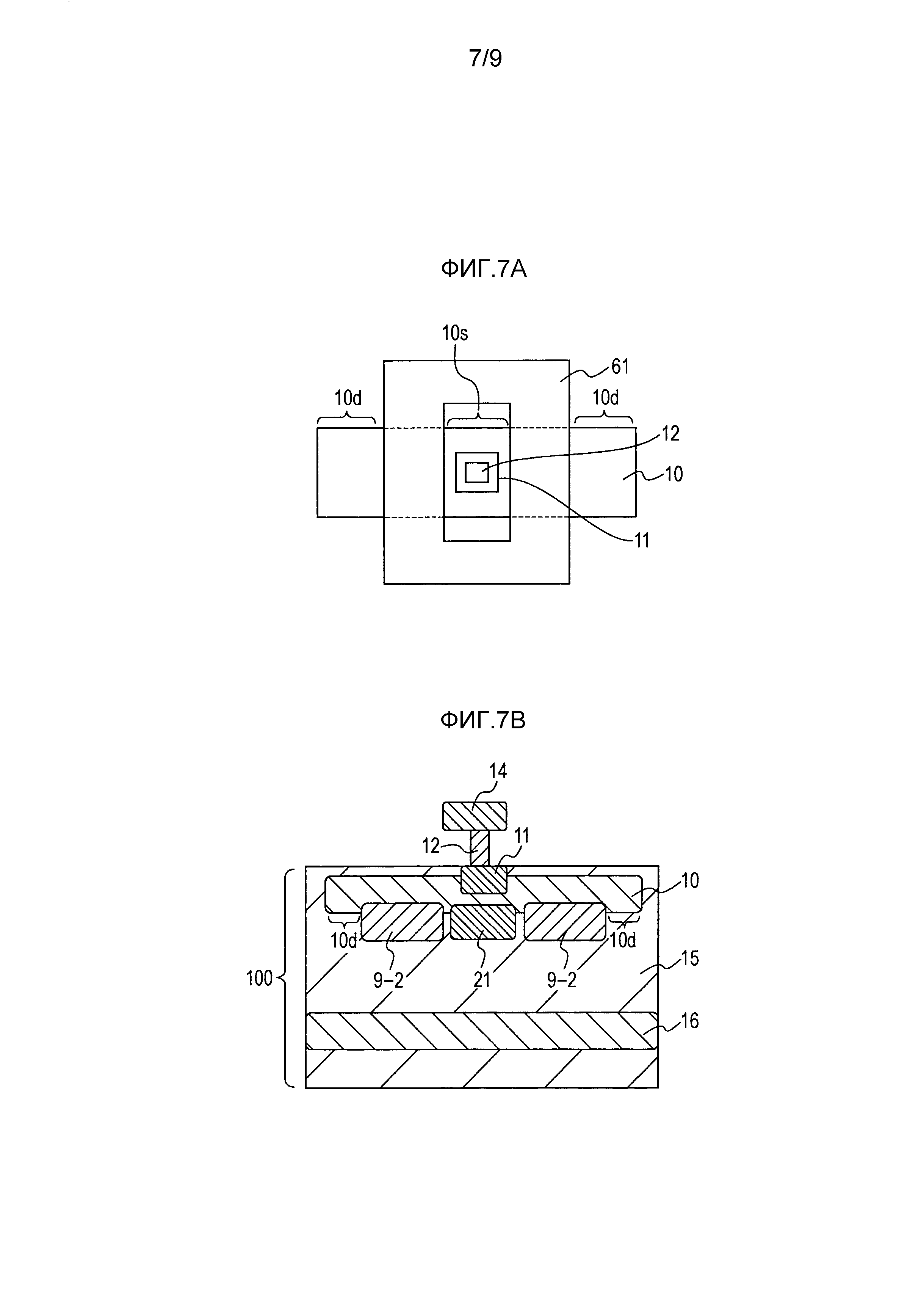

[0016] Фиг. 7A изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений.

[0017] Фиг. 7B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

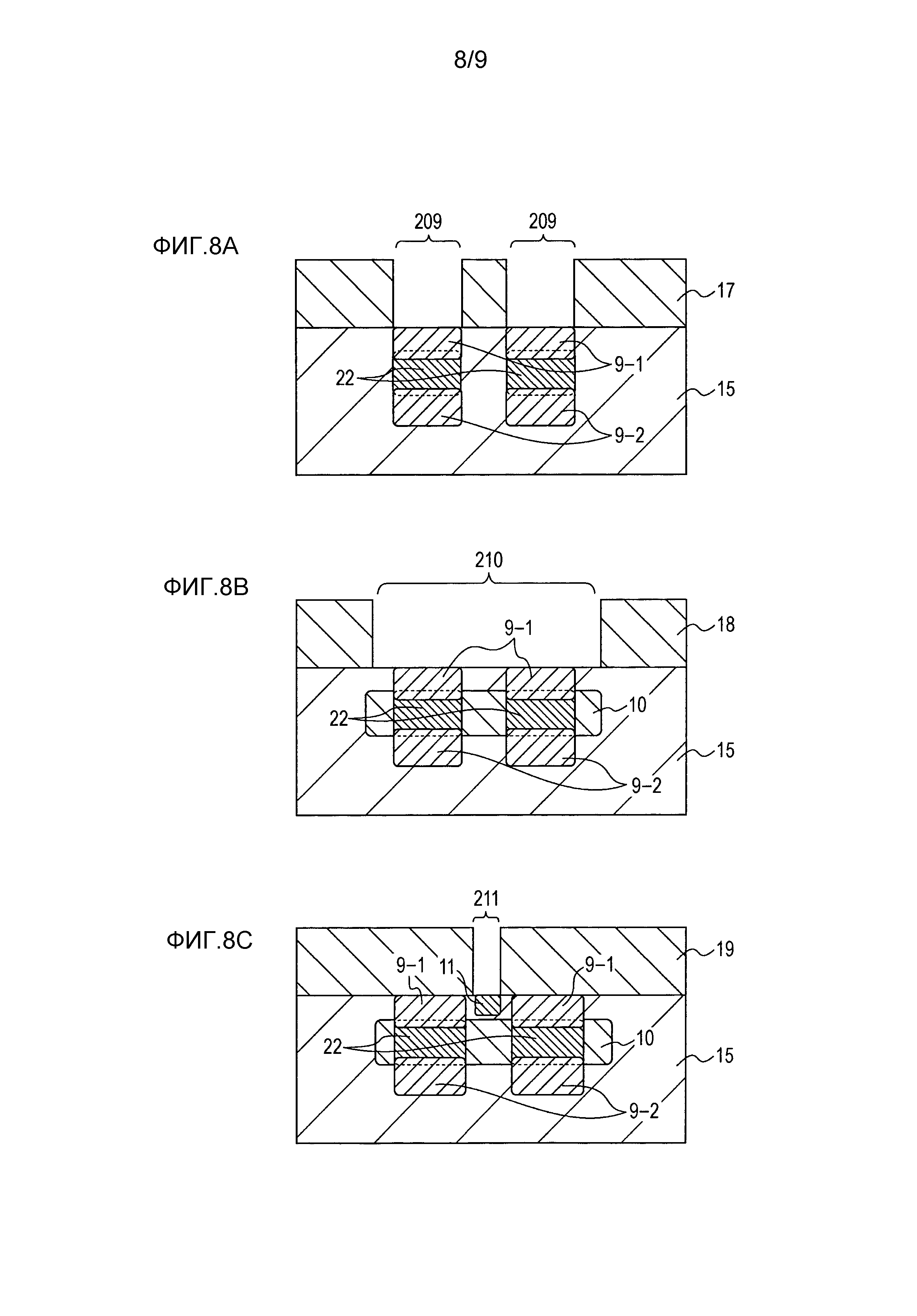

[0018] Фиг. 8A-8C изображают графические представления, используемые для объяснения способа производства устройства формирования изображений.

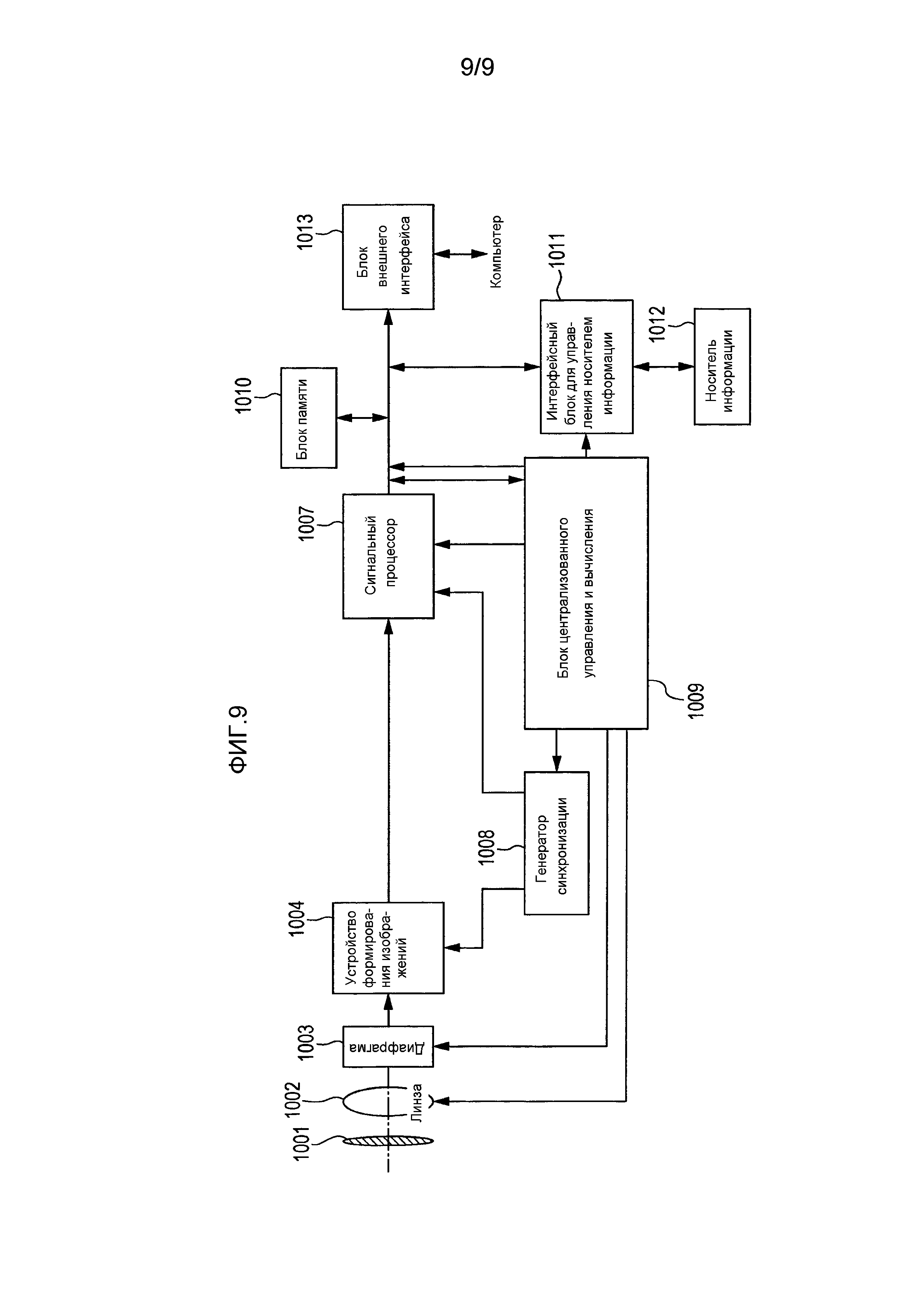

[0019] Фиг. 9 изображает блок схему системы формирования изображений.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0020] Согласно некоторым вариантам осуществления настоящего раскрытия могут быть улучшены характеристики полевого транзистора с p-n-переходом.

[0021] В полевом транзисторе с p-n-переходом, известном изобретателю, часть области затвора расположена или размещена под истоковой областью. Профиль концентрации примеси, или распределение, является однородным. Соответственно, если область затвора имеет высокую концентрацию примеси, то концентрация примеси области под истоковой областью может быть высокой.

[0022] Если концентрация примеси области под истоковой областью является высокой, то ток канала, выводимый из полевого транзистора с p-n-переходом, может варьироваться вследствие обеднения истоковой области. Другими словами, характеристики полевого транзистора с p-n-переходом могут ухудшиться.

[0023] Некоторые варианты осуществления настоящего раскрытия обеспечивают устройство формирования изображений, включающее в себя полевой транзистор с p-n-переходом, где его характеристики могут быть улучшены.

[0024] Вариант осуществления настоящего раскрытия обеспечивает устройство формирования изображений, включающее в себя множество пикселов. Каждый пиксел включает в себя полевой транзистор с p-n-переходом (далее в настоящем документе, называемый транзистором JFET). Транзистор JFET включает в себя область затвора, область канала, стоковая область и истоковую область, сформированные, соответственно, на полупроводниковой подложке. В транзисторе JFET, тип проводимости области затвора отличается от типов проводимости области канала, стоковой области и истоковой области. В настоящем варианте осуществления, в устройстве формирования изображений используется транзистор JFET с горизонтальной структурой, в котором направление тока канала параллельно поверхности полупроводниковой подложки.

[0025] Варианты осуществления согласно настоящему раскрытию представляют собой структуру полупроводниковой области, обеспеченную в более глубоком положении, чем область канала, и/или способ ее производства.

[0026] Далее в настоящем документе, варианты осуществления настоящего раскрытия будут подробно описаны со ссылкой на приложенные чертежи. Настоящее раскрытие не ограничено одним только вариантом осуществления, который будет описан ниже. Кроме того, примеры, в которых частичная конфигурация одного из следующих вариантов осуществления добавлена к другому варианту осуществления или заменена частичной конфигурацией другого варианта осуществления, также являются вариантами осуществления настоящего раскрытия.

[0027] В вариантах осуществления, которые будут описаны, область затвора имеет P-тип, а область канала, стоковая область и истоковая область имеют N-тип. Настоящее раскрытие включает в себя варианты осуществления, где тип проводимости каждой полупроводниковой области является обратным.

ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0028] Фиг. 1 изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений из настоящего варианта осуществления. Фиг. 1 иллюстрирует один пиксел. Пиксел включает в себя часть фотоэлектрического преобразования, такую, как фотодиод, транзистор переноса, транзистор сброса и транзистор JFET. Устройство формирования изображений из настоящего варианта осуществления включает в себя множество пикселов, иллюстрированных на Фиг. 1.

[0029] В настоящем варианте осуществления, часть фотоэлектрического преобразования является фотодиодом. Фотодиод включает в себя полупроводниковую область 1 N-типа, сформированную на поверхности полупроводниковой подложки, и полупроводниковую область 2 P-типа, сформированную под полупроводниковой областью 1 N-типа. Полупроводниковая область 1 N-типа и полупроводниковая область 2 P-типа формируют P-N-переход. Дырка, сгенерированная посредством падающего света, накапливается в полупроводниковой области 2 P-типа в качестве информационного заряда. Информационный заряд, накопленный в полупроводниковой области 2 P-типа, переносится в плавающую диффузионную область 3 (далее в настоящем документе, называемую областью 3 FD). Область 3 FD является полупроводниковой областью P-типа. Электрод 4 затвора переноса переносит информационный заряд из полупроводниковой области 2 P-типа в область 3 FD.

[0030] Транзистор JFET включает в себя область 9 затвора P-типа, область 10 канала N-типа и истоковую область 11 N-типа. Канал сформирован, по меньшей мере, в части области 10 канала N-типа. Канал управляется посредством напряжения в области 9 затвора. Транзистор JFET из настоящего варианта осуществления включает в себя множество областей 9 затвора. Область 10 канала пересекает каждую из областей 9 затвора, при его рассмотрении в плане. Область 10 канала расположена или размещена таким образом, чтобы пересекать область 9 затвора со стороны истока до стороны стока.

[0031] В настоящей спецификации, при выполнении ссылки на размещение, положения или формы элементов при их рассмотрении в плане, или только в плане, это означает размещение, положения или формы ортогональных проекций элементов, которые вертикально спроецированы на плоскость, параллельную поверхности полупроводниковой подложки. Следовательно, ортогональная проекция области затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекают друг друга на плоскости. Поверхность полупроводниковой подложки определена как граница между полупроводниковой областью и изолятором. Проекция может являться тенью объекта, которая произведена на плоскости во время экспонирования объекта параллельными лучами, которые проходят под прямым углом к плоскости.

[0032] Часть области 10 канала (обозначенная как область 10d на Фиг. 1) формирует стоковая область транзистора JFET. Канал транзистора JFET сформирован в части пересечения между областью 9 затвора и областью 10 канала. Концентрация примеси истоковой области 11 выше, чем концентрация примеси области 10 канала. Истоковая область 11 электрически соединена с выходной линией 14 при помощи контактного штыря 12. Область 3 FD электрически соединена с областью 9 затвора. В вышеописанной конфигурации, транзистор JFET выводит сигнал на основе напряжения области 3 FD.

[0033] МОП (металл-оксид-полупроводник) транзистор сброса включает в себя стоковая область 5 P-типа, истоковую область 7 P-типа и электрод 8 затвора. Стоковая область 5 электрически соединена с проводом 13 сброса напряжения стоковой области при помощи контактного штыря 6. Истоковая область 7 МОП транзистора сброса электрически соединена с областью 9 затвора транзистора JFET. В вышеописанной конфигурации, МОП транзистор сброса сбрасывает напряжение затвора транзистора JFET. Может быть легко использован МОП транзистор для транзистора сброса. Другой тип транзисторов, включая транзистор JFET, может быть использован для транзистора сброса.

[0034] Транзистор JFET включает в себя множество областей 9 затвора, которые являются развернутыми при их рассмотрении в плане. Области 9 затвора расположены или размещены таким образом, чтобы размещать между их слоями истоковую область 11 в плане. Другими словами, ортогональная проекция истоковой области 11 на плоскости, параллельной поверхности полупроводниковой подложки, расположена, в плоскости, между ортогональными проекциями областей 9 затвора на плоскости. Кроме того, транзистор JFET включает в себя множество стоковых областей. Точнее, область 10 канала включает в себя множество частей 10d со стороны стока. Каждая из стоковых областей расположена или размещена на противоположной стороне от истоковой области 10 относительно соответствующей одной из областей 9 затвора. Канал сформирован для каждой из областей 9 затвора. Области 9 затвора могут быть расположены или размещены параллельно друг к другу при их рассмотрении в плане. Области 9 затвора электрически соединены друг с другом посредством полупроводниковой области, имеющей тот же тип проводимости, что и область 9 затвора. В настоящем варианте осуществления, область 3 FD и истоковая область 7 МОП транзистора сброса осуществляют электрическое соединение области 9 затвора друг с другом.

[0035] Согласно вышеописанной конфигурации, может быть расширена эффективная ширина канала транзистора JFET. Другими словами, может быть улучшена запирающая способность вентиля транзистора JFET. Следовательно, устройство формирования изображений может работать с высокой скоростью. Транзистор JFET может включать в себя только одну область затвора. В частности, одна из двух областей 9 затвора, иллюстрированных на Фиг. 1 и соответствующих стоковой области, может быть удалена.

[0036] Пиксел включает в себя полупроводниковую область 21 P-типа. Полупроводниковая область 21 накладывается на истоковую область 11 при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области 21 P-типа на плоскость, параллельную поверхности полупроводниковой подложки, накладывается на ортогональную проекцию истоковой области 11 на плоскость. Полупроводниковая область 21 P-типа расположена или размещена между двумя областями 9 затвора при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области 21 P-типа на плоскость, параллельную поверхности полупроводниковой подложки, расположена между ортогональными проекциями двух областей 9 затвора на плоскость. Полупроводниковая область 22 P-типа накладывается на часть области 10 канала при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области P-типа на плоскость, параллельную поверхности полупроводниковой подложки, накладывается на часть ортогональной проекции области 10 канала на плоскость.

[0037] Фиг. 2 изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 2 схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1. Элементы на Фиг. 2, соответствующие иллюстрированным на Фиг. 1, обозначены посредством тех же самых ссылочных обозначений, что и на Фиг. 1.

[0038] Фиг. 2 иллюстрирует полупроводниковую подложку 100. Изоляционная пленка, которая не иллюстрирована, обеспечена на полупроводниковой подложке 100. Поверхность SR полупроводниковой подложки 100 определена в качестве границы между полупроводниковой подложкой 100 и изоляционной пленкой, которая не иллюстрирована. Направление длины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 2, так и поверхности SR. Направление глубины полупроводниковой подложки 100 определено как направление, перпендикулярное поверхности SR.

[0039] Фотодиод и транзистор JFET сформированы в полупроводниковой области 15 N-типа. Ток стока (или, ток канала) транзистора JFET обеспечены посредством полупроводниковой области 15 N-типа. Часть для обеспечения тока стока, сконфигурированная для обеспечения тока стока для полупроводниковой области 15 N-типа, сформирована в части области пиксела или за пределами области пиксела. Часть для обеспечения тока стока, например, включает в себя контактный штырь, соединяющий полупроводниковую подложку и электрические провода.

[0040] Под полупроводниковой областью 15 N-типа находится полупроводниковая область 16 N-типа, которая имеет более высокую концентрацию примеси, чем концентрация примеси в полупроводниковой области 15 N-типа. Сопротивление полупроводниковой подложки 100 может быть понижено посредством полупроводниковой области 16 N-типа. Соответственно, может быть возможно понизить падение напряжения вследствие тока стока, обеспеченного для транзистора JFET. Следовательно, может быть возможно уменьшить помехи, такие как темное пятно, которые происходят вследствие изменения напряжения полупроводниковой подложки в зависимости от местоположений. В результате, качество изображения может быть улучшено. В других случаях, ток стока может быть повышен. В результате, устройство формирования изображений может работать с высокой скоростью.

[0041] Часть 10d со стороны стока области 10 канала может быть опущена, и часть полупроводниковой области 15 N-типа может формировать стоковая область. Стоковая область может быть определена как полупроводниковая область N-типа, которая расположена или размещена, в плане, рядом с областью, в которой должен быть сформирован канал.

[0042] Область 9 затвора включает в себя поверхностную область 9-1 затвора и скрытую область 9-2 затвора. Как поверхностная область 9-1 затвора, так и скрытая область 9-2 затвора имеют P-тип. Две поверхностные области 9-1 затвора расположены или размещены в направлении вдоль поверхности SR, две скрытые области 9-2 затвора расположены или размещены в направлении вдоль поверхности SR, поверхностная область 9-1 затвора и скрытая область 9-2 затвора расположены или размещены в направлении глубины. Поверхностная область 9-1 затвора расположена или размещена между поверхностью SR полупроводниковой подложки 100 и скрытой областью 9-2 затвора.

[0043] Область 10 канала расположена или размещена на глубине между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора. Транзистор JFET с горизонтальной структурой сформирован в вышеописанной конфигурации. В транзисторе JFET с горизонтальной структурой направление длины канала параллельно поверхности SR полупроводниковой подложки 100.

[0044] Поверхностная область 9-1 затвора и скрытая область 9-2 затвора электрически соединены друг с другом. Соединительная часть между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора расположена или размещена таким образом, чтобы не накладываться на область 10 канала при их рассмотрении в плане. Согласно вышеописанной конфигурации, канал транзистора JFET может управляться как посредством поверхностной области 9-1 затвора, так и посредством скрытой области 9-2 затвора.

[0045] Поверхностная область 9-1 затвора и скрытая область 9-2 затвора накладываются друг на друга при их рассмотрении в плане. Другими словами, ортогональная проекция поверхностной области 9-1 затвора на плоскость, параллельную поверхности полупроводниковой подложки, идентична ортогональной проекции скрытой области 9-2 затвора на плоскость. В вышеописанной конфигурации, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы при помощи одной и той же маски, которая является предпочтительной для уменьшения колебаний характеристик транзистора JFET.

[0046] Не требуется, чтобы ортогональная проекция поверхностной области 9-1 затвора была идентична ортогональной проекции скрытой области 9-2 затвора. Например, поверхностная область 9-1 затвора, скрытая область 9-2 затвора и область 10 канала могут быть расположены или размещены таким образом, чтобы поверхностная область 9-1 затвора пересекала область 10 канала в плане, и, при этом, скрытая область 9-2 затвора содержала всю область 10 канала в плане. В вышеописанной конфигурации, поверхностная область 9-1 затвора и скрытая область затвора сформированы при помощи разных масок.

[0047] Либо поверхностная область 9-1 затвора, либо скрытая область 9-2 затвора могут быть опущены. В настоящем варианте осуществления, каждая из областей 9 затвора, которые развернуты при их рассмотрении в плане, включает в себя поверхностную область 9-1 затвора и скрытую область 9-2 затвора. Однако, по меньшей мере, одна из областей 9 затвора, которые развернуты в плане, могут иметь поверхностную область 9-1 затвора или скрытую область 9-2 затвора.

[0048] Как иллюстрировано на Фиг. 2, полупроводниковая область 21 P-типа расположена или размещена между двумя скрытыми областями 9-2 затвора. Полупроводниковая область 21 P-типа расположена или размещена в глубже, чем область 10 канала. Если полупроводниковая область 21 P-типа и область 10 канала сформированы посредством ионных имплантаций, то пик в профиле концентрации примеси, или распределении, вдоль направления глубины полупроводниковой области 21 P-типа расположен в глубже, чем пик в профиле концентрации примеси вдоль направления глубины области 10 канала. Направление глубины определено как направление, перпендикулярное к поверхности SR.

[0049] В настоящем варианте осуществления, вся полупроводниковая область 21 P-типа расположена или размещена на той же самой глубине, что и скрытая область 9-2 затвора. В одном из вариантов осуществления, только часть полупроводниковой области P-типа может быть расположена или размещена на той же самой глубине, что и скрытая область 9-2 затвора

[0050] Концентрация примеси полупроводниковой области 21 P-типа ниже, чем концентрация примеси скрытой области 9-2 затвора. Полупроводниковая область 21 P-типа и скрытая область 9-2 затвора электрически соединены друг с другом. В частности, полупроводниковая область P-типа продолжается в пространственном отношении от полупроводниковой области 21 P-типа до скрытой области 9-2 затвора.

[0051] В качестве изменения настоящего варианта осуществления, может существовать обедненный слой между полупроводниковой областью 21 P-типа и скрытой областью 9-2 затвора. Другими словами, может существовать полупроводниковая область N-типа, обеднение которой происходит между полупроводниковой областью 21 P-типа и скрытой областью 9-2 затвора.

[0052] В конфигурации, где концентрация примеси полупроводниковой области 21 P-типа ниже, чем концентрация примеси скрытой области 9-2 затвора, может быть трудно осуществить обеднение истоковой области 11. В результате, электрическая характеристика транзистора JFET может быть улучшена. Полупроводниковая область 21 P-типа, обеспеченная между двумя скрытыми областями 9-2 затвора, может понизить паразитный ток, который проходит через область между двумя скрытыми областями 9-2 затвора.

[0053] В изменении настоящего варианта осуществления, полупроводниковая область N-типа может быть непрерывно расположена или размещена между двумя скрытыми областями 9-2 затвора, вместо полупроводниковой области 21 P-типа. В вышеописанной конфигурации, могут быть уменьшены колебания электрической характеристики транзистора JFET. Может быть осуществлено обеднение всей полупроводниковой области N-типа, непрерывно расположенного или размещенного между двумя скрытыми областями 9-2 затвора. Другими словами, две скрытые области 9-2 затвора могут быть соединены посредством обедненного слоя. В этой конфигурации, между двумя скрытыми областями 9-2 затвора сформирован, потенциальный барьер, созданный посредством обедненного слоя, который может понизить паразитный ток, проходящий через область между двумя скрытыми областями 9-2 затвора.

[0054] В данном случае будет описан другой аспект структуры в поперечном разрезе, иллюстрированной на Фиг. 2. Полупроводниковая область P-типа, расположенная или размещенная глубже, чем область 10 канала, имеет профиль концентрации примеси, или распределение, который является характерным. Полупроводниковая область P-типа включает в себя первую часть, вторую часть и третью часть. Концентрация примеси второй части и концентрация примеси третьей части соответственно выше, чем концентрация примеси первой части. Первая часть расположена или размещена между второй частью и третьей частью. Полупроводниковая область 21 P-типа может соответствовать первой части. Две скрытые области 9-2 затвора могут соответствовать второй и третьей частям.

[0055] Первая часть накладывается на истоковую область 11 при их рассмотрении в плане. Другими словами, ортогональная проекция первой части на плоскость, параллельная поверхности SR полупроводниковой подложки, накладывается на ортогональную проекцию истоковой области 11 на плоскости. В настоящем варианте осуществления, вторая часть и третья часть не накладываются на истоковую область при их рассмотрении в плане. В другом варианте осуществления, вторая часть и третья часть могут накладываться на истоковую область при их рассмотрении в плане.

[0056] Согласно вышеописанной конфигурации, поскольку концентрация примеси первой части является низкой, может быть сложно осуществить обеднение истоковой области. В результате электрическая характеристика транзистора JFET может быть улучшена.

[0057] Фиг. 3A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 3 схематично иллюстрирует структуру в поперечном разрезе вдоль линии C-D на Фиг. 1. Элементы Фиг. 3A, соответствующие иллюстрированным на Фиг. 1 и/или на Фиг. 2, определяются посредством тех же самых ссылочных обозначений, что и на Фиг. 1 и/или на Фиг. 2. Направление ширины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 3A, так и поверхности SR.

[0058] Как иллюстрировано на Фиг. 3А, полупроводниковая область 21 P-типа является более широкой, чем область 10 канала в направлении ширины канала. В настоящем варианте осуществления, полупроводниковая область 21 P-типа тянется в пределах, в которых полупроводниковая область 21 P-типа достигает области, находящейся непосредственно под областью 3 FD, и области, находящейся непосредственно под истоковой областью 7 МОП транзистора сброса. Полупроводниковая область 21 P-типа может предотвращать омическую проводимость между областью 10 канала и полупроводниковой областью 15 N-типа. Фактически, профили распределения потенциалов могут быть разработаны таким образом, чтобы электрическое сопротивление, вдоль направления, перпендикулярного к поверхности SR, между областью 10 канала и полупроводниковой областью 15 N-типа, могло быть выше, чем электрическое сопротивление, вдоль направления длины канала, между источником и стоковой областью транзистора JFET.

[0059] Фиг. 3B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 3B схематично иллюстрирует структуру в поперечном разрезе вдоль линии E-F на Фиг. 1. Элементы Фиг. 3B? соответствующие иллюстрированным в любой из с Фиг. 1 по 3A обозначены посредством тех же самых ссылочных обозначений, что и на с Фиг. 1 по Фиг. 3А. Направление ширины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 3B, так и поверхности SR.

[0060] Как было упомянуто выше, поверхностная область 9-1 затвора и скрытая область 9-2 затвора электрически соединены друг с другом. В настоящем варианте осуществления, область, имеющая тот же самый тип проводимости, осуществляет электрическое соединение поверхностной области 9-1 затвора и скрытой области 9-2 затвора. Например, на Фиг. 3B, область 3 FD и истоковая область 7 МОП транзистора сброса могут тянуться в направлении глубины полупроводниковой подложки в пределах, в которых они могут осуществлять электрическое соединение поверхностной области 9-1 затвора и скрытой области 9-2 затвора. Несмотря на то что на Фиг. 3 поверхностная область 9-1 затвора и скрытая область 9-2 затвора расположены или размещены на расстоянии друг от друга, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы, в качестве другого варианта, в непрерывно в пространственном отношении посредством диффузии примеси вдоль направления, перпендикулярного к поверхности SR.

[0061] В настоящем варианте осуществления, область 9 затвора и область 10 канала пересекают друг друга в планарной структуре, иллюстрированной на Фиг. 1. Другими словами, ортогональная проекция области 9 затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области 10 канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекают друг друга.

[0062] Пересечение области 9 затвора и области 10 канала означает, что каждая область расположена или размещена таким образом, чтобы пересекать другую область. Другими словами, по меньшей мере, две части области 9 затвора выступают из области 10 канала и, по меньшей мере, две части области 10 канала выступают из области 9 затвора.

[0063] Часть области канала, которая расположена или размещена между двумя областями 9 затвора при их рассмотрении в плане на Фиг. 1, определена как часть 10s со стороны истока области 10 канала. Часть, в пределах области 10 канала, расположенная или размещенная на противоположной стороне к области 10s со стороны истока относительно области 9 затвора, определена как часть 10d со стороны стока области 10 канала. На Фиг. 2 также указаны часть 10s со стороны истока и часть 10d со стороны стока, соответственно. Каждая из части 10s со стороны истока и части 10d со стороны стока области 10 канала не накладываются на область 9 затвора. Другими словами, часть 10s со стороны истока и часть 10d со стороны стока ортогональной проекции области 10 канала, соответствующим образом выступают из ортогональной проекции области 9 затвора. Соответственно, как иллюстрировано на Фиг. 2, длина канала транзистора JFET ограничена посредством конца области 9 затвора. Как иллюстрировано на Фиг. 3B, ширина канала транзистора JFET ограничена посредством конца области 10 канала.

[0064] В соответствии с вышеописанной конфигурацией, даже при том, что могут иметься ошибки совмещения между маской, используемой для формирования области 9 затвора, и маской, используемой для формирования области 10 канала, форма канала транзистора JFET является фактически устойчивой, или постоянной, или неизменной. Следовательно, колебания длины канала и ширины канала транзистора JFET могут быть уменьшены. В результате, колебания характеристики транзистора JFET могут быть уменьшены.

[0065] Уменьшение колебаний в электрической характеристики транзистора JFET может быть достигнуто независимо от формы области 9 затвора или формы области 10 канала. Уменьшение колебаний может быть получено вследствие структуры, в которой область 9 затвора и область канала пересекают друг друга при их рассмотрении в плане. Периферийная поверхность, в плане, области 9 затвора может включать в себя две параллельные линии вдоль направления ширины канала, как иллюстрировано на Фиг. 1. В этой конфигурации, колебание электрической характеристики может быть дополнительно уменьшено. Периферийная поверхность, в плане, области 10 канала может включать в себя две параллельные линии вдоль направления длины канала, как иллюстрировано на Фиг. 1. В этой конфигурации, колебание электрической характеристики может быть дополнительно уменьшено. Область 9 затвора и/или область 10 канала могут иметь прямоугольные формы, соответственно, для того, чтобы маски, используемые для формирования области 9 затвора и области канала, могли быть упрощены. Периферийные поверхности области 9 затвора и области 10 канала могут включать в себя кривые линии. В этой конфигурации, могут быть уменьшены колебания электрической характеристики транзистора JFET вследствие ошибки совмещения при вращении.

[0066] Длина канала транзистора JFET образована как расстояние между концом со стороны стока и концом со стороны истока области 9 затвора. Часть 10d со стороны стока и часть 10s со стороны истока области 10 канала разделены на обе стороны области 9 затвора при их рассмотрении в плане, что дает в результате уменьшение колебаний характеристик. Другими словами, уменьшение колебаний характеристик может быть получено посредством того, что каждая части 10s со стороны истока и части 10d со стороны стока ортогональной проекции области 10 канала выступают из ортогональной проекции области 9 затвора.

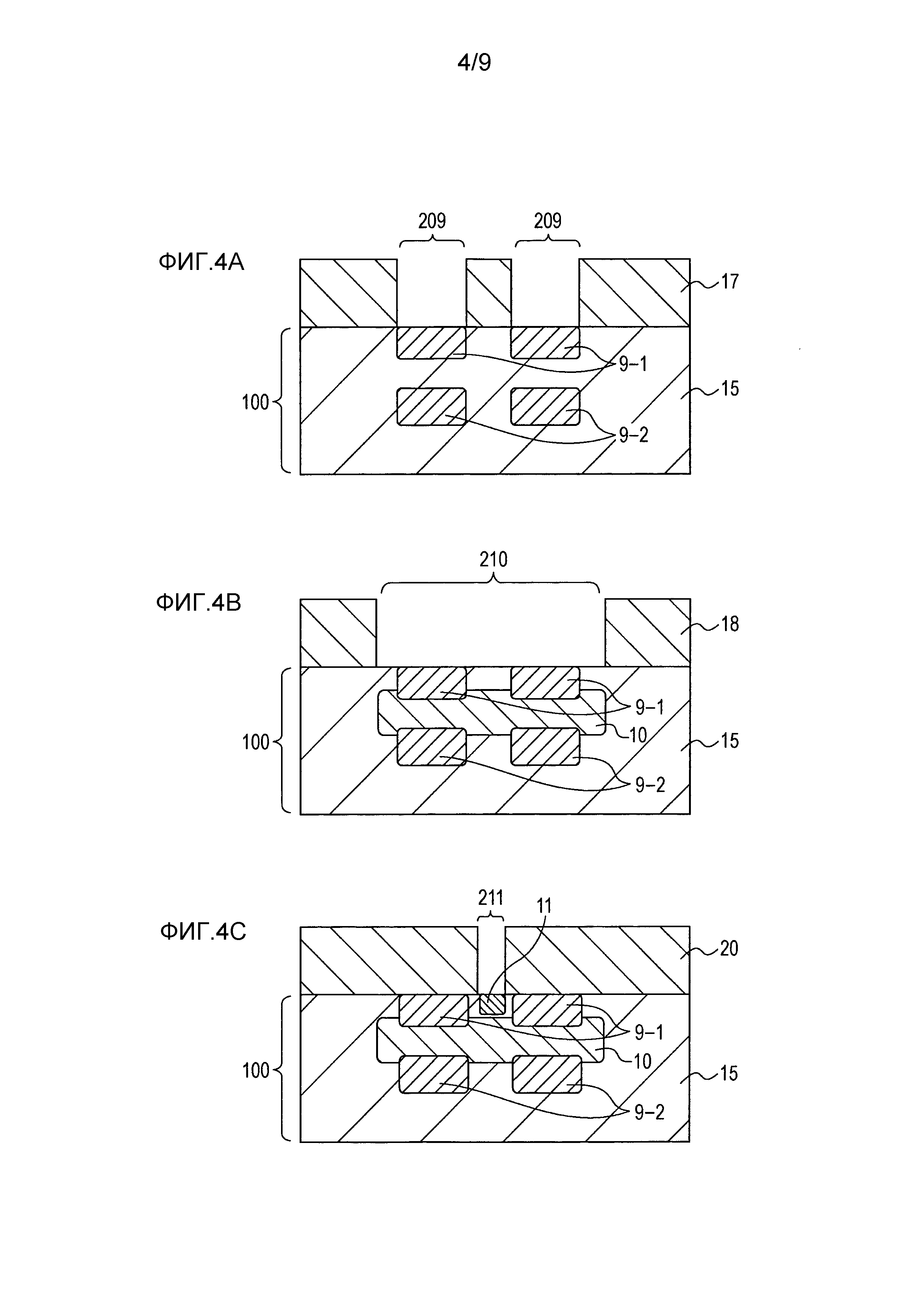

[0067] Далее в настоящем документе, будет объяснен пример способа производства устройства формирования изображений из настоящего варианта осуществления. Фиг. 4A-4C изображают графическое представление, предназначенное для объяснения способа производства устройства формирования изображений из настоящего варианта осуществления. Каждая из Фиг. 4A-4C схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1. Элементы из Фиг. 4A-4C, соответствующие иллюстрированным в любой из с Фиг. 1 по 3B, обозначаются посредством тех же самых ссылочных обозначений, что и с Фиг. 1 по 3B.

[0068] На этапе, иллюстрированном на Фиг. 4A, сформирована область 9 затвора транзистора JFET. На этом этапе используется первая маска 17, которая задает первое окно 209. Первая маска 17, например, получается посредством формирования рисунка в фоторезисте посредством способа фотолитографии.

[0069] Осуществляется легирование примесями, являющимися акцепторами, такими, как бор, полупроводниковой подложки 100 через первое окно 209, в результате чего область 9 затвора формируется в области, соответствующей первому окну 209. Например, область 9 затвора может быть сформирована посредством ионной имплантации с использованием первой маски 17. Посредством выполнения множества ионных имплантаций с разными энергиями имплантируемых ионов, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы на отличных друг от друга глубинах. В целом, более высокий уровень энергии используется для формирования полупроводниковой области в более глубоком положении на полупроводниковой подложке 100. В соответствии с энергиями имплантируемых ионов, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы непрерывно в пространстве посредством диффузии примеси вдоль направления, перпендикулярного поверхности SR. После формирования области 9 затвора, первая маска 17 удаляется.

[0070] Помимо ионной имплантации, может быть использован способ термической диффузии для выполнения легирования примесью полупроводниковой подложки 100.

[0071] На этапе, иллюстрированном на Фиг. 4B, формируется область 10 канала транзистора JFET. На этом этапе используется третья маска 18, которая задает третье окно 210. Третью маску 18, например, получают посредством формирования рисунка в фоторезисте посредством способа фотолитографии.

[0072] Выполняется легирование примесями, являющимися донорами, такими, как фосфор и мышьяк, в полупроводниковую подложку 100 через третье окно 210, в результате чего область 10 канала формируется в области, соответствующей третьему окну 210. Например, область 10 канала может быть сформирована посредством ионной имплантации с использованием третьей маски 18. Энергия имплантируемых ионов, используемая для формирования области 10 канала, может быть отрегулирована таким образом, чтобы область 10 канала была сформирована на глубине между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора. После формирования области 10 канала, третья маска 18 удаляется.

[0073] Несмотря на то что на Фиг. 4 это не показано, полупроводниковая область P-типа, которая осуществляет электрическое соединение множества областей 9 затвора друг с другом, может быть сформирована с использованием маски 19, которая задает окна 203 и 207. Маску 19, например, получают посредством формирования рисунка в фоторезисте посредством способа фотолитографии.

[0074] В настоящем варианте осуществления, область 3 FD и истоковая область 7 из МОП транзистора сброса формируются с использованием маски 19. Эти области осуществляют электрическое соединение областей 9 затвора друг с другом. После формирования полупроводниковой области P-типа, которая осуществляет электрическое соединение множества областей 9 затвора друг с другом, маска 19 удаляется.

[0075] На этапе, иллюстрированном на Фиг. 4C, формируется истоковая область 11, которая соединена с частью 10s со стороны истока области 10 канал. На этом этапе используется четвертая маска 20, которая задает четвертое окно 211. Четвертая маска 20 является твердой маской. Четвертая маска 20 включает в себя изоляционную пленку, изготовленную из неорганического материала, такого, как оксид кремния, нитрид кремния и оксинитрид кремния.

[0076] Выполняется легирование примесями, являющимися донорами, такими, как фосфор и мышьяк, в полупроводниковую подложку 100 через четвертое окно 211, в результате чего истоковая область 11 формируется в области, соответствующей четвертому окну 211.

[0077] Четвертая маска 20 может быть использована в качестве межслойной изоляционной пленки, в случае использования твердой маски в качестве четвертой маски 20, как было упомянуто выше. В частности, после формирования истоковой области 11, четвертая маска 20 остается не удаленной, и затем, контактный штырь 12, электрически соединенный с истоковой областью 11, формируется в четвертом окне 211. После этого, выходная линия 14, соединенная с контактным штырем 12, формируется на четвертой маске 20.

[0078] Далее будут объяснены планарные структуры масок 17-19 и их относительные положения. Фиг. 5A и 5B изображают графические представления, схематично иллюстрирующие маски 17-19, используемые на этапах, иллюстрированных на Фиг. 4A-4C. Элементы из Фиг. 5A-5B, соответствующие иллюстрированным на любой из с Фиг. 4A по 4C, обозначены посредством тех же самых ссылочных обозначений, что и с Фиг. 4A по 4C.

[0079] Каждая из Фиг. 5A и 5B иллюстрирует первое окно 209, третье окно 210 и окна 203 и 207. Фиг. 5B отличает каждую часть третьего окна 210. В настоящем варианте осуществления, каждое из первого окна 209, третьего окна 210 и окон 203 и 207 имеет прямоугольную форму. Первая маска 17, которая задает первое окно 209, обозначена как область, находящаяся за пределами прямоугольника, обозначающего окно 209. Третья маска 18, которая задает третье окно 210, обозначена как область, находящаяся за пределами прямоугольника, обозначающего третье окно 210. Маска 19, которая задает окна 203 и 207, обозначена как область, находящаяся за пределами прямоугольников, обозначающих окна 203 и 207.

[0080] Для простоты объяснения, окна 209, 210, 203 и 207 иллюстрированы таким образом, чтобы осуществлять наложение друг на друга на Фиг. 5A и 5B, в результате чего они обозначают совмещения между масками. Однако маска может быть удалена после формирования соответствующей полупроводниковой области на каждом этапе. Соответственно, две или более маски не обязательно предоставлены в один и тот же момент времени.

[0081] Первое окно 209 и третье окно 210 пересекают друг друга при их рассмотрении в плане. Другими словами, ортогональная проекция первого окна 209 на плоскость, параллельную поверхности полупроводниковой подложки 100, пересекает ортогональную проекцию третьего окна 210 на плоскости.

[0082] Как иллюстрировано на Фиг. 5B, третье окно 210 включает в себя часть 210s со стороны истока и часть 210d со стороны стока. Часть 210s со стороны истока третьего окна 210 соответствует части 210s со стороны истока области 10 канала. Часть 210d со стороны стока окна 210 соответствует части 10d со стороны стока области 10 канала. На Фиг. 5B имеются две части 210d со стороны стока: одна является частью на левой стороне первого окна 209L, другая является частью на правой стороне первого окна 209R.

[0083] Каждая из части 210s со стороны истока и части 210d со стороны стока третьего окна 210 накладываются на первую маску 17 при их рассмотрении в плане. Другими словами, каждая ортогональная проекция части 210s со стороны истока на плоскости параллельна поверхности полупроводниковой подложки 100, а ортогональная проекция части 210d со стороны стока на плоскости накладывается на ортогональную проекцию первой маски 17 на плоскости. Соответственно, как иллюстрировано на Фиг. 5, длина канала транзистора JFET ограничена посредством концов первого окна 209. Ширина канала транзистора JFET ограничена посредством концов третьего окна 210.

[0084] Согласно вышеописанной конфигурации, даже при том, что могут существовать ошибки совмещения между первой маской 17, используемой для формирования области 9 затвора, и третьей маской 18, используемой для формирования области 10 канала, форма канала транзистора JFET является почти устойчивой, или постоянной, или неизменной. Следовательно, колебания длины канала и ширины канала транзистора JFET могут быть уменьшены. В результате, колебания характеристики транзистора JFET могут быть уменьшены.

[0085] В настоящем варианте осуществления, первое окно включает в себя множество окон 209L и 209R, которые разделены посредством первой маски 17. Каждое из окон 209L и 209R пересекает третье окно 210 при их рассмотрении в плане. Другими словами, каждая из ортогональных проекций множества окон 209L и 209R на плоскость, параллельную поверхности полупроводниковой подложки 100, пересекает ортогональную проекцию третьего окна 210. Часть 210s со стороны истока третьего окна 210 накладывается на первую маску 17, в частности, на часть первой маски 17, которая расположена или размещена между этими двумя окнами 209L и 209R, при их рассмотрении в плане.

[0086] Первое окно 209 частично накладывается на окна 203 и 207 при их рассмотрении в плане. Другими словами, ортогональная проекция первого окна 209 на плоскость, параллельную поверхности полупроводниковой подложки 100, частично накладывается на ортогональные проекции окон 203 и 207 на плоскость.

[0087] Согласно вышеописанной конфигурации, может быть расширена эффективная ширина канала транзистора JFET. Другими словами, может быть улучшена запирающая способность вентиля транзистора JFET. Следовательно, устройство формирования изображений может работать с высокой скоростью.

[0088] Будет объяснен этап формирования полупроводниковой области 21 P-типа. Вот пример, в котором полупроводниковая область 21 P-типа сформирована после этапа, иллюстрированного на Фиг. 4C. Однако полупроводниковая область P-типа может быть сформирована в любой момент времени в процессе изготовления устройства формирования изображений. В случае использования жесткой маски для четвертой маски 20, полупроводниковая область 21 P-типа может быть сформирована до формирования истоковой области 11.

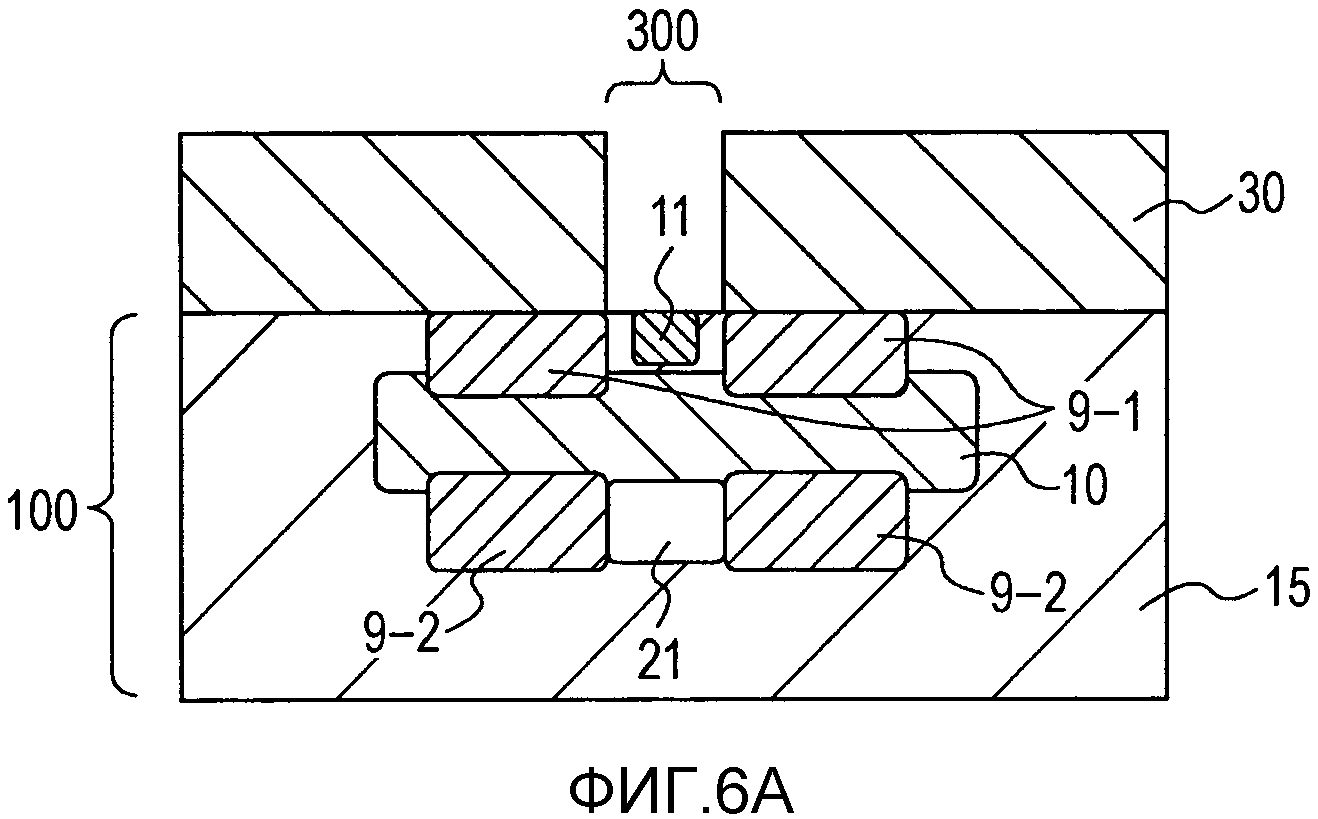

[0089] Фиг. 6A изображает графическое представление для объяснения способа производства устройства формирования изображений. Фиг. 6A схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1. Элементы из Фиг. 6A, соответствующие иллюстрированным на любой из с Фиг. 1 по 3B, обозначены посредством тех же самых ссылочных обозначений, что и с Фиг. 1 по 3B.

[0090] На этапе, иллюстрированном на Фиг. 6A, формируется полупроводниковая область 21 P-типа. На этом этапе используется вторая маска 30, которая задает второе окно 300. Вторую маску 30, например, получают посредством формирования рисунка в фоторезисте посредством способа фотолитографии.

[0091] Выполняется легирование примесями, являющимися акцепторными примесями, такими, как бор, в полупроводниковую подложку 100 через второе окно 300, в результате чего, полупроводниковая область 21 P-типа формируется в области, соответствующей второму окну 300. Например, полупроводниковая область 21 P-типа может быть сформирована посредством ионной имплантации с использованием второй маски 30. После формирования полупроводниковой области 21 P-типа, вторая маска 30 удаляется.

[0092] На вышеупомянутом этапе, выполняется легирование примесями, являющимися акцепторными примесями, в область на ту же самую глубину, что и скрытая область 9-2 затвора. В случае формирования полупроводниковой области 21 P-типа посредством ионной имплантации, энергия имплантируемых ионов, используемая для формирования полупроводниковой области 21 P-типа, может быть отрегулирована таким образом, чтобы выполнялось легирование примесями, являющимися акцепторными примесями, в область на той же самой глубине, что и скрытая область 9-2 затвора.

[0093] В настоящем варианте осуществления, выполняется легирование примесями, являющимися акцепторными примесями, в результате чего формируется полупроводниковая область 21 P-типа. В качестве изменения, полупроводниковая область N-типа может быть сформирована между двумя скрытыми областями 9-2 затвора. В структуре вышеупомянутого изменения, концентрация примеси полупроводниковой области N-типа может быть понижена посредством выполнения легирования примеси, как иллюстрировано на Фиг. 6A. В результате, паразитный ток может быть уменьшен.

[0094] Помимо ионной имплантации, может быть использован способ термической диффузии для выполнения легирования примесью полупроводниковой подложки 100.

[0095] Далее будет объяснена планарная структура второй маски 30 и относительные положения между второй маской 30 и масками 17-20. Фиг. 6B изображает графическое представление, схематично иллюстрирующее маски 17-20 и 30, используемые на этапах, иллюстрированных на Фиг. 4A-4C и 6A. Элементы из Фиг. 6B, соответствующие, иллюстрированным на любой из с Фиг. 4А по 4C, обозначаются посредством тех же самых ссылочных обозначений, что и с Фиг. 4A по 4C.

[0096] Фиг. 6B иллюстрирует первое окно 209, второе окно 300, третье окно 210, четвертое окно 211 и окна 203, 207. В настоящем варианте осуществления, второе окно 300 имеет прямоугольную форму. Вторая маска 30, которая задает второе окно 300, обозначена как область, находящаяся за пределами прямоугольника, обозначающего второе окно 300. В настоящем варианте осуществления, четвертое окно 211 имеет квадратную форму. Четвертая маска 20, которая задает четвертое окно 211, обозначена как область, находящаяся за пределами квадрата, обозначающего четвертое окно 211.

[0097] Для простоты объяснения, множество окон иллюстрировано таким образом, чтобы осуществлять наложение друг на друга на Фиг. 6B, в результате чего, Фиг. 6B обозначает совмещение между масками. Однако маска может быть удалена после формирования соответствующей полупроводниковой области на каждом этапе. Соответственно, две или более маски не обязательно предоставлены в один и тот же момент времени.

[0098] Теперь будет объяснено изменение настоящего варианта осуществления. Фиг. 7A изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений из настоящего варианта осуществления. Транзистор JFET иллюстрирован на Фиг. 7A. Элементы Фиг. 7A, соответствующие иллюстрированным на Фиг. 1, обозначаются посредством тех же ссылочных обозначений, что и на Фиг. 1. Структура устройства формирования изображений аналогична структуре первого варианта осуществления, за исключением объясненных иначе элементов. Несмотря на то что это не иллюстрировано на Фиг. 7A, полупроводниковая область 21 P-типа фактически обеспечена таким же образом, как и на Фиг. 1.

[0099] Одним из отличительных признаков настоящего варианта осуществления является форма области 61 затвора транзистора JFET. В частности, область 61 затвора окружает часть 10s со стороны истока области 10 канала при их рассмотрении в плане. Две части области 61 затвора соответствующим образом пересекают область 10 канала при их рассмотрении в плане. Каждая из области 10s со стороны истока и области 10d со стороны стока области 10 канала не накладываются на область 61 затвора. Каждая из области 10s со стороны истока и области 10d со стороны стока выступают из области 61 затвора. Соответственно, длина канала транзистора JFET ограничена концом области 61 затвора. Ширина канала транзистора JFET ограничена концом области 10 канала.

[00100] Согласно вышеописанной конфигурации, даже при том, что могут существовать ошибки совмещения между маской, используемой для формирования области 61 затвора, и маской, используемой для формирования области 10 канала, форма канала транзистора JFET является почти устойчивой, или постоянной, или неизменной. Следовательно, колебания длины канала и ширины канала транзистора JFET могут быть уменьшены. В результате, колебания характеристики транзистора JFET могут быть уменьшены.

[00101] В изменении, иллюстрированном на Фиг. 7A, область 61 затвора является непрерывной в пространственном отношении. Поверхностная область затвора и скрытая область затвора электрически соединены друг с другом посредством соединительной части, которая не накладывается на область 10 канала при их рассмотрении в плане. Следовательно, эффективная ширина канала транзистора JFET может быть расширена, при одновременном пропуске этапа формирования полупроводниковой области, имеющей тот же самый тип проводимости, что и две области затвора, и соединяющей две области затвора. Например, этап формирования области 3 FD, изображенной на Фиг. 1, может быть опущен.

[00102] Теперь будет объяснено другое изменение. Фиг. 7B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Транзистор JFET иллюстрирован на Фиг. 7B. Элементы Фиг. 7B, соответствующие иллюстрированным на Фиг. 1, обозначены посредством тех же самых ссылочных обозначений, что и на Фиг. 1. Структура устройства формирования изображений аналогична первому варианту осуществления за исключением объясненных иначе элементов. Область 9 затвора транзистора JFET, иллюстрированная на Фиг. 6C, включает в себя только скрытую область 9-2 затвора.

[00103] Как было описано выше, согласно некоторым из вариантов осуществления, полупроводниковая область 21 P-типа обеспечена в пикселе. Концентрация примеси полупроводниковой области 21 P-типа ниже, чем концентрация примеси скрытой области 9-2 затвора. Согласно вышеописанной конфигурации, полупроводниковая область 21 P-типа может предотвращать распространение обедненного слоя в истоковую область. В результате, характеристика транзистора JFET может быть улучшена.

[00104] В некоторых других вариантах осуществления, обедненная полупроводниковая область N-типа расположена или размещена таким образом, чтобы продолжиться в пространственном отношении от одной скрытой области 9-2 затвора в другую скрытую область 9-2 затвора. Согласно вышеописанной конфигурации, можно предотвратить распространение обедненного слоя в истоковую область. В результате, характеристика транзистора JFET может быть улучшена.

[00105] Область между двумя скрытыми областями 9-2 затвора легируется примесями P-типа (акцепторными примесями). Соответственно, имеется возможность достижения высокого электрического сопротивления между областью 10 канала и полупроводниковой областью 15 N-типа. В результате, имеется возможность уменьшения паразитного тока, который проходит через область, отличную от канала, образованную посредством области 9 затвора и области 10 канала. Поскольку зависимость паразитного потока от напряжения затвора является низкой, паразитный ток большой силы может ухудшить вольтамперную характеристику транзистора JFET. Следовательно, уменьшение паразитного потока может улучшить вольтамперную характеристику транзистора JFET.

[00106] Концентрация примеси полупроводниковой области 21 P-типа может быть отрегулирована таким образом, чтобы дополнительно уменьшать паразитный ток. В частности, концентрация примеси полупроводниковой области P-типа может быть выше, чем концентрация примеси скрытой области затвора.

ВТОРОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00107] Далее будет описан другой вариант осуществления. Главное отличие от первого варианта осуществления заключается в том, что транзистор JFET включает в себя структуру LDD (слаболегированного стока). Объяснение будет сфокусировано на отличиях от первого варианта осуществления, и объяснение той же самой структуры, что и в первый вариант осуществления, будет опущено.

[00108] Планарная структура устройства формирования изображений из настоящего варианта осуществления является такой же, как и в первом варианте осуществления. Другими словами, Фиг. 1 схематично иллюстрирует планарную структуру устройства формирования изображений из настоящего варианта осуществления. В настоящем варианте осуществления, полупроводниковая область N-типа добавлена к области, которая накладывается на области затвора из Фиг. 1.

[00109] Фиг. 8A-8C изображают графическое представление для объяснения способа производства устройства формирования изображений из настоящего варианта осуществления. Каждая из Фиг. 8A-8C схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1, которая является поперечным сечением, включающим в себя направление длины канала транзистор JFET.

[00110] На этапе, иллюстрированном на Фиг. 8A, формируются поверхностная область 9-1 затвора и скрытая область 9-2 затвора. Способ формирования поверхностной области 9-1 затвора и скрытой области 9-2 затвора является таким же, как иллюстрированный на Фиг. 4A из первого варианта осуществления. Как описано в объяснении первого варианта осуществления, на этом этапе используется первая маска 17, которая задает первое окно 209.

[00111] В настоящем варианте осуществления полупроводниковая область 22 N-типа сформирована с использованием первой маски 17, которая использовалась или будет использована для формирования поверхностной области 9-1 затвора и скрытой области 9-2 затвора. Выполняется легирование примесями, являющимися донорами, такими, как фосфор и мышьяк, в полупроводниковую подложку 100 через первое окно 209, в результате чего полупроводниковая область 22 N-типа формируется в области, соответствующей первому окну 209.

[00112] Первую маску 17, например, получают посредством формирования рисунка в фоторезисте посредством способа фотолитографии. В других случаях, первая маска 17 может являться твердой маской.

[00113] Полупроводниковая область 22 N-типа накладывается на область 9 затвора при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области 22 N-типа на плоскость, параллельную поверхности полупроводниковой подложки 100, идентична ортогональной проекции области 9 затвора на плоскости. Полупроводниковая область 22 N-типа расположена или размещена на глубине между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора. Поверхностная область 9-1 затвора, скрытая область 9-2 затвора и полупроводниковая область 22 N-типа могут быть сформированы посредством ионной имплантации. В этом случае, энергии имплантируемых ионов, используемые для формирования поверхностной области 9-1 затвора, скрытой области 9-2 затвора и полупроводниковой области 22 N-типа могут быть отрегулированы таким образом, чтобы полупроводниковая область 22 N-типа была расположена или размещена на глубине между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора.

[00114] На этапе, иллюстрированном на Фиг. 8B, формируется область 10 канала транзистора JFET. Поскольку этап, предназначенный для формирования области 10 канала, является таким же самым, как и этап в первом варианте осуществления, его подробное объяснение будет опущено.

[00115] На этапе, иллюстрированном на Фиг. 8C, формируется истоковая область 11. Поскольку этап формирования истоковой области 11 является таким же, как и в первом варианте осуществления, его подробное объяснение будет опущено.

[00116] Часть области 10 канала, легирование которой примесями не было выполнено на этапе, иллюстрированном на Фиг. 8A, функционирует в качестве области выравнивания потенциала (или, области ослабления электрического поля). Канал формируется в области, в которой область 10 канала и полупроводниковая область 22 N-типа накладываются друг на друга. Легирование примесями выполняется в области на каждом из двух этапов формирования области 10 канала и формирования полупроводниковой области 22 N-типа. Соответственно, другая часть области канала, то есть, часть, легирование которой примесями не выполнялось на этапе, иллюстрированном на Фиг. 9A, имеет относительно низкую концентрацию примеси. Следовательно, может быть возможно уменьшить концентрацию примеси части области 10 канала, которая выступает из области 9 затвора.

[00117] Согласно стоку с низкой концентрацией примеси, может быть ослаблено электрическое поле рядом со стоковой областью транзистора JFET. Если рядом со стоковой областью сгенерировано большое электрическое поле транзистора JFET, то ток канала производит ионизацию соударением, и таким образом, формирует носители заряда. Сгенерированные носители заряда могут сталкиваться с областью 9 затвора, который накапливает носители заряда сигнала, в результате чего могут быть сгенерированы помехи. Ослабление электрического поля вокруг стоковой области транзистора JFET может предотвратить ионизацию соударением, которая вызывает помехи. В результате, помехи в пикселе могут быть уменьшены.

[00118] В целом, ток канала транзистора JFET производит ионизацию соударением в области отсечки, находящейся рядом со стоковой областью. Для ослабления электрического поля области отсечки и предотвращения ионизации соударением, может быть использована низкая концентрация примеси стоковой области.

[00119] В настоящем варианте осуществления, канал транзистора JFET может быть образован только полупроводниковой областью 22 N-типа без формирования области 10 канала. В этом случае, часть полупроводниковой области 15 N-типа формирует стоковая область. Без области 10 канала, ширина канала транзистора JFET образуется как расстояние между областью 3 FD и истоковой областью 7 МОП транзистора сброса вдоль направления ширины канала.

[00120] Как было описано выше, согласно настоящему варианту осуществления, помехи могут быть уменьшены в дополнение к получению технического эффекта первого варианта осуществления.

ТРЕТИЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00121] Далее будет описана система формирования изображений согласно варианту осуществления настоящего раскрытия. Примеры системы формирования изображений включают в себя цифровые фотокамеры, цифровые видеокамеры, копировальные устройства, факсимиле, мобильные телефоны, автомобильные камеры и орбитальные спутники. Фиг. 9 иллюстрирует блок-схему цифровой фотокамеры, служащей примером системы формирования изображений.

[00122] На Фиг. 9, ссылочное обозначение 1001 обозначает экран для защиты линзы, 1002 обозначает линзу, вызывающую выполнение фокусирования устройством 1004 формирования изображений на оптическом изображении объекта, подлежащего фотографической фиксации, и 1003 обозначает диафрагму, сконфигурированную для изменения количества света, проходящего через линзу 1002. Ссылочный номер 1004 обозначает устройство формирования изображений, описанное в вышеупомянутых вариантах осуществления, и сконфигурировано для преобразования оптического изображения, сформированного посредством линзы 1002, в данные изображения. Блок аналого-цифрового (AD) преобразования сформирован на полупроводниковой подложке устройства 1004 формирования изображений. Ссылочное обозначение 1007 обозначает, сигнальный процессор, сконфигурированный для подвергания графических данных, выведенных посредством устройства 1004 формирования изображений, различным типам коррекции или сжатию графических данных. На Фиг. 9, ссылочное обозначение 1008 обозначает генератор синхронизирующих импульсов, сконфигурированный для вывода различных типов сигналов синхронизации на устройство 1004 формирования изображений, и сигнальный процессор 1007, а 1009 обозначает весь блок управления, сконфигурированный для управления всей фотографической камерой. Ссылочное обозначение 1010 обозначает блок памяти кадров, сконфигурированный для временного хранения данных изображения, 1011 обозначает интерфейсный блок, сконфигурированный для выполнения записи или считывания носителя информации, и 1012 обозначает носитель информации, способный присоединяться и отсоединяться от устройства 1004 формирования изображений, такой, как полупроводниковое запоминающее устройство или подобное, сконфигурированный для предварительного формирования записи или считывания графических данных. Кроме того, ссылочное обозначение 1013 обозначает интерфейсный блок, сконфигурированный для обмена данными с внешним компьютером или подобным. В данном случае, сигнал синхронизации или подобное могут быть введены снаружи системы формирования изображений. Система формирования изображений может включать в себя, по меньшей мере, устройство 1004 формирования изображений и сигнальный процессор 1007, сконфигурированный для обработки графического сигнала, выведенного из устройства 1004 формирования изображений.

[00123] В настоящем варианте осуществления была описана конфигурация, в которой устройство 1004 формирования изображений и блок AD преобразования обеспечены на другой полупроводниковой подложке. Однако устройство 1004 формирования изображений и блок AD преобразования могут быть сформированы на одной и той же полупроводниковой подложке. Кроме того, устройство 1004 формирования изображений и сигнальный процессор 1007 могут быть сформированы на одной и той же полупроводниковой подложке.

[00124] Кроме того, сигнальный процессор 1007 может быть сконфигурирован для обработки сигнала на основе носителя электрического сигнала, сгенерированной в первом блоке 101A фотоэлектрического преобразования, и сигнала на основе несущей электрического сигнала, сгенерированной во втором блоке 102A фотоэлектрического преобразования, для получения информации о расстоянии от устройства 1004 формирования изображений до объекта.

[00125] Устройство формирования изображений согласно одному из первого варианта осуществления и второго варианта осуществления используется в качестве устройства 1004 формирования изображений в системе формирования изображений согласно настоящему варианту осуществления. Следовательно, характеристика транзистора JFET может быть улучшена посредством применения варианта осуществления настоящего раскрытия к системе формирования изображений.

[00126] Несмотря на то что настоящее раскрытие было описано со ссылкой на иллюстративные варианты осуществления, следует понимать, что изобретение не ограничено раскрытыми иллюстративными вариантами осуществления. Объем следующей формулы изобретения должен получить самую широкую интерпретацию для того, чтобы охватывать все такие модификации и эквивалентные структуры и функции.