Результат интеллектуальной деятельности: УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Настоящая технология относится к устройствам обработки данных и способам обработки данных, и, более конкретно, к устройству обработки данных и способу обработки данных, которые позволяют улучшить, например, устойчивость к ошибкам данных.

Уровень техники

Коды LDPC (проверки четности с низкой плотностью) имеют высокие возможности по коррекции ошибок, и в настоящее время их начинают широко использовать в системах передачи данных, включающих в себя цифровую спутниковую широковещательную передачу, такую как DVB (цифровая широковещательная передача видеоданных)-S.2, которая воплощена, например в Европе (см., например, непатентный документ 1). Кроме того, рассматривается использование кодов LDPC при наземной цифровой широковещательной передаче следующего поколения.

Последние исследования показали, что коды LDPC, имеющие большую длину кода, обладают возможностями, приближающимися к пределу Шеннона, такими, как у турбокода и т.п. Кроме того, код LDPC отличается тем, что минимальное расстояние пропорционально его длине кода. Учитывая это, особенности кода LDPC имеют преимущества, состоящие в том, что вероятность ошибки блока является высокой, и мало вероятно возникают, так называемые, явления минимального уровня ошибок, которые наблюдают в характеристиках декодирования турбокодов и т.п.

Такие коды LDPC подробно описаны ниже. Коды LDPC представляют собой линейные коды, и не обязательно двоичные коды. В этом описании, однако, коды LDPC описаны, как двоичные коды.

Наиболее существенная особенность кода LDPC состоит в том, что матрица проверки четности, определяющая код LDPC, является разреженной. Здесь разреженная матрица представляет собой матрицу, которая имеет очень малое количество элементов матрицы, равных "1" (или матрицу, в которой большинство элементов равно "0").

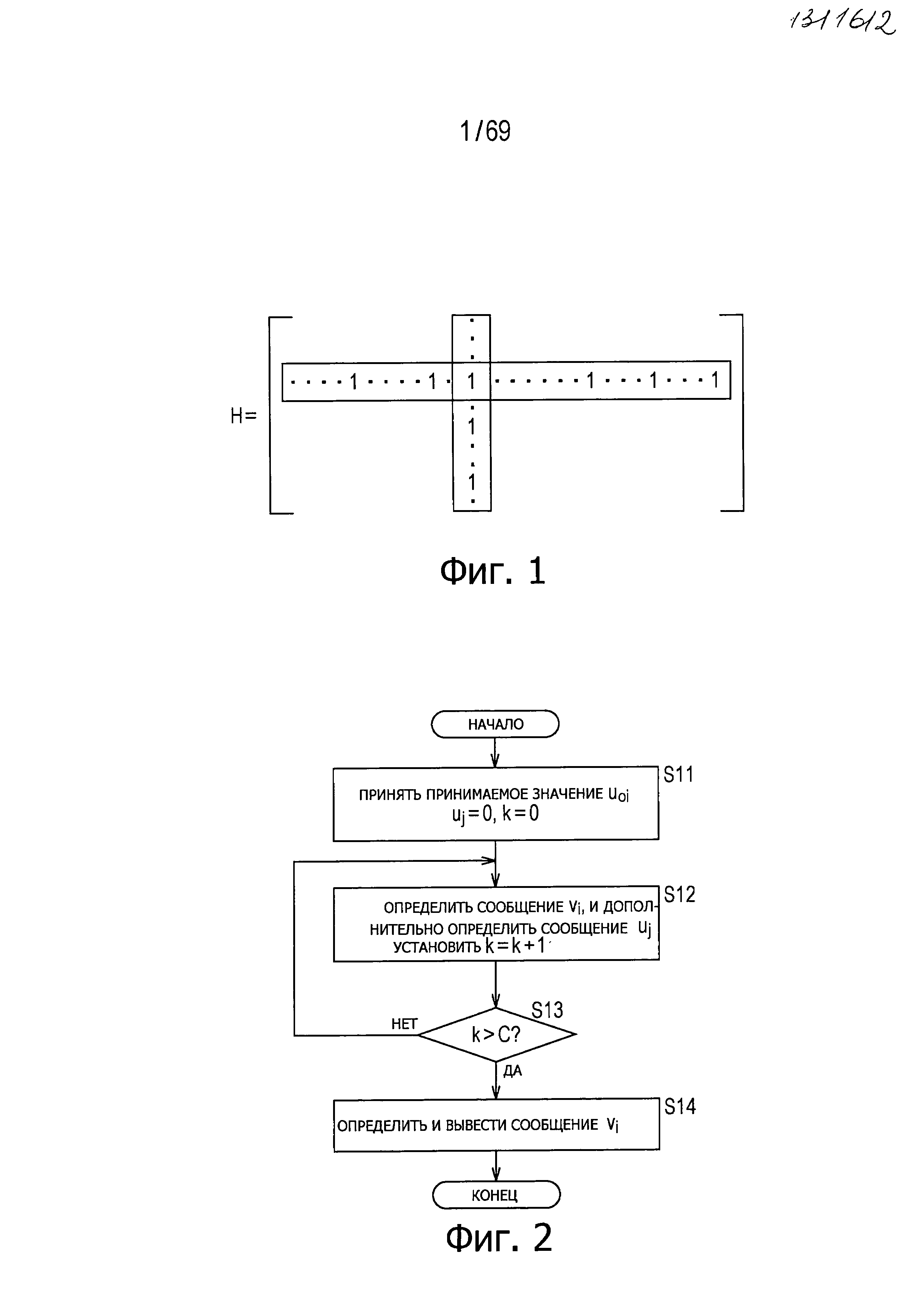

На фиг.1 показан пример матрицы Н проверки четности кода LDPC.

В матрице Н проверки четности, показанной на фиг.1, вес каждого столбца.(вес столбца) (количество элементов равных "1") равен "3", и вес каждой строки (вес строки) равен "6".

При кодировании, когда используется код LDPC (кодирование LDPC), генерируют порождающую матрицу G, например, на основе матрицы Н проверки четности, и порождающую матрицу G умножают на двоичные информационные биты для генерирования кодового слова (кода LDPC).

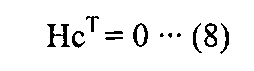

В частности, устройство кодирования, которое выполняет кодирование LDPC, вначале вычисляет такую порождающую матрицу G, чтобы она удовлетворяла уравнению GHT=0, в отношении транспонированной матрицы HT матрицы Н проверки четности. Здесь, если порождающая матрица G представляет собой матрицу K×N, устройство кодирования умножает порождающую матрицу G на строку битов (вектор u) из информационных битов, состоящих из К битов, для генерирования кодового слова с (=uG), состоящего из N битов. Кодовое слово (код LDPC), генерируемое устройством кодирования, принимают на стороне приема через заданный канал.

Декодирование кода LDPC может быть выполнено путем использования алгоритма пропуска сообщений, который представляет собой алгоритм, рассматриваемый, как вероятностное декодирование Галлагера, и основано на распространении степени уверенности в, так называемом, графе Таннера, сформированном с переменными узлами (также называются узлами сообщения) и узлами проверки. Ниже переменные узлы и узлы проверки также, соответственно, называются просто узлами.

На фиг.2 показаны процедуры для декодирования кода LDPC.

Следует отметить, что реальное значение (LLR приема), представляющее логарифм отношения вероятности указывающей вероятность того, что значение i-ого знакового бита в коде LDPC (одно кодовое слово), принятом на стороне приема, равно "0", также будет называться принятым значением u0i в соответствующих случаях. Кроме того, сообщение, которое выводят от узла проверки, представлено, как uj, и сообщение, которое выводят от переменного узла, представлено, как vi.

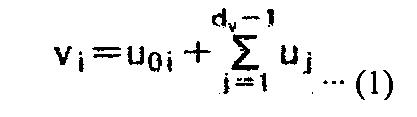

Вначале, при декодировании кода LDPC, как показано на фиг.2, код LDPC принимают на этапе S11. Сообщение (сообщение узла проверки) uj инициируют, делая равным "0", и переменную k, которая представляет собой целое число, как периодически повторяющийся счетчик обработки, инициируют, сбрасывая в "0". Операция затем переходит на этап S12. На этапе S12, на основе принятого значения u0i, полученного в результате приема кода LDPC, выполняют вычисление, показанное в уравнении (1) (вычисление переменного узла), для определения сообщения (сообщение переменного узла) vi. Кроме того, на основе сообщения vi, выполняют вычисление (вычисление узла проверки), показанное в уравнении (2), для определения сообщения uj.

[Математическая формула 1]

[Математическая Формула 2]

В уравнении (1) и в уравнении (2), dv и dc представляют параметры, которые могут быть произвольно выбраны и представляют количество элементов, равных "1", в вертикальном направлении (в столбце) и в горизонтальном направлении (строке) в матрице Н проверки четности, соответственно. В случае кода (3, 6), например, dv равен 3, и dc равен 6.

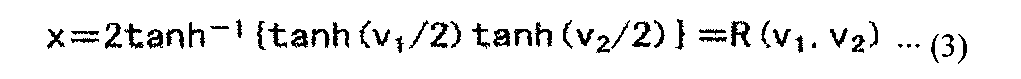

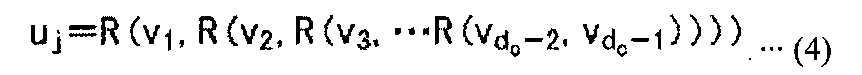

При вычислении переменного узла, показанного в уравнении (1), и при вычислении узла проверки, показанного в уравнении (2), сообщения, которые вводят от ребер (линии, каждая из которых соединяет переменный узел и проверочный узел), которые готовы для вывода сообщений, не подвергают вычислениям. Поэтому, диапазон вычислений составляет от 1 до dv-1 или от 1 до dc-1. На практике, вычисление проверочного узла, показанное в уравнении (2), выполняют путем подготовки заранее таблицы функции R (v1, v2) показанной в уравнении (3), определенной одним выходом для двух входных данных v1 и v2, и постоянно (рекурсивно) используя таблицу, как показано в уравнении (4).

[Математическая формула 3]

[Математическая формула 4]

Кроме того, на этапе S12, выполняют последовательное приращение переменной к только на "1", и операция затем переходит на этап S13. На этапе S13 выполняют проверку для определения, превышает ли переменная k заданное число С повторений декодирования. Если определяют, что переменная k не больше, чем С на этапе S13, операция возвращается на этап S12, и повторяют те же процедуры, как описаны выше.

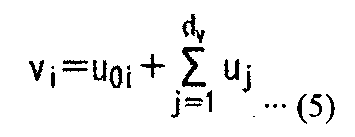

Если определяют, что переменная k больше, чем С на этапе S13, операция переходит на этап S14, и вычисление, показанное в уравнении (5), выполняют для определения сообщения vi, в качестве результата декодирования, который должен быть выведен в конечном итоге. Сообщение vi затем выводят, и операция декодирования кода LDPC подходит к концу.

[Математическая формула 5]

Здесь вычисление, показанное в уравнении (5), выполняют, используя сообщения uj от всех ребер, соединенных с переменными узлами, в отличие от вычисления переменного узла, показанного в уравнении (1).

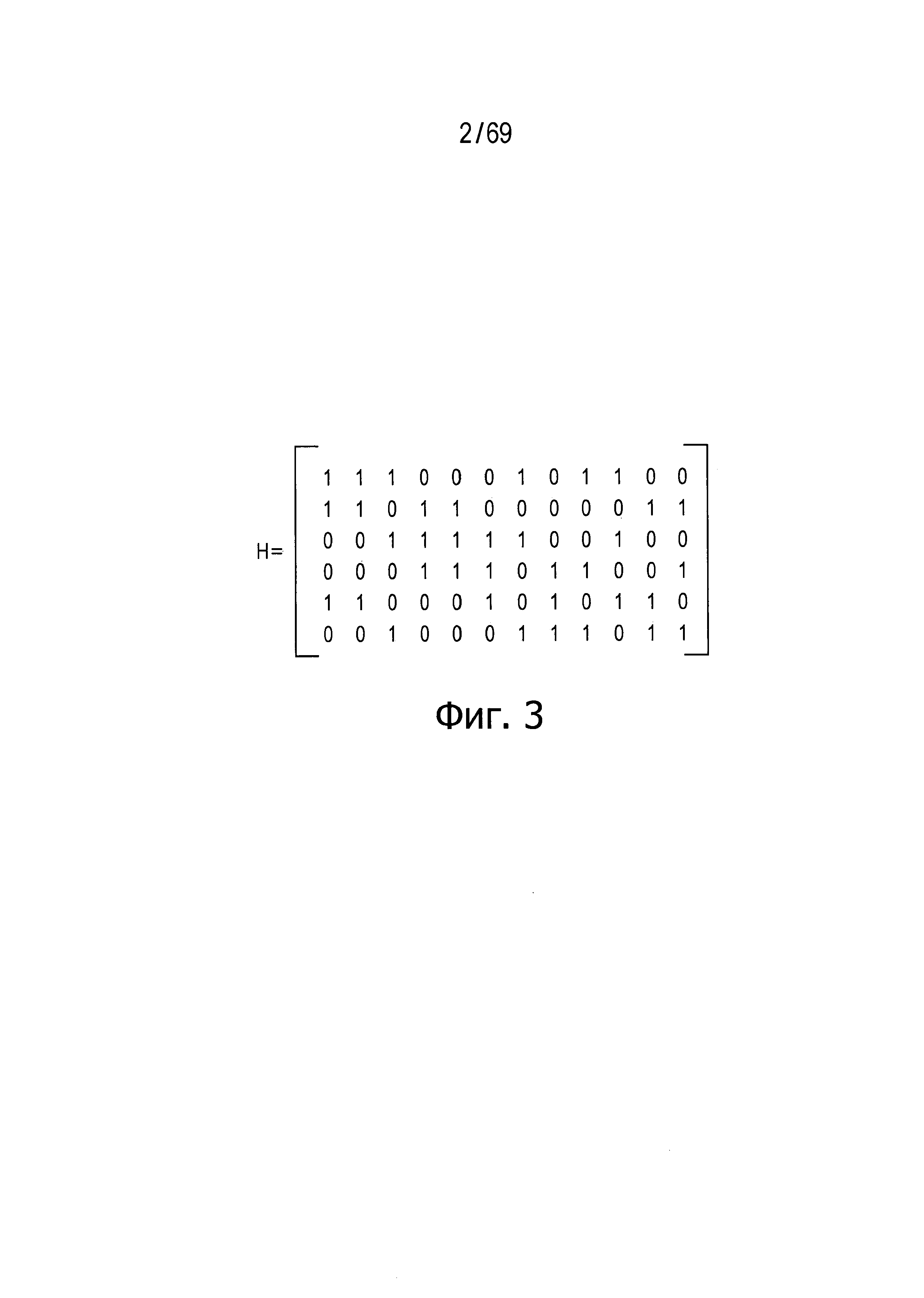

На фиг.3 показан пример матрицы Н проверки четности кода LDPC (3, 6) (скорость кода 1/2, длина кода 12).

В матрице Н проверки четности, показанной на фиг.3, вес столбца равен 3, и вес строки равен 6, как и в случае, представленном на фиг.1.

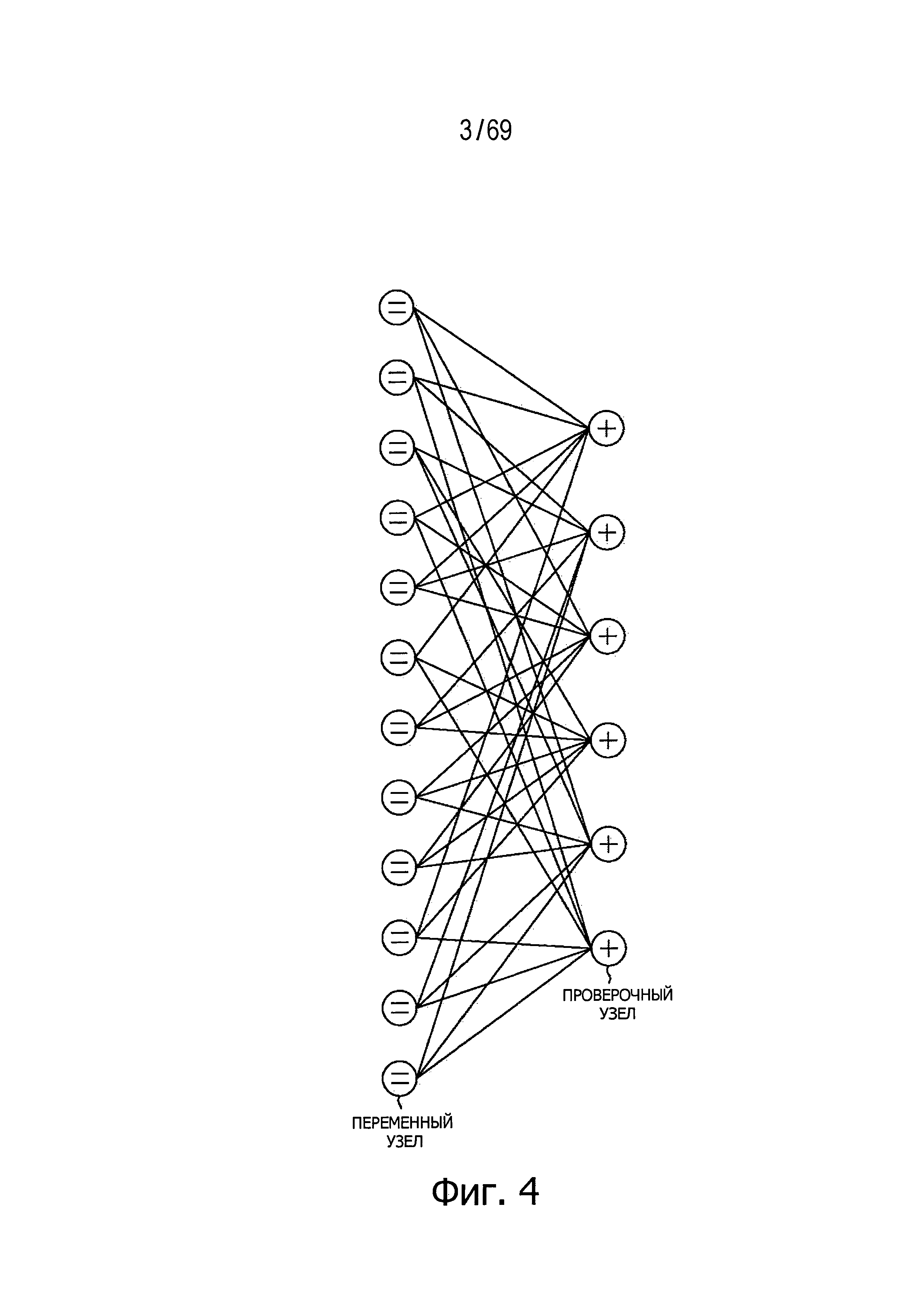

На фиг.4 показан граф Таннера матрицы Н проверки четности, показанной на фиг.3.

На фиг.4 каждый "+" представляет проверочный узел, и каждый "=" представляет переменный узел. Проверочные узлы и переменные узлы соответствуют строкам и столбцам, соответственно, матрицы Н проверки четности. Соединительные линии между проверочными узлами и переменными узлами представляют собой ребра, и они эквивалентны элементам "1" матрицы проверки четности.

В частности, когда элемент в j-ой строке и i-ом столбце в матрице проверки четности равен 1, переменный узел (представленный знаком "-"), то есть, i-ый сверху, и проверочный узел (представленный "+"), то есть, j-ый сверху, соединены ребром на фиг.4. Ребро указывает, что знаковый бит, соответствующий переменному узлу, имеет ограничение, соответствующее проверочному узлу.

В соответствии с алгоритмом "сумма-произведение", который представляет собой способ декодирования кодов LDPC, вычисление переменного узла и вычисление проверочного узла выполняют многократно.

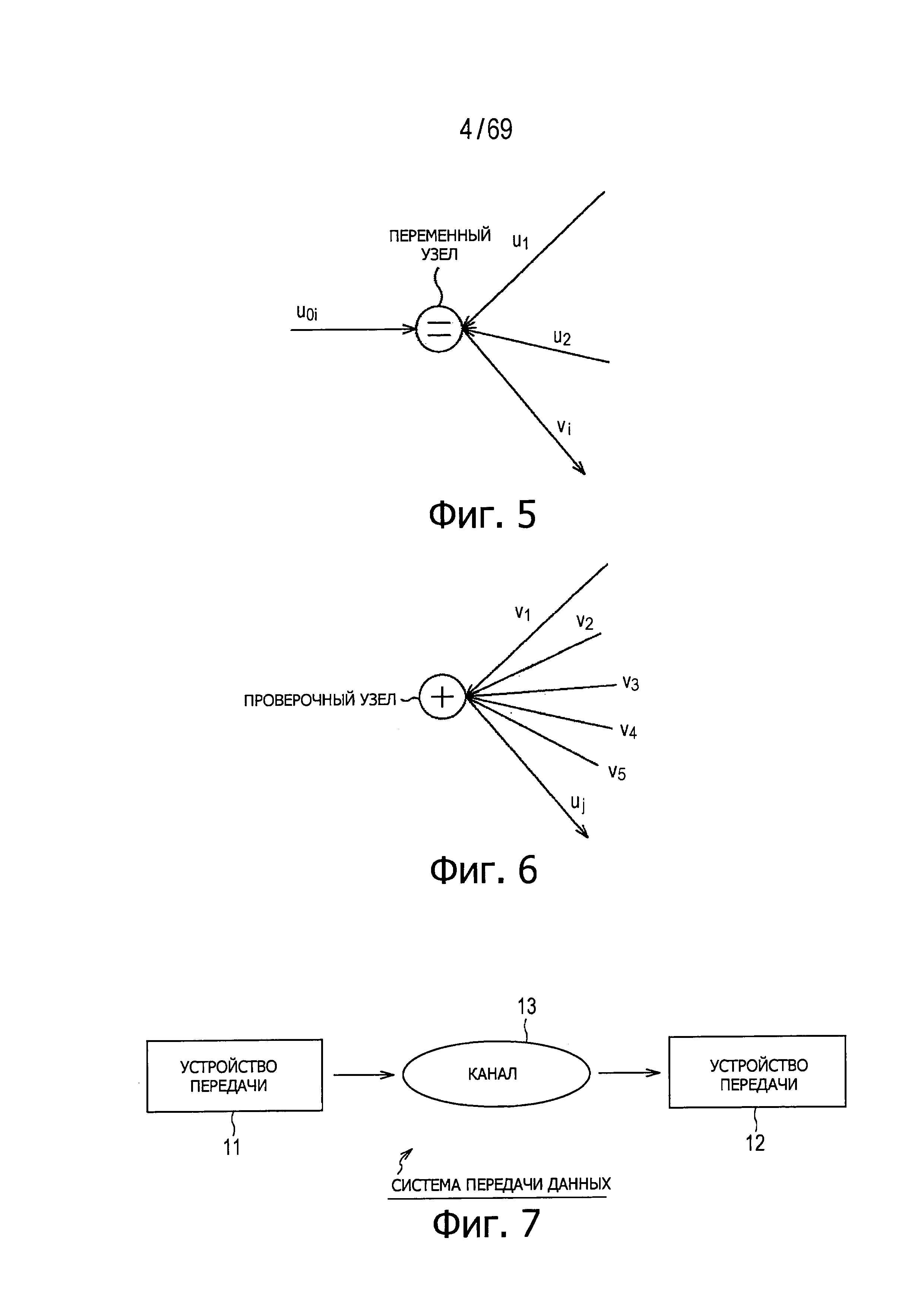

На фиг.5 показано вычисление переменного узла, который выполняют в переменном узле.

В переменном узле сообщение vi, соответствующее ребру, которое должно быть вычислено, может быть определено путем вычисления переменного узла, показанного в уравнении (1), используя сообщения u1 и u2 из остальных ребер, соединенных с переменным узлом, и принятое значение u0i. Сообщение, соответствующее любому из других ребер, может быть определено так же, как и представлено выше.

На фиг.6 показано вычисление проверочного узла, выполняемого в проверочном узле.

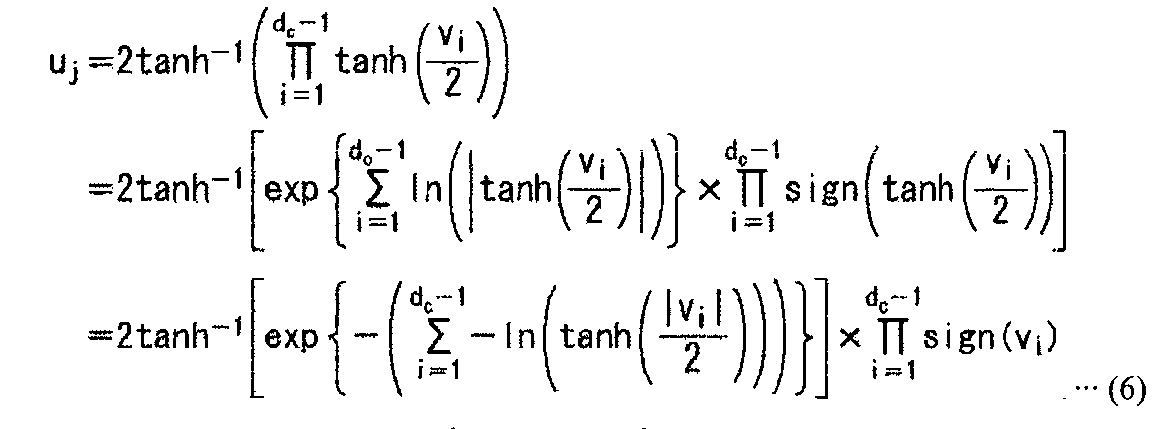

Вычисление проверочного узла, показанное в уравнении (2), также может быть выражено уравнением (6), используя взаимозависимость, выраженную уравнением a×b={ln(|a|)+ln(|b|)}×знак (а)×знак (b). Здесь, знак (x) равен 1, когда х≥0, и равен -1, когда х<0.

[Математическая формула 6]

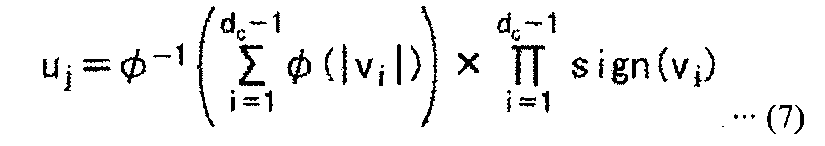

Когда х≥0, уравнение, φ-1(х)=2tanh-1(е-x), удовлетворяется, где функция φ(х) определена, как φ(х)=ln(tanh(х/2)). В соответствии с этим, уравнение (6) может быть преобразовано в уравнение (7).

[Математическая формула 7]

В проверочном узле вычисление проверочного узла, показанного в уравнении (2), выполняют в соответствии с уравнением (7).

В частности, в проверочном узле, сообщение uj, соответствующее ребру, которое должно быть вычислено, может быть определено путем вычисления проверочного узла, показанного в уравнении (7), используя сообщения v1, v2, v3, v4 и v5 от других ребер, соединенных с проверочным узлом, как показано на фиг.6. Сообщение, соответствующее любому из других ребер, может быть определено так же, как описано выше.

Следует отметить, что функция φ(х) в уравнении (7) может быть выражена уравнением φ(х)=ln((ex+1)/(ех-1)), и φ(х)=φ-1(х) удовлетворяется, когда х>0. Когда функцию φ(х) и φ-1(х) воплощают в аппаратных средствах, можно использовать LUT (справочные таблицы), но обе таблицы представляют собой идентичные LUT.

Список литературы

Непатентный документ

НЕПАТЕНТНЫЙ ДОКУМЕНТ 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Задачи, решаемые изобретением

Коды LDPC используются в DVB-S.2, которые представляют собой стандарты для цифровой спутниковой широковещательной передачи, и в DVB-T.2, которые представляют собой стандарты для цифровой наземной широковещательной передачи. Коды LDPC также планируются использовать в DVB-C.2, которые представляют собой стандарты для следующего поколения цифровой широковещательной передачи CATV (кабельного телевидения).

При цифровой широковещательной передаче, в соответствии со стандартами DVB, такими как DVB-S.2, код LDPC преобразуют (символизируют) в символы ортогональной модуляции (цифровая модуляция), такой как QPSK (квадратурная манипуляция со сдвигом фазы) и передают символы, отображенные на точки сигнала.

При выражении символами кода LDPC знаковые биты кода LDPC переставляют по два или больше знаковых бита одновременно, и переставленные знаковые биты используются в качестве символьных битов.

Существуют различные виды способов, предполагаемых, в качестве способов перестановки знаковых битов, для выражения кодов LDPC в виде символов, и некоторые из них, например, установлены в DVB-T.2.

В то же время, DVB-T.2 представляют собой стандарты для цифровой широковещательной передачи, предназначенной для фиксированных оконечных устройств, таких как телевизионные приемники, установленные в домах, и могут быть не пригодны для цифровой широковещательной передачи, предназначенной для портативных оконечных устройств.

В частности, портативные оконечные устройства должны иметь меньшие размеры схемы, чем стационарные оконечные устройства, и должны быть разработаны для потребления меньшей энергии. Поэтому, для уменьшения нагрузки, требуемой при выполнении операций, таких как декодирование кодов LDPC в каждом портативном оконечном устройстве при цифровой широковещательной передаче для портативных оконечных устройств, количество повторений при декодировании (количество С повторений при декодировании) каждого кода LDPC, длина кода каждого кода LDPC и т.п. могут быть ограничены меньшими значениями, чем в случае цифровой широковещательной передачи для стационарных оконечных устройств.

При таких ограничениях, все еще требуется поддерживать определенный уровень устойчивости к ошибкам.

Настоящая технология была разработана с учетом таких обстоятельств, и предназначена для обеспечения для данных, таких как коды LDPC, более высокой устойчивости к ошибкам.

Решение задач

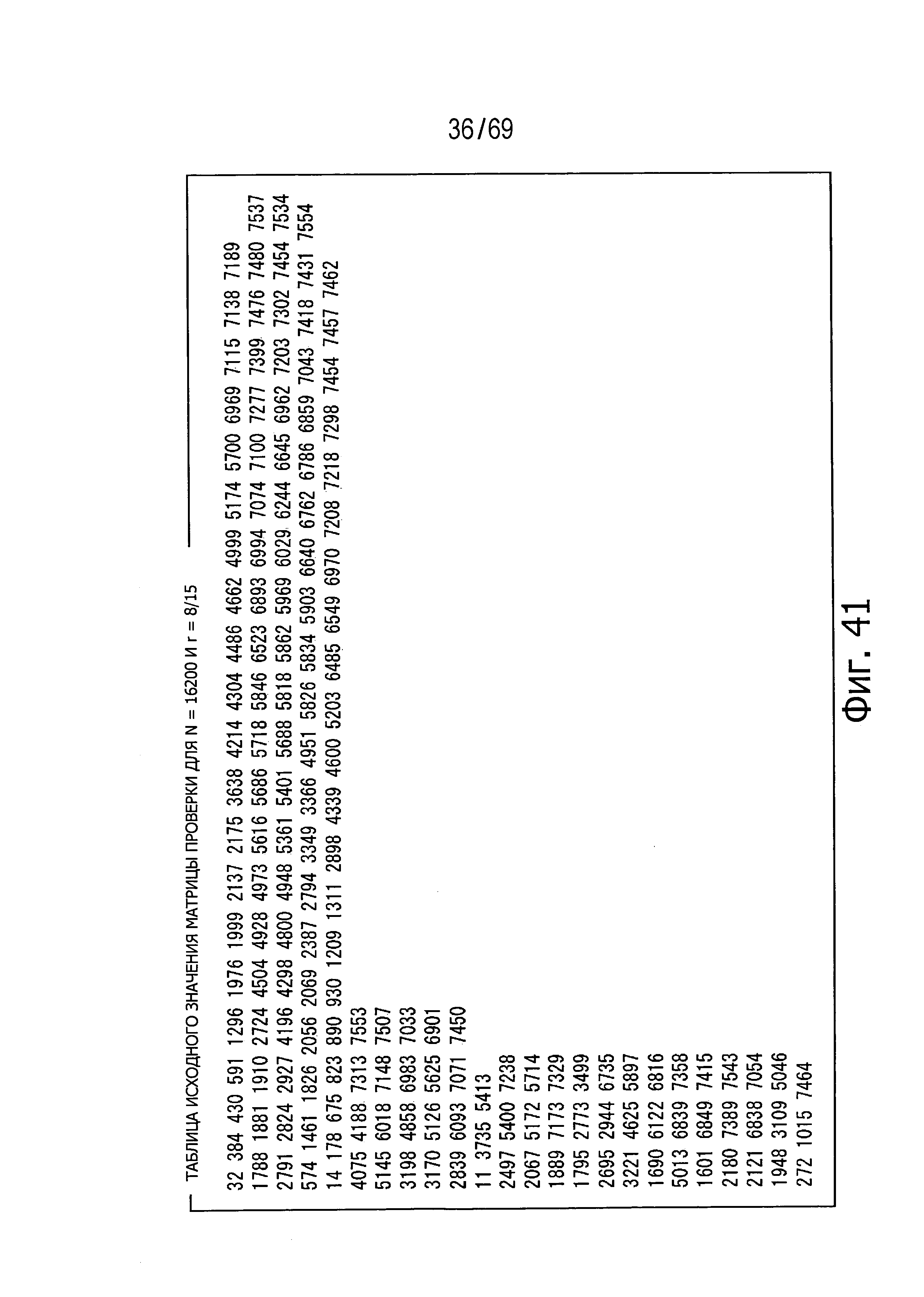

Устройство/способ обработки данных, в соответствии с первым аспектом настоящей технологии, включает в себя: модуль/этап кодирования для кодирования LDPC для генерирования кода LDPC, имеющего длину кода 16200 битов, и скорость кода 8/15, на основе матрицы проверки четности для кодов LDPC; и модуль/этап перестановки для смены мест знаковых битов кода LDPC, кодированного в модуле/на этапе кодирования с символьными битами для символа, соответствующего одной из 256 точек сигнала, определенных по 256QAM. Код LDPC, кодированный в модуле/на этапе кодирования, включает в себя информационные биты и биты проверки четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок матрицы проверки четности, соответствующий битам проверки четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

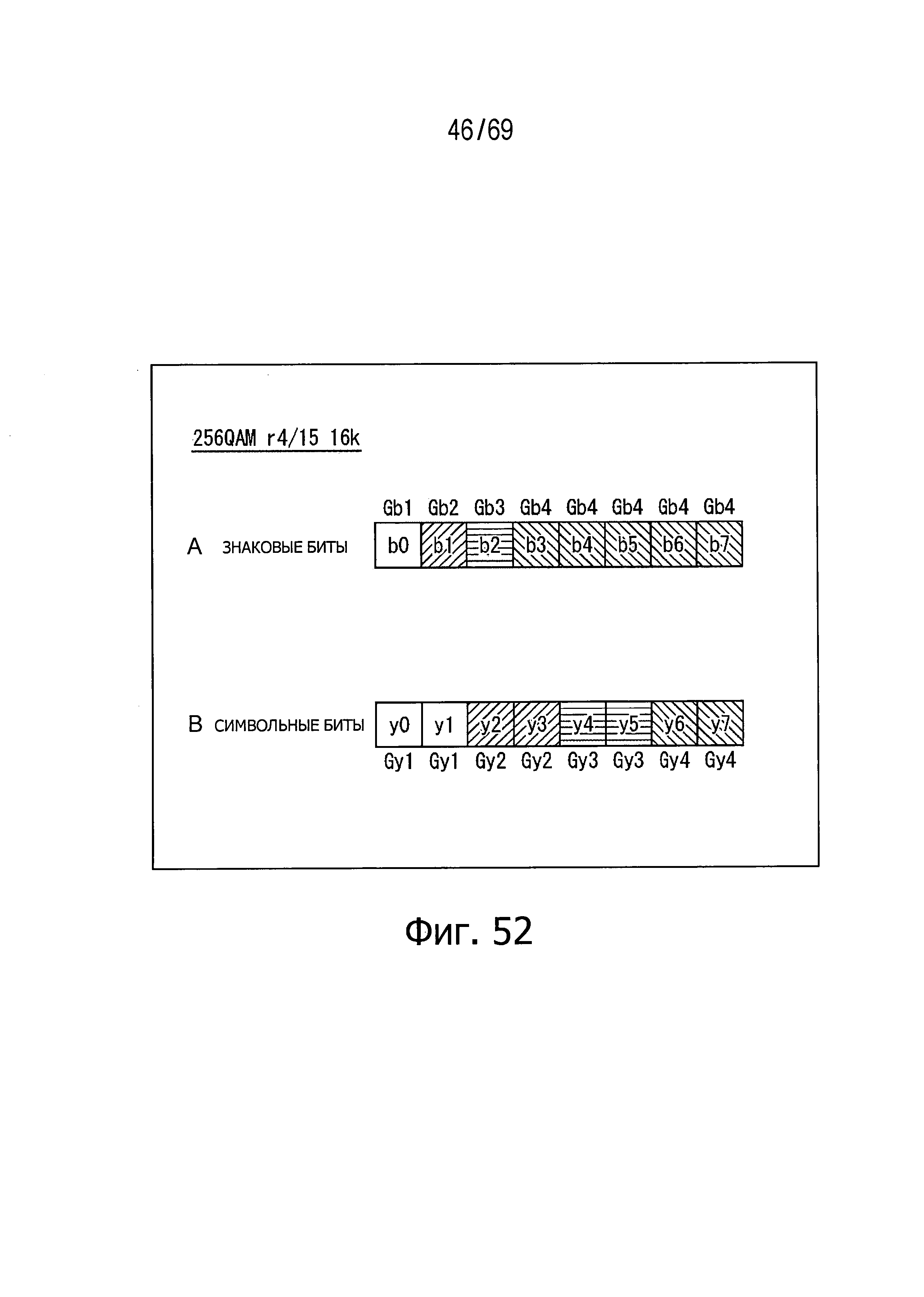

В модуле/на этапе перестановки заменяют бит b0 битом y2, бит b1 битом y6, бит b2 битом y1, бит b3 битом y0, бит b4 битом y7, бит b5 битом y5, бит b6 битом y3 и бит b7 битом y4, где восьми знаковым битам, которые содержатся в восьми модулях хранения, каждый из которых имеет емкость 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому назначают один символ, при этом (#i+1)-ый бит, считая от самого верхнего бита из восьми знаковых битов, выражается, как бит b#i, и (#i+1)-ый бит, содержащийся в самом верхнем бите из восьми символьных битов одного символа, выражен как бит y#i.

В описанном выше первом аспекте кодирование LDPC для генерирования кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15, выполняют на основе матрицы проверки четности для кодов LDPC, и знаковые биты кода LDPC заменяют символьными битами символа, соответствующего одной из 256 точек сигнала, определенных 256QAM. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" информационного участка матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

В случае, когда восемь знаковых битов, которые сохранены в восьми модулях хранения, каждый из которых имеет емкость хранения 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому назначают один символ, (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми знаковых битов, выражается в качестве бита b#i, и (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми символьных битов для одного символа, выражается в качестве бита y#i, причем бит b0 заменяют битом y2, бит b1 заменяют битом y6, бит b2 заменяют битом y1, бит b3 заменяют битом y0, бит b4 заменяют битом y7, бит b5 заменяют битом y5, бит b6 заменяют битом y3 и бит b7 заменяют битом y4.

Устройство/способ обработки данных, в соответствии со вторым аспектом настоящей технологии, включает в себя: модуль/этап обратной перестановки для замены символьных битов символа, соответствующего одной из 256 точек сигнала, определенных 256QAM, знаковыми битами кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15; и модуль/этап декодирования для декодирования кода LDPC на основе матрицы проверки четности для кодов LDPC после перестановки кода LDPC модулем/этапом обратной перестановки. Модуль/этап обратной перестановки заменяет бит y2 битом b0, бит y6 битом b1, бит y1 битом b2, бит y0 битом b3, бит y7 битом b4, бит y5 битом b5, бит y3 битом b6 и бит y4 битом b7, где восемь знаковых битов содержатся в восьми модулях хранения, каждый из которых имеет емкость хранения 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому из которых назначен один символ, (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми знаковых битов, выражен в качестве бита b#i, и (#i+1)-ый бит, отсчитанный от верхнего бита из восьми символьных битов одного символа, выражен в качестве бита y#i. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

В описанном выше втором аспекте символьные биты символа, соответствующего одной из 256 точек сигнала, определенных 256QAM, заменяют знаковыми битами кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15, и переставленный код LDPC декодируют на основе матрицы проверки четности для кодов LDPC. Модуль/этап обратной перестановки заменяет бит y2 битом b0, бит y6 битом b1, бит y1 битом b2, бит y0 битом b3, бит y7 битом b4, бит y5 битом b5, бит y3 битом b6 и бит y4 битом b7, где восемь знаковых битов содержатся в восьми модулях хранения, каждый из которых имеет емкость 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому из которых назначен один символ, (#i+1)-й бит, отсчитанный от верхнего бита из этих восьми знаковых битов, выражен в качестве бита b#i, и (#i+1)th бит, отсчитанный от верхнего бита из восьми символьных битов одного символа, выражен в качестве бита y#i. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы с промежутками в 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

Устройство обработки данных может представлять собой независимое устройство, или может представлять собой внутренний блок в отдельном устройстве.

Эффекты изобретения

В соответствии с настоящей технологией, может быть повышена устойчивость к ошибкам.

Краткое описание чертежей

На фиг.1 показана схема для пояснения матрицы Н проверки четности кода LDPC.

На фиг.2 блок-схема последовательности операций для пояснения процедуры декодирования кода LDPC.

На фиг.3 показана схема, представляющая пример матрицы проверки четности кода LDPC.

На фиг.4 показана схема, представляющая граф Таннера матрицы проверки четности.

На фиг.5 показана схема, представляющая переменный узел.

На фиг.6 показана схема, представляющая проверочный узел.

На фиг.7 показана схема, представляющая пример структуры варианта осуществления системы передачи, к которой применена настоящая технология.

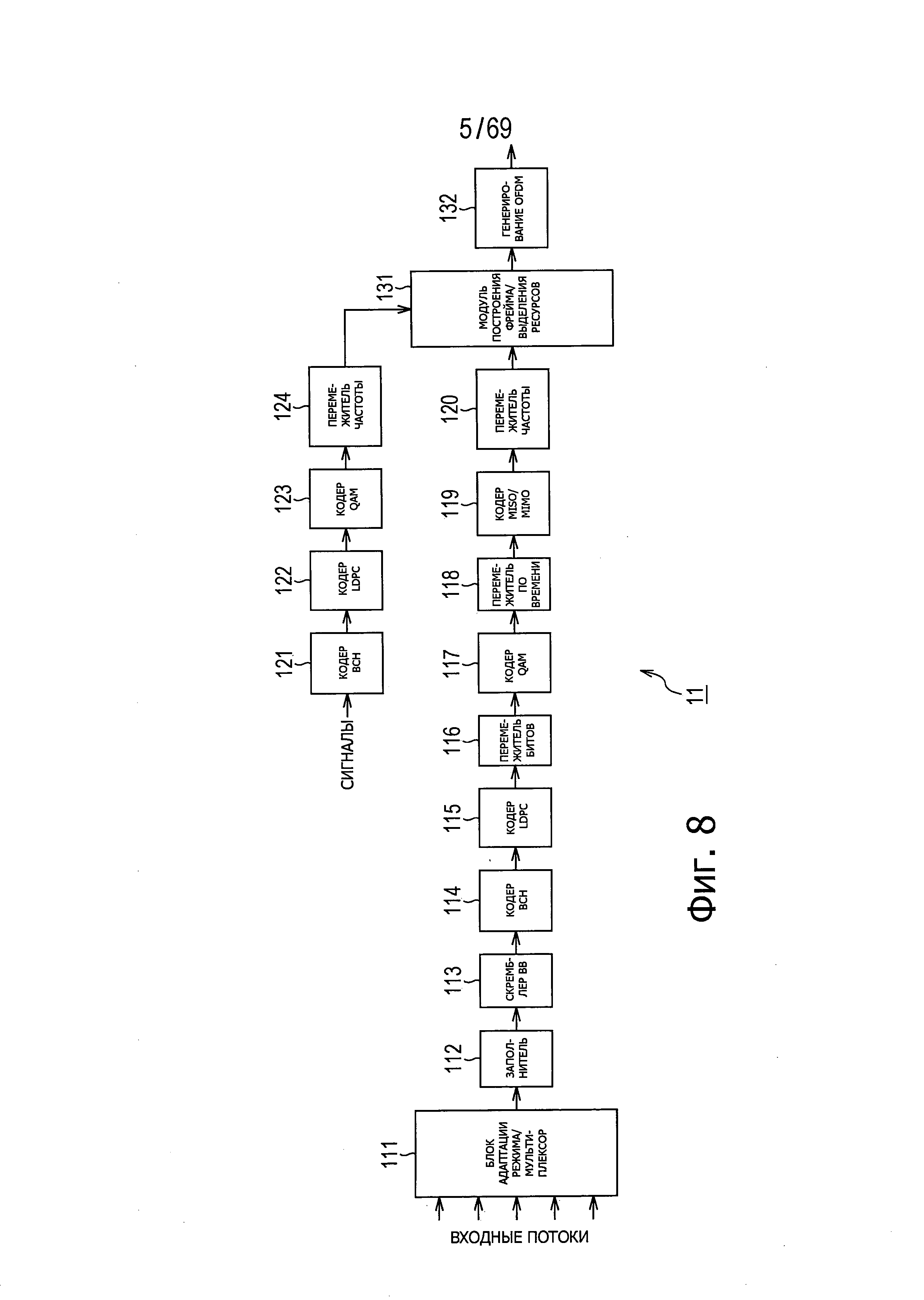

На фиг.8 показана блок-схема, представляющая пример структуры устройства 11 передачи.

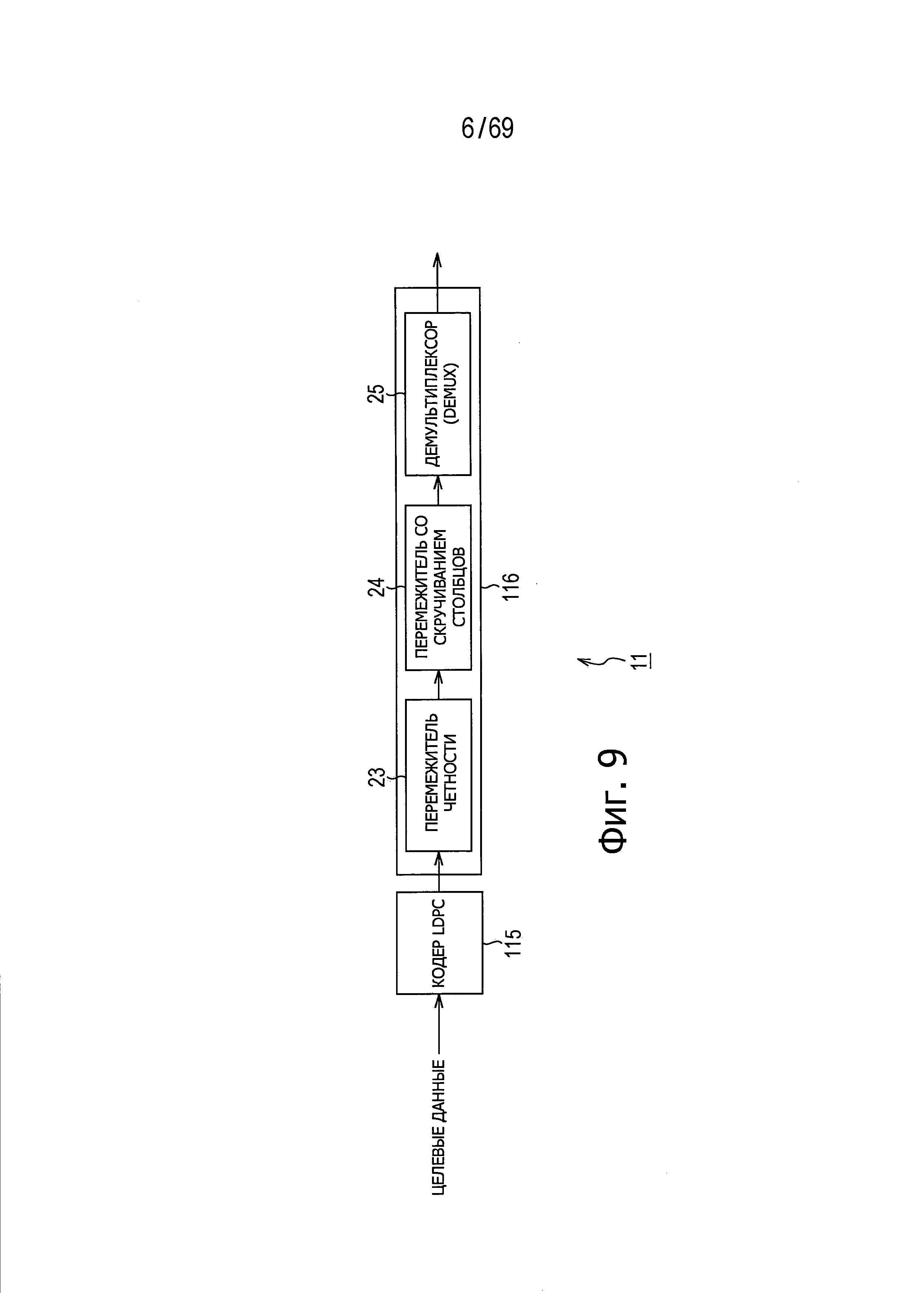

На фиг.9 показана блок-схема, представляющая пример структуры перемежителя 116 битов.

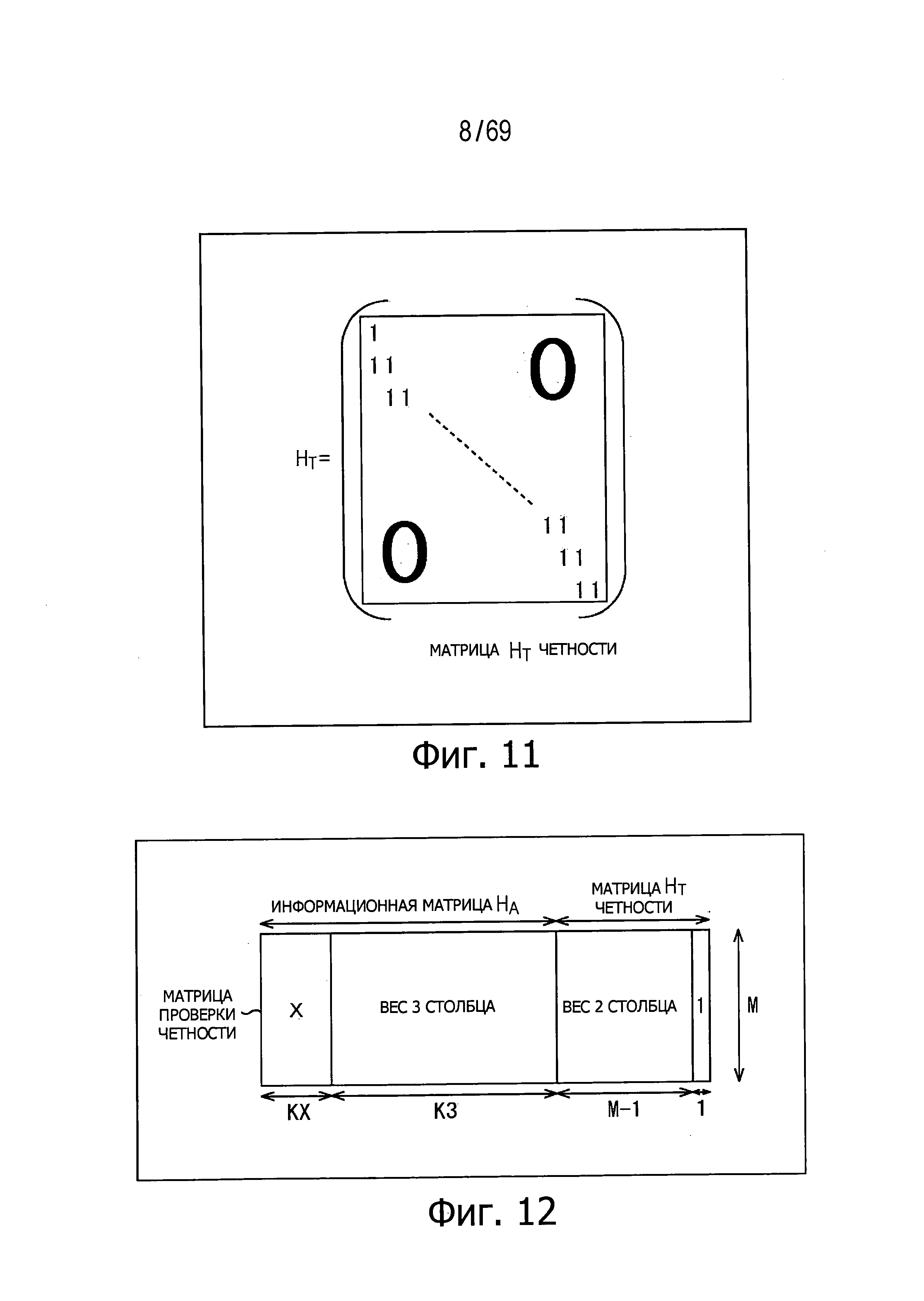

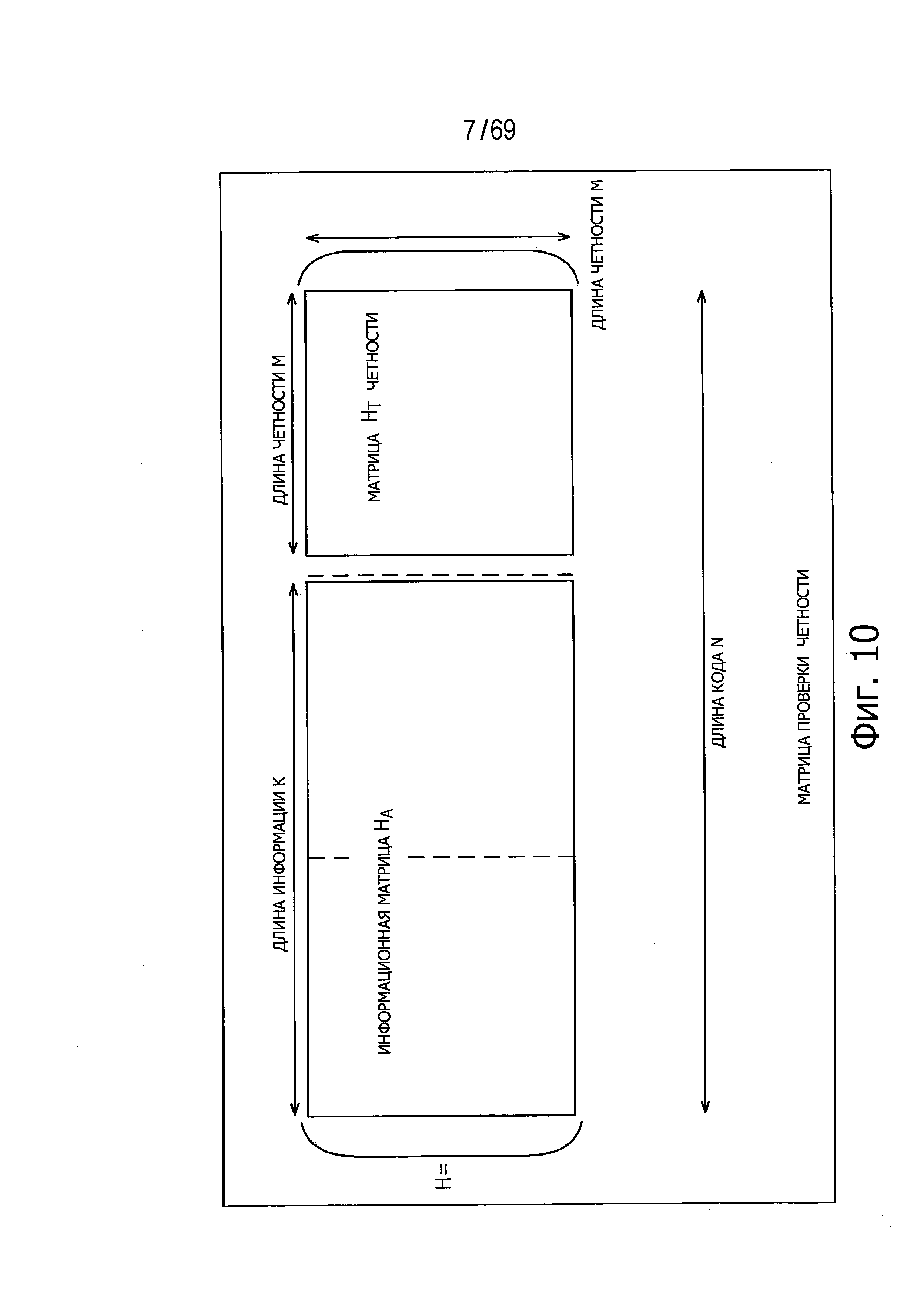

На фиг.10 показана схема, представляющая матрицу проверки четности.

На фиг.11 показана схема, представляющая матрицу четности.

На фиг.12 показана схема для пояснения матрицы проверки четности кода LDPC, определенного в стандартах DVB-S.2.

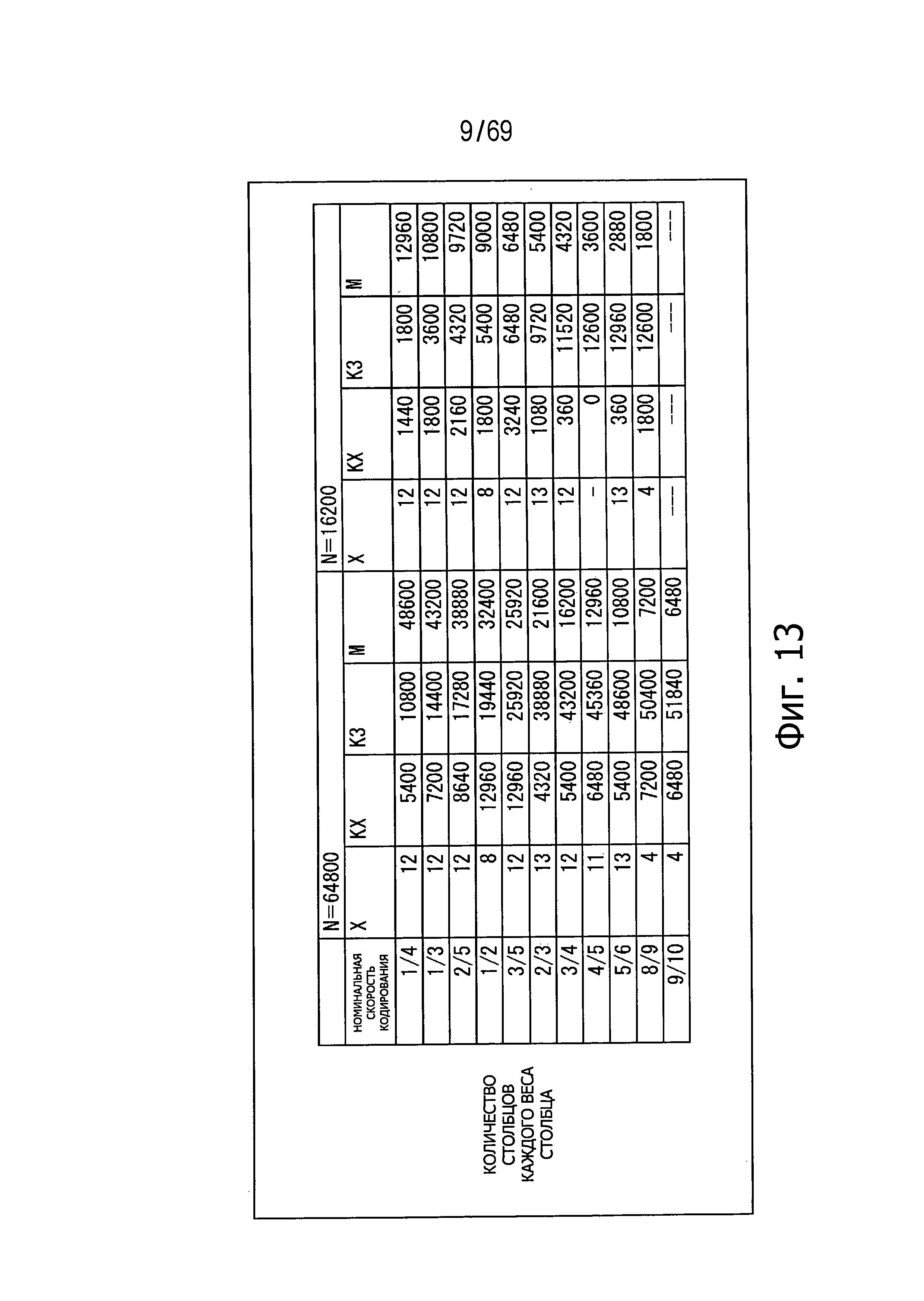

На фиг.13 показана схема для пояснения матрицы проверки четности кода LDPC, определенного в стандартах DVB-S.2.

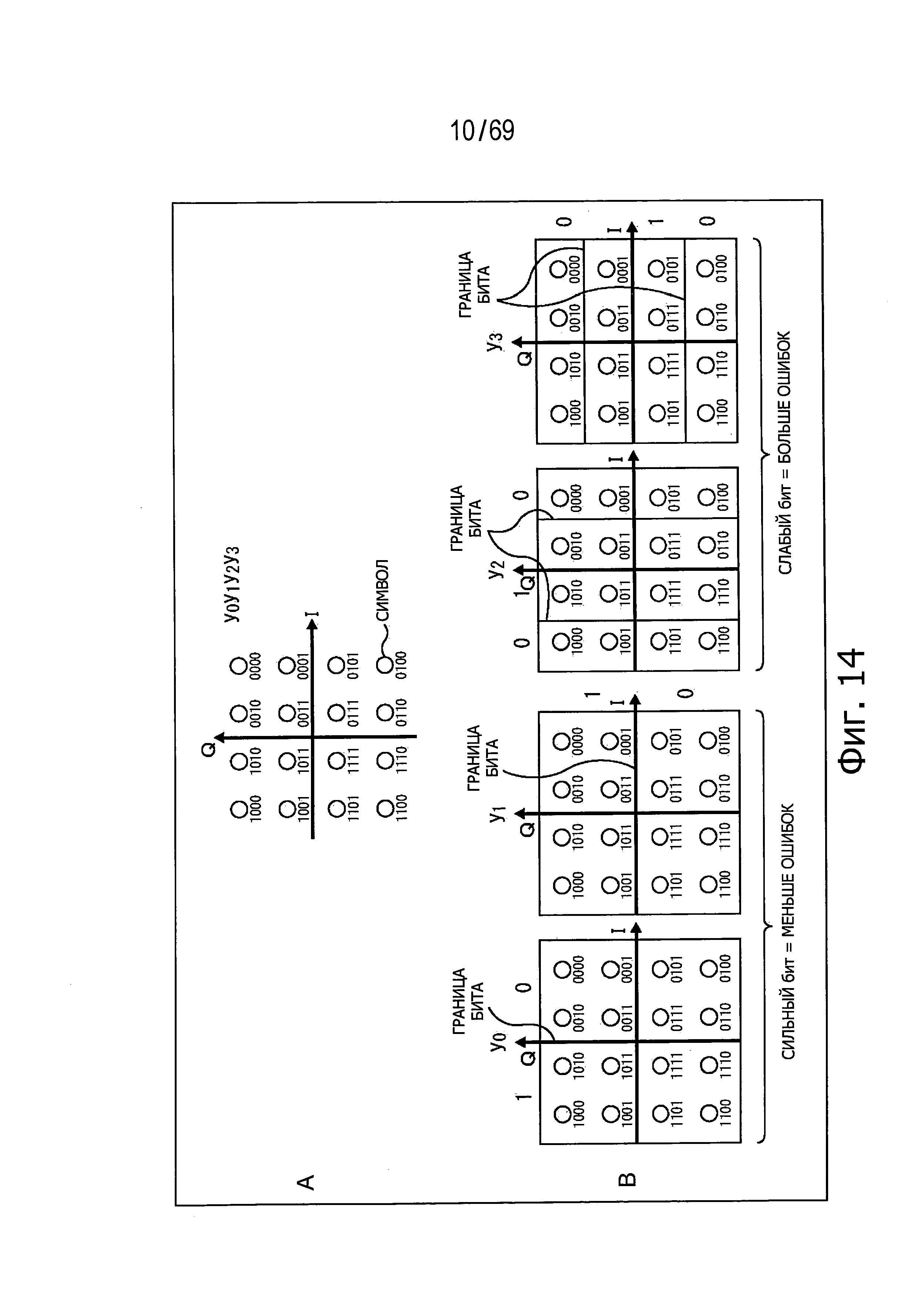

На фиг.14 показана схема, представляющая компоновку точки сигнала 16QAM.

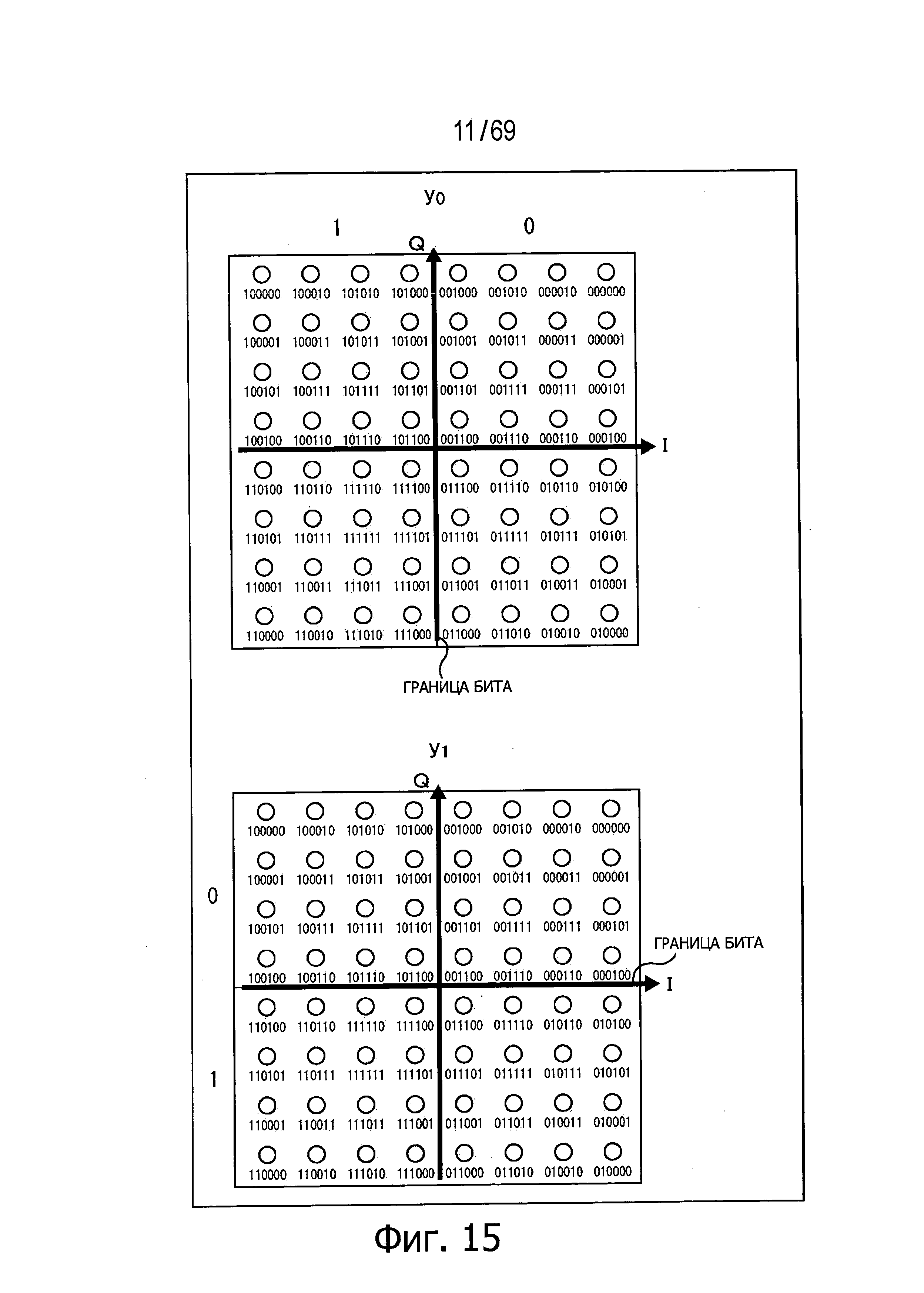

На фиг.15 показана схема, представляющая компоновку точки сигнала 64QAM.

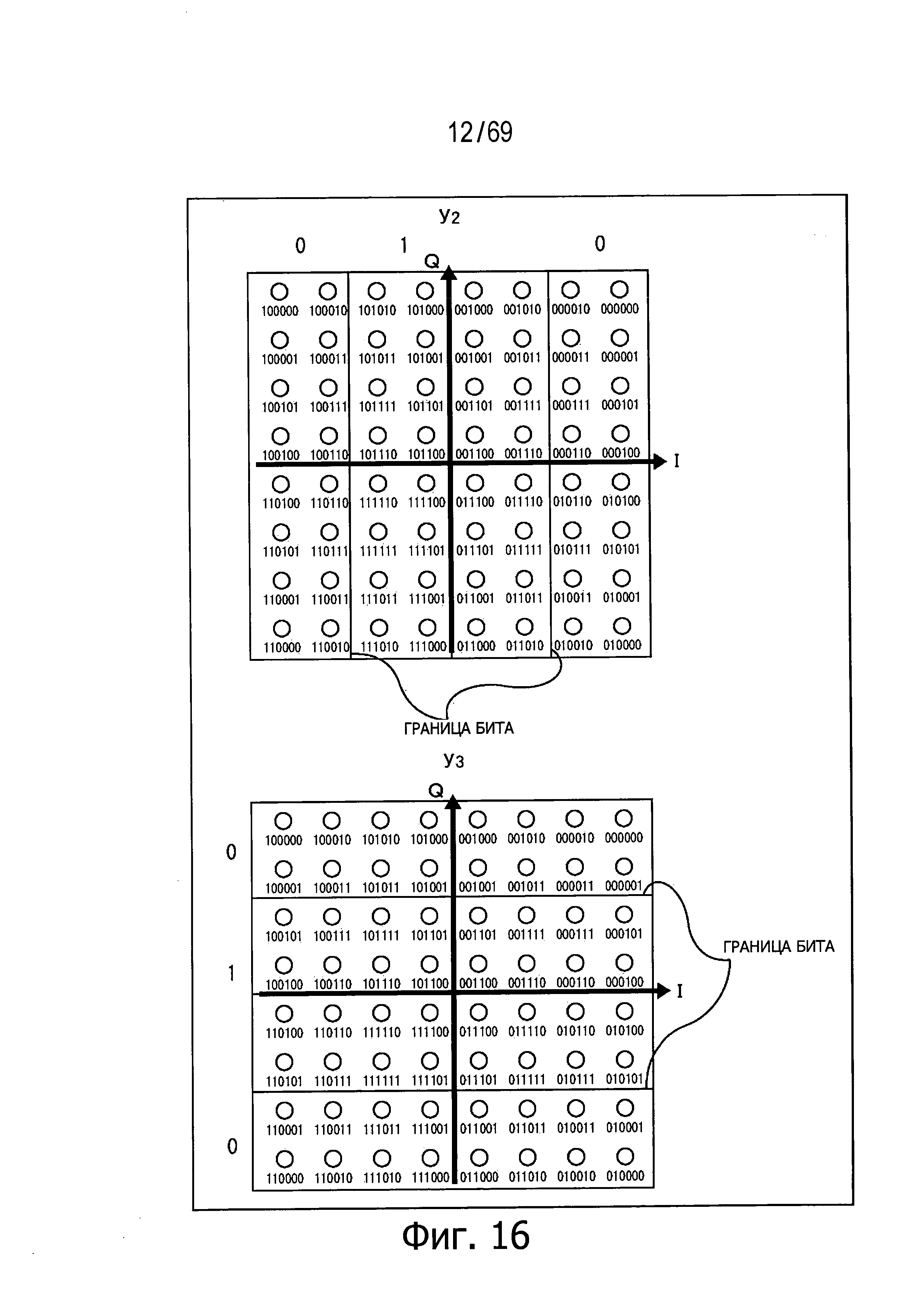

На фиг.16 показана схема, представляющая компоновку точки сигнала 64QAM.

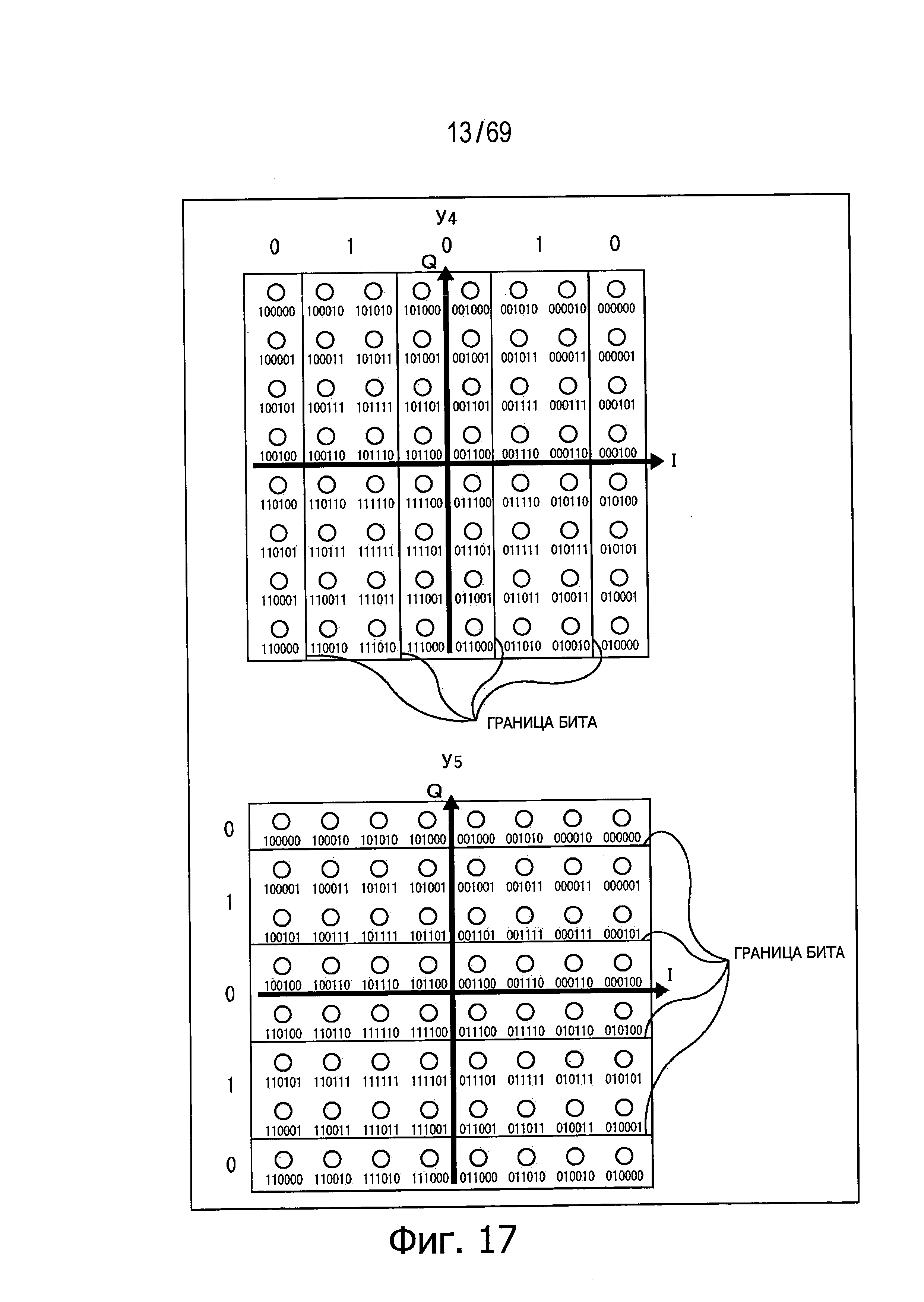

На фиг.17 показана схема, представляющая компоновку точки сигнала 64QAM.

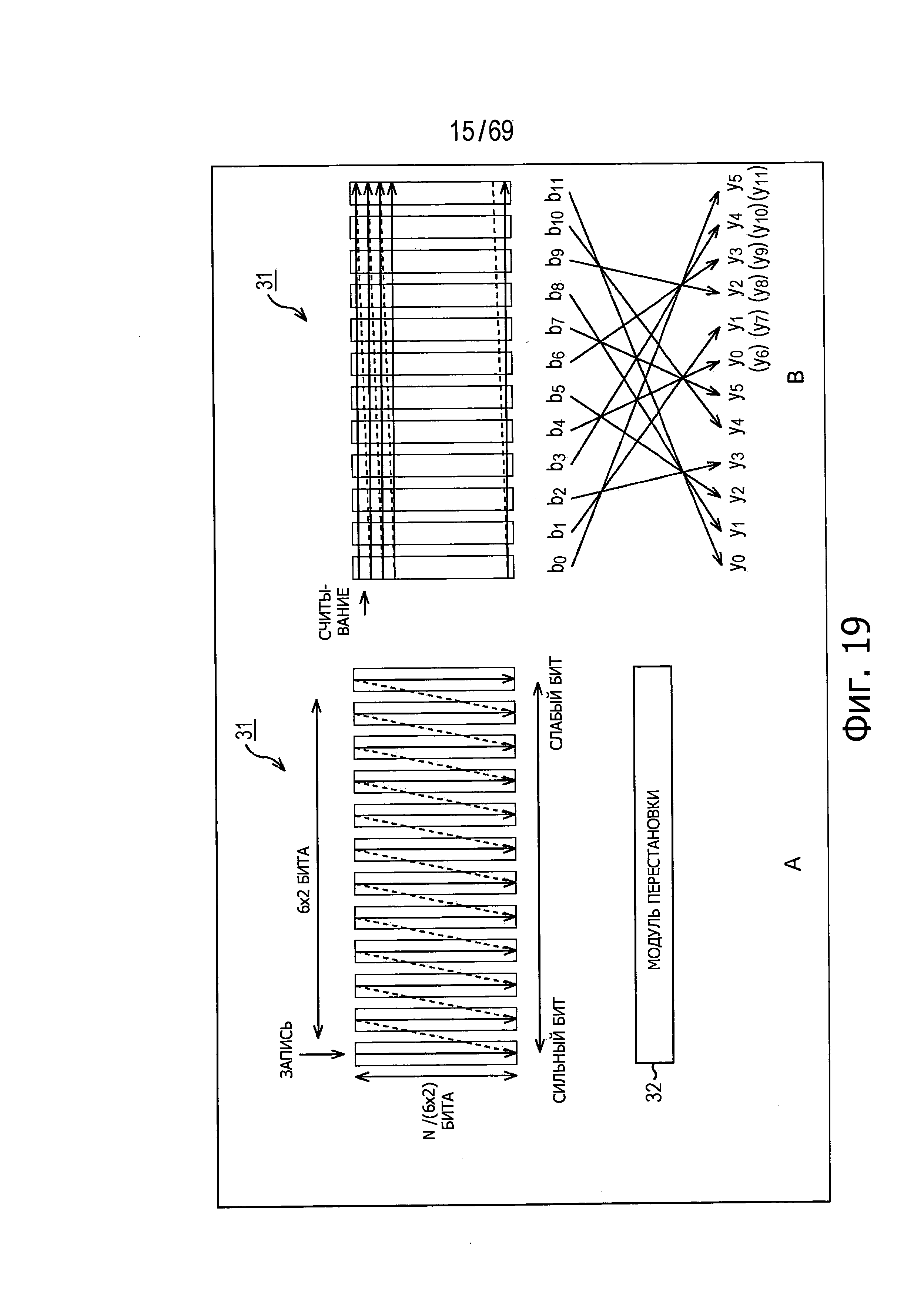

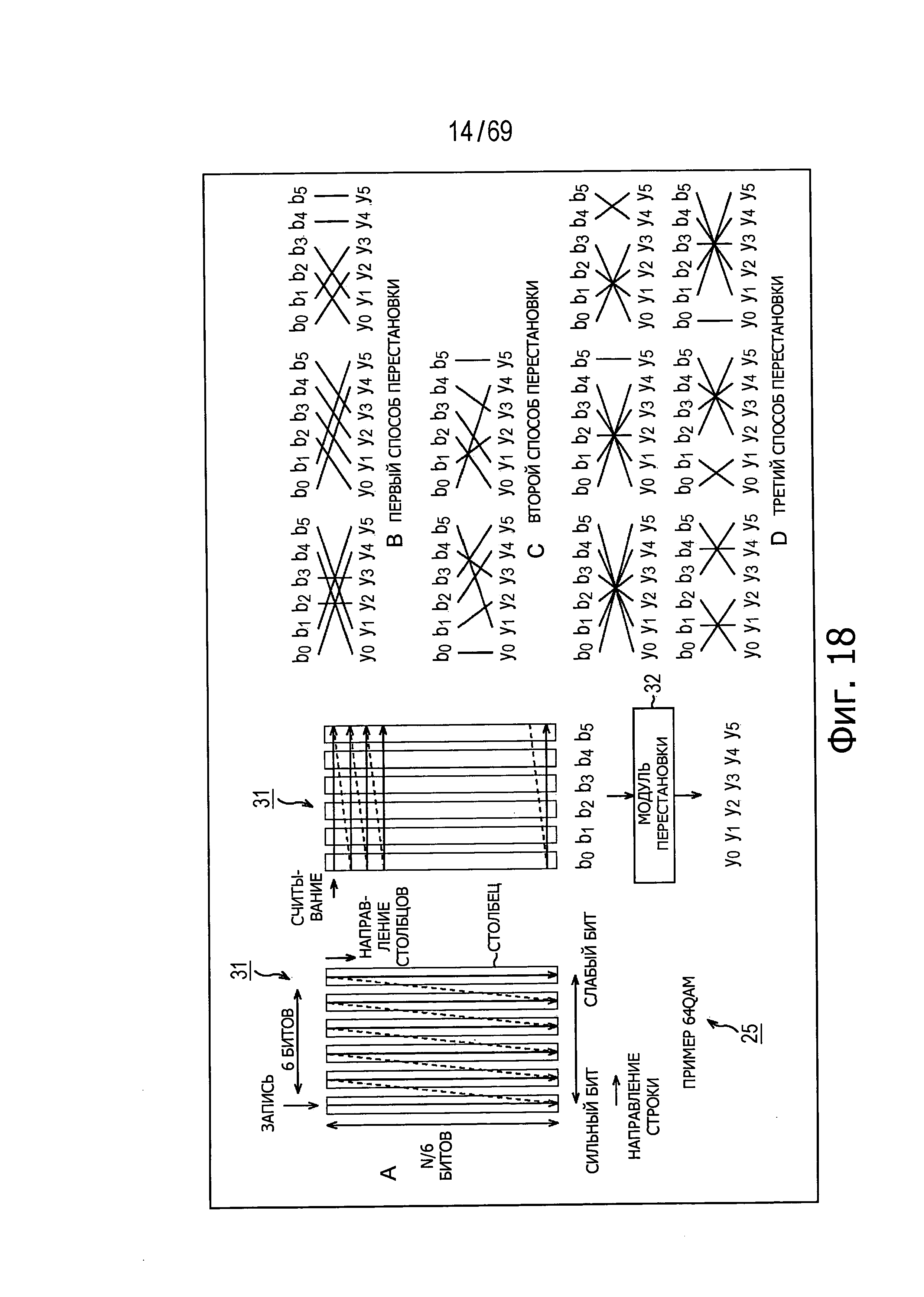

На фиг.18 показана схема для пояснения операции демультиплексора 25.

На фиг.19 показана схема для пояснения операции демультиплексора 25.

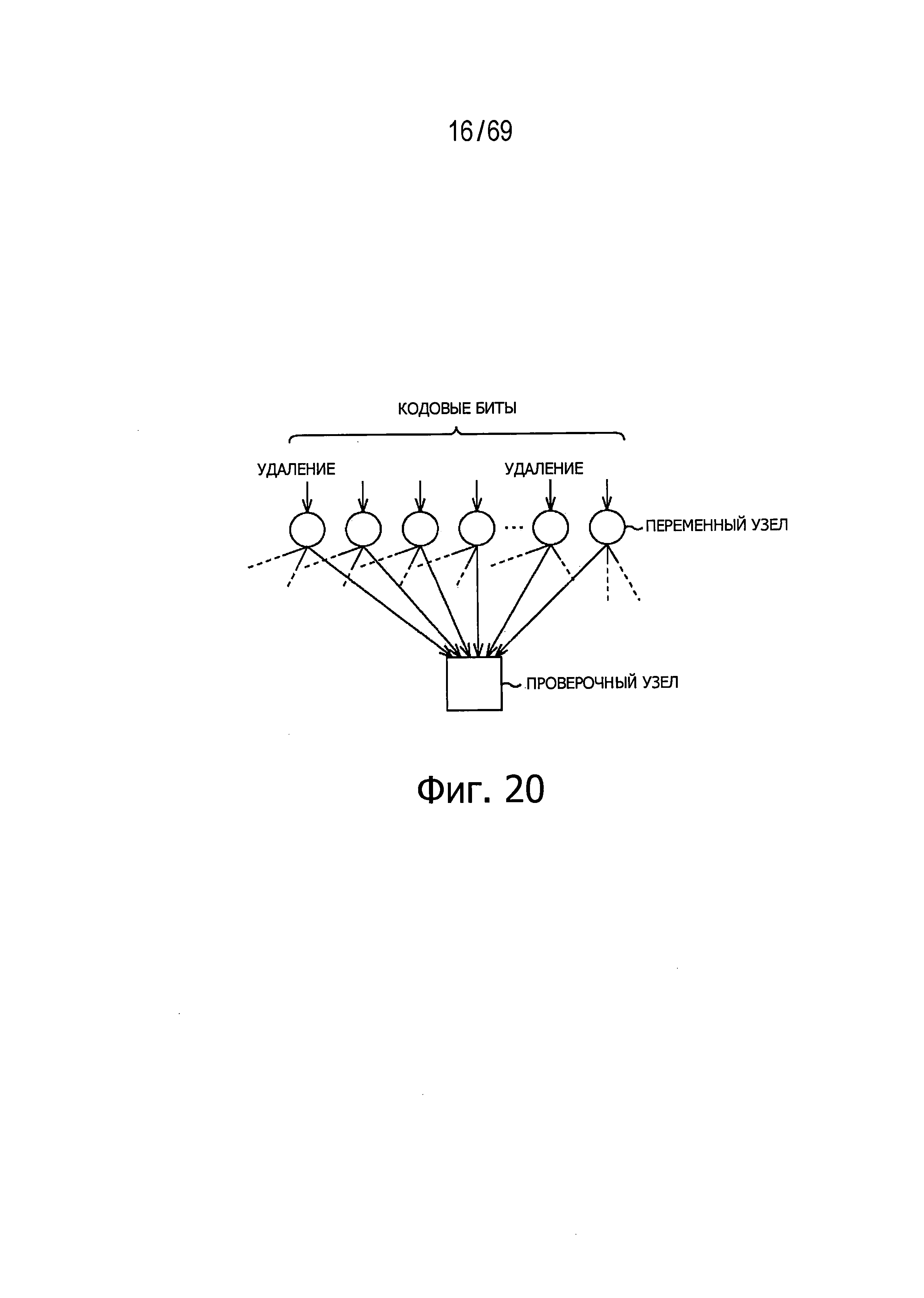

На фиг.20 показана схема, представляющая граф Таннера для декодировании кода LDPC.

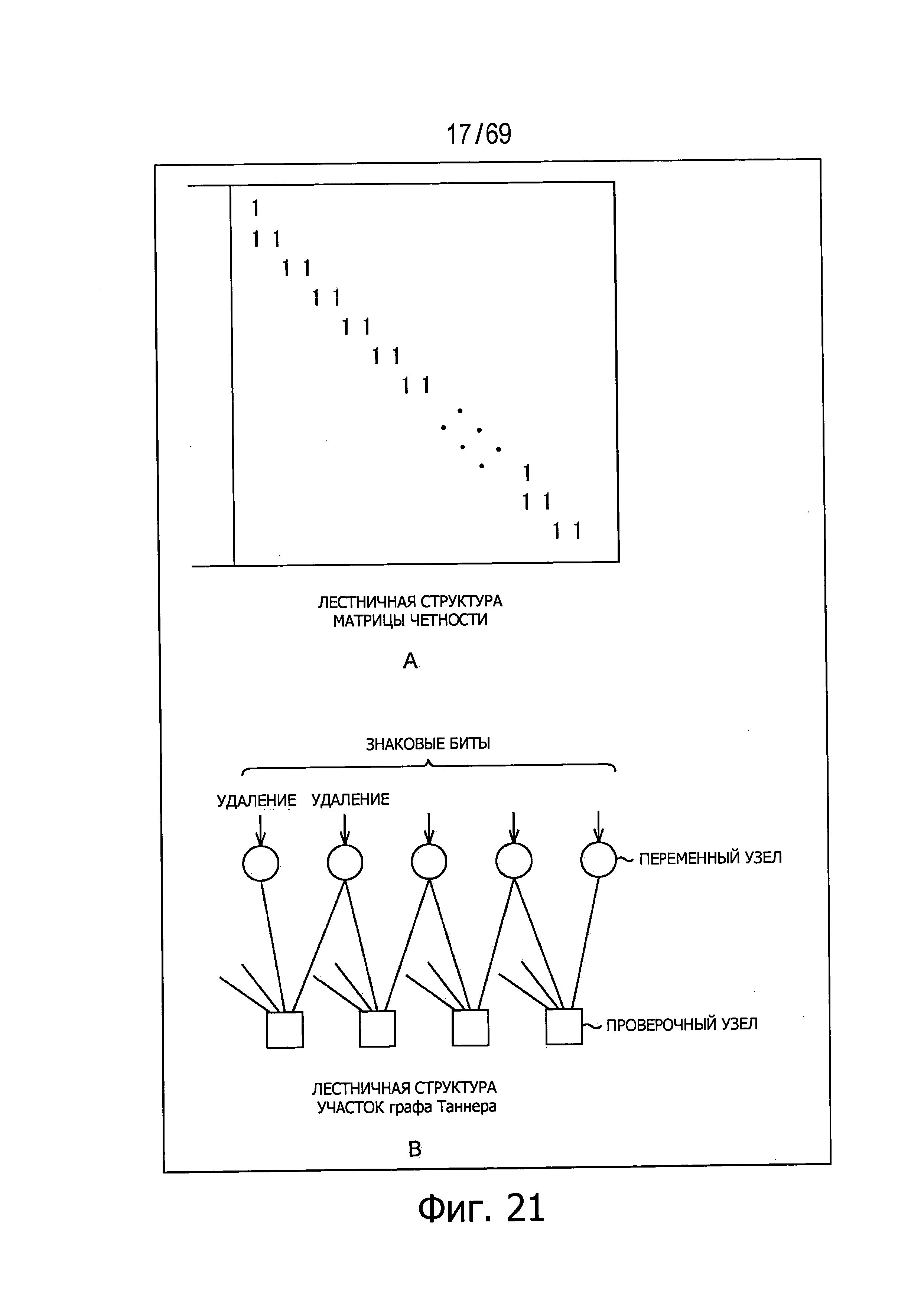

На фиг.21 показана схема, представляющая матрицу HT четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT четности.

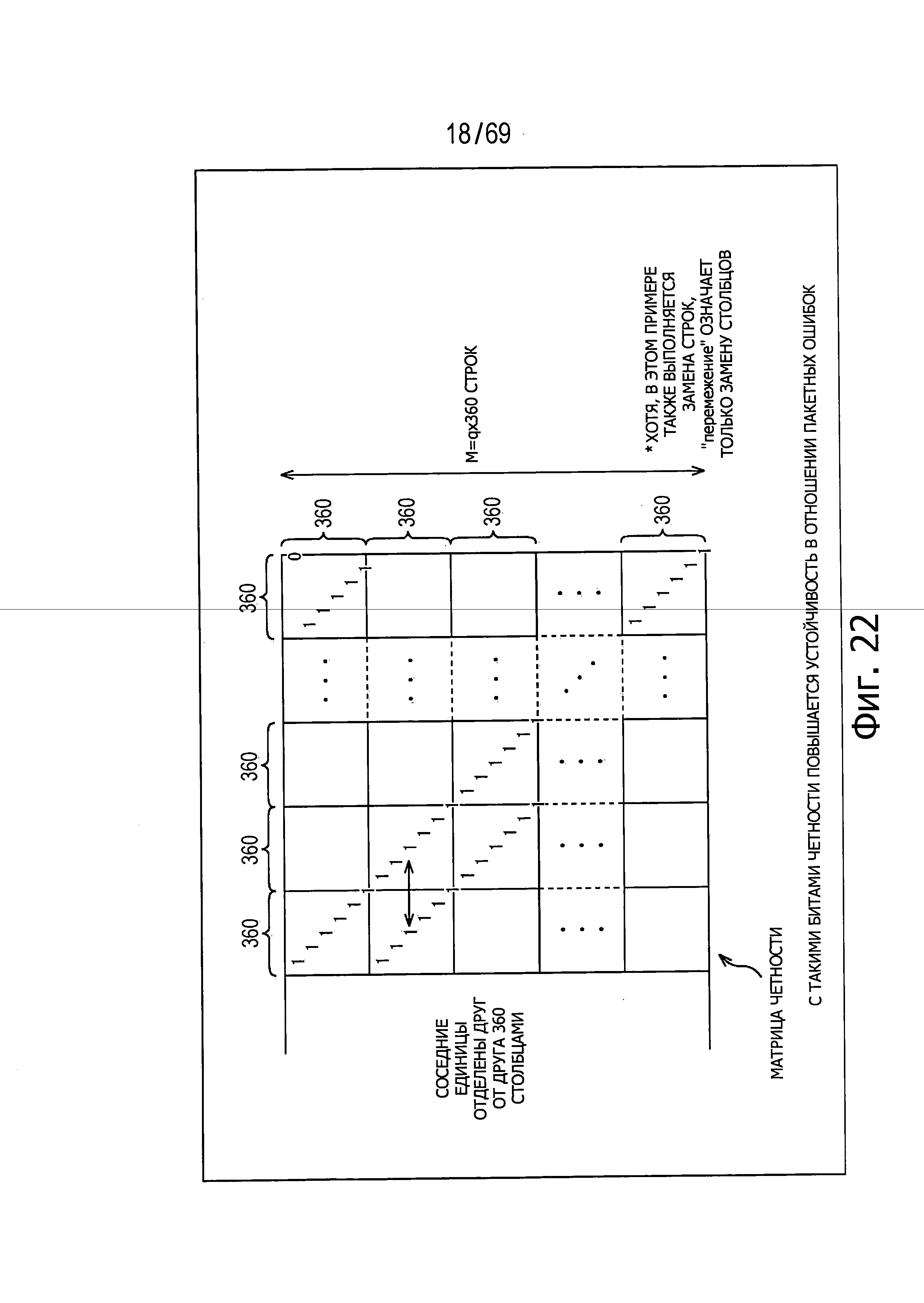

На фиг.22 показана схема, представляющая матрицу HT четности матрицы Н проверки четности, соответствующую коду LDPC, подвергнутому перемежению четности.

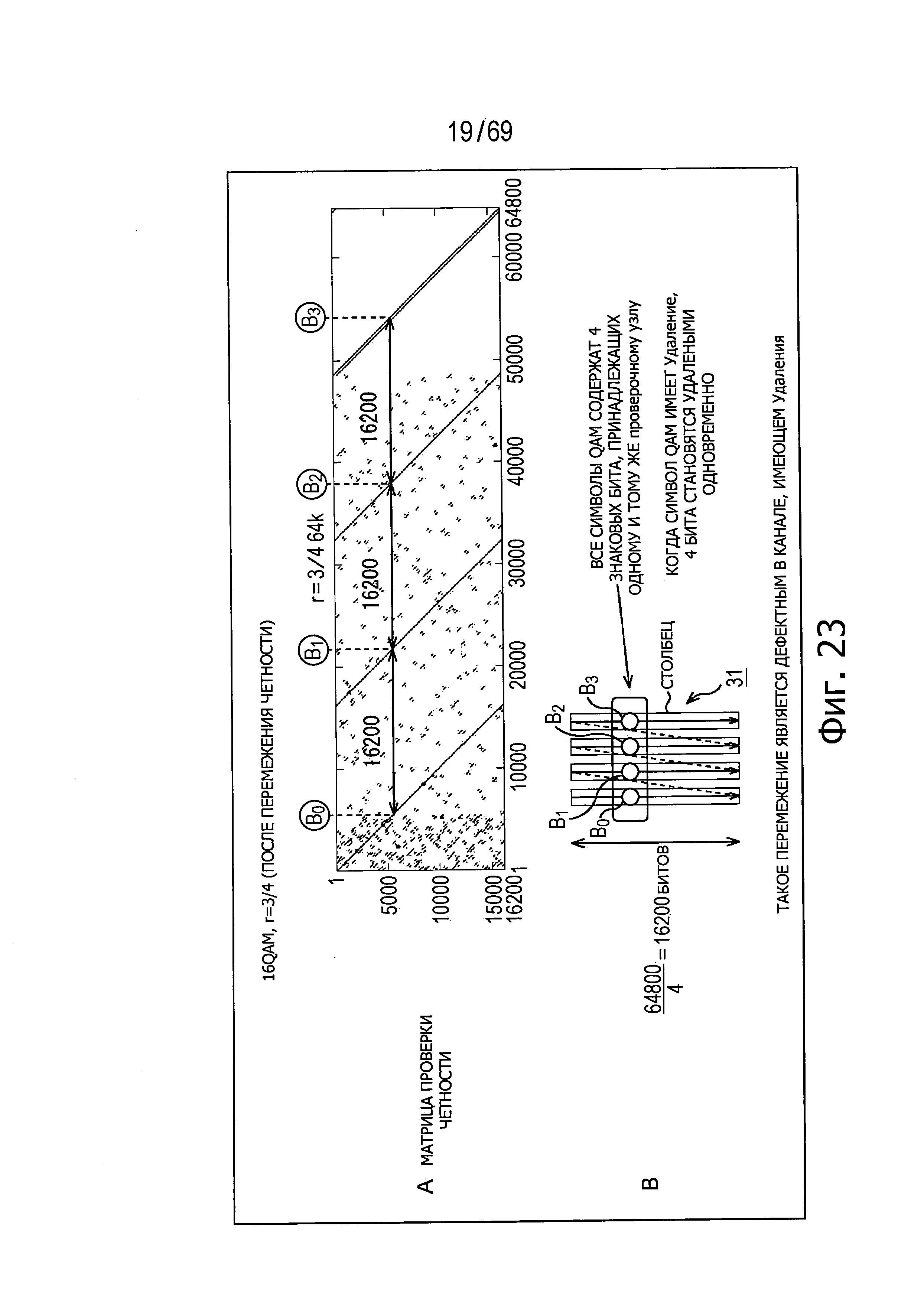

На фиг.23 показана схема, представляющая преобразованную матрицу проверки четности.

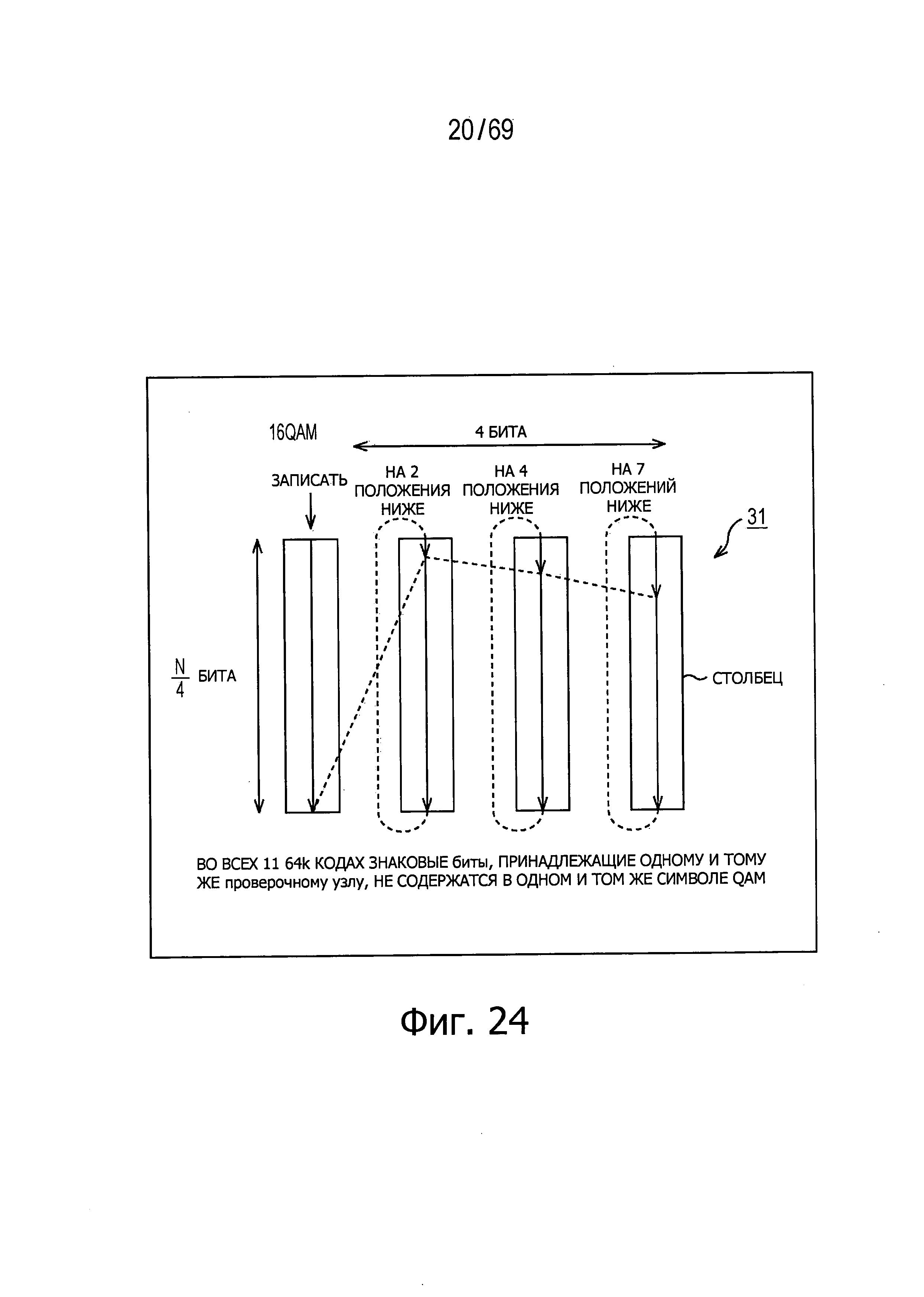

На фиг.24 показана схема для пояснения операция перемежителя 24 со скручиванием столбцов.

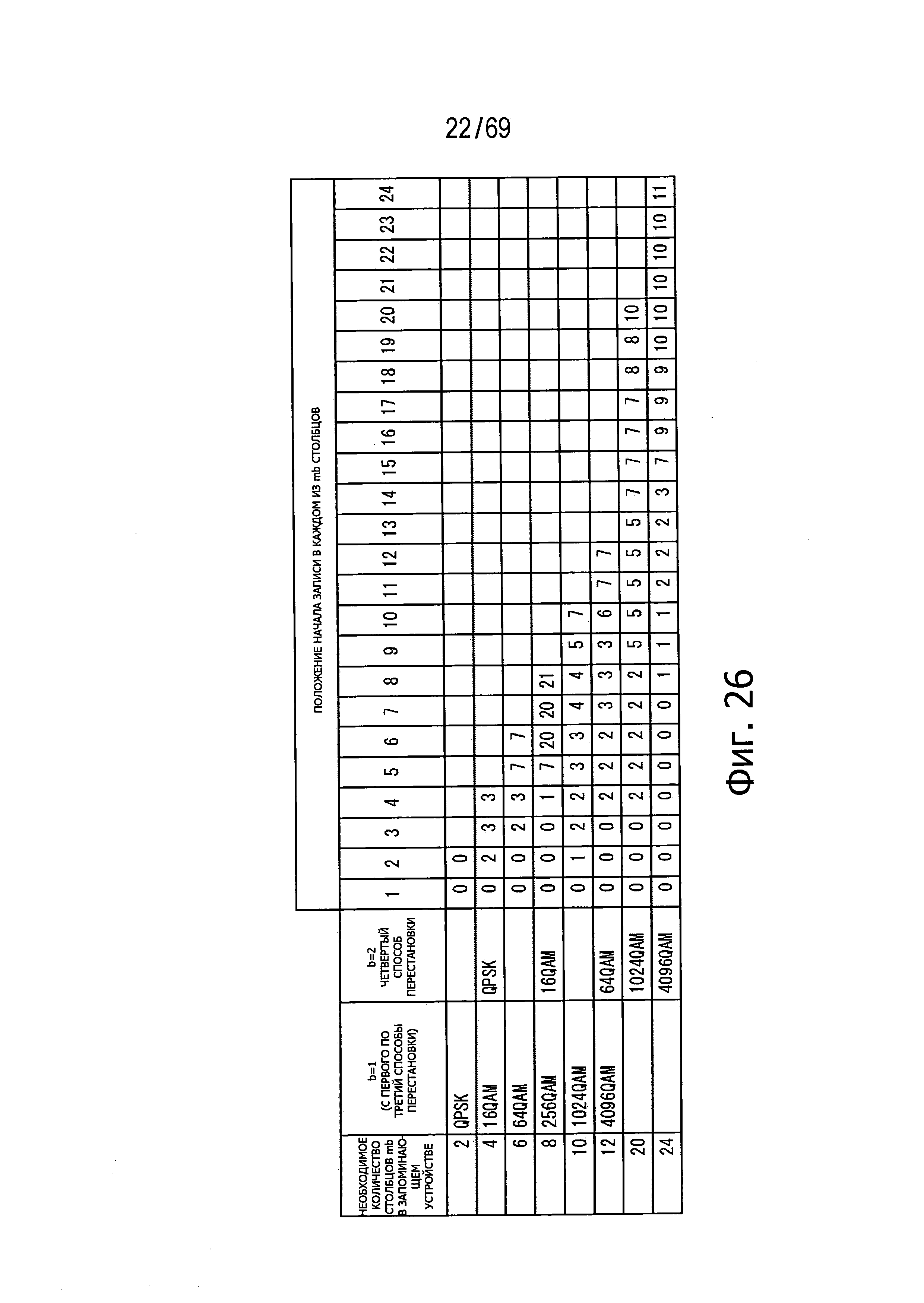

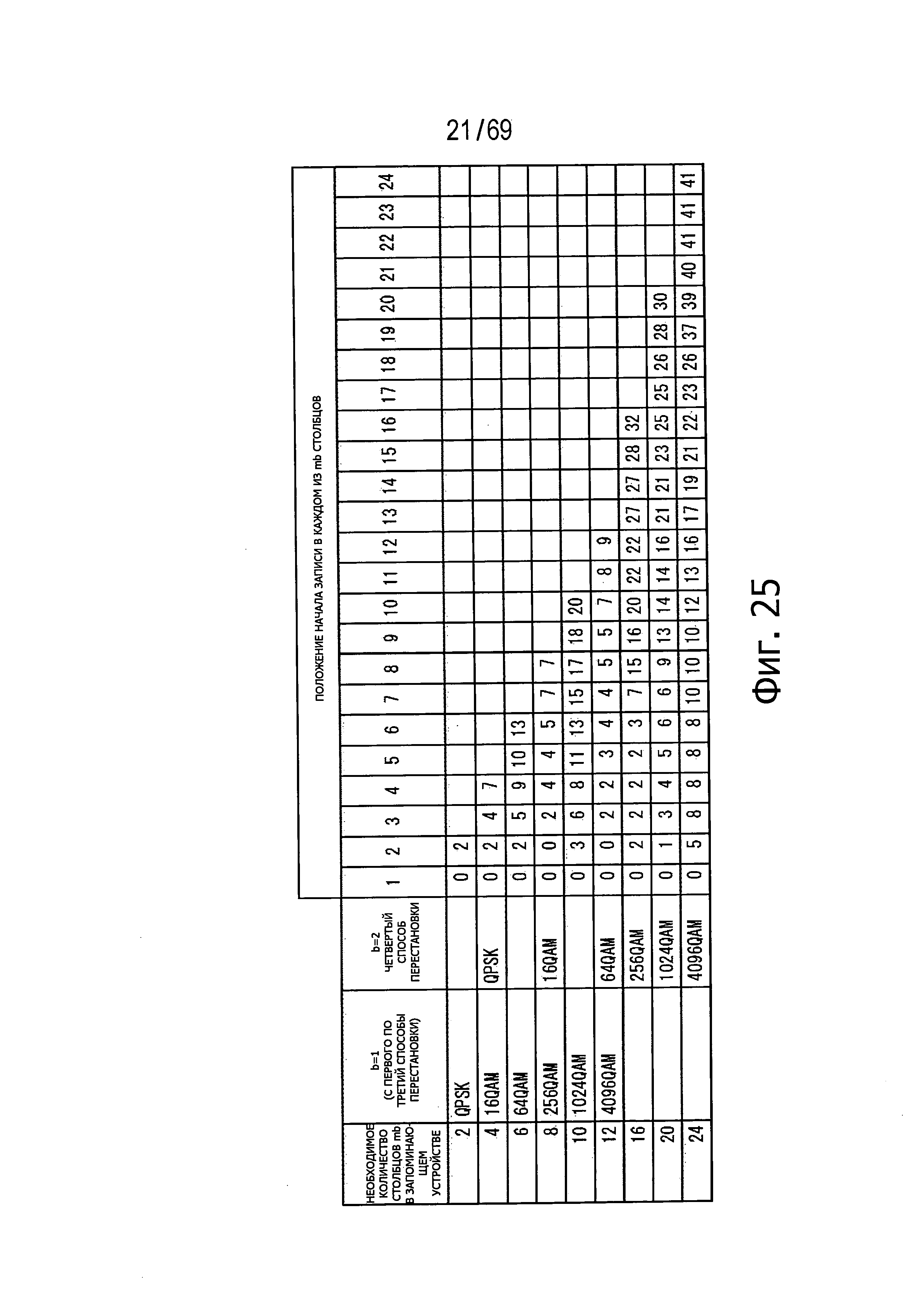

На фиг.25 показана схема, представляющая заданное количество столбцов для перемежения со скручиванием столбцов в запоминающем устройстве 31, и адреса положений начала записи.

На фиг.26 показана схема, представляющая требуемое количество столбцов для перемежения со скручиванием столбцов в запоминающем устройстве 31, и адреса положений начала записи.

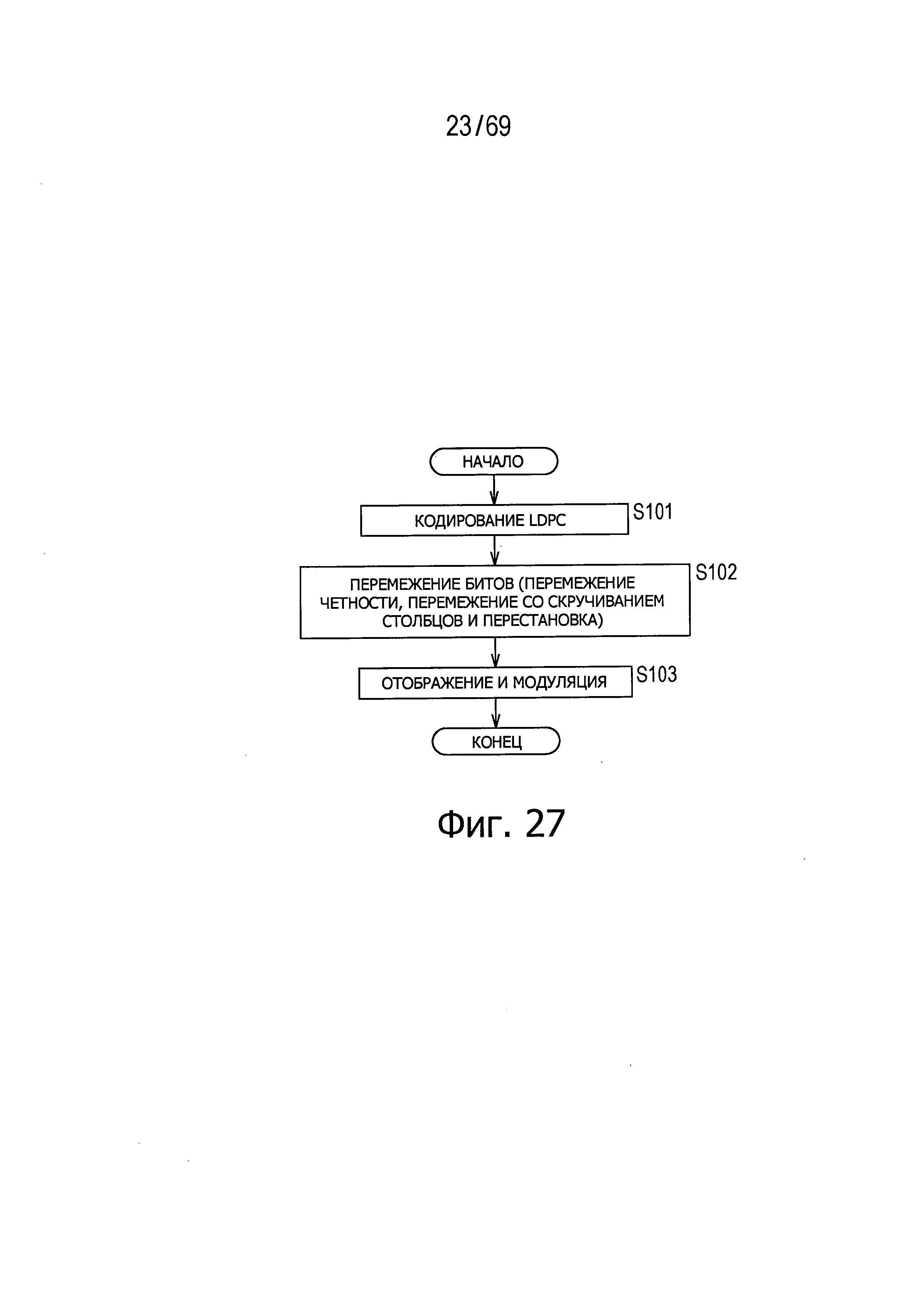

На фиг.27 показана блок-схема последовательности операций для пояснения операций, которые будут выполнены в перемежителе 116 битов и кодере 117 QAM.

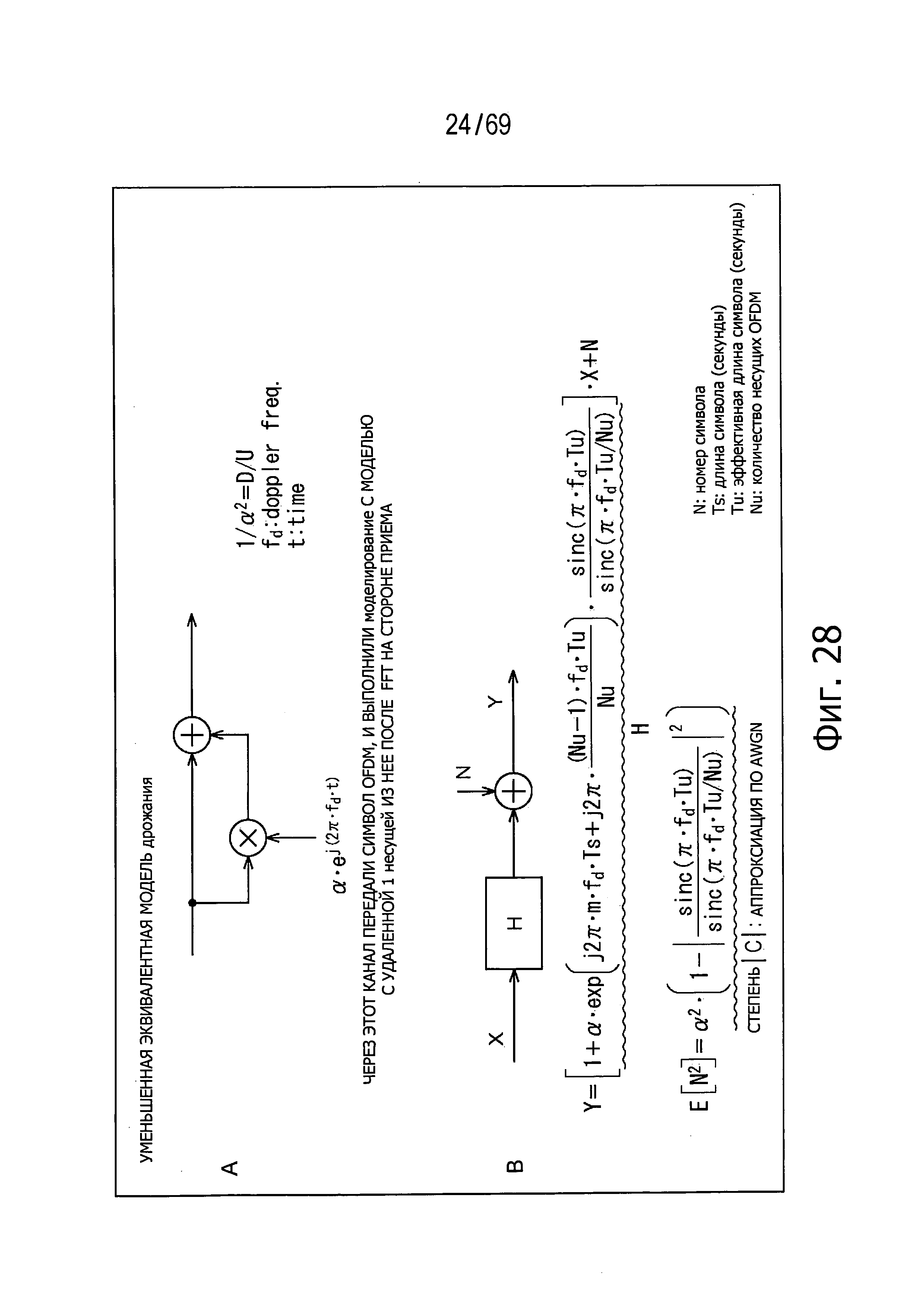

На фиг.28 показана схема, представляющая модель канала, используемого при моделировании.

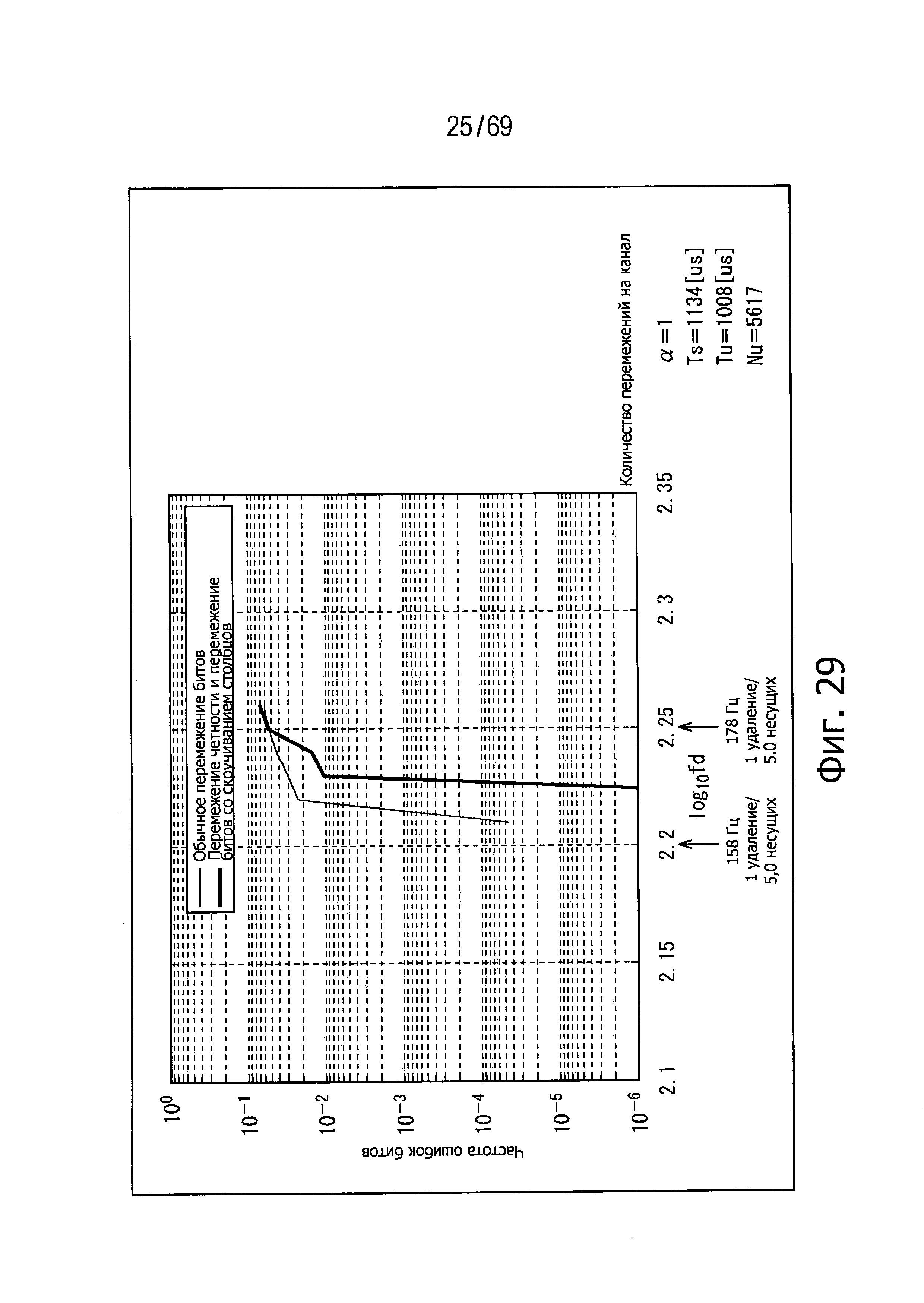

На фиг.29 показана схема, представляющая взаимосвязь между частотами ошибки, полученными при моделировании, и частотой Допплера дрожания.

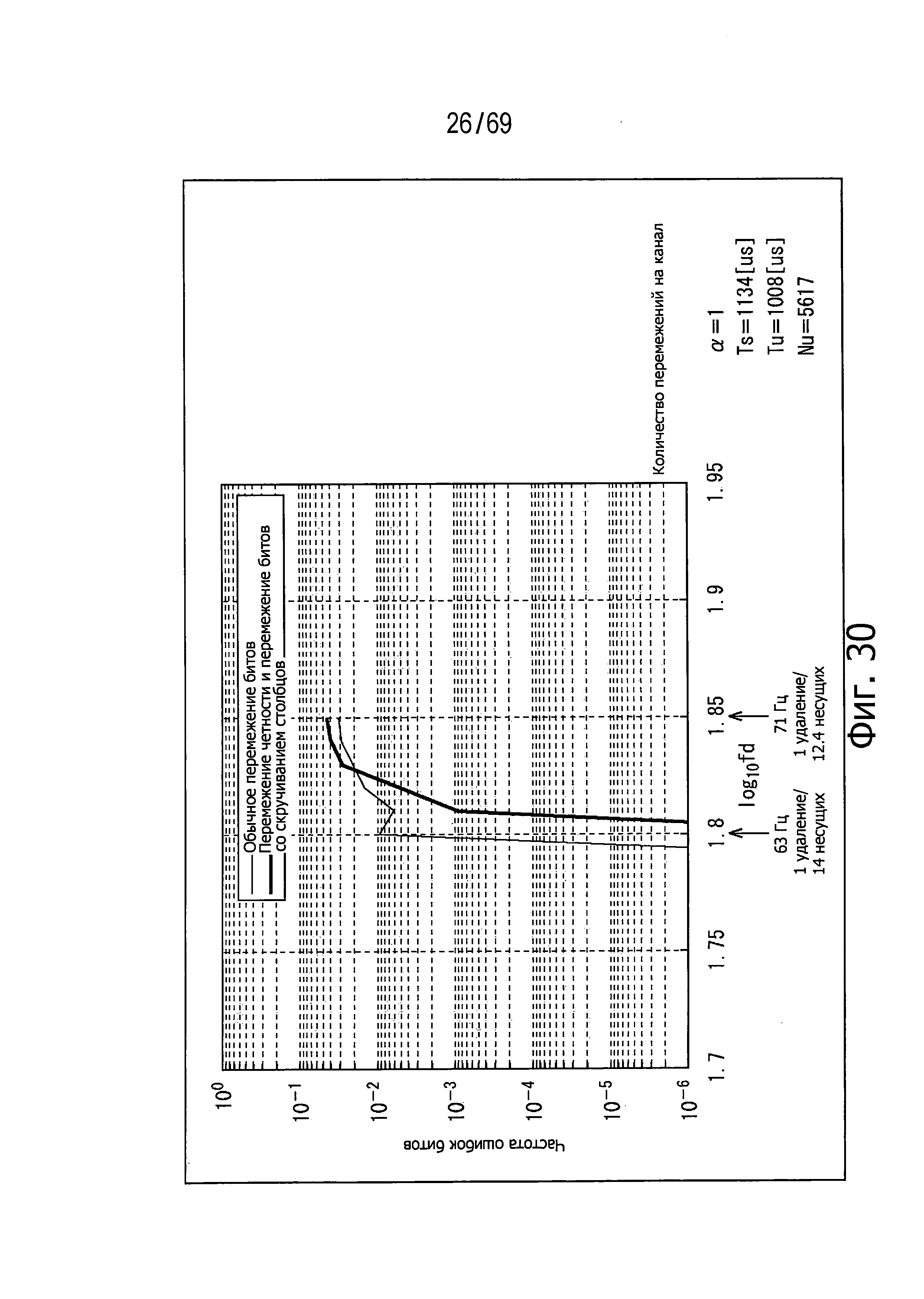

На фиг.30 показана схема, представляющая взаимосвязь между скоростями ошибки, полученными при моделировании, и частотой fa Допплера дрожания.

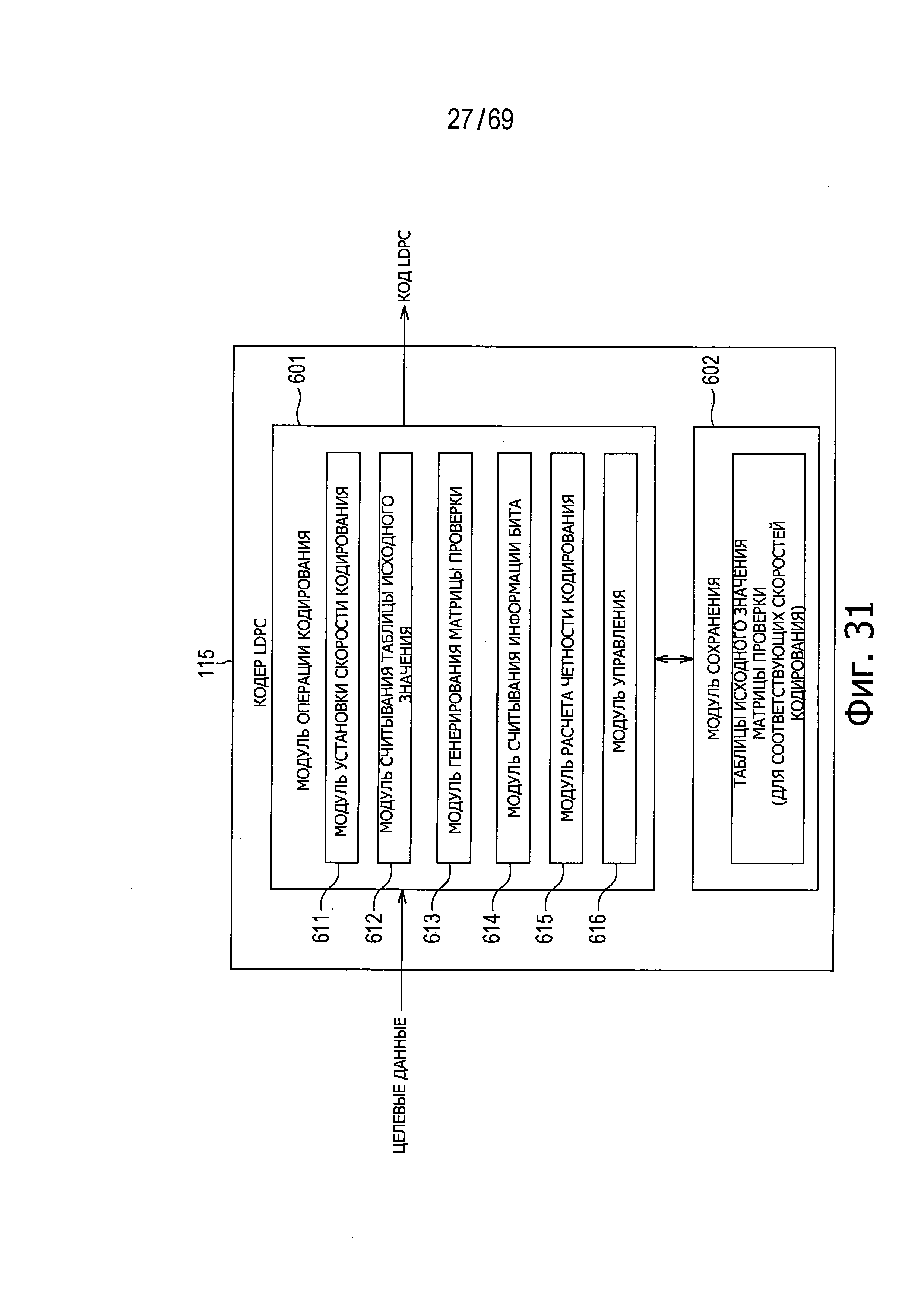

На фиг.31 показана блок-схема, представляющая пример структуры кодера 115 LDPC.

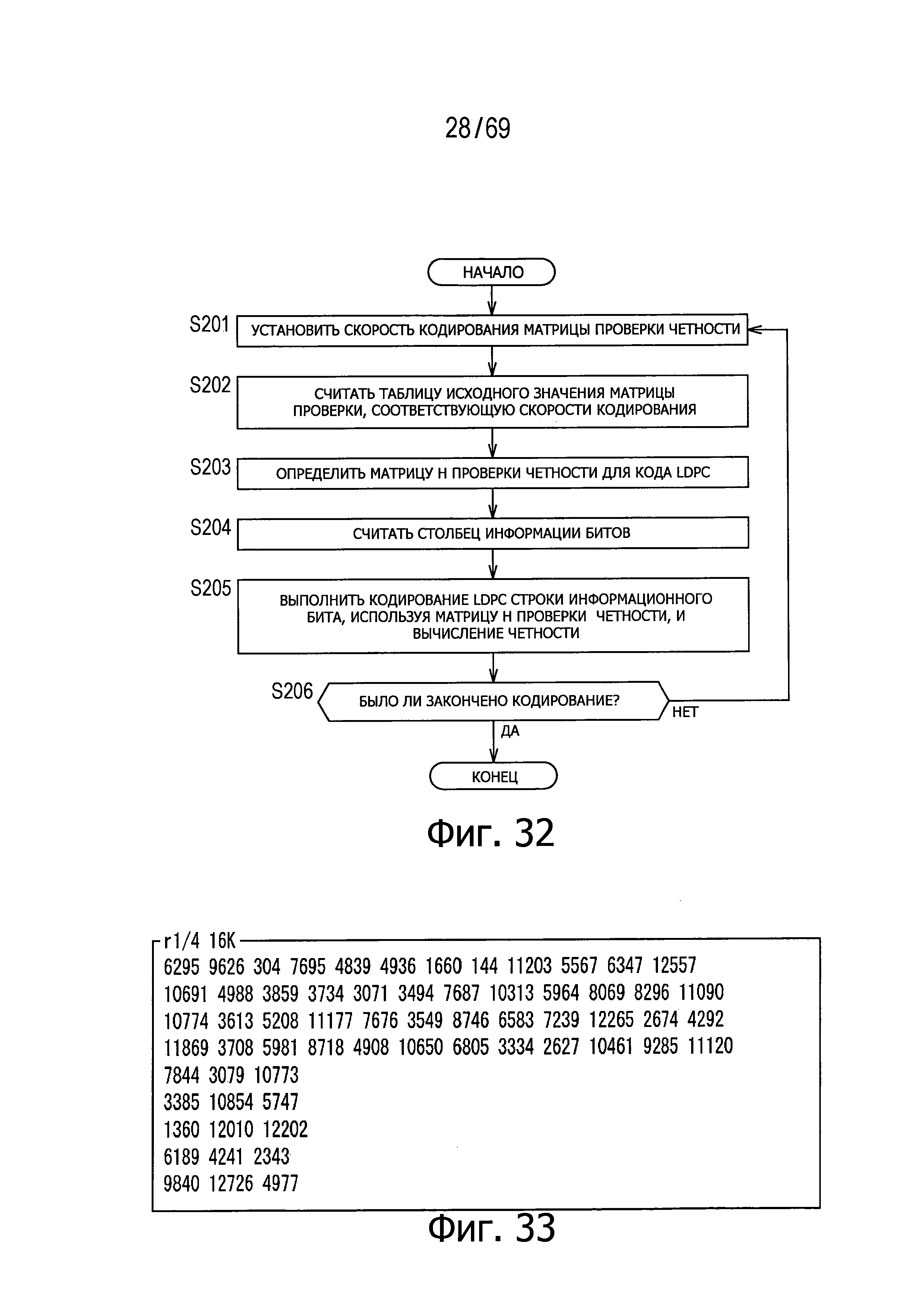

На фиг.32 показана блок-схема последовательности операций для пояснения операции кодера для кодера 115.

На фиг.33 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/4 и длины кода 16200.

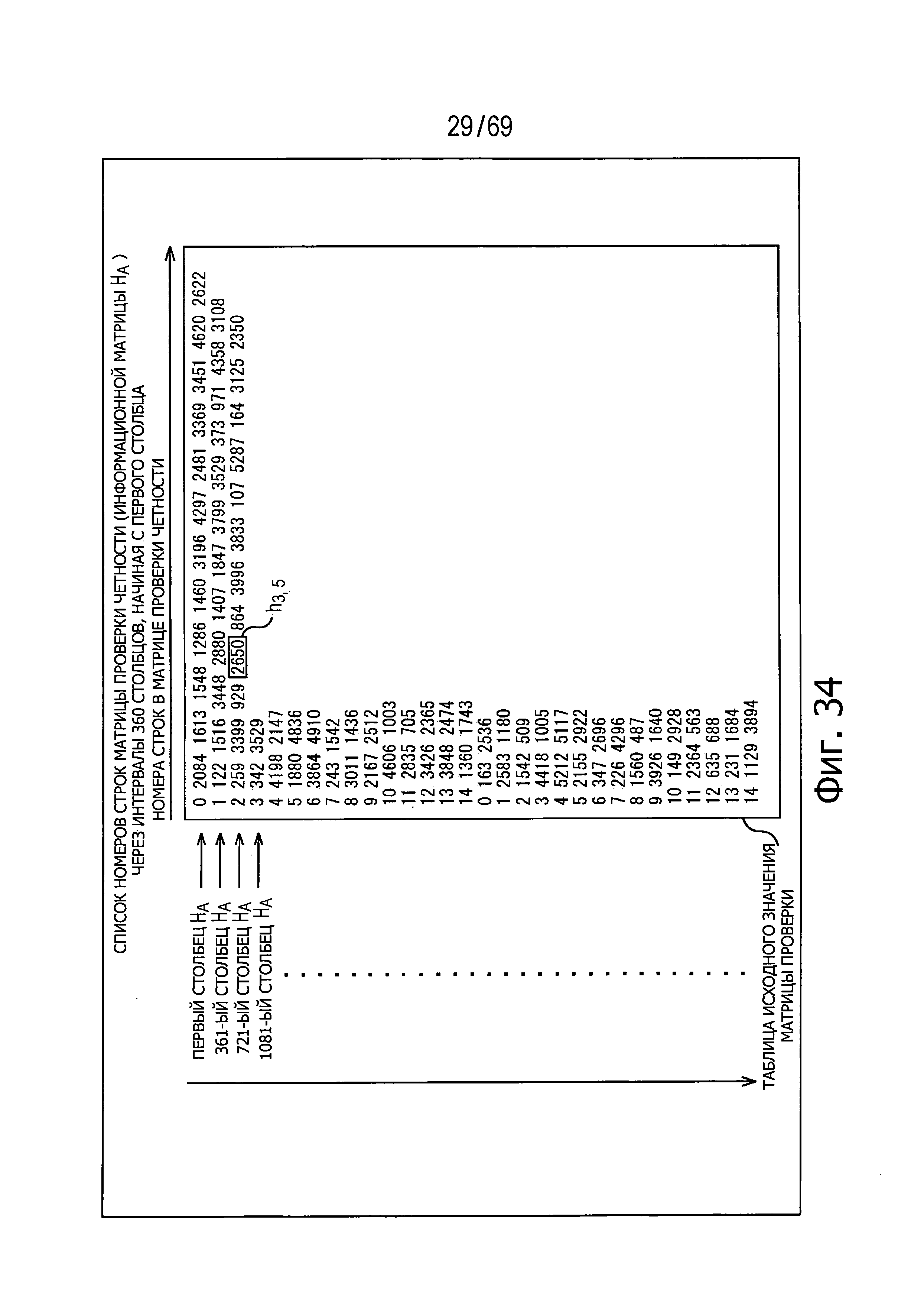

На фиг.34 показана схема, представляющая способ определения матрицы Н проверки четности из таблицы исходного значения матрицы проверки.

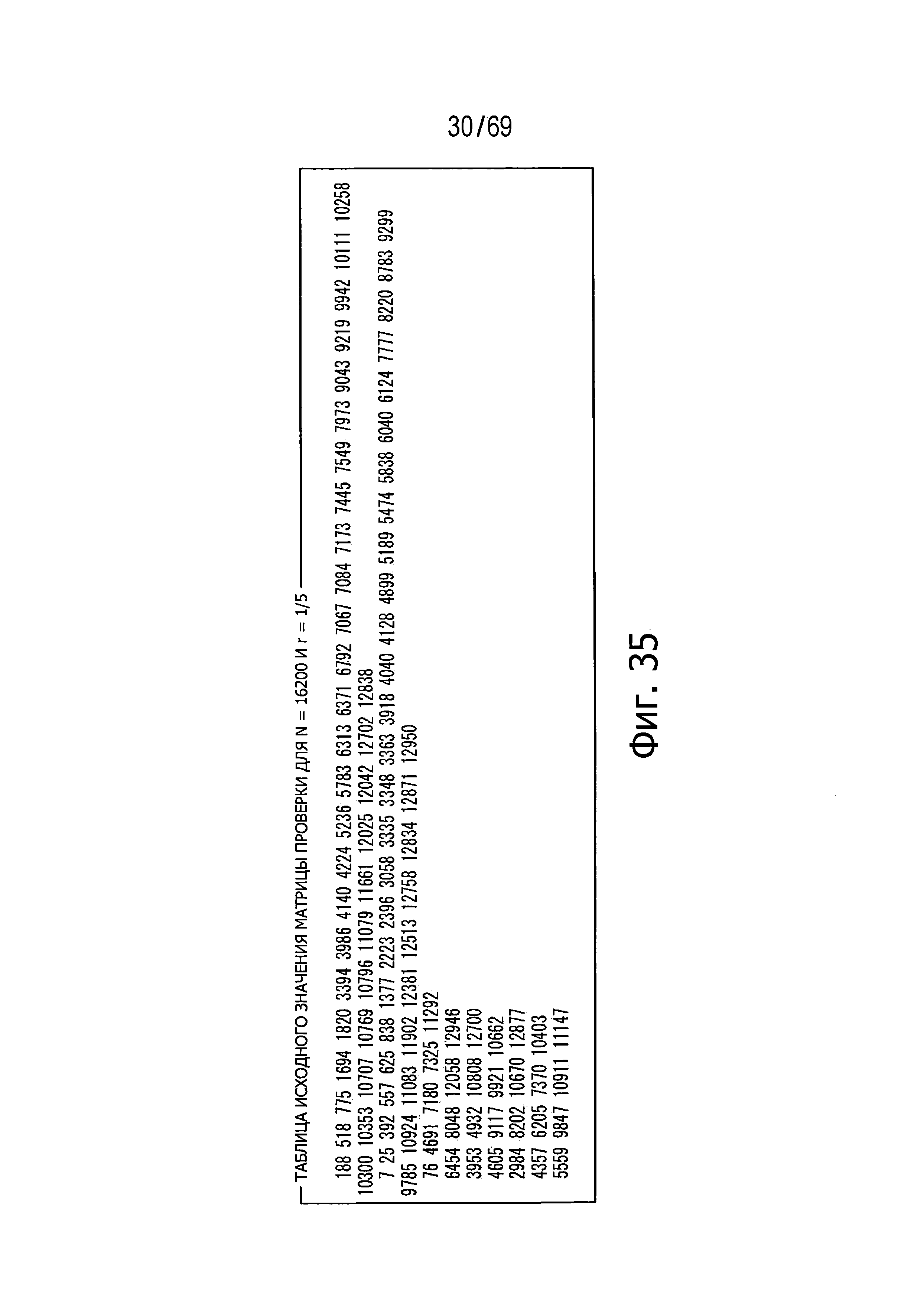

На фиг.35 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/5 и длины кода 16200.

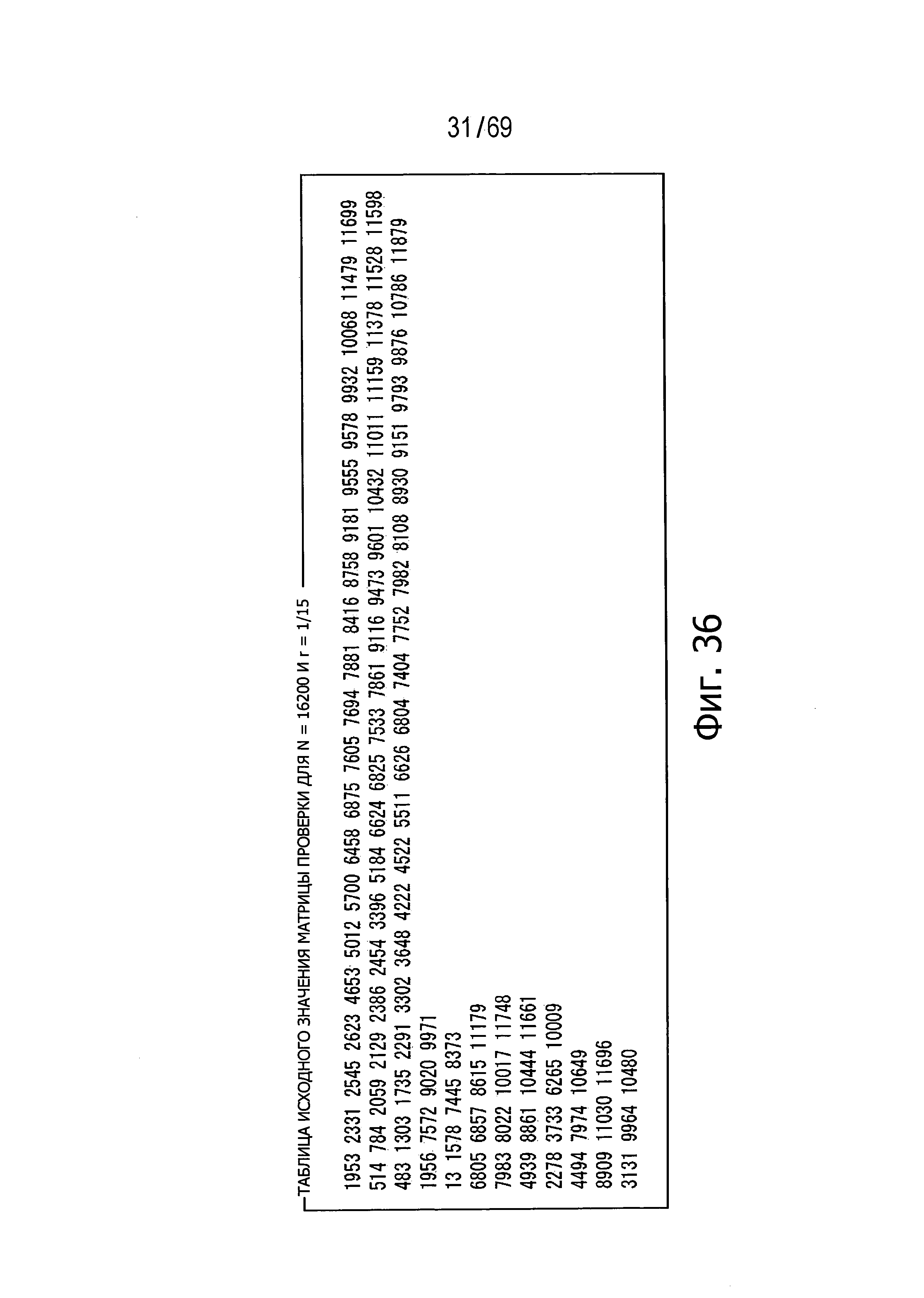

На фиг.36 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 4/15 и длины кода 16200.

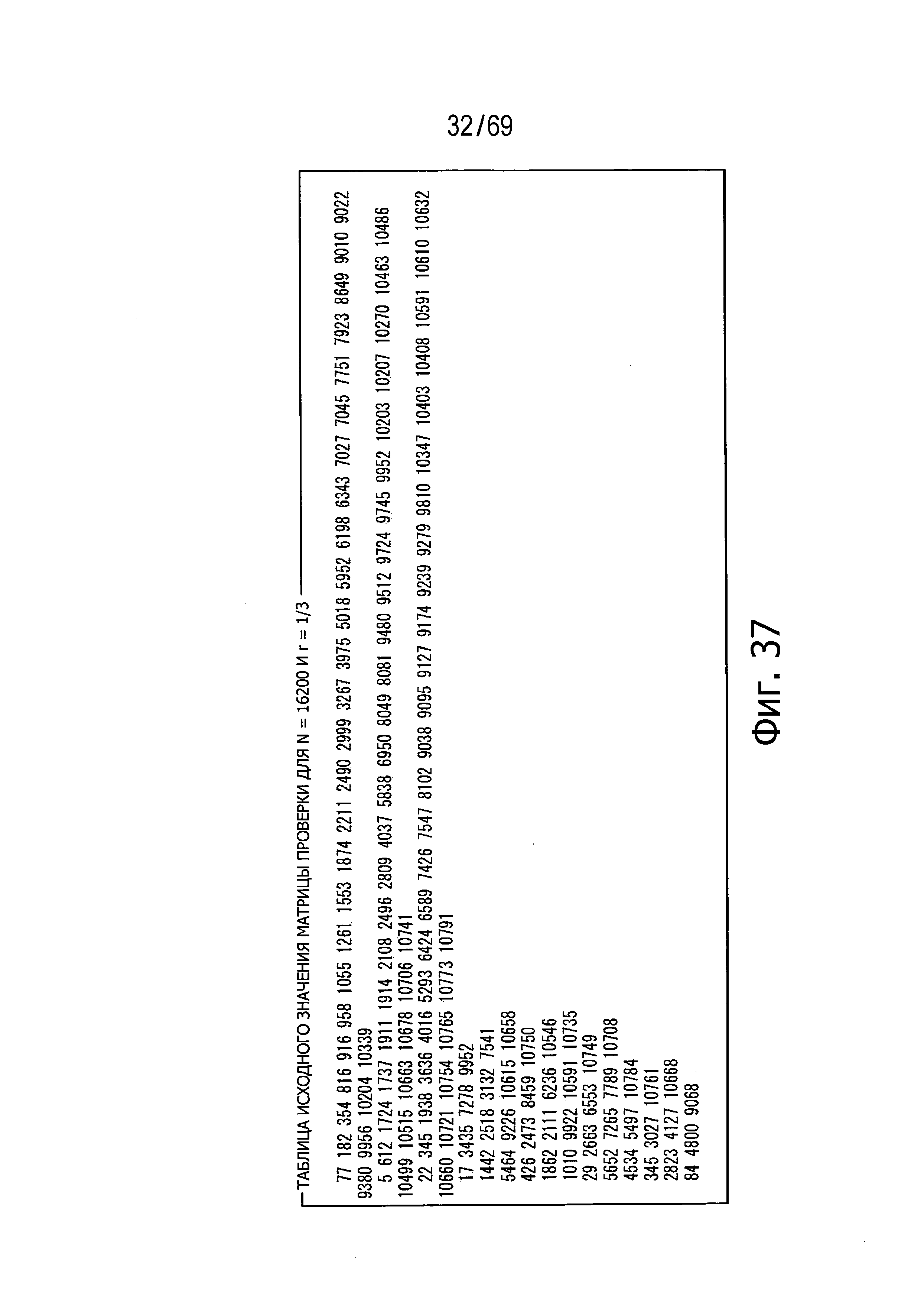

На фиг.37 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/3 и длины кода 16200.

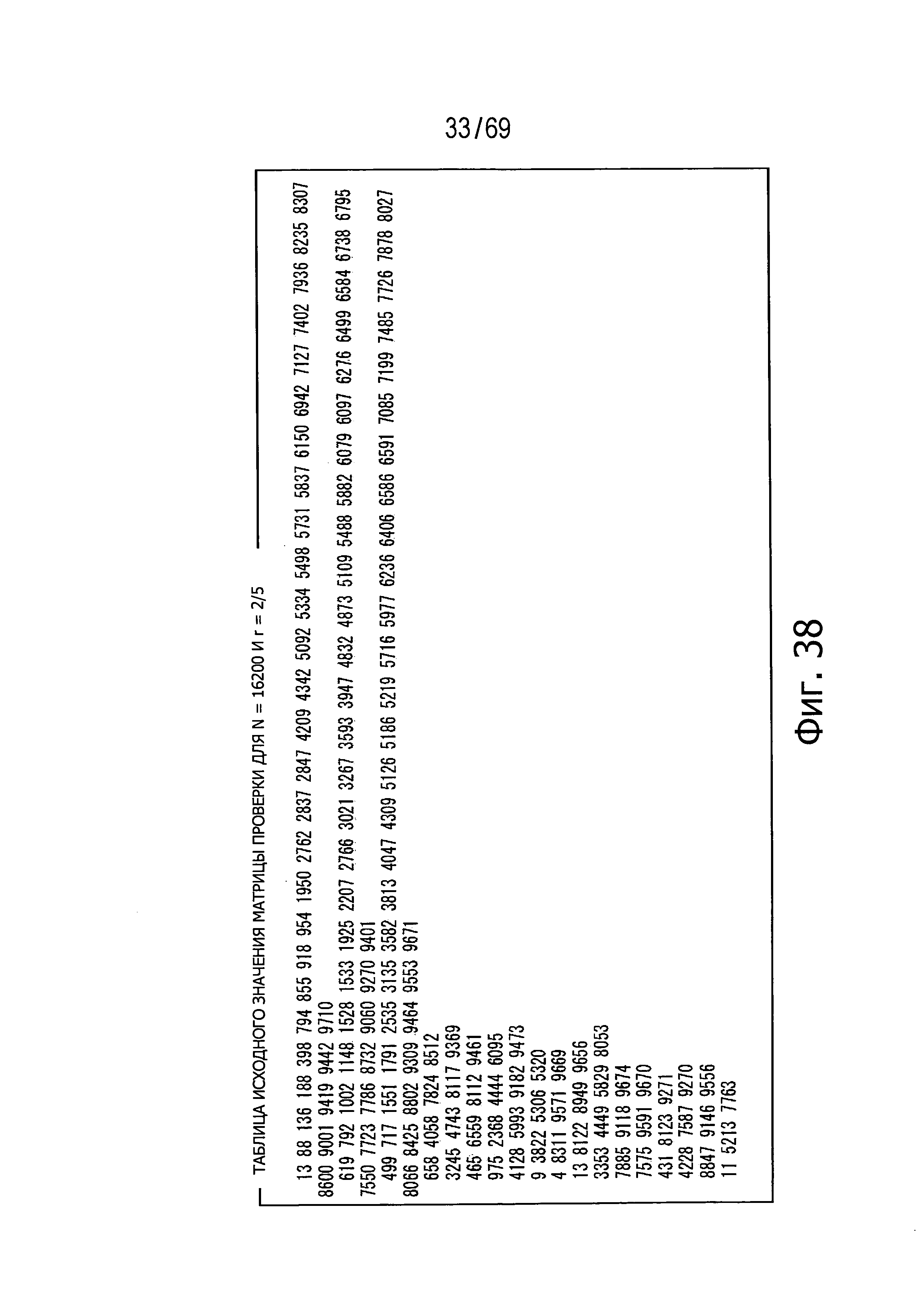

На фиг.38 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 2/5 и длины кода 16200.

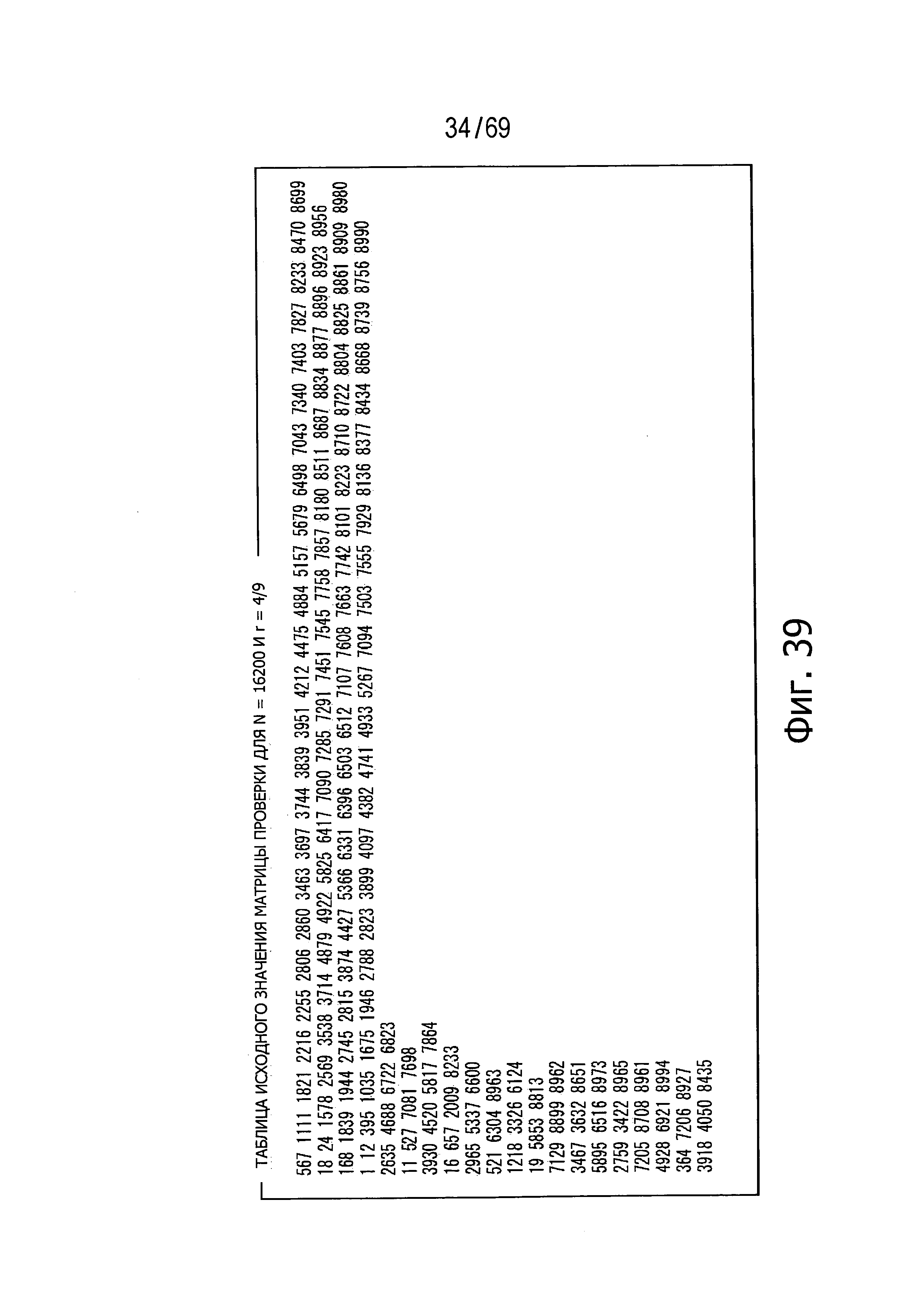

На фиг.39 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 4/9 и длины кода 16200.

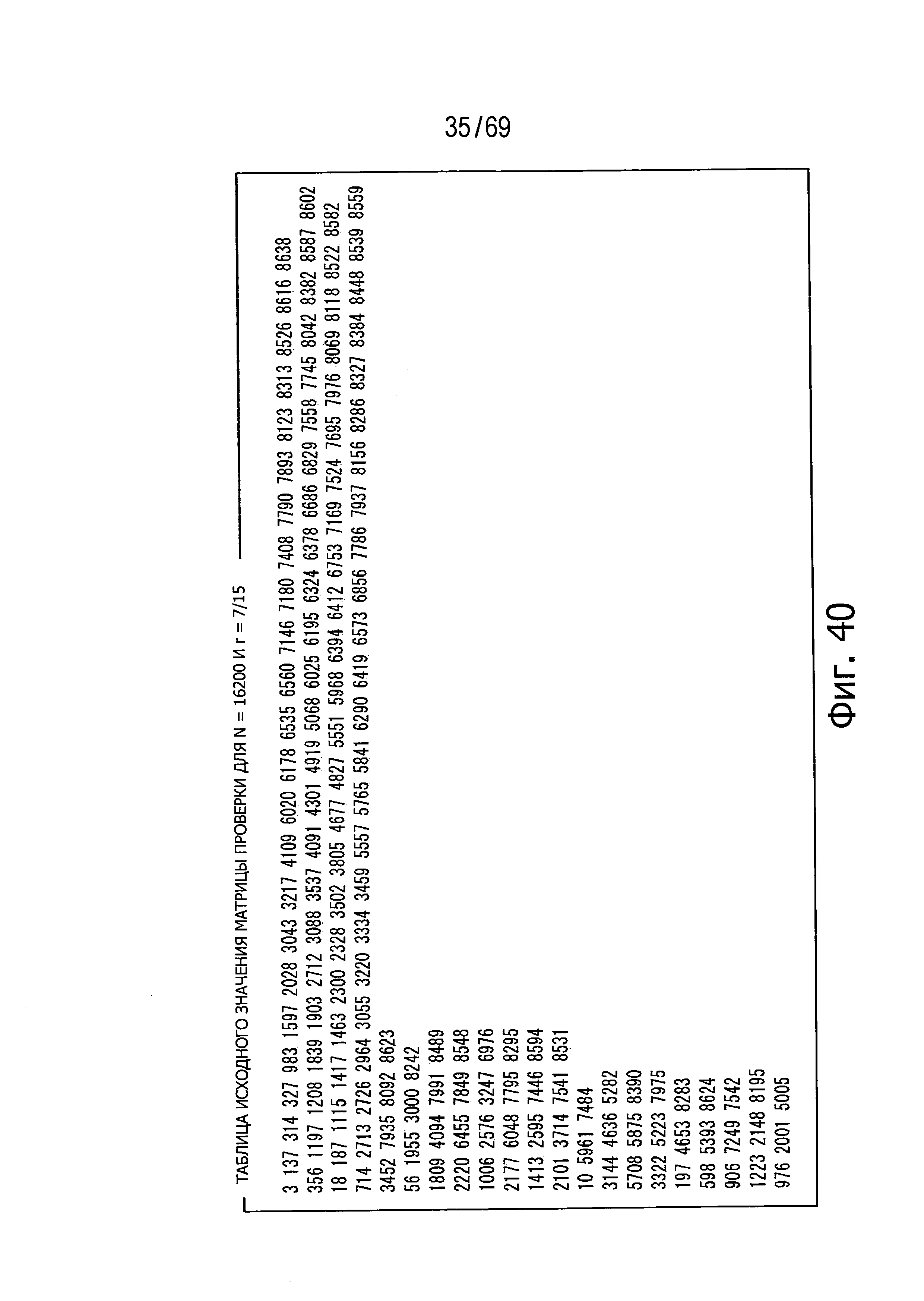

На фиг.40 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 7/15 и длины кода 16200.

На фиг.41 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 8/15 и длины кода 16200.

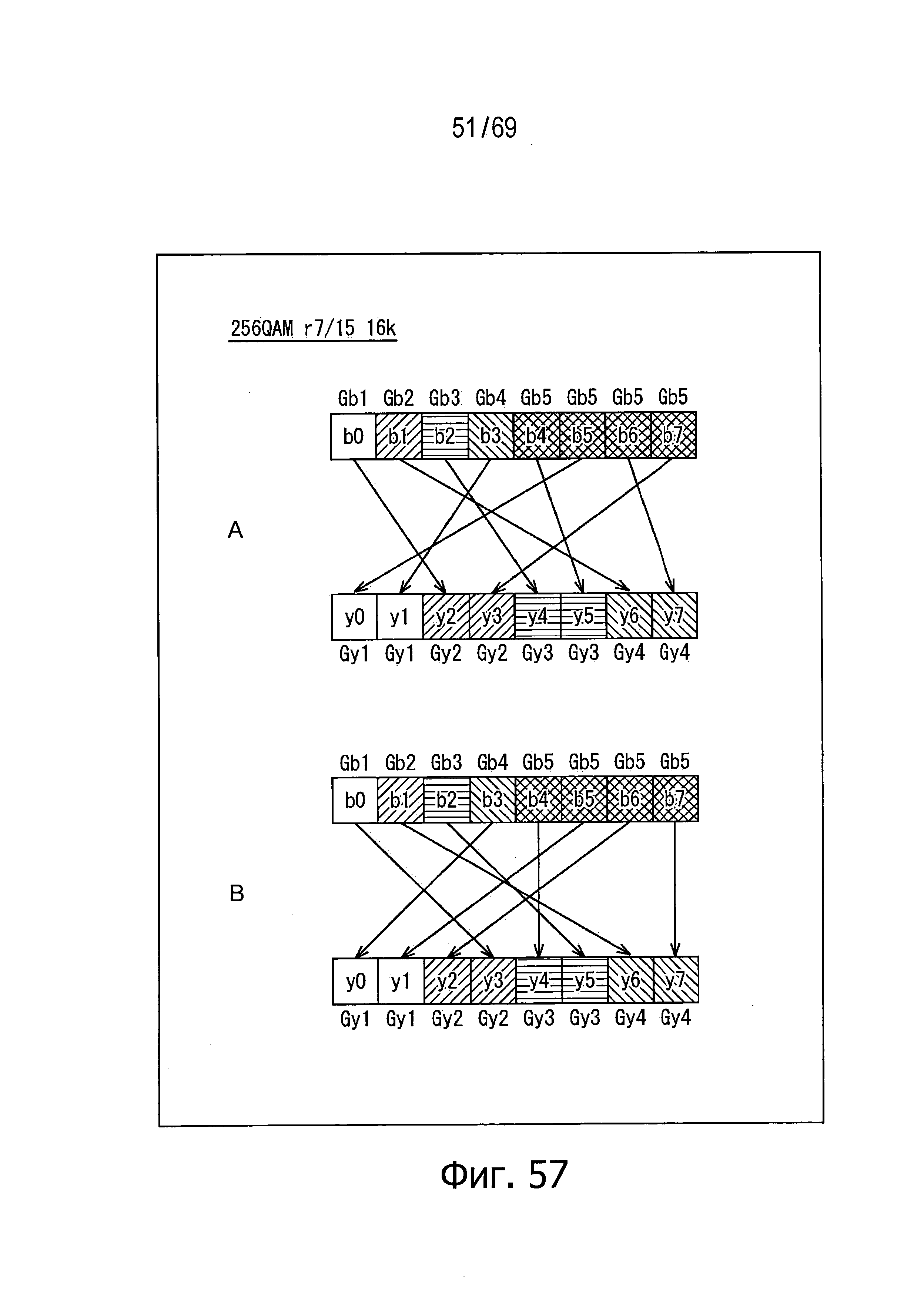

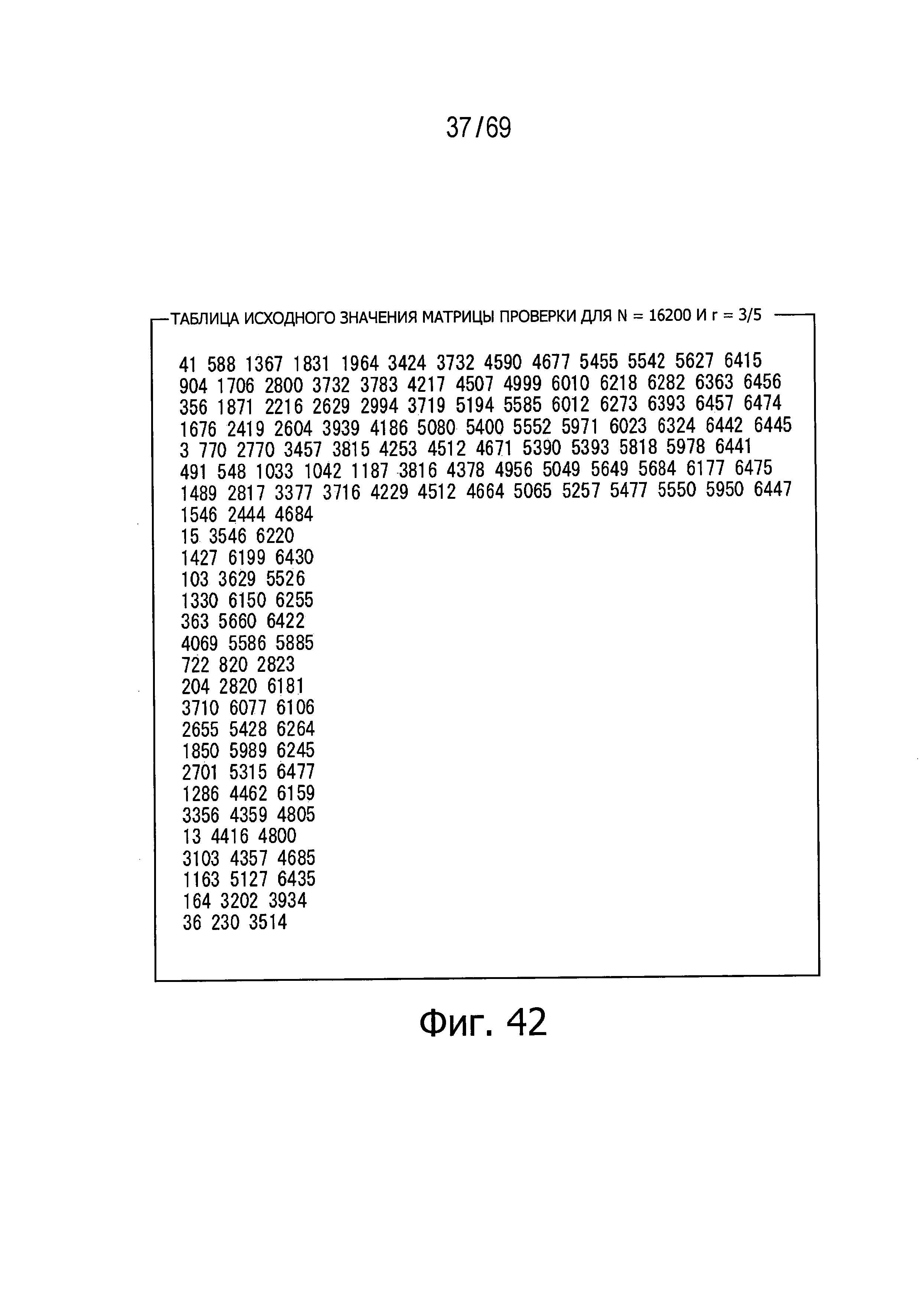

На фиг.42 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 3/5 и длины кода 16200.

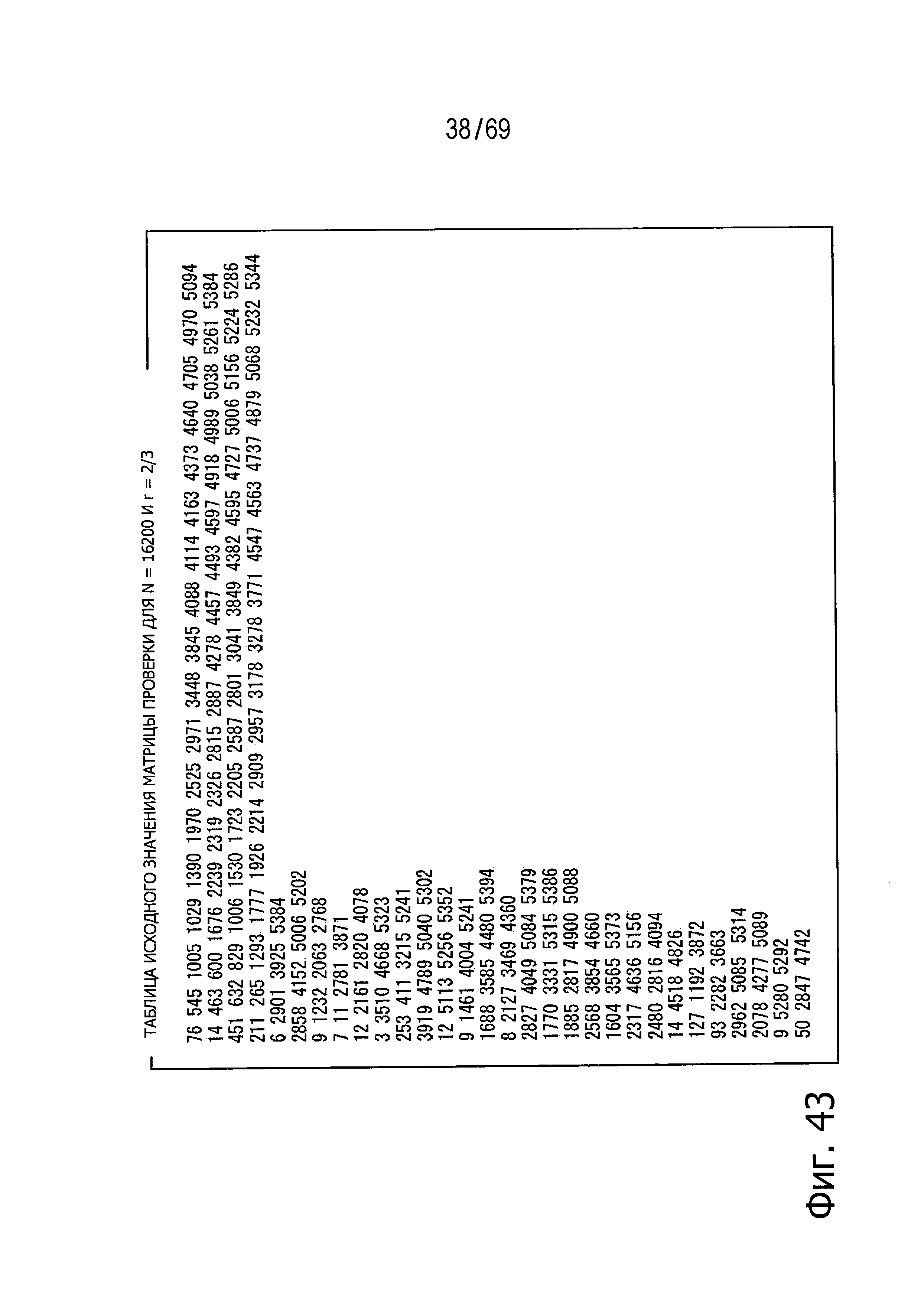

На фиг.43 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 2/3 и длины кода 16200.

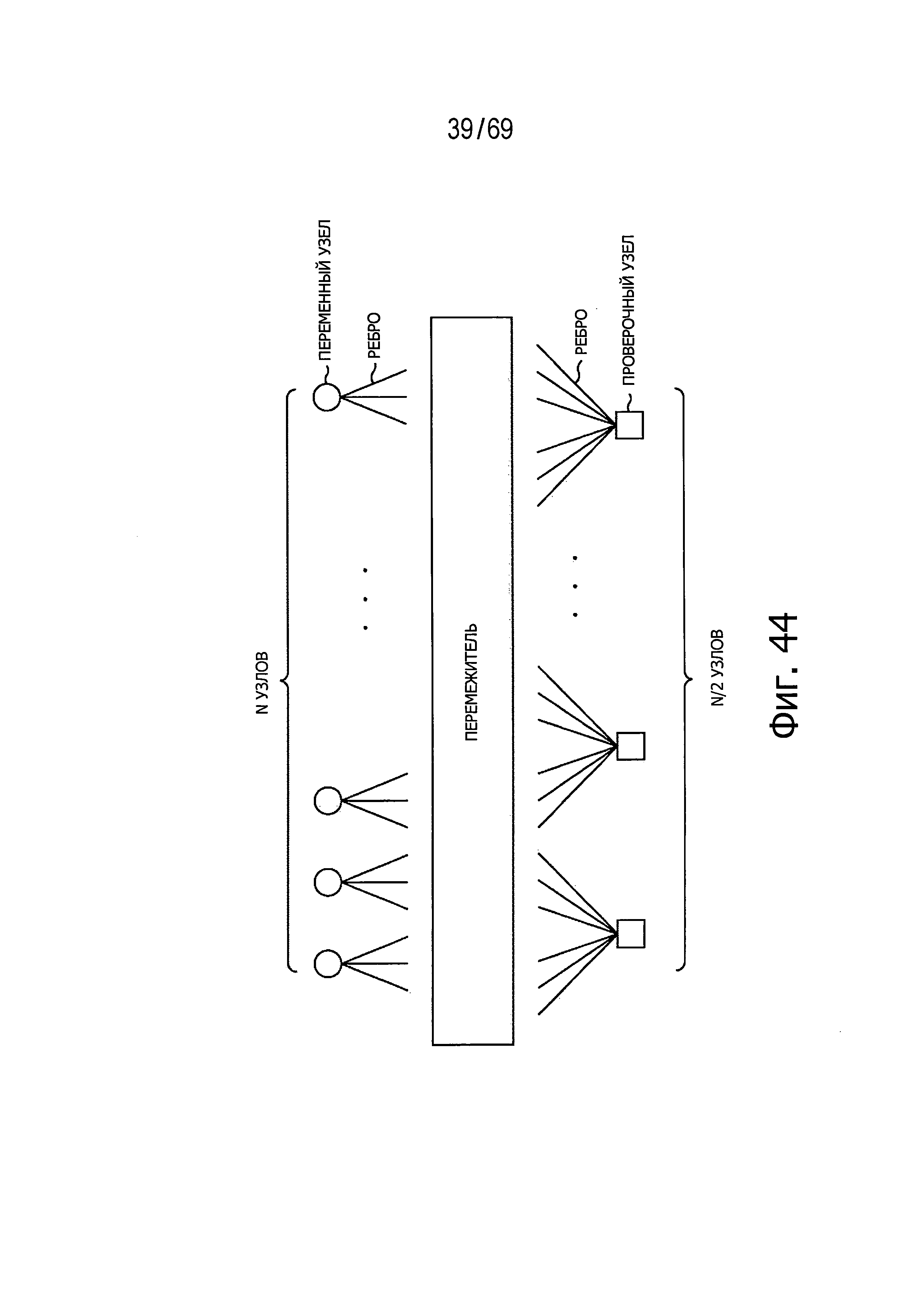

На фиг.44 показана схема, представляющая пример графа Таннера совокупности в порядке последовательности, в которой вес столбца равен 3, и вес строки равен 6.

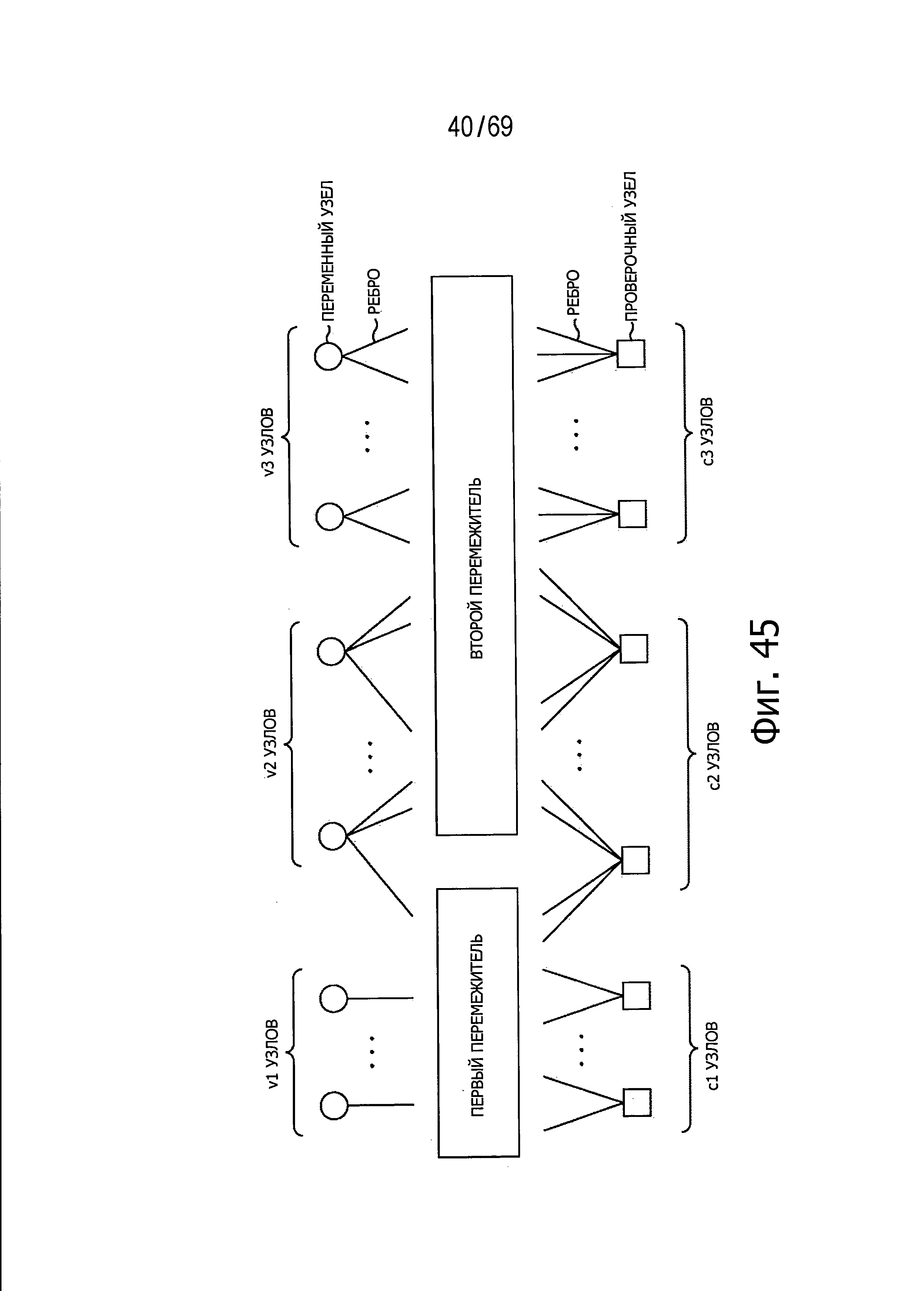

На фиг.45 показана схема, представляющая пример графа Таннера совокупности многореберного типа.

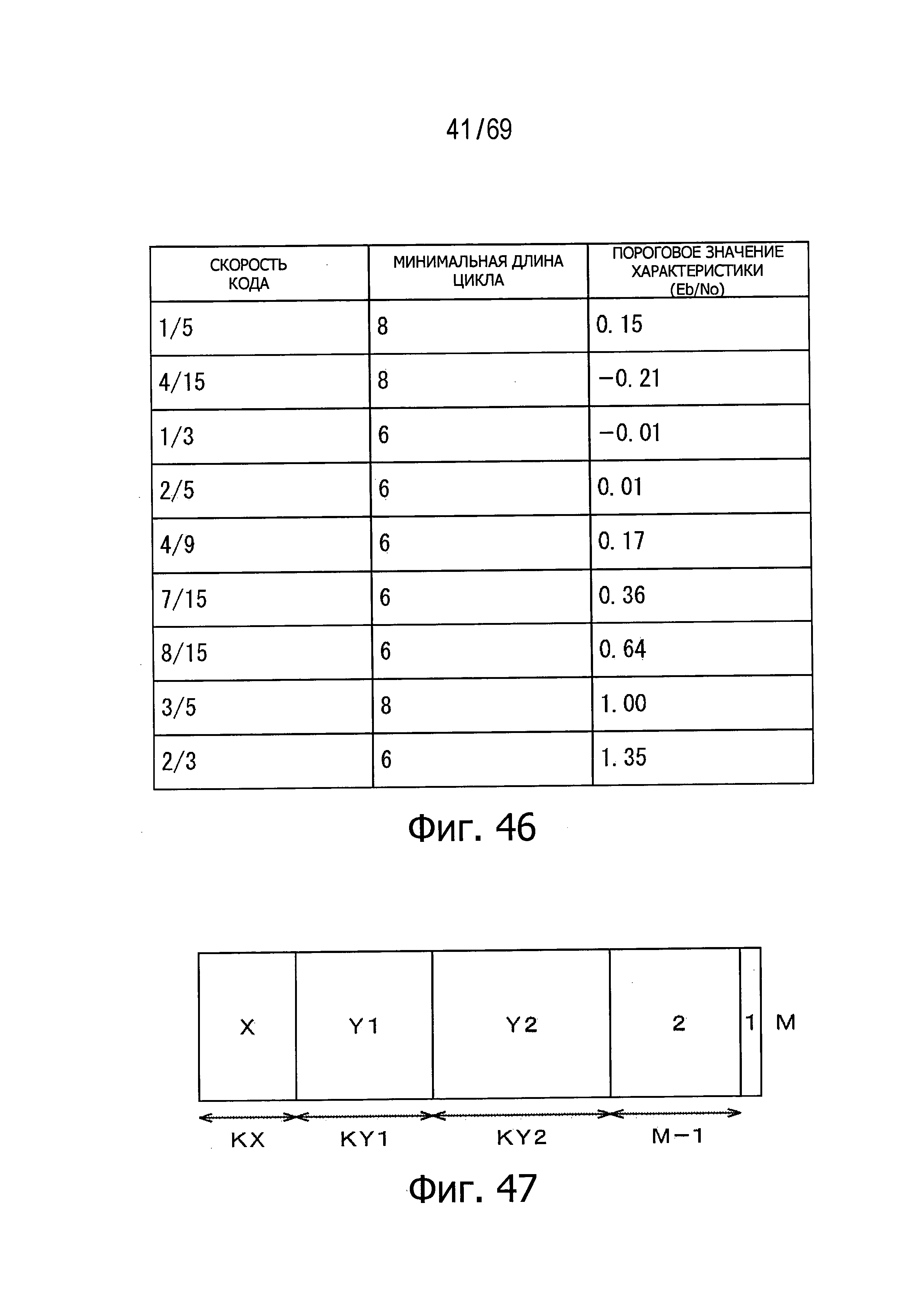

На фиг.46 показана схема, представляющая минимальные длины цикла и пороговые значения рабочей характеристики матриц проверки четности кодов LDPC, имеющих длину кода 16200.

На фиг.47 показана схема для пояснения матрицы проверки четности кода LDPC, имеющего длину кода 16200.

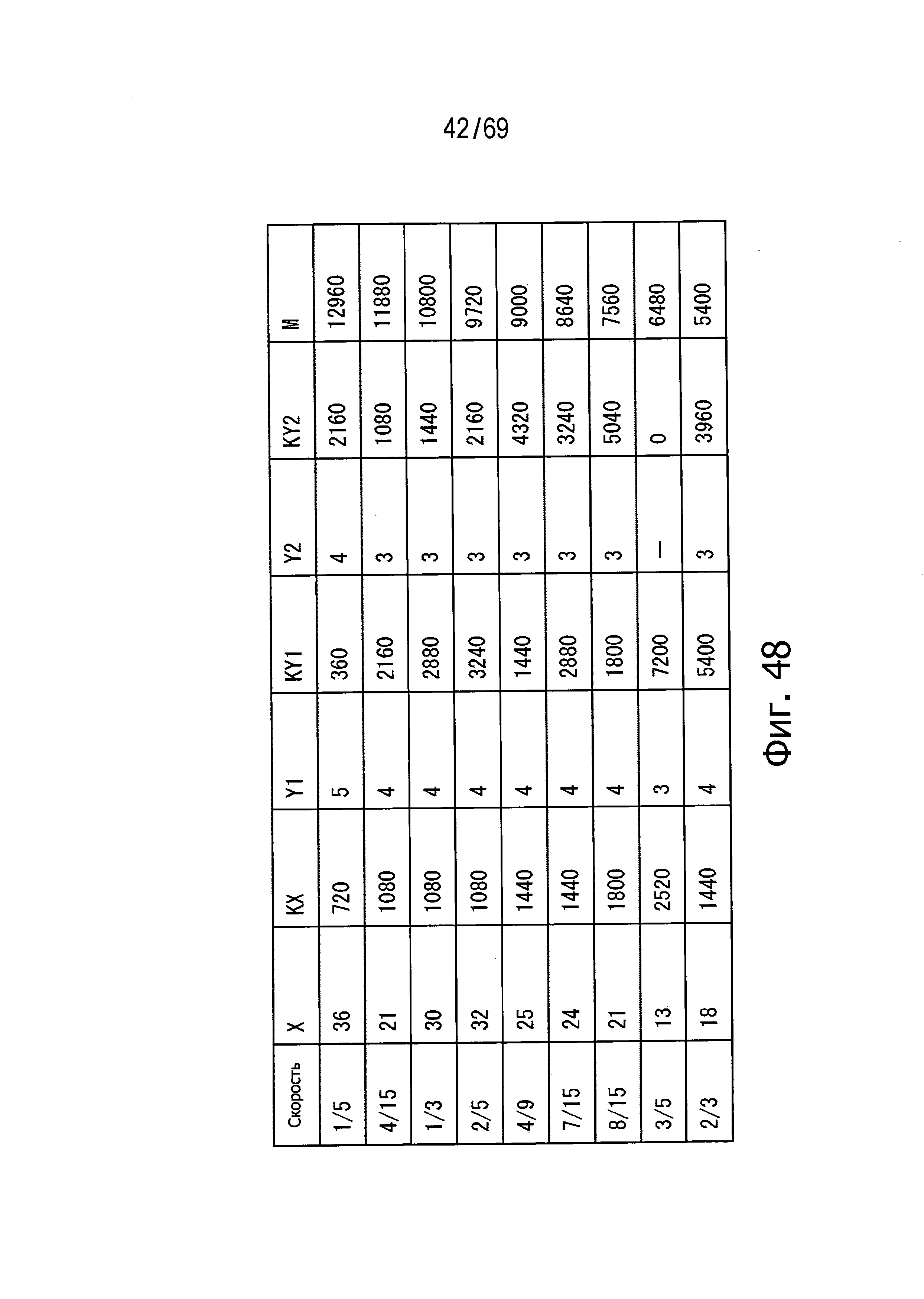

На фиг.48 показана схема для пояснения матрицы проверки четности кода LDPC, имеющего длину кода 16200.

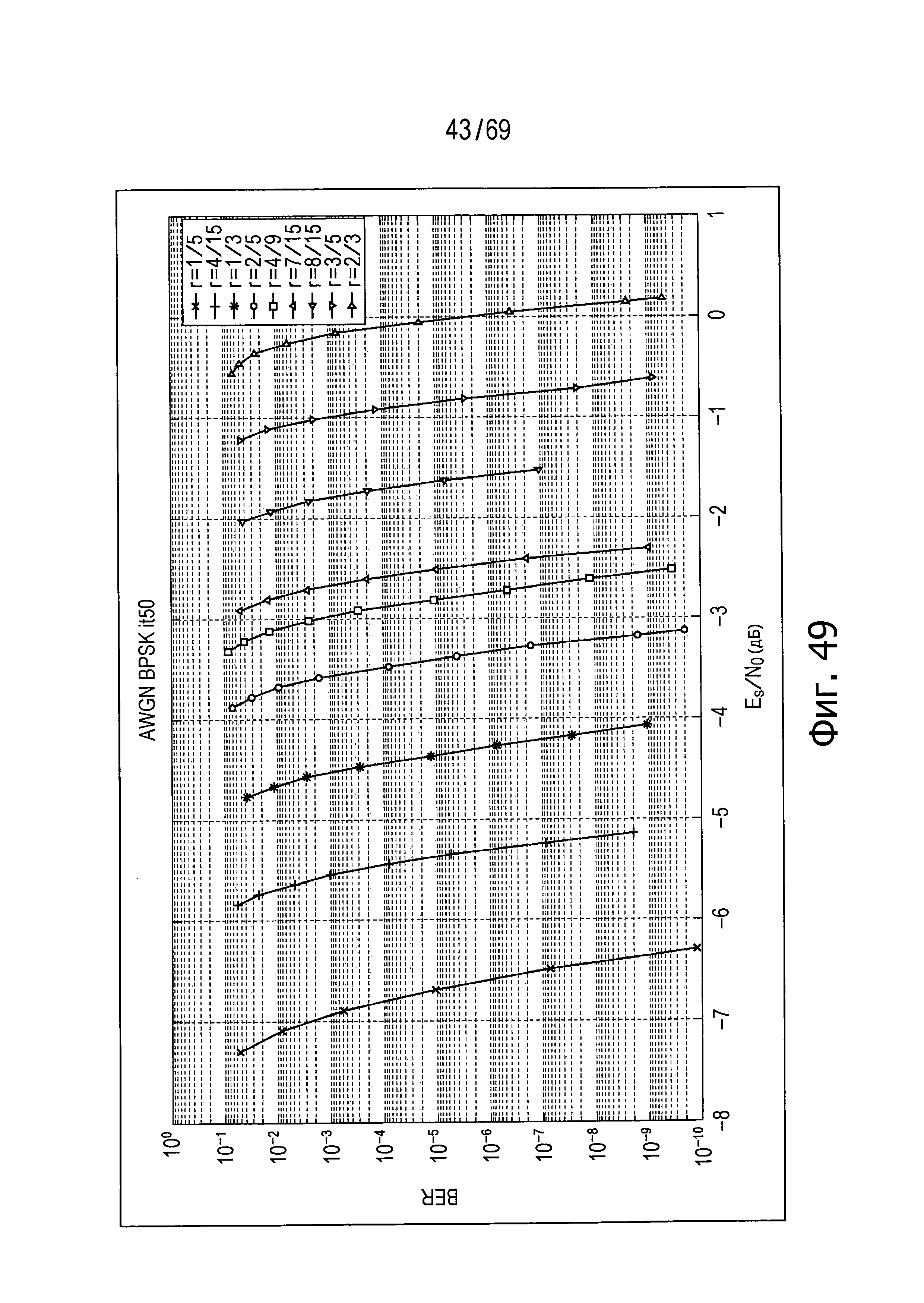

На фиг.49 показана схема, представляющая результаты моделирования, выполненного для измерения BER кодов LDPC, имеющих длину кода 16200.

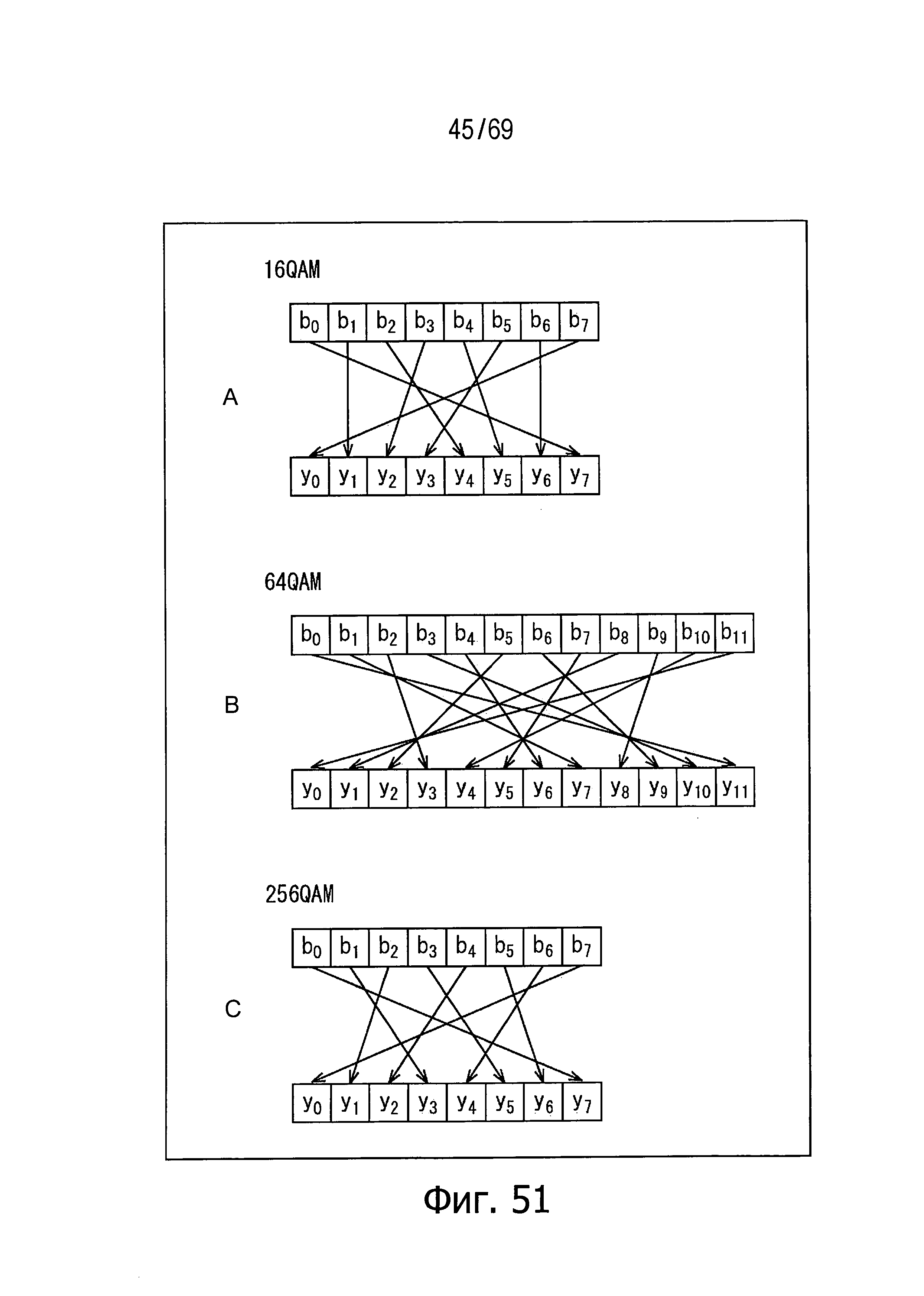

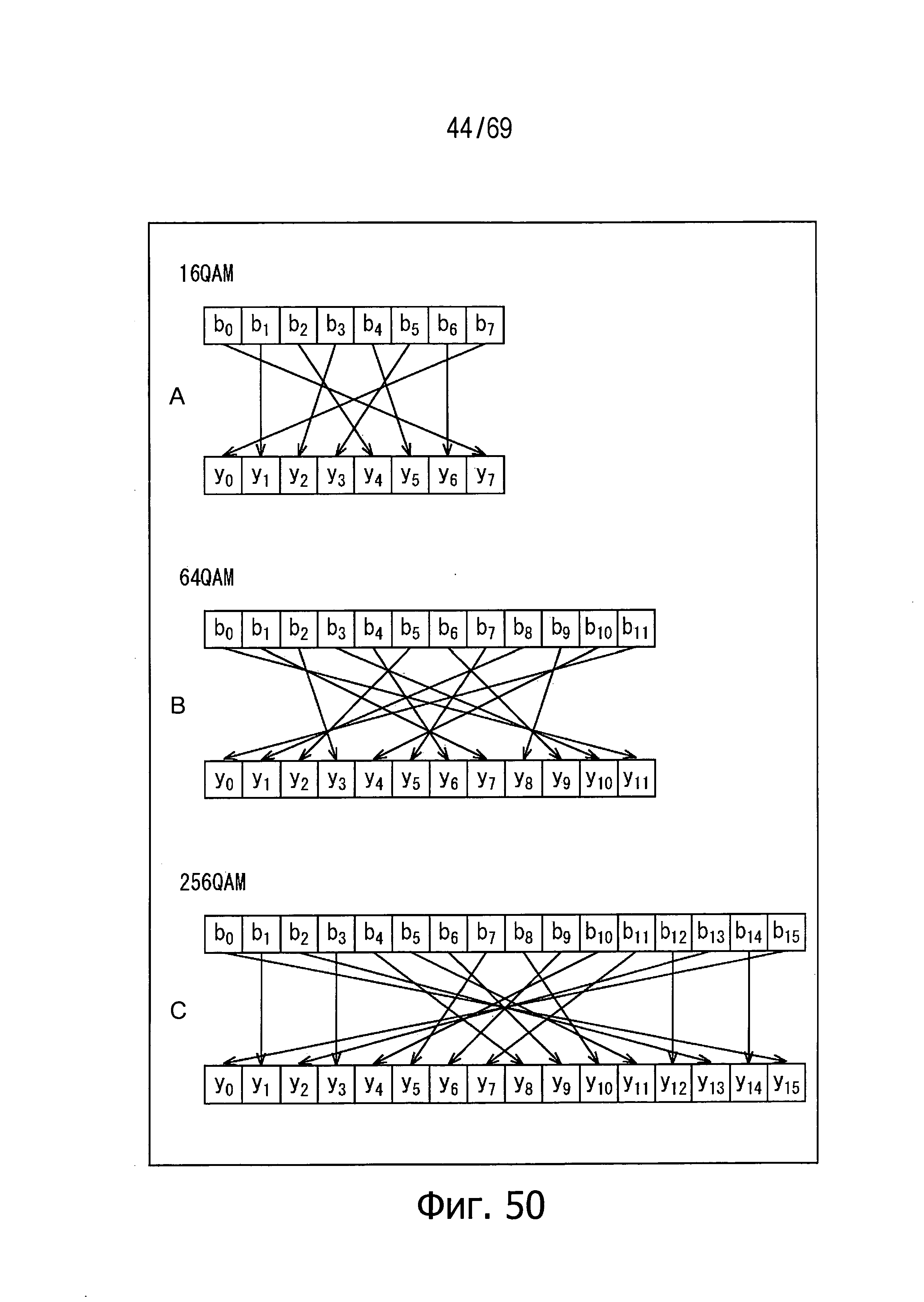

На фиг.50 показана схема для пояснения операции перестановки в соответствии с существующими способами.

На фиг.51 показана схема для пояснения операции перестановки в соответствии с существующими способами.

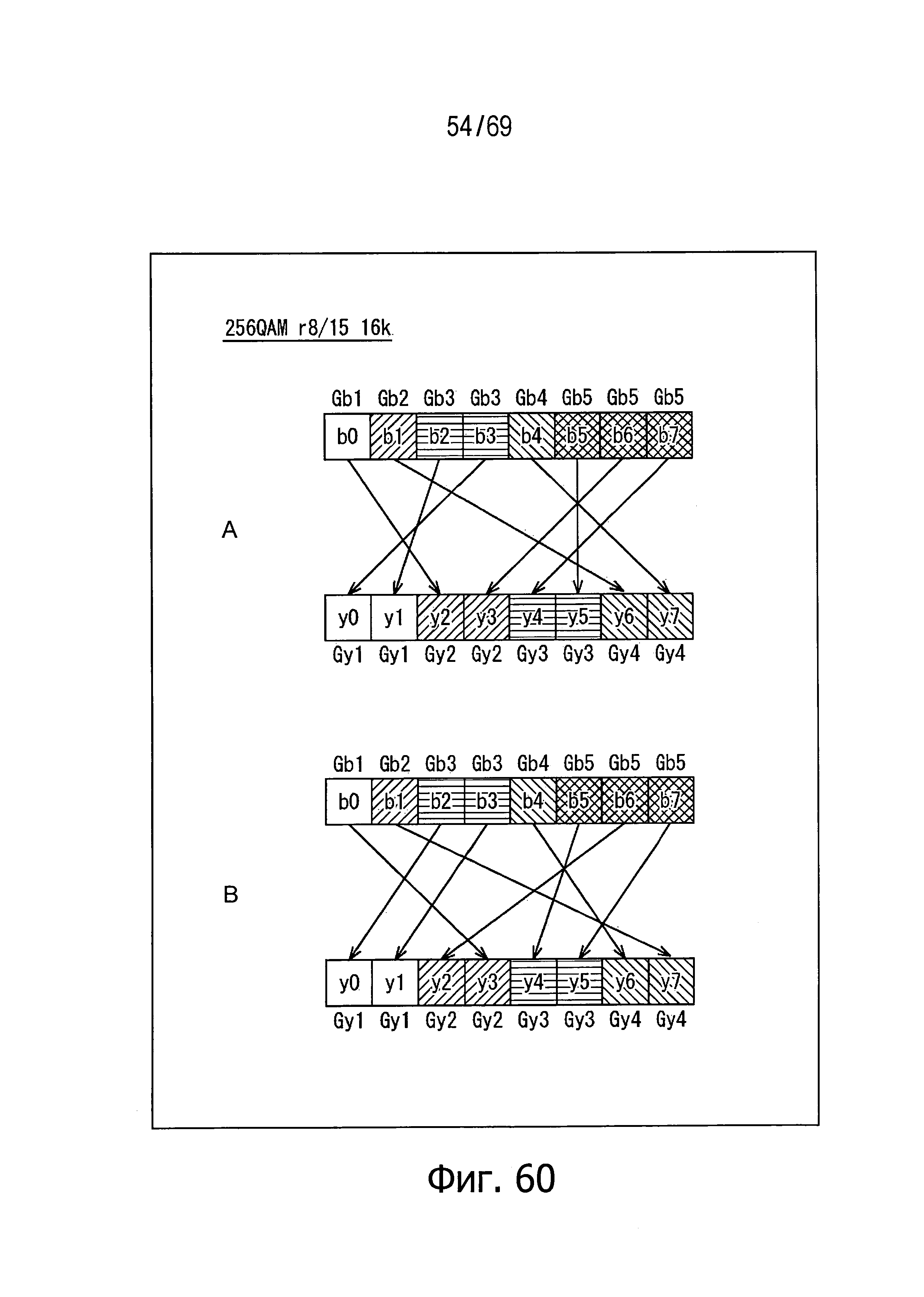

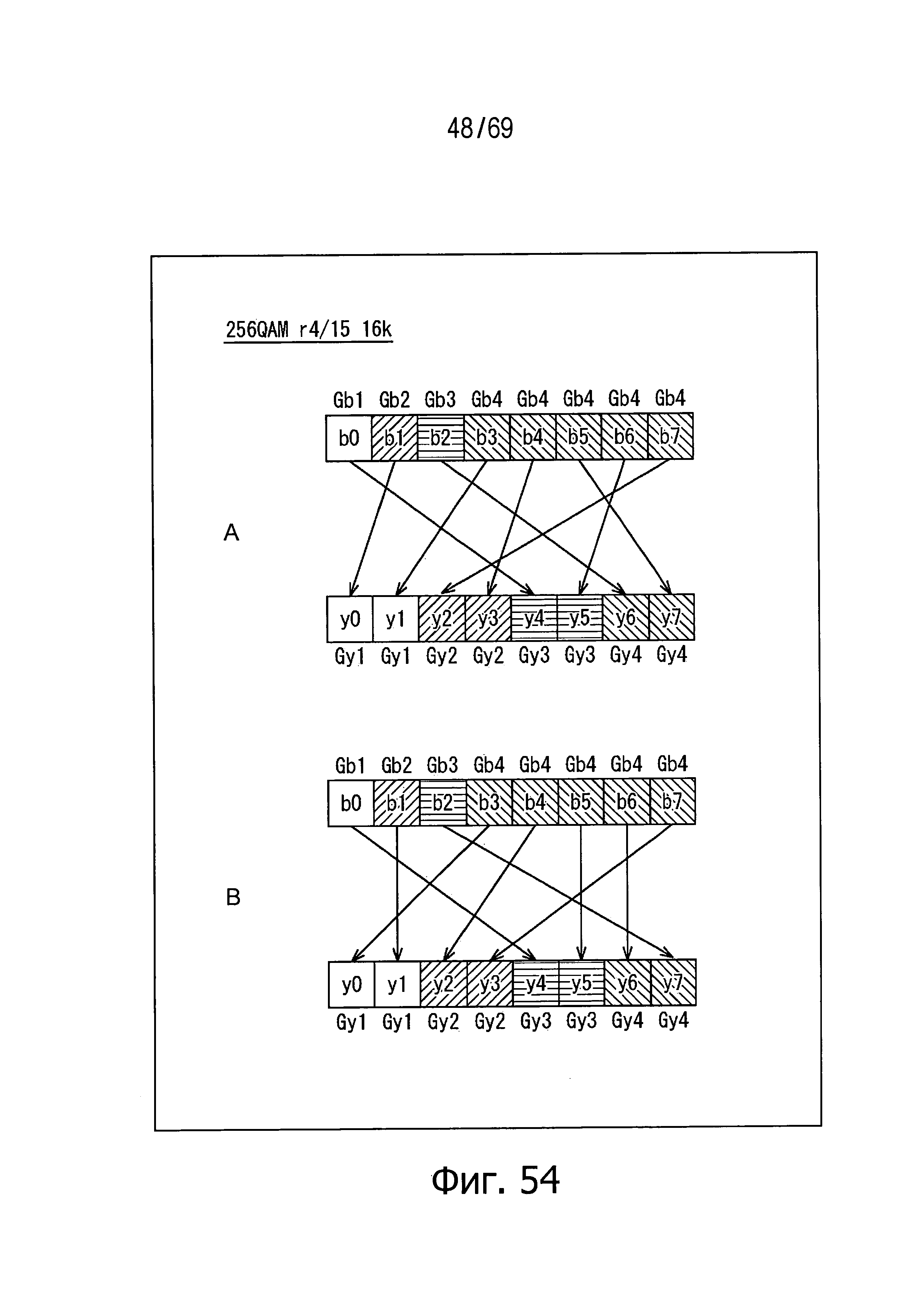

На фиг.52 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15 модулирован 256QAM, и кратное число b равно 1.

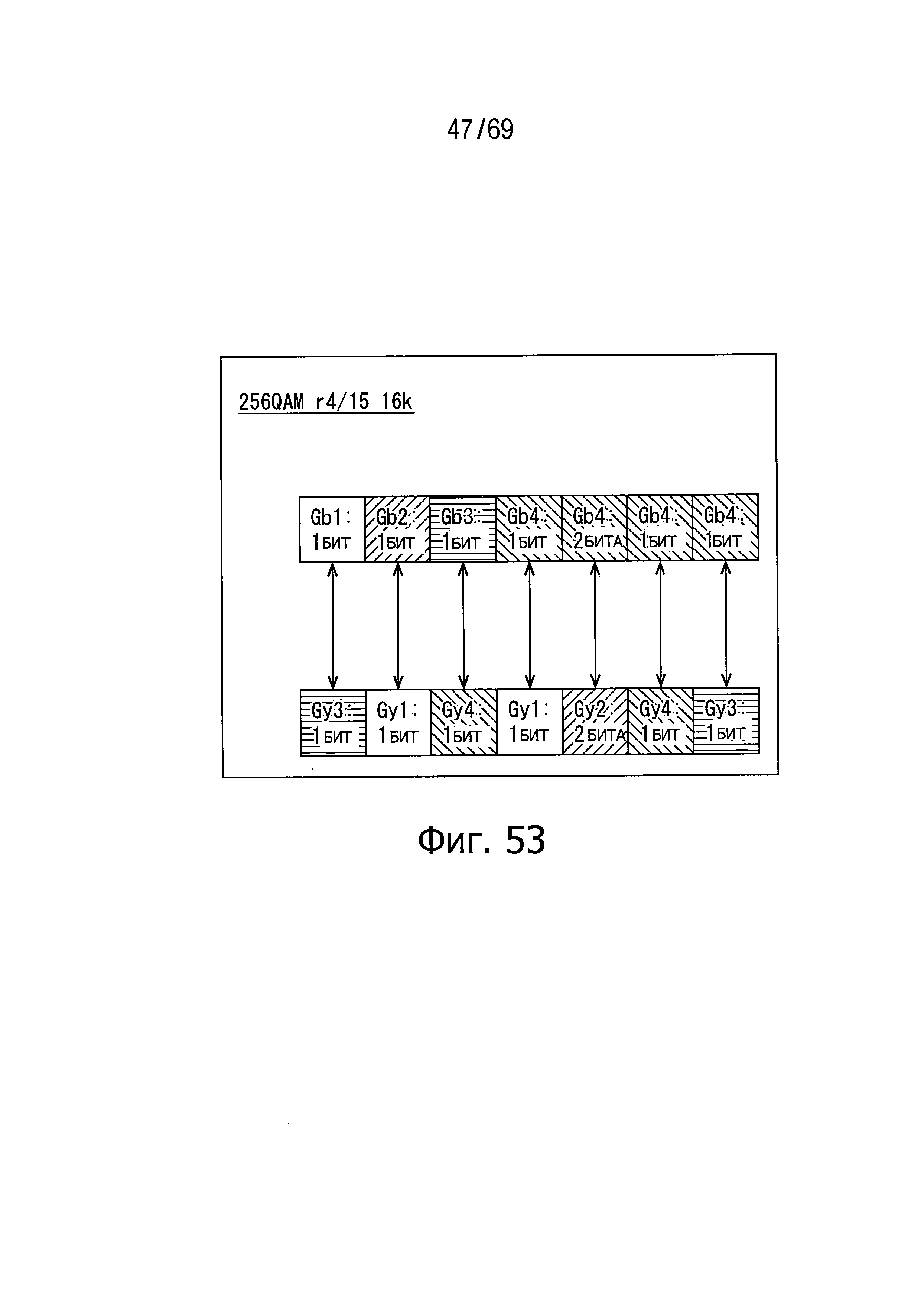

На фиг.53 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15 модулирован 256QAM, и кратное число b равно 1.

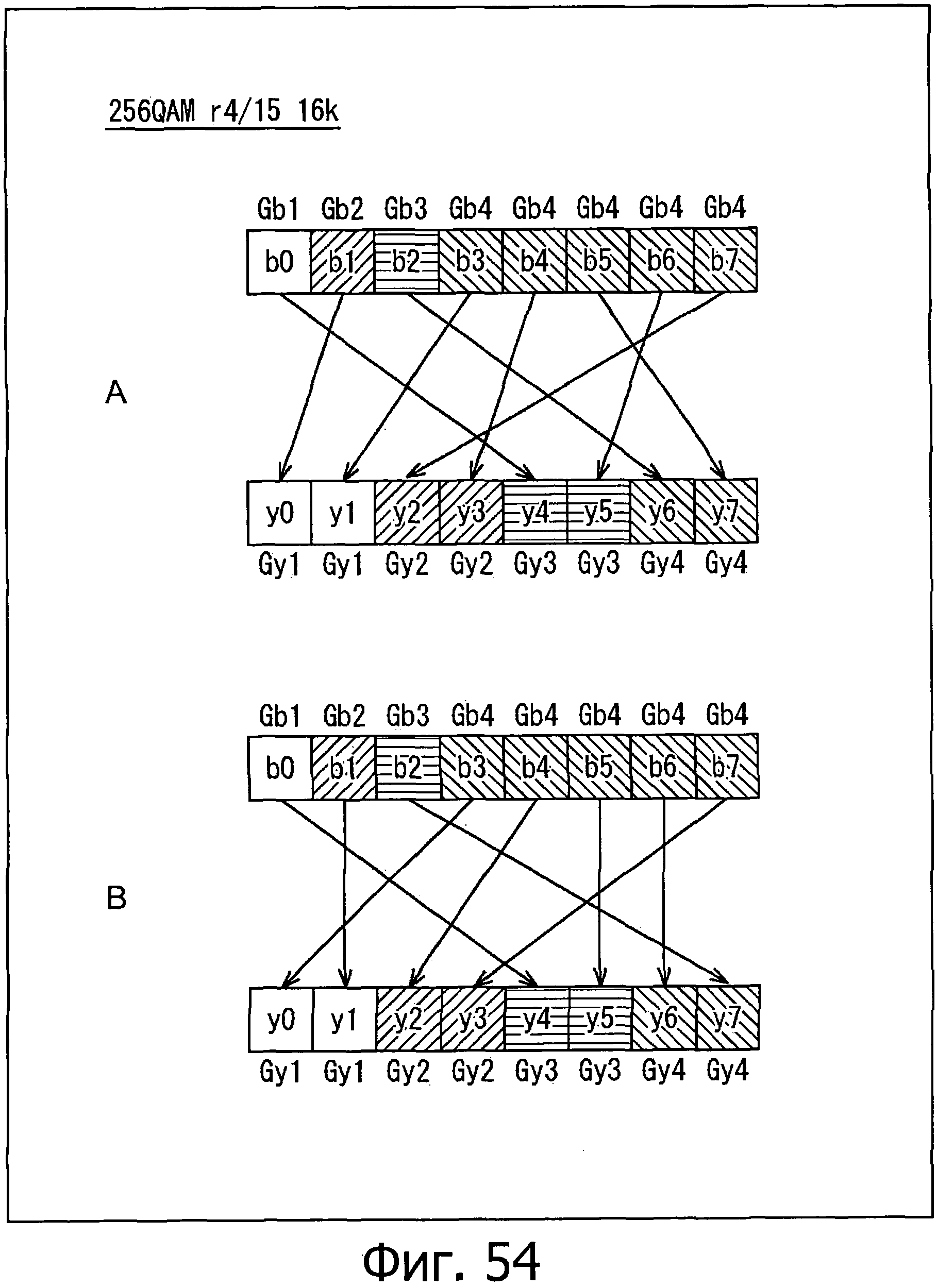

На фиг.54 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15, модулирован 256QAM, и кратное число b равно 1.

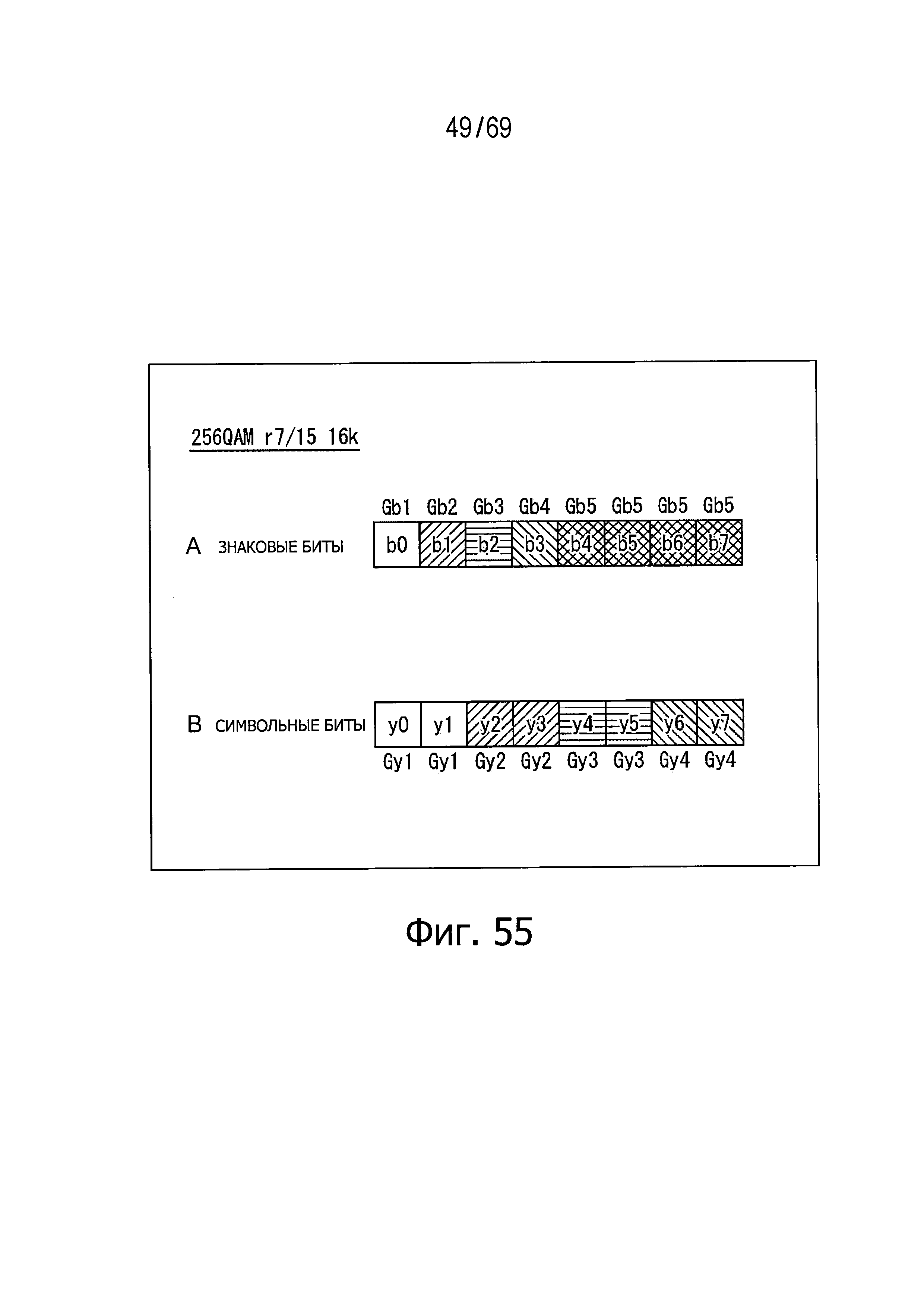

На фиг.55 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

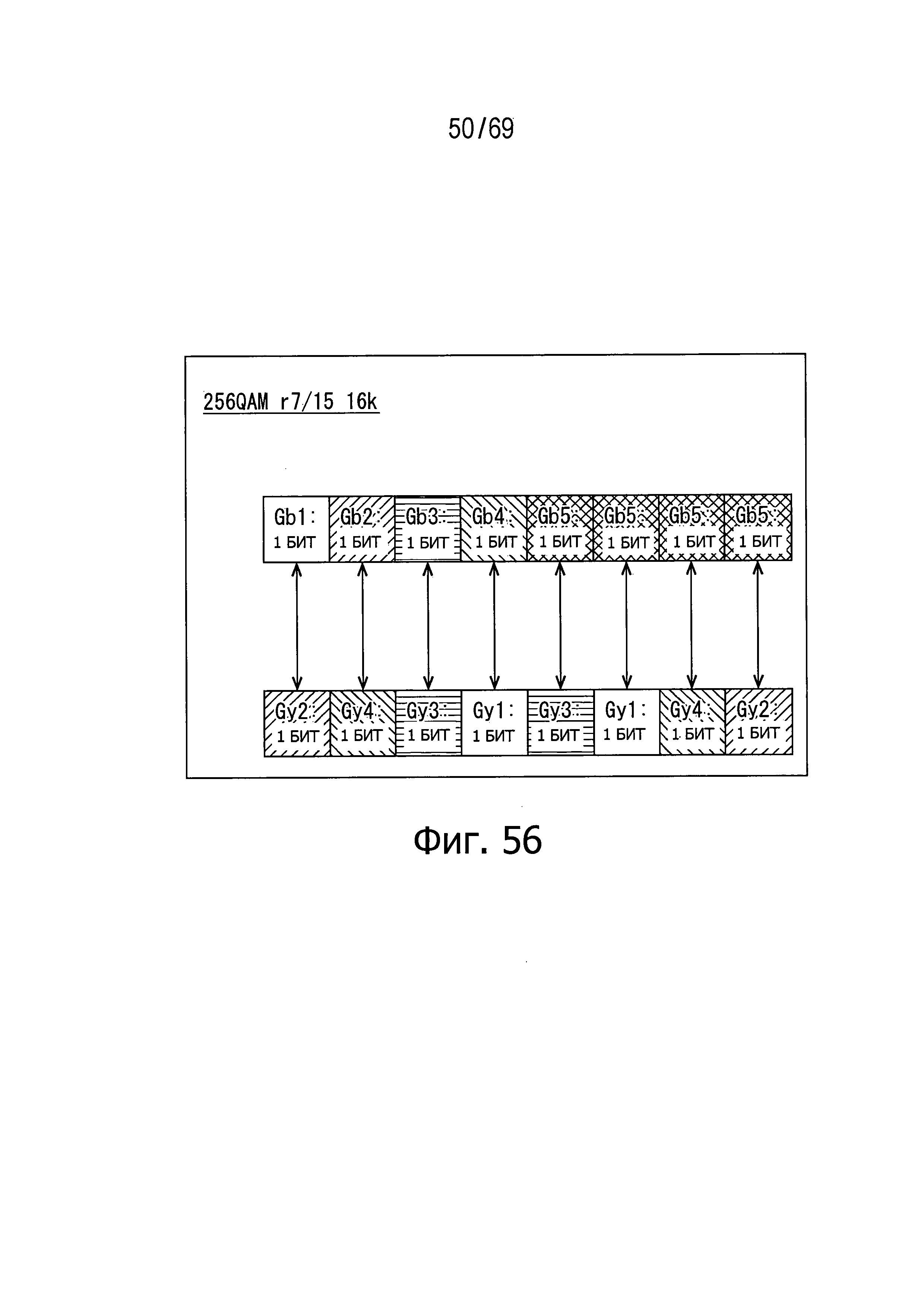

На фиг.56 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.57 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

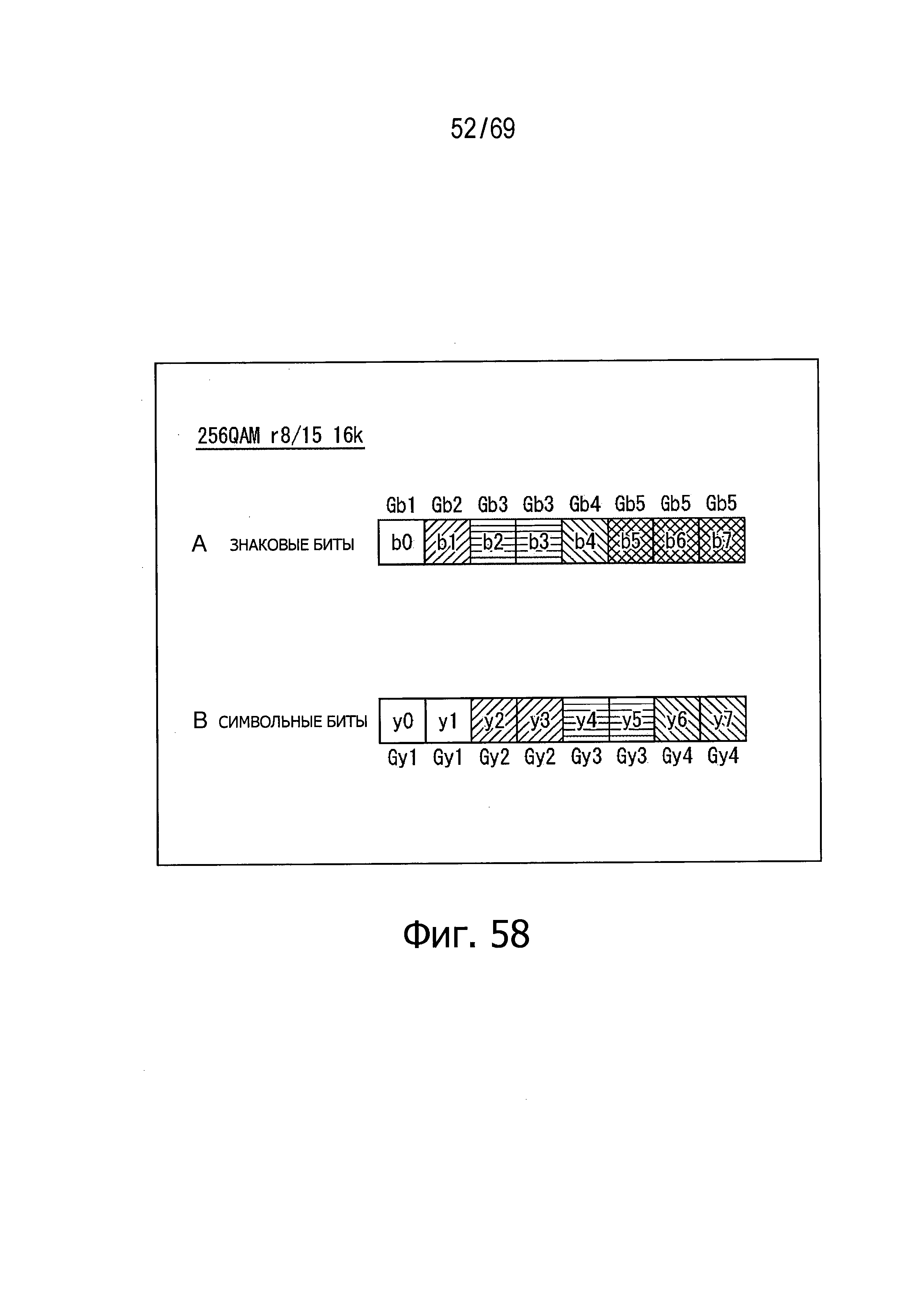

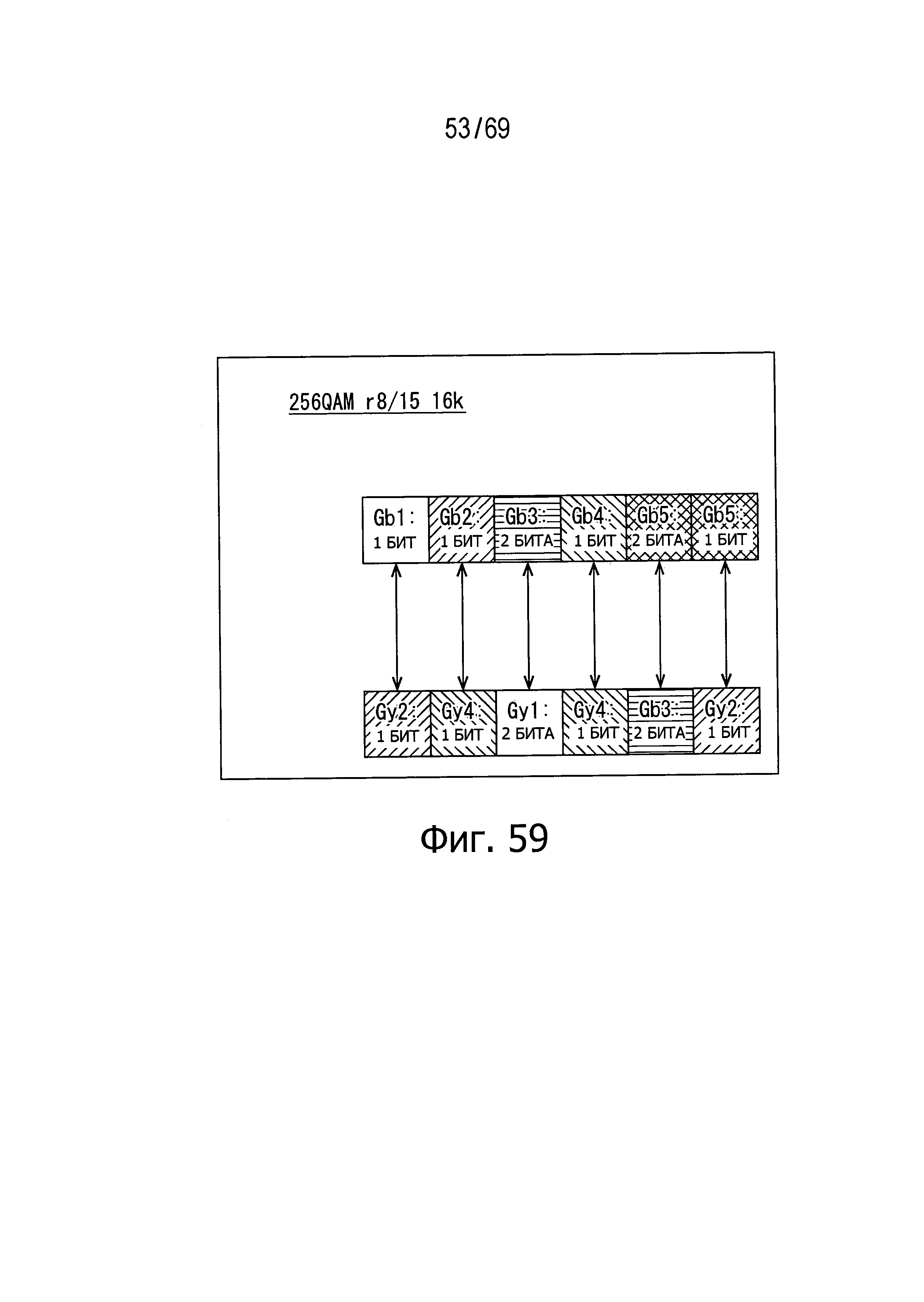

На фиг.58 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 2560AM, и кратное число b равно 1.

На фиг.59 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.60 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 256QAM, и кратное число b равно 1.

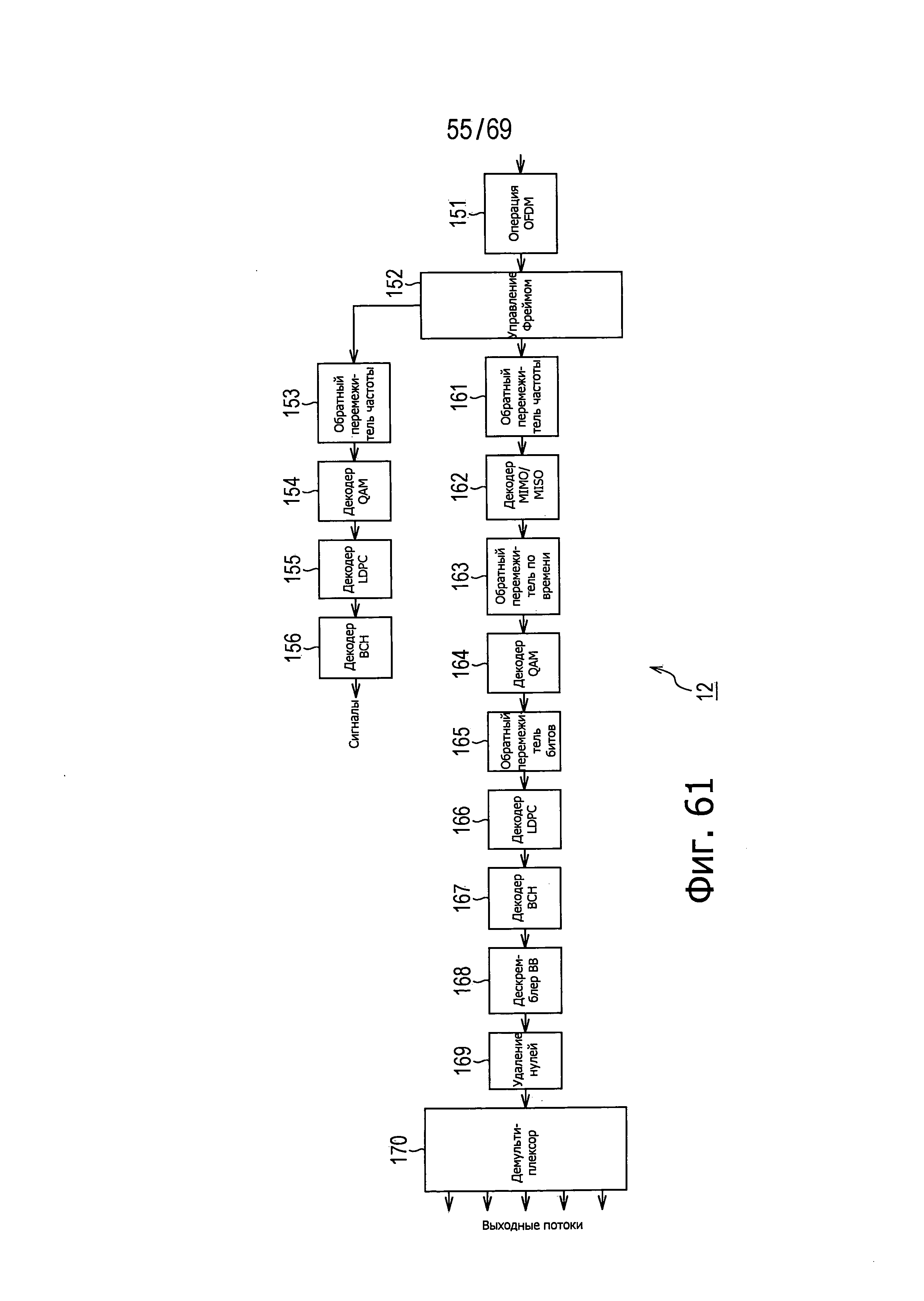

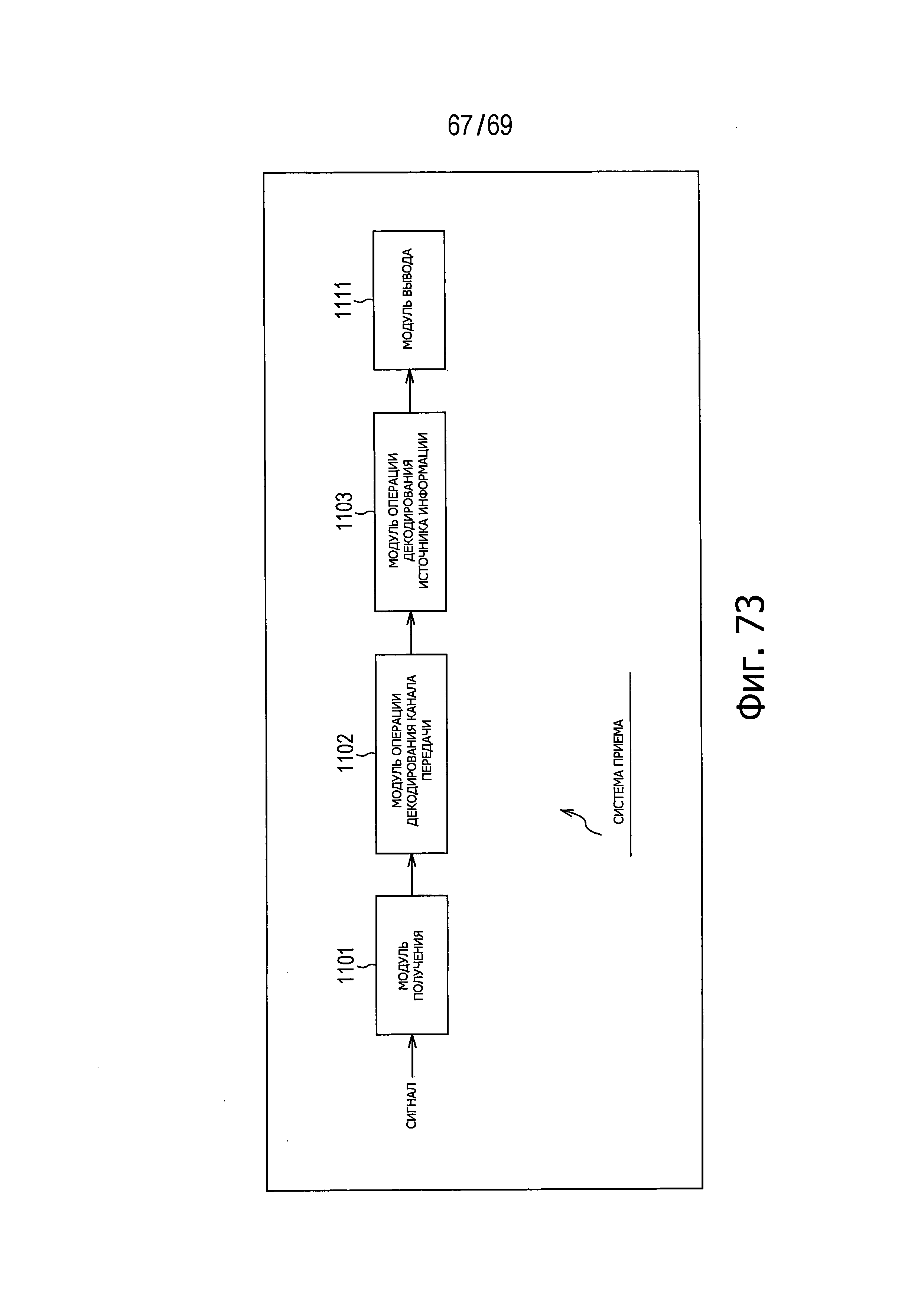

На фиг.61 показана блок-схема, представляющая пример структуры устройства приема 12.

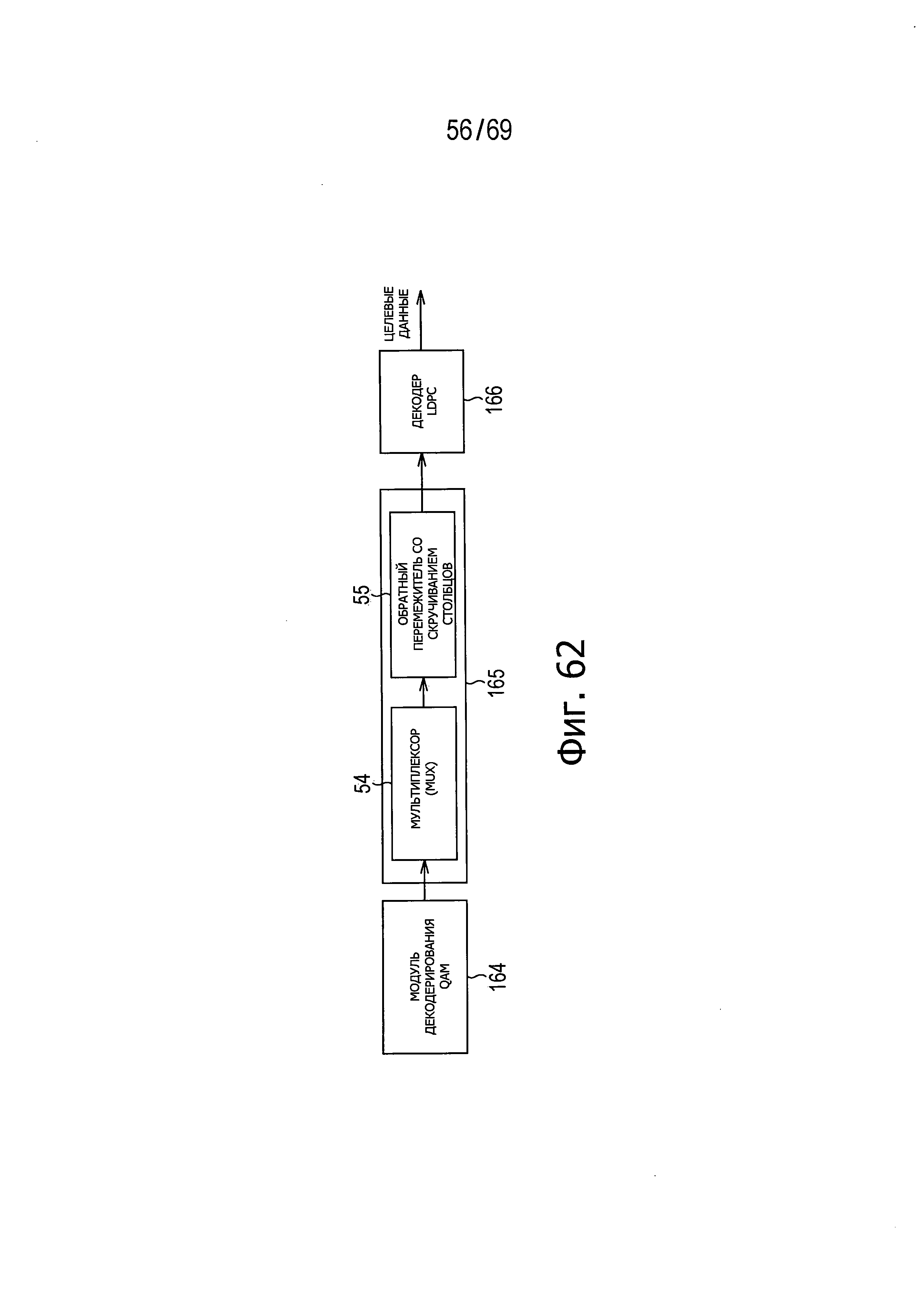

На фиг.62 показана блок-схема, представляющая пример структуры обратного перемежителя 165 битов.

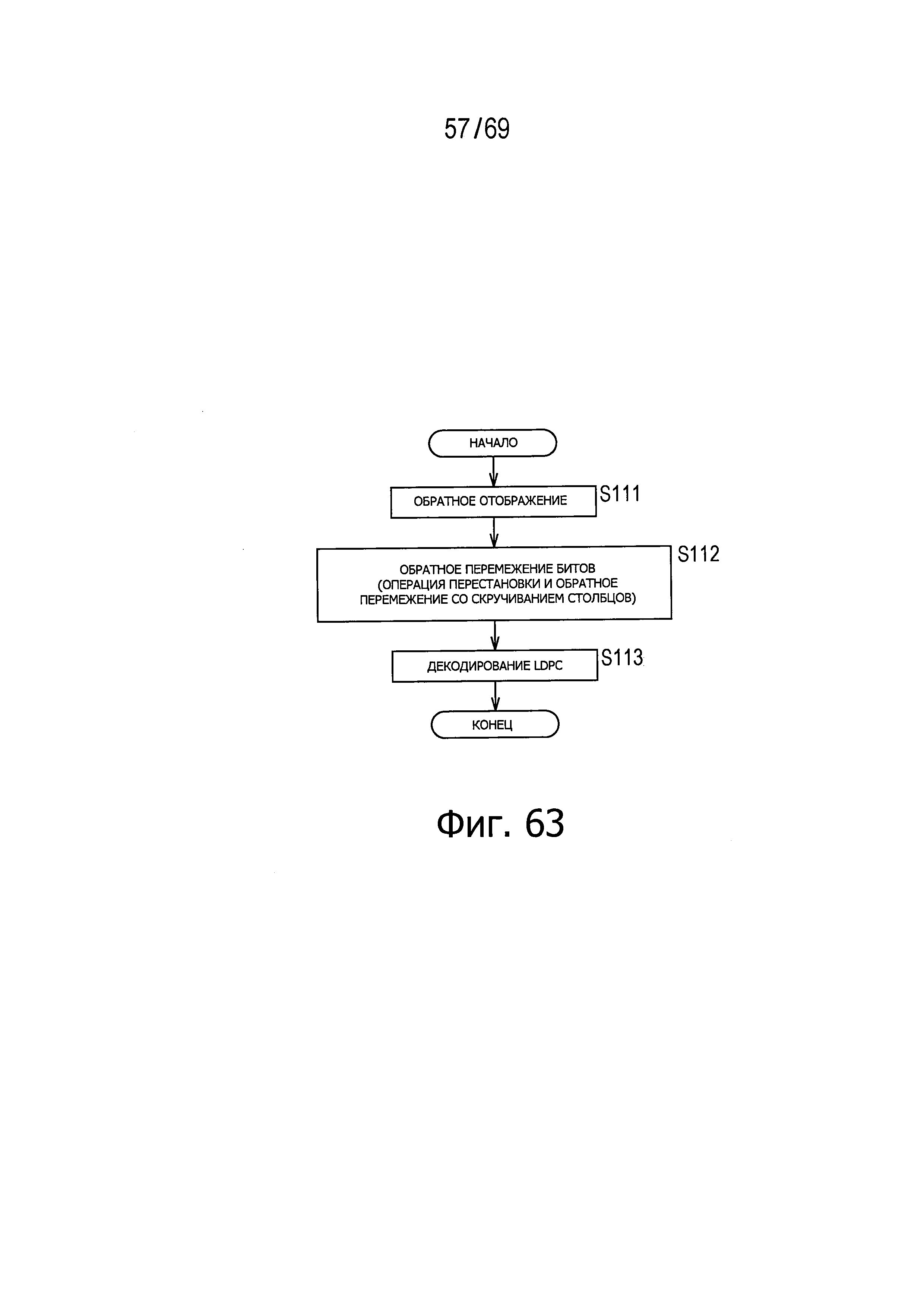

На фиг.63 показана блок-схема последовательности операций для пояснения операций, выполняемых декодером QAM 164, обратным перемежителем 165 битов и декодером 166 LDPC.

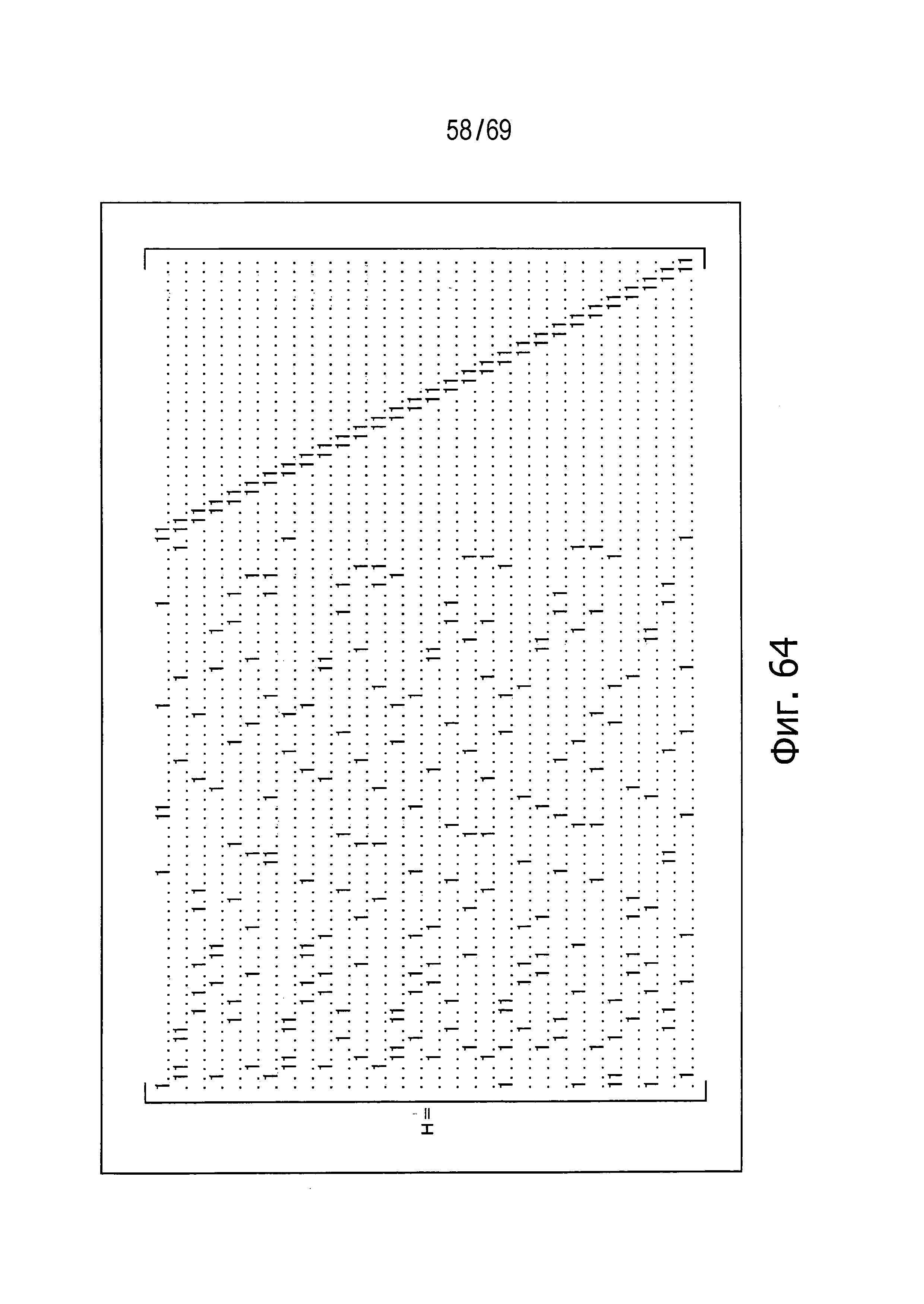

На фиг.64 показана схема, представляющая пример матрицы проверки четности кода LDPC.

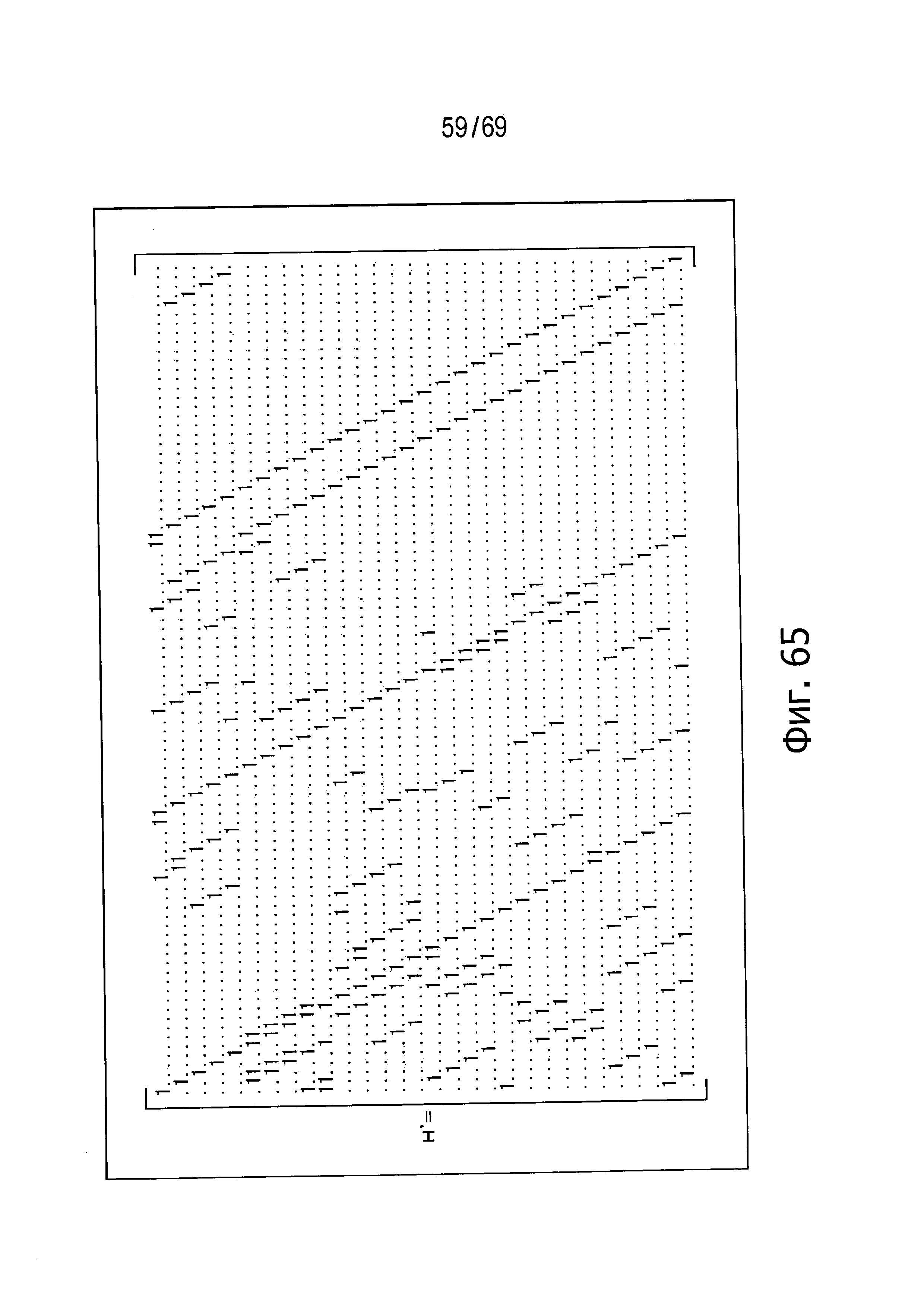

На фиг.65 показана схема, представляющая матрицу (преобразованную матрицу проверки четности), полученную путем выполнения замены строки и замены столбца в матрице проверки четности.

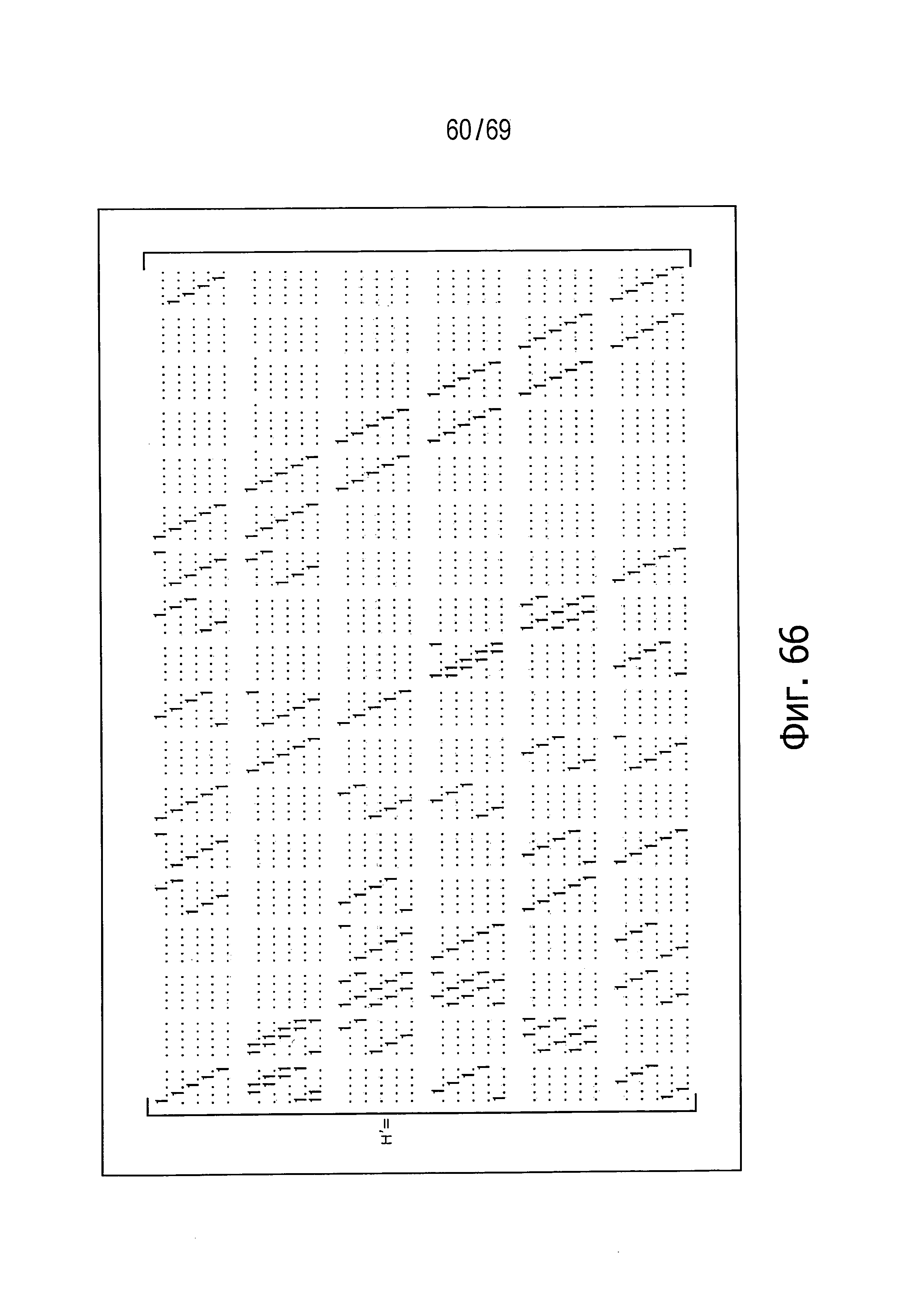

На фиг.66 показана схема, представляющая преобразованную матрицу проверки четности, разделенную на модули 5×5.

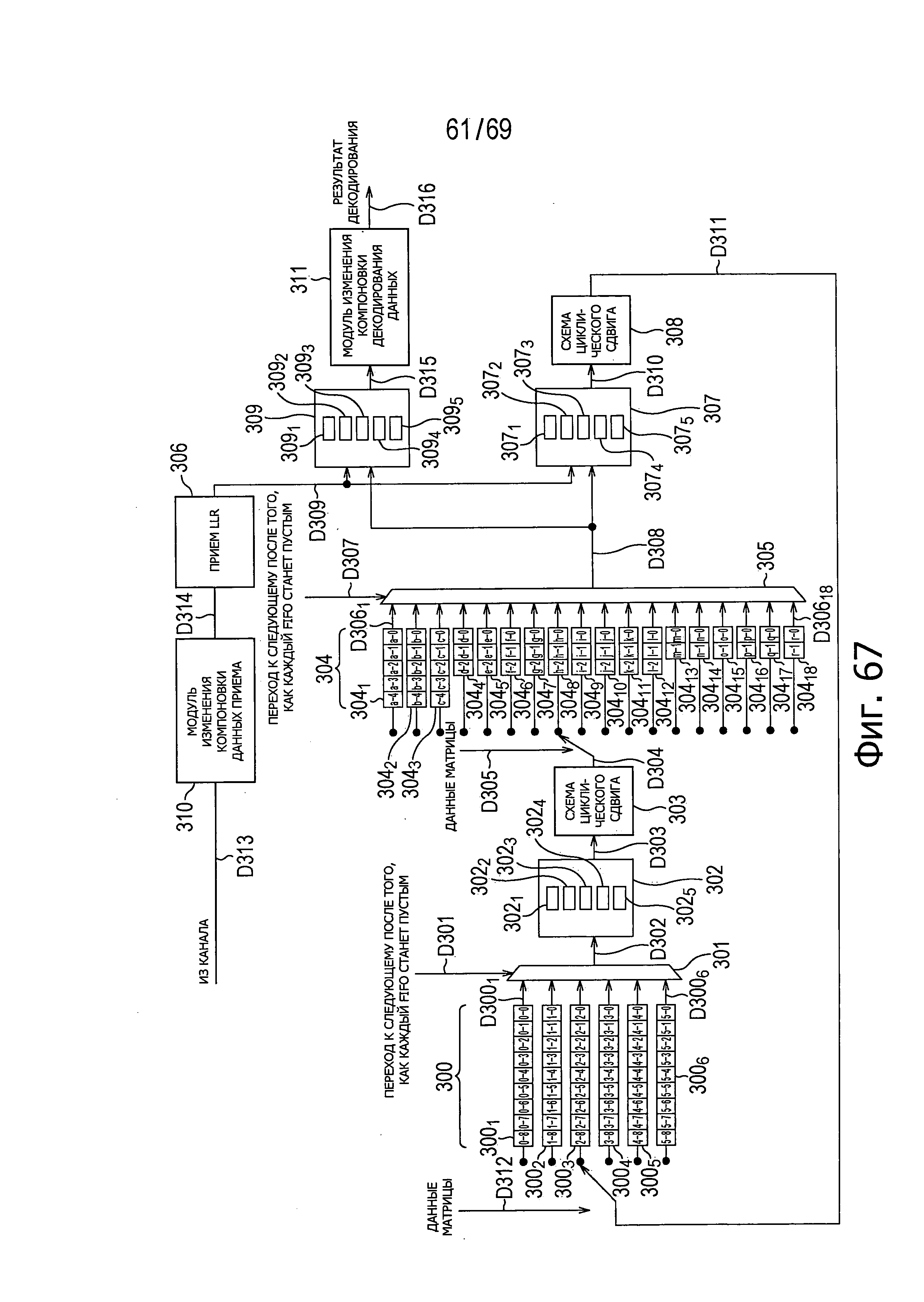

На фиг.67 показана блок-схема, представляющая пример структуры устройства декодирования, которое совместно выполняет Р вычислений узла.

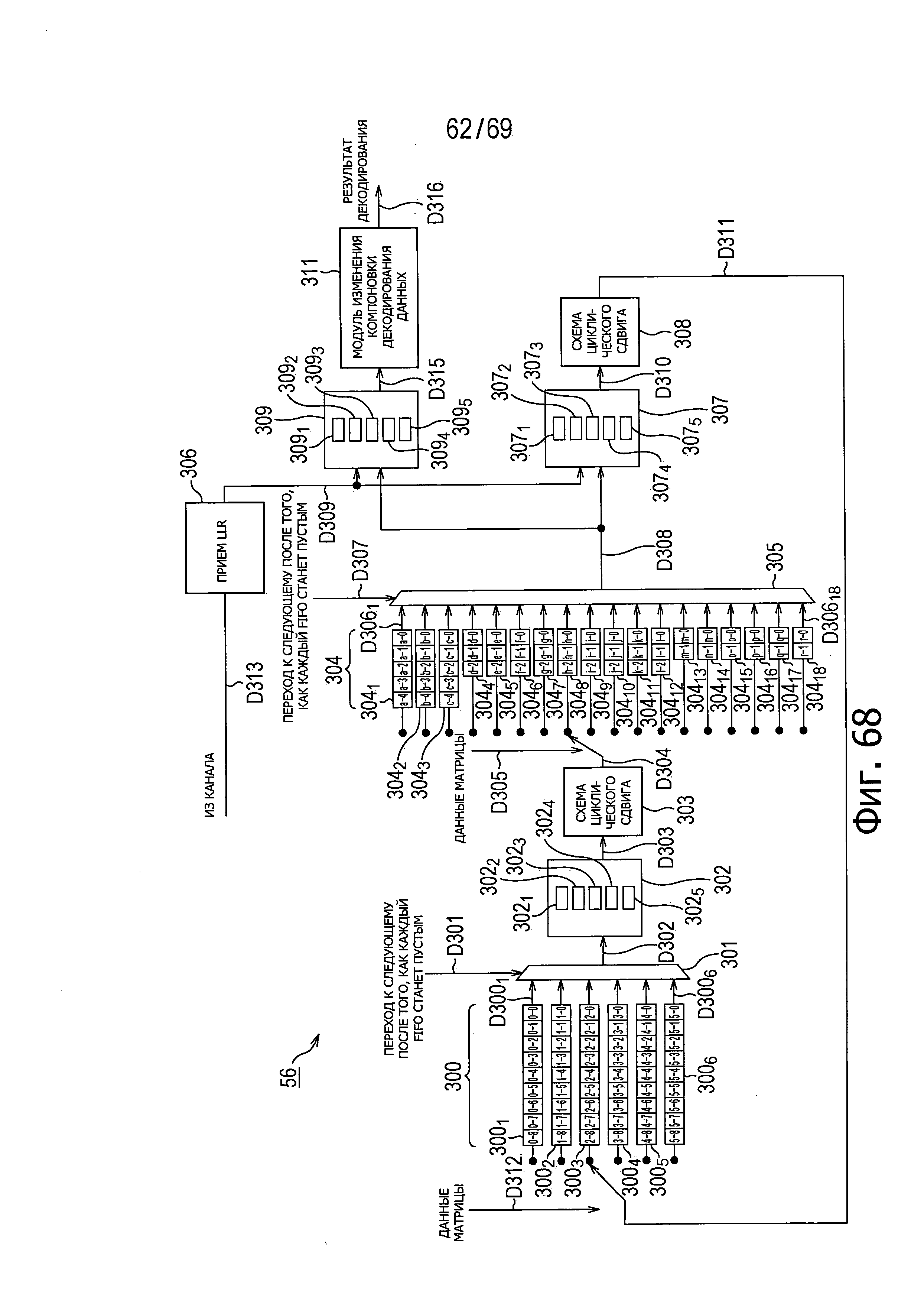

На фиг.68 показана блок-схема, представляющая пример структуры декодера 166 LDPC.

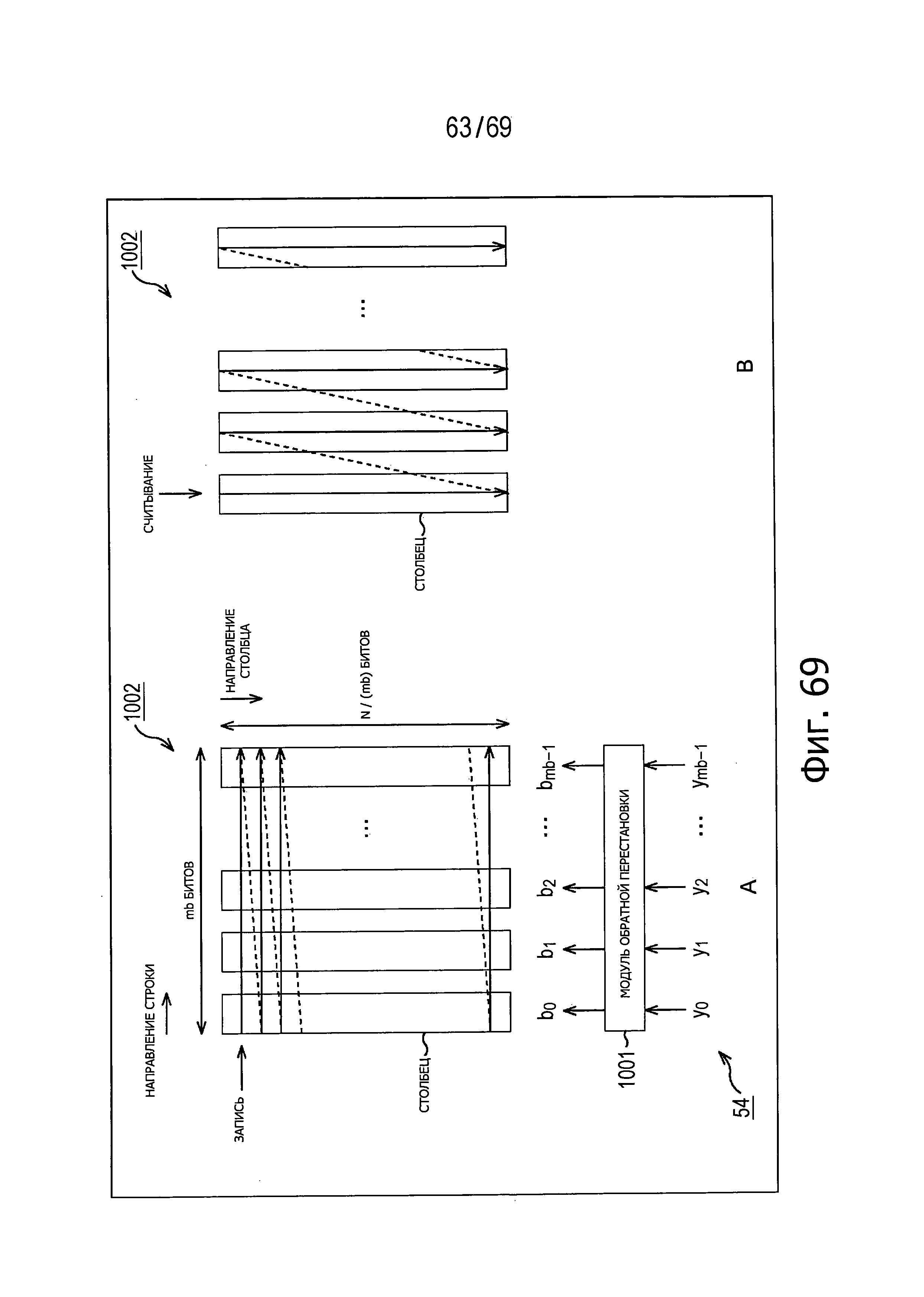

На фиг.69 показана схема для пояснения операции мультиплексора 54 обратного перемежителя 165 бита.

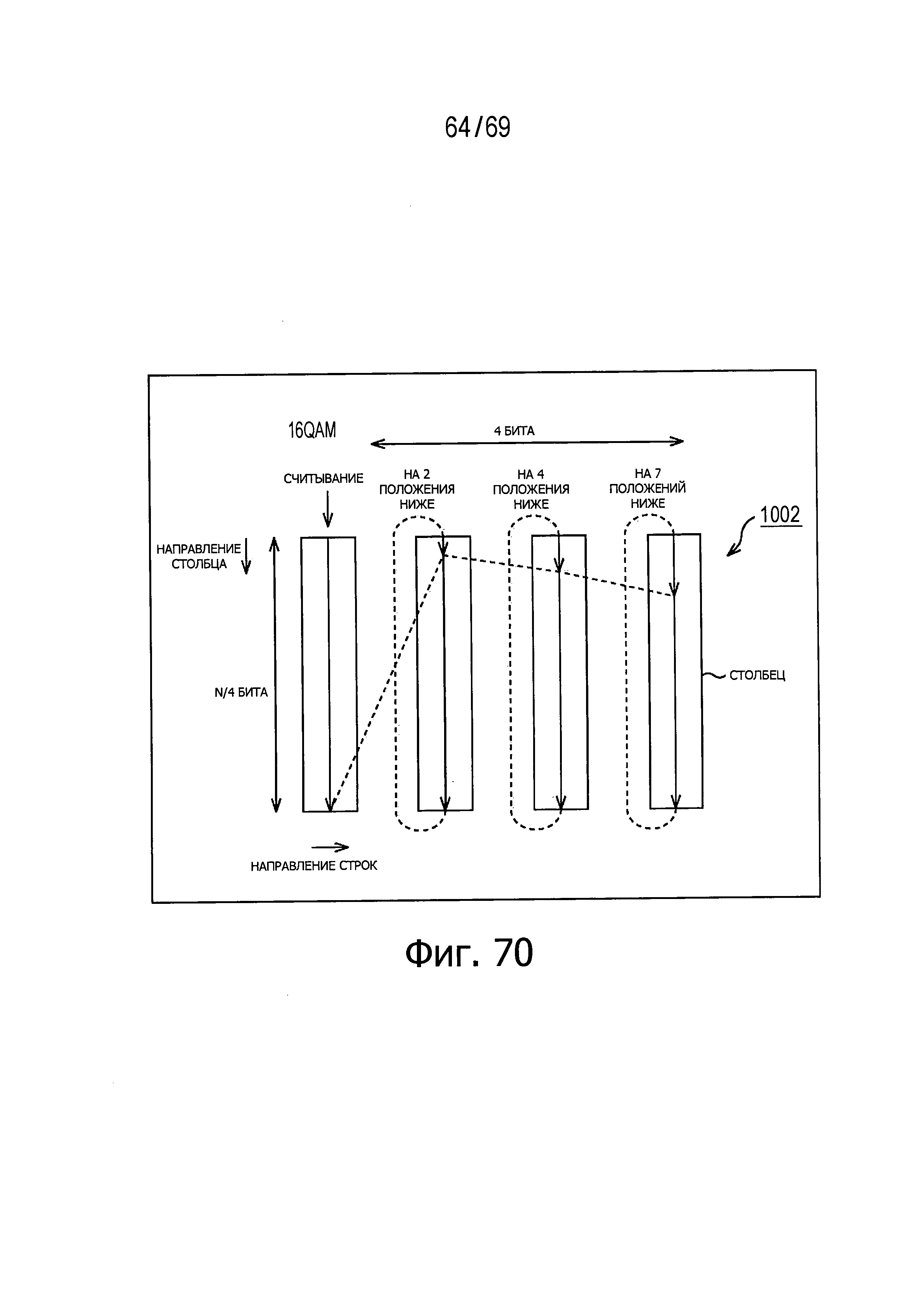

На фиг.70 показана схема для пояснения операции обратного перемежителя 55 со скручиванием столбцов.

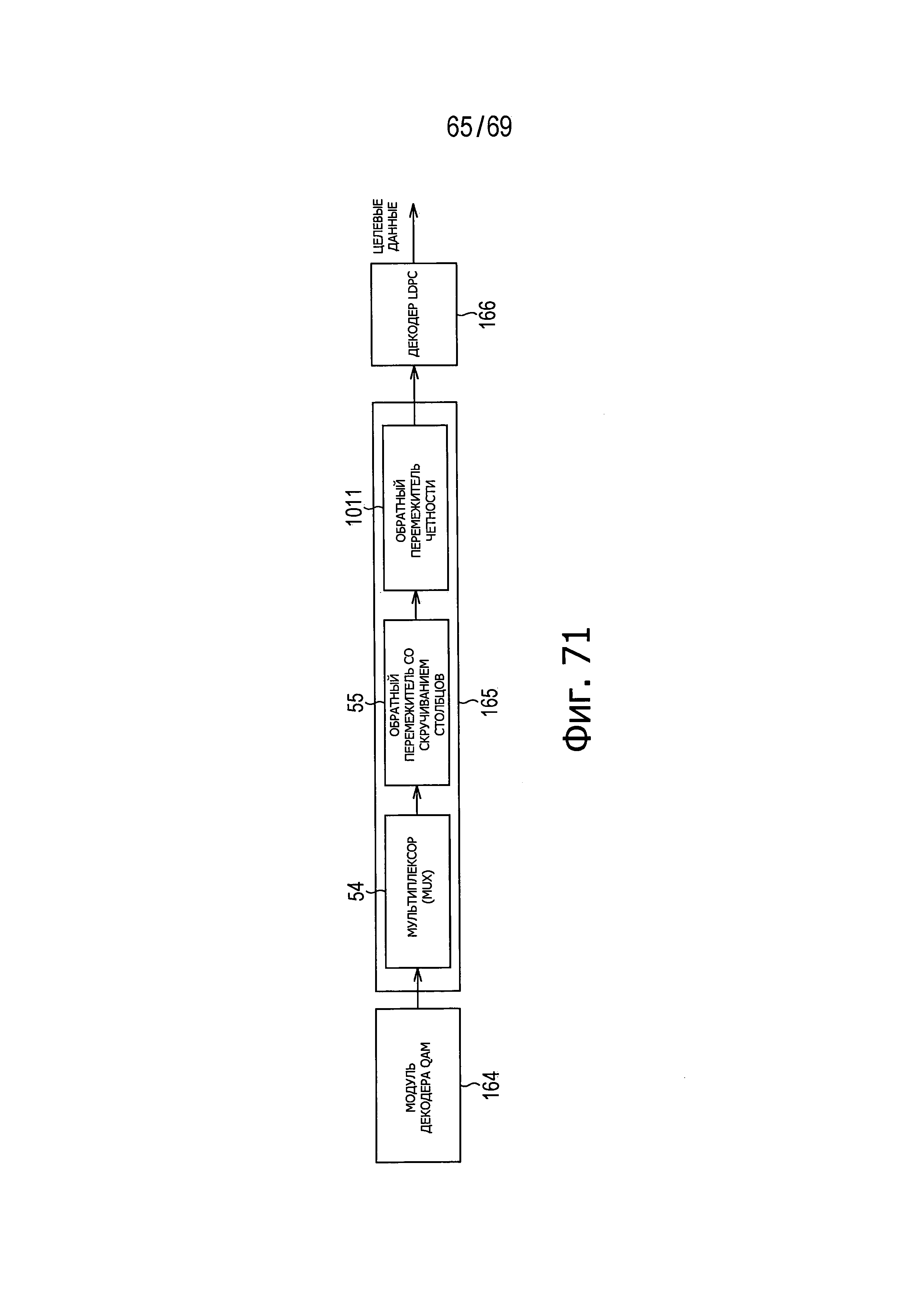

На фиг.71 показана блок-схема, представляющая другую примерную структуру обратного перемежителя 165 битов.

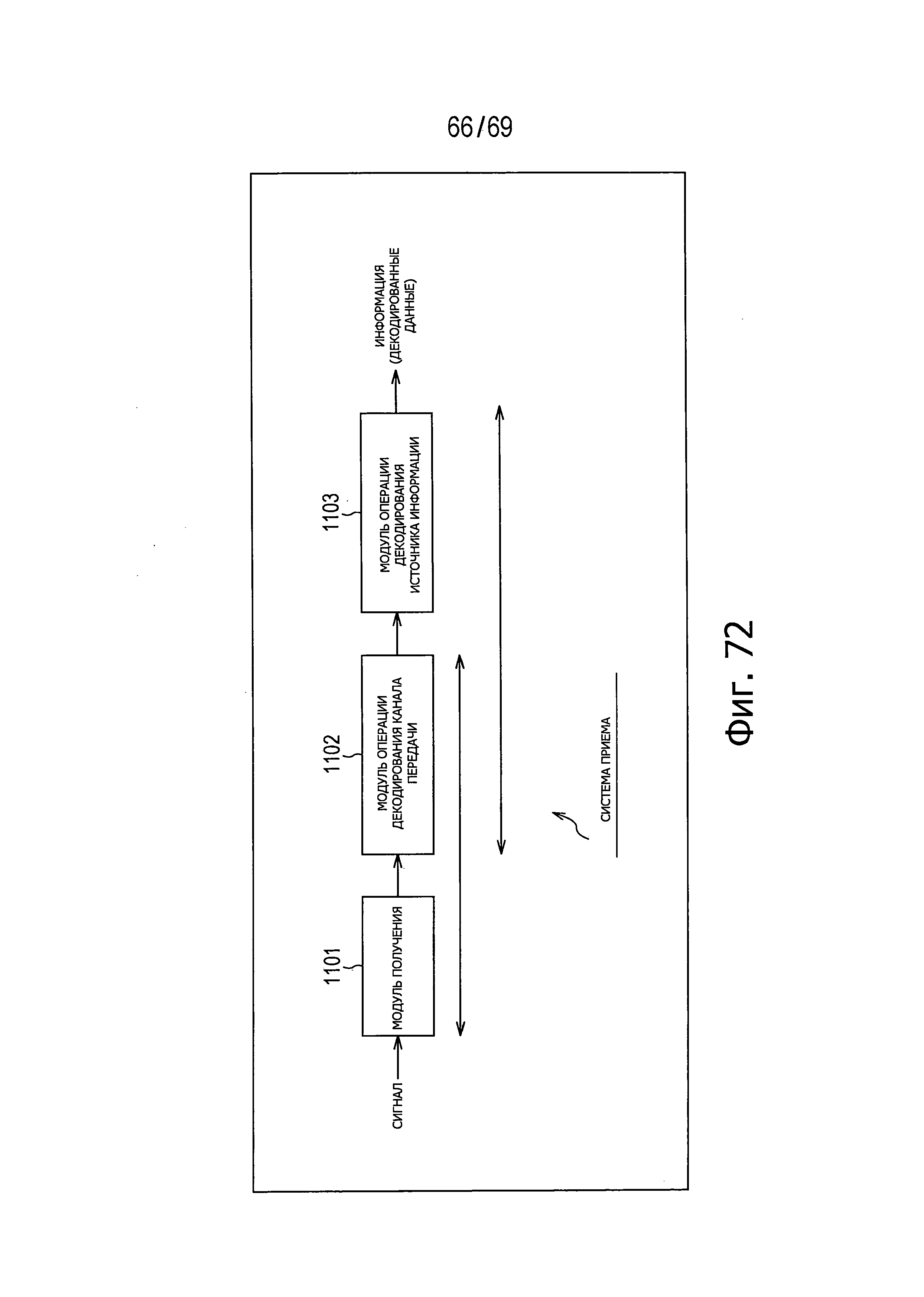

На фиг.72 показана блок-схема, представляющая первую примерную структуру системы приема, в которой может быть применено устройство 12 приема.

На фиг.73 показана блок-схема, представляющая вторую примерную структуру системы приема, в которой может быть применено устройство 12 приема.

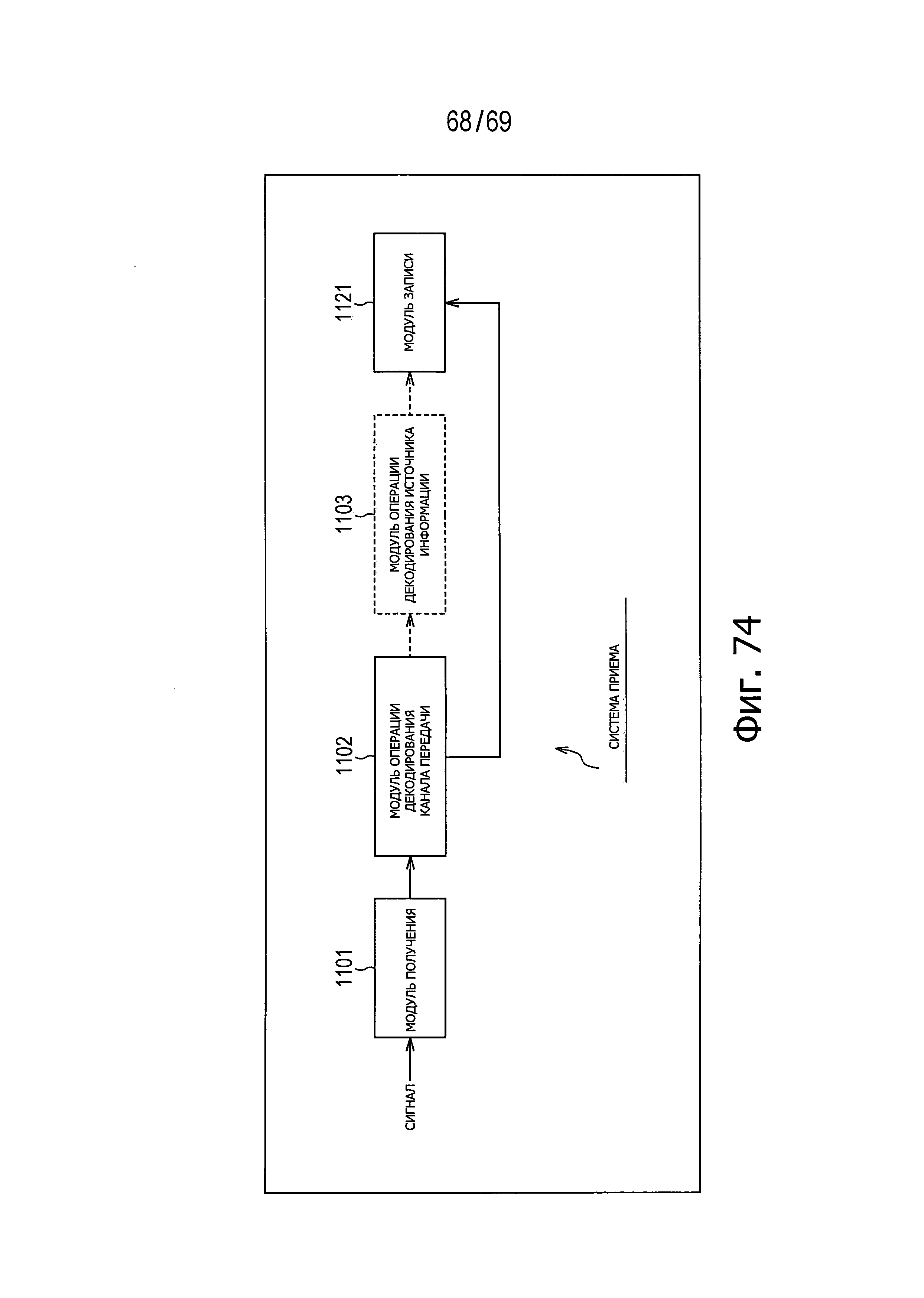

На фиг.74 показана блок-схема, представляющая третью примерную структуру системы приема, в которой может быть применено устройство 12 приема.

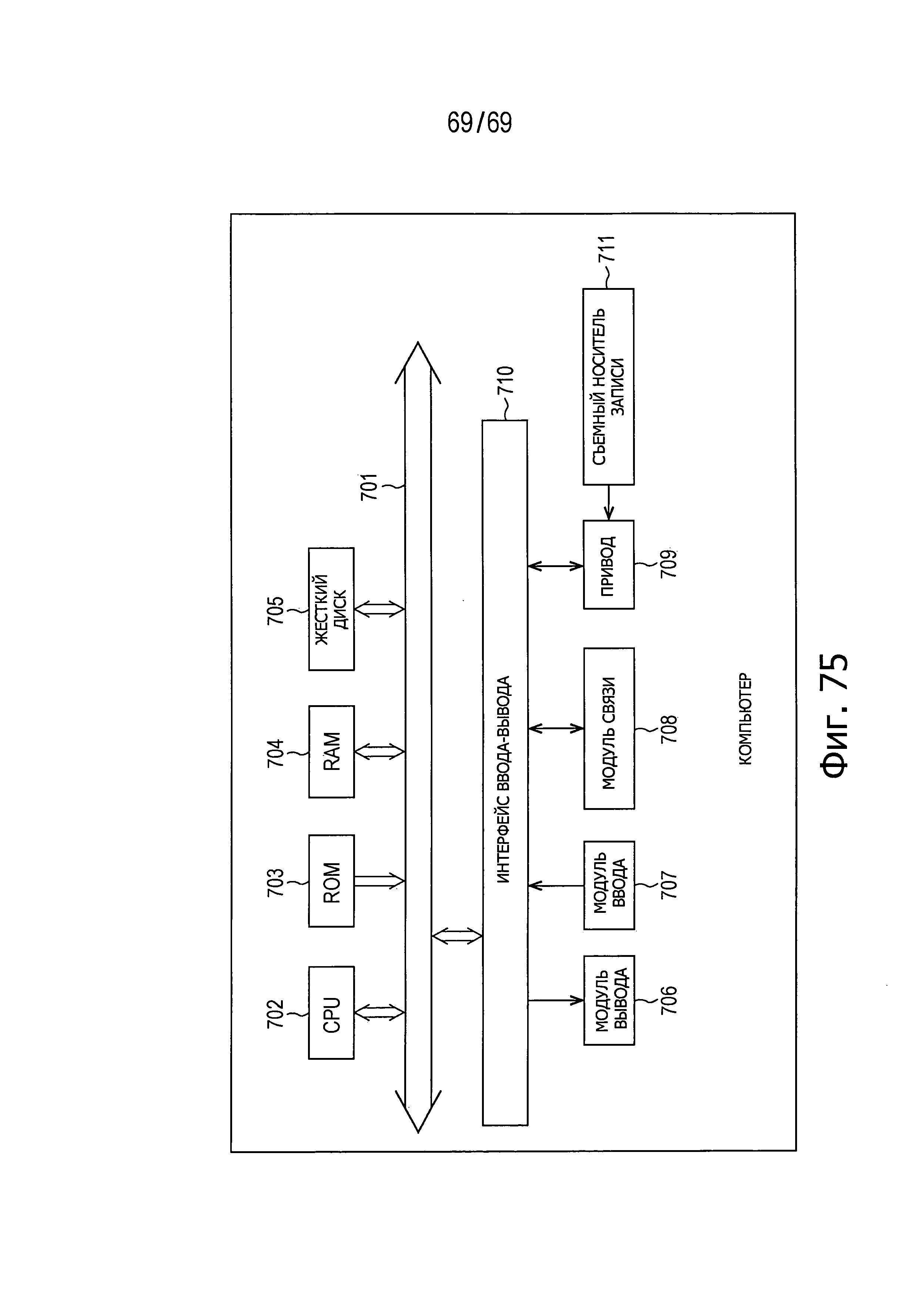

На фиг.75 показана блок-схема, представляющая пример структуры варианта осуществления компьютера, в котором применена настоящая технология.

Подробное описание изобретения

Пример структуры системы передачи, в которой применяется настоящая технология

На фиг.7 показан пример структуры варианта осуществления системы передачи, в которой применяется настоящая технология ("система" означает логическую сборку устройств, и устройства, которые представляют данную структуру, не обязательно размещены в одном том же корпусе).

На фиг.7 показана система передачи, которая включает в себя устройство 11 передачи и устройство 12 приема.

Устройство 11 передачи выполняет передачу (широковещательную) (доставку) шоу, предназначенных для стационарных оконечных устройств и портативных оконечных устройств. В частности, устройство 11 передачи кодирует целевые данные передачи, такие, как данные изображения и аудиоданные, как шоу, предназначенные для стационарных оконечных устройств и портативных оконечных устройств, в коды LDPC, и передает эти коды LDPC через канал 13, например, по наземным волнам.

Устройство 12 приема представляет собой, например, портативное оконечное устройство. Устройство 12 приема принимает коды LDPC, переданные от устройства 11 передачи через канал 13, и декодирует коды LDPC в целевые данные перед выводом целевых данных.

Здесь коды LDPC, используемые в системе передачи, показанной на фиг.7, известны своей чрезвычайно высокой производительностью в каналах AWGN (аддитивный белый Гауссов шум).

Однако пакетные ошибки и удаления могут возникать в канале 13 наземных волн и т.п. Например, в системе OFDM (мультиплексирование с ортогональным разделением частоты) возникают моменты времени, когда мощность определенного символа становится равной нулю (удаление), в соответствии с задержкой эхо-сигнала (по-другому пути, чем основной путь) в среде с многолучевым распространением радиоволн, в которой D/U (отношение желательного/нежелательного) составляет 0 дБ (мощность нежелательного или эхо сигнала равна мощности желательного или сигнала в основном канале передачи).

Кроме того, когда D/U составляет 0 дБ, в случае дрожания сигнала (канал, в котором задержка равна нулю, и который имеет эхо-сигнал на Допплеровской частоте, добавленной к сигналу), мощность всех символов OFDM в определенные моменты времени может становиться равной нулю (удаление) из-за Допплеровской частоты.

Кроме того, на стороне устройства 12 приема, в некоторых случаях, пакетные ошибки возникают, из-за условий на линии от модуля приема (не показан), такого как антенна, которая принимает сигналы от устройства 11 передачи, до устройства 12 приема, и нестабильности источника питания устройства 12 приема.

При декодировании кода LDPC, с другой стороны, в строке матрицы Н проверки четности или в переменном узле, соответствующем знаковому биту кода LDPC, вычисление переменного узла, показанного в уравнении (1), включающее в себя добавление (принятого значения u0i для) знакового бита кода LDPC, выполняют, как уже описано со ссылкой на фиг.5. Поэтому, если возникает ошибка в знаковом бите, используемом при вычислении переменного узла, ухудшается точность получаемого в результате сообщения.

При декодировании кода LDPC вычисление проверочного узла, показанного в уравнении (7), выполняют в проверочном узле, используя сообщения, определенные в переменных узлах, подключенных к проверочному узлу. Поэтому, если количество проверочных узлов, которое приводит к появлению одновременных ошибок (включая в себя стирания) в подключенных переменных узлах (или в знаковых битах кодов LDPC, соответствующих переменным узлам), становится большим, характеристики декодирования ухудшаются.

Таким образом, когда одновременно возникает удаление в двух или больше переменных узлах, подключенных к проверочному узлу, проверочный узел возвращает во все переменные узлы сообщение, указывающее, что вероятность того, что значения равны "0", и вероятность того, значения равны "1", равны друг другу. В этом случае, проверочный узел, который возвращает сообщение, указывающее равные вероятности, не способствует одной из операции декодирования (один набор вычислений переменного узла и вычислений проверочного узла). В результате, количество повторений операции декодирования должно быть увеличено, и характеристики декодирования ухудшаются. Кроме того, увеличивается потребление энергии устройством 12 приема, которое декодирует коды LDPC.

С учетом этого, система передачи данных, показанная на фиг.7, улучшает устойчивость к пакетным ошибкам и удалениям при поддержании высоких рабочих характеристик в каналах AWGN.

Пример структуры устройства 11 передачи

На фиг.8 показана блок-схема, представляющая пример структуры устройства 11 передачи, показанного на фиг.7.

В устройстве 11 передачи один или более входных потоков, как целевые данные, подают на модуль 111 адаптации режима/мультиплексора.

Модуль 111 адаптации режима/мультиплексора выполняет выбор режима и мультиплексирует один или более входных потоков, подаваемых на него. Полученные в результате данные подают на заполнитель 112.

Заполнитель 112 выполняет необходимое заполнение нулями (вставку нулей) для данных, подаваемых от модуля 111 адаптации режима/мультиплексора, и подает полученные в результате данные на ВВ скремблер 113.

ВВ скремблер 113 выполняет операцию распределения энергии для данных, подаваемых от заполнителя 112, и подает полученные в результате данные на кодер 114 BCH.

Кодер 114 ВСН выполняет кодирование ВСН для данных, подаваемых от скремблера 113 ВВ, и подает полученные в результате данные в качестве целевых данных LDPC, которые должны быть подвергнуты кодированию LDPC, на кодер 115 LDPC.

Для целевых данных LDPC, подаваемых от кодера 114 ВСН, кодер 115 LDPC выполняет кодирование LDPC, в соответствии с матрицей проверки четности, имеющей лестничную структуру, в матрице четности, соответствующей битам четности кодов LDPC, и выводит код LDPC, имеющий целевые данные LDPC, в качестве информационного бита.

Таким образом, кодер 115 LDPC выполняет кодирование LDPC для кодирования целевых данных LDPC в код LDPC, такой, как код LDPC, установленный в стандартах DVB-T.2, и выводит полученный в результате код LDPC.

В соответствии со стандартами DVB-T.2, коды LDPC, установленные в стандартах DVB-S.2, используются, если только длина кода равна 16200 битов, и скорость кода составляет 3/5. Коды LDPC, установленные в стандартах DVB-T.2, представляют собой коды IRA (неравномерное накопление с повторением), и матрицы четности в матрицах проверки четности кодов LDPC имеют лестничную структуру. Матрицы четности и лестничные структуры будут описаны ниже. Коды IRA раскрыты, например, в публикации "Irregular Repeat-Accumulate Codes," Н. Jin, A. Khandekar, and R.J. McEliece, in Proceedings of 2nd International Symposium on Turbo Codes and Related Topics, pp.1-8, Sept. 2000.

Код LDPC, который выводят от кодера 115 LDPC, подают на перемежитель 116 битов.

Перемежитель 116 битов выполняет перемежение последнего описанного бита для кода LDPC, подаваемого от кодера 115 LDPC, и код LDPC, подаваемый в перемежение битов, подают на кодер 117 QAM.

Кодер 117 QAM выполняет ортогональную модуляцию (многоуровневую модуляцию) для кода LDPC, подаваемого от перемежителя 116 битов, путем отображения каждого модуля знакового бита (каждого модуля символа) одного или более битов кода LDPC в точку сигнала, представляющую один символ ортогональной модуляции.

Таким образом, кодер 117 QAM выполняет ортогональную модуляцию путем отображения кода LDPC, подаваемого от перемежителя 116 битов, в сигнальные точки, которые определены способом модуляции для ортогональной модуляции, выполняемой для кода LDPC в плоскости I-Q (совокупность I-Q), установленной осью I, указывающей компонент I одной фазы, в качестве колебаний несущей, и осью Q, указывающий компонент Q, перпендикулярный волнам несущей.

Здесь примеры способов модуляции для ортогональной модуляции, выполняемой кодером 117 QAM, включают в себя способы модуляции, установленные в стандартах DVB-T, такие как QPSK (квадратурная манипуляция со сдвигом фазы), 16QAM (квадратурная амплитудная модуляция), 64QAM, 256QAM, 1024QAM и 4096QAM. Способ модуляции, используемый при ортогональной модуляции на кодере 117 QAM, устанавливают заранее, например, в соответствии с операцией оператора устройства 11 передачи. Кодер 117 QAM также выполняет другую ортогональную модуляцию, такую как 4РАМ (импульсно-амплитудная модуляция).

Данные, получаемые в результате операции, выполняемой кодером 117 QAM (символы, отображенные на точки сигнала), подают на перемежитель 118 по времени.

Перемежитель 118 по времени выполняет перемежение по времени (перемежение в направлении времени) для каждого модуля символа данных (символов), подаваемых от кодера 117 QAM, и подает полученные в результате данные на кодер 119 MISO/MIMO.

Кодер 119 MISO/MIMO выполняет кодирование пространство-время для данных (символов), подаваемых от перемежителя 118 по времени, и подает полученные в результате данные на перемежитель 120 по частоте.

Перемежитель 120 по частоте выполняет перемежение по частоте (перемежение в направлении частоты) для каждого модуля символа данных (символов), подаваемых от кодера 119 MISO/MIMO, и подает полученные в результате данные на модуль 131 построителя фреймов/выделения ресурсов.

В то же время, данные управления (сигналы) для управления передачей, такие как преамбула, называемая L1, подают на кодер 121 ВСН.

Аналогично кодеру 114 ВСН, кодер 121 ВСН выполняет кодирование ВСН для данных управления, подаваемых на него, и подает полученные в результате данные на кодер 122 LDPC.

Аналогично кодеру 115 LDPC, кодер 122 LDPC выполняет кодирование LDPC для данных, подаваемых, в качестве целевых данных LDPC, от кодера 121 ВСН, и подает полученный в результате код LDPC на кодер 123 QAM.

Так же, как и кодер 117 QAM, кодер 123 QAM выполняет ортогональную модуляцию для кода LDPC, подаваемого от кодера 122 LDPC, путем отображения каждого модуля знакового бита (каждого модуля символов) одного или более битов кода LDPC на точку сигнала, представляющую один символ ортогональной модуляции, и подает полученные в результате данные (символы) на перемежитель 124 по частоте.

Аналогично перемежителю 120 по частоте, перемежитель 124 по частоте выполняет перемежение по частоте каждого модуля символа данных (символов), подаваемых от кодера 123 QAM, и подает полученные в результате данные на модуль 131 построителя фреймов/выделения ресурсов.

Модуль 131 построителя фреймов/выделения ресурсов вставляет пилотный символ в каждое соответствующее положение в данных (символах), подаваемых от перемежителей 120 и 124 по частоте, и создает фрейм, сформированный с заданным количеством символов, из полученных в результате данных (символов). Этот фрейм подают на модуль 132 генерирования OFDM.

Модуль 132 генерирования OFDM генерирует соответствующий сигнал OFDM из фрейма, подаваемого от модуля 131 построителя фреймов/выделения ресурсов, и передает сигнал OFDM через канал 13 (фиг.7).

На фиг.9 показана структура примера перемежителя 116 битов, показанного на фиг.8.

Перемежитель 116 битов представляет собой устройство обработки данных, которое выполняет перемежение данных, и сформировано с перемежителем 23 четности, перемежителем 24 со скручиванием столбцов и демультиплексором (DEMUX) 25.

Перемежитель 23 четности выполняет перемежение четности для перемежения бита четности кода LDPC, подаваемого от кодера 115 LDPC, в положение другого бита четности, и подает код LDPC, подвергнутый перемежению четности, в перемежитель 24 со скручиванием столбцов.

Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов для кода LDPC, подаваемого от перемежителя 23 четности, и подает код LDPC, подвергнутый перемежению со скручиванием столбцов, на демультиплексор 25.

Таким образом, на кодере 117 QAM, показанном на фиг.8, знаковый бит одного или больше битов кода LDPC отображает на точку сигнала, представляющую один символ ортогональной модуляции, и код LDPC затем передают.

В перемежителе 24 со скручиванием столбцов, последнее описанное перемежение со скручиванием столбцов выполняют, как операцию изменения конфигурации, для изменения конфигурации знаковых битов кода LDPC, подаваемых от перемежителя 23 четности, таким образом, что знаковые биты кода LDPC, соответствующие "1" в произвольной строке в матрице проверки четности, используемые на кодере 115 LDPC, не содержатся в одном символе.

Демультиплексор 25 выполняет операцию перестановки кода LDPC, подаваемого от перемежителя 24 со скручиванием столбцов, для перестановки положения двух или больше знаковых битов, которые должны представлять собой символы в коде LDPC. Таким образом, получают код LDPC с повышенной устойчивостью к AWGN. Демультиплексор 25 затем подает два или больше знаковых бита кода LDPC, полученных в результате операции перестановки, как символы, на кодер 117 QAM (фиг.8).

На фиг.10 показана матрица Н проверки четности, используемая при кодировании LDPC на кодере 115 LDPC, показанном на фиг.8.

Матрица Н проверки четности имеет структуру LDGM (матрица генерирования низкой плотности), и может быть выражена уравнением H=[HA|HT] (матрица, имеющая матрицу HA информации, как элемент с левой стороны, и матрицу HT четности, как элемент с правой стороны), где матрица HA информации соответствует информационным битам для знаковых битов кода LDPC, и матрица HT четности соответствует битам четности для знаковых битов кода LDPC.

Здесь для знаковых битов одного кода LDPC (одно кодовое слово) количество информационных битов и количество битов четности называются информационной длиной К и длиной М четности. Кроме того, количество знаковых битов в одном коде LDPC называется длиной N(=К+М) кода.

Информационную длину K и длину М четности кода LDPC, имеющего определенную длину N кода, определяют по их скорости кода. Матрица Н проверки четности представляет собой матрицу, имеющую М строк и N столбцов. Матрица HA информации представляет собой матрицу размером M×K, и матрица HT четности представляет собой матрицу М×М.

На фиг.11 показана матрица HT четности для матрицы Н проверки четности кода LDPC, установленного в стандартах DVB-T.2 (и DVB-S.2).

Матрица HT четности для матрицы Н проверки четности кода LDPC, установленного в стандартах DVB-T.2, имеет лестничную структуру, в которой элементы "1" расположены ступенчато, как показано на фиг.11. В матрице HT четности вес строки равен 1 в первой строке, и равен 2 в каждой из остальных строк. В то же время, вес столбца равен 1 в последнем столбце и равен 2 в каждом из остальных столбцов.

Как описано выше, код LDPC, имеющий матрицу Н проверки четности с лестничной структурой в матрице HT четности, может быть легко сгенерирован путем использования матрицы Н проверки четности.

Таким образом, код LDPC (одно кодовое слово) представлен вектором с строки, и вектор столбца, полученный в результате транспонирования вектора строки, представлен, как cT. Для вектора с строки, в качестве кода LDPC, участок информационного бита представлен вектором А строки, и участок битов четности представлен вектором Т строки.

В этом случае, вектор с строки может быть выражен с помощью уравнения с=[А|Т] (вектор строки имеющий вектор А строки, как элемент с левой стороны, и вектор Т строки, как элемент с правой стороны), где вектор А строки представляет собой информационные биты, и вектор Т строки представляет собой биты четности.

Матрица Н проверки четности и с вектор с=[А|Т] строки, как код LDPC, должны удовлетворять уравнению HcT=0, и вектор Т строки, как биты четности вектора с=[А|Т] строки, которые удовлетворяют уравнению HcT=0, могут быть последовательно определены (по порядку), путем изменения элемента в каждой строке на "0" в векторе HcT столбца в уравнении, HcT=0, начиная от элемента в первой строке, если матрица HT четности в матрице Н=[HA|HT] проверки четности имеет лестничную структуру, показанную на фиг.11.

На фиг.12 показана схема для пояснения матрицы Н проверки четности кода LDPC, представленного в стандартах DVB-T.2.

В столбцах КХ, начиная от первой строки матрицы Н проверки четности кода LDPC, установленного в стандартах DVB-T.2, вес столбца равен X. В столбцах K3, следующих после столбцов КХ, вес столбца равен 3. В столбцах (М-1), следующих после столбцов К3, вес столбца равен 2. В последнем одном столбце вес столбца равен 1.

Здесь KX+K3+(M-1)+1 равно длине N кода.

На фиг.13 показана схема, представляющая количества KX, K3 и М столбцов, и вес X столбцов при каждой кодовой скорости r для кодов LDPC, установленных в стандартах DVB-T.2.

В стандартах DVB-T.2 установлены коды LDPC с длинами N кода 64800 битов и 16200 битов.

Что касается кодов LDPC, с длиной N кодов, равной 64800 битов, установлены 11 скоростей кода (номинальных скоростей), равные 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10. Что касается кодов LDPC, с длиной кодов N 16200 битов, установлены 10 скоростей кода 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9.

Здесь длина N кода 64800 битов также называется 64 килобита, и длина N кода 16200 битов также называется 16 килобит.

Что касается кода LDPC, известно, что знаковый бит, соответствующий столбцу с большим весом столбца в матрице Н проверки четности, имеет меньшую частоту ошибок.

В матрице Н проверки четности, установленной в стандартах DVB-T.2, показанной на фиг.12 и 13, столбец ближе к верху (с левой стороны) проявляет тенденцию иметь больший вес столбца. В соответствии с этим, в коде LDPC, соответствующем матрице Н проверки четности, знаковый бит, расположенный ближе к верхней части, проявляет тенденцию быть более сильным в отношении ошибок (или иметь запас устойчивости к ошибкам), и знаковый бит, расположенный ближе к концу, проявляет тенденцию быть более слабым в отношении ошибок.

На фиг.14 показана компоновка (точек сигнала, соответствующих) 16 символов в плоскости I-Q, в случае, когда выполняют 16QAM на кодере 117 QAM, показанном на фиг.8.

Таким образом, в позиции А на фиг.14 показаны символы 16QAM для DVB-T.2.

В 16QAM один символ представляет четыре бита, и присутствуют 16 (=24) символов. 16 символов расположены так, что квадрат 4×4 в направлении I и в направлении Q формируется вокруг исходной точки в плоскости I-Q.

В случае, когда бит yi представляет (i+1)-ый бит, отсчитанный, начиная с верхнего бита в столбце битов, представленных одним символом, четыре бита, представленные одним символом 16QAM, могут быть представлены битами y0, y1, y2 и y3 в порядке от самого верхнего бита. В случае, когда способ модуляции представляет собой 16QAM, четыре бита, такие как знаковый бит кода LDPC, преобразуют (преобразуют в символы) в символ (значение символа) из четырех битов y0-y3.

На фиг.14, в позиции В показаны границы битов в четырех соответствующих битах (ниже также называются символьными битами) y0-y3, представленных символом 16QAM.

Здесь границы символов в символьном бите yi (i=0, 1, 2 и 3 на фиг.14) представляют собой границу между символами, с которыми символьный бит yi равен 0, и символам, с которыми символьный бит yi равен 1.

Как показано в позиции В на фиг.14, ось Q в плоскости I-Q представляет собой только одну границу битов в самом верхнем символьном бите y0 среди четырех символьных битов y0-y3, представленных символом 16QAM, и ось I в плоскости I-Q представляет собой только одну границу битов во втором символьном бите y1 (второй самый верхний бит, отсчитываемый от самого верхнего бита).

В третьем символьном бите y2 линия между первым и вторым столбцами слева, и линия между третьим и четвертым столбцами среди символов 4×4, используются, как границы битов.

Кроме того, в четвертом символьном бите y3, линия между первой и второй строками сверху, и линия между третьей и четвертой строками среди символов 4×4 используются, как границы битов.

Среди символьных битов yi, представленных символами, символьный бит, имеющий большее количество символов, расположенных дальше от границы битов, проявляет тенденцию иметь меньшее количество ошибок (или иметь меньшую вероятность ошибок), и символьный бит, имеющий большее количество символов, расположенный ближе к границе битов, проявляет тенденцию иметь большее количество ошибок (или иметь большую вероятность ошибки).

В случае, когда биты, которые проявляют тенденцию иметь меньшее количество ошибок (или проявляют тенденцию устойчивости к ошибкам), называются "сильными битами", и биты, которые проявляют тенденцию иметь больше ошибок (или являются более слабыми в отношении ошибок) называются "слабыми битами", верхний символьный бит y0, и второй символьный бит y1 являются символьными битами среди четырех символьных битов y0-y3 символа 16QAM, и третий символьный бит y2, и четвертый символьный бит y3 представляют собой слабые биты.

На фиг.15-17 показана компоновка (точек сигнала, соответствующих) 64 символов в плоскости I-Q, в случае, когда выполняют 64QAM на кодере 117 QAM, показанном на фиг.8, или символов 16QAM в DVB-T.2.

В 64QAM один символ представляет шесть битов, и при этом присутствуют 64 (=26) символов. 64 символа расположены так, что квадрат 8×8 в направлении I и в направлении Q формируется вокруг исходной точки в плоскости I-Q.

Символьные биты одного символа 64QAM могут быть представлены, как биты y0, y1, y2, y3, y4 и y5 в порядке от самого верхнего бита. Когда способ модуляции представляет собой 64QAM, шесть знаковых битов кода LDPC преобразуют в символ из шести символьных битов y0-y5.

На фиг.15 показаны соответствующие границы битов в самом верхнем символьном бите y00 и во втором символьном бите y1 среди символьных битов y0-y5 символа 64QAM. На фиг.16 показаны соответствующие границы битов в третьем символьном бите y2 и четвертом символьном бите y3. На фиг.17 показаны соответствующие границы битов в пятом символьной бите y4 и в шестом символьном бите y5.

Как показано на фиг.15, присутствует одна граница битов в каждом верхнем символьном бите y0 и втором символьном бите y1. Кроме того, как показано на фиг.16, существуют две границы битов в каждом третьем символьном бите y2 и четвертом символьном бите y3. Как показано на фиг.17, существуют четыре границы битов в каждом пятом символьном бите y4 и в шестом символьном бите y5.

В соответствии с этим, для символьных битов y0-y5 для символа 64QAM, самый верхний символьный бит y0 и второй символьный бит y1 представляют собой сильные биты, и третий символьный бит y2, и четвертый символьный бит y3 представляют собой вторые самые сильные биты. Пятый символьный бит y4 и шестой символьный бит y5 представляют собой слабые биты.

Как можно видеть на фиг.14 и фиг.15-17, для символьных битов, для символа ортогональной модуляции, верхние биты проявляют тенденцию быть сильными битами, и нижние биты проявляют тенденцию быть слабыми битами.

Как описано выше со ссылкой на фиг.12 и 13, в коде LDPC, который выводят от кодера 115 LDPC (фиг.8), присутствуют знаковые биты, которые являются устойчивыми к ошибкам, и знаковые биты, которые являются слабыми в отношении ошибок.

Кроме того, как описано выше со ссылкой на фиг.14-17, среди символьных битов для символа ортогональной модуляции, выполняемой на кодере 117 QAM, присутствуют сильные биты и слабые биты.

Поэтому, когда знаковые биты, которые являются слабыми в отношении ошибок в коде LDPC, назначают для слабых символьных битов символа ортогональной модуляции, общая устойчивость к ошибкам становится низкой.

С учетом этого, был предложен перемежитель, который перемежает знаковые биты кода LDPC путем назначения знаковых битов, которые являются слабыми в отношении ошибок в коде LDPC, в основном, для сильных битов (символьных битов) для символа ортогональной модуляции.

Демультиплексор 25, показанный на фиг.9, может выполнять такую операцию перемежения.

На фиг.18 показана схема, предназначенная для пояснения операции демультиплексора 25, показанного на фиг.9.

В частности, в позиции А на фиг.18 показан пример функциональной структуры демультиплексора 25.

Демультиплексор 25 включает в себя запоминающее устройство 31 и модуль 32 перестановки.

Код LDPC подают от кодера 115 LDPC на запоминающее устройство 31.

Запоминающее устройство 31 имеет емкость хранения для хранения mb битов в направлении строки (горизонтальном направлении) и N/(mb) битов в направлении столбца (вертикальном направлении), записывает знаковые биты подаваемого кода LDPC в направлении столбца, считывает знаковые биты в направлении строки и подает знаковые биты на модуль 32 перестановки.

Здесь N (=длина K информации+длина М четности) представляет собой длину кода для кода LDPC, как описано выше.

Кроме того, m представляет количество знаковых битов кода LDPC для формирования одного символа, и b представляет заданное положительное целое число, которое представляет собой кратное число, предназначенное для умножения m на целое число. Как описано выше, демультиплексор 25 преобразует в символы (отображает в форме символов) знаковые биты кода LDPC, и кратное число b представляет количество символов, которое должно быть получено демультиплексором 25, выполняющим одну операцию преобразования символов.

На фиг.18 в позиции А показана структура примера демультиплексора 25 в случае, когда способ модуляции представляет собой 64QAM, и, поэтому, количество m знаковых битов кода LDPC для формирования одного символа равно 6.

Кроме того, в позиции А на фиг.18, множество чисел b равно 1 и, в соответствии с этим, запоминающее устройство 31 имеет емкость хранения N/(6×1)×(6×1) битов в направлении столбца и в направлении строки.

В запоминающем устройстве 31, каждая область хранения, которая имеет один бит в направлении строки и продолжается в направлении столбца, ниже будет называться столбцом, соответственно. В позиции А на фиг.18 запоминающее устройство 31 сформировано из шести (=6×1) столбцов.

В демультиплексоре 25 запись знаковых битов кода LDPC в столбцы, формирующие запоминающее устройство 31, в направлении сверху вниз (в направлении столбца), выполняют по столбцам в направлении слева направо.

После того, как запись знаковых битов будет закончена в самом нижнем положении, в самом правом столбце, знаковые биты считывают из первой строки всех столбцов, формирующих запоминающее устройство 31, в направлении строки по шесть битов (mb битов) одновременно, и затем подают на модуль 32 перестановки.

Модуль 32 перестановки выполняет операцию перестановки для перестановки положения шести знаковых битов, подаваемых от запоминающего устройства 31, и выводит полученные в результате шесть битов, как шесть символьных битов y0, y1, y2, y3, y4 и y5, которые представляют один символ 64QAM.

В частности, mb битов (шесть битов в данном примере) считывают в направлении строки из запоминающего устройства 31. В случае, когда i-ый бит (i=0, 1 …, mb-1), подсчитанный с самого верхнего бита среди m знаковых битов, считываемых из запоминающего устройства 31, будет представлен как бит bi, шесть знаковых битов, считываемых в направлении строки из запоминающего устройства 31, могут быть выражены, как биты b0, b1, b2, b3, b4 и b5 в порядке от самого верхнего бита.

Во взаимосвязи с весом столбца, описанном со ссылкой на фиг.12 и 13, знаковые биты, расположенные в направлении бита b0, представляют собой знаковые биты, устойчивые к ошибкам, и знаковые биты, расположенные в направлении бита b5, представляют собой знаковые биты, которые являются слабыми в отношении ошибок.

Модуль 32 перестановки может выполнять операцию перестановки для перестановки положения шести знаковых битов b0-b5, считанных из запоминающего устройства 31 таким образом, что знаковые биты, слабые в отношении ошибок среди шести знаковых битов b0-b5, считанные из запоминающего устройства 31, назначают для сильных битов среди символьных битов y0-y5 одного символа 64QAM.

Изготовители предложили различные способы, в качестве способов перестановки, для перестановки шести знаковых битов b0-b5, считываемых из запоминающего устройства 31, и назначения шести знаковых битов для шести символьных битов y0-y5, которые представляют один символ 64QAM.

На фиг.18 в позиции В показан первый способ перестановки, в позиции С показан второй способ перестановки и в позиции D показан третий способ перестановки.

В позициях В-D на фиг.18 (и на фиг.19, которая будет описана ниже), каждая строка, соединяющая биты bi и yj, указывает, что знаковый бит bi назначен для символьного бита yj символа (или заменяет символьный бит yj).

В качестве первого способа перестановки, показанного в позиции В на фиг.18, было предложено использовать один из трех способов перестановки. В качестве второго способа перестановки, показанного в позиции С на фиг.18, было предложено использовать один из двух способов перестановки.

В качестве третьего предложенного способа перестановки, показанного в позиции D на фиг.18, были последовательно выбраны и использовались шесть способов перестановки.

На фиг.19 показан пример структуры демультиплексора 25 в случае, когда способ модуляции представляет собой 64QAM (количество m знаковых битов в коде LDPC, которые должны быть отображены на один символ, равно 6, как в примере, показанном на фиг.18) и кратное число b равно 2, и также показан четвертый способ перестановки.

В случае, когда кратное число b равно 2, запоминающее устройство 31 имеет емкость накопления N/(6×2)×(6×2) битов в направлении столбца и в направлении строки, и сформированы 12(=6×2) столбцов.

На фиг.19 в позиции А показан порядок записи кода LDPC в запоминающее устройство 31.

В демультиплексоре 25 запись знаковых битов кода LDPC в столбцы, формирующие запоминающее устройство 31, в направлении сверху вниз (в направлении столбца) выполняют по столбцам в направлении слева направо, как описано выше со ссылкой на фиг.18.

После окончания записи знаковых битов в самом нижнем положении, в самом правом столбце, знаковые биты считывают из первой строки всех столбцов, формирующих запоминающее устройство 31, в направлении строки по 12 битов (mb битов) одновременно, и затем подают на модуль 32 перестановки.

Модуль 32 перестановки выполняет операцию перестановки, для перестановки положения 12 знаковых битов, подаваемых от запоминающего устройства 31, в соответствии с четвертым способом перестановки, и выводит полученные в результате 12 битов, которые составляют 12 битов, представляющих два символа (b символов) 64QAM, или шесть символьных битов y0, y1, y2, y3, y4 и y5, которые представляют один символ 64QAM, и шесть символьных битов y0, y1, y2, y3, y4 и y5, которые представляют следующий один символ.

На фиг.19, в позиции В показан четвертый способ перестановки, используемый модулем 32 перестановки, показанным в позиции А на фиг.19, для выполнения операции перестановки.

В случае, когда кратное число b равно 2 (как в случаях, когда кратное число b равно 3 или больше), mb знаковых битов назначают для mb символьных битов для b последовательных символов при операции перестановки. Как показано на фиг.19, в дальнейшем, (i+1)-ый бит, подсчитанный от верхнего бита среди mb символьных битов, для b последовательных символов, выражен как бит (символьный бит) yi, для простоты пояснения.

Кроме того, когда способ перестановки является соответствующим, следует ли увеличить частоту ошибок в каналах AWGN, зависит от скорости кода и длины кода каждого кода LDPC, способа модуляции и т.п.

Перемежение четности

Далее, со ссылкой на фиг.20-22, будет описано перемежение четности, выполняемое перемежителем 23 четности, показанным на фиг.9.

На фиг.20 показана (часть) графа Таннера матрицы проверки четности кода LDPC.

Как показано на фиг.20, когда два или больше (знаковых бита, соответствующих) переменных узлов, соединенных с проверочным узлом, одновременно имеют ошибки, такие как удаления, проверочный узел возвращает сообщение, указывающее, что вероятность того, что значение равно "0", и вероятность того что значение равно "1", равны друг другу, во все переменные узлы, соединенные с проверочным узлом. Поэтому, когда переменные узлы, соединенные с одним и тем же проверочным узлом, одновременно содержат удаление и т.п., характеристика декодирования ухудшаются.

В то же время, код LDPC, который выводят от кодера 115 LDPC, показанного на фиг.8, и который установлен в стандартах DVB-T.2, представляет собой код IRA, и матрица HT четности матрицы Н проверки четности имеет лестничную структуру, как показано на фиг.11.

На фиг.21 показана матрица HT четности, имеющая лестничную структуру, и граф Таннера, соответствующий матрице HT четности.

В частности, в позиции А на фиг.21 показана матрица HT четности, имеющая лестничную структуру, и позиции В на фиг.21 показан граф Таннера, соответствующий матрице HT четности, показанной в позиции А на фиг.21.

В матрице HT четности, имеющей лестничную структуру, элементы "1", расположенные рядом друг с другом в каждой строке (за исключением первой строки). Поэтому, в графе Таннера матрицы HT четности, два соседних переменных узла, соответствующие столбцу двух соседних элементов, имеющих значение "1" в матрице HT четности, соединены с одним и тем же проверочным узлом.

Когда биты четности, соответствующие двум соседним переменным узлам, одновременно имеют ошибки из-за пакетных ошибок или удаления и т.п., проверочный узел, соединенный с двумя переменными узлами (переменные узлы, запрашивающие сообщение, используя биты четности), соответствующими двум битам четности, имеющим ошибки, возвращает сообщение, обозначающее, что вероятность того, что значение составляет "0", и вероятность того, что значение, представляет собой "1", равны друг другу, в переменные узлы, соединенные с проверочным узлом. В результате, ухудшаются характеристики декодирования. Когда длина пакета (количество битов четности, имеющих последовательные ошибки) становится большой, количество проверочных узлов, возвращающих сообщение равной вероятности, становится большим, и характеристики декодирования дополнительно ухудшаются.

Для предотвращения деградации характеристик декодирования, перемежитель 23 четности (фиг.9) выполняет перемежение четности для перемежения битов четности кода LDPC, подаваемого от кодера 115 LDPC в положениях других битов четности.

На фиг.22 показана матрица HT четности матрицы Н проверки четности, соответствующей коду LDPC, подвергаемому перемещению четности, выполняемому перемежителем 23 четности, показанным на фиг.9.

Здесь, информационная матрица НА матрицы Н проверки четности, соответствующей коду LDPC, который выводят от кодера 115 LDPC, и который установлен в соответствии со стандартами DVB-T.2, имеет циклическую структуру.

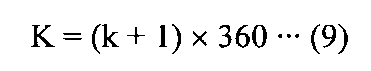

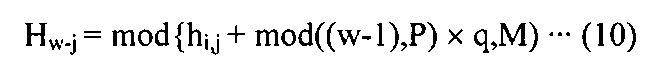

Циклическая структура представляет собой структуру, в которой столбец является таким же, как столбец, сформированный в результате циклического сдвига другого столбца. Например, циклическая структура также представляет собой структуру, в которой положения элементов "1" в каждой строке Р столбцов циклически сдвинуты в направлении столбца на значение, пропорциональное значению q, полученному в результате деления первого столбца из Р столбцов на длину М четности. После этого Р столбцов в циклической структуре будут называться единичным числом столбцов в циклической структуре.

Что касается кодов LDPC, установленных в стандартах DVB-T.2, существуют два типа кодов LDPC, имеющих длину N кода 64800 битов и 16200 битов, как описано выше со ссылкой на фиг.12 и 13. Для каждого из двух типов кодов LDPC единичное число Р столбцов в циклической структуре определено, как 360, что представляет собой один из делителей длины М четности, за исключением 1 и М.

Длина М четности имеет значение, выраженное уравнением M=q×P=q×360 для разных значений q при каждой скорости кода. Длина М четности имеет другое значение, чем простое число. Поэтому, так же, как и единичное число Р столбцов в циклической структуре, значение q представляет собой другой один из делителей длины М четности, за исключением 1 и М, и его получают путем деления длины М четности на единичное число Р столбцов в циклической структуре (произведение Р и q, которые являются делителями длины М четности, равно длине М четности).

В случае, когда K представляет длину информации, x представляет целое число, которое не меньше, чем 0, и меньше чем P, и y представляет целое число, которое не меньше, чем 0, и меньше, чем q, как описано выше, перемежитель 23 четности выполняет перемежение четности для перемежения (K+qx+y+1)-ого знакового бита среди знаковых битов N-битного кода LDPC в положение (K+Py+х+1)-ого знакового бита.

Как (K+qx+y+1)-ый знаковый бит, так и (K+Py+х+1)-ый знаковый бит, представляют собой знаковые биты после (K+1)-ого знакового бита, и, поэтому, они представляют собой биты четности. В соответствии с этим, в результате перемежения четности, положения битов четности кода LDPC сдвигаются.

В результате такого перемежения четности, (биты четности, соответствующие) переменным узлам, соединенным с одним и тем же проверочным узлом, отделяются друг от друга на расстояние, эквивалентное единичному числу Р столбцов в циклической структуре, или на 360 битов в данном случае. В соответствии с этим, когда длина пакета меньше, чем 360 битов, можно предотвратить одновременные ошибки в переменных узлах, соединенных с одним и тем же проверочным узлом. В результате, может быть повышена устойчивость к пакетным ошибкам.

Код LDPC, подвергаемый перемежению четности, для перемежения (K+qx+y+1)-ого знакового бита в положение (K+Py+х+1)-ого знакового бита, является тем же, что и код LDPC матрицы проверки четности, полученной в результате выполнения замены столбца для замены (K+qx+y+1)-ого столбца в оригинальной матрице Н проверки четности на (K+Py+х+1)-ый столбец (полученная в результате матрица проверки четности ниже будет также называться преобразованной матрицей проверки четности).

В матрице четности преобразованной матрицы проверки четности появляется псевдоциклическая структура, имеющая циклы из Р столбцов (360 столбцов на фиг.22), как показано на фиг.22.

Здесь псевдоциклическая структура означает структуру, которая представляет собой циклическую структуру, за исключением некоторых участков. В преобразованной матрице проверки четности, получаемой в результате выполнения замены столбцов, эквивалентной перемежению четности матрицы проверки в матрице проверки четности кода LDPC, установленного в стандартах DVB-T.2, не хватает только одного среди множества элементов "1" (и имеется один дополнительный элемент "0" вместо этого) на участке правого угла из 360 строк и 360 столбцов (матрица сдвига, которая будет описана ниже). В этом аспекте структура не является (идеальной) циклической структурой, но представляет собой, так называемую, псевдоциклическую структуру.

Преобразованная матрица проверки четности, показанная на фиг.22, представляет собой матрицу, сформированную путем выполнения в оригинальной матрице Н проверки четности не только замены столбцов, эквивалентной перемежению четности, но также и операции замены строк (замена строки), для формирования преобразованной матрицы проверки с описанной ниже определяющей матрицей.

Перемежение со скручиванием столбцов

Со ссылкой теперь на фиг.23-26, будет описано перемежение со скручиванием столбцов, как операция изменения компоновки, выполняемая перемежителем 24 со скручиванием столбцов, показанным на фиг.9.

В устройстве 11 передачи, показанном на фиг.8, один или больше знаковых битов кода LDPC передают, как один символ. В частности, в случае, когда два знаковых бита формируют один символ, QPSK используют, например, как способ модуляции. В случае, когда четыре знаковых бита формируют один символ, 16QAM используют, например, как способ модуляции.

В случае, когда два или больше знаковых бита передают, как один символ, когда возникает удаление в символе, все знаковые биты символа имеют ошибки (удаление).

Поэтому, для снижения вероятности возникновения в (соответствующих знаковых битах) переменных узлах, соединенных с одним и тем же проверочным узлом, одновременного появления удаления, и, таким образом, для улучшения характеристики декодирования, необходимо предотвратить соединение переменных узлов, соответствующих знаковым битам одного символа, с одним и тем же проверочным узлом.

В то же время, в матрице Н проверки четности кода LDPC, который должен быть выведен от кодера 115 LDPC, и установленной в стандартах DVB-T.2, информационная матрица HA имеет циклическую структуру, и матрица HT четности имеет лестничную структуру, как описано выше. В преобразованной матрице проверки четности, которая представляет собой матрицу проверки четности кода LDPC, в котором выполняют перемежение четности, циклическая структура (точнее, псевдоциклическая структура, как описано выше) также появляется в матрице четности, как описано выше со ссылкой на фиг.22.

На фиг.23 показана преобразованная матрица проверки четности.

В частности, в позиции А на фиг.23 показана преобразованная матрица проверки четности матрицы Н проверки четности для кода LDPC, имеющего длину N кода 64800 битов и скорость кода (r) равную 3/4.

В позиции А на фиг.23 положения элементов, имеющих значение "1" в преобразованной матрице проверки четности, обозначены точками (·).

В позиции В на фиг.23 иллюстрируется операция, которая выполняется демультиплексором 25 (фиг.9) для кода LDPC преобразованной матрицы проверки четности, показанной в позиции А на фиг.23, или кода LDPC, который был подвергнут перемежению четности.

В позиции В на фиг.23, способ модуляции представляет собой 16QAM, и знаковые биты кода LDPC, подвергаемые перемежению четности, записывают в направлении столбца в четырех столбцах, формирующих запоминающее устройство 31 демультиплексора 25.

Знаковые биты, записанные в направлении столбца в четырех столбцах, формирующих запоминающее устройство 31, считывают по четыре бита одновременно в направлении строки, и затем формируют один символ.

В этом случае, четыре знаковых бита b0, b1, b2 и b3, которые формируют один символ, могут представлять собой знаковые биты, соответствующие элементам "1" в произвольной строке, в преобразованной матрице проверки четности, показанной в позиции А на фиг.23. В этом случае переменные узлы, соответствующие знаковым битам b0, b1, b2 и b3, соединены с одним и тем же проверочным узлом.

Поэтому, в случае, когда четыре знаковых бита b0, b1, b2 и b3 одного символа представляют собой знаковые биты, соответствующие элементам "1" в произвольной строке в преобразованной матрице проверки четности, если удаление происходит в символе, соответствующее сообщение не может быть получено от проверочного узла, с которым соединены переменные узлы, соответствующие знаковым битам b0, b1, b2 и b3. В результате, ухудшаются характеристики декодирования.

В случае других скоростей кода, кроме ¾, знаковые биты, соответствующие переменным узлам, соединенным с тем же самым проверочным узлом, также могут формировать один символ 16QAM.

Учитывая это, перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов для перемежения знаковых битов кода LDPC, которые были подвергнуты перемежению четности, и которые были поданы из перемежителя 23 четности, таким образом, что знаковые биты, соответствующие элементам "1" в произвольной строке, в преобразованной матрице проверки четности, не будут содержаться в одном символе.

На фиг.24 показана схема, поясняющая перемежение со скручиванием столбцов.

В частности, на фиг.24 показано запоминающее устройство 31 (фиг.18 и 19) демультиплексора 25.

Как описано выше со ссылкой на фиг.18, запоминающее устройство 31 имеет емкость хранения для содержания mb битов в направлении столбца (вертикальном направлении) и N/(mb) битов в направлении строки (горизонтальном направлении), и сформировано из mb столбцов. Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцом в запоминающем устройстве 31, путем управления положениями начала записи при записи знаковых битов кода LDPC в направлении столбца и считывания знаковых битов в направлении строки.

Таким образом, перемежитель 24 со скручиванием столбцов соответствующим образом изменяет положения начала записи, в которых начинается запись знакового бита в соответствующих столбцах, таким образом, что знаковые биты, формирующие один символ, предназначенный для считывания в направлении строки, не являются знаковыми битами, соответствующими элементам "1" в произвольной строке в преобразованной матрице проверки четности (или компоновка знаковых битов кода LDPC изменяется таким образом, чтобы знаковые биты, соответствующие элементам "1" в произвольной строке, в матрице проверки четности, не содержатся в одном символе).

Здесь, на фиг.24 показана примерная структура запоминающего устройства 31 в случае, когда способ модуляции представляет собой 16QAM, и кратное число b, описанное со ссылкой на фиг.18, равно 1. В соответствии с этим, число m знаковых битов кода LDPC, которое составляет один символ, равно 4, и запоминающее устройство 31 сформировано из четырех (=mb) столбцов.

В перемежителе 24 со скручиванием столбцов (вместо демультиплексора 25, показанного на фиг.18), запись знаковых битов кода LDPC в четыре столбца, формирующих запоминающее устройство 31 в направлении сверху вниз (в направлении столбца), выполняют для столбцов в направлении слева направо.

Когда запись знаковых битов заканчивается в самом правом столбце, перемежитель 24 со скручиванием столбцов считывает знаковые биты, по четыре бита (mb бита) одновременно, в направлении строки из первой строки всех столбцов, формирующих запоминающее устройство 31, и выводит знаковые биты, как код LDPC, подвергнутый перемежению со скручиванием столбцов, на модуль 32 перестановки (показанный на фиг.18 и 19) демультиплексора 25.

Когда адрес верхних положений (самое верхнее положение) в каждом столбце равен 0, и адреса соответствующих положений в направлении столбца представлены целыми числами в порядке возрастания, перемежитель 24 со скручиванием столбцов устанавливает положение начала записи в положении с адресом 0 самого левого столбца, устанавливает положение начала записи в положении с адресом 2 во втором столбце (слева), устанавливает положение начала записи в положении с адресом 4 в третьем столбце, и устанавливает положение начала записи в положении с адресом 7 в четвертом столбце.