Результат интеллектуальной деятельности: ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано в многопортовых блоках статических ОЗУ.

Наиболее распространенным вариантами статической КМОП ячейки памяти в многопортовых блоках статических ОЗУ (регистровых файлах) в настоящее время являются КМОП ячейки памяти на основе КМОП D-триггера, портов записи данных и портов чтения (Патент US №7106620 В2, кл. G11C 11/00, опублик. Sep. 12. 2006; Патент US №7656739 В2, кл. G11C 11/4063, опублик. Feb. 2. 2010). Воздействие одиночной ядерной частицы на ячейку памяти комплементарной металл-оксид-полупроводниковой структуры (далее КМОП) приводит к временному переходу ячейки памяти в неравновесное состояние и при превышении порога переключения к сбою ее состояния и хранимых данных.

Недостатком описанных выше технических решений является недостаточная надежность хранения данных при воздействии одиночных ядерных частиц.

Наиболее близкой по технической сущности и достигаемому результату является ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, включающая триггер, состоящий из двух групп транзисторов, портов записи данных и портов чтения, размещенных на кристалле интегральной микросхемы, выходы портов записи данных соединены с соответствующими выводами двух групп транзисторов триггера (Ultra-LowPowerRadiationHardenedbyDesignMemoryCircuits / IEEETransactionsonNuclearScience, 2007, Vol.54, №6, p. 2004-2011). Повышение надежности хранения данных при воздействии одиночных ядерных частиц достигается использованием в ячейке памяти триггера с дублированием хранения логического состояния (ячейка DICE) в двух группах транзисторов.

Недостатком описанной ячейки является недостаточная надежность чтения данных в режиме временного перехода ячейки памяти в неравновесное состояние, вызванного воздействием одиночной ядерной частицы.

Задачей настоящего изобретения является повышение надежности работы ячейки при воздействии одиночной ядерной частицы.

Техническим результатом, ожидаемым от использования изобретения, является повышение помехоустойчивости и надежности чтения данных, когда триггер ячейки памяти на основе двух групп транзисторов находится в неравновесном состоянии, вызванном воздействием одиночной ядерной частицы.

Указанный технический результат достигается тем, что ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, включающая триггер, состоящий из двух групп транзисторов, портов записи данных и портов чтения, размещенных на кристалле интегральной микросхемы, выходы портов записи данных соединены с соответствующими выводами двух групп транзисторов триггера, согласно изобретению ячейка памяти снабжена двумя инверторами и двумя инверторами с третьим состоянием, при этом первые выводы первой и второй групп транзисторов триггера соединены с входом первого инвертора, вторые выводы первой и второй групп транзисторов триггера соединены с входом второго инвертора, а третий вывод первой группы транзисторов триггера и третий вывод второй группы транзисторов триггера соединены, соответственно, с первыми входами первого и второго инверторов с третьим состоянием, при этом выход первого инвертора соединен со вторым входом первого и третьим входом второго инверторов с третьим состоянием, а выход второго инвертора соединен с третьим входом первого и вторым входом второго инверторов с третьим состоянием, выходы которых соединены с входами данных портов чтения.

А также тем, что транзистор структуры металл-оксид-полупроводник с каналом электронной проводимости второго инвертора, транзистор структуры металл-оксид-полупроводник с каналом дырочной проводимости первого инвертора и транзисторы первого инвертора с третьим состоянием размещены на кристалле интегральной микросхемы на расстоянии, обеспечивающем одинаковое воздействие одиночной ядерной частицы на них с первой группой транзисторов ячейки памяти, а транзистор структуры металл-оксид-полупроводник с каналом электронной проводимости первого инвертора, транзистор структуры металл-оксид-полупроводник с каналом дырочной проводимости второго инвертора, транзисторы второго инвертора с третьим состоянием размещены на кристалле интегральной микросхемы на расстоянии, обеспечивающем одинаковое воздействие одиночной ядерной частицы на них со второй группой транзисторов ячейки памяти, причем две группы транзисторов ячейки памяти размещены на кристалле интегральной микросхемы одна от другой на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового.

Указанная совокупность признаков позволяет повысить помехоустойчивость и надежность чтения данных из ячейки, когда триггер ячейки памяти на основе двух групп транзисторов находится в неравновесном состоянии, вызванном воздействием одиночной ядерной частицы.

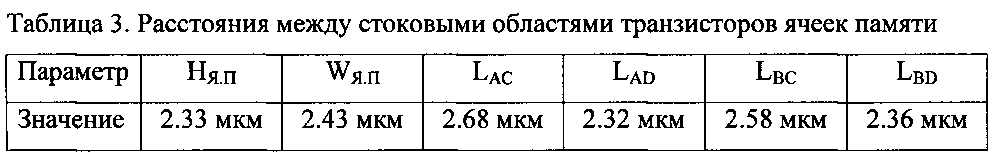

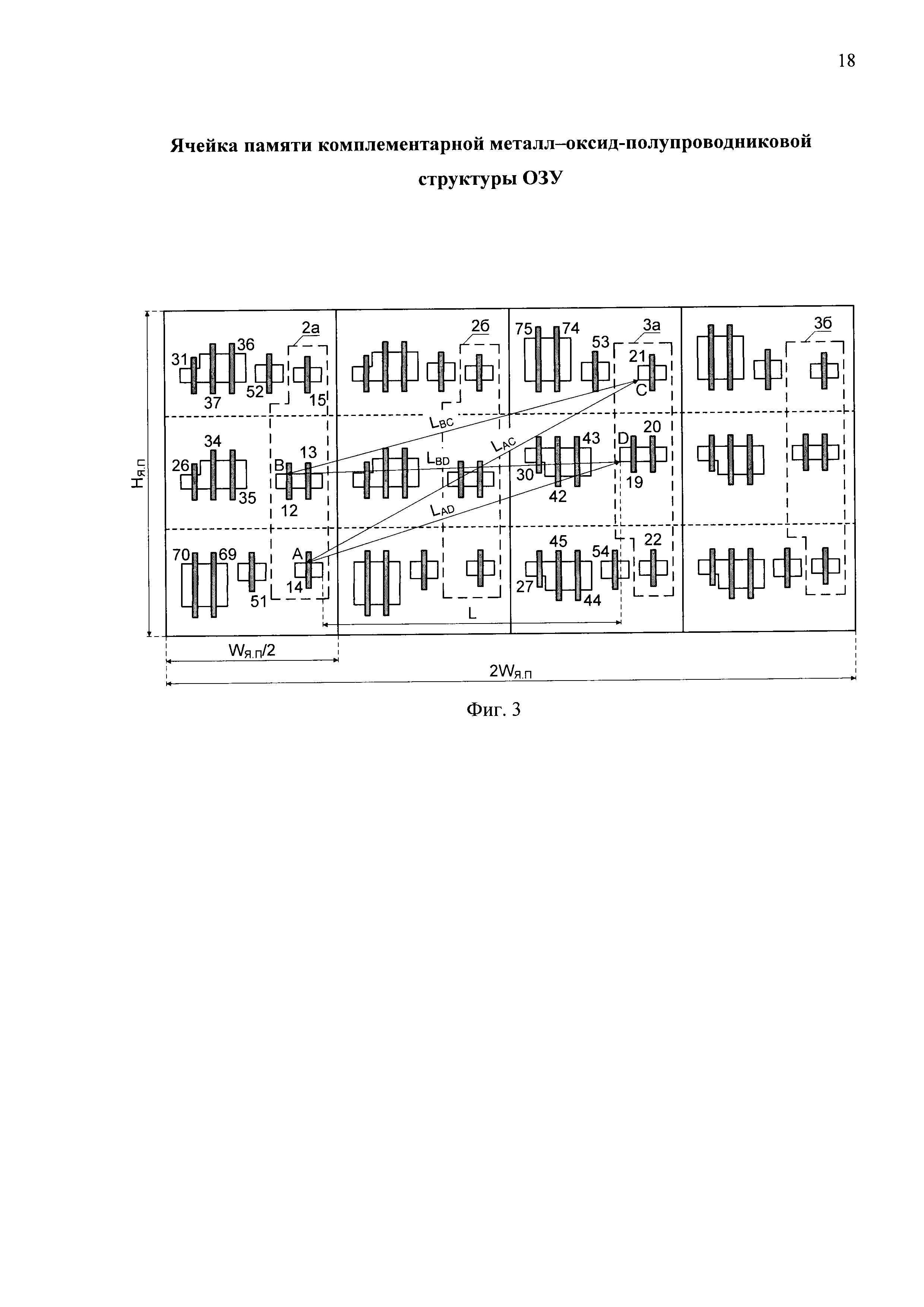

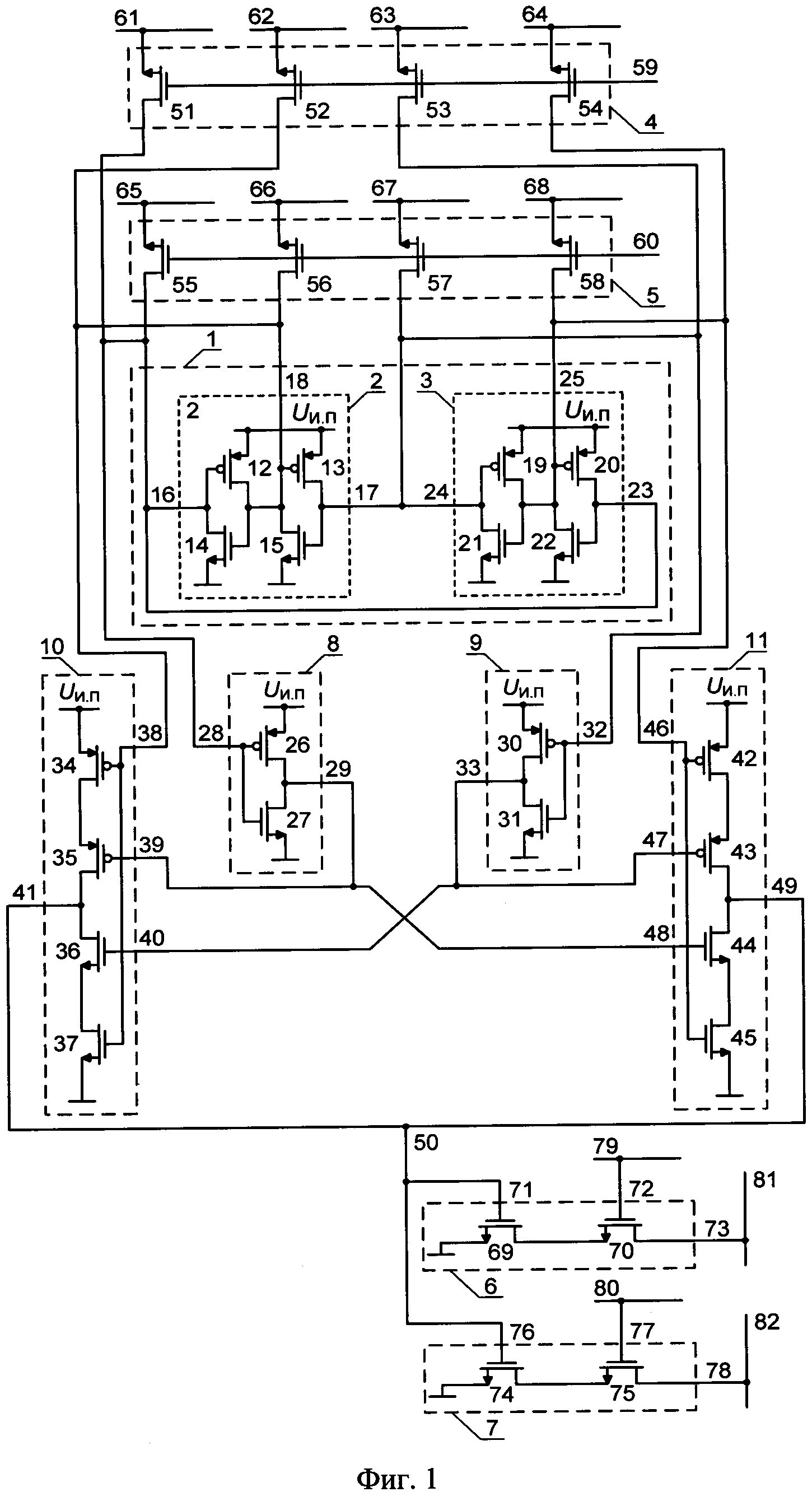

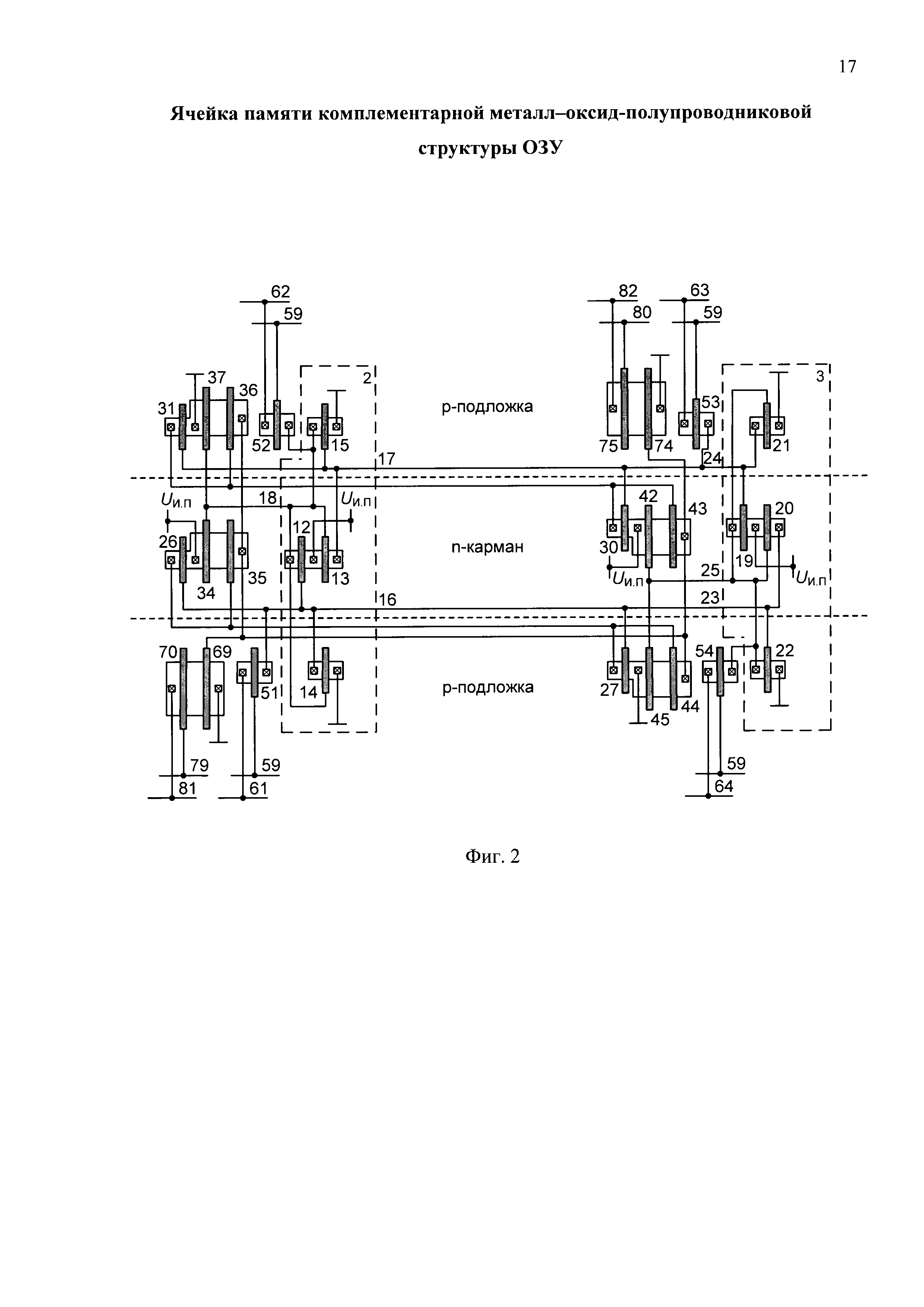

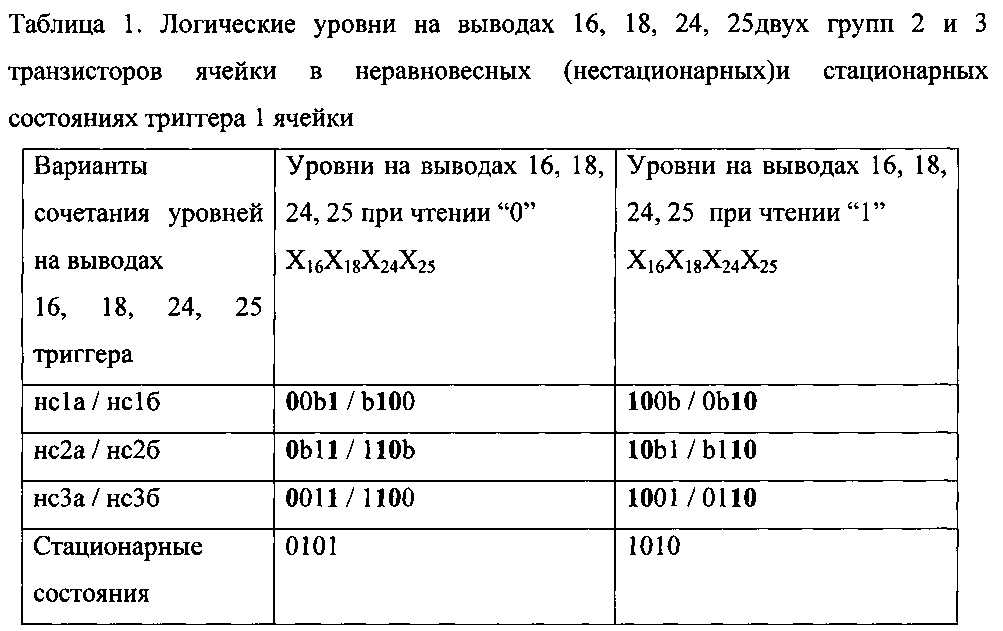

Изобретение поясняется чертежами, где на фиг. 1 изображена электрическая принципиальная схема ячейки памяти с двумя портами записи и двумя порами чтения, на фиг. 2 изображена схема взаимного расположения транзисторов одной двухпортовой по чтению ячейки памяти, на фиг. 3 изображена схема взаимного расположения транзисторов в двухпортовом по чтению базовом элементе ОЗУ, содержащем две ячейки памяти.

Использованы обозначения: РМОП транзистор - это транзистор со структурой металл-оксид-полупроводник и каналом дырочной проводимости, то есть P-типа, NМОП транзистор - транзистор со структурой металл-оксид-полупроводник и каналом электронной проводимости, то есть N-типа.

Ячейка памяти содержит триггер 1, состоящий из первой и второй групп 2, 3 транзисторов, порты 4, 5 записи данных, порты 6, 7 чтения, два инвертора 8, 9 и два инвертора с третьим состоянием 10, 11. Первая группа 2 на PМОП транзисторах 12, 13 и NМОП транзисторах 14, 15 триггера 1 имеет три вывода 16, 17,18, вторая группа 3 на PМОП транзисторах 19, 20 и NΜΟΠ транзисторах 21, 22 триггера 1 имеет три вывода 23, 24, 25, первый инвертор 8 на PМОП транзисторе 26 и ΝМОП транзисторе 27 имеет вход 28 и выход 29, второй инвертор 9 на РМОП транзисторе 30 и NМОП транзисторе 31 имеет вход 32 и выход 33, первый инвертор 10 с третьим состоянием на PМОП транзисторах 34, 35 и ΝΜΟΠ транзисторах 36, 37 имеет три входа 38, 39, 40 и выход 41, второй инвертор 11 с третьим состоянием на PМОП транзисторах 42, 43 и NMOП транзисторах 44, 45 имеет три входа 46, 47, 48 и выход 49. Первый и второй выводы 16 и 17 первой группы 2 транзисторов соединены с первым и вторым выводом 23 и 24 второй группы 3 транзисторов. Кроме того, первые выводы 16, 23 и вторые выводы 17, 24 первой и второй групп 2, 3 транзисторов триггера 1, соответственно, соединены с входом 28 первого инвертора 8 и входом 32 второго инвертора 9, третий вывод 18 первой группы 2 транзисторов триггера 1 и третий вывод 25 второй группы 3 транзисторов триггера 1 соединены, соответственно, с первыми входами 38, 46 первого и второго инверторов 10, 11 с третьим состоянием, выход 29 первого инвертора 8 соединен с вторым входом 39 первого и третьим входом 48 второго инверторов 10, 11 с третьим состоянием, выход 33 второго инвертора 9 соединен с третьим входом 40 первого и вторым входом 47 второго инверторов 10, 11 с третьим состоянием, выходы 41, 49 которых соединены с общей шиной 50 выходов инверторов 10, 11 с третьим состоянием. Кроме того, два порта 4, 5 записи данных содержат по четыре проходных ключа на NМОП транзисторах 51, 52, 53, 54 и, соответственно, на NМОП транзисторах 55, 56, 57, 58, затворы проходных ключей NМОП транзисторах 51, 52, 53, 54 и NМОП транзисторах 55, 56, 57, 58, соответственно, соединены с линиями 59 и 60 выборки.

Один из выводов проходных ключей на ΝΜΟΠ транзисторах 51, 52, 53, 54 первого порта 4 записи данных, а также проходных ключей на NΜΟΠ транзисторах 55, 56, 57, 58 второго порта 5 записи данных соединен, соответственно, с выводом 16, 18, 24, 25 групп 2 и 3 транзисторов триггера 1 ячейки памяти; другой вывод проходных ключей на NМОП транзисторах 51, 52, 53, 54 первого порта 4 записи данных соединен, соответственно, с одной из четырех битовых линий 61, 62, 63, 64 первого порта 4 записи, а другой вывод проходных ключей на NМОП транзисторах55, 56, 57, 58 второго порта 5 записи данных соединен, соответственно, с одной из четырех битовых линий 65, 66, 67, 68 порта 5 записи. Кроме того, первый порт 6 чтения на ΝΜΟΠ транзисторах 69, 70 имеет два входа 71, 72 и выход 73, второй порт 7 чтения на NМОП транзисторах 74, 75 имеет два входа 76, 77 и выход 78; первые входы 71 и 76 первого и второго портов 6, 7 чтения соединены с выходной шиной 50 инверторов 10, 11 с третьим состоянием, вторые входы 72 и 77 первого и второго портов 6, 7 чтения соединены с соответствующими линиями 79 и 80 выборки чтения, выходы 73 и 78 первого и второго портов 6, 7 чтения соединены с соответствующими битовыми линиями 81 и 82 чтения.

Описанное устройство работает следующим образом.

Ячейка памяти может работать в одном из трех режимов: запись, хранение и чтение.

Запись данных в ячейку памяти осуществляется в четыре узла, которыми являются выводы 16 и 18 и выводы 24 и 25 первой и второй групп 2 и 3 транзисторов. Запись производится через проходные ключи на NMOH транзисторах 51, 52, 53, 54 или на NМОП транзисторах 55, 56, 57, 58 портов 4 или 5 записи. Одновременная запись через оба порта 4, 5 записи запрещена. При записи через порт 4 или 5 записи на битовые линии 61, 62, 63, 64 или 65, 66, 67, 68 подают записываемые данные в дифференциальной форме, а именно, на выводы 16 и 24 групп 2 и 3 транзисторов в нормальном виде, а на выводы 18 и 25 - в инверсном. Установкой активного уровня на линиях 59 или 60 выборки открывают проходные ключи порта 4 или порта 5 чтения, пропуская записываемые данные (сигналы) на выводы 16, 18, 24, 25 ячейки памяти.

В режиме хранения на линиях 59, 60 выборки и линиях 79, 80 выборки чтения устанавливают неактивный уровень, что поддерживает все порты 4, 5 записи и порты 6, 7 чтения в закрытом состоянии. На выводах 16, 18, 24, 25 и на шине 50 ячейки памяти в стационарном ее состоянии хранятся уровни сигналов, соответствующие записанным данным.

Чтение данных из ячейки памяти осуществляется с шины 50 ячейки. Чтение в многопортовой ячейке памяти производится через равнозначные (независимые) порты 6 и 7 чтения. При чтении через порт 6 чтения и (или) порт 7 на линии 79 и (или) 80 выборки чтения устанавливают активный уровень, порт 6 и (или) порт 7 чтения открывается, позволяя считывать хранимый сигнал (данные) с шины 50 ячейки памяти на соответствующие битовые линии 81 и (или) 82 чтения.

Критичными при оценке характеристик надежности чтения данных ячейки памяти являются воздействия одиночной частицы, когда ее трек проходит под малым углом к поверхности кристалла микросхемы, что соответствует углам наклона трека частицы относительно нормали к поверхности кристалла микросхемы θ=75°-60°. Наиболее жестким случаем является случай, когда трек частицы проходит, например, в непосредственной близости или просто через область обратно смещенного pn перехода сток-подложка одного из запертых транзисторов первой группы 2, а на второй подвергнутый воздействию транзистор из второй группы 3, действует заряд неосновных носителей, диффундирующих к нему от ближайшей к нему области трека частицы. Чтобы сбой ячейки памяти не произошел, расстояние L между парами МОП транзисторов из двух групп 2 и 3 должно быть больше порогового значения LПОР. Симметричным критическим вариантом воздействия является прохождение трека частицы в направлении от второй группы 3 транзисторов к первой группе 2 при преобладающем воздействии на область обратно смещенного pn перехода сток-подложка одного из запертых транзисторов второй группы 3 транзисторов.

При воздействии на триггер 1 ячейки памяти одиночной ядерной частицы, когда трек частицы направлен от запертого транзистора первой группы 2 к запертому транзистору второй группы 3, неравновесные носители заряда, образованные вдоль трека, диффундируют к транзисторам ячейки и выводятся в виде импульсов тока на выводы, соответствующие стоковым электродам запертых транзисторов групп 2 и 3 транзисторов, и перезаряжают емкости этих узлов. Этот процесс сопровождается образованием импульсов напряжений помех, которые переводят триггер ячейки памяти на группах 2 и 3 транзисторов в неравновесное состояние, которое может завершиться возвращением в исходное равновесное (стационарное) состояние триггера ячейки или сбоем состояния при превышении порога переключения.

Критичными для оценки надежности чтения данных в ячейке памяти являются не только сбой и искажение хранимого состояния в режиме хранения данных, но также и искажения при чтении данных в неравновесных состояниях во время воздействия одиночных ядерных частиц.

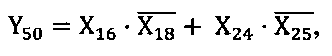

Для ячеек памяти при проектно-технологических нормах 65 нм и менее с разделенными на две группы транзисторами (которые разнесены на кристалле ОЗУ на расстояние, снижающее вероятность сбоя триггера ячейки памяти) длительность неравновесного состояния может достигать 1 нс. В неравновесном состоянии триггера можно осуществлять надежное чтение данных из ячейки памяти, определяя два (из четырех) вывода триггера ячейки, которые сохраняют во время воздействия частицы свои исходные состояния из исходного стационарного состояния ячейки до воздействия. Варианты сочетания логических уровней (и значений напряжений) на выводах 16, 18, 24, 25 первой и второй групп 2 и 3 транзисторов триггера ячейки в неравновесных состояниях приведены в таблице 1. Жирным шрифтом в таблице 1 отмечены уровни на выводах 16, 18, 24, 25 триггера ячейки, сохраняющих значения, соответствующие исходным уровням в стационарном состоянии при хранении "0" (0101) и "1" (1010).

На одном из выводов 16, 18, 24, 25, который в нестационарном состоянии оказывается в режиме с двумя открытыми транзисторами, устанавливается напряжение UИ.П×b, а нормированный уровень на этом выводе будет иметь некое промежуточное значение b. Значение b зависит от соотношения крутизны характеристик РМОП и NМОП транзисторов и ограничено значениями 0,2<b<0,4.

Сочетания значений логических уровней Х16Х18Х24Х25 на выводах 16, 18, 24, 25 триггера ячейки памяти для всех вариантов нестационарных состояний характеризуются кольцевой повторяемостью уровней на выводах 16, 18, 24, 25 триггера, а именно комбинаций 0b10, b110 и 0110, которые повторяются циклически четырежды в разных вариантах нестационарных состояний, сдвигаясь по кольцу выводов 16, 18, 24, 25 и образуя 12 вариантов нестационарных состояний для двух исходных стационарных состояний 1010 и 0101 на выводах 16, 18, 24, 25.

Для вариантов нестационарных состояний в таблице 1 использованы обозначения следующего вида: нс1а и нс1б, где цифра соответствует номеру варианта нестационарного состояния (одинаковые для состояний 0 и 1), а буквы "а" и "б" соответствуют симметрии состояний с общим цифровым номером отдельно для хранимых и считываемых "0" и "1".

Ячейка памяти на основе триггера из двух групп 2 и 3 транзисторов, двух инверторов 8, 9, входы 28 и 32 которых, соответственно, соединены с выводами 16 и 24 первой и второй групп 2 и 3 транзисторов, а выходы 29 и 33, соответственно, с вторыми входами 39, 47 инверторов 10, 11 с третьим состоянием, объединенных между собой перекрестными связями их вторых и третьих входов 39 и 48, 47 и 40, первые входы 38 и 46 которых соединены с выводами 18 и 25 первой и второй групп 2 и 3 транзисторов, а выходы 41, 49 объединены шиной 50 ячейки, описывается как в стационарных, так и неравновесных (нестационарных) состояниях, представленных в таблице 1, передаточной логической функцией следующего вида:

где X16, Х18, Х24, Х25 - логические уровни на выводах 16, 18, 24, 25 триггера ячейки памяти; Y50 - логический уровень на шине 50 ячейки памяти.

Результаты моделирования характеристик ячейки памяти по проектно-технологической норме объемный КМОП 28 нм.

Чтение логического "0" при нахождении триггера ячейки в нестационарных (согласно таблице 1 при чтении "0") и стационарном (0101) состояниях при вариациях значений напряжений логических нуля и единицы на выводах 16, 18, 24, 25 триггера ячейки памяти в пределах U0=0-0.3 В и U1=0.6-0.9 В дает результат чтения при всех нестационарных и стационарном состояниях ячейки значение U50=U0=0 на шине 50 ячейки.

Чтение логического "1" при нахождении триггера ячейки в нестационарных (согласно таблице 1 при чтении "1") и стационарном (1010) состояниях при вариациях значений напряжений логических нуля и единицы на выводах 16, 18, 24, 25 триггера ячейки памяти в пределах U0=0-0.3 В и U1=0.6-0.9 В дает результат чтения при всех нестационарных и стационарном состояниях ячейки значение UВЫХ47=U0=UИ.П=0.9 В на шине 50 ячейки.

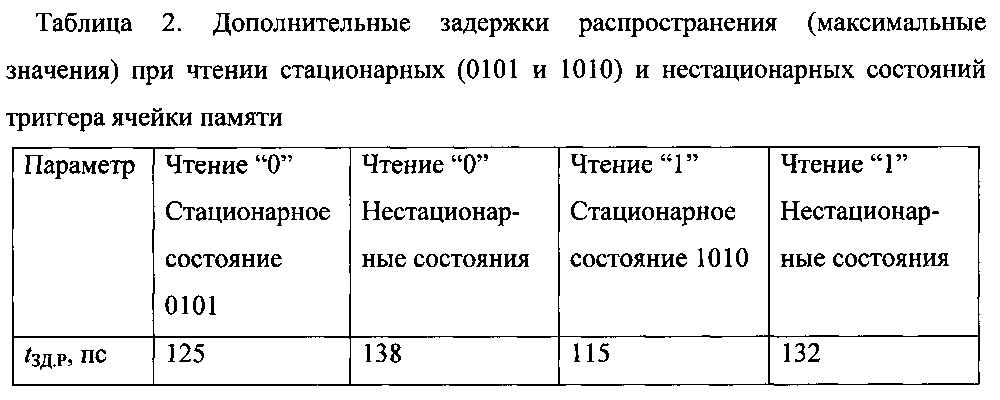

Динамические искажения в режиме чтения характеризует задержка распространения tЗД.Р сигналов состояний с выводов 16, 18, 24, 25 на шину 50, обусловленная введением инверторов 8, 9, 10, 11 в состав ячейки памяти. В таблице 2 приведены значения задержки распространения сигнала - tЗД.Р при чтении данных в стационарных и нестационарных состояниях. Задержки с такими значениями не влияют на результаты чтения данных.

При нахождении триггера ячейки в неравновесном (нестационарном) состоянии "0" в случае направления трека частицы от первой группы 2 к второй группе 3 транзисторов и преимущественного воздействия заряда с трека частицы на первую группу 2 транзисторов триггера 1 на выводе 16 первой группы 2 транзисторов триггера 1 ячейки сохраняется логическое состояние "0", соответствующее исходному стационарному состоянию на выводе 16 первой группы 2 транзисторов триггера 1 ячейки, при этом на выходе 29 инвертора 8 будет состояние "1" (соответственно, NМОП транзистор 27 заперт), которое, управляя инвертором 11 по третьему входу 48, поддерживает инвертор 11 в состоянии "0" по его выходу 49. Одновременно, состояние "1" по выходу 29 инвертора 8, управляя инвертором 10 по второму входу 39, поддерживает инвертор 10 в высокоимпедансном состоянии по его выходу 41, поскольку на его первом входе 38 устанавливается неравновесный (нестационарный) уровень "0" вывода 18 первой группы 2 транзисторов триггера 1 ячейки (а точнее, значение в диапазоне от 0 до b).

При нахождении триггера 1 ячейки в неравновесном (нестационарном) состоянии "1" на выводе 16 первой группы 2 транзисторов триггера 1 ячейки и одновременно на входе 28 инвертора 8 устанавливается напряжение, соответствующее логическому уровню "0" (0 или b) практически как при чтении "0", а на выходе 29 состояние "1" (соответственно, NМОП транзистор 27 заперт).

Таким образом, для повышения надежности чтения необходимо исключить возможность изменения логического состояния "1" по выходу 29 инвертора 8, существенно снизив вероятность воздействия заряда с трека частицы на запертый NМОП транзистор 27, для чего NМОП транзистор 27 должен быть размещен на кристалле микросхемы на максимально возможном расстоянии от первой группы 2 транзисторов ячейки памяти, чтобы максимально снизить воздействие на него, когда основное воздействие частицы оказывается на первую группу 2 транзисторов.

При нахождении триггера ячейки в неравновесном (нестационарном) состоянии "0" изменение состояния на выходе инвертора 9 не влияет на состояние инвертора 11, когда основное воздействие частицы оказывается на первую группу 2 транзисторов. Это объясняется тем, что при логическом уровне "1" на входе 32 инвертора 9NМОП транзистор 31 открыт, а при уровне сигнала "0" на входе 32ΝΜΟΠ транзистор 31 заперт и при воздействии заряда с трека частицы на него инвертор 9 перейдет по выходу 32 в состояние "0", но это не повлияет на состояние сигнала выходе 49 инвертора 11, и соответственно, на шине 50 ячейки останется уровень "0".

При нахождении триггера ячейки в неравновесном (нестационарном) состоянии "1" на выводе 24 второй группы 3 транзисторов триггера 1 и на входе 32 инвертора 9 сохраняется исходный логический уровень "1" вывода 24; соответственно, NМОП транзистор 31 находится в открытом состоянии при чтении "1" и воздействие заряда с трека частицы не приведет к изменению состояния NМОП транзистора 31 и изменению логического состояния инвертора 9.

Таким образом, надежность чтения будет выше, если NМОП транзистор 3 расположить в зоне воздействия заряда с трека частицы около первой группы 2 транзисторов триггера 1 ячейки, что не повлияет при чтении "0" или "1" на правильное значение уровня сигнала на выходе 49 инвертора 11 и на шине 50 ячейки.

В случае преобладающего воздействия заряда от одиночной ядерной частицы на вторую группу 3 транзисторов триггера 1 характеристики воздействия на NМОП транзисторы 27 и 31 симметрично меняются, но рекомендации по их взаимному расположению на кристалле микросхемы относительно первой и второй групп 2 и 3 транзисторов сохраняются.

Для достижения технического результата - повышения надежности чтения данных ячейки памяти в нестационарных состояниях, возникающих при воздействии одиночных ядерных частиц, группы 2 и 3 транзисторов триггера ячейки памяти, сопутствующие транзисторы инверторов 10, 11 с третьим состоянием и PМОП транзисторы инверторов 8, 9 должны быть разнесены относительно друг друга на расстояние больше порогового L>LПОР, NМОП транзисторы 27 и 31 инверторов 8, 9 должны быть размещены рядом с противоположными группами 2 и 3 транзисторов.

Пример реализации изобретения

Устройство по изобретению реализовано в виде многопортового ОЗУ в составе КМОП СБИС микропроцессорной системы по проектной норме 28 нм. Накопитель содержит 32×64 предложенных ячеек памяти. Эскизное изображение конструкции одной ячейки памяти с двумя портами чтения приведено на фиг. 2. Эскизное изображение конструкции базового элемента памяти из двух ячеек памяти с двумя портами чтения приведено на фиг. 3. Для достижения технического результата - повышения надежности чтения данных из ячейки при воздействии одиночной ядерной частицы в режиме, когда триггер ячейки памяти на основе двух групп 2 и 3 транзисторов находится в неравновесном (нестационарном) состоянии, NМОП транзистор 31 второго инвертора 9, РМОП транзистор 26 первого инвертора 8 и транзисторы 34, 35, 36, 37 первого инвертора 10 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с первой группой 2 транзисторов ячейки памяти и образуют первый блок ячейки памяти, NМОП транзистор 27 первого инвертора 8, РМОП транзистор 30 второго инвертора 9 и транзисторы 42, 43, 44, 45 второго инвертора 11 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с второй группой 3 транзисторов триггера 1 и образуют второй блок ячейки памяти, при этом первый и второй блоки ячейки памяти, включающие группы 2 и 3 транзисторов ячейки памяти (см. фиг. 3), размещены на расстоянии больше или равном пороговому расстоянию L=2,1 мкм ≥ LПОР=2,0 мкм для исключения одновременного воздействия заряда с трека одиночной ядерной частицы на обе группы 2 и 3 транзисторов с уровнем больше порогового.

Эскизное изображение конструкции базового элемента из двух ячеек памяти с двумя портами чтения каждая приведено на фиг. 3. Основой структуры статического многопортового ОЗУ является базовый элемент, состоящий из двух предложенных ячеек памяти, которые выполняются в виде четырех блоков. Каждая из ячеек памяти с размером по вертикали НЯ.П состоит из двух блоков с размером по горизонтали WЯ.П/2 каждый, где WЯ.П - суммарный размер одной ячейки по горизонтали (см. фиг. 3), всего четыре блока, которые чередуются.

Первая ячейка памяти содержит группы 2а и 3а транзисторов, вторая ячейка памяти - группы 2б и 3б транзисторов. Каждый из четырех блоков включает транзисторы одного порта чтения и два проходных ключа одного порта записи для записи данных. Расположение транзисторов в каждой ячейке на фиг.3 соответствует расположению транзисторов в ячейке на фиг. 2.

В таблице 3 приведены значения расстояний между стоковыми областями транзисторов А, В, С, D, расположенных в разных группах ячейки памяти и одновременно находящихся в запертом состоянии при хранении "0" в ячейке памяти. Эти расстояния LAC, LAD, LBC, LBD>LПОР=2,0 мкм, что обеспечивает требуемый уровень сбое устойчивости ячеек памяти, изготовленных по проектно-технологической норме объемный КМОП 28 нм, но не исключает неравновесных (нестационарных) состояний ячейки памяти.