Результат интеллектуальной деятельности: ДИФФЕРЕНЦИАЛЬНЫЙ ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Вид РИД

Изобретение

Изобретение относится к области измерительной техники, а именно к измерительным преобразователям с частотной формой выходных сигналов.

Известен измерительный преобразователь (см. патент РФ 2280946, опубликован 27.07.2006 в Бюл. №21), который выполнен на двух генераторах периодических сигналов, частоты которых задаются резонаторами с собственными (резонансными) частотами, зависящими от значения преобразуемой величины и преобразователя разностного сигнала с использованием фазового компаратора на основе D-триггера.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбран в качестве прототипа.

Недостатком прототипа является низкая точность измерений из-за наличия динамических погрешностей при малой разности преобразуемых частот.

Решаемой технической задачей является создание дифференциального измерительного преобразователя с высокими метрологическими характеристиками.

Достигаемым техническим результатом является повышение быстродействия и уменьшение погрешности.

Для достижения технического результата в дифференциальном измерительном преобразователе, содержащем два генератора частотных сигналов с частотозадающими элементами, первый фазовый компаратор, новым является то, что дополнительно введены первый, второй и третий элементы задержки, первый и второй счетчики, блок управления, второй фазовый компаратор, первый и второй сумматоры сигналов, первый и второй квантователи сигналов, генератор опорной частоты, реверсивный счетчик и блок его управления, первый и второй выходы которого соединены соответственно со входом сброса и входом запрета счета реверсивного счетчика, выход которого является выходом устройства, суммирующий и вычитающий входы которого соединены соответственно через первый и второй квантователи сигналов с выходами первого и второго сумматоров, первые входы которых соединены с первым и вторым выходами первого фазового компаратора, а вторые их входы соединены со вторым и первым выходами второго фазового компаратора, первые входы первого и второго фазовых компараторов объединены между собой и соединены с входом третьего элемента задержки и с первым входом блока управления реверсивным счетчиком, второй вход которого является управляющим входом, при этом блок управления включает в себя первый и второй дешифраторы, первый, второй и третий логические элементы 2И, выходы первого и второго логических элементов 2И соединены со вторым и третьим входами первого фазового компаратора, выход третьего логического элемента 2И соединен с первыми входами обоих фазовых компараторов, выход третьего элемента задержки соединен со входами сброса первого и второго счетчиков, группы выходов которых соединены с группами входов первого и второго дешифраторов, первые выходы которых соединены с первыми входами первого и второго логических элементов 2И, вторые входы которых соединены с выходами первого и второго генераторов частотных сигналов, вторые выходы дешифраторов соединены со входами третьего логического элемента 2И, вторым и третьим входами второго фазового компаратора и входами запрета счета первого и второго счетчиков соответственно, счетные входы которых через первый и второй элементы задержки соединены с выходами первого и второго генераторов частотных сигналов, входы синхронизации которых объединены и соединены с выходом генератора опорной частоты и со вторыми входами квантователей сигналов.

Новая совокупность существенных признаков позволяет в заявляемом устройстве повысить точность измерений и быстродействие за счет уменьшения погрешности.

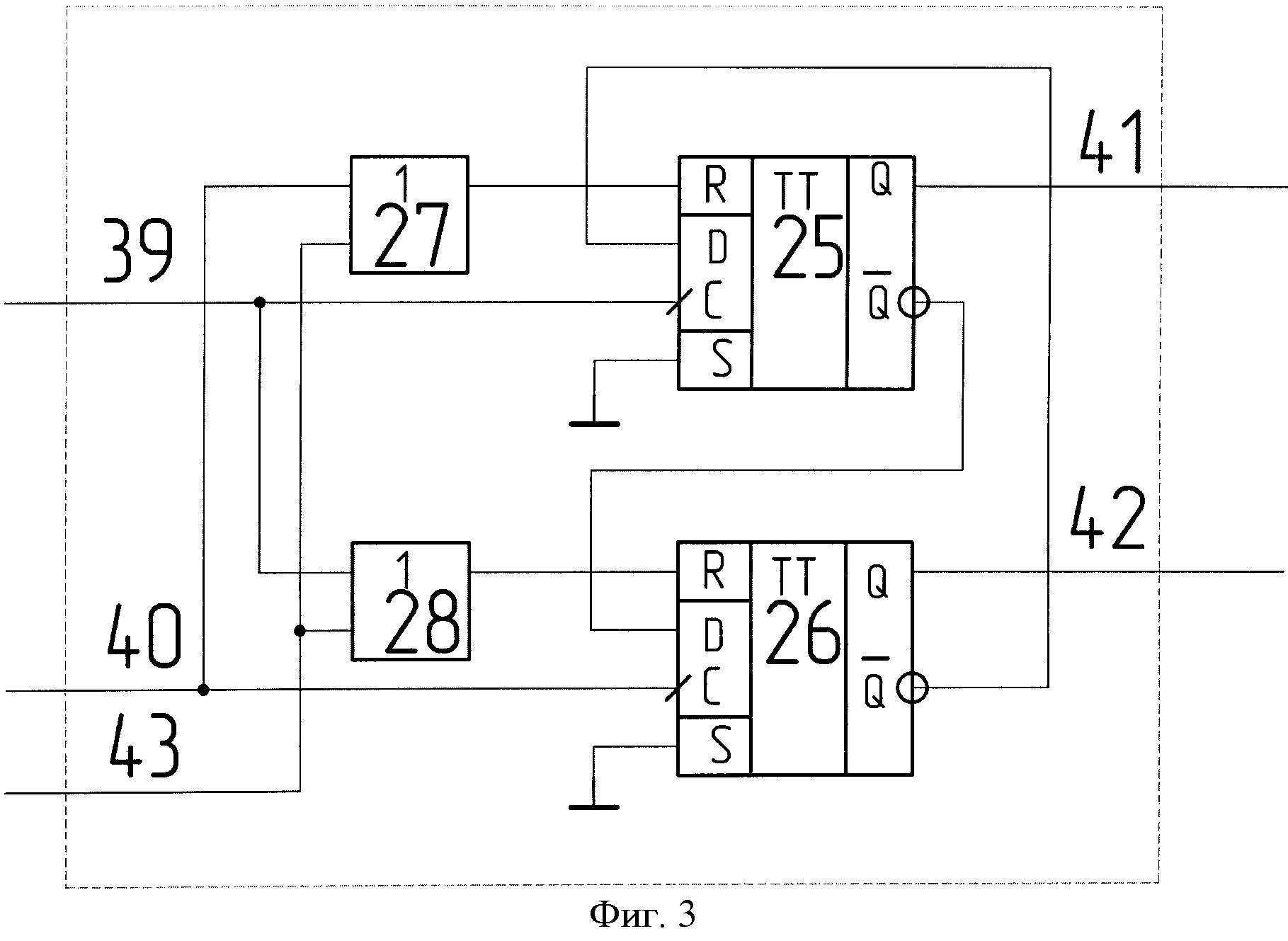

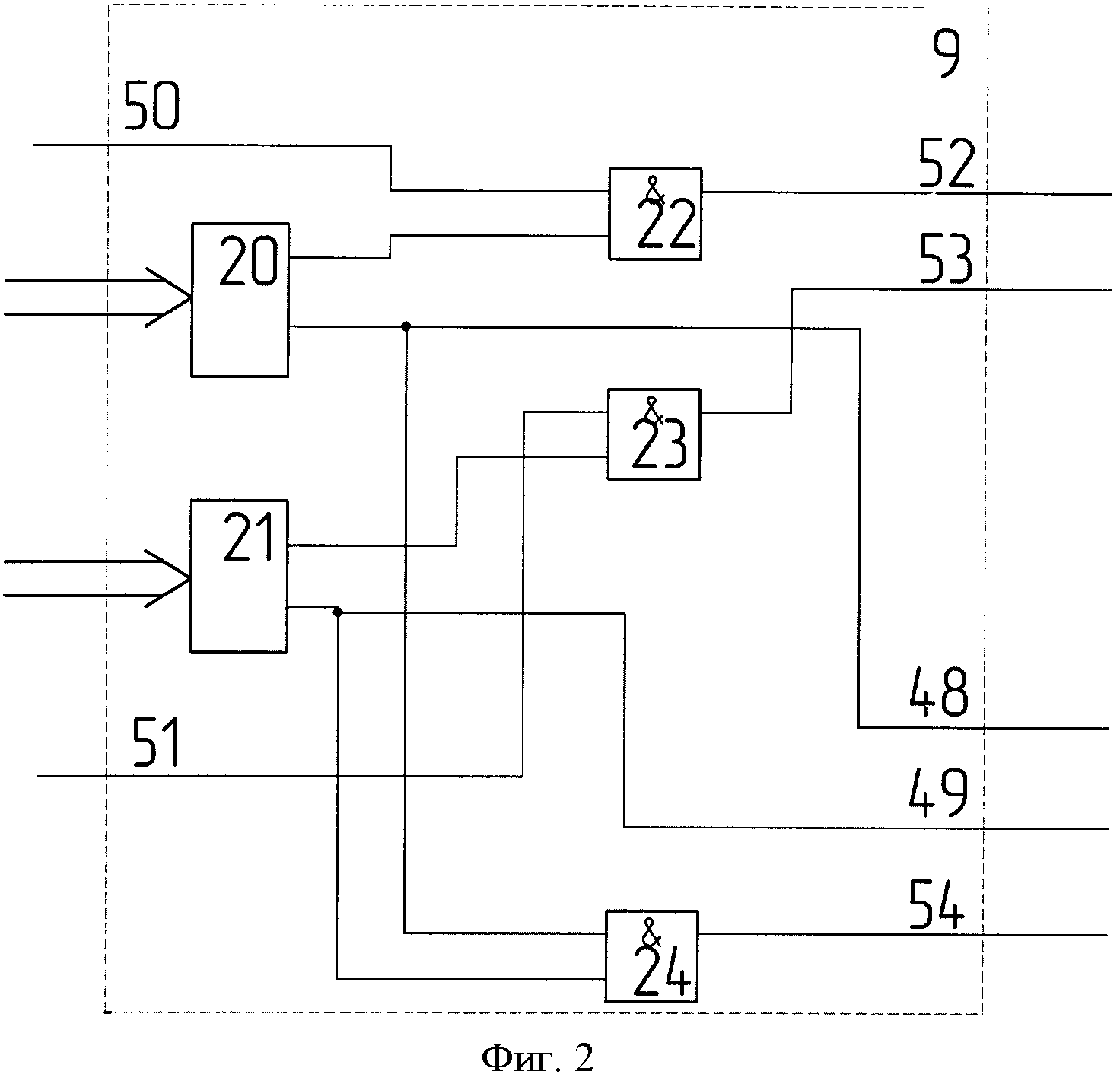

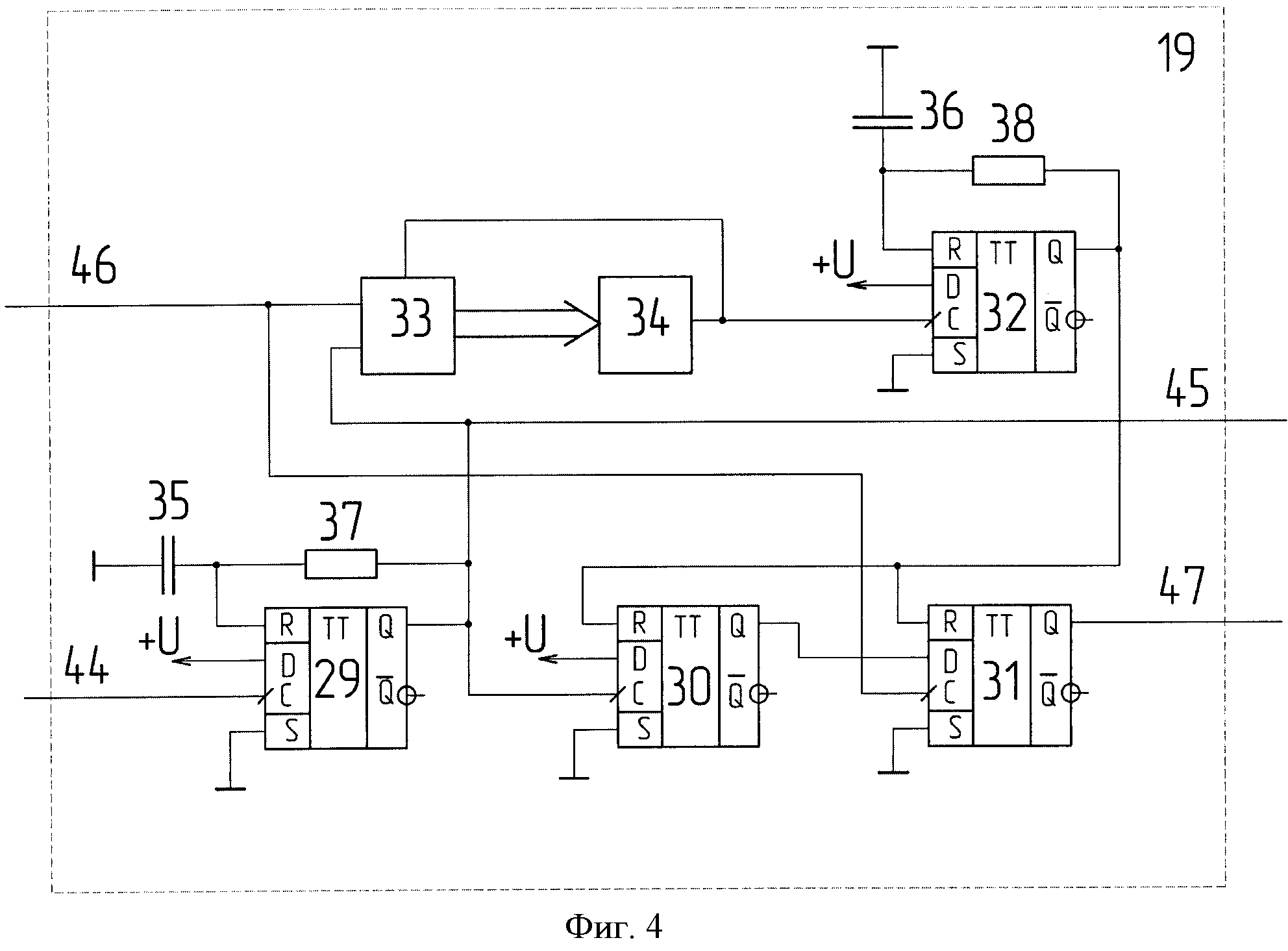

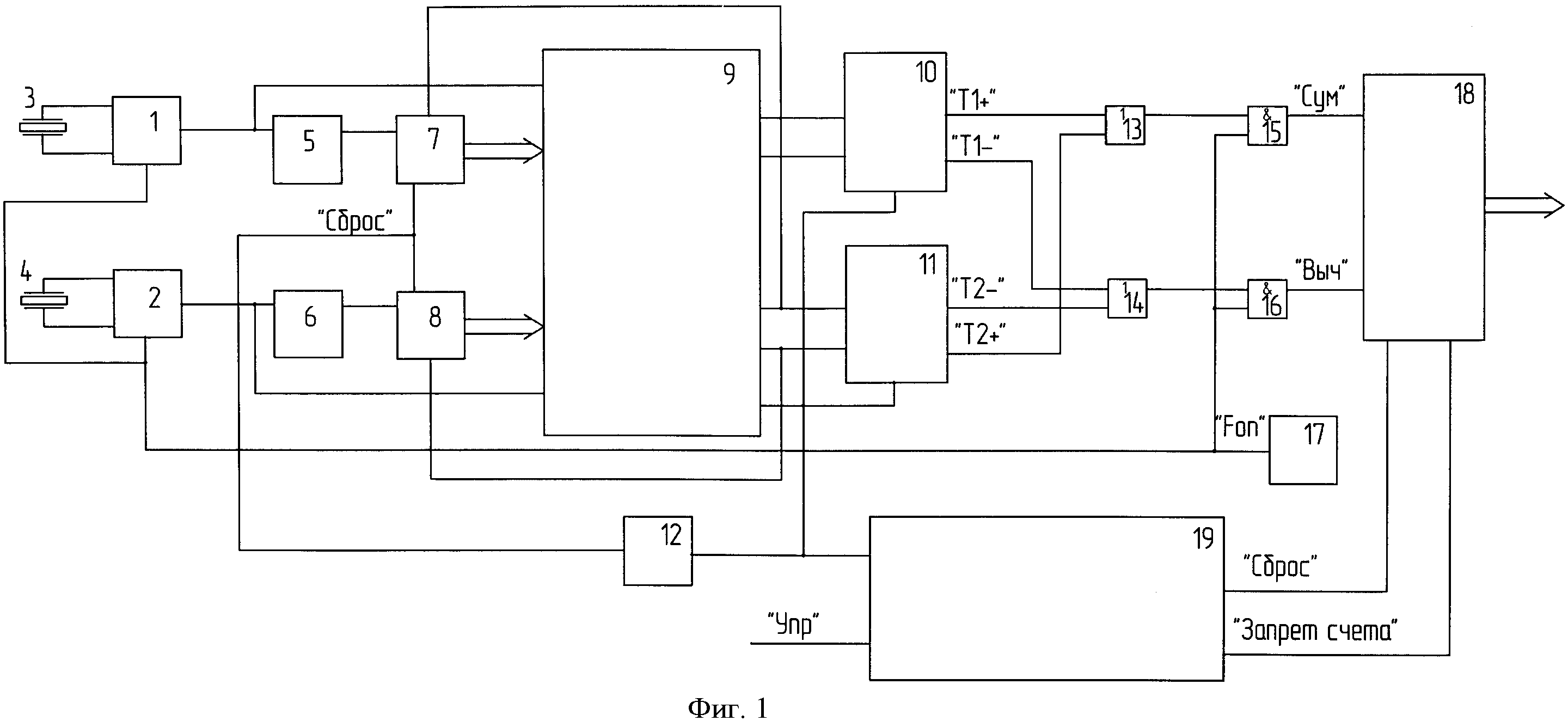

На фиг. 1 изображена функциональная схема дифференциального преобразователя. На фиг. 2 и фиг. 3 изображены электрическая принципиальная схема блока управления и фазового компаратора. На фиг. 4 изображена электрическая принципиальная схема блока управления реверсивным счетчиком.

Дифференциальный измерительный преобразователь (см. фиг. 1) содержит первый 1 и второй 2 генераторы частотных сигналов с частотозадающими элементами 3 и 4, первый фазовый компаратор (ФК) 10, первый 5, второй 6 и третий 12 элементы задержки, первый 7 и второй 8 счетчики, блок управления (БУ) 9, второй фазовый компаратор (ФК) 11, первый 13 и второй 14 сумматоры сигналов, первый 15 и второй 16 квантователи сигналов (логический элементы 2И), генератор опорной частоты 17, реверсивный счетчик 18 и блок его управления 19, первый и второй выходы которого соединены соответственно со входом сброса и входом запрета счета реверсивного счетчика 18, выход которого является выходом устройства. Суммирующий и вычитающий входы реверсивного счетчика 18 соединены соответственно через первый 15 и второй 16 квантователи сигналов с выходами первого 13 и второго 14 сумматоров, первые входы которых соединены с первым и вторым выходами первого фазового компаратора 10, а вторые их входы соединены со вторым и первым выходами второго фазового компаратора 11, первые входы первого 10 и второго 11 фазовых компараторов объединены между собой и соединены с входом третьего элемента задержки 12 и с первым входом блока управления реверсивным счетчиком 19, второй вход которого является управляющим входом. Блок управления 9 (см. фиг. 2) включает в себя первый 20 и второй 21 дешифраторы, первый 22, второй 23 и третий 24 логические элементы 2И, выходы первого 22 и второго 23 логических элементов 2И соединены со вторым и третьим входами первого фазового компаратора 10, выход третьего логического элемента 2И 24 соединен с первыми входами фазовых компараторов 10, 11, выход третьего элемента задержки 12 соединен со входами сброса первого 7 и второго 8 счетчиков, группы выходов которых соединены с группами входов первого 20 и второго 21 дешифраторов, первые выходы которых соединены с первыми входами первого 22 и второго 23 логических элементов 2И, вторые входы которых соединены с выходами первого 1 и второго 2 генераторов частотных сигналов. Вторые выходы дешифраторов 20, 21 соединены со входами третьего логического элемента 2И 24, вторым и третьим входами второго фазового компаратора 11 и входами запрета счета первого 7 и второго 8 счетчиков, счетные входы которых через первый 5 и второй 6 элементы задержки соединены с выходами первого 1 и второго 2 генераторов частотных сигналов, входы синхронизации которых объединены и соединены с выходом генератора опорной частоты 17 и со вторыми входами квантователей сигналов 15, 16.

Фазовые компараторы 10, 11 (см. фиг. 3) выполнены идентичными, каждый из которых содержит первый D-триггер 25, второй D-триггер 26, первый логический элемент ИЛИ 27 и второй логический элемент ИЛИ 28. Входами 39, 40 ФК являются входы "С" D-триггеров 25, 26, а выходами ФК являются их прямые выходы 41, 42. Инверсный выход D-триггера 25 соединен со входом "D" D-триггера 26, а инверсный выход D-триггера 26 соединен со входом "D" D-триггера 25. Входы "S" D-триггеров 25, 26 соединены с общей шиной питания, а входы "R" соединены с выходами логических элементов ИЛИ 27, 28, первые входы которых объединены и соединены с выходом 54 логического элемента 2И 24 из состава БУ 9. Вторые входы логических элементов ИЛИ 27, 28 соединены со входами "С" D-триггеров 26, 25 соответственно.

Устройство управления реверсивным счетчиком 19 (см. фиг. 4) содержит первый 29, второй 30, третий 31, четвертый 32 D-триггеры, счетчик циклов 33, дешифратор кода 34, первый 35 и второй 36 конденсаторы, первый 37 и второй 38 резисторы. Управляющим входом 44 блока управления реверсивным счетчиком 19 является вход "С" D-триггера 29, прямой выход которого соединен через первый резистор 37 со входом "R" D-триггера 29, со входом сброса счетчика циклов 33, со входом "С" D-триггера 30, является первым выходом 45 блока управления реверсивным счетчиком 19, который соединен со входом "сброс" реверсивного счетчика 18. Вход "R" D-триггера 29 через конденсатор 35 соединен с общей шиной питания. Счетный вход счетчика циклов 33 соединен со входом "С" D-триггера 31 и является первым входом 46 блока управления реверсивным счетчиком 19. Прямой выход D-триггера 30 соединен со входом "D" D-триггера 31, прямой выход которого является вторым выходом 47 блока управления реверсивным счетчиком 19 и соединен со входом запрета счета реверсивного счетчика 18. Группа выходов счетчика циклов 33 соединена с группой входов дешифратора кода 34, выход которого соединен со входом запрета счета счетчика циклов 33 и со входом "С" D-триггера 32, прямой выход которого соединен с объединенными между собой входами "R" D-триггеров 30, 31, через резистор 38 со входом "R" D-триггера 32, вход "R" которого через конденсатор 36 соединен с общей шиной питания. Входы "D" D-триггеров 29, 30, 32 подключены к плюсовой шине питания, а входы "S" D-триггеров 29, 30, 31, 32 соединены с общей шиной питания.

Устройство работает следующим образом. При подключении питания к устройству триггеры счетчиков 7, 8 и ФК 10, 11 устанавливаются в случайное произвольное состояние ("0" или "1"). Генераторы 1, 2, 17 после переходного процесса устанавливают на своих выходах импульсные сигналы с заданными параметрами (амплитуда, длительность, частота). Счетчики 7, 8 начинают счет поступающих на их входы импульсы последовательностей f1, f2, при этом состояние их выходного кода будет меняться, и по достижению состояния соответствующему заданному числу "n" одним из счетчиков 7 или 8, сигналом с выхода 48 (49) дешифратора 20 или 21 БУ 9 осуществляется запрет на дальнейший счет счетчиком 7 или 8 с сохранением достигнутого состояния "n", а также выдается сигнал на соответствующий вход элемента "2И" 24 в БУ 9 (см. фиг. 2). При достижении состояния "n" другим счетчиком 7 или 8 с выхода, соединенного с ним дешифратора 20 или 21, поступит сигнал на другой вход элемента "2И" 24, при этом на его выходе появится сигнал "сброс", поступающий на входы сброса фазовых компараторов 10, 11 и через элемент задержки 12 на входы сброса счетчиков 7, 8, которые устанавливаются в состояние "0", что соответствует исходному состоянию устройства и началу цикла преобразования.

Дешифраторы 20, 21 выделяют два состояния счетчиков: состояние "0", устанавливаемое по сигналу "сброс", и состояние "n", которое соответствует набору заданного числа n входных импульсов. В состоянии "0" счетчика 7 (8) разрешается передача выходных импульсов генератора 1 (2), поступающих на вход 50 (51) БУ 9 и через логический элемент 2И 22 (23) (см. фиг. 2) на выход 52 (53) БУ 9 и на вход 39 (40) ФК 10, на выходе 41 (42) которого устанавливается уровень "1". В состоянии "n" счетчика 7 (8) на выходе 48 (49) БУ 9 устанавливается уровень "1", поступающих на вход 39 (40) ФК 11 и вход запрета счетчика 7 (8). В случае, когда оба счетчика 7, 8 устанавливаются в состоянии ″n″, на выходе логического элемента "2И" 24 формируется сигнал "сброс" на выходе 54 БУ 9, поступающий на входы 43 сброса ФК 10, 11, на вход 46 блока управления реверсивным счетчиком 19 и через элемент задержки 12 на вход сброса счетчиков 7, 8.

ФК 10, 11 позволяют определять очередность поступающих на их входы 39, 40 несовпадающих импульсных сигналов. В случае поступления сигнала первым на вход 39 (40) ФК 10 (11), D-триггер 25 (26) установится в состояние "1", передавая на свой выход 41 (42) соответствующий уровень ("1"). При этом состояние D-триггера 26 (25) и уровень сигнала на выходе 42 (41) остается неизменным (равным "0"). Таким образом, в случае подачи на входы 39, 40 ФК 10, 11 пары несовпадающих во времени импульсов с интервалом Δt на одном из его выходов будет сформирован импульс напряжения с длительностью Δt, равной их разновременности поступления на входы 39, 40.

Опережающий импульс в паре импульсов, поступающей на входы 39 (40) ФК 10 (11) устанавливает по входу "С" один из его D-триггеров 25 (26) в состояние "1", а запаздывающий импульс сбрасывает его по входу "R" в исходное состояние "0". Изменение состояния D-триггера передается на один из выходов ФК 10 (11). Длительность выходного импульса равна разновременности поступления сигналов на входы 39 (40) ФК 10 (11), а привязка сигнала к конкретному выходу определяет принадлежность к входу, на который поступил опережающий сигнал. Пары импульсных сигналов, поступающих от БУ 9 на входы 39, 40 ФК 10, 11, разделены во времени, по крайней мере, на n периодов меньшей из частот генераторов 1, 2. Выходные сигналы ФК 10, 11 поступают на сумматоры сигналов 13, 14 (логические элементы 2 ИЛИ). При этом суммирование разнесенных во времени выходных сигналов ФК 10, 11 в каждом цикле преобразования, возможно только в двух комбинациях:

- при наличии опережающего сигнала на входе 39 ФК 10 и на входе 40 ФК 11 выходные сигналы ФК 10 и ФК 11 поступают на входы сумматора сигналов 13;

- при наличии опережающего сигнала на входе 40 ФК 10 и на входе 39 ФК 11 выходные сигналы ФК 10 и ФК 11 поступают на входы сумматора сигналов 14.

Выходные сигналы дешифраторов 20, 21, поступающие на входы элементов 2И 22, 23, разрешают прохождение выходных сигналов f1, f2 генераторов 1, 2 на входы 39, 40 ФК 10. Под действием импульсных сигналов последовательностей f1, f2, прошедших на выход элементов 2И 22, 23, будет изменено состояние одного из D-триггеров 25 или 26. В случае, если импульс последовательности f1 опередит импульс последовательности f2, в состояние "1" будет установлен D-триггер 25 с соответствующим изменением уровня напряжения на выходе 41 ФК 10. На входе "D" D-триггера 26 установлен нулевой уровень, препятствующий смене его состояния сигналом по входу "С". Приход запаздывающего импульса последовательности f2 на вход 40 ФК 10, не изменяя состояния D-триггера 26, установит в исходное (нулевое) состояние D-триггер 25 с соответствующим изменением напряжения на выходе 41 ФК 10. В случае, если импульс последовательности f2 опередит импульс последовательности f1 в состояние "1" будет установлен D-триггер 26 с соответствующим напряжением на выходе 42 ФК 10 и уровнем "0" на входе D-триггера 25. Выходной сигнал ФК 10, в зависимости от очередности поступления на его входы через элементы "2И" 22, 23 импульсов последовательностей f1, f2, формируется на выходе 41 или 42 в виде однократного (за цикл преобразования) импульса с длительностью  на выходе 41 и

на выходе 41 и  на выходе 42, равной разновременности прихода импульсных сигналов на входы 39, 40 ФК 10, и через сумматор сигнала 13 или 14 поступает на первый вход квантователя сигналов (элемент 2И) 15 или 16. Это приводит к появлению на выходе квантователя сигналов 15 или 16, соответственно, на входе "сложение" или "вычитание" реверсивного счетчика 18 пачки импульсов с частотой генератора опорного сигнала 17 fоп. Первый импульс на входе каждого из счетчиков 7 (8), изменяя их исходное состояние и соответственно уровень сигнала на выходе дешифраторов 20 (21), запрещает прохождение последующих импульсов последовательностей f1 и f2 на входы 39, 40 ФК 10.

на выходе 42, равной разновременности прихода импульсных сигналов на входы 39, 40 ФК 10, и через сумматор сигнала 13 или 14 поступает на первый вход квантователя сигналов (элемент 2И) 15 или 16. Это приводит к появлению на выходе квантователя сигналов 15 или 16, соответственно, на входе "сложение" или "вычитание" реверсивного счетчика 18 пачки импульсов с частотой генератора опорного сигнала 17 fоп. Первый импульс на входе каждого из счетчиков 7 (8), изменяя их исходное состояние и соответственно уровень сигнала на выходе дешифраторов 20 (21), запрещает прохождение последующих импульсов последовательностей f1 и f2 на входы 39, 40 ФК 10.

После формирования импульса на одном из выходов первого ФК 10 через интервал времени, равный n периодам следования импульсов последовательности f1 или f2, один из счетчиков 7 или 8 первым устанавливается в состояние "n" и с выхода соответствующего дешифратора 20 или 21 через выходы 48 или 49 на вход 39 или 40 ФК 11 и вход элемента "2И" 24 поступает сигнал, устанавливающий соответствующий D-триггер 25 или 26 в состояние "1". Это состояние передается через сумматор сигналов 14 или 13 на вход квантователя сигналов 16 или 15, на выходе которого начнется формирование пачки импульсов с частотой foп, подаваемой на вход "вычитание" или "сложение" реверсивного счетчика 18. После набора числа n импульсов "отстающим" счетчиком 8 или 7 на выходе соответствующего дешифратора 21 или 20 появляется перепад напряжения, передаваемый на вход 40 или 39 ФК 11, вход элементов "2И" 24. При этом происходит возврат D-триггера 25 или 26 ФК 11 в исходное состояние, формирование импульса сброса на выходе элемента "2И" 24, передача его через элемент задержки 12 на входы сброса счетчиков 7, 8. Одновременно завершается формирование импульсов длительностью  ,

,  на выходе 42 или 41 ФК 11, а на выходе сумматора сигналов 14 или 13 завершается формирование пачки импульсов на выходе квантователя сигналов 15 или 16 и подаваемых соответственно на вход "вычитание" или "суммирование" реверсивного счетчика 18, и формируется импульс сброса на выходе элемента "2И" 24, передаваемый на входы 43 ФК 10, 11, на первый вход 46 устройства управления реверсивным счетчиком и через элемент задержки 12 на входы сброса счетчиков 7, 8, завершая тем самым очередной цикл преобразования.

на выходе 42 или 41 ФК 11, а на выходе сумматора сигналов 14 или 13 завершается формирование пачки импульсов на выходе квантователя сигналов 15 или 16 и подаваемых соответственно на вход "вычитание" или "суммирование" реверсивного счетчика 18, и формируется импульс сброса на выходе элемента "2И" 24, передаваемый на входы 43 ФК 10, 11, на первый вход 46 устройства управления реверсивным счетчиком и через элемент задержки 12 на входы сброса счетчиков 7, 8, завершая тем самым очередной цикл преобразования.

До прихода управляющего импульса на вход 44 блока управления реверсивным счетчиком 19, на его выходе 47 установлен запрет на счет реверсивного счетчика 18. При подаче управляющего сигнала на вход 44 блока управления реверсивным счетчиком 19 в виде короткого импульса, на выходе D-триггера 29 формируется импульс на сброс счетчика циклов 33, сброс реверсивного счетчика 18, и D-триггер 30 устанавливается в состояние "1". Длительность импульса на выходе D-триггера 29 определяется параметрами времязадающей RC-цепи, состоящей из конденсатора 35 и резистора 37.

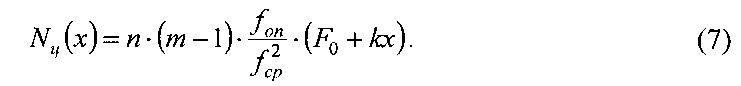

С приходом импульса окончания цикла, с выхода элемента "2И" 24 D-триггер 31 устанавливается в состояние "1", разрешая счет реверсивному счетчику 18 пачек импульсов, подаваемых на его входы "вычитание" или "суммирование" и при этом начинает отсчет счетчик циклов 33. За один цикл преобразования состояние реверсивного счетчика 18 определяется алгебраической суммой чисел импульсов в пачках, поданных на его входы в начале и в конце цикла преобразования. При достижении счетчика циклов 33 состояния "m", на выходе дешифратора кода 34 устанавливается сигнал запрета счета счетчику циклов 33, при этом на выходе D-триггера 32 формируется импульс, по которому D-триггеры 30, 31 устанавливаются в исходное (нулевое) состояние и на выходе 47 формируется сигнал запрета счета реверсивному счетчику 18. Длительность импульса на выходе D-триггера 32 определяется параметрами времязадающей RC-цепи, состоящей из конденсатора 36 и резистора 38. В реверсивном счетчике 18 сохраняется цифровой код, накопленный за "(m-1)" число циклов, т.к. на "m" цикле преобразования счет реверсивным счетчиком 18 не производится. Далее цифровой код с группы выходов реверсивного счетчика 18 может быть считан потребителем для дальнейших преобразований. При следующей подаче управляющего сигнала на вход 44 блока управления реверсивным счетчиком 19 процесс счета повторяется.

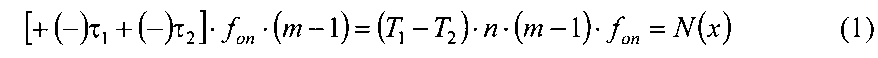

Двоичный код числа за (m-1) цикл преобразования определяется функционалом:

где τ1, τ2 - интервалы времени, определяющие разновременность прихода импульсов последовательностей f1, f2 на входы первого и второго ФК 10, 11 в начале и конце цикла преобразования;

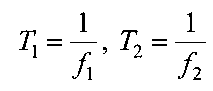

- периоды следования сигналов последовательностей f1, f2 соответственно;

- периоды следования сигналов последовательностей f1, f2 соответственно;

N(x) - число импульсов, фиксируемое реверсивным счетчиком 18 за (m-1) циклов преобразования.

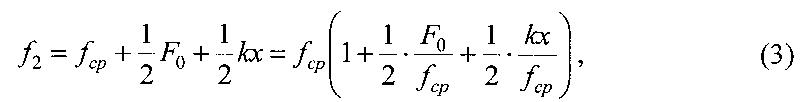

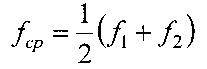

Значение частот f1, f2 генераторов 1, 2 может быть представлено в виде следующих сумм:

где  - среднее значение выходных частот генераторов 1, 2;

- среднее значение выходных частот генераторов 1, 2;

х - измеряемый параметр на входе первичных преобразователей 3, 4;

k - коэффициент преобразования датчиков 3, 4;

F0 - начальная разность частот f1, f2 при х=0.

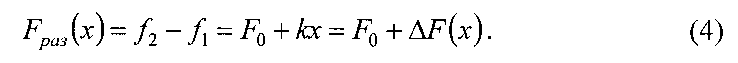

Выходной величиной дифференциального преобразователя прототипа является разность частот

С учетом выражений (2), (3) выражение (1) будет иметь вид:

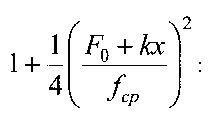

При практической реализации дифференциального преобразователя значения отношений частот  и

и  не превышает 0,1 и выражение (5) можно представить в виде:

не превышает 0,1 и выражение (5) можно представить в виде:

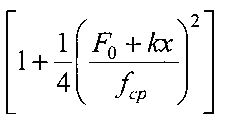

Или, с учетом малости члена

Таким образом, функция преобразования (7) заявляемого устройства подобна функции преобразования (4) прототипа. Наличие множителя  приводит к появлению некоторой незначительной нелинейности, которая при необходимости может быть учтена.

приводит к появлению некоторой незначительной нелинейности, которая при необходимости может быть учтена.

Работоспособность изобретения подтверждена моделированием на ЭВМ и экспериментальными исследованиями макетов устройства.

Дифференциальный измерительный преобразователь, содержащий два генератора частотных сигналов с частотозадающими элементами, первый фазовый компаратор, отличающийся тем, что дополнительно введены первый, второй и третий элементы задержки, первый и второй счетчики, блок управления, второй фазовый компаратор, первый и второй сумматоры сигналов, первый и второй квантователи сигналов, генератор опорной частоты, реверсивный счетчик и блок его управления, первый и второй выходы которого соединены соответственно со входом сброса и входом запрета счета реверсивного счетчика, выход которого является выходом устройства, суммирующий и вычитающий входы которого соединены соответственно через первый и второй квантователи сигналов с выходами первого и второго сумматоров, первые входы которых соединены с первым и вторым выходами первого фазового компаратора, а вторые их входы соединены со вторым и первым выходами второго фазового компаратора, первые входы первого и второго фазовых компараторов объединены между собой и соединены с входом третьего элемента задержки и с первым входом блока управления реверсивным счетчиком, второй вход которого является управляющим входом, при этом блок управления включает в себя первый и второй дешифраторы, первый, второй и третий логические элементы 2И, выходы первого и второго логических элементов 2И соединены со вторым и третьим входами первого фазового компаратора, выход третьего логического элемента 2И соединен с первыми входами обоих фазовых компараторов, выход третьего элемента задержки соединен со входами сброса первого и второго счетчиков, группы выходов которых соединены с группами входов первого и второго дешифраторов, первые выходы которых соединены с первыми входами первого и второго логических элементов 2И, вторые входы которых соединены с выходами первого и второго генераторов частотных сигналов, вторые выходы дешифраторов соединены со входами третьего логического элемента 2И, вторым и третьим входами второго фазового компаратора и входами запрета счета первого и второго счетчиков соответственно, счетные входы которых через первый и второй элементы задержки соединены с выходами первого и второго генераторов частотных сигналов, входы синхронизации которых объединены и соединены с выходом генератора опорной частоты и со вторыми входами квантователей сигналов.