Результат интеллектуальной деятельности: МНОГОПОРТОВЫЙ КОНТРОЛЛЕР ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ПОРТАМИ, АССОЦИИРОВАННЫМИ С КЛАССАМИ ТРАФИКА

Вид РИД

Изобретение

УРОВЕНЬ ТЕХНИКИ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Это изобретение относится к области контроллеров запоминающего устройства.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Цифровые системы обычно включают в себя запоминающую систему, образованную из полупроводниковых запоминающих устройств, например статического оперативного запоминающего устройства (SRAM), динамического оперативного запоминающего устройства (DRAM), синхронного DRAM (SDRAM), SDRAM с удвоенной скоростью передачи данных (DDR, DDR2, DDR3 и т.д.), включая маломощные версии SDRAM (LPDDR, LPDDR2 и т.д.) и т.д. Запоминающая система является энергозависимой, хранящей данные во включенном состоянии, но не в выключенном, однако также обеспечивает доступ с малой задержкой по сравнению с энергонезависимыми запоминающими устройствами, такими как флэш-память, магнитные запоминающие устройства, например накопители на дисках, или оптические запоминающие устройства, например компакт-диск (CD), универсальный цифровой диск (DVD) и накопители BluRay.

[0003] Запоминающие устройства, образующие запоминающую систему, имеют низкоуровневый интерфейс для считывания и записи в запоминающее устройство в соответствии с зависящими от запоминающего устройства протоколами. Источники, которые формируют операции в запоминающем устройстве, обычно взаимодействуют через интерфейс более высокого уровня, например шину, интерфейс двухточечной пакетный передачи и т.п. Источники могут быть процессорами, периферийными устройствами, например устройствами ввода/вывода (I/O), аудио- и видеоустройствами и т.п. Как правило, операции в запоминающем устройстве включают в себя операции считывания запоминающего устройства для передачи данных из запоминающего устройства в устройство и операции записи в запоминающее устройство для передачи данных из источника в запоминающее устройство. Операции считывания запоминающего устройства в этом документе могут короче называться операциями считывания или считываниями, и аналогичным образом операции записи в запоминающее устройство в этом документе могут короче называться операциями записи или записями.

[0004] Соответственно, обычно имеется контроллер запоминающего устройства для приема операций в запоминающем устройстве от интерфейса более высокого уровня и управления запоминающими устройствами для выполнения принятых операций. Контроллер запоминающего устройства обычно также включает в себя очереди для захвата операций в запоминающем устройстве и может включать в себя схемы для повышения быстродействия. Например, некоторые контроллеры запоминающего устройства планируют операции считывания запоминающего устройства перед более ранними операциями записи в запоминающее устройство, которые затрагивают разные адреса.

[0005] Контроллеры запоминающего устройства обладают ограниченной видимостью разных типов трафика, который может выдаваться источниками. Соответственно, контроллеры запоминающего устройства не способы разделять трафик с меньшей крупностью разбиения. Таким образом, повышения быстродействия в контроллерах запоминающего устройства ограничены более грубыми механизмами, например планированием операций считывания до операций записи.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] В одном варианте осуществления контроллер запоминающего устройства может включать в себя несколько портов для приема запросов к запоминающему устройству. Каждый порт может ассоциироваться с конкретным типом трафика, например в реальном масштабе времени (RT), графики и не в реальном масштабе времени (NRT). Каждый тип трафика имеет разные требования и характеристику (поведение). В результате предоставления разных портов контроллер запоминающего устройства может параллельно подвергаться воздействию разных типов запросов и соответственно может принимать интеллектуальные решения по планированию на основе смеси трафика.

[0007] В некоторых вариантах осуществления разные порты могут использовать разные протоколы связи. Например, интерфейс центрального процессора (CPU) может использоваться для процессоров, графический интерфейс может использоваться для графических устройств и т.п. В некоторых вариантах осуществления сторонние производители могут разработать один или несколько интерфейсов и могут продавать устройства, которые взаимодействуют с использованием этих интерфейсов. Поскольку в контроллере запоминающего устройства поддерживаются разные порты, системы, которые заключают в себе и контроллер запоминающего устройства и сторонние устройства, могут отказаться от промежуточных схем для преобразования протоколов между сторонними устройствами и контроллером запоминающего устройства. Системы могут стать проще и дешевле, и можно устранить задержку, которая добавлялась бы промежуточными схемами.

[0008] В некоторых вариантах осуществления параметры качества обслуживания (QoS) могут передаваться контроллеру запоминающего устройства вместе с операциями в запоминающем устройстве. Контроллер запоминающего устройства может использовать относительные уровни QoS для планирования запросов к запоминающему устройству из портов в каналы запоминающего устройства. Разные типы трафика могут иметь разные спецификации уровней QoS, и контроллер запоминающего устройства может конфигурироваться для разрешения конфликтов между разными типами параметров QoS для планирования. Более того, средства управления совместным использованием полосы частот могут влиять на планирование.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0009] Нижеследующее подробное описание ссылается на прилагаемые чертежи, которые теперь описываются вкратце.

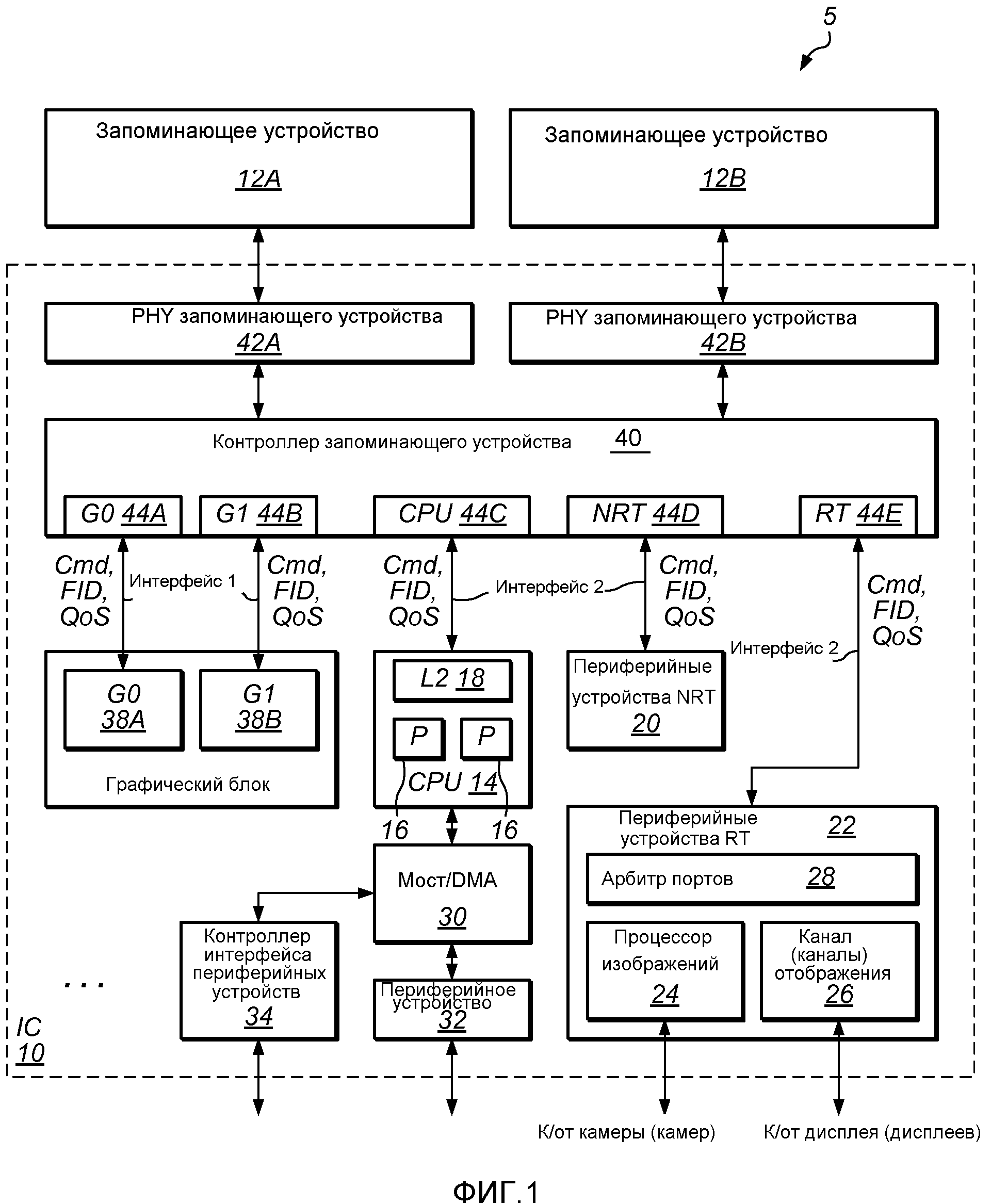

[0010] Фиг. 1 - блок-схема одного варианта осуществления системы, включающей в себя контроллер запоминающего устройства.

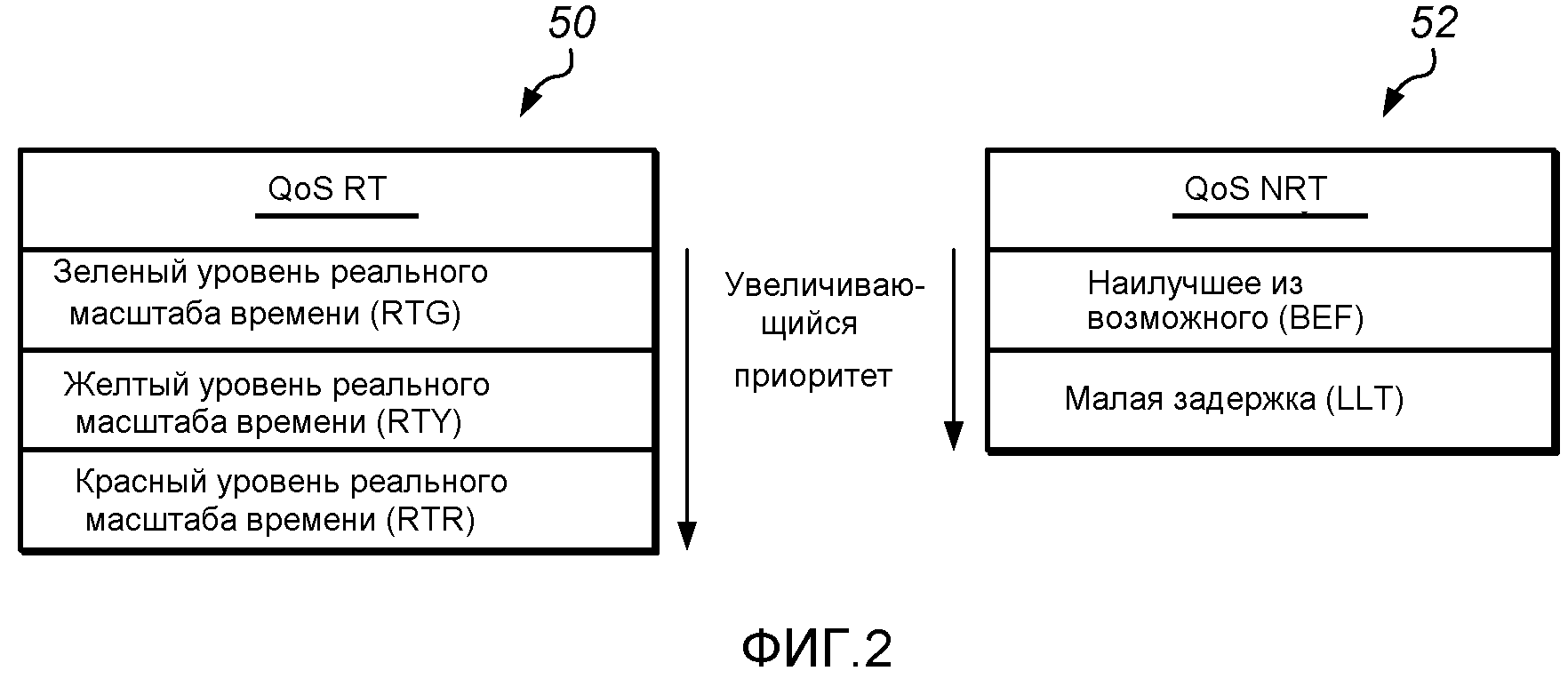

[0011] Фиг. 2 - блок-схема одного варианта осуществления уровней QoS, которые могут задаваться для классов RT и NRT трафика.

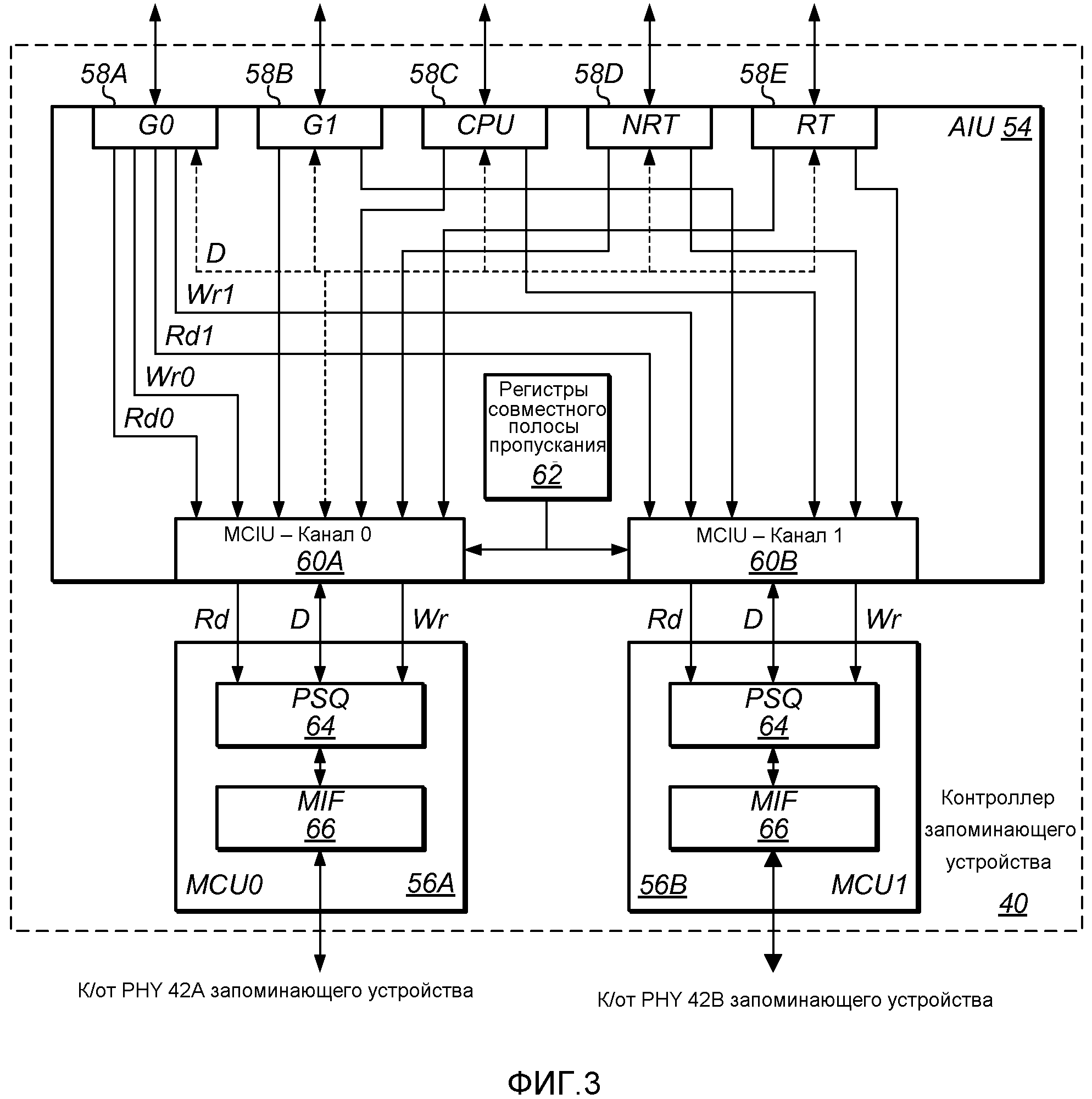

[0012] Фиг. 3 - блок-схема одного варианта осуществления контроллера запоминающего устройства, показанного на фиг. 1.

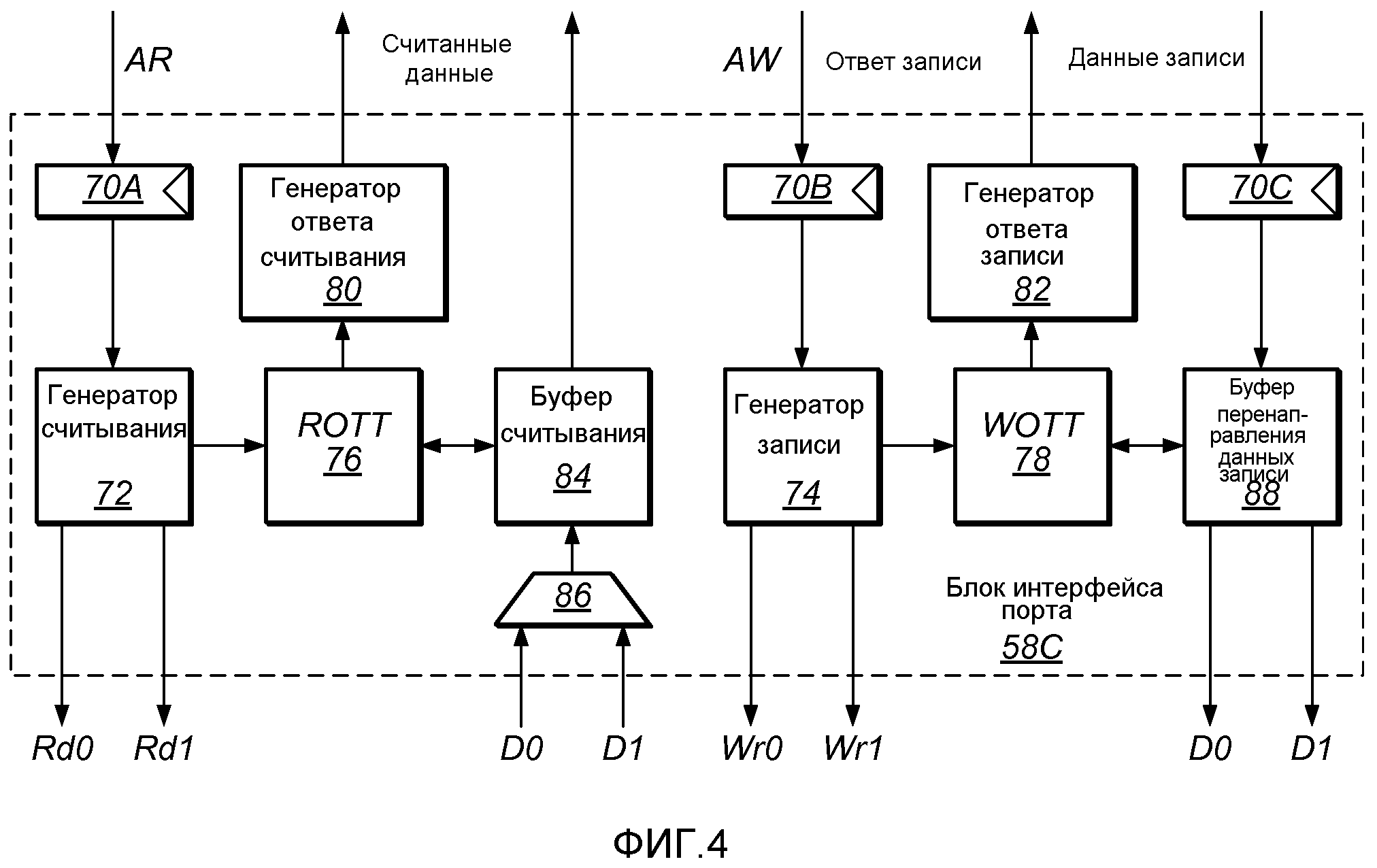

[0013] Фиг. 4 - блок-схема одного варианта осуществления блока интерфейса порта, который может включаться в один вариант осуществления блока интерфейса агента, показанный на фиг. 3.

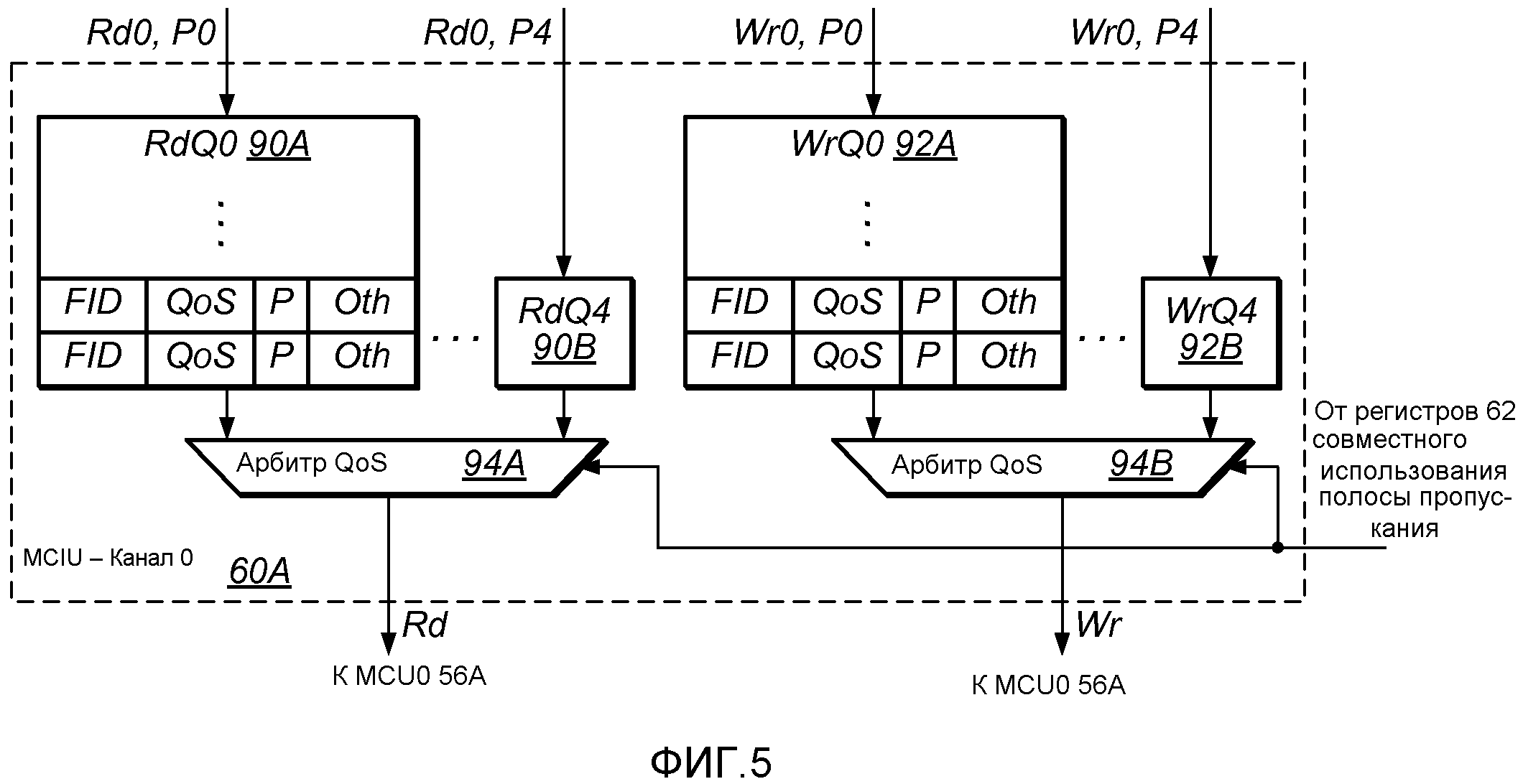

[0014] Фиг. 5 - блок-схема одного варианта осуществления блока интерфейса канала запоминающего устройства, который может включаться в один вариант осуществления блока интерфейса агента, показанный на фиг. 3.

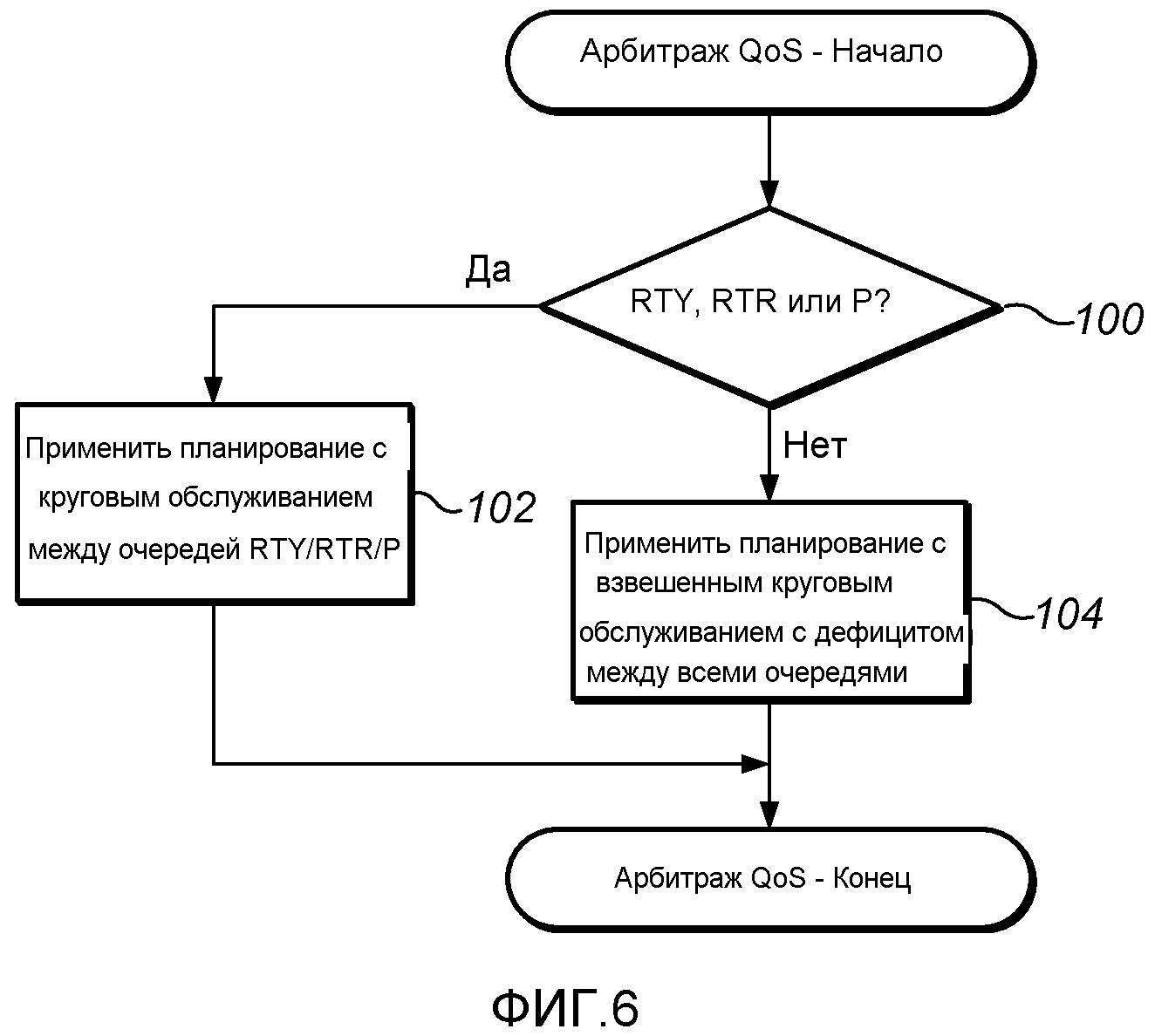

[0015] Фиг. 6 - блок-схема операций, иллюстрирующая работу одного варианта осуществления арбитра QoS, показанного на фиг. 5.

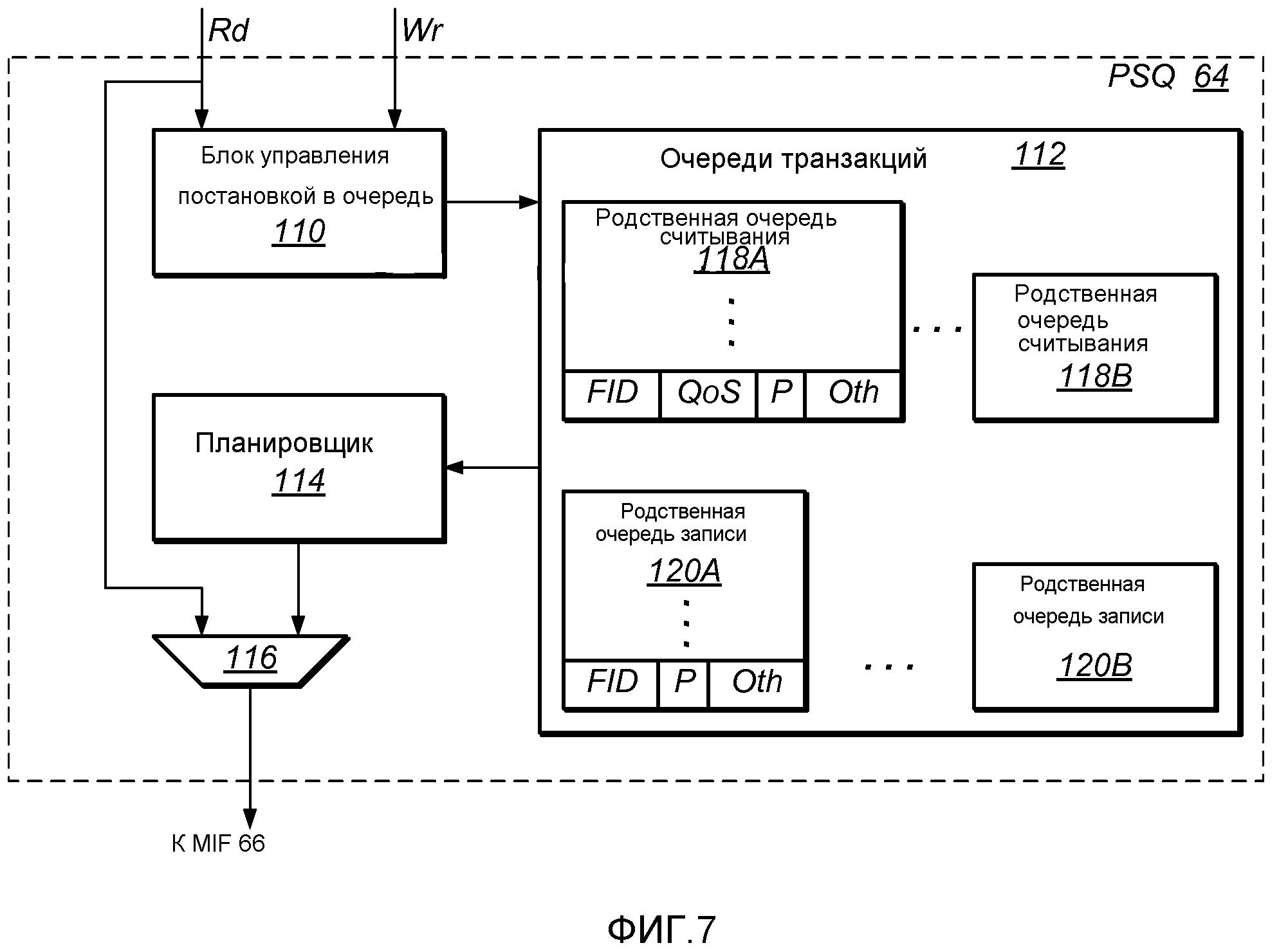

[0016] Фиг. 7 - блок-схема одного варианта осуществления очереди предварительной сортировки (PSQ), проиллюстрированной в блоке канала запоминающего устройства на фиг. 3.

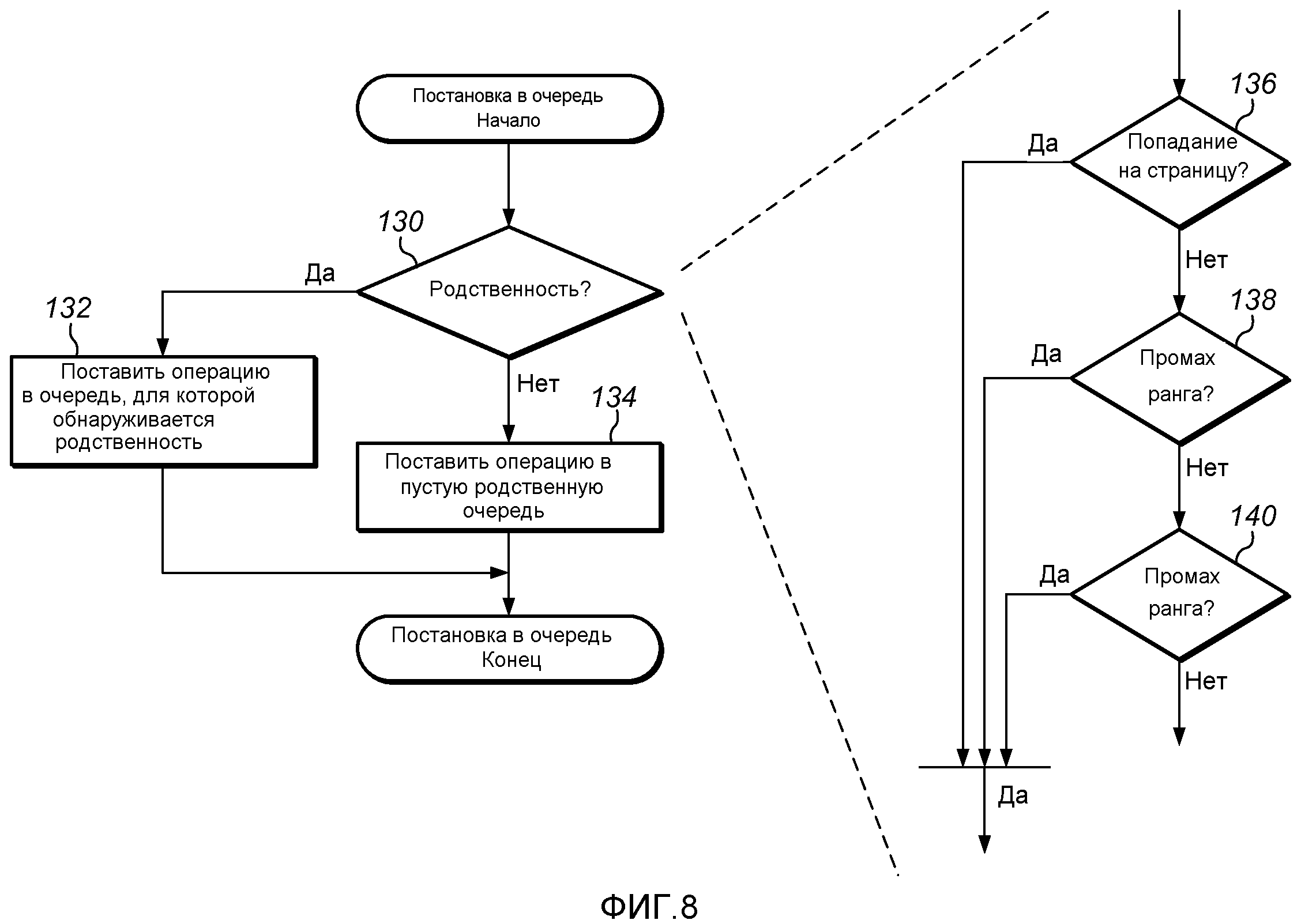

[0017] Фиг. 8 - блок-схема операций, иллюстрирующая работу одного варианта осуществления блока управления постановкой в очередь, показанного на фиг. 7.

[0018] Фиг. 9 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора между считываниями и записями, которые нужно планировать.

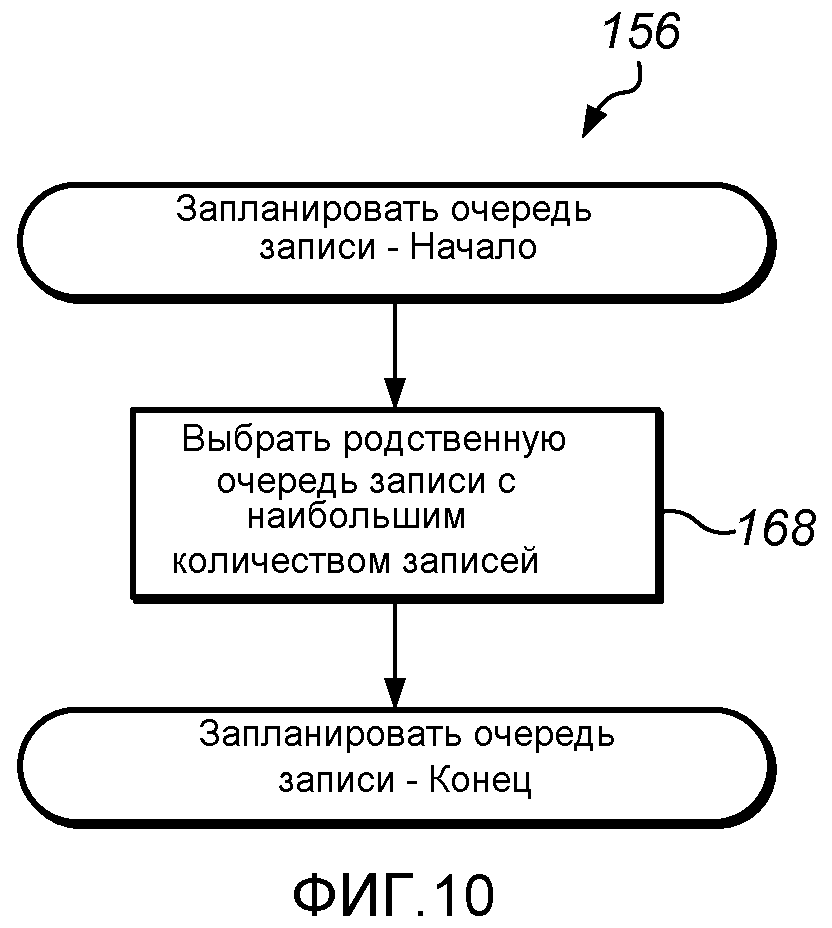

[0019] Фиг. 10 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора операции записи, которую нужно планировать.

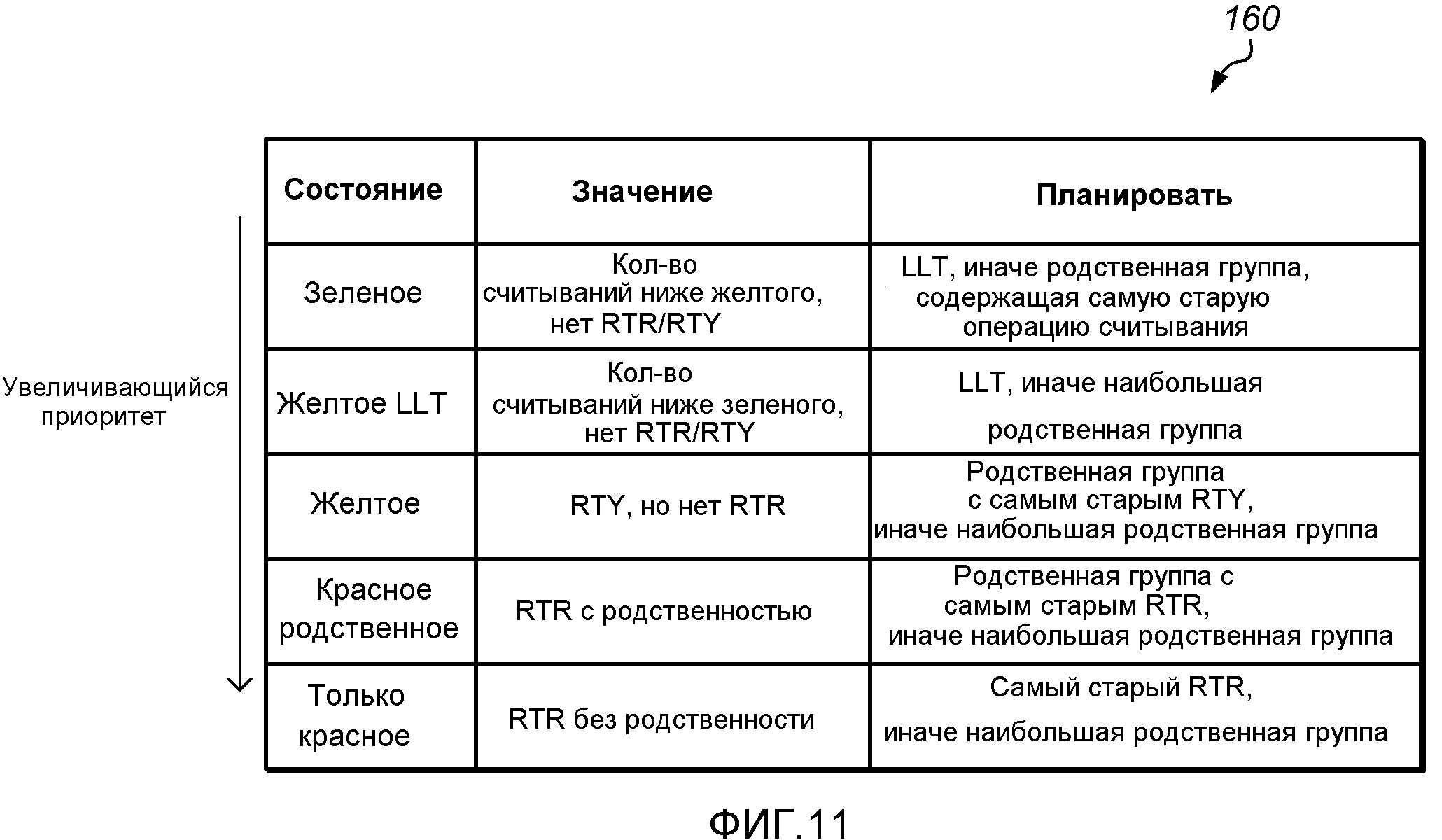

[0020] Фиг. 11 - таблица, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора считывания, которое нужно планировать.

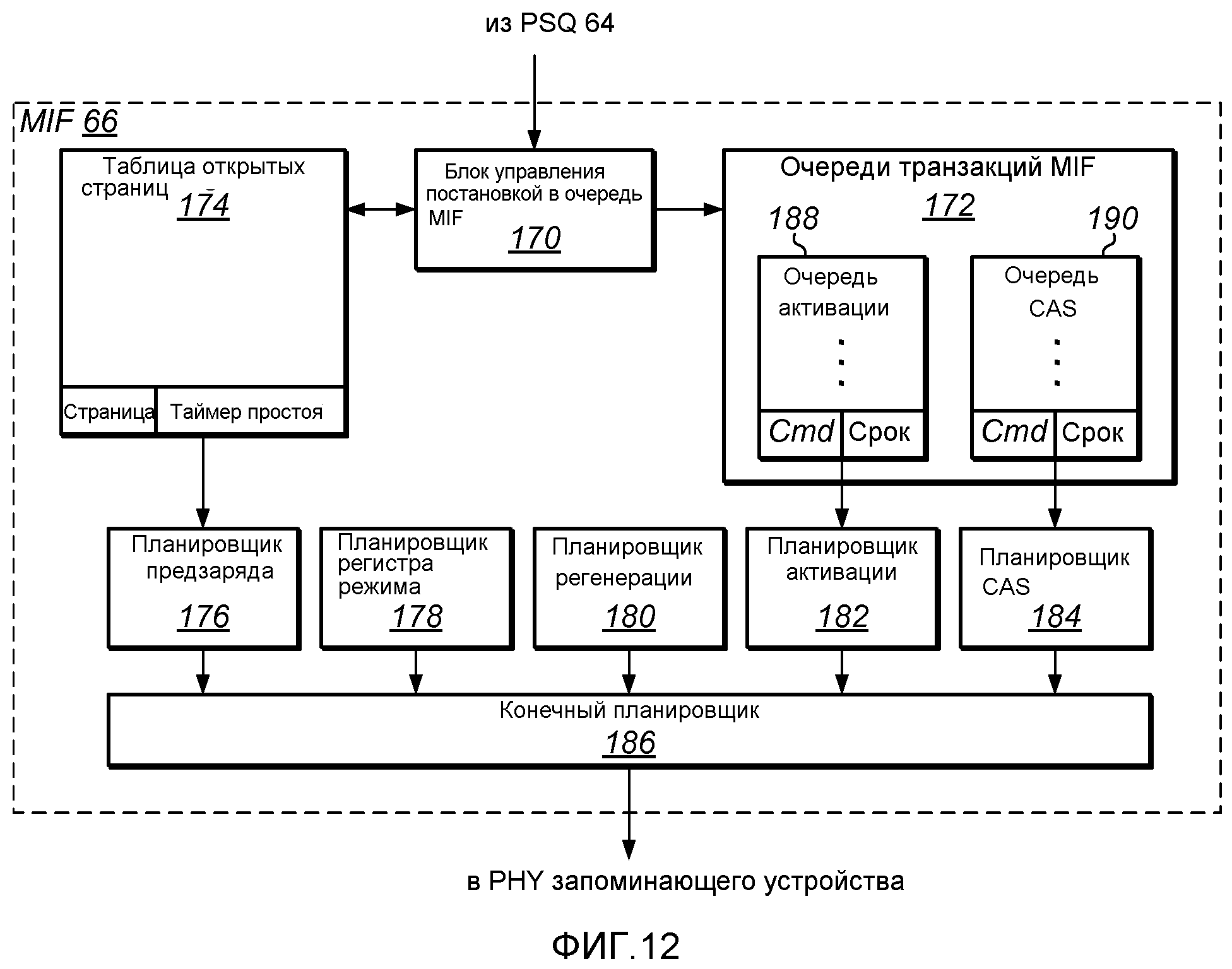

[0021] Фиг. 12 - блок-схема одного варианта осуществления блока интерфейса запоминающего устройства (MIF), показанного на фиг. 3.

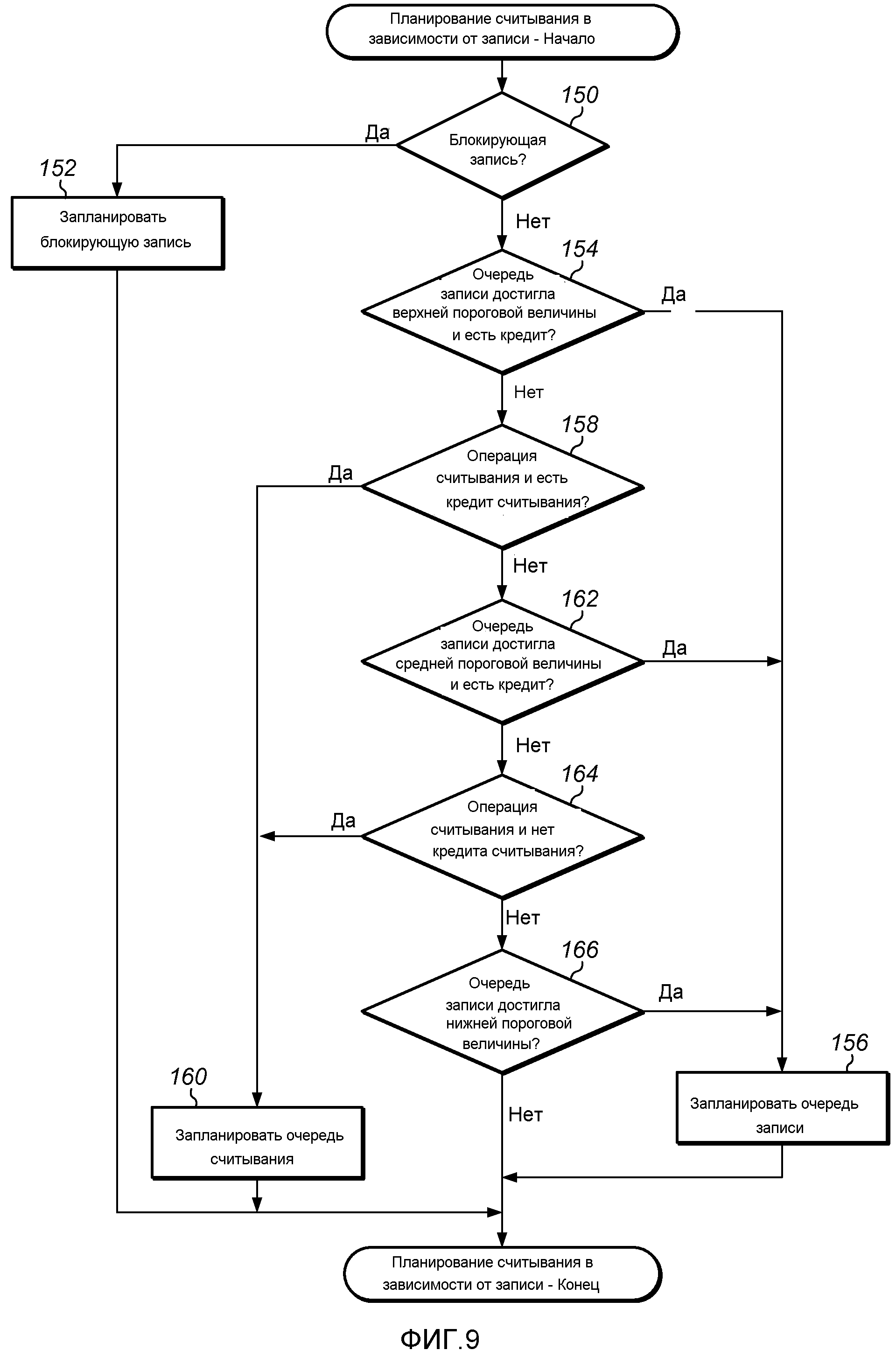

[0022] Фиг. 13 - блок-схема операций, иллюстрирующая работу одного варианта осуществления блока управления постановкой в очередь MIF, показанного на фиг. 12.

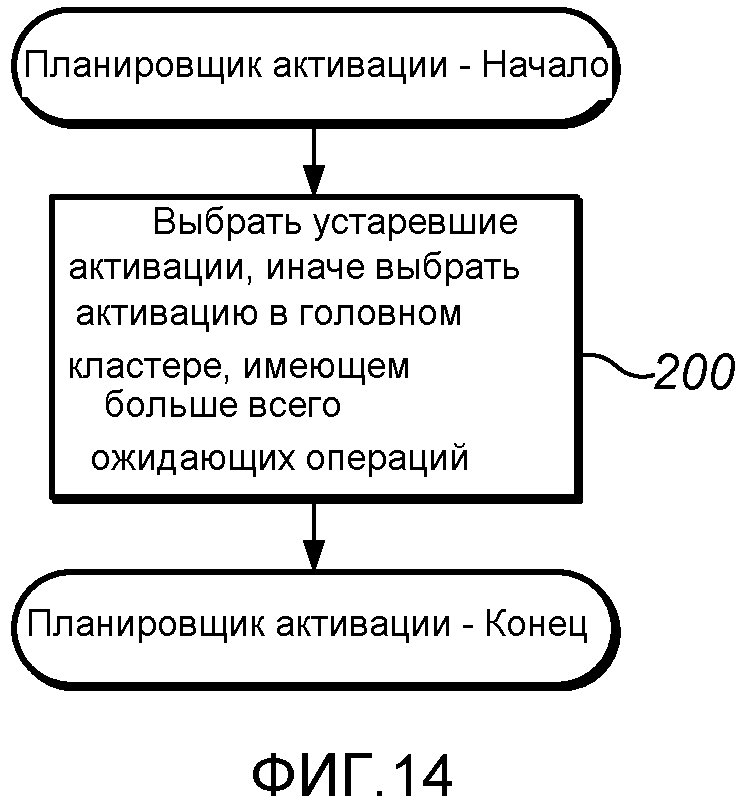

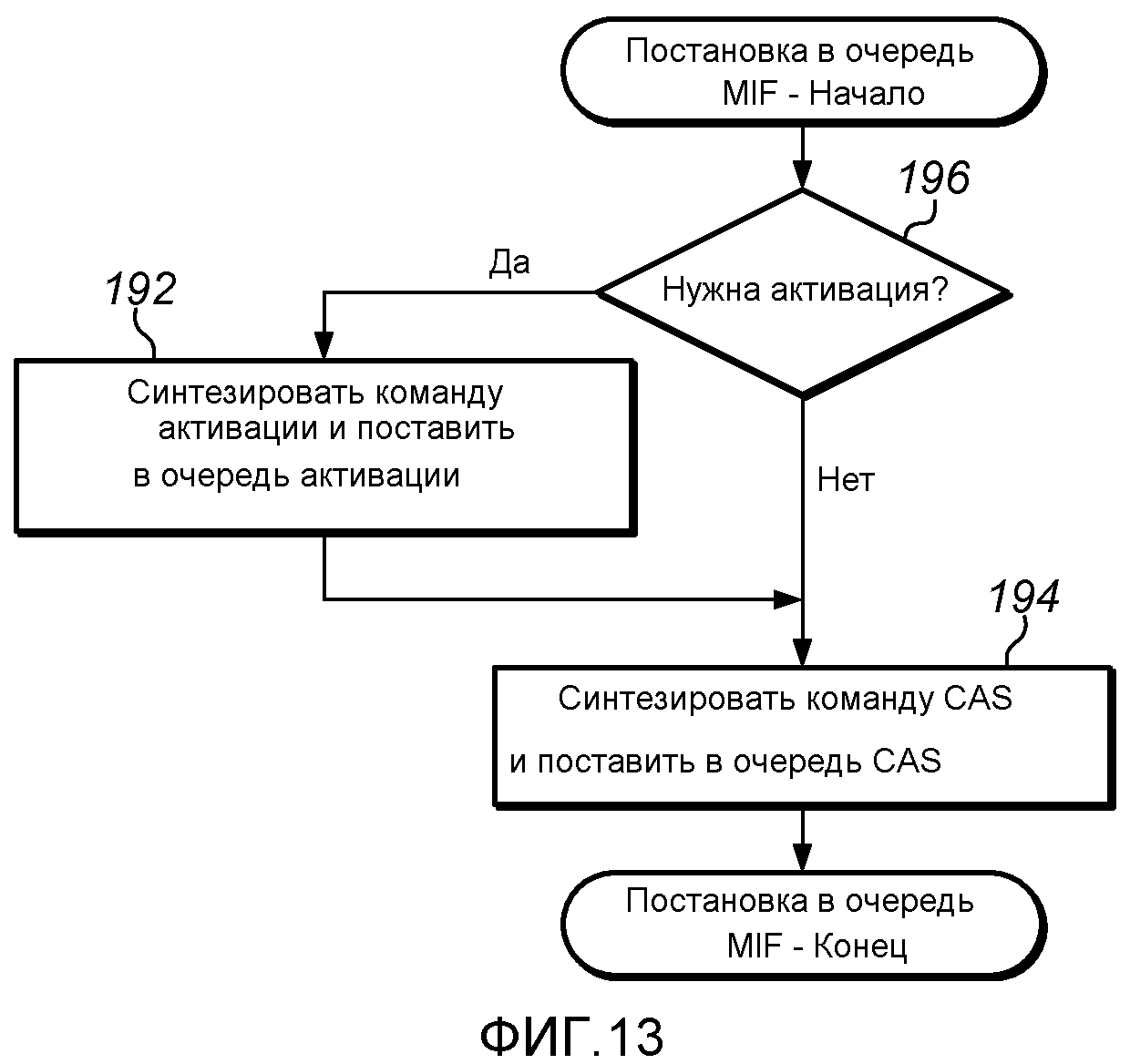

[0023] Фиг. 14 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика активации, показанного на фиг. 12.

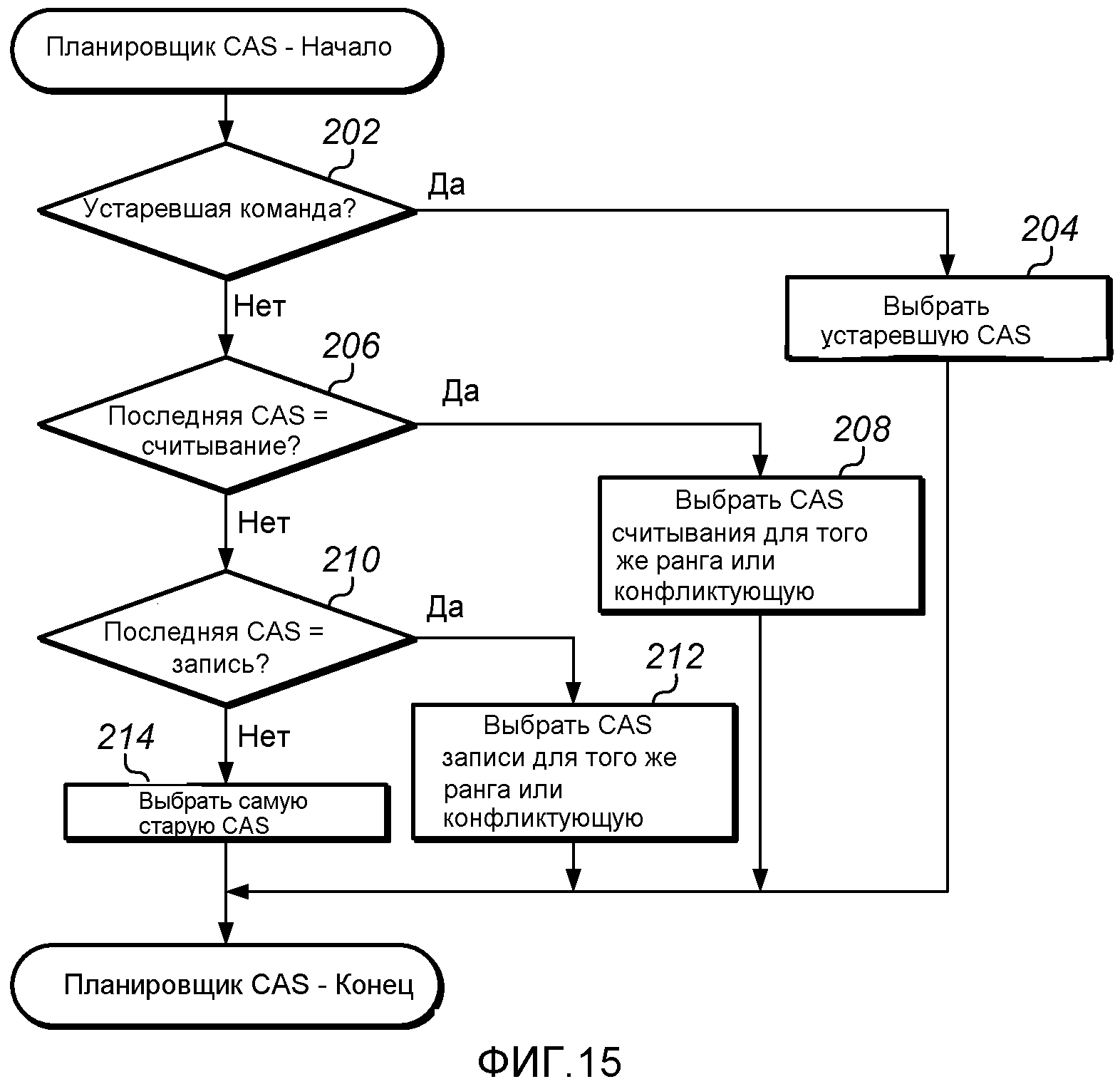

[0024] Фиг. 15 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика строба адреса столбца (CAS), показанного на фиг. 12.

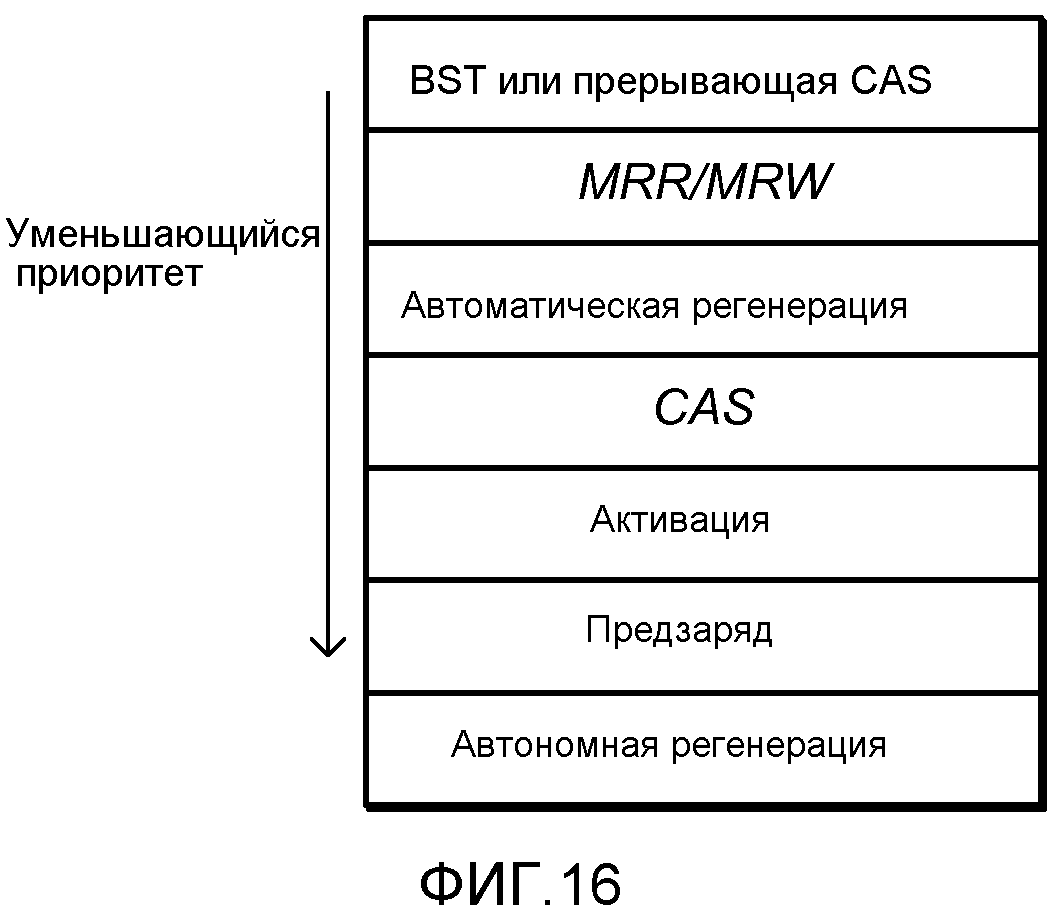

[0025] Фиг. 16 - таблица, иллюстрирующая работу одного варианта осуществления конечного планировщика, показанного на фиг. 12.

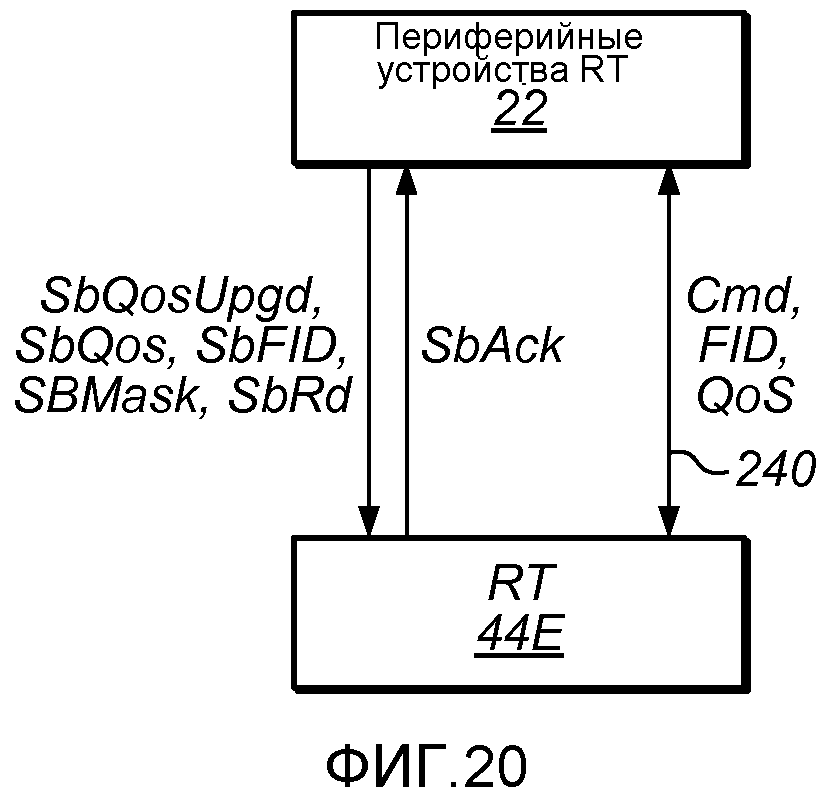

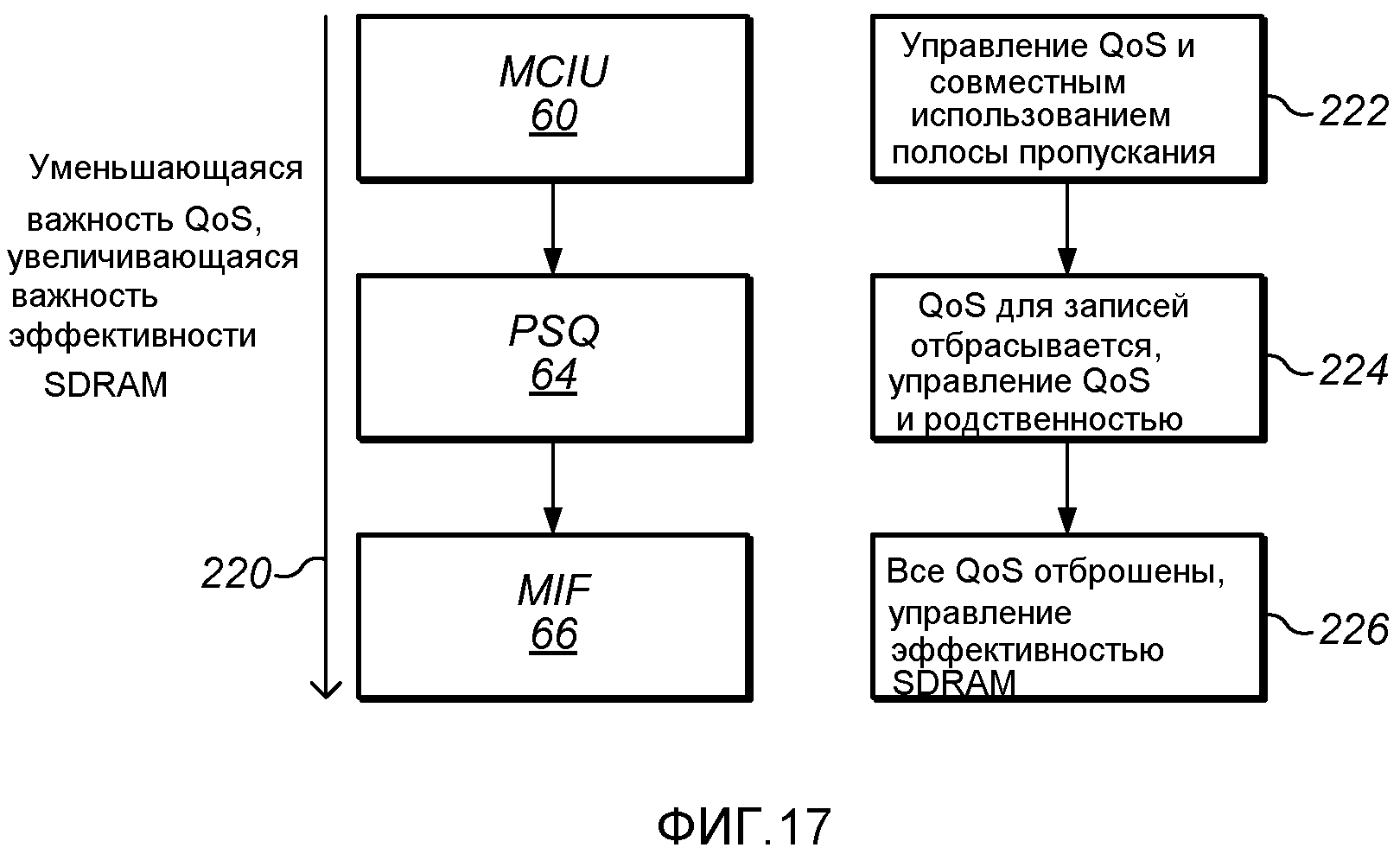

[0026] Фиг. 17 - блок-схема одного варианта осуществления организации очереди на высоком уровне и относительной важности параметров QoS и оптимизации пропускной способности запоминающего устройства при планировании на различных уровнях.

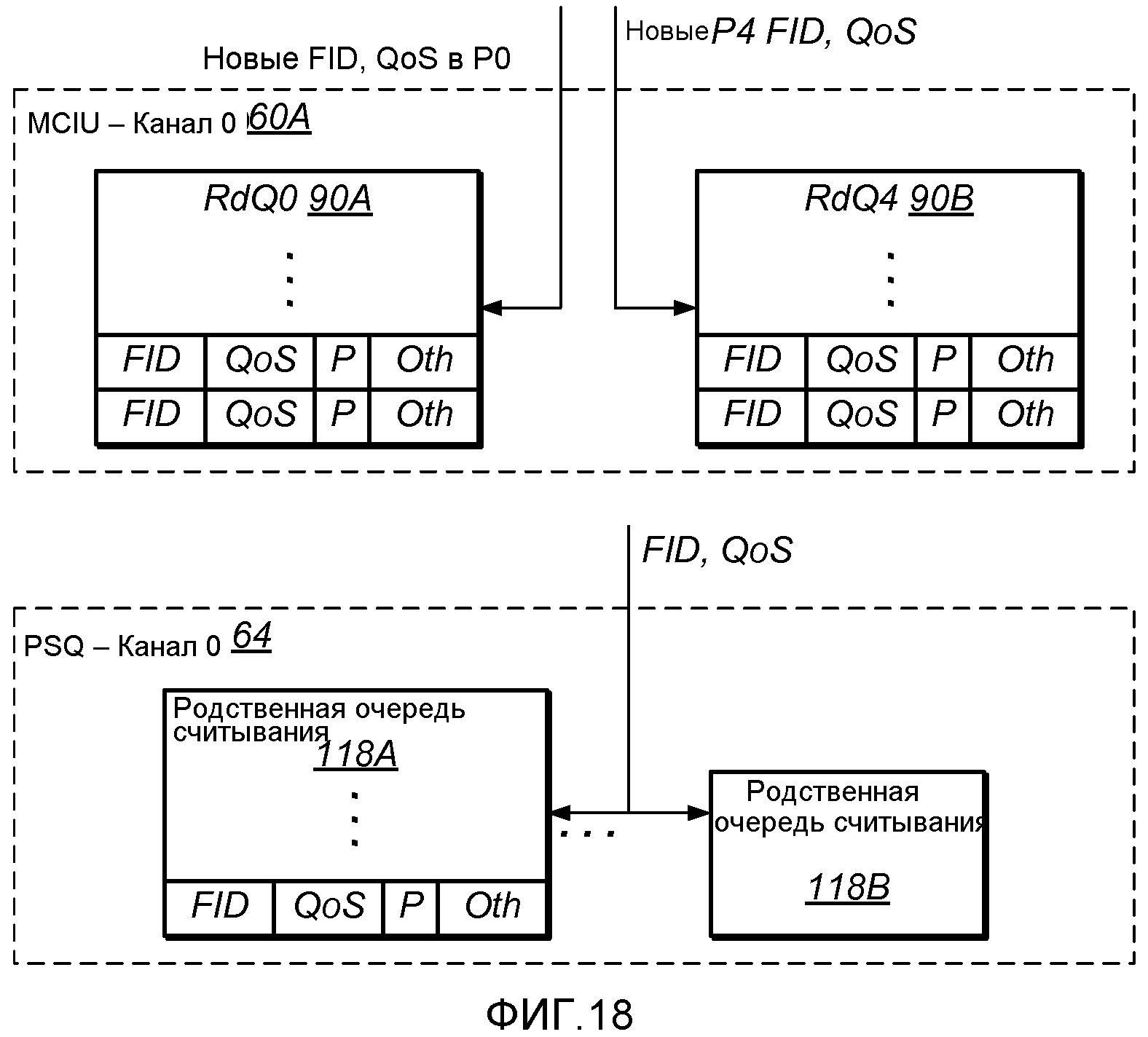

[0027] Фиг. 18 - блок-схема одного варианта осуществления возможностей контроллера запоминающего устройства для поддержки внутриполосного повышения QoS.

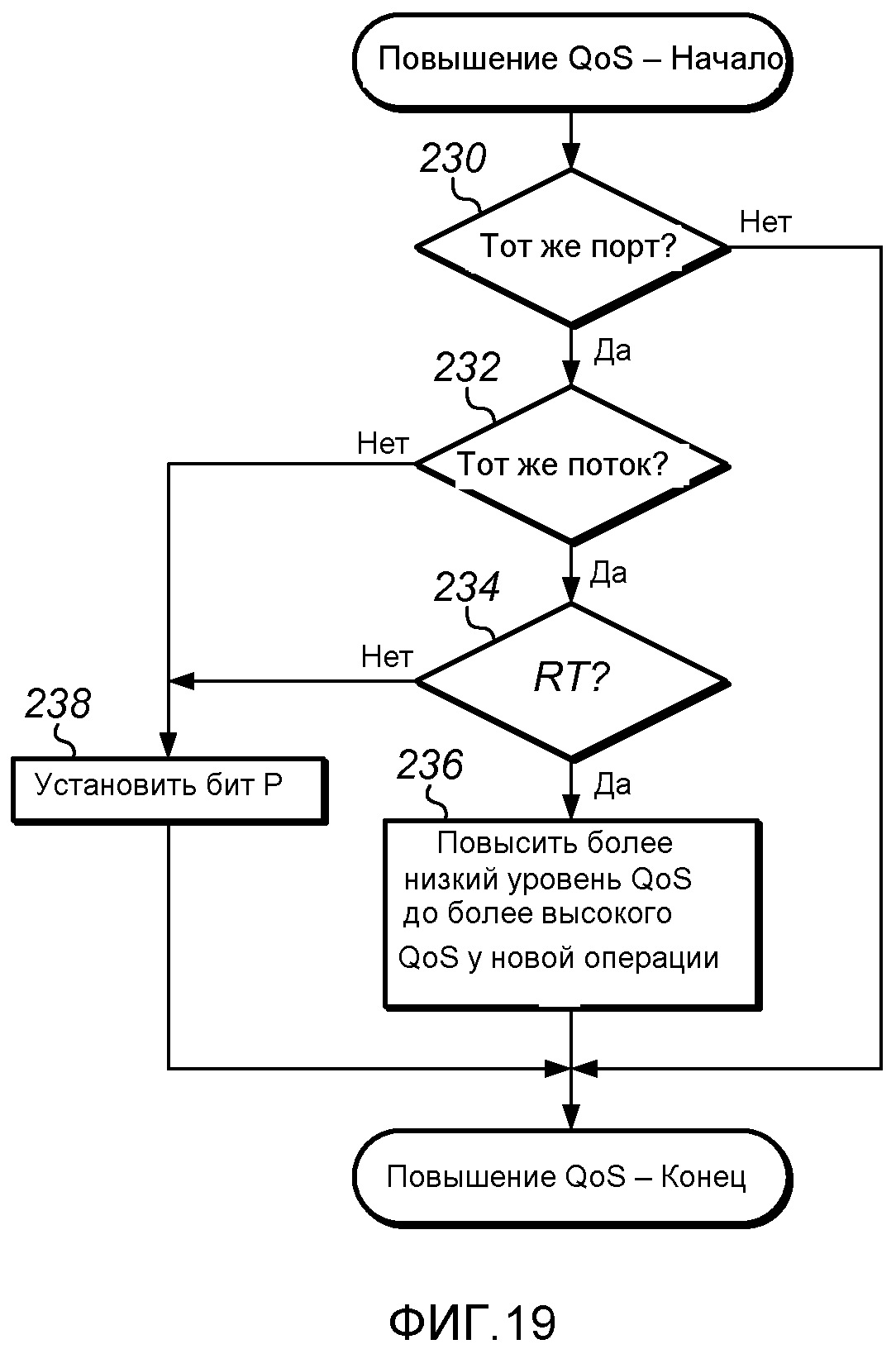

[0028] Фиг. 19 - блок-схема операций, иллюстрирующая работу одного варианта осуществления внутриполосного повышения QoS.

[0029] Фиг. 20 - блок-схема одного варианта осуществления интерфейса повышения QoS боковой полосы.

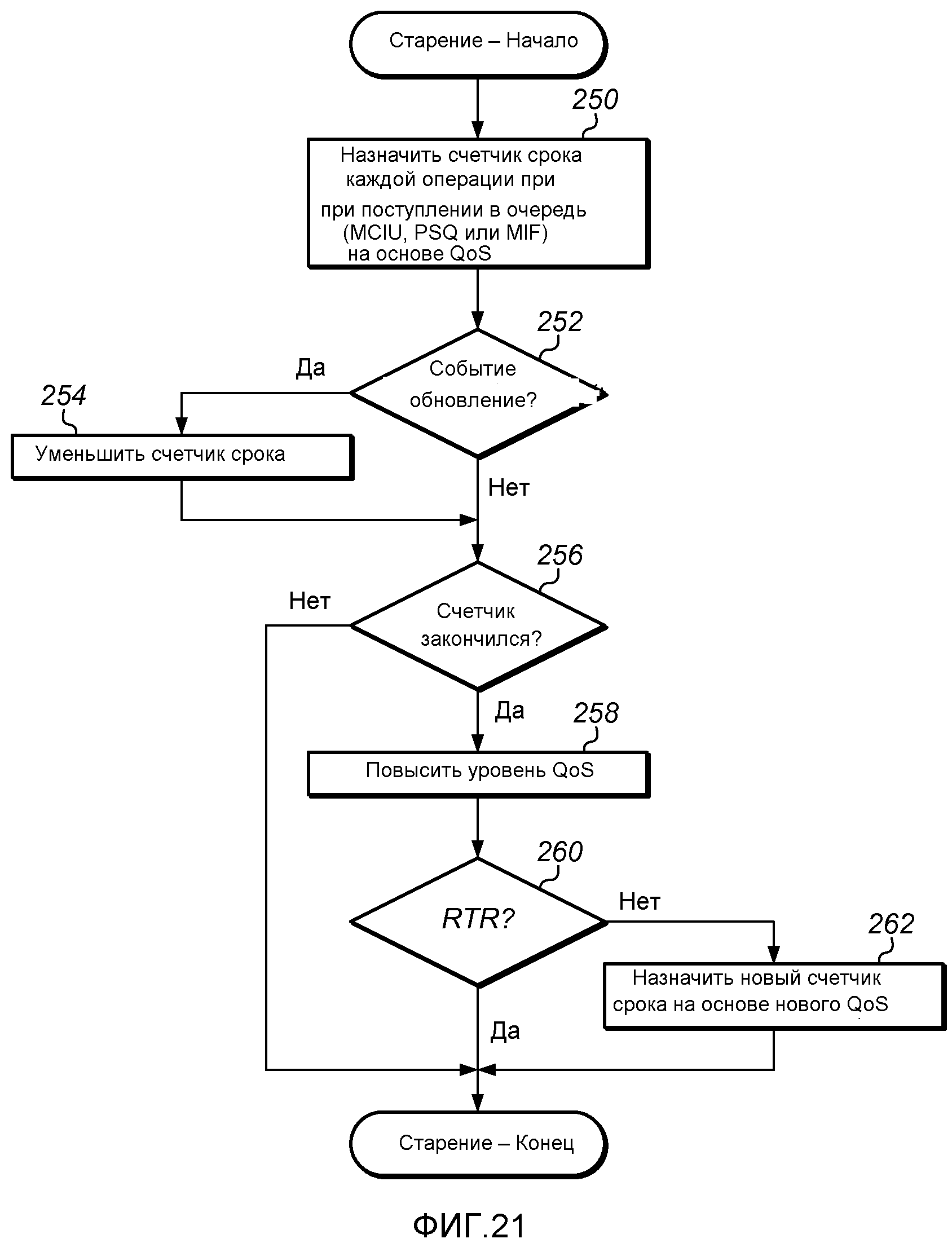

[0030] Фиг. 21 - блок-схема операций, иллюстрирующая один вариант осуществления повышения QoS вследствие старения операций.

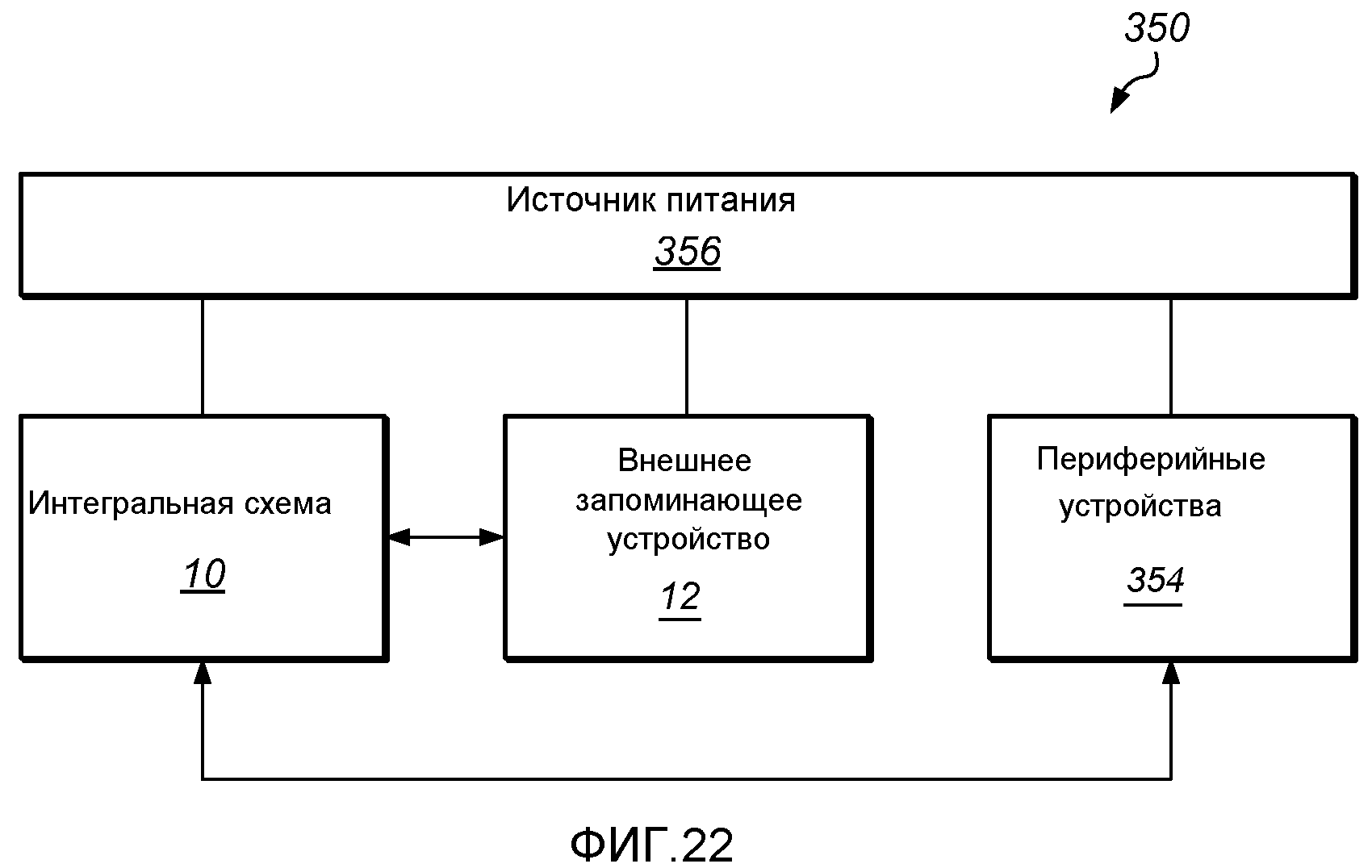

[0031] Фиг. 22 - блок-схема одного варианта осуществления системы, включающей в себя интегральную схему, проиллюстрированную на фиг. 1.

[0032] Хотя изобретение допускает различные модификации и альтернативные виды, его характерные варианты осуществления показаны в качестве примера на чертежах и будут подробно описаны в этом документе. Однако следует понимать, что чертежи и подробное описание к ним не предназначены для ограничения изобретения конкретным раскрытым видом, а наоборот, направлены на охват всех модификаций, эквивалентов и альтернатив, входящих в сущность и объем настоящего изобретения, которые заданы прилагаемой формулой изобретения. Заголовки, используемые в этом документе, служат только для организационных целей и не предназначены для использования в ограничении объема описания. При использовании по всей данной заявке слово "может" используется в разрешающем смысле (то есть в значении "имеющий возможность для..."), а не в обязательном смысле (то есть в значении "должен"). Аналогичным образом слова "включают в себя", "включающий" и "включает в себя" означают "включающий", но не только.

[0033] Различные блоки, схемы или другие компоненты могут описываться как "сконфигурированные для" выполнения задачи или задач. В таком контексте "сконфигурированный для" является свободным изложением структуры, в целом означающей "имеющий схемы, которые" выполняют задачу или задачи во время работы. По существу, блок/схема/компонент может быть сконфигурирован для выполнения задачи, даже когда блок/схема/компонент в настоящее время не включен. Вообще, схемы, которые образуют структуру, соответствующую "сконфигурированный для", могут включать в себя аппаратные схемы. Аналогичным образом для удобства в описании различные блоки/схемы/компоненты могут описываться как выполняющие задачу или задачи. Такие описания следует интерпретировать как включающие в себя фразу "сконфигурированный для". Перечисление блока/схемы/компонента, который конфигурируется для выполнения одной или нескольких задач, в явной форме предназначено не для применения интерпретации шестого пункта 35 U.S.C. § 112 для того блока/схемы/компонента.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0034] Обращаясь теперь к фиг. 1, показана блок-схема одного варианта осуществления системы 5. В варианте осуществления по фиг. 1 система 5 включает в себя интегральную схему 10 (IC), соединенную с внешними запоминающими устройствами 12A-12B. В проиллюстрированном варианте осуществления интегральная схема 10 включает в себя центральный процессор 14 (CPU), который включает в себя один или несколько процессоров 16 и кэш 18 уровня 2 (L2). Другие варианты осуществления могут не включать в себя кэш 18 L2 и/или могут включать в себя дополнительные уровни кэша. Более того, рассматриваются варианты осуществления, которые включают в себя более двух процессоров 16 и которые включают в себя только один процессор 16. Интегральная схема 10 дополнительно включает в себя набор из одного или нескольких периферийных устройств 20, не относящихся к реальному масштабу времени (NRT), и набор из одного или нескольких периферийных устройств 22 реального масштаба времени (RT). В проиллюстрированном варианте осуществления периферийные устройства RT включают в себя процессор 24 изображений, один или несколько каналов 26 отображения и арбитр 28 портов. Другие варианты осуществления по желанию могут включать в себя больше или меньше процессоров 24 изображений, больше или меньше каналов 26 отображения и/или любые дополнительные периферийные устройства реального масштаба времени. Процессор 24 изображений может соединяться для приема данных изображений от одной или нескольких камер в системе 5. Аналогичным образом каналы 26 отображения могут соединяться с одним или несколькими контроллерами дисплея (не показаны), которые управляют одним или несколькими дисплеями в системе. В проиллюстрированном варианте осуществления CPU 14 соединяется с контроллером 30 моста/прямого доступа к памяти (DMA), который может соединяться с одним или несколькими периферийными устройствами 32 и/или одним или несколькими контроллерами 34 интерфейса периферийных устройств. Количество периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств может меняться от нуля до любого нужного числа в различных вариантах осуществления. Система 5, проиллюстрированная на фиг. 1, дополнительно включает в себя графический блок 36, содержащий один или несколько графических контроллеров, например G0 38A и G1 38B. Количество графических контроллеров в расчете на графический блок и количество графических блоков в других вариантах осуществления может меняться. Как проиллюстрировано на фиг. 1, система 5 включает в себя контроллер 40 запоминающего устройства, соединенный с одной или несколькими схемами 42A-42B физического интерфейса (PHY) запоминающих устройств. PHY 42A-42B запоминающих устройств конфигурируются для взаимодействия по выводам интегральной схемы 10 с запоминающими устройствами 12A-12B. Контроллер 40 запоминающего устройства также включает в себя набор портов 44A-44E. Порты 44A-44B соединяются с графическими контроллерами 38A-38B соответственно с помощью первого типа интерфейса (Интерфейс 1). CPU 14 соединяется с портом 44C с помощью второго типа интерфейса (Интерфейс 2). Периферийные устройства 20 NRT и периферийные устройства 22 RT соединяются с портами 44D-44E соответственно с помощью второго типа интерфейса. Количество портов, включенных в контроллер 40 запоминающего устройства, может меняться в других вариантах осуществления, как и количество контроллеров запоминающего устройства. Количество PHY 42A-42B запоминающих устройств и соответствующих запоминающих устройств 12A-12B в других вариантах осуществления может быть равно одному или более двух.

[0035] В одном варианте осуществления каждый порт 44A-44E может ассоциироваться с конкретным типом трафика. Например, в одном варианте осуществления типы трафика могут включать в себя трафик RT, трафик NRT и графический трафик. Другие варианты осуществления могут включать в себя другие типы трафика в дополнение или вместо подмножества вышеупомянутых типов трафика. Каждый тип трафика может характеризоваться по-разному (например, в показателях требований и характеристики (поведения)), и контроллер запоминающего устройства может по-разному обрабатывать типы трафика, чтобы обеспечить более высокое быстродействие на основе этих характеристик. Например, трафик RT требует обслуживания каждой операции в запоминающем устройстве в рамках конкретного количества времени. Если задержка операции превышает конкретное количество времени, то в периферийном устройстве RT может произойти ошибочная операция. Например, данные изображений могут потеряться в процессоре 24 изображений, или может визуально исказиться отображенное изображение на дисплеях, с которыми соединяются каналы 26 отображения. Трафик RT можно охарактеризовать, например, как изохронный. С другой стороны, графический трафик может иметь относительно большую полосу частот, но не является чувствительным к задержке. Трафик NRT, например от процессоров 16, более чувствителен к задержке по причинам быстродействия, но выдерживает большую задержку. То есть трафик NRT обычно может обслуживаться с любой задержкой, не вызывая ошибочную работу в устройствах, формирующих трафик NRT. Аналогичным образом, менее чувствительный к задержке графический трафик, но с большей полосой частот обычно может обслуживаться с любой задержкой. Другой трафик NRT может включать в себя трафик аудио, который имеет относительно малую полосу частот и обычно может обслуживаться с разумной задержкой. Большая часть трафика периферийных устройств также может быть NRT (например, трафик к запоминающим устройствам, например магнитному, оптическому или твердотельному запоминающему устройству).

[0036] В результате предоставления портов 44A-44E, ассоциированных с разными типами трафика, контроллер 40 запоминающего устройства может подвергаться воздействию разных типов трафика параллельно, и соответственно может допускать принятие лучших решений о том, какие операции в запоминающем устройстве обслуживать перед другими, на основе типа трафика. В некоторых вариантах осуществления каждый порт может предназначаться исключительно для трафика RT либо трафика NRT. В других вариантах осуществления порты могут ассоциироваться с конкретным типом трафика, но в порту могут поддерживаться другие типы трафика. В варианте осуществления графический трафик может считаться трафиком NRT, но наличие видимости для графического трафика отдельно от другого трафика NRT может быть полезным для балансирования полосы частот между другими источниками NRT и источником RT. Аналогичным образом, наличие процессорного трафика отдельно от других источников NRT может быть полезным при балансировании полосы частот. В проиллюстрированном варианте осуществления порт 44E RT может ассоциироваться с трафиком RT, а оставшиеся порты 44A-44D могут ассоциироваться с трафиком NRT.

[0037] Как правило, порт может быть точкой связи в контроллере 40 запоминающего устройства для взаимодействия с одним или несколькими источниками. В некоторых случаях порт может предназначаться для источника (например, порты 44A-44B могут предназначаться графическим контроллерам 38A-38B соответственно). В других случаях порт может совместно использоваться несколькими источниками (например, процессоры 16 могут совместно использовать порт 44C CPU, периферийные устройства 20 NRT могут совместно использовать порт 44D NRT, и периферийные устройства RT, например каналы 26 отображения и процессор 24 изображений, могут совместно использовать порт 44E RT). Порт может соединяться с одним интерфейсом для взаимодействия с одним или несколькими источниками. Таким образом, когда источники совместно используют некий интерфейс, может присутствовать арбитр на стороне источников интерфейса для выбора между источниками. Например, кэш 18 L2 может служить для контроллера 40 запоминающего устройства в качестве арбитра для порта 44C CPU. Арбитр 28 портов может служить в качестве арбитра для порта 44E RT, и аналогичный арбитр портов (не показан) может быть арбитром для порта 44D NRT. Одиночный источник в порту или сочетание источников в порту может называться агентом.

[0038] Каждый порт 44A-44E соединяется с интерфейсом для взаимодействия с соответствующим агентом. Интерфейс может быть любым типом средств связи (например, шиной, двухточечным межсоединением и т.п.) и может реализовывать любой протокол. В некоторых вариантах осуществления все порты 44A-44E могут реализовать один и тот же интерфейс и протокол. В других вариантах осуществления разные порты могут реализовывать разные интерфейсы и/или протоколы. Например, проиллюстрированный на фиг. 1 вариант осуществления включает в себя графические контроллеры 38A-38B, использующие один тип интерфейса/протокола, и CPU 14, периферийные устройства 20 NRT и периферийные устройства 22 RT, использующие другой тип интерфейса/протокола. Интерфейс может обращаться к определениям сигналов и электрическим свойствам интерфейса, а протокол может быть логическим определением связи по интерфейсу (например, включающим в себя команды, правила упорядочения, поддержку когерентности, при их наличии и т.п.). Поддержка более одного интерфейса в различных портах 44A-44E может устранить потребность в преобразовании из одного интерфейса, поддерживаемого источником/агентом, в интерфейс, поддерживаемый контроллером 40 запоминающего устройства, что может повысить быстродействие в некоторых вариантах осуществления. Дополнительно некоторые варианты осуществления интегральной схемы 10 могут включать в себя схемы, приобретенные у стороннего производителя в виде предварительно размещенного в корпусе блока, обычно называемого в промышленности интеллектуальной собственностью (IP). IP может быть "жесткой" (в этом случае она задается в виде таблицы соединений схем, которые разводятся и размещаются на IC в виде блока) или "мягкой" (в этом случае она задается в виде синтезируемого блока, который можно синтезировать вместе с другими блоками, которые нужно включить в интегральную схему 10). И жесткая и мягкая IP включает в себя заданный интерфейс и протокол, которые проектировщику интегральной схемы 10 обычно нельзя изменять (по меньшей мере без уплаты пошлины стороннему производителю, который владеет этой IP). Соответственно, поддержка нескольких интерфейсов/протоколов может дать возможность упрощенного включения IP стороннего производителя.

[0039] В варианте осуществления каждый источник может назначать параметр качества обслуживания (QoS) каждой операции в запоминающем устройстве, переданной этим источником. Параметр QoS может идентифицировать запрошенный уровень обслуживания для операции в запоминающем устройстве. Операциям в запоминающем устройстве со значениями параметров QoS, запрашивающими более высокие уровни обслуживания, может отдаваться предпочтение перед операциями в запоминающем устройстве, запрашивающими более низкие уровни обслуживания. Например, каждый из интерфейсов к портам 44A-44E на фиг. 1 показан включающим в себя команду (Cmd), идентификатор потока (FID) и параметр QoS (QoS). Команда может идентифицировать операцию в запоминающем устройстве (например, считывание или запись). Команда/операция считывания запоминающего устройства вызывает передачу данных из запоминающего устройства 12A-12B в источник, тогда как команда/операция записи в запоминающее устройство вызывает передачу данных из источника в запоминающее устройство 12A-12B. Команды также могут включать в себя команды для программирования контроллера 40 запоминающего устройства. Например, то, какие диапазоны адресов отображаются в какие каналы запоминающего устройства, параметры совместного использования полосы пропускания и т.п. могут быть программируемыми в контроллере 40 запоминающего устройства. FID может идентифицировать операцию в запоминающем устройстве как часть потока операций в запоминающем устройстве. Поток операций в запоминающем устройстве обычно может быть связанным, тогда как операции в запоминающем устройстве из разных потоков, даже от одного и того же источника, могут быть не связаны. Часть FID (например, поле источника) может идентифицировать источник, а оставшаяся часть FID может идентифицировать поток (например, поле потока). Таким образом, FID может быть аналогичен ID транзакции, и некоторые источники могут просто передавать ID транзакции в качестве FID. В таком случае поле источника в ID транзакции может быть полем источника в FID, и порядковый номер (который идентифицирует транзакцию среди транзакций от одного и того же источника) в ID транзакции может быть полем потока в FID. Однако источники, которые группируют транзакции в виде потока, могут по-разному использовать FID. В качестве альтернативы потоки могут соотноситься с полем источника (например, операции от одного и того же источника могут быть частью одного и того же потока, а операции от другого источника являются частью другого потока). Возможность идентифицировать транзакции потока может использоваться различными способами, описанными ниже (например, повышение QoS, переупорядочение и т.п.).

[0040] Таким образом, заданный источник может конфигурироваться для использования параметров QoS, чтобы идентифицировать, какие операции в запоминающем устройстве важнее для источника (и соответственно должны обслуживаться до других операций в запоминающем устройстве от того же источника), особенно для источников, которые поддерживают неупорядоченные передачи данных относительно адресных передач от источника. Кроме того, параметры QoS могут позволить источникам запрашивать более высокие уровни обслуживания, нежели другие источники в том же порту и/или источники в других портах.

[0041] В некоторых вариантах осуществления разные типы трафика могут иметь разные определения параметров QoS. То есть разные типы трафика могут иметь разные наборы параметров QoS. Значимость данного значения параметра QoS зависит от набора параметров QoS, из которого он извлекается. Например, может быть задан набор параметров QoS RT, и может быть задан набор параметров QoS NRT. Таким образом, значению параметра QoS RT придается значимость в рамках набора параметров QoS RT, а значению параметра QoS NRT придается значимость в рамках набора параметров QoS NRT. Другие варианты осуществления могут реализовать одинаковый набор параметров QoS во всех портах или среди всех типов трафика.

[0042] Контроллер 40 запоминающего устройства может конфигурироваться для обработки параметров QoS, принятых в каждом порту 44A-44E, и может использовать относительные значения параметров QoS для планирования операций в запоминающем устройстве, принятых в портах, относительно других операций в запоминающем устройстве из этого порта и относительно других операций в запоминающем устройстве, принятых в других портах. Точнее говоря, контроллер 40 запоминающего устройства может конфигурироваться для сравнения параметров QoS, которые извлекаются из разных наборов параметров QoS (например, параметры QoS RT и параметры QoS NRT), и может конфигурироваться для принятия решений по планированию на основе этих параметров QoS.

[0043] Параметры QoS соответственно могут быть значениями, которые передаются вместе с операциями в запоминающем устройстве и которые могут использоваться в контроллере запоминающего устройства для идентификации запрошенных уровней QoS. Уровни QoS могут находиться относительно других уровней и могут задавать, какие операции в запоминающем устройстве предпочтительно выбирать перед другими, имеющими более низкие уровни QoS. Таким образом, уровни QoS могут функционировать как своего рода приоритет после интерпретации контроллером 40 запоминающего устройства для рассмотрения уровней QoS, заданных в разных наборах, хотя приоритет может быть сбалансирован другими факторами.

[0044] В некоторых вариантах осуществления контроллер 40 запоминающего устройства может конфигурироваться для повышения уровней QoS для ожидающих операций в запоминающем устройстве. Могут поддерживаться различные механизмы повышения. Например, контроллер 40 запоминающего устройства может конфигурироваться для повышения уровня QoS для ожидающих операций в запоминающем устройстве из потока в ответ на прием другой операции в запоминающем устройстве из того же потока, которая имеет параметр QoS, задающий более высокий уровень QoS. Этот вид повышения QoS может называться внутриполосным повышением, поскольку параметры QoS, переданные с использованием обычного способа передачи операции в запоминающем устройстве, также служат в качестве неявного запроса повышения для операций в запоминающем устройстве в том же потоке. Контроллер 40 запоминающего устройства может конфигурироваться для принудительной отправки ожидающих операций в запоминающем устройстве из одинакового порта или источника, но не одинакового потока, в качестве вновь принятой операции в запоминающем устройстве, задающей более высокий уровень QoS. В качестве другого примера контроллер 40 запоминающего устройства может конфигурироваться для соединения с интерфейсом боковой полосы от одного или нескольких агентов, и может повышать уровни QoS в ответ на прием запроса повышения по интерфейсу боковой полосы. В другом примере контроллер 40 запоминающего устройства может конфигурироваться для отслеживания относительного срока ожидающих операций в запоминающем устройстве. Контроллер 40 запоминающего устройства может конфигурироваться для повышения уровня QoS старых операций в запоминающем устройстве с определенными сроками. Сроки, при которых происходит повышение, могут зависеть от текущего параметра QoS старой операции в запоминающем устройстве.

[0045] Контроллер 40 запоминающего устройства может конфигурироваться для определения канала запоминающего устройства, адресуемого каждой операцией в запоминающем устройстве, принятой в портах, и может конфигурироваться для передачи операций в запоминающем устройстве запоминающему устройству 12A-12B по соответствующему каналу. Количество каналов и отображение адресов в каналы может меняться в различных вариантах осуществления и может быть программируемым в контроллере запоминающего устройства. Контроллер запоминающего устройства может использовать параметры QoS у операций в запоминающем устройстве, отображенных в один и тот же канал, для определения порядка операций в запоминающем устройстве, переданных в тот канал. То есть контроллер запоминающего устройства может переупорядочить операции в запоминающем устройстве от их исходного порядка приема в портах. Более того, во время обработки в канале операции в запоминающем устройстве могут быть снова переупорядочены в одной или нескольких точках. На каждом уровне переупорядочения можно уменьшить внимание, уделенное параметрам QoS, и можно увеличить факторы, которые влияют на эффективность пропускной способности запоминающего устройства. Как только операции в запоминающем устройстве достигают конца конвейера канала запоминающего устройства, операции можно упорядочить по сочетанию уровней QoS и эффективности пропускной способности запоминающего устройства. В некоторых вариантах осуществления можно реализовать высокое быстродействие.

[0046] Процессоры 16 могут реализовывать любую архитектуру системы команд и могут конфигурироваться для выполнения команд, заданных в этой архитектуре системы команд. Процессоры 16 могут применять любую микроархитектуру, включающую в себя скалярную, суперскалярную, конвейерную, суперконвейерную, неупорядоченную, упорядоченную, спекулятивную, неспекулятивную и т.п., или их сочетания. Процессоры 16 могут включать в себя схемы и опционально могут реализовывать методики микропрограммирования. Процессоры 16 могут включать в себя один или несколько кэшей уровня 1, и соответственно кэш 18 является кэшем L2. Другие варианты осуществления могут включать в себя несколько уровней кэшей в процессорах 16, и кэш 18 может быть следующим уровнем ниже по иерархии. Кэш 18 может применять любой размер и любую конфигурацию (наборно-ассоциативный кэш, кэш прямого отображения и т.п.).

[0047] Графические контроллеры 38A-38B могут быть любыми схемами графической обработки. В целом, графические контроллеры 38A-38B могут конфигурироваться для представления объектов, которые нужно отобразить, в буфере кадра. Графические контроллеры 38A-38B могут включать в себя графические процессоры, которые могут выполнять программное обеспечение графики для выполнения части или всей графической операции и/или аппаратное ускорение некоторых графических операций. Величина аппаратного ускорения и программной реализации может меняться от одного варианта осуществления к другому.

[0048] Периферийные устройства 20 NRT могут включать в себя любые периферийные устройства, не относящиеся к реальному масштабу времени, которым по причинам быстродействия и/или полосы пропускания предоставляется независимый доступ к запоминающему устройству 12A-12B. То есть доступ периферийных устройств 20 NRT не зависит от CPU 14 и может проходить параллельно операциям CPU в запоминающем устройстве. Другие периферийные устройства, например периферийное устройство 32 и/или периферийные устройства, соединенные с интерфейсом периферийных устройств, управляемым контроллером 34 интерфейса периферийных устройств, также могут быть периферийными устройствами, не относящимися к реальному масштабу времени, но могут не требовать независимого доступа к запоминающему устройству. Различные варианты осуществления периферийных устройств 20 NRT могут включать в себя видеокодеры и декодеры, схемы преобразователя масштаба/вращателя, схемы сжатия/восстановления изображений и т.п.

[0049] Как упоминалось выше, периферийные устройства 22 RT могут включать в себя процессор 24 изображений и каналы 26 отображения. Каналы 26 отображения могут включать в себя схемы для выборки одного или нескольких кадров и для смешивания кадров, чтобы создать изображение на дисплее. Каналы 26 отображения могут дополнительно включать в себя один или несколько видеоконвейеров. Результатом каналов 26 отображения может быть поток пикселей, которые нужно отобразить на экране дисплея. Значения пикселей могут передаваться контроллеру дисплея для отображения на экране дисплея. Процессор 26 изображений может принимать данные с камеры и перерабатывать эти данные в изображение для сохранения в запоминающем устройстве.

[0050] Контроллер 30 моста/DMA может содержать схемы для сопряжения периферийного устройства (устройств) 32 и контроллера (контроллеров) 34 интерфейса периферийных устройств с областью памяти. В проиллюстрированном варианте осуществления контроллер 30 моста/DMA может переносить операции в запоминающем устройстве от периферийных устройств/контроллеров интерфейса периферийных устройств через CPU 14 в контроллер 40 запоминающего устройства. CPU 14 также может поддерживать когерентность между перенесенными операциями в запоминающем устройстве и операциями в запоминающем устройстве от процессоров 16/кэша 18 L2. Кэш 18 L2 также может разрешать конфликты перенесенных операций в запоминающем устройстве с операциями в запоминающем устройстве от процессоров 16, которые нужно передать по интерфейсу CPU в порт 44C CPU. Контроллер 30 моста/DMA также может предоставлять операцию DMA от лица периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств для передачи блоков данных в запоминающее устройство и из него. Конкретнее, контроллер DMA может конфигурироваться для выполнения передач в запоминающее устройство 12A-12B и из него посредством контроллера 40 запоминающего устройства от лица периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств. Контроллер DMA может быть программируемым с помощью процессоров 16 для выполнения операций DMA. Например, контроллер DMA может быть программируемым посредством дескрипторов. Дескрипторы могут быть структурами данных, сохраненными в запоминающем устройстве 12A-12B, которые описывают передачи DMA (например, адреса источника и назначения, размер и т.п.). В качестве альтернативы контроллер DMA может быть программируемым посредством регистров в контроллере DMA (не показаны).

[0051] Периферийные устройства 32 могут включать в себя любые требуемые устройства ввода/вывода или другие аппаратные средства, которые включаются в интегральную схему 10. Например, периферийные устройства 32 могут включать в себя сетевые периферийные устройства, например один или несколько контроллеров управления доступом к среде передачи (MAC), таких как MAC Ethernet или контроллер Wireless Fidelity (WiFi). В периферийные устройства 32 может включаться звуковой блок, включающий в себя различные устройства обработки звуковых сигналов. В периферийные устройства 32 может включаться один или несколько цифровых процессоров сигналов. Периферийные устройства 32 могут включать в себя любой другой требуемый функционал, например таймеры, встроенное в кристалл запоминающее устройство секретных значений, механизм шифрования и т.п., или любое их сочетание.

[0052] Контроллеры 34 интерфейса периферийных устройств могут включать в себя любые контроллеры для любого типа интерфейса периферийных устройств. Например, контроллеры интерфейса периферийных устройств могут включать в себя различные контроллеры интерфейса, например контроллер универсальной последовательной шины (USB), контроллер межсоединения периферийных компонентов (PCIe), интерфейс флэш-памяти, выводы универсального ввода/вывода (I/O) и т.п.

[0053] Запоминающие устройства 12A-12B могут быть любым типом запоминающего устройства, например динамическим оперативным запоминающим устройством (DRAM), синхронным DRAM (SDRAM), SDRAM с удвоенной скоростью передачи данных (DDR, DDR2, DDR3 и т.п.) (включая мобильные версии SDRAM, например mDDR3 и т.п., и/или маломощные версии SDRAM, например LPDDR2 и т.п.), RAMBUS DRAM (RDRAM), статическое RAM (SRAM) и т.п. Одно или несколько запоминающих устройств могут соединяться на монтажной плате для образования модулей запоминающего устройства, например модулей запоминающего устройства с однорядным расположением выводов (SIMM), модулей запоминающего устройства с двухрядным расположением выводов (DIMM) и т.п. В качестве альтернативы устройства могут размещены в корпусе интегральной схемы 10 в конфигурации "кристалл на кристалле", конфигурации "корпус на корпусе" или многокристальной модульной конфигурации.

[0054] PHY 42A-42B запоминающих устройств могут управлять низкоуровневым физическим интерфейсом к запоминающему устройству 12A-12B. Например, PHY 42A-42B запоминающих устройств могут отвечать за синхронизацию сигналов, за надлежащее тактирование в синхронном DRAM и т.п. В одном варианте осуществления PHY 42A-42B запоминающих устройств могут конфигурироваться для синхронизации с тактовыми импульсами, поставляемыми в интегральной схеме 10, и могут конфигурироваться для формирования тактовых импульсов, используемых запоминающим устройством 12.

[0055] Отметим, что другие варианты осуществления могут включать в себя другие сочетания компонентов, включая подмножества или надмножества компонентов, показанных на фиг. 1, и/или другие компоненты. Хотя один экземпляр заданного компонента может быть показан на фиг. 1, другие варианты осуществления могут включать в себя один или несколько экземпляров заданного компонента. Аналогичным образом, по всему данному подробному описанию может включаться один или несколько экземпляров заданного компонента, даже если показан только один, и/или могут использоваться варианты осуществления, которые включают в себя только один экземпляр, даже если показано несколько экземпляров.

[0056] Отметим, что другие варианты осуществления контроллера 40 запоминающего устройства могут не реализовывать несколько портов, но все же могут реализовывать параметры QoS, разные параметры/уровни QoS для разных типов или классов трафика, например NRT и RT, и повышение QoS.

[0057] Обращаясь далее к фиг. 2, показана пара таблиц 50 и 52, иллюстрирующих определение набора уровней QoS RT и набора уровней QoS NRT соответственно, для одного варианта осуществления. Другие варианты осуществления могут включать в себя дополнительные или заменяющие уровни, и другие варианты осуществления могут включать в себя дополнительные уровни совместно с подмножеством проиллюстрированных уровней. Как проиллюстрировано указывающими вниз стрелками рядом с таблицами 50 и 52 на фиг. 2, таблицы иллюстрируют уровни QoS в некотором наборе с увеличивающимся приоритетом. То есть зеленый уровень QoS реального масштаба времени (RTG) является уровнем QoS RT наименьшего приоритета; желтый уровень QoS реального масштаба времени (RTY) является уровнем QoS RT среднего приоритета; и красный уровень QoS реального масштаба времени (RTR) является уровнем QoS RT наивысшего приоритета. Аналогичным образом уровень QoS наилучшего из возможного (BEF) является уровнем QoS NRT наименьшего приоритета, а уровень QoS с малой задержкой (LLT) является уровнем QoS NRT наивысшего приоритета. Иллюстрация уровней QoS RT и уровней QoS NRT рядом друг с другом на фиг. 2 не предназначена для указания относительного приоритета уровней QoS RT относительно уровней QoS NRT. Вместо этого контроллер 40 запоминающего устройства может определять такие относительные приоритеты частично на основе других факторов, указывающих трафик, который поступает на контроллер 40 запоминающего устройства по различным типам и портам.

[0058] Уровни QoS RTG, RTY и RTR могут отражать относительные уровни срочности от источника RT. То есть, когда уменьшается количество времени перед тем, как данные требуются источнику RT, чтобы предотвратить ошибочную операцию, увеличивается уровень QoS, назначенный каждой операции в запоминающем устройстве, чтобы указать большую срочность. Рассматривая операции, имеющие большую срочность, как операции с более высоким приоритетом, контроллер 40 запоминающего устройства может быстрее возвращать данные источнику RT и соответственно может способствовать правильной работе источника RT.

[0059] Например, канал 26 отображения может инициировать считывание данных кадра из запоминающего устройства 12A-12B для следующего кадра, который необходимо отобразить в кадровый интервал гашения для дисплея. Кадр фактически не отображается до окончания кадрового интервала гашения, и соответственно канал 26 отображения может использовать уровень RTG в течение этого периода времени. Когда кадр начинает отображаться (то есть контроллер дисплея начинает считывание пикселей кадра из выхода канала 26 отображения), канал 26 отображения может повысить уровень QoS у операций считывания данных кадра в запоминающее устройство до уровня RTY. Например, если объем данных кадра, который считывается перед отображаемым текущим пикселем, уменьшается ниже первой пороговой величины, то уровень можно повысить до RTY. На второй пороговой величине (меньше первой пороговой величины) канал 26 отображения может повысить уровень QoS у операций в запоминающем устройстве до RTR.

[0060] Уровень QoS NRT BEF может быть запросом на возврат данных так быстро, как может контроллер 40 запоминающего устройства, как только удовлетворяются потребности других потоков данных. С другой стороны, уровень QoS NRT LLT может быть запросом данных с малой задержкой. NRT-операции в запоминающем устройстве, имеющие уровень QoS LLT, в показателях приоритета перед другими транзакциями запоминающего устройства могут рассматриваться тщательнее, чем имеющие уровень QoS BEF (по меньшей мере в некоторых случаях). В других случаях уровни QoS BEF и LLT могут рассматриваться контроллером 40 запоминающего устройства как одинаковые.

[0061] Обращаясь далее к фиг. 3, показана блок-схема одного варианта осуществления контроллера 40 запоминающего устройства. В варианте осуществления из фиг. 3 контроллер 40 запоминающего устройства включает в себя блок 54 интерфейса агента (AIU) и один или несколько блоков 56A-56B каналов запоминающего устройства. Может присутствовать один блок 56A-56B канала запоминающего устройства для каждого канала запоминающего устройства, включенного в данный вариант осуществления, а другие варианты осуществления могут включать в себя один канал или более двух каналов. Как проиллюстрировано на фиг. 3, AIU 54 может включать в себя несколько блоков 58A-58E интерфейса портов. Конкретнее, в контроллере 40 запоминающего устройства может присутствовать блок 58A-58E интерфейса порта для каждого порта 44A-44E. AIU 54 может дополнительно включать в себя блоки 60A-60B интерфейсов каналов запоминающего устройства (MCIU) (один для каждого блока 56A-56B канала запоминающего устройства). AIU 54 может дополнительно включать в себя один или несколько регистров 62 совместного использования полосы пропускания, которые могут быть программируемыми для указания, как должна совместного использования полоса пропускания портами. Блоки 58A-58E интерфейсов портов могут соединяться для приема операций в запоминающем устройстве и приема/передачи данных и ответов в соответствующем порту, а также могут соединяться с MCIU 60A-60B. MCIU 60A-60B могут дополнительно соединяться с регистрами 62 совместного использования полосы пропускания и с соответствующими MCU 56A-56B. Как проиллюстрировано на фиг. 3, MCU 56A-56B могут включать в себя очередь 64 предварительной сортировки (PSQ) и схему 66 интерфейса запоминающего устройства (MIF). PSQ 64 соединяются с соответствующими MCIU 60A-60B и с MIF 66 в том же MCU 56A-56B. MIF 66 в каждом MCU 56A-56B соединяется с соответствующей PHY 42A-42B запоминающего устройства.

[0062] AIU 54 может конфигурироваться для приема операций в запоминающем устройстве в портах 44A-44E и переключения операций в запоминающем устройстве на каналы, адресуемые этими операциями в запоминающем устройстве, используя параметры QoS у операций в запоминающем устройстве в качестве фактора при принятии решения, какие операции в запоминающем устройстве передавать одному из MCU 56A-56B перед другими операциями в запоминающем устройстве к тому же MCU 56A-56B. Другие факторы могут включать в себя средства управления совместным использованием полосы пропускания для совместного использования полосы пропускания в каналах запоминающего устройства между портами.

[0063] Конкретнее, каждый блок 58A-58E интерфейса порта может конфигурироваться для приема операций в запоминающем устройстве из соответствующего порта 44A-44E и может конфигурироваться для определения канала запоминающего устройства, на который направлена данная операция в запоминающем устройстве. Блок 58A-58E интерфейса порта может передавать операцию в запоминающем устройстве соответствующему MCIU 60A-60B и может передавать считывания отдельно от записей в проиллюстрированном варианте осуществления. Таким образом, например, блок 58A интерфейса порта может иметь соединение Rd0 и соединение Wr0 с MCIU 60A для операций считывания и операций записи соответственно. Аналогичным образом блок 58A интерфейса порта может иметь соединение Rd1 и Wr1 с MCIU 60B. Другие блоки 58B-58E интерфейсов портов могут иметь аналогичные соединения с MCIU 60A-60B. Также может присутствовать интерфейс данных для передачи считанных данных из блоков 58A-58B интерфейса портов в MCIU 60A-60B, проиллюстрированный в целом в виде пунктирного интерфейса "D" для MCIU 60A на фиг. 3.

[0064] MCIU 60A-60B могут конфигурироваться для постановки в очередь операций в запоминающем устройстве, предоставленных блоками 58A-58E интерфейса портов, и для разрешения конфликтов между операциями в запоминающем устройстве, чтобы выбирать операции для передачи соответствующим MCU 56A-56B. Разрешение конфликтов (арбитраж) между операциями, заданными в данном канале запоминающего устройства, может не зависеть от арбитража между операциями, заданными в других каналах запоминающего устройства.

[0065] MCIU 60A-60B могут соединяться с регистрами 62 совместного использования полосы пропускания, которые могут быть запрограммированы для указания, как пропускная способность запоминающего устройства в канале должна распределяться операциям в запоминающем устройстве в данном канале. Например, в одном варианте осуществления MCIU 60A-60B могут использовать алгоритм взвешенного циклического обслуживания с дефицитом для выбора среди портов, когда отсутствует трафик с высоким приоритетом (например, уровни RTR или RTY QoS в трафике RT). Когда присутствует трафик RTR или RTY, механизм циклического обслуживания может использоваться для выбора среди портов, которые имеют трафик RTR/RTY. Веса в механизме взвешенного циклического обслуживания с дефицитом могут быть программируемыми для распределения относительно большей полосы пропускания одному порту по сравнению с другим портом. Веса могут выбираться для поддержки, например, процессорного трафика по сравнению с графическими и NRT-портами, или для поддержки графических портов по сравнению с другими портами. В различных вариантах осуществления может использоваться любой набор весов. Другие варианты осуществления могут измерять распределение полосы пропускания другими способами. Например, могут использоваться процентные отношения общей полосы пропускания. В других вариантах осуществления кредитная система может использоваться для управления относительным количеством операций от каждого порта, которые выбираются. Однако в различных вариантах осуществления операции обычно могут выбираться на основе параметров QoS и требований к совместному использованию полосы пропускания.

[0066] MCU 56A-56B конфигурируются для планирования операций в запоминающем устройстве из очередей, которые требуется передать по каналу запоминающего устройства. MCU могут конфигурироваться для постановки в очередь отдельно считываний и записей в PSQ 64 и могут конфигурироваться для разрешения конфликтов между считываниями и записями с использованием, например, системы на основе кредитов. В системе на основе кредитов считывания и записи распределяются некоторому количеству кредитов. Количество кредитов записи и кредитов считывания не должны быть равны. Каждая запланированная операция в запоминающем устройстве может потреблять кредит. Как только кредиты записи и кредиты считывания уменьшаются до нуля или меньше, и имеется ожидающая транзакция, которую нужно планировать, оба кредита можно увеличить на соответствующее выделенное количество кредитов. Другие варианты осуществления могут использовать другие механизмы для выбора между считываниями и записями. В одном варианте осуществления кредитная система может быть частью арбитражного механизма между считываниями и записями (вместе с измерениями заполненности очереди записи). То есть, когда очередь записи становится полнее, приоритет записей в арбитражном механизме можно увеличить. Дополнительные подробности излагаются ниже.

[0067] В одном варианте осуществления параметры QoS у операций записи могут аннулироваться при поступлении в PSQ 64. Операции считывания могут сохранять параметры QoS, и параметры QoS могут влиять на планирование считывания из PSQ 64.

[0068] В варианте осуществления MCU 56A-56B могут планировать операции в запоминающем устройстве в пакетах операций (причем каждая операция в пакете потребляет кредит). Если пакет уменьшает счетчик кредитов до нуля, то можно позволить завершить пакет, и можно уменьшить счетчик кредитов до отрицательного числа. Когда счетчики кредитов позже увеличиваются, можно учесть отрицательные кредиты, и соответственно общее количество кредитов после увеличения может быть меньше выделенного количества кредитов.

[0069] Чтобы создать пакеты операций в запоминающем устройстве для планирования, MCU 56A-56B могут группировать операции в запоминающем устройстве в родственные группы. Можно сказать, что операция в запоминающем устройстве проявляет родственность с другой операцией в запоминающем устройстве (или можно сказать, что она является родственной другой операции в запоминающем устройстве), если операции могут выполняться эффективно в интерфейсе запоминающего устройства при выполнении в непосредственной близости во времени. Эффективность может измеряться в показателях увеличенного использования полосы пропускания. Например, SDRAM характеризуются страницей, которую можно открыть с использованием команды активации (вместе с адресом страницы). Размер страницы может меняться от одного варианта осуществления к другому, и в целом может относиться к количеству смежных битов, которые могут быть доступны, как только передана команда активации. Асинхронные DRAM аналогичным образом могут иметь страницу, которая может открываться путем установления управляющего стробирующего сигнала адреса строки и предоставления адреса строки. Две или более операции в запоминающем устройстве, которые обращаются к данным на одной и той же странице, могут быть родственными, потому что только одна активация/RAS может потребоваться в интерфейсе для операций в запоминающем устройстве. SDRAM также имеют независимые банки и ранги. Банк может быть совокупностью запоминающих элементов в микросхеме SDRAM, которые могут иметь открытую строку (в которой можно обнаружить попадания на страницу). Ранг может выбираться посредством выбора микросхемы от контроллера запоминающего устройства и может включать в себя одну или несколько микросхем SDRAM. Операции в запоминающем устройстве для разных рангов или банков также могут быть родственными операциями, потому что они не конфликтуют и соответственно не требуют закрытия страницы и открытия новой страницы. Операции в запоминающем устройстве можно рассматривать как родственные операции, только если они передают данные в одинаковом направлении (то есть операции считывания могут быть родственными только с другими операциями считывания, и аналогичным образом операции записи могут быть родственными только с другими операциями записи). Операции в запоминающем устройстве для одинаковой страницы (или открытой страницы) могут называться попаданиями на страницу, а операции в запоминающем устройстве для разных банков/рангов могут называться попаданиями в банк и попаданиями в ранг соответственно.

[0070] MCU 56A-56B также могут конфигурироваться для планирования команд в интерфейсе запоминающего устройства для запоминающих устройств 12A-12B (посредством PHY 42A-42B запоминающих устройств), чтобы выполнять запланированные операции в запоминающем устройстве. Конкретнее, в варианте осуществления MCU 56A-56B могут конфигурироваться для предварительного синтезирования команд для каждой операции в запоминающем устройстве и постановки в очередь этих команд. MCU 56A-56B могут конфигурироваться для планирования команд, чтобы обеспечить эффективное использование пропускной способности запоминающего устройства. В варианте осуществления MIF 66 в каждом MCU 56A-56B могут реализовывать предварительный синтез команд и планирование команд.

[0071] Обращаясь теперь к фиг. 4, показана блок-схема одного варианта осуществления блока 58C интерфейса порта. Другие схемы 58A-58B и 58D-58E интерфейсов портов могут быть аналогичными, хотя и могут быть отличия в реализации для схем интерфейсов портов, которые соединяются с разными интерфейсами. В проиллюстрированном варианте осуществления блок 58C интерфейса порта включает в себя буферы 70A-70B, соединенные с интерфейсами считывания (AR) и записи (AW) для приема операций считывания и записи в запоминающее устройство соответственно, как проиллюстрировано на фиг. 4. Буферы 70A-70B соединяются с генератором 72 инициирования считывания и генератором 74 инициирования записи соответственно, которые соединяются с интерфейсами Rd0/Rd1 и интерфейсами Wr0/Wr1 соответственно. Генератор 72 инициирования считывания соединяется с таблицей 76 невыполненных транзакций считывания (ROTT), а генератор 74 инициирования записи соединяется с таблицей 78 невыполненных транзакций записи (WOTT). ROTT 76 соединяется с генератором 80 ответа считывания, который конфигурируется для формирования ответа считывания по интерфейсу. ROTT также соединяется с буфером 84 считывания, который соединяется для приема данных от любого MCU 56A-56B через мультиплексор 86 и предоставления считанных данных по интерфейсу. WOTT 78 соединяется с генератором 82 ответа записи, который конфигурируется для формирования ответа записи по интерфейсу. WOTT 78 также соединяется с буфером 88 перенаправления данных записи, который соединяется для предоставления данных MCU 56A-56B и соединяется для приема данных из буфера 70C, который соединяется для приема данных записи из интерфейса.

[0072] Для операции считывания буфер 70A может конфигурироваться для приема операции от интерфейса. Буфер 70A может предоставляться для захвата операции считывания и удержания ее для обработки генератором 72 инициирования считывания. В варианте осуществления буфер 70A может быть "скользящим" буфером с двумя входами, который позволяет захватить вторую операцию в случае задержки на период, пока недоступный ресурс станет доступным, соответственно упрощая синхронизацию распространения обратных запросов к источнику (источникам) по интерфейсу. Буферы 70B-70C аналогичным образом могут быть скользящими буферами с двумя входами. Другие варианты осуществления по желанию могут включать в себя дополнительные входы в скользящие буферы.

[0073] Генератор 72 инициирования считывания может конфигурироваться для декодирования адреса операции считывания, чтобы определить, какой канал запоминающего устройства адресуется операцией считывания. Генератор 72 инициирования считывания может конфигурироваться для передачи операции считывания в адресуемый канал запоминающего устройства по интерфейсу Rd0 или Rd1. В некоторых вариантах осуществления операция считывания может совмещать каналы запоминающего устройства. Каждая операция считывания может задавать размер (то есть количество байтов для считывания, начиная с адреса операции). Если сочетание размера и адреса указывает, что байты считываются из более чем одного канала, то генератор 72 инициирования считывания может конфигурироваться для формирования нескольких операций считывания для адресуемых каналов. Считанные данные от нескольких операций считывания могут накапливаться в буфере 84 считывания для возврата источнику.

[0074] Генератор 72 инициирования считывания также может конфигурироваться для обновления ROTT 76, назначая запись в ROTT 76 для отслеживания хода считывания. Как только данные приняты в буфере 84 считывания, ROTT 76 может конфигурироваться для сигнализации генератору 80 ответа считывания, чтобы тот формировал ответ считывания для передачи данных к источнику. Если считанные данные требуется возвращать по порядку в интерфейсе (например, в соответствии с протоколом интерфейса), то данные могут остаться буферизованными в буфере 84 считывания, пока не возвращены предыдущие считывания, а затем ROTT 76 может сигнализировать генератору 80 ответа считывания, чтобы тот передавал данные. ROTT 76 может соединяться для приема различных сигналов состояния от MCU 56A-56B для обновления состояния ожидающих операций считывания (не показано на фиг. 4).

[0075] Буфер 70B, генератор 74 инициирования записи и WOTT 78 могут работать аналогичным образом для операций записи. Однако данные по интерфейсу принимаются, а не передаются. Данные записи можно принять в буфере 88 перенаправления данных записи и можно перенаправить в текущее расположение соответствующей операции записи. WOTT 78 может сигнализировать ответ записи, как только гарантировано завершение записи, прекращая записи в интерфейсе с ответом записи раньше, чем это могло бы стать возможным иным способом.

[0076] Отметим, что хотя вариант осуществления, проиллюстрированный на фиг. 4, включает в себя интерфейс, который раздельно передает операции считывания и записи в запоминающее устройство (AR и AW соответственно), другие варианты осуществления могут включать в себя одну передающую среду для операций считывания и записи. В таком варианте осуществления один буфер 70 может принимать операции, и генератор 72 инициирования считывания и генератор 74 инициирования записи могут декодировать команду от интерфейса, чтобы различать операции считывания и записи. В качестве альтернативы может быть один генератор, который формирует операции считывания и записи и соответственно обновляет ROTT 74 или WOTT 78.

[0077] Обращаясь теперь к фиг. 5, показана блок-схема, иллюстрирующая один вариант осуществления MCIU 60A. MCIU 60B может быть аналогичным за исключением того, что он соединяется для приема входных данных Rd1 и Wr1 из каждого порта и соединяется с MCU 56B. В проиллюстрированном варианте осуществления MCIU включает в себя набор очередей считывания, например очередей 90A-90B считывания, показанный на фиг. 5, и набор очередей записи, например очередей 92A-92B записи. Может присутствовать одна очередь считывания и одна очередь записи для каждого порта. Каждая очередь считывания соединяется с выходом Rd0 одного из блоков 58A-58E интерфейсов портов и соединяется с арбитром 94A QoS. Каждая очередь записи соединяется с выходами Wr0 соответствующего одного из блоков 58A-58E интерфейсов портов и с арбитром 94B QoS. Выходы арбитров 94A-94B QoS предоставляются в MCU 56A в качестве входов считывания и записи соответственно. Арбитры 94A-94B QoS соединяются для приема данных из регистров 62 совместного использования полосы пропускания.

[0078] Два входа очереди считывания показаны в очереди 90A считывания, и другие очереди считывания могут быть аналогичными. Очередь 90A считывания включает в себя FID операции в запоминающем устройстве, параметр QoS операции, бит принудительного задания (P) и другое поле (Oth). FID и параметр QoS могут быть теми же значениями, которые передавались вместе с операцией в запоминающем устройстве по интерфейсу в контроллер 40 запоминающего устройства. В качестве альтернативы одно или оба значения для удобства могут перекодироваться контроллером 40 запоминающего устройства внутри себя. Бит принудительного задания может использоваться для принудительного задания более высокого приоритета у операции в запоминающем устройстве, если вторая операция в запоминающем устройстве располагается за этой операцией в запоминающем устройстве и является более высоким уровнем QoS, чем эта операция в запоминающем устройстве. Например, вторая операция в запоминающем устройстве может приниматься в том же порту, что и операция в запоминающем устройстве, и интерфейс в этом порту может требовать, чтобы данные возвращались в таком же порядке, как передаются операции в запоминающем устройстве. Путем принудительного задания более высокого приоритета операция в запоминающем устройстве может выполняться быстрее и соответственно может дать возможность быстрого обслуживания второй операции в запоминающем устройстве с более высоким уровнем QoS. Другое поле может включать в себя различную информацию для операции в запоминающем устройстве (например, информацию об адресе, размере и т.п.). Аналогичным образом, два входа очереди записи показаны в очереди 92A записи, и она может включать в себя поля, аналогичные очереди 90A считывания. Другое поле при желании может хранить иную информацию для записей по сравнению со считываниями.

[0079] Арбитры 94A-94B QoS могут разрешать конфликты между очередями 90A-90B считывания и очередями 92A-92B записи соответственно. Арбитры QoS могут учитывать как уровни QoS (которые указаны параметрами QoS в очередях), так и параметры совместного использования полосы пропускания из регистров совместного использования полосы пропускания. Выбранная операция считывания и записи (при наличии) передается в MCU 56A.

[0080] Отметим, что в некоторых вариантах осуществления может присутствовать один или несколько обходных путей из блока интерфейса порта в арбитры 94A и/или 94B QoS (не показано на фиг. 5). Например, считывания от блока 58C интерфейса порта CPU могут по обходному пути идти в арбитр 94A QoS, чтобы разрешить считывания с меньшей задержкой к процессорам. В некоторых вариантах осуществления одна или несколько операций в запоминающем устройстве в очередях 90A-90B и/или 92A-92B могут скрываться от арбитров 94A-94B QoS. Например, операции записи, для которых соответствующие данные еще не достигли контроллера 40 запоминающего устройства, могут скрываться от арбитров 92A-92B QoS, чтобы избежать операции блокирующей записи из других портов, для которых соответствующие данные достигли контроллера 40 запоминающего устройства.

[0081] Фиг. 6 - блок-схема операций, иллюстрирующая работу одного варианта осуществления каждого из арбитров 94A-94B QoS. Хотя для упрощения понимания этапы показаны в конкретном порядке, могут использоваться другие порядки. Этапы могут выполняться параллельно в комбинаторной логике в арбитрах 94A-94B QoS. Этапы, сочетания этапов и/или блок-схема операций в целом могут конвейерно обрабатываться за несколько тактов. Арбитры 94A-94B QoS могут конфигурироваться для реализации работы, проиллюстрированной на фиг. 6.

[0082] Если по меньшей мере одна операция в запоминающем устройстве в одной из очередей, с которой соединяется арбитр QoS, имеет уровень QoS RT в виде RTY или RTR, либо бит принудительного задания устанавливается по меньшей мере для одной операции в запоминающем устройстве (этап 100 ветвления, ветвь "да"), то арбитр QoS может разрешать конфликты между очередями, имеющими уровни RTY или RTR QoS и/или установленные биты принудительного задания (этап 102). Поскольку в этом варианте осуществления каждая очередь соответствует порту, арбитр QoS может эффективно разрешать конфликты между портами, имеющими уровни RTY или RTR QoS и/или установленные биты принудительного задания. Таким образом, в этом варианте осуществления AIU 54 может считать равными уровни QoS в виде RTG, BEF и LLT. AIU 54 в этом варианте осуществления может считать уровни RTR и RTY QoS и операции установки бита принудительного задания равными друг другу и имеющими более высокий приоритет, нежели другие уровни. Другие варианты осуществления могут иметь дополнительную крупность разбиения (например, RTR может считаться более высоким приоритетом, чем RTY, RTG и LLT могут считаться более высоким приоритетом, чем BEF, и т.п.). Более того, другие варианты осуществления могут реализовывать иную схему, нежели круговое обслуживание.

[0083] С другой стороны, если отсутствуют операции в запоминающем устройстве, имеющие уровни RTY или RTR QoS, и отсутствуют операции в запоминающем устройстве, имеющие установленные биты принудительного задания (этап 100 ветвления, ветвь "нет"), то арбитр QoS может разрешать конфликты между всеми очередями (всеми портами) (этап 104). Например, арбитр QoS может реализовать схему взвешенного циклического обслуживания с дефицитом между портами, где веса могут основываться на параметрах совместного использования полосы пропускания (или параметры совместного использования полосы пропускания могут быть весами). Другие варианты осуществления могут реализовывать другие арбитражные схемы между всеми портами.

[0084] Обращаясь теперь к фиг. 7, показана блок-схема одного варианта осуществления PSQ 64. В проиллюстрированном варианте осуществления PSQ 64 включает в себя блок 110 управления постановкой в очередь, набор очередей 112 транзакций, планировщик 114 и обходной мультиплексор 116. Блок 110 управления постановкой в очередь соединяется для приема операций считывания и записи от соответствующего MCIU 60A или 60B и соединяется с очередями 112 транзакций. Очереди 112 транзакций дополнительно соединяются с планировщиком 114, выход которого соединяется с обходным мультиплексором 116. Обходной мультиплексор 116 также соединяется для приема операции считывания и конфигурируется для выбора между операцией в запоминающем устройстве, запланированной планировщиком 114, и операцией считывания. Например, операция считывания может обходить очереди 112 транзакций, если отсутствуют считывания в очередях 112 транзакций и количество записей ниже некоторого порогового уровня. Другие варианты осуществления могут не реализовывать обход, и обходной мультиплексор 116 можно исключить.

[0085] Как проиллюстрировано на фиг. 7, очереди 112 транзакций могут включать в себя набор родственных очередей считывания, например очередей 118A-118B, и набор родственных очередей записи, например очередей 120A-120B. Количество родственных очередей считывания и родственных очередей записи может меняться от одного варианта осуществления к другому, и количество родственных очередей считывания не должно быть равным количеству родственных очередей записи. Каждая родственная очередь может хранить одну или несколько операций в запоминающем устройстве, которые определены блоком 110 управления постановкой в очередь как проявляющие родственность друг с другом. Таким образом, когда операция в запоминающем устройстве принимается блоком 110 управления постановкой в очередь, блок 110 управления постановкой в очередь может конфигурироваться для сравнения операции в запоминающем устройстве с родственными очередями 118A-118B (для операции считывания) или с родственными очередями 120A-120B (для операции записи). Если операция в запоминающем устройстве является родственной, то ее можно поставить в соответствующую родственную очередь. Если это не так, то операцию в запоминающем устройстве можно поставить в другую родственную очередь. В варианте осуществления родственную очередь считывания можно зарезервировать для считываний, которые не являются родственными, и аналогичным образом родственную очередь записи можно зарезервировать для записей, которые не являются родственными.

[0086] Планировщик 114 может конфигурироваться для планирования операций в запоминающем устройстве, которые нужно передать в MIF 66. Для операций считывания планировщик 114 может конфигурироваться для учета уровней QoS в родственных очередях 118A-118B считывания и количества родственных операций в запоминающем устройстве в каждой родственной очереди 118A-118B считывания. Один вариант осуществления более подробно описывается ниже. Однако в целом планировщик 114 может конфигурироваться для поддержки операций считывания, которые имеют высокие уровни QoS и большие количества родственных операций в запоминающем устройстве. Для операций записи уровни QoS могут аннулироваться в PSQ 64. То есть уровни QoS у операций записи могут отбрасываться, когда операции записи записываются в очереди 112 транзакций. Как проиллюстрировано в типовых входах в каждую из очередей 118A и 120A, операции считывания могут сохранять QoS, тогда как операции записи не могут. Планировщик 114 может конфигурироваться для планирования между операциями считывания и операцией записи, например, на основе заполненности очередей записи и уровней QoS в очередях считывания. Дополнительные подробности будут предоставлены ниже.

[0087] Отметим, что в некоторых вариантах осуществления родственные очереди 118A-118B считывания и родственные очереди 120A-120B записи можно конкретизировать физически (например, в виде отдельных структур данных или в виде одной или нескольких структур данных, которые разделяются логическими схемами в PSQ 64 и/или отделяются программно). В других вариантах осуществления родственные очереди могут быть виртуальными. То есть может присутствовать, например, очередь считывания и очередь записи, и может использоваться маркировка для идентификации родственных операций.

[0088] Фиг. 8 - блок-схема операций, иллюстрирующая работу одного варианта осуществления блока 110 управления постановкой в очередь в ответ на прием операции в запоминающем устройстве. Хотя для упрощения понимания этапы показаны в конкретном порядке, могут использоваться другие порядки. Этапы могут выполняться параллельно в комбинаторной логике в блоке 110 управления постановкой в очередь. Этапы, сочетания этапов и/или блок-схема операций в целом могут конвейерно обрабатываться за несколько тактов. Блок 110 управления постановкой в очередь может конфигурироваться для реализации работы, проиллюстрированной на фиг. 8. Блок 110 управления постановкой в очередь может конфигурироваться для реализации работы, проиллюстрированной на фиг. 8, параллельно для операции считывания и операции записи, принятых одновременно.

[0089] Блок 110 управления постановкой в очередь может сравнить принятую операцию с соответствующими родственными очередями 118A-118B или 120A-120B, чтобы определить, проявляет ли принятая операция родственность с операциями в очереди (этап 130 ветвления). В ответ на обнаружение родственности (и если для операции имеется место в родственной очереди) блок 110 управления постановкой в очередь может поставить операцию в родственную очередь (этап 132). В ответ на необнаружение родственности блок 110 управления постановкой в очередь может поставить операцию в пустую родственную очередь (этап 134).

[0090] Обнаружение родственности показано в развернутом представлении на фиг. 8 для одного варианта осуществления. Операция может быть родственной, если это попадание на страницу с другими операциями в родственной очереди (этап 136 ветвления, ветвь "да") или промах банка или ранга с другими операциями (этапы 138 и 140 ветвления соответственно, ветви "да"). Если это не так (этапы 136, 138 и 140 ветвления, ветви "нет"), то операция не является родственной с операциями в очереди. Обнаружение, проиллюстрированное этапами 136, 138 и 140 ветвления, может выполняться параллельно для каждой родственной очереди.

[0091] Фиг. 9 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика 114 для планирования между операциями считывания и операциями записи в очередях 112 транзакций. Хотя для упрощения понимания этапы показаны в конкретном порядке, могут использоваться другие порядки. Этапы могут выполняться параллельно в комбинаторной логике в планировщике 114. Этапы, сочетания этапов и/или блок-схема операций в целом могут конвейерно обрабатываться за несколько тактов. Планировщик 114 может конфигурироваться для реализации работы, проиллюстрированной на фиг. 9.

[0092] В варианте осуществления из фиг. 9 имеются три пороговые величины для заполненности очереди записи (то есть для количества операций записи в очередях 112 транзакций): верхняя, средняя и нижняя. Верхний уровень указывает больше операций записи в очередях 112 транзакций, чем указывает средний уровень, а средний уровень указывает больше операций записи в очередях 112 транзакций, чем указывает нижний уровень. Пороговые величины в различных вариантах осуществления могут быть неизменными или программируемыми.

[0093] Планировщик 114 может конфигурироваться для обнаружения блокирующей записи (этап 150 ветвления, ветвь "да") и может конфигурироваться для планирования блокирующей записи (этап 152). Блокирующая запись может быть операцией записи, которая имеет установленный бит принудительного задания (указывающий, что операция в запоминающем устройстве, имеющая более высокий уровень QoS, располагается за этой операцией записи). Операция блокирующей записи также может быть операцией записи, которая блокирует операцию считывания по такому же адресу (или операция записи обновляет по меньшей мере один байт, считанный операцией считывания).

[0094] Если блокирующие записи отсутствуют, то планирование операции считывания в зависимости от операций записи может основываться на кредитной системе. То есть операциям считывания и операциям записи может назначаться некоторое количество кредитов. Запланированная операция в запоминающем устройстве может потреблять один кредит из соответствующего счетчика кредитов. В проиллюстрированном варианте осуществления, как только израсходованы кредиты считывания и планируется операция считывания, кредиты для считываний и записей можно перезагрузить путем добавления начальных значений кредита к текущим счетчикам. Поскольку родственные операции можно планировать в пакете, то счетчики кредитов могут уменьшиться ниже нуля, когда планируется операция считывания или записи. То есть планировщик 114 может не прерывать пакет родственных операций, если счетчик кредитов для операций уменьшается до нуля. Для краткости обсуждение относительно фиг. 9 ниже может ссылаться на операции считывания в очереди считывания и операции записи в очереди записи. Очередь считывания может включать в себя сочетание родственных очередей 118A-118B считывания, а очередь записи может включать в себя сочетание родственных очередей 120A-120B записи.

[0095] В ответ на обнаружение, что очередь записи достигла верхней пороговой величины и имеется по меньшей мере один доступный кредит записи (этап 154 ветвления, ветвь "да"), планировщик 114 может конфигурироваться для планирования из очереди записи (этап 156). Если очередь записи не достигла верхней пороговой величины или нет доступных кредитов записи (этап 154 ветвления, ветвь "нет"), но планировщик 114 определяет, что имеется по меньшей мере одна операция считывания в очереди считывания и имеется доступный кредит считывания (этап 158 ветвления, ветвь "да"), то планировщик 114 может конфигурироваться для планирования из очереди считывания (этап 160). Если в очереди считывания нет операций считывания или отсутствуют доступные кредиты считывания (этап 158 ветвления, ветвь "нет"), но планировщик 114 определяет, что очередь записи достигла средней пороговой величины и имеется доступный кредит записи (этап 162 ветвления, ветвь "да"), то планировщик может конфигурироваться для планирования из очереди записи (этап 156). Если очередь записи не достигла средней пороговой величины или нет доступных кредитов записи (этап 162 ветвления, ветвь "нет"), но планировщик 114 определяет, что имеется по меньшей мере одна операция считывания в очереди считывания и нет доступного кредита считывания (этап 164 ветвления, ветвь "да"), то планировщик 114 может конфигурироваться для планирования из очереди считывания (этап 160). Как упоминалось ранее, планировщик 114 в этом случае также может конфигурироваться для перезагрузки кредитов считывания и записи. Если нет операции считывания в очереди считывания (этап 164 ветвления, ветвь "нет") и планировщик 114 определяет, что очередь записи достигла нижней пороговой величины (этап 166 ветвления, ветвь "да"), то планировщик 114 может конфигурироваться для планирования из очереди записи (этап 156).

[0096] Хотя блок-схема операций из фиг. 9 иллюстрирует отсутствие планирования из очереди записи, пока очередь записи не достигнет нижней пороговой величины, некоторые варианты осуществления могут планировать из очереди записи, если планировщик 114 простаивает в течение некоторого периода времени. Период времени может быть фиксированным или программируемым.

[0097] Фиг. 10 - блок-схема, иллюстрирующая работу одного варианта осуществления планировщика 114 для реализации планирования из очереди записи (этап 156). Как проиллюстрировано на фиг. 10, планировщик 114 может конфигурироваться для планирования родственной очереди 120A-120B записи, имеющей наибольшее количество операций записи (этап 168).

[0098] Фиг. 11 - таблица, иллюстрирующая различные состояния, в которых может находиться планировщик 114 для планирования операций считывания из очереди считывания (этап 160). Состояния иллюстрируются в увеличивающемся порядке приоритета. Таким образом, если бы больше одной записи в таблице из фиг. 11 соответствовало содержимому очереди считывания, то запись с наивысшим приоритетом может быть состоянием планировщика 114. Планировщик 114 может конфигурироваться для планирования операций, как проиллюстрировано в столбце "Планировать" из фиг. 11 для соответствующего состояния.

[0099] Таблица из фиг. 11 может относиться к количеству считываний в очереди считывания выше или ниже зеленой или желтой пороговой величины. Зеленая и желтая пороговые величины могут отличаться от уровней RTG и RTY QoS и могут быть аналогичны рассмотренным выше пороговым величинам очереди записи. Зеленые и желтые пороговые величины могут быть неизменными или программируемыми. Более того, родственная группа может относиться к запланированной. Родственная группа может быть группой операций в одной из родственных очередей 118A-118B считывания.

[0100] Состояние считывания планировщика может быть зеленым, если количество считываний в очереди считывания ниже желтой пороговой величины (и не превышало желтую пороговую величину с момента входа в зеленое состояние), и если в очереди нет считываний RTY или RTR. В зеленом состоянии планировщик 114 может конфигурироваться для планирования операции считывания LLT, при ее наличии. Также могут планироваться операции в родственной очереди считывания с операцией считывания LLT, при их наличии. Если нет операций считывания LLT, то может планироваться родственная группа, имеющая самую старую операцию считывания.