Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ ЗАГРУЗКИ ИНТЕГРАЛЬНОЙ СХЕМЫ SOC И ИНТЕГРАЛЬНАЯ СХЕМА ТИПА SOC

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области техники беспроводной связи, а более точно к устройству для загрузки интегральной схемы «системы на кристалле» (SoC) и к интегральной схеме типа SoC.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Интегральная схема типа SoC, которая обычно содержит процессор, имеет принцип работы, отличный от специализированной интегральной схемы (ASIC). В процессе работы интегральная схема типа SoC должна поддерживаться программным обеспечением, которое компилируется в двоичный файл компилятором, а затем передается во внешнее запоминающее устройство этой интегральной схемы типа SoC. В большинстве случаев запоминающее устройство представляет собой интегральную схему флэш-памяти. Интегральная схема типа SoC связана с интегральной схемой флэш-памяти через интерфейс. Двоичный файл интегральной схемы флэш-памяти будет автоматически передан в память процессора после включения этой интегральной схемы флэш-памяти. Памятью процессора является внутреннее пространство памяти процессора, или же ею может быть флэш-память. Этот процесс осуществляется автоматически посредством модуля загрузки перед перезапуском и разблокировкой процессора. Как производительность интегральной схемы типа SoC, так и производительность системы сильно зависят от эффективности передачи данных внешнего запоминающего устройства в память интегральной схемы типа SoC устройством для загрузки. Благодаря повышению эффективности загрузки в ходе служебного процесса на уровне кристалла будет ускорен процесс отладки программного обеспечения, тем самым значительно повышена эффективность работы. Процесс загрузки программного обеспечения встроенной системы будет ускорен за счет повышения эффективности загрузки в ходе служебного процесса на уровне системы; в особенности для встроенной системы, снабженной операционной системой, такое ускорение процесса загрузки повысит производительность системы. Таким образом, возможность ускорить загрузку интегральной схемы типа SoC имеет большое значение как относительно служебных процессов на уровне кристалла, так и для служебных процессов на уровне системы.

Существующие устройства для выполнения загрузки интегральной схемы типа SoC включают, в основном, два следующих типа: первый, относящиеся к которому устройства обладают фиксированными параметрами интерфейса шины, так что дальность передачи и адреса передачи таких устройств не могут быть сконфигурированы, и эти устройства не могут гибко использоваться в различных средах обработки данных; второй, относящиеся к которому устройства для загрузки не обладают интерфейсом с прямым доступом к памяти (DMA), поэтому эффективность передачи таких устройств для загрузки является низкой, адреса передачи не могут быть сконфигурированы, и эти устройства для загрузки не могут гибко использоваться в различных средах обработки данных. Два указанных выше способа реализуют процесс загрузки интегральной схемы типа SoC в отношении аппаратных средств, однако эти способы не позволяют решить задачу повышения эффективности загрузки. В крупномасштабной встроенной системе производительность системы напрямую зависит от эффективности загрузки.

КРАТКОЕ ОПИСАНИЕ ИЗОБРТЕНИЯ

Главной целью изобретения является создание устройства для загрузки интегральной схемы типы SoC и интегральной схемы типа SoC для того, чтобы улучшить эффективность загрузки интегральной схемы типа SoC и повысить производительность интегральной схемы типа SoC.

Настоящее изобретение предоставляет устройство для загрузки интегральной схемы типа SoC; и это устройство для загрузки содержит модуль интерфейса памяти, согласующий модуль шины DMA, модуль выполнения загрузки и модуль настройки параметров, где

модуль интерфейса памяти снабжен интерфейсом шины памяти и сконфигурирован для соединения с внешней памятью;

согласующий модуль шины DMA снабжен интерфейсом шины DMA и сконфигурирован для передачи данных во внешнюю память в место для хранения, которое соответствует назначенному адресу;

модуль выполнения загрузки связан с модулем интерфейса памяти и согласующим модулем шины DMA соответственно и сконфигурирован для отправки команд считывания и записи данных во внешнюю память через модуль интерфейса памяти и для преобразования данных, передаваемых внешней памятью в данные, согласованные с согласующим модулем шины DMA, и

модуль настройки параметров сконфигурирован для настройки параметров для согласующего модуля шины DMA, модуля интерфейса памяти и модуля выполнения загрузки.

Предпочтительно модуль настройки параметров может содержать модуль настройки шинного интерфейса и модуль настройки DMA, где

модуль настройки шинного интерфейса сконфигурирован для настройки параметров модуля интерфейса памяти и согласующего модуля шины DMA, где эти параметры включают битовую ширину шины данных, параметр битовой ширины шины адреса, тип пакетной передачи и длину передаваемого пакета;

модуль настройки DMA сконфигурирован для настройки параметров согласующего модуля шины DMA, где эти параметры включают назначенный для передачи адрес и длину передачи данных, и

модуль настройки параметров управляющих команд сконфигурирован для настройки управляющих команд для отправки команд считывания и записи данных во внешнюю память.

Предпочтительно модуль настройки шинного интерфейса может быть дополнительно сконфигурирован для такой настройки типа пакетной передачи, чтобы им был 8-разрядный режим, 16-разрядный режим, 32-разрядный режим и 64-разрядный режим.

Предпочтительно модуль настройки шинного интерфейса может быть дополнительно сконфигурирован для такой настройки длины передаваемого пакета, чтобы она составляла от 1 до 16 бит.

Предпочтительно согласующий модуль шины DMA может содержать расширенную шинную архитектуру для микроконтроллеров (АМВА) 2.0, АМВА3.0 или основную шину интерфейса протокола открытого ядра (ОСР).

Настоящее изобретение предоставляет интегральную схему типа SoC; эта интегральная схема типа SoC снабжена устройством для загрузки, где устройство для загрузки содержит модуль интерфейса памяти, согласующий модуль шины DMA, модуль выполнения загрузки и модуль настройки параметров, где

модуль интерфейса памяти снабжен интерфейсом шины памяти и сконфигурирован для соединения с внешней памятью;

согласующий модуль шины DMA снабжен интерфейсом шины DMA и сконфигурирован для передачи данных во внешнюю память в место для хранения, которое соответствует назначенному адресу;

модуль выполнения загрузки связан с модулем интерфейса памяти и согласующим модулем шины DMA соответственно и сконфигурирован для отправки команд считывания и записи данных во внешнюю память через модуль интерфейса памяти и для преобразования данных, передаваемых внешней памятью в данные, согласованные с согласующим модулем шины DMA, и

модуль настройки параметров сконфигурирован для настройки параметров для согласующего модуля шины DMA, модуля интерфейса памяти и модуля выполнения загрузки.

Предпочтительно, интегральная схема типа SoC может дополнительно содержать любое из вышеописанных устройств для загрузки.

Устройство для загрузки интегральной схемы типа SoC или интегральная схема типа SoC в соответствии с настоящим изобретением могут повысить эффективность загрузки и повысить производительность системы, где интегральная схема типа SoC установлена наладкой согласующего модуля шины DMA и модуля настройки параметров.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

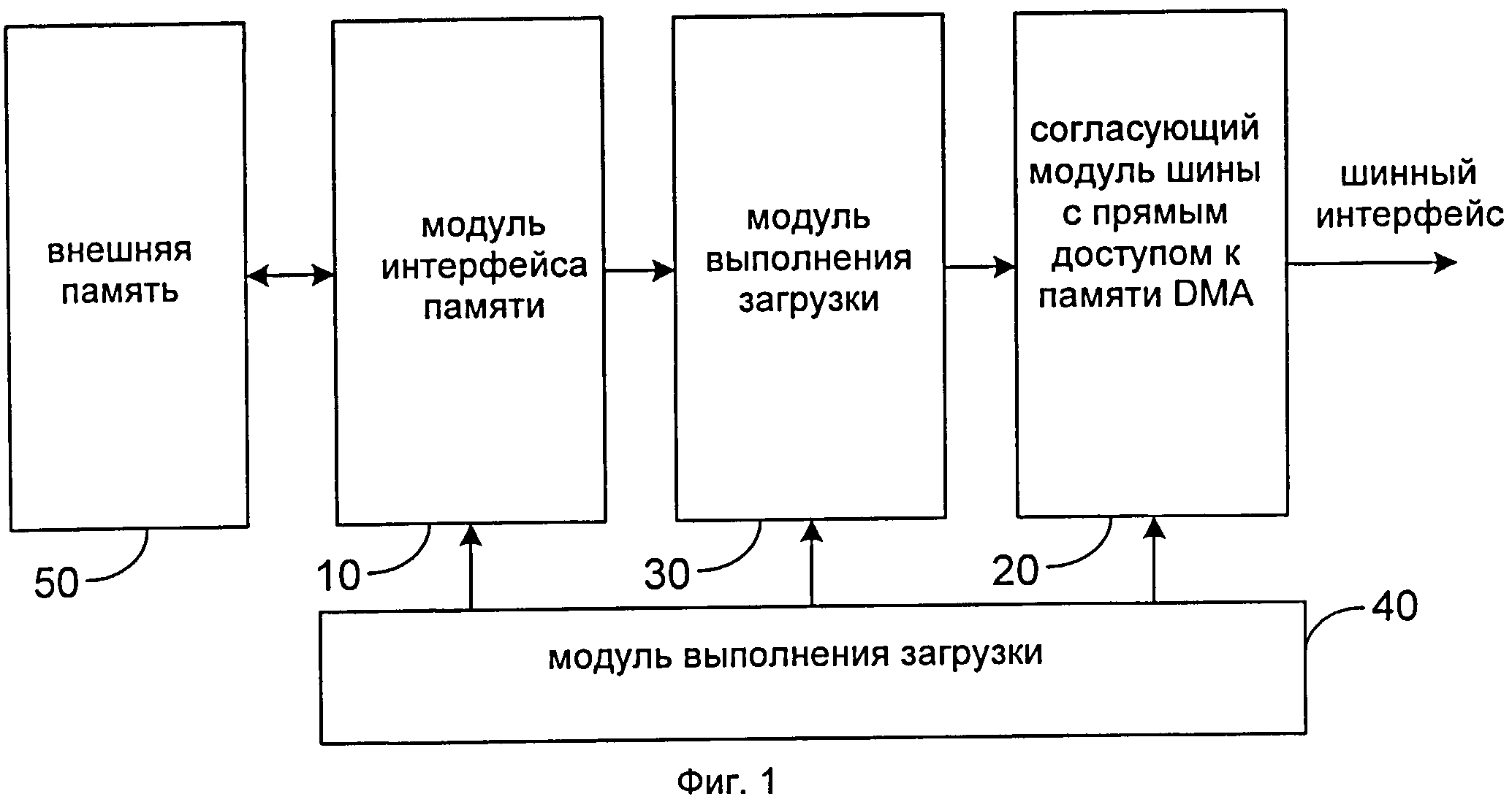

На фиг.1 изображена блок-схема устройства для загрузки интегральной схемы типа SoC в соответствии с одним вариантом осуществления настоящего изобретения, и

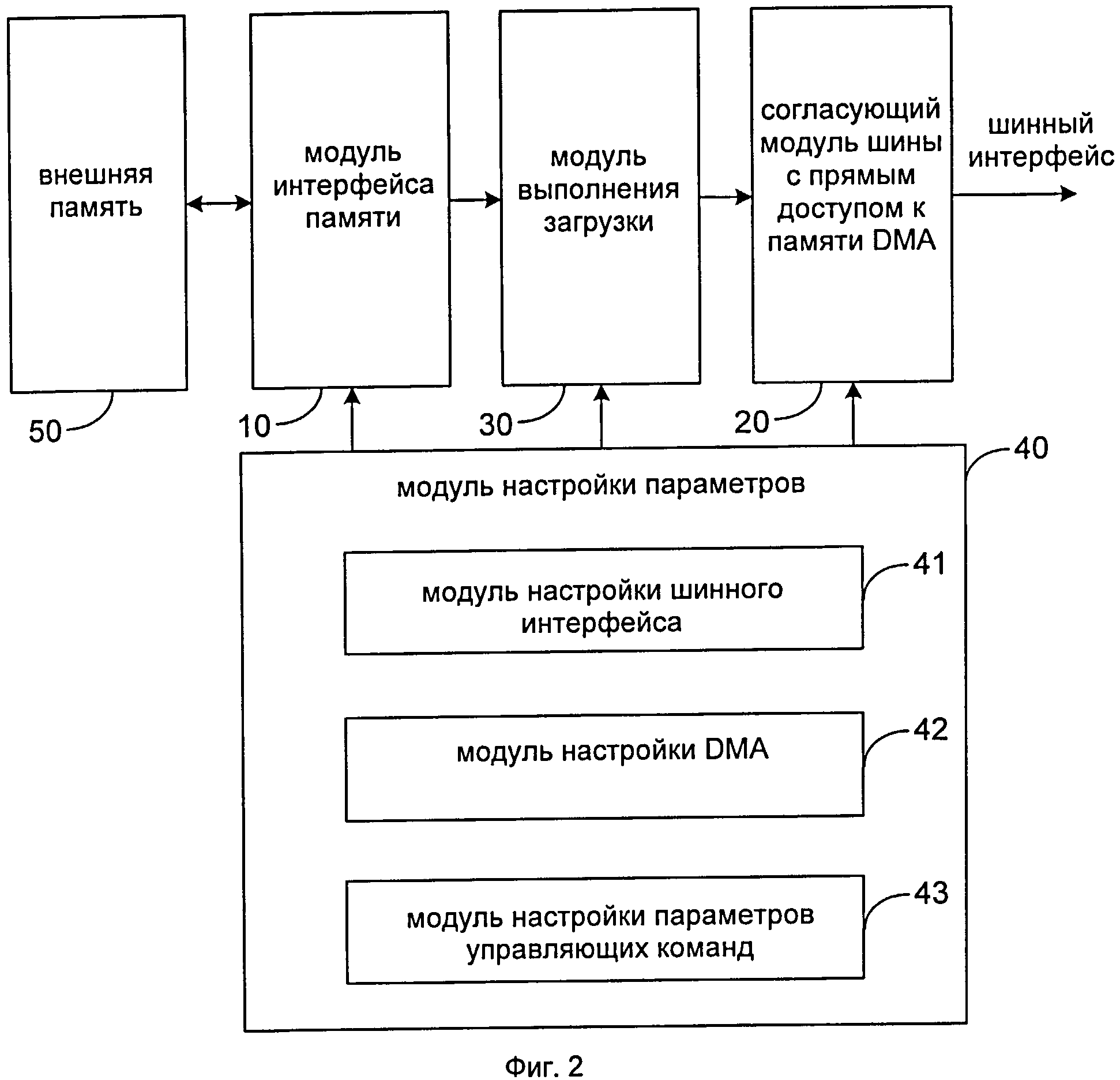

на фиг.2 изображена блок-схема устройства для загрузки интегральной схемы SoC в соответствии с вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

Следует понимать, что описанные здесь варианты осуществления используются только для объяснения настоящего изобретения и не используются для ограничения объема изобретения.

На фиг.1 изображена структура устройства для загрузки интегральной схемы типа SoC в соответствии с одним вариантом осуществления настоящего изобретения. Это устройство для загрузки содержит: модуль 10 интерфейса памяти, согласующий модуль 20 шины DMA, модуль 30 выполнения загрузки и модуль 40 настройки параметров, где

модуль 10 интерфейса памяти снабжен интерфейсом шины памяти и сконфигурирован для соединения с внешней памятью 50; внешняя память 50 может быть флэш-памятью. Модуль 10 интерфейса памяти осуществляет функцию связи интегральной схемы типа SoC и внешней интегральной схемы флэш-памяти и, в основном, содержит шину данных, шину адреса, сигнал индикации данных и т.д.;

согласующий модуль 20 шины DMA снабжен интерфейсом шины DMA и сконфигурирован для передачи данных во внешнюю память в место для хранения, которое соответствует назначенному адресу; DMA, который является способом передачи данных между памятью и периферийным устройством, отличается от способа передачи с прерыванием и не занимает время центрального процессора (CPU). Таким способом данные можно считывать и записывать без команд, выполняемых процессором, и без внутреннего регистра процессора; вместо этого для достижения высокой эффективности передачи данные записываются периферийным устройством в память или считываются из памяти непосредственно через шину данных системы. Когда передача данных выполняется DMA, цикл шины генерируется самим устройством или контроллером DMA. Устройство DMA, которое само генерирует цикл шины, называется ведущим устройством, в то время как устройство DMA, которое зависит от контроллера DMA для генерирования цикла передачи данных, называется подчиненным устройством. Настоящее изобретение относится преимущественно к ведущему устройству. Согласующий модуль 20 шины DMA может передавать данные от внешней флэш-памяти в место для хранения в процессоре, которое соответствует назначенному адресу. Рабочие режимы шины данных и шины адреса согласующего модуля 20 шины DMA могут быть сконфигурированы;

модуль 30 выполнения загрузки связан с модулем 10 интерфейса памяти и согласующим модулем 20 шины DMA соответственно и конфигурируется для отправки команд считывания и записи данных во внешнюю память 50 через модуль 10 интерфейса памяти и для преобразования данных, передаваемых внешней памятью 50 в данные, согласованные с согласующим модулем 20 шины DMA, и

модуль 40 настройки параметров сконфигурирован для настройки параметров для модуля 10 интерфейса памяти, согласующего модуля 20 шины DMA, и модуля 30 выполнения загрузки. В варианте осуществления модуль 40 настройки параметров может с помощью кодов настраивать параметры модуля 10 интерфейса памяти, согласующего модуля 20 шины DMA, и модуля 30 выполнения загрузки.

В варианте осуществления устройства для загрузки в соответствии с настоящим изобретением эффективность передачи может быть повышена путем наладки модуля 10 интерфейса памяти, согласующего модуля 20 шины DMA, модуля 30 выполнения загрузки и модуля 40 настройки параметров, и параметры могут быть гибко настроены для каждой части; повышается эффективность загрузки и улучшается производительность системы, в которой установлена интегральная схема типа SoC.

Согласно фиг.2 в варианте осуществления модуль 40 настройки параметров может содержать:

модуль 41 настройки шинного интерфейса, который сконфигурирован для настройки параметров модуля 10 интерфейса памяти и согласующего модуля 20 шины DMA; эти настраиваемые параметры включают битовую ширину шины данных, параметр битовой ширины шины адреса, тип пакетной передачи и длину передаваемого пакета; в варианте осуществления модуль 41 настройки шинного интерфейса может настраивать флэш-интерфейсные параметры, и эти флэш-интерфейсные параметры включают битовую ширину шины данных и битовую ширину шины адреса, которые могут быть настроены с возможностью режимов 8, 16, 32, 64 и т.д., соответственно, указывая, что шиной данных или адреса является шина шириной 8 бит, 16 бит, 32 бит и 64 бита соответственно. Кроме того, модуль 41 настройки шинного интерфейса может также осуществлять настройку параметров интерфейса шины DMA. Эти параметры интерфейса шины DMA включают битовую ширину шины данных и битовую ширину шины адреса, которые могут быть настроены с возможностью режимов 8, 16, 32, 64 и т.д. соответственно, указывая, что шиной данных или адреса является шина шириной 8 бит, 16 бит, 32 бит и 64 бита соответственно. Кроме того, модуль 41 настройки шинного интерфейса может также настраивать тип пакетной передачи, длину передаваемого пакета и т.д. Тип пакетной передачи может быть настроен таким образом, чтобы им был 8-разрядный режим, 16-разрядный режим, 16-разрядный режим и 32-разрядный режим, а длина передаваемого пакета может быть настроена таким образом, чтобы она составляла от 1 до 16 бит;

модуль 42 настройки DMA, который сконфигурирован для настройки параметров согласующего модуля 20 шины DMA. Настроенные параметры включают назначенный для передачи адрес и длину передаваемых данных;

модуль 43 настройки параметров управляющих команд, который сконфигурирован для настройки управляющих команд для отправки команд считывания и записи данных во внешнюю память 50. В варианте осуществления модуль 43 настройки параметров управляющих команд может настроить по меньшей мере 10 управляющих команд для управления внешней памяти 50 (например, внешней флэш-памятью). Эти 10 управляющих команд могут быть заданы свободно.

В приведенных выше вариантах осуществления согласующим модулем 20 шины DMA могут являться любые шины. Эти шины содержат расширенную шинную архитектуру для микроконтроллеров (АМВА) 2.0, АМВА3.0 или интерфейсы основной шины протокола открытого ядра (ОСР) и т.д.

Настоящее изобретение дополнительно предоставляет интегральную схему типа SoC, содержащую устройство для загрузки, упомянутое выше. Как показано на фиг.1, это устройство для загрузки содержит: модуль 10 интерфейса памяти, согласующий модуль 20 шины DMA, модуль 30 выполнения загрузки и модуль 40 настройки параметров, где

модуль 10 интерфейса памяти снабжен интерфейсом шины памяти и сконфигурирован для соединения с внешней памятью 50; эта внешняя память 50 может быть флэш-памятью. Модуль 10 интерфейса памяти осуществляет функцию связи между интегральной схемой типа SoC и внешней интегральной схемой флэш-памяти и, в основном, содержит шину данных, шину адреса, сигнал индикации данных и т.д.;

согласующий модуль 20 шины DMA снабжен интерфейсом шины DMA и сконфигурирован для передачи данных во внешнюю память в место для хранения, которое соответствует назначенному адресу; DMA, который является способом передачи данных между памятью и периферийным устройством, отличается от способа передачи с прерыванием и не занимает время CPU. Таким способом данные можно считывать и записывать без команд, выполняемых процессором, и без внутреннего регистра процессора; вместо этого для достижения высокой эффективности передачи данные записываются периферийным устройством в память или считываются из памяти непосредственно через шину данных системы. Когда передача данных выполняется посредством DMA, цикл шины генерируется самим устройством или контроллером DMA. Устройство DMA, которое само генерирует цикл шины, называется ведущим устройством, в то время как устройство DMA, которое зависит от контроллера DMA для генерирования цикла передачи данных, называется подчиненным устройством. Настоящее изобретение относится преимущественно к ведущему устройству. Согласующий модуль 20 шины DMA может передавать данные от внешней флэш-памяти в место для хранения в процессоре, которое соответствует назначенному адресу. Рабочие режимы шины данных и шины адреса этого согласующего модуля 20 шины DMA могут быть сконфигурированы;

модуль 30 выполнения загрузки связан с модулем 10 интерфейса памяти и согласующим модулем 20 шины DMA соответственно и сконфигурирован для отправки команд считывания и записи данных во внешнюю память 50 через модуль 10 интерфейса памяти, и для преобразования данных, передаваемых внешней памятью 50 в данные, согласованные с согласующим модулем 20 шины DMA, и

модуль 40 настройки параметров сконфигурирован для настройки параметров для модуля 10 интерфейса памяти, согласующего модуля 20 шины DMA, и модуля 30 выполнения загрузки. В варианте осуществления модуль 40 настройки параметров может с помощью кодов настраивать параметры модуля 10 интерфейса памяти, согласующего модуля 20 шины DMA и модуля 30 выполнения загрузки.

Кроме того, интегральная схема типа SoC в соответствии с настоящим изобретением дополнительно содержит устройство для загрузки, подобное показанному на фиг.2.

В вариантах осуществления в соответствии с настоящим изобретением эффективность передачи может быть повышена путем наладки устройства для загрузки в интегральной схеме типа SoC, а параметры могут быть гибко настроены для каждой части; повышается эффективность загрузки и улучшается производительность системы, в которой расположена интегральная схема типа SoC.

Описанное выше представляет собой только предпочтительные варианты осуществления изобретения, но не предназначено для ограничения объема патентных притязаний настоящего изобретения. Любые эквивалентные изменения структуры или последовательности операций, которые сделаны на основе описания и графических материалов настоящего изобретения или любое прямое либо косвенное применение в других смежных областях техники также подпадают под действие патентной охраны изобретения.