Результат интеллектуальной деятельности: СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Вид РИД

Изобретение

Изобретение относится к способу и системам управления летательными аппаратами, вращающимися по углу крена, и может быть использовано в системах управления ракетами, формирующими на борту команды управления, например теленаведение в луче.

Известен способ формирования линеаризированного сигнала на вращающейся по углу крена ракете и линеаризатор сигнала, основанный на нем [патент России №2282129 от 20.08.06 г., МКИ7 F41G 7/00], выбранные в качестве прототипов. Известный способ формирования линеаризированного сигнала на вращающейся по углу крена ракете, включающий формирование установленным на ракете датчиком угла крена импульсов, при котором разбивают период вращения ракеты по углу крена на временные интервалы, соответствующие одной четверти кренового периода, измеряют и запоминают длительность текущего временного интервала.

Известный линеаризатор сигнала содержит датчик крена, вычислитель, интегратор и последовательно соединенные формирователь кренового сигнала и формирователь ступенчатого сигнала, при этом первый и второй выходы датчика крена соединены соответственно с первым и вторым входами формирователя кренового сигнала.

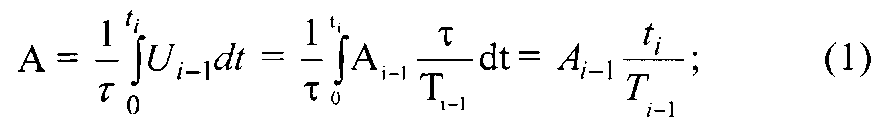

Как следует из изложенного выше величина размаха, т.е. амплитуда от пика до пика, линеаризированного сигнала на выходе линеаризатора для каждой четверти кренового периода равна

где τ - постоянная времени интегрирования,

T - длительность временного интервала.

Поскольку дискретная величина амплитуды A=Ai-1=Ai=const в каждой четверти креновоо периода, то при суммировании значения величины A из выражения (1) с величиной минус A/2 при величине, например A=2B и ti=Ti-1, значение величины размаха линеаризированного сигнала будет изменяться от минус 1B до +1B. Таким образом, при постоянной величине угловой скорости вращения ракеты по углу крена линеаризированный сигнал относительно нуля симметричен, а величина его размаха равна заданной, т.е. 2B. Однако при ускорении или замедлении вращения ракеты по углу крена, например, уменьшении ti относительно Ti-1 на 10% согласно выражения (1) с учетом суммирования линеаризированный сигнал будет изменяться от минус 1B до +0,8B, т.е. несимметрично относительно нуля, а величина его размаха 1,8B не будет равна заданной, т.е. 2B.

Ракета с момента старта и до момента попадания ее, например, в луч (в системе теленаведения) управляется автономно. При этом широтно-импульсная модулированная (ШИМ) команда управления, формируемая на ракете, например, по тангажу, равная нулю при ускоренном или замедленном движении ракеты, искажается. При этом вместо нулевой команды формируется 0,1 ед. команды, согласно примеру, приведенному выше.

Таким образом, в известном техническом решении, осуществляющим формирование линеаризированного сигнала по величине длительности предыдущего кренового импульса, при изменении величины длительности креновых импульсов возникает ошибка, величина которой тем больше, чем больше или меньше (отрицательный знак) ускорение ракеты на траектории ее полета.

Следовательно, недостатком известного способа формирования линеаризированного сигнала на вращающейся по углу крена ракете и известного линеаризатора сигнала, основанного на нем, является недостаточно высокая точность формирования линеаризованного сигнала при изменении скорости полета (ускорении) ракеты.

Известен способ интегрирования для формирования линеаризированного сигнала [Л. Фолкенберри "Применение операционных усилителей и линейных ИС", М.: Мир, стр.126-132, рис.6.2, 6.4, прототип], при котором интегрируют амплитуду линеаризированного сигнала в интервале времени, равном длительности углового интервала. Известный способ включает установку нулевого логического уровня в исходном состоянии интегратора на выходах D-триггеров и ввод входного к-разрядного двоичного параллельного числа на входы сумматоров.

Известен регистр сдвига с параллельным вводом [У. Титце, К. Шенк «Полупроводниковая схемотехника», Москва, Мир, 1983 г., стр.356 рис.20.18 прототип], где применяют способ и устройство увеличения (интегрирования, например, во времени) двоичного в параллельном виде числа. Устройство, реализующее известный способ интегрирования, содержит "n" последовательно соединенных одноразрядных ячеек, в каждую из которых входят D-триггер, сумматор.

В известном техническом решении максимальная величина двоичного числа определяется количеством "n" ячеек. При этом величину выходного двоичного числа в исходном состоянии выставляют равной нулю (0000). А затем первый тактовый импульс (его фронт) записывает в D-триггеры двоичное параллельное число, например 0001, осуществляя его ввод. Последующие тактовые импульсы его увеличивают (при сдвиге вправо) соответственно в два (21), четыре (22), восемь (23) и т.д. раз (при соответствующем количестве ячеек). Таким образом, изменение выходного сигнала нелинейное, кроме первых трех значений: 0, 20 и 21, что ухудшает точность формирования линеаризированного сигнала величины угла крена.

Следовательно, недостатком известного способа интегрирования двоичного числа в параллельном виде и устройства, его реализующего, является небольшая линейная зона изменения выходного сигнала, которую требуется корректировать, например, с помощью программируемого запоминающего устройства. Это накладывает ограничение на применение известного технического решения.

Задачей предлагаемой группы изобретений является повышение точности формирования линеаризированного сигнала на вращающейся по углу крена ракете, за счет исключения или уменьшения изменения амплитуды линеаризированного сигнала при ускорении или замедлении полета ракеты, а также повышение линейности линеаризированного сигнала, что повышает в целом точность формирования команд управления ракетой.

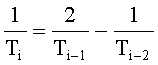

Поставленная задача достигается тем, что в способе формирования линеаризированного сигнала на вращающейся по углу крена ракете, включающем формирование установленным на ракете датчиком угла крена импульсов, при котором разбивают период вращения ракеты по углу крена на временные интервалы, соответствующие одной четверти кренового периода, измерение и запоминание длительность текущего временного интервала Ti-1, новым является то, что, до момента запоминания величины длительности текущего временного интервала запоминают ее предыдущее значение длительности Ti-2 и вычисляют величину  как

как  , где Ti - последующая длительность временного интервала, i=0, 1, 2, и т.д., при этом величину

, где Ti - последующая длительность временного интервала, i=0, 1, 2, и т.д., при этом величину  умножают на A=const - заданная дискретная величина амплитуды линеаризированного сигнала, и в течение изменения временного интервала от 0 до ti, соответствующего величине углового интервала равного четверти кренового периода вращения ракеты, величину

умножают на A=const - заданная дискретная величина амплитуды линеаризированного сигнала, и в течение изменения временного интервала от 0 до ti, соответствующего величине углового интервала равного четверти кренового периода вращения ракеты, величину  интегрируют, после чего процесс повторяют вновь.

интегрируют, после чего процесс повторяют вновь.

Линеаризатор сигнала, содержащий интегратор, вычислитель, последовательно соединенные формирователь кренового сигнала и формирователь ступенчатого сигнала, датчик крена, первый и второй выходы которого соединены с соответствующими входами формирователя кренового сигнала, новым является то, что, в него введены регистр и формирователь тактовых импульсов, а интегратор выполнен цифровым, при этом вход формирователя тактовых импульсов соединен с третьим выходом формирователя ступенчатого сигнала, а выход - с тактовым входом интегратора, вход записи регистра соединен с четвертым выходом формирователя ступенчатого сигнала, информационный выход регистра соединен со вторым информационным входом вычислителя, а информационный вход регистра вместе с первым информационным входом вычислителя соединен с вторым выходом формирователя ступенчатого сигнала, причем информационный выход вычислителя соединен с информационным входом интегратора, вход обнуления которого соединен с первым являющимся управляющим выходом формирователя ступенчатого сигнала. Формирователь тактовых импульсов выполнен как цифровой делитель частоты. Формирователь ступенчатого сигнала выполнен в виде синхронизатора, регистра формирователя, логической схемы "И", счетчика импульсов, последовательно включенных первого, второго и третьего формирователей импульсов, "RS"-триггера, при этом инвертируемый выход "RS"-триггера и выход регистра формирователя являются соответственно первым и вторым выходами формирователя ступенчатого сигнала, выход синхронизатора и первый вход логической схемы "И" являются третьим выходом формирователя ступенчатого сигнала, четвертым выходом которого является первый вход "RS"-триггера и первый выход первого формирователя импульсов.

Переключаемый линеаризатор сигнала, содержащий интегратор, вычислитель, последовательно соединенные формирователь кренового сигнала и формирователь ступенчатого сигнала, датчик крена, первый и второй выходы которого соединены с соответствующими входами формирователя кренового сигнала, новым является то, что, в него введены регистр, блок управления, коммутатор, второй вычислитель и формирователь тактовых импульсов, а интегратор выполнен цифровым, при этом вход формирователя тактовых импульсов соединен с третьим выходом формирователя ступенчатого сигнала, а выход - с тактовым входом интегратора, выполненный как цифровой, при этом первый информационный вход второго вычислителя и информационный вход регистра вместе с информационным входом первого вычислителя соединен со вторым выходом формирователя ступенчатого сигнала, информационный выход регистра соединен со вторым информационным входом второго вычислителя, информационный выход которого соединен со вторым информационным входом коммутатора, первый информационный вход которого соединен с информационным выходом первого вычислителя, информационный выход коммутатора соединен с информационным входом интегратора, а управляющий вход коммутатора - с выходом блока управления, вход которого соединен с первым выходом датчика крена, вход записи регистра соединен с четвертым выходом формирователя ступенчатого сигнала, первый выход которого соединен с входом обнуления интегратора. Формирователь тактовых импульсов выполнен как цифровой делитель частоты. Формирователь ступенчатого сигнала выполнен в виде синхронизатора, регистра формирователя, логической схемы "И", счетчика импульсов, последовательно включенных первого, второго и третьего формирователей импульсов, "RS"-триггера, при этом инвертируемый выход "RS"-триггера и выход регистра формирователя являются соответственно первым и вторым выходами формирователя ступенчатого сигнала, выход синхронизатора и первый вход логической схемы "И" являются третьим выходом формирователя ступенчатого сигнала, четвертым выходом которого является первый вход "RS"-триггера и первый выход первого формирователя импульсов. Блок управления выполнен как "RS"-триггер, R-вход которого соединен с первым выходом датчика крена, а S-вход с выходом бортового источника питания. Коммутатор выполнен, как два одинаковых электронных ключа.

Технический результат достигается также тем, что, способ интегрирования для формирования линеаризированного сигнала на вращающейся по углу крена ракете, включающий интегрирование в интервале времени, равном длительности углового интервала, амплитуды тактовых импульсов, установку нулевого логического уровня в исходном состоянии на выходах D-триггеров и ввод к-разрядного двоичного параллельного числа на входы сумматоров, новым является то, что на первые входы ai сумматоров подают соответствующее значение каждого разряда входного к-разрядного двоичного параллельного числа, которые поразрядно суммируют в каждом последующем соответствующем сумматоре по вторым его входам bi+1 с величинами разрядов двоичного параллельного числа с выходов переноса Ci+1 из каждого предыдущего сумматора, запоминают значение суммарного параллельного двоичного числа на выходе суммы Si, соответствующей каждому сумматору в момент формирования первого фронта нарастания тактовых импульсов, а после дополнительно суммируют запомненные значения каждого разряда двоичного параллельного числа, поступающего на входы переноса ci данных сумматоров, со значениями сумм первых входов ai со вторыми bi, где i=1, 2, …к - номера разрядов двоичного параллельного числа (от младшего к старшему), после чего данный цикл суммирования многократно повторяют в моменты формирования второго и последующих фронтов нарастания тактовых импульсов, причем длительность интервала интегрирования выставляют соответствующую длительности углового интервала, равного 90°, по окончанию которой устанавливают на выходах D-триггеров нулевой логический уровень, а затем повторяют вновь процесс интегрирования, причем этом с каждым циклом суммирования текущее значение выходного двоичного параллельного числа, разряды которого формируют на выходах D-триггеров, увеличивают на постоянную дискретную величину амплитуды, количество дискретных величин которой ограничивают заданной величиной, соответствующей длительности углового интервала, меняют дискретную величину перед началом процесса интегрирования, при котором обновляют входное к-разрядное двоичное параллельное число.

Цифровой интегратор, содержащий "n" последовательно соединенных цифровых одноразрядных ячеек, в каждую из которых входит D-триггер, сумматор, новым является то, что, сумматор выполнен двухвходовым, выход суммы которого соединен с информационным входом D-триггера, информационный выход которого из последующей ячейки соединен с информационным входом из предыдущей ячейки, выход D-триггера соединен с входом переноса сумматора, который из каждой предыдущей цифровой одноразрядной ячейки соединен с вторым входом сумматора из каждой последующей цифровой одноразрядной ячейки, причем первые входы сумматоров из всех цифровых одноразрядных ячеек соединены вместе и являются информационным входом цифрового интегратора, второй вход сумматора из первой цифровой одноразрядной ячейки и первый вход сумматора из последней одноразрядной ячейки не заимствованы и соединены с корпусом, а выходы D-триггеров из соответствующих ячеек объединены и являются выходом цифрового интегратора.

Заявленный способ формирования линеаризированного сигнала на вращающейся по углу крена ракете реализуется следующим образом. С момента старта ракета начинает вращаться по углу крена, например, за счет разворота лопастей стабилизаторов. При этом датчик угла крена, установленный на ракете, формирует импульсы. Эти импульсы представляют собой два логических сигнала единичный и нулевой, логические уровни которых равны угловым интервалам 180°, а период повторения каждого из них соответствует 360°. Причем эти два логических сигнала сдвинуты по фазе относительно друг друга на 90°. Используя эти два логических сигнала, разбивают креновый период (угловой интервал 0°…360°) на временные интервалы, соответствующие одной четверти кренового периода т.е. 0°…90°, 90°…180°, 180°…270°, 270°…360°.

Полет ракеты представляет собой винтовое движение, слагаемое из прямолинейного поступательного движения со скоростью υ и вращения вокруг своей оси с угловой скоростью вращения ω, например, за счет стабилизаторов, создающих вращательное движение. ["Физический энциклопедический словарь". Гл. редактор A.M. Прохоров, Москва, "Сов. Энциклопедия" 1984 г., стр.77], при этом

где p - параметр винта.

При равномерно-ускоренном или равномерно-замедленном движении ракеты на участке изменения скорости от υ0 до υt средняя (промежуточная) скорость υср определится как

Откуда

Следовательно, измеряя величины υ0 и υср, можно определить ожидаемую величину скорости υt.

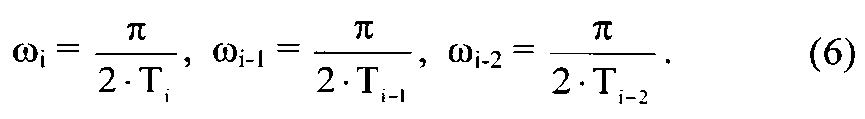

Таким образом, при равномерно-ускоренном или равномерно-замедленном полете ракеты, т.е. при линейном или близкому к линейному изменению скорости полета, зная два значения угловой скорости (скорости вращения ракеты по углу крена): ωi-2 - предыдущее (соответствующее начальной скорости υ0) и ωi-1 - текущее (соответствующее средней скорости υcp.), с учетом выражения (4) можно однозначно вычислить значение последующей (будущей) угловой скорости ωi - последующую (соответствующую конечной υt) без учета постоянной величины коэффициента p (параметра винта).

где i=0…n каждые предыдущая (i-2), текущая (i-1) и последующая (будущая - i) четверти периодов вращения ракеты по углу крена, каждая из которых соответствует угловому интервалу 90°, и определяет величины соответствующих угловых скоростей.

Учитывая, что

Подставляя их в выражение (4) получим для каждой четверти кренового периода

Таким образом, измеряют и запоминают длительность текущего временного интервала Ti-1. Причем до момента запоминания величины длительности текущего временного интервала, переписывают ее предыдущее значение Ti-2, которое также запоминают, а затем вычисляют величину  , используя выражение (7), где Ti - последующая (будущая) длительность временного интервала, i=0, 1, 2 и т.д., при этом при вычислении дополнительно умножают величину

, используя выражение (7), где Ti - последующая (будущая) длительность временного интервала, i=0, 1, 2 и т.д., при этом при вычислении дополнительно умножают величину  на Ai=A=const согласно выражению (1).

на Ai=A=const согласно выражению (1).

Поскольку запоминают величины Ti-1 и Ti-2, то запоминается и вычисленная величина  , определяющая величину изменяемого угла крена ракеты (в каждой четверти 0°-90°, 90°-180°, 180°-270° и 270°-360°) в течение временного интервала ti. Для этого вычисленную величину

, определяющая величину изменяемого угла крена ракеты (в каждой четверти 0°-90°, 90°-180°, 180°-270° и 270°-360°) в течение временного интервала ti. Для этого вычисленную величину  интегрируют в течение временного интервала от 0 до ti равного Ti. После чего процесс повторяют вновь.

интегрируют в течение временного интервала от 0 до ti равного Ti. После чего процесс повторяют вновь.

Таким образом, формируемый линеаризированный сигнал на вращающейся по углу крена ракете, при малом изменении величины ускорения ракеты в течение 3/4 кренового периода, практически исключает изменение величины (размаха) сигнала, ведущего к не симметрии его относительно нуля.

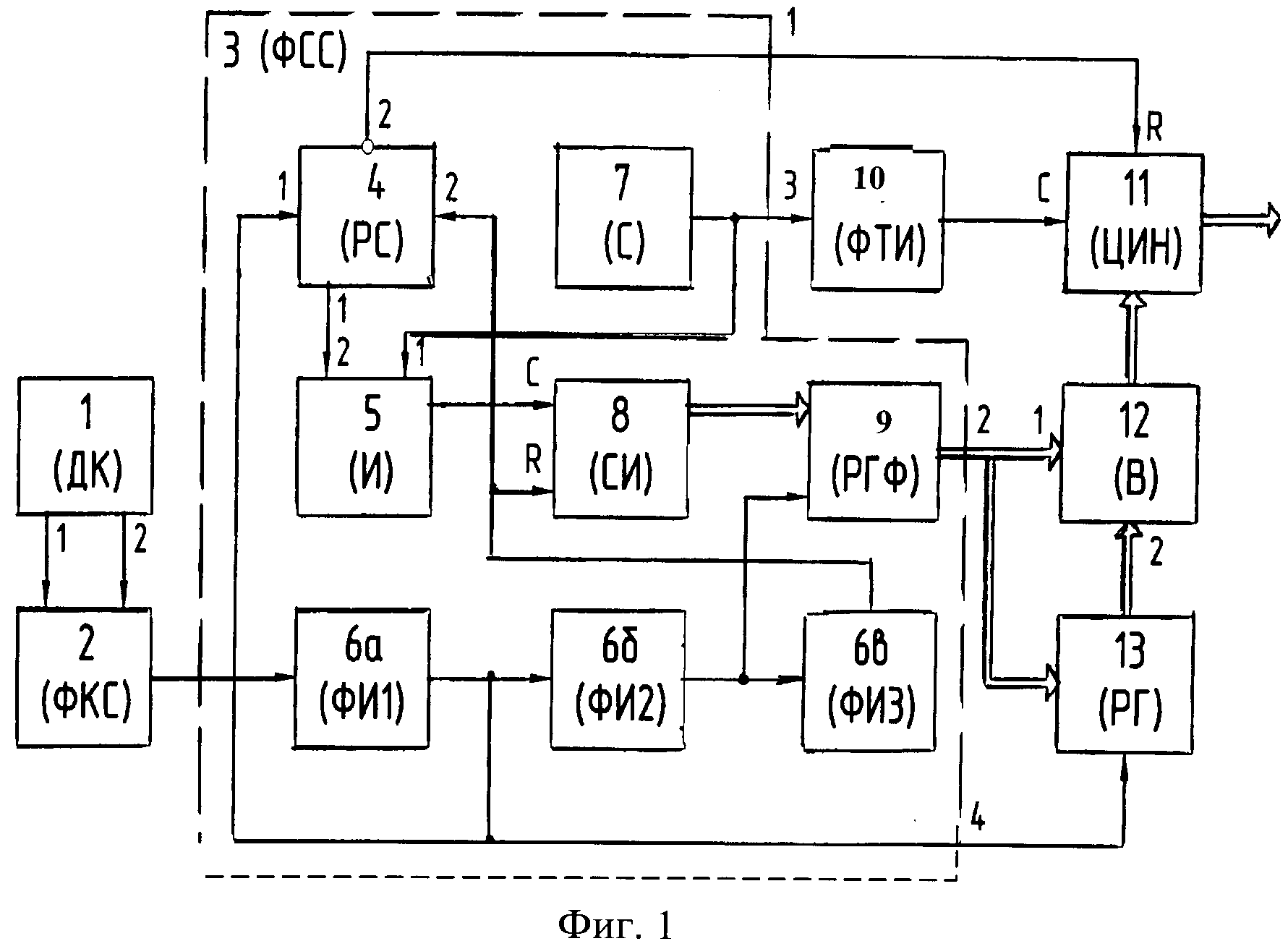

Предлагаемое изобретение поясняется чертежами:

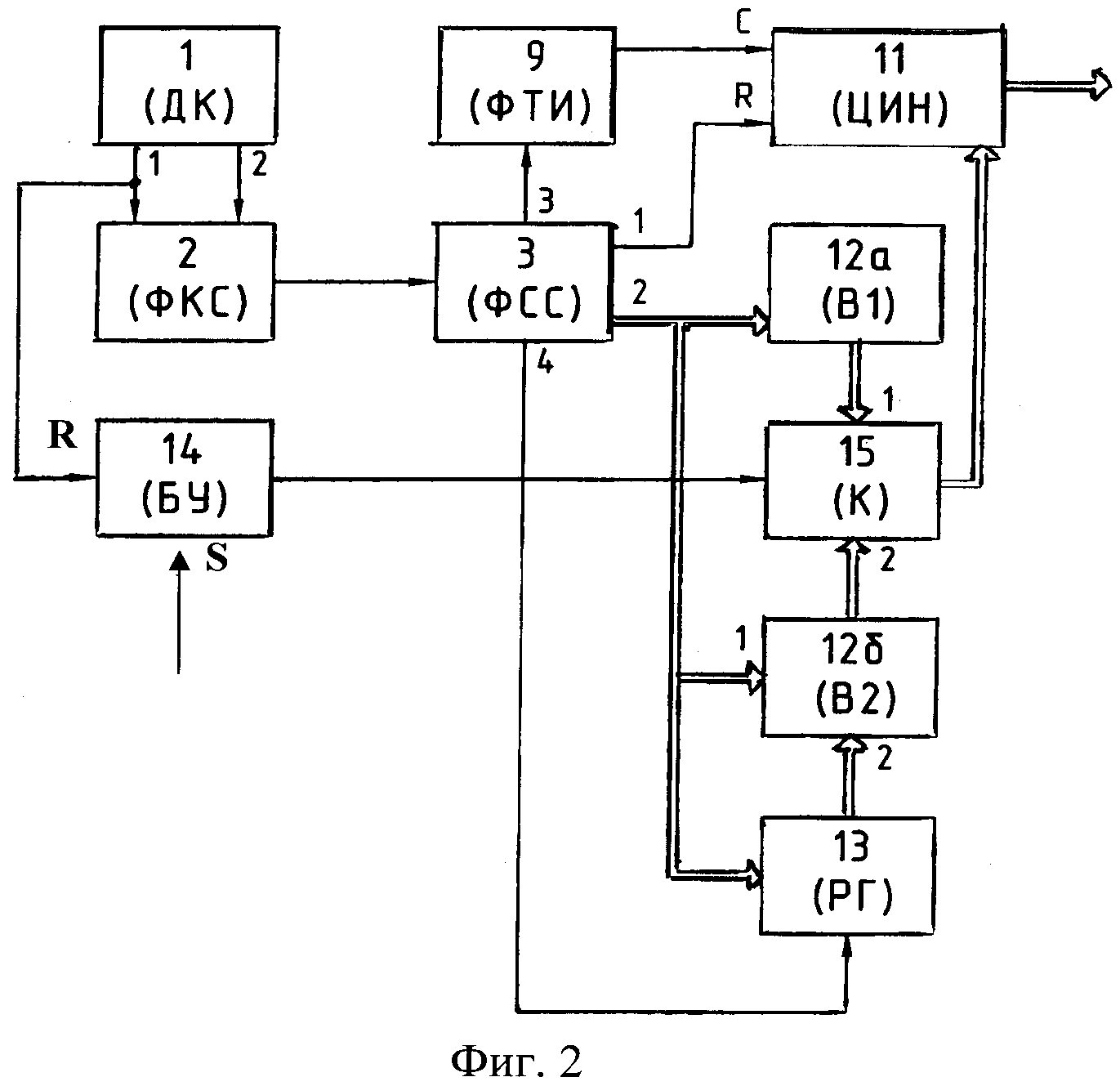

На фиг.1 и 2 приведены структурные электрические схемы соответственно линеаризатора сигнала и переключаемого линеаризатора сигнала, основанных на этом способе, где: 1 - датчик крена (ДК), 2 - формирователь кренового сигнала (ФКС), 3 - формирователь ступенчатого сигнала (ФСС), 4 - "RS"-триггер (PC), 5 - логическая схема "И" (И), 6а, 6б и 6в - первый, второй и третий формирователи импульсов, соответственно (ФИ1, ФИ2 и ФИ3), 7 - синхронизатор (С), 8 - счетчик импульсов (СИ), 9 - формирователь тактовых импульсов (ФТИ), 10 - регистр формирователя (РГФ), 11 - цифровой интегратор (ЦИН), 12 - вычислитель (В) для фиг.1 и 12а, 12б - первый и второй вычислители соответственно (В1 и B2) для фиг.2, 13 - регистр (РГ), 14 - блок управления (БУ), 15 - коммутатор (К).

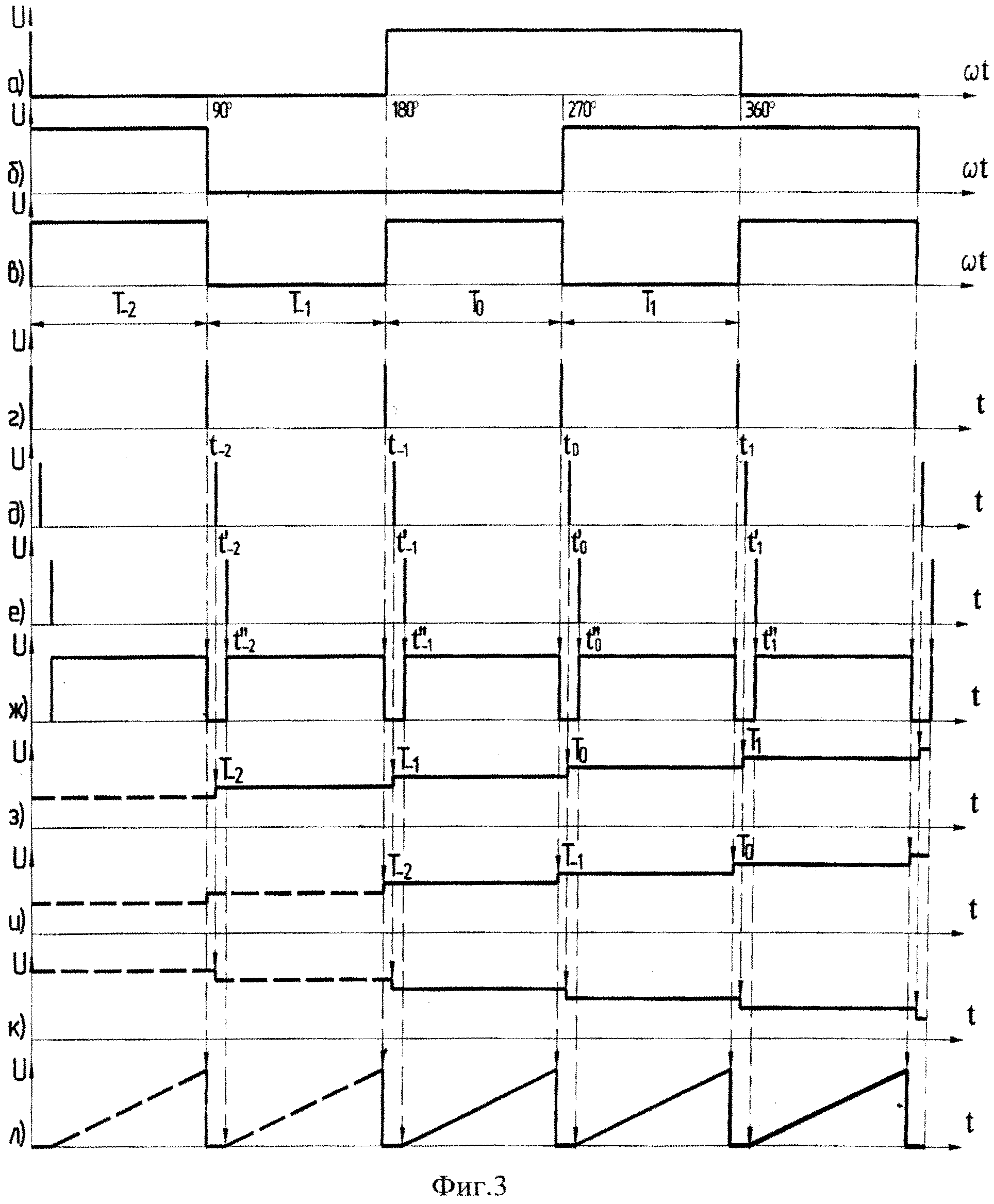

На фиг.3 приведены эпюры сигналов, где представлены: эпюры "а" и "б" - сигналы на первом и втором выходах датчика крена 1, эпюра "в" - сигнал на выходе формирователя кренового сигнала 2, эпюры "г", "д" и "е" - сигналы на выходах, соответственно, первого 6а, второго 6б и третьего 6в формирователей импульсов, эпюра "ж" - сигнал на не инвертированном первом выходе "RS"-триггера 4, эпюра "з" - сигнал на выходе регистра формирователя 10, эпюра "и" - сигнал на выходе регистра 13, эпюра "к" - сигнал на выходе вычислителя 12, эпюра "л" - сигнал (упрощенный в аналоговом виде) на выходе цифрового интегратора 11. На эпюрах "з" и "и" условно приведено изменение величины сигналов U.

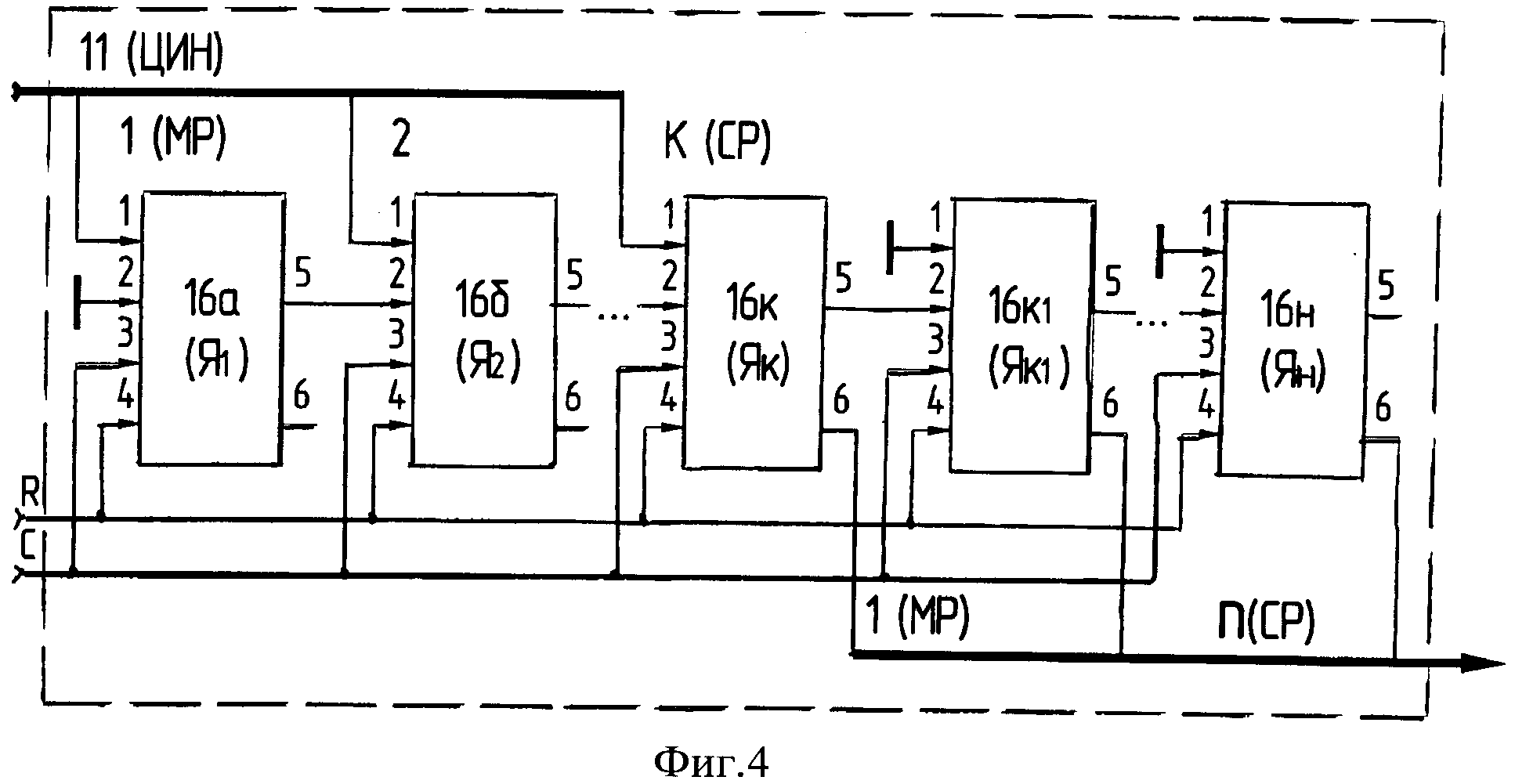

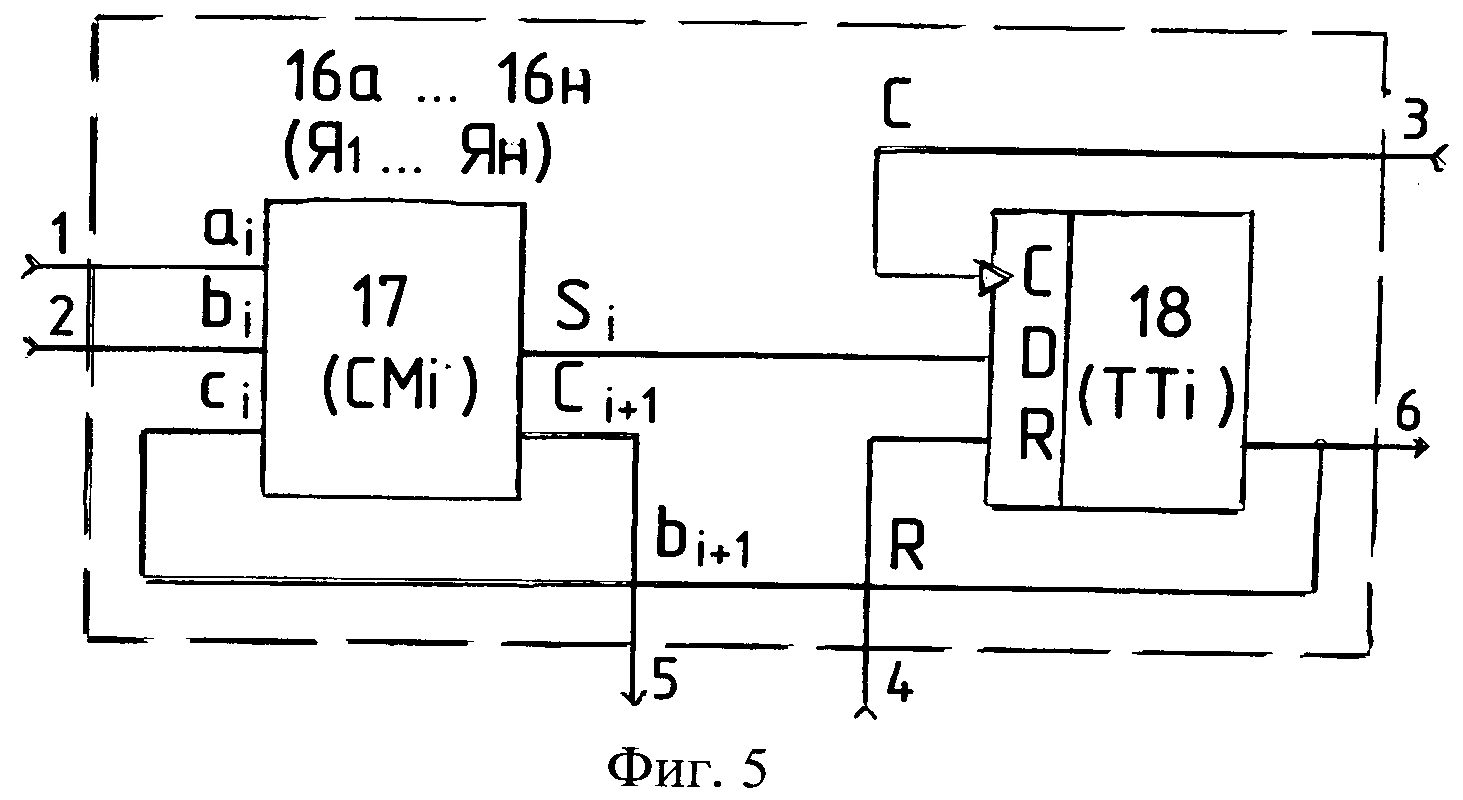

На фиг.4 и 5 приведены структурная и принципиальная электрические схемы соответственно цифрового интегратора для формирования сигнала величины угла крена на вращающейся по крену ракете и его ячеек, где представлены: 16а, 16б, …16n - первая, вторая, … n-ая цифровые ячейки (разряды) интегратора соответственно (Я1, Я2, …Яn); 17 - двухвходовый сумматор (CMi) и 18 - D-триггер (TTi), входящие в каждую цифровую ячейку, где i=1, 2, …n; (в данном случае n=4).

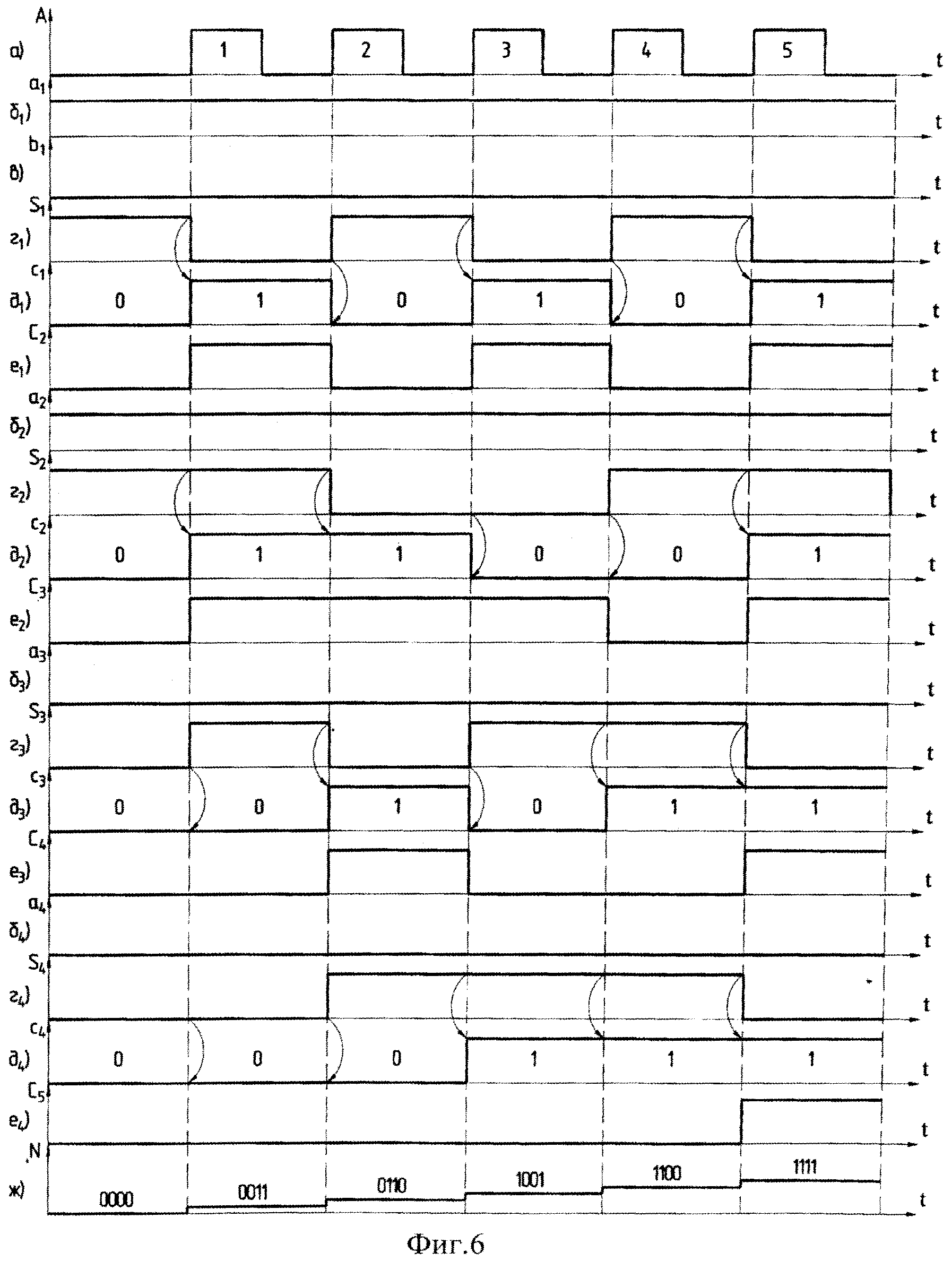

На фиг.6 приведены эпюры сигналов, в качестве примера для входного четырехразрядного двоичного параллельного числа 0011 (в десятичном виде 21+20=3), где представлены: эпюра "а" - сигнал на третьих входах цифровых ячеек 16, т.е. на тактовых входах (С) D-триггеров 18 из ячеек 16а, …16n (при n=); эпюры "б1", "б2", "б3" и "б4" - сигналы на первых входах соответственно первого а1, второго а2, третьего а3 и четвертого а4 сумматоров 17а, 17б, 17г и 17д, т.е. от младшего (первого) до старшего (четвертого) разрядов; эпюра "в" - сигнал на втором входе b1 сумматора 17а из первой цифровой ячейки 16а; эпюры "г1", "г2", "г3" и "г4" - сигналы суммы на выходах первого S1, второго S2, третьего S3 и четвертого S4 сумматоров соответственно 18а, 18б, 18г и 18д; эпюры "д1", "д2", "д3" и "д4" - сигналы переноса на входах первого с1, второго с2, третьего с3 и четвертого с4 сумматоров соответственно 17а, 17б, 17г и 17д; эпюры e1", "е2", "е3" и "е4" - сигналы на выходах переноса первого С2, второго С3, третьего С4 и четвертого С5 сумматоров соответственно 17а, 17б, 17г и 17д; эпюра "ж" - сигнал на выходах соответственно первого 18а, второго 18б, третьего 18в и четвертого 18г D-триггеров (выходы 6 цифровых ячеек 16), формирующий четырехразрядное двоичное число;

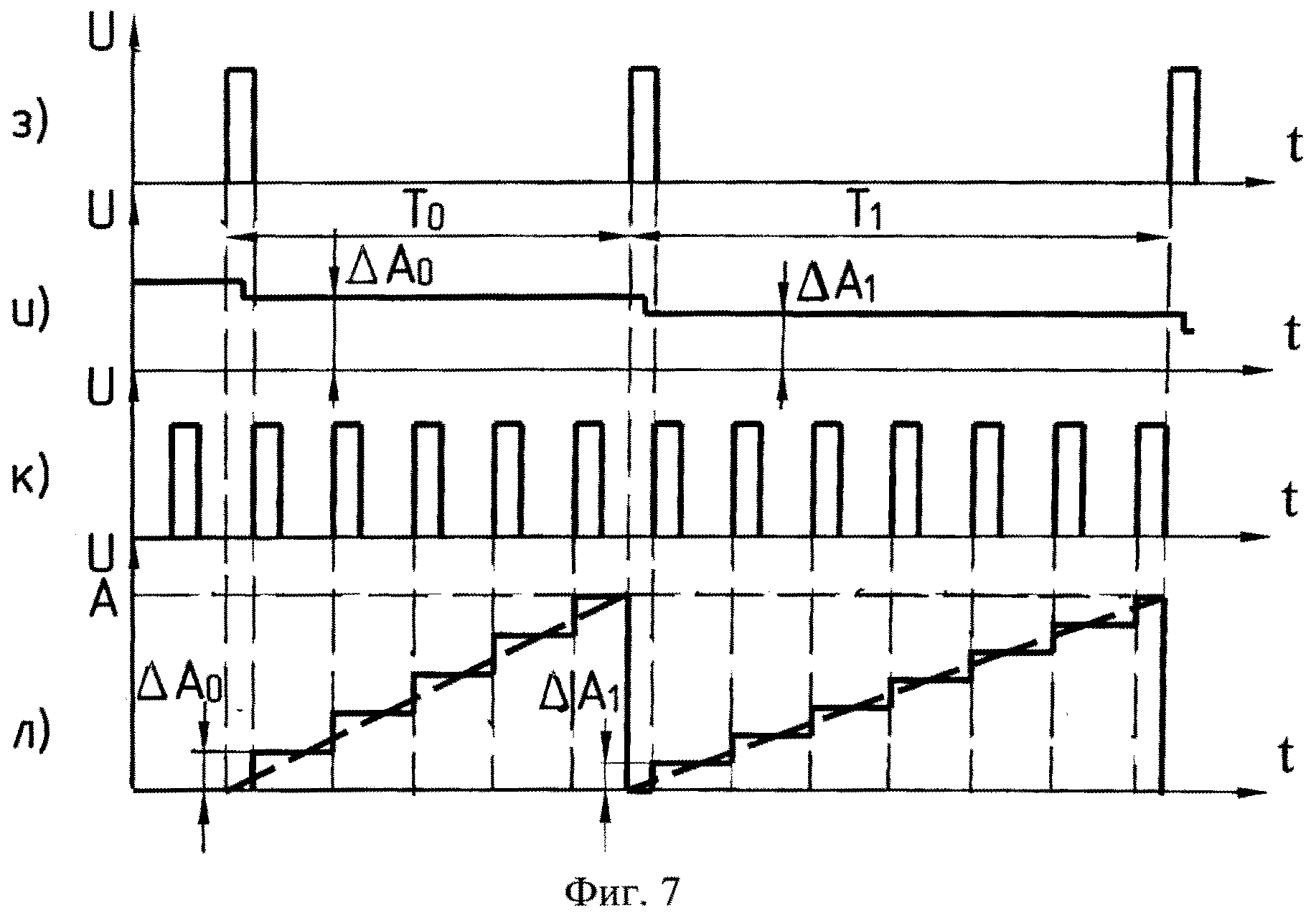

На фиг.7 приведены эпюры сигналов при изменении угловой скорости вращения ракеты, где представлены: "з" - сигнал на входе обнуления (вход R) цифрового интегратора 11, "и" - сигнал на информационном входе (входы ai сумматоров) цифрового интегратора 11, "к" - сигнал на тактовом входе (вход С) цифрового интегратора 11, "л" - линеаризированный сигнал на выходе цифрового интегратора 11.

В лиинеаризаторе сигнала (фиг.1) первый (выход 1) и второй (выход 2) выходы датчика крена 1 соединены с соответствующими входами формирователя кренового сигнала 2, последовательно соединенного с формирователем ступенчатого сигнала 3, второй выход которого (выход 2) соединен с первым информационным входом (вход 1) вычислителя 12. Интегратор 11 выполнен цифровым, вход обнуления (вход R) которого соединен с управляющим инвертируемым выходом "RS"-триггера 4, который является первым выходом (выход 1) формирователя ступенчатого сигнала. В линеаризатор сигнала введен формирователь тактовых импульсов 9, выход которого соединен с тактовым входом (вход C) интегратора, а вход его соединен с выходом синхронизатора 7, который является третьим выходом (выход 3) формирователя ступенчатого сигнала, регистр 13 и вычислитель 12. При этом информационный вход регистра соединен со вторым выходом формирователя ступенчатого сигнала, а информационный выход регистра соединен со вторым информационным (вход 2) входом вычислителя 12, информационный выход которого соединен с информационным входом цифрового интегратора. Четвертый выход (выход 4) формирователя ступенчатого сигнала соединен с входом записи регистра 13. При этом четвертый выход формирователя ступенчатого сигнала - это выход первого 6а формирователя импульсов, вход которого соединен с выходом формирователя кренового сигнала 2.

В переключаемом линеаризаторе сигнала (фиг.2) первый и второй выходы датчика крена 1 соединены с соответствующими входами формирователя кренового сигнала 2, последовательно соединенного с формирователем ступенчатого сигнала 3. Интегратор 11 выполнен цифровым, вход обнуления которого (вход R) соединен с инвертируемым выходом "RS"-триггера 4, который является управляющим первым выходом (выход 1) формирователя ступенчатого сигнала. В переключаемый линеаризатор сигнала введены: формирователь тактовых импульсов 9, два вычислителя первый 12а и второй 12б, коммутатор 15, регистр 13 и блок управления 14. При этом второй выход (выход 2) формирователя ступенчатого сигнала соединен с информационным входом вычислителя 12а, с первым информационным входом (вход 1) второго вычислителя 12б и с информационным входом регистра 13.

Третий выход (выход 3) формирователя ступенчатого сигнала - это выход синхронизатора 7, соединен с входом формирователя тактовых импульсов 9, выход которого соединен с тактовым входом (вход С) цифрового интегратора. Четвертый выход (выход 4) формирователя ступенчатого сигнала соединен с входом записи регистра, информационный выход которого соединен со вторым информационным входом (вход 2) второго вычислителя. Информационный выход вычислителя соединен со вторым информационным входом (вход 2) коммутатора 15, первый информационный вход (вход 1) которого соединен с информационным выходом первого вычислителя. Информационный выход коммутатора соединен с информационным входом цифрового интегратора. Управляющий вход коммутатора соединен с выходом блока управления 14, вход которого соединен с первым выходом датчика крена 1. Четвертый выход формирователя ступенчатого сигнала - это выход первого 6а формирователя импульсов (не показано), вход которого соединен с выходом формирователя кренового сигнала 2.

Формирователь ступенчатого сигнала выполнен в виде синхронизатора 7, регистра формирователя 10, логической схемы "И" 5, счетчика импульсов 8, последовательно включенных первого 6а, второго 6б и третьего 6в формирователей импульсов и "RS"-триггера 4, инвертируемый выход которого и выход регистра формирователя 10 являются соответственно первым (выход 1) и вторым (выход 2) выходами формирователя ступенчатого сигнала 3. Выход синхронизатора 7 и первый вход логической схемы "И" 5 являются третьим выходом (выход 3) формирователя ступенчатого сигнала, четвертым выходом (выход 4) которого является первый вход "RS"-триггера и первый выход первого формирователя импульсов.

Датчик крена 1 может быть выполнен как позиционный гироскоп ("Основы радиоуправления" под ред. Вейцеля В.А. и Типугина В.Н., Москва, Советское радио, 1973 г., стр.49-52, рис.1.29), при этом оси XГ и YГ меняют местами, а вместо механического потенциометра с токосъемником применяют оптоэлектронный с двумя парами светодиод-фотодиод, разделяемыми непрозрачной цилиндрической поверхностью с прорезями, причем центр цилиндра, образующего эту поверхность, соединен с осью рамки, а две пары светодиод-фотодиод закреплены на корпусе гироскопа.

В формирователе кренового сигнала 2, представляющем собой логическую схему «исключающее ИЛИ» и логической схеме "И" 5 можно применить, например, микросхемы соответственно 564ЛА7 и 564ТМ2. "RS"-триггер 4, например, последовательно соединенные "RS"-триггер и инвертор.

Формирователи импульсов 6а, 6б и 6в - это ждущие мультивибраторы, при этом первый из них срабатывает по фронтам нарастания и спада входного импульсного сигнала, а второй и третий - по фронтам спада.

Синхронизатор 7 может быть выполнен как, например, кварцованный автогенератор импульсов. Счетчик импульсов 8, регистры 10 и 13 могут быть выполнены на микросхемах соответственно 564ИЕ10 и 564ИР6. Вычислитель 12, а также вычислители 12а и 12б могут быть выполнены на ПЗУ, например, на микросхеме 556РТ7. Формирователь тактовых импульсов 9 представляет собой цифровой делитель частоты.

Блок управления 14 выполнен как "RS"-триггер, вход "S" которого соединен с выходом устройства, формирующего разовый импульс в момент выхода бортового источника питания (не показано) на рабочий режим. На R-входе блока управления, соединенном с первым выходом датчика крена 1, сигнал которого приведен на эпюре "а" фиг.3, формируются импульсы из фронта нарастания этого сигнала. Таким образом, на выходе блока управления формируется импульс, который возникает до начала вращения ракеты по углу крена, т.е. соответственно ωt=0°, а заканчивается в момент времени, соответствующий ωt=180°.

Коммутатор 15 может быть выполнен как два одинаковых электронных ключа. Импульсный сигнал с выхода блока управления 14 поступает непосредственно на управляющий вход первого и через инвертор - второго электронных ключей.

Сумматор 17 - это двухвходовый сумматор, где 1 и 2 - входы суммирования соответственно первого ai и второго bi числа (одного разряда), ci - вход переноса, Ci+1 - выход переноса, Si - сумма. D-триггер 18, например, микросхема 564ТМ2.

Линеаризатор сигнала, приведенный на фиг.1, работает следующим образом. При вращении ракеты по углу крена датчик крена 1 формирует два сигнала, сдвинутые по фазе относительно друг друга на 90° (эпюры "а" и "б" на фиг.3). Эти два сигнала поступают соответственно на первый и второй входы формирователя кренового сигнала 2, на выходе которого формируется сигнал (эпюры "в" на фиг.3). При поступлении этого импульсного сигнала на вход формирователя ступенчатого сигнала 3, а именно: на вход последовательно включенных формирователей импульсов 6а, 6б и 6в на их выходах сформируются импульсы, задержанные во времени относительно друг друга, соответственно эпюры "г", "д" и "е" (фиг.3).

В момент времени, например t-1 импульс с выхода первого формирователя импульсов 6а (эпюра "г" фиг.3) поступает на первый (вход 1) "RS"-триггера 4 и устанавливает на его инвертированном выходе (выход 2) единичный логический уровень (фиг.1). Данный выход является управляющим выходом (выход 1) формирователя ступенчатого сигнала 3, с которого единичный логический уровень поступает на вход обнуления (вход R) цифрового интегратора 11 и устанавливает на его выходе нулевое значение.

На не инвертированном выходе (выход 1) "RS"-триггера 4 устанавливается нулевой логический уровень (эпюра "ж" на фиг.3). Этот уровень поступает на второй (вход 2) вход логической схемы "И" 5 и запрещает прохождение сигнала с синхронизатора 7 (поступающего на ее первый вход 1) на выход логической схемы И 5. При этом импульсы перестают поступать на счетный вход (вход С) счетчика импульсов 8 и он из режима счета количества импульсов переходит в режим хранения этого посчитанного количества импульсов (двоичного числа), соответствующего величине временного интервала T-1.

Одновременно этот же импульс в момент времени t-1 с выхода записи (выход 4) формирователя ступенчатого сигнала 3 поступает на вход записи регистра 13 и записывает в него информацию (в двоичном параллельном коде), с информационного второго выхода (выхода 2) формирователя ступенчатого сигнала 3, т.е. с выхода регистра формирователя 10 (эпюра "и" на фиг.3), соответствующую величине интервала T-2, которая ранее была записана в регистр формирователя 10 импульсом t-2 (эпюра "д" на фиг.3). В момент времени  импульс, с выхода второго формирователя импульсов 6б (эпюра "д" на фиг.3) поступает на вход записи регистра формирователя 10 и записывает в него величину числа, соответствующего величине T-1 (эпюра "з" на фиг.3) с выхода счетчика импульсов 8.

импульс, с выхода второго формирователя импульсов 6б (эпюра "д" на фиг.3) поступает на вход записи регистра формирователя 10 и записывает в него величину числа, соответствующего величине T-1 (эпюра "з" на фиг.3) с выхода счетчика импульсов 8.

В момент времени  импульс с выхода третьего формирователя импульсов 6в (эпюра "е" на фиг.3) поступает на вход установки в нулевое состояние (вход R) счетчика импульсов 8 и устанавливает на его выходе логические нули.

импульс с выхода третьего формирователя импульсов 6в (эпюра "е" на фиг.3) поступает на вход установки в нулевое состояние (вход R) счетчика импульсов 8 и устанавливает на его выходе логические нули.

Аналогично этот же импульс (эпюра "е" на фиг.3) поступает на вход (вход 2) "RS"-триггера 4 и устанавливает на его не инвертированном (выход 1) выходе - логическую единицу, которая разрешает прохождение через первый вход логической схемы И 5 на ее выход импульсов с синхронизатора 7 на счетный вход (вход С) счетчика импульсов 8.

Числа в двоичном параллельном коде с информационного выхода (выход 2) формирователя ступенчатого сигнала 3 (регистра формирователя 10) и выхода регистра 13 поступают, соответственно, на первый (вход 1) и второй (вход 2) информационные входы вычислителя 12, который производит вычисление (например, при A0=1).

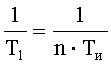

где Tи - период повторения импульсов на выходе синхронизатора 7, n - число этих импульсов в интервале T0.

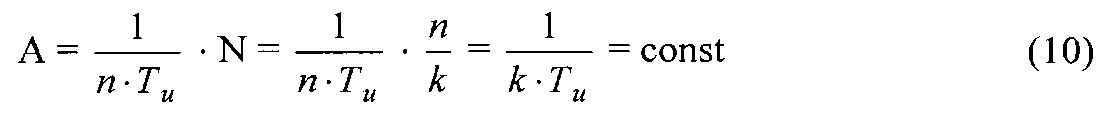

Это двоичное число  (эпюра "к" на фиг.3 в аналоговом виде) поступает на информационный вход цифрового интегратора 11. На тактируемый вход (вход С) цифрового интегратора подают тактовые импульсы с выхода формирователя тактовых импульсов 9, который уменьшает (делит) частоту повторения импульсов с выхода синхронизатора 7 формирователя ступенчатого сигнала (выход 3) в k раз, т.е. увеличивает их период повторения. Следовательно, за время интегрирования изменяемое от 0 до t0 равное интервалу T0, число тактовых импульсов (число дискретов) N в линеаризированном сигнале на выходе цифрового интегратора 11 будет равно

(эпюра "к" на фиг.3 в аналоговом виде) поступает на информационный вход цифрового интегратора 11. На тактируемый вход (вход С) цифрового интегратора подают тактовые импульсы с выхода формирователя тактовых импульсов 9, который уменьшает (делит) частоту повторения импульсов с выхода синхронизатора 7 формирователя ступенчатого сигнала (выход 3) в k раз, т.е. увеличивает их период повторения. Следовательно, за время интегрирования изменяемое от 0 до t0 равное интервалу T0, число тактовых импульсов (число дискретов) N в линеаризированном сигнале на выходе цифрового интегратора 11 будет равно

Таким образом, поскольку k=const, а n прямо пропорциональна длительности T0, то число дискретов N также прямо пропорционально длительности T0, при этом амплитуда линеаризированного сигнала A (эпюра "л" на фиг.3) равна

т.е. амплитуда линеаризированного сигнала A не зависит от длительности интервала T0.

Для исключения формирования ложного сигнала на выходе цифрового интегратора 11, в интервале формирования исходных данных для вычисления  , импульсом (с единичным логическим уровнем) с инвертированного (выход 2) выхода "RS"-триггера 4 (инвертированная эпюра "ж" на фиг.3), поступающим на вход обнуления цифрового интегратора 11, обнуляют его в течении

, импульсом (с единичным логическим уровнем) с инвертированного (выход 2) выхода "RS"-триггера 4 (инвертированная эпюра "ж" на фиг.3), поступающим на вход обнуления цифрового интегратора 11, обнуляют его в течении  (эпюра "л" на фиг.3, где приведена аналоговая форма сигнала).

(эпюра "л" на фиг.3, где приведена аналоговая форма сигнала).

Как следует из изложенного выше, задержки, вносимые вторым 6б и третьим 6в формирователями импульсов, изображенные соответственно на эпюрах "д" и "е" на фиг.3 в действительности чрезвычайно малы. А следовательно, мала длительность импульсов с нулевым логическим уровнем (эпюра "ж" на фиг.3).

После чего процесс интегрирования повторяется вновь. При этом аналогично, с момента времени t0 во второй регистр 13 запишут информацию о величине длительности T-1, а в регистр формирователь 10-T0 и вычислитель 12 вычислит величину  . По этой величине дискретно в течение времени 0-t1=T1 цифровой интегратор 11 вновь построит линеаризированный сигнал с амплитудой A и т.д.

. По этой величине дискретно в течение времени 0-t1=T1 цифровой интегратор 11 вновь построит линеаризированный сигнал с амплитудой A и т.д.

Как следует из изложенного выше в первоначальный момент времени, например от 0° до 180° (эпюра "и" на фиг.3) отсутствует информация о величинах длительностей предыдущих креновых импульсов на входе (входах) вычислителя 12, а значит и линеаризированный сигнал, что изображено пунктиром (на эпюрах "з", "и", "к" и "л" фиг.3). Поэтому для исключении ошибки при формировании широтно-импульсно модулированных команд на ракете, вращающейся по углу крена, на этот период времени, например, вводят задержку на раскрытие рулей или их блокировку в среднем положении (если допустима задержка начала управления) и т.д.

Переключаемый линеаризатор сигнала, приведенный на фиг.2 (исключающий задержку), работает аналогично приведенному на фиг.1 с момента времени, соответствующего ω·t=180°.

В этот момент времени блок управления 14 подключает через аналоговый коммутатор 15 к информационному входу цифрового интегратора 11 второй вычислитель 12б. А до этого момента времени работает аналогично приведенному на фиг.1, при отсутствии регистра 13, т.е. только по одному предыдущему значению величины интервала Ti-1. При этом используется только первый вычислитель 12а, сигнал с которого поступает через первый информационный вход (вход 1) аналогового коммутатора 15 на информационный вход цифрового интегратора 11.

Заявленный способ интегрирования для формирования линеаризированного сигнала на ракете реализуется следующим образом. В исходном состоянии на выходе цифрового интегратора устанавливают нулевой логический уровень, т.е. выходное параллельное двоичное число равно нулю. Кроме того, формируют тактовые импульсы.

На информационный вход цифрового интегратора 11 осуществляют ввод входного к-разрядного двоичного параллельного числа, например,  (эпюра "к" на фиг.3 в аналоговом виде). Для этого на первые входы ai, соответствующих двухвходовых сумматоров цифрового интегратора подают значения каждого разряда (логические уровни единица или ноль) входного к-разрядного двоичного параллельного числа. Эти значения суммируют поразрядно в каждом последующем сумматоре по вторым входам bi+1 с величинами разрядов двоичного параллельного числа с выходов переноса Ci+1 из каждого предыдущего сумматора. Например, на первый ai, вход второго (i=2) сумматора поступает второй (старший) разряд входного двоичного параллельного числа, который суммируют (по второму входу bi+1) со значением разряда переноса с выхода первого Ci+1 (i=1) сумматора, т.е. сумматора, на первый вход которого поступает младший (первый) разряд ai входного двоичного параллельного числа.

(эпюра "к" на фиг.3 в аналоговом виде). Для этого на первые входы ai, соответствующих двухвходовых сумматоров цифрового интегратора подают значения каждого разряда (логические уровни единица или ноль) входного к-разрядного двоичного параллельного числа. Эти значения суммируют поразрядно в каждом последующем сумматоре по вторым входам bi+1 с величинами разрядов двоичного параллельного числа с выходов переноса Ci+1 из каждого предыдущего сумматора. Например, на первый ai, вход второго (i=2) сумматора поступает второй (старший) разряд входного двоичного параллельного числа, который суммируют (по второму входу bi+1) со значением разряда переноса с выхода первого Ci+1 (i=1) сумматора, т.е. сумматора, на первый вход которого поступает младший (первый) разряд ai входного двоичного параллельного числа.

При этом каждый i-ый D-триггер запоминает значение разряда (логический уровень) Si суммарного параллельного двоичного числа с выхода каждого i-го двухвходового сумматора в моменты формирования фронтов нарастания тактовых импульсов. После прохождения каждого фронта нарастания тактовых импульсов запомненные значения каждого разряда двоичного параллельного числа дополнительно суммируют по входам переноса ci, с соответствующими разрядами из предыдущего суммарного параллельного двоичного числа.

Выставляют длительность интервала интегрирования соответствующую длительности углового интервала, равного 90° (в каждой четверти кренового периода), по окончанию которого устанавливают на выходе интегратора нулевой логический уровень, а затем повторяют вновь процесс интегрирования. При этом с каждым циклом суммирования увеличивают на постоянную дискретную величину текущее значение выходного двоичного параллельного числа, разряды которого формируют на выходе интегратора. Количество дискретных величин ограничивают заданной величиной, соответствующей длительности углового интервала 90°, меняют дискретную величину перед началом процесса интегрирования, при котором обновляют входное к-разрядное двоичное параллельное число.

Причем второй вход b1_младшего (первого) разряда (i=1) первого двухвходового сумматора (первой ячейки) соединяют с корпусом, поскольку он является незадействованным из-за отсутствия предыдущего двухвходового сумматора. Первые входы  ,, являющимися входами сумматоров, формирующих разряды входного двоичного параллельного большего к-того, соединяют с корпусом, поскольку они являются незадействованными из-за отсутствия данных разрядов во входном к-разрядном двоичном параллельном числе.

,, являющимися входами сумматоров, формирующих разряды входного двоичного параллельного большего к-того, соединяют с корпусом, поскольку они являются незадействованными из-за отсутствия данных разрядов во входном к-разрядном двоичном параллельном числе.

Цифровой интегратор 11 (фиг.4), реализующий заявленный способ интегрирования для формирования линеаризированного сигнала на ракете, содержит "n" последовательно соединенных цифровых одноразрядных ячеек 16а, 16б, …16n, в каждую из которых входит D-триггер 18 и двухвходовый сумматор 17. Входы установки в нуль (входы R) D-триггеров из всех цифровых одноразрядных ячеек 16а…16н соединены вместе и являются входом установки в исходное состояние интегратора. Входы тактовых импульсов (входы С) D-триггерах из всех одноразрядных ячеек соединены вместе и являются тактовым входом интегратора.

В каждой из цифровой одноразрядной ячейке (фиг.5) выход суммы Si сумматора 17 соединен с информационным входом (вход D) D-триггера 18, выход которого соединен с входом переноса ci сумматора 17. Выход переноса Ci+1 сумматора 17 из каждой предыдущей цифровой одноразрядной ячейки 16а, 16б, …16n соединен со вторым входом bi+1 сумматора 17 из каждой последующей цифровой одноразрядной ячейки.

Второй вход b1 сумматора из первой цифровой одноразрядной ячейки 16а и первые незадействованные входы сумматоров из последних цифровых одноразрядных ячеек 16к1, …16n соединены с корпусом.

Цифровой интегратор 11 для формирования сигнала величины угла крена на вращающейся по крену ракете, приведенный на фиг.4, работает следующим образом.

Информация о величине угла крена ракеты, представленная в виде двоичного параллельного числа поступает на первые входы соответствующих цифровых ячеек 16а, 16б, …16к, т.е. на первые входы ai сумматоров соответственно 17а, 17б, …17к.

Причем младший разряд двоичного параллельного числа поступает на первый вход первой цифровой ячейки 16а, следующий за ним второй разряд поступает на первый вход второй одноразрядной цифровой ячейки 16б и т.д. вплоть до старшего к-разряда, который поступает на первый вход цифровой одноразрядной ячейки 16к.

При этом, например, в случае наличия последующих цифровых одноразрядных ячеек 16к1, …16n (незадействованных по этому входу) их первые входы соединяют с корпусом. Следует отметить, что незадействованные по первому входу цифровые ячейки старших разрядов требуются, в случае необходимости, увеличения интервала интегрирования, соответствующего увеличению диапазона (изменения величины) сигнала угла крена ракеты, что исключает ограничение линеаризированного цифрового сигнала.

На вторые входы b1 сумматоров 17б…17n поступает импульсные сигналы с выхода переноса сумматора из предыдущей цифровой одноразрядной ячейки. При этом второй вход сумматора 17 из первой цифровой одноразрядной ячейки 16а соединен с корпусом, т.к. отсутствует предыдущая ячейка, а значит и сигнал переноса с ее выхода. Третьи входы (входы тактирования C на фиг.4) всех цифровых ячеек 16 объединены вместе и на их входы подаются тактовые импульсы постоянной частоты с выхода формирователя тактовых импульсов 9 (эпюра «а» на фиг.6).

Предварительно, например, в момент выхода бортового источника питания на рабочий режим (если это требуется), а также в моменты окончания интервалов интегрирования формируют импульсы, которые поступают на четвертые входы (входы обнуления R) всех цифровых ячеек 16, объединенных вместе и устанавливают на их выходах, а именно на выходах всех D-триггеров 18 (выход 6) нулевой логический уровень.

В качестве примера входной сигнал цифрового интегратора представлен двухразрядным параллельным двоичным числом 0011 в параллельном виде (в десятичном коде 3), для которого приведены соответствующие величины логических уровней ai (эпюры «б1», «б2», «б3» и «б4» на фиг.6). При этом расположение разрядов двоичного параллельного четырехразрядного числа на фиг.4 слева направо, т.е. от младшего (MP) к старшему (CP), совпадает с принадлежностью разрядов соответственно первой 16а, второй 16б, третьей 16в и четвертой 16г цифровым одноразрядным ячейкам.

После обнуления сумматор 17а из первой ячейки 16а суммирует два сигнала по входу a1 - логическую единицу и по входу b1 - логический нуль (эпюры «б1» и «в» на фиг.6 соответственно). При этом на выходе S1 сумматора 17а формируется единичный логический уровень (эпюра «г1» на фиг.6). В момент прихода переднего фронта (нарастания) первого тактового импульса (эпюра «а» фиг.6) единичный логический уровень c выхода S1 сумматора 17а по D входу D-триггера 18а прописывается на его выход, с которого он поступает на вход переноса c1 сумматора 17а (эпюра «д1» фиг.6). На выходе S1 сумматора 17а сформируется нулевой логический уровень, т.к. S1=1+1=0 при переносе 1 на выход C2. Нулевой логический уровень c выхода S1 поступает на D вход D-триггера 18а и передним фронтом второго тактового импульса (эпюра «а» фиг.6) прописывается на его выход, c которого поступает на вход переноса c1 сумматора 17а. Далее процесс повторяется.

Таким образом, в первой цифровой ячейке 16а на выходе S1 сумматора 17а формируется сигнал, изменение логических уровней которого приведены на эпюре «г1» фиг.6. Аналогично при превышении величины S1 (суммы) больше единицы, когда на выходе S1 формируется нулевой логический уровень, на выходе переноса C2 появится единичный логический уровень (эпюра «д1» фиг.6). Как следует из этой эпюры логические уровни нуль и единица соответствуют величине двоичного числа первого (младшего разряда), определяющего величину линеаризированного сигнала.

Сигнал переноса (выход 5) первой цифровой ячейки 16а (сигнал C2 c выхода сумматора 17а) поступает на вторые вход b2 сумматора 17б из второй цифровой ячейки 16б, на первый вход а2 которого поступает второй (следующий после первого младшего разряда) разряд двоичного входного числа (эпюра «б2» на фиг.6), который представляет собой единичный логический уровень. В первоначальный момент времени на выходе S2 сумматора 17б из второй цифровой ячейки 16б формируется единичный логический уровень, т.к. суммируются нулевой и единичный логические уровни, при этом на входе переноса c2 - нулевой логический уровень.

В момент прихода переднего фронта первого тактового импульса (эпюра «а» на фиг.6) единичный логический уровень c выхода S2 сумматора 17б по D входу D-триггера 18б прописывается на его выходе и поступает на вход переноса c2 сумматора 17б. При этом сигнал переноса C2 c выхода сумматора 17а из первой цифровой ячейки 16а (эпюра «е1» на фиг.6) поступает на второй вход b2 сумматора 17б из второй цифровой ячейки 16б с небольшим запаздыванием, обусловленным временем прохождения сигнала через двухвходовый сумматор из первой цифровой ячейки. Сигнал переноса C2 изменяет свой логический уровень из нулевого в единичный на втором входе b2 сумматора (эпюра «е1» на фиг.6). Следовательно, на выходе S2 останется единичный логический уровень, а на выходе переноса C3 изменится логический уровень из нулевого в единичный из за переноса единицы (эпюра «д2» на фиг.6).

Передний фронт второго тактового импульса (эпюра «а» на фиг.6) поступает на D вход D-триггера 18б и прописывает на его выходе единичный логический уровень с выхода сумматора S2, т.е. оставляет единичный логический уровень, поступающий на вход переноса c2 сумматора 17б (эпюра «д2» на фиг.6). Сигнал переноса C2 поступает на второй вход b2 сумматора 17б (эпюра «д1» на фиг.6) аналогично с небольшим запаздыванием, при этом на выходе S2 сумматора 17б сформируется нулевой логический уровень, а на его выходе переноса C3 сохранится единичный логический уровень (эпюра «д2» на фиг.6).

Передний фронт третьего тактового импульса (эпюра «а» на фиг.6) поступает на D вход D-триггера 17б и прописывает на его выходе нулевой логический уровень c выхода S2, который поступает на вход переноса c2 сумматора 17б. При этом аналогично на второй вход b2 сумматора 17б поступает сигнал переноса C2 (эпюра «д1» на фиг.6), который изменяет логический уровень с нулевого на единичный и на выходе S2 сумматора формируется нулевой логический уровень, а на выходе переноса C3 сохранится единичный логический уровень (эпюра «д2» фиг.6).

Далее при поступлении передних фронтов четвертого и последующих тактовых импульсов (эпюра «а» на фиг.6) весь процесс для второй цифровой ячейки 16б повторяется.

Сигнал переноса (выход 5) второй цифровой ячейки 16б поступает на второй вход b3 сумматора 17в из третьей цифровой ячейки 16в. На первый вход a3 сумматора 17в поступает третий разряд двоичного входного числа (эпюра «в3» на фиг.6), который представляет собой нулевой логический уровень. В первоначальный момент времени на выходе S3 сумматора 17в из третьей цифровой ячейки 16в формируется нулевой логический уровень, т.к. суммируются два нулевых логических уровня.

В момент прихода переднего фронта первого тактового импульса (эпюра «а» на фиг.6) нулевой логический уровень с выхода S3 сумматора 17 по D входу D-триггера 18в прописывается на его выход, а затем поступает на вход переноса c3 сумматора 17в. При этом аналогично изложенному выше сигнал переноса C3 (единичный логический уровень) на втором входе b3 сумматора 17в (эпюра «д2» на фиг.6) поступит с небольшим запаздыванием. При этом на выходе S3 изменится нулевой логический уровень на единичный (эпюра «г3» на фиг.6), а на выходе переноса C4 останется нулевой логический уровень (эпюра «д3» на фиг.6).

Передний фронт второго тактового импульса (эпюра «а» на фиг.6), поступающий на D вход D-триггера 18в (эпюра «д3» на фиг.6), прописывает на его выход единичный логический уровень c выхода S3 сумматора 17в, который поступает на вход переноса c3 сумматора.

При этом единичный логический уровень в сигнале на втором входе b3 сумматора (эпюра «д2» на фиг.6) не изменится, а на выходах S3 и C4 сумматора сформируются соответственно нулевой и единичный логические уровни (эпюры «г3» и «д3» на фиг.6 соответственно).

Передний фронт третьего тактового импульса (эпюра «а» на фиг.6) поступает на D вход D-триггера 18в при этом прописывается c выхода S3 сумматора 17в на выходе D-триггера 18в нулевой логический уровень, который поступает затем на вход переноса c3 сумматора 17в. На второй вход b3 сумматора 17в поступает сигнал с выхода переноса C3 сумматора 17б, в котором изменяется логический уровень c нулевого на единичный (эпюра «д2» на фиг.6). На выходе S3 сумматора 17 сформируется единичный логический уровень, а на выходе переноса C4 - нулевой логический уровень (эпюра «д3» на фиг.6).

Аналогично передние фронты четвертого и пятого тактовых импульсов сформируют на выходе S3 и выходе переноса C4 сумматора 17в соответствующие логические уровни, приведенные на фиг.6.

Сигнал переноса C4 c выхода 5 третьей цифровой ячейки 16в поступает на второй вход b4 сумматора 17г из четвертой цифровой ячейки 16г. На первый вход a4 сумматора 17г поступает четвертый (старший) разряд двоичного входного числа (эпюра «в4» на фиг.6), который представляет собой нулевой логический уровень. В первоначальный момент времени на выходе S4 сумматора 17г из четвертой цифровой ячейки 17г формируется нулевой логический уровень (суммируются два нулевых логических уровня).

В момент прихода переднего фронта первого тактового импульса (эпюра «а» на фиг.6) нулевой логический уровень c выхода S4 сумматора 17г по D входу D-триггера 18г прописывается на его выход и поступает на вход переноса c4 сумматора 17. При этом сигнал переноса (нулевой логический уровень) на втором входе b4 сумматора 17г (эпюра «д3» на фиг.6) останется неизменным. Сигналы на выходе S4 и на выходе переноса C5 также останутся неизменными, т.е. нулевыми логическими уровнями (эпюры «г4» и «д4» на фиг.6).

В момент прихода переднего фронта второго тактового импульса (эпюра «а» на фиг.6) на входах сумматора 17г присутствуют нулевые логические уровни сигналов a4 и c4 и единичный b4, формирующие на его выходе S4 единичный логический уровень (эпюра «г4» на фиг.4). Передний фронт второго тактового импульса, поступающий на D входе D-триггера 18г, прописывает на его выход единичный логический уровень, который поступает на вход переноса c4 сумматора 17г.

При этом единичный логический уровень в сигнале на втором входе b4 сумматора 17г (эпюра «д3» на фиг.6) изменит свой логический уровень с нулевого на единичный и на выходах S4 и C5 сумматора 17г сформируются соответственно нулевой и единичный логические уровни (эпюры «г4» и «д4» на фиг.6 соответственно).

Передний фронт третьего тактового импульса (эпюра «а» на фиг.6) поступает на D входе D-триггера 18г и прописывает с выхода S4 сумматора 17г на выход D-триггера единичный логический уровень (сохраняет предыдущий), который поступает на вход переноса c4 сумматора 17г.

При этом на втором входе b4 сумматора 17г изменится логический уровень c единичного на нулевой (эпюра «д3» на фиг.6) и на выходе S4 сумматора 17г сформируется единичный логический уровень, а на выходе переноса C5 сохранится нулевой логический уровень (эпюра «д4» на фиг.6).

Передний фронт четвертого тактового импульса поступает на D вход D-триггера 18г и прописывает с выхода S4 сумматора 17г на выход D-триггера единичный логический уровень, который поступает на вход переноса c4 сумматора 17г (сохраняются предыдущие логические уровни на выходах S4 сумматора и D-триггера).

При этом на втором входе b4 сумматора 17г изменится логический уровень c нулевого на единичный (эпюра «д3» на фиг.6), а на выходах S4 и переноса C5 сумматора 17г сохранятся предыдущие единичные логические уровни (эпюры «б4» и «д4» на фиг.6 соответственно).

Передний фронт пятого тактового импульса поступает на D вход D-триггера 18г и прописывает с выхода S4 сумматора 17г на выход D-триггера единичный логический уровень, который поступает на вход переноса c4 сумматора 17г (сохраняется предыдущий логический уровень). При этом на втором входе b4 сумматора 17г сохранится единичный логический уровень (эпюра «д3» на фиг.6), причем на выходе S4 сумматора 17г изменится логический уровень из единичного в нулевой, а на выходе переноса C5 сохранится предыдущий единичный логический уровень (эпюры «б4» и «д4» на фиг.6 соответственно).

В момент прихода, например переднего фронта шестого импульса, из него формируют импульс обнуления, который поступает на R входы цифровых ячеек и устанавливает на их выходах нулевой логический уровень. После чего процесс интегрирования повторяют вновь.

Таким образом, в процессе интегрирования при изменении количества тактовых импульсов от нуля до пяти двоичное число на выходах переноса сумматоров из каждой цифровой ячейки увеличивается. При этом формируется двоичное число в параллельном виде, увеличивающееся с каждым тактовым импульсом на величину входного числа в данном случае на величину 11 в двоичном коде. Согласно фиг 6, исходное состояние интегратора - 0000, в момент прихода первого тактового импульса - 1100, второго - 0110, третьего - 1001, четвертого - 0011 ив момент прихода пятого тактируемого импульса с учетом сигнала переноса c4 в четвертой ячейке 1г - 1111.

Следовательно, максимальная величина сигнала на выходе четырехразрядного цифрового интегратора в данном случае равна 1111 (15=3·5 в десятичном коде), что соответствует эпюре «ж» на фиг.6. Как следует из изложенного выше, входной сигнал (в двоичном параллельном коде) - это два единичных логических уровня, которые поступают на вторые входы a1, a1 и a2 соответственно первой и второй цифровых одноразрядных ячеек, а входы a3 и a4, а также второй вход b1 соединены с корпусом, при этом выходной сигнал (его разряд) снимаются с шестых выходов всех четырех цифровых одноразрядных ячеек.

В ряде случаев, например, при невозможности понижения частоты тактовых импульсов, когда параллельное двоичное число имеет избыточное количество разрядов, младшие выходные разряды не используются, что приведено на фиг.4.

В общем случае как следует из изложенного выше входное к-разрядное двоичное параллельно число, например,  соответствует величине дискрета ΔA0 в интервале T0, а при уменьшении угловой скорости вращения ракеты по углу крена, т.е. при T1>T0 в следующем интервале интегрирования T1 соответствует величине дискрета ΔA1<ΔA0 (эпюра "и" на фиг.7 в аналоговом виде). При этом обнуление цифрового интегратора 11 осуществляют импульсами, приведенными на эпюре "з" фиг.7 (импульсы со второго выхода "RS"-триггера 4). Каждый фронт нарастания тактовых импульсов (эпюра "к" на фиг.7) c выхода формирователя тактовых импульсов 9 увеличивает величину интегрированного сигнала на величину дискрета соответственно ΔA0 или ΔA1 (эпюра "л" на фиг.7).

соответствует величине дискрета ΔA0 в интервале T0, а при уменьшении угловой скорости вращения ракеты по углу крена, т.е. при T1>T0 в следующем интервале интегрирования T1 соответствует величине дискрета ΔA1<ΔA0 (эпюра "и" на фиг.7 в аналоговом виде). При этом обнуление цифрового интегратора 11 осуществляют импульсами, приведенными на эпюре "з" фиг.7 (импульсы со второго выхода "RS"-триггера 4). Каждый фронт нарастания тактовых импульсов (эпюра "к" на фиг.7) c выхода формирователя тактовых импульсов 9 увеличивает величину интегрированного сигнала на величину дискрета соответственно ΔA0 или ΔA1 (эпюра "л" на фиг.7).

Таким образом, каждый тактовый импульс (его фронт нарастания) осуществляет суммирование (на сумматорах) двоичного числа ΔA0 в параллельном коде с числом хранящимся в ячейках (D триггерах): вначале с нулем, затем с ΔA0, 2ΔA0, 3ΔA0 и т.д. до момента обнуления цифрового интегратора 11. Затем процесс повторяется вновь для ΔA1 (эпюра "л" на фиг.7) и т.д. Как следует из изложенного, величина дискрета ΔAi обратно пропорциональна величине Ti, а число дискретов - прямо пропорционально Ti. При этом минимальное количество дискретов соответствует максимальной скорости полета ракеты. Это следует учитывать для исключения уменьшения точности, обусловленной уменьшением количества дискретов в линеаризированном сигнале, что устраняется соответственным увеличением частоты тактируемого сигнала, а значит и количеством ячеек.

В описании с целью упрощения и облегчения понимания работы заявленного технического решения некоторые эпюры сигналов приведены в аналоговом виде.

Следовательно, предлагаемая группа изобретений способ формирования линеаризированного сигнала на вращающейся по углу крена ракете, линеаризатор сигнала, переключаемый линеаризатор сигнала, способ интегрирования для формирования линеаризированного сигнала на ракете и цифровой интегратор для его осуществления позволяет повысить точность формирования линеаризированного сигнала на вращающейся по углу крена ракете, за счет исключения или уменьшения изменения размаха (амплитуды) линеаризированного сигнала при ускорении или замедлении полета ракеты.