Результат интеллектуальной деятельности: СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЬНОЙ СХЕМОЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Вид РИД

Изобретение

Область техники

Изобретение относится к области силовой электроники. Изобретение относится к способу управления преобразовательной схемой в соответствии с ограничительной частью независимых пунктов формулы.

Уровень техники

Преобразовательные схемы используются сегодня во множестве областей. Особенно просто шкалируемая по напряжению преобразовательная схема описана в WO 2007/023064 А1. Такая преобразовательная схема из уровня техники изображена на фиг.1, причем для наглядности показан только один ее фазный модуль. Здесь преобразовательная схема содержит на каждую фазу один фазный модуль, причем каждый фазный модуль содержит первую и вторую частичные преобразовательные системы, последовательно соединенные между собой. Точка соединения обеих последовательно включенных частичных преобразовательных систем образует выход, например для электрической нагрузки. Каждая частичная преобразовательная система содержит, по меньшей мере, одну двухполюсную коммутационную ячейку, причем в случае нескольких коммутационных ячеек частичной преобразовательной системы они последовательно соединены между собой. Каждая двухполюсная коммутационная ячейка содержит управляемые двунаправленные силовые полупроводниковые выключатели с управляемым однонаправленным прохождением тока и емкостный накопитель энергии. На фиг.1 каждая коммутационная ячейка содержит два включенных последовательно управляемых двунаправленных силовых полупроводниковых выключателя с управляемым однонаправленным прохождением тока и емкостной накопитель энергии, включенный параллельно сериесной схеме из двух силовых полупроводниковых выключателей. Преобразовательная схема общего вида описана также в WO 2007/33852 А2.

Поскольку преобразовательная схема в WO 2007/023064 А1 или WO 2007/33852 А2 содержит слабо демпфированные колебательные контуры, состоящие из двух или более фазных модулей, возникающие в них колебания тока должны демпфироваться с помощью регулирования посредством первой и второй частичных преобразовательных систем. Для этого в WO 2007/33852 А2 описан способ управления, который основан на принципе произвольно выбираемых отрезков времени для операций коммутации управляемых двунаправленных силовых полупроводниковых выключателей в коммутационных ячейках первой и второй частичных преобразовательных систем следует.

Раскрытие изобретения

Задачей изобретения является создание усовершенствованного и альтернативного уровню техники способа управления преобразовательной схемой, посредством которого можно активно демпфировать нежелательные колебания и искажения в токах первых и вторых частичных преобразовательных систем.

Эта задача решается посредством признаков пп.1, 4 и 7 формулы. В зависимых пунктах приведены предпочтительные варианты осуществления изобретения.

Преобразовательная схема содержит по меньшей мере два фазных модуля, причем каждый фазный модуль включает в себя первую и вторую частичные преобразовательные системы, и для каждого фазного модуля частичные преобразовательные системы последовательно соединены между собой. Каждая частичная преобразовательная система включает в себя несколько последовательно включенных двухполюсных коммутационных ячеек, и каждая коммутационная ячейка содержит управляемые двунаправленные силовые полупроводниковые выключатели с управляемым однонаправленным направлением прохождения тока и емкостный накопитель энергии. Предложенным способом управление силовыми полупроводниковыми выключателями коммутационных ячеек первой частичной преобразовательной системы происходит посредством управляющего сигнала, а управление силовыми полупроводниковыми выключателями коммутационных ячеек второй частичной преобразовательной системы - посредством другого управляющего сигнала. Для первой частичной преобразовательной системы управляющий сигнал формируется из опорного сигнала в отношении напряжения на первой частичной преобразовательной системе, а для второй частичной преобразовательной системы другой управляющий сигнал формируется из опорного сигнала в отношении напряжения на второй частичной преобразовательной системе. Согласно изобретению, управляющий сигнал формируется дополнительно из демпфирующего сигнала в отношении первой частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через первую частичную преобразовательную систему и задаваемого значения сопротивления. Кроме того, другой управляющий сигнал формируется дополнительно из демпфирующего сигнала в отношении второй частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через вторую частичную преобразовательную систему и задаваемого значения сопротивления.

Каждый демпфирующий сигнал соответствует по своему действию падению напряжения на омическом сопротивлении в соответствующей частичной преобразовательной системе и нужным образом демпфирует токи через соответствующую частичную преобразовательную систему.

В другом варианте осуществления изобретения демпфирующий сигнал в отношении первой частичной преобразовательной системы формируется дополнительно из задаваемого опорного тока через первую частичную преобразовательную систему. Демпфирующий сигнал в отношении второй частичной преобразовательной системы формируется дополнительно из задаваемого опорного тока через вторую частичную преобразовательную систему. Задавая опорный ток при формировании соответствующего демпфирующего сигнала, можно демпфировать определенные составляющие колебаний токов через соответствующую частичную преобразовательную систему.

В одном альтернативном варианте осуществления изобретения для первой частичной преобразовательной системы управляющий сигнал формируется из сформированного в центральном вычислительном блоке опорного сигнала в отношении соответствующей коммутационной ячейки первой частичной преобразовательной системы. Для каждой коммутационной ячейки первой частичной преобразовательной системы предусмотрен локальный вычислительный блок, причем опорный сигнал в отношении соответствующей коммутационной ячейки первой частичной преобразовательной системы передается на локальные вычислительные блоки коммутационных ячеек первой частичной преобразовательной системы. Управляющий сигнал формируется в каждом локальном вычислительном блоке коммутационных ячеек первой частичной преобразовательной системы дополнительно из демпфирующего сигнала в отношении соответствующей коммутационной ячейки первой частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через соответствующую коммутационную ячейку первой частичной преобразовательной системы и задаваемого значения сопротивления. Для второй частичной преобразовательной системы другой управляющий сигнал формируется из сформированного в центральном вычислительном блоке опорного сигнала в отношении соответствующей коммутационной ячейки второй частичной преобразовательной системы. Кроме того, для каждой коммутационной ячейки второй частичной преобразовательной системы предусмотрен локальный вычислительный блок, причем опорный сигнал в отношении соответствующей коммутационной ячейки второй частичной преобразовательной системы передается на локальные вычислительные блоки коммутационных ячеек второй частичной преобразовательной системы. Далее другой управляющий сигнал в каждом локальном вычислительном блоке коммутационных ячеек второй частичной преобразовательной системы дополнительно формируется в отношении соответствующей коммутационной ячейки второй частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через соответствующую коммутационную ячейку второй частичной преобразовательной системы и задаваемого значения сопротивления.

За счет описанной выше альтернативы демпфирование токов через частичные преобразовательные системы происходит предпочтительно в коммутационных ячейках. Каждый демпфирующий сигнал соответствует по своему действию падению напряжения на омическом сопротивлении в каждой коммутационной ячейке, причем общее действие соответствует сериесной схеме из омических сопротивлений, благодаря чему токи через соответствующие коммутационные ячейки соответствующей частичной преобразовательной системы демпфируются нужным образом. За счет локального измерения токов через коммутационные ячейки может обеспечиваться дублирование и, тем самым, готовность демпфирования даже при отказе измерения тока, например в одной коммутационной ячейке. За счет локального формирования управляющего сигнала отпадает необходимость его передачи к отдельным коммутационным ячейкам.

В другом варианте осуществления изобретения соответствующий демпфирующий сигнал в отношении соответствующей коммутационной ячейки первой частичной преобразовательной системы дополнительно формируется из задаваемого опорного тока через соответствующую коммутационную ячейку первой частичной преобразовательной системы, а соответствующий демпфирующий сигнал в отношении соответствующей коммутационной ячейки второй частичной преобразовательной системы дополнительно формируется из задаваемого опорного тока через соответствующую коммутационную ячейку второй частичной преобразовательной системы. Помимо уже упомянутых выше преимуществ, задавая опорный ток при формировании соответствующего демпфирующего сигнала, можно демпфировать определенные составляющие колебаний токов через коммутационные ячейки соответствующей частичной преобразовательной системы.

В одной альтернативе изобретения для первой частичной преобразовательной системы управляющий сигнал формируется из сформированного в центральном вычислительном блоке демпфирующего опорного сигнала в отношении напряжения на первой частичной преобразовательной системе, причем демпфирующий опорный сигнал в отношении напряжения на первой частичной преобразовательной системе формируется из задаваемого опорного тока через первую частичную преобразовательную систему, задаваемого значения сопротивления и опорного сигнала в отношении напряжения на первой частичной преобразовательной системе. Для каждой коммутационной ячейки первой частичной преобразовательной системы предусмотрен локальный вычислительный блок, причем демпфирующий опорный сигнал в отношении напряжения на первой частичной преобразовательной системе передается на локальные вычислительные блоки коммутационных ячеек первой частичной преобразовательной системы. Управляющий сигнал в каждом локальном вычислительном блоке коммутационных ячеек первой частичной преобразовательной системы дополнительно формируется из демпфирующего сигнала в отношении соответствующей коммутационной ячейки первой частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через соответствующую коммутационную ячейку первой частичной преобразовательной системы и задаваемого дополнительного значения сопротивления. К тому же для второй частичной преобразовательной системы указанный другой управляющий сигнал формируется из формированного в центральном вычислительном блоке демпфирующего опорного сигнала в отношении напряжения на второй частичной преобразовательной системе, причем демпфирующий опорный сигнал в отношении напряжения на второй частичной преобразовательной системе формируется из задаваемого опорного тока через вторую частичную преобразовательную систему, задаваемого значения сопротивления и опорного сигнала в отношении напряжения на второй частичной преобразовательной системе. Кроме того, для каждой коммутационной ячейки второй частичной преобразовательной системы предусмотрен локальный вычислительный блок, причем демпфирующий опорный сигнал в отношении напряжения на второй частичной преобразовательной системе передается на локальные вычислительные блоки коммутационных ячеек второй частичной преобразовательной системы. Кроме того, другой управляющий сигнал формируется в каждом локальном вычислительном блоке коммутационных ячеек второй частичной преобразовательной системы дополнительно из демпфирующего сигнала в отношении соответствующей коммутационной ячейки второй частичной преобразовательной системы, причем демпфирующий сигнал формируется из измеренного тока через соответствующую коммутационную ячейку второй частичной преобразовательной системы и задаваемого дополнительного значения сопротивления. Также с помощью этого варианта изобретения выборочно могут демпфироваться определенные составляющие колебаний токов через коммутационные ячейки соответствующей частичной преобразовательной системы. Кроме того, опорный ток предпочтительно не передается на локальные вычислительные блоки.

Эти и другие задачи, преимущества и признаки изобретения становятся очевидными из нижеследующего подробного описания предпочтительных вариантов его осуществления в сочетании с чертежами.

Краткое описание чертежей

На чертежах:

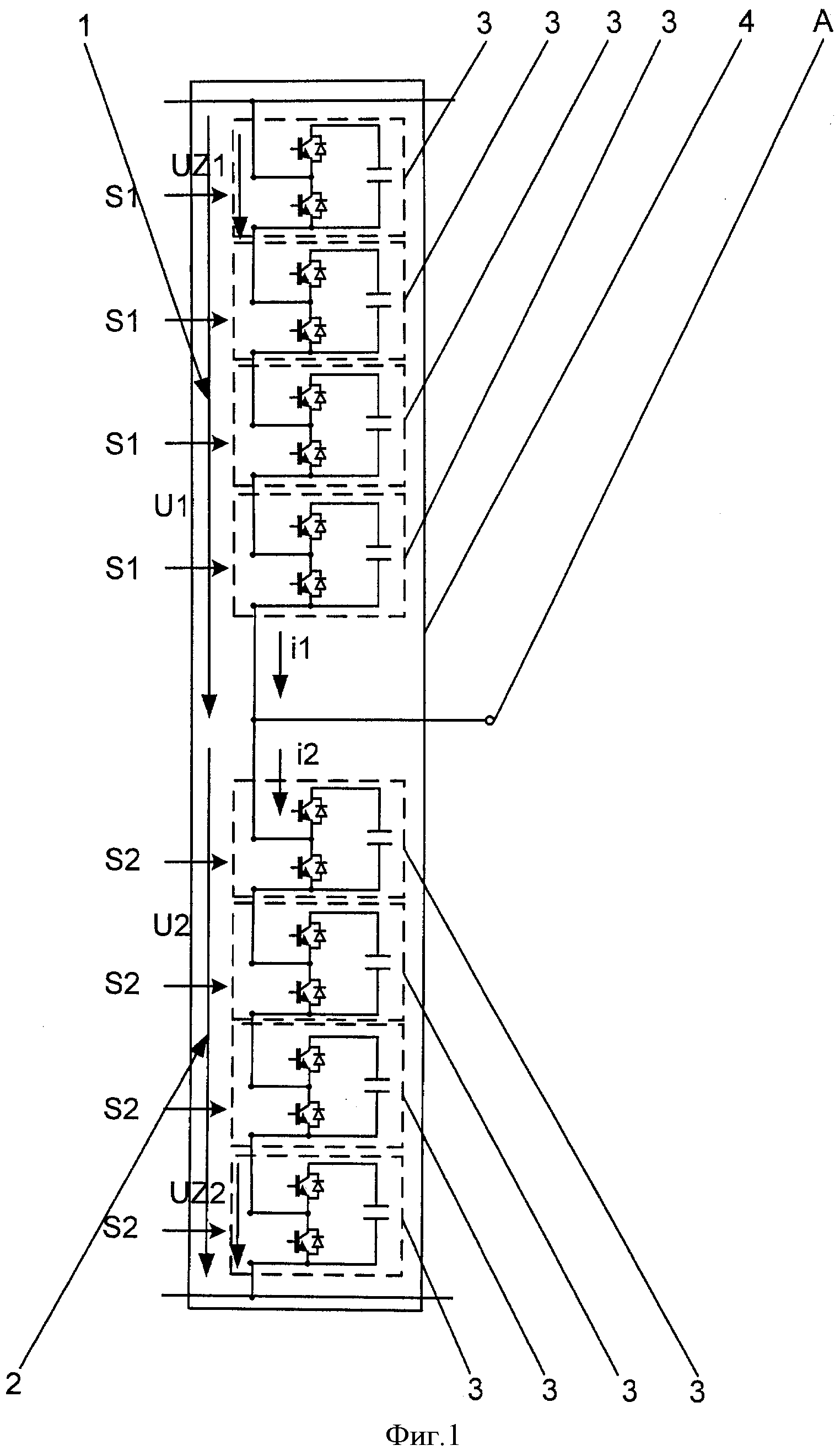

фиг.1 - вариант преобразовательной схемы из уровня техники;

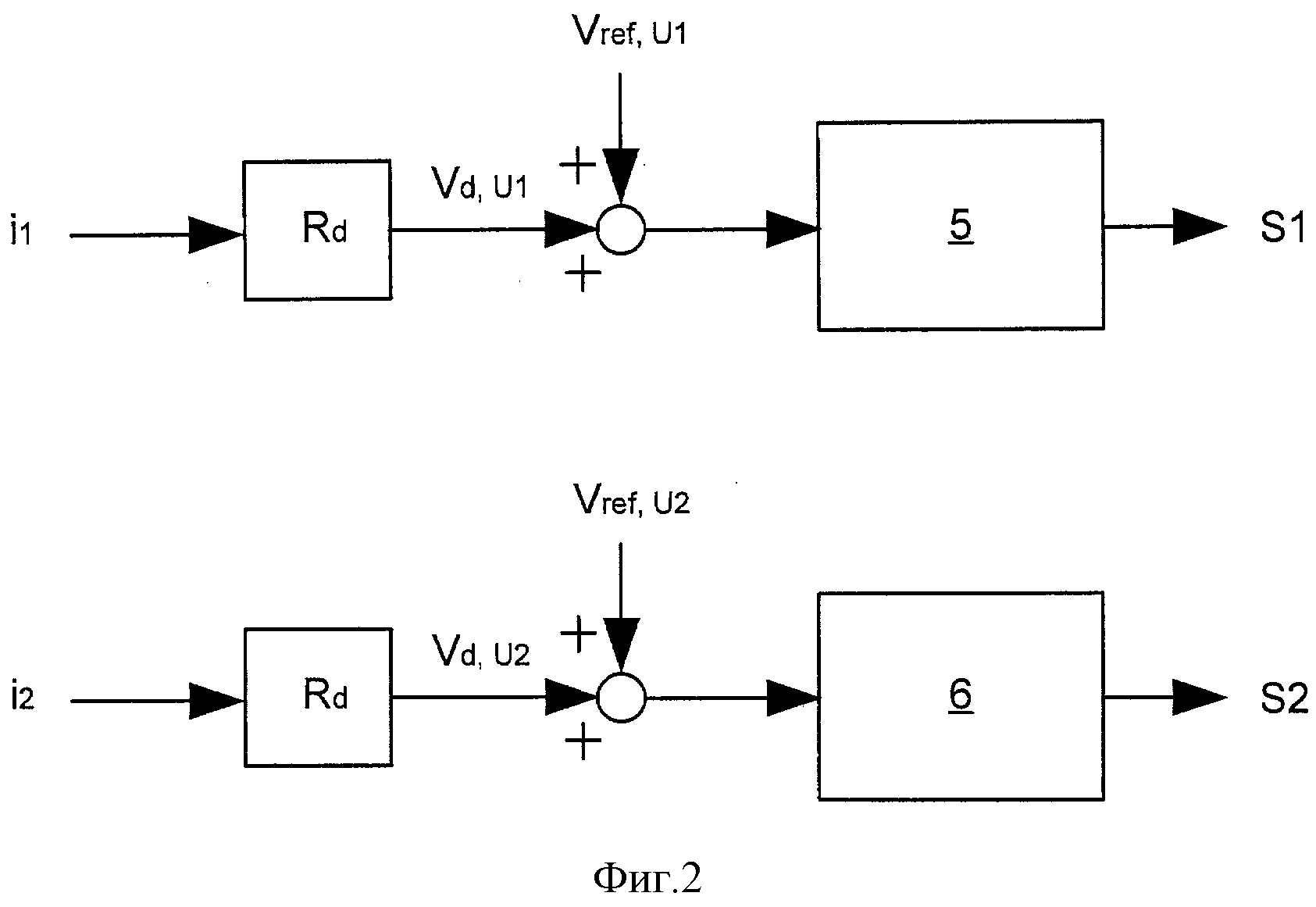

фиг.2 - первый вариант устройства для осуществления способа управления преобразовательной схемой;

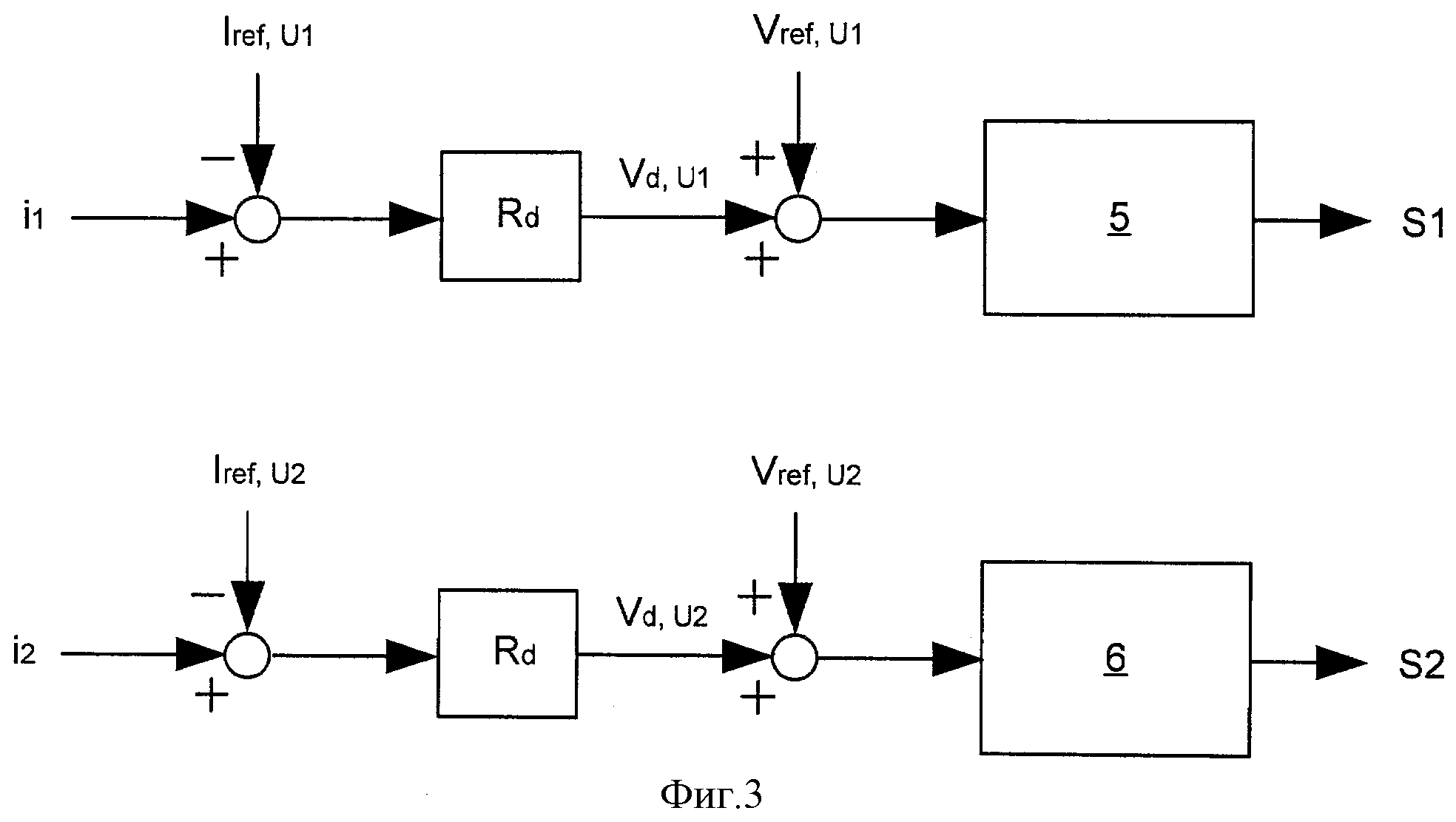

фиг.3 - второй вариант устройства для осуществления способа управления преобразовательной схемой;

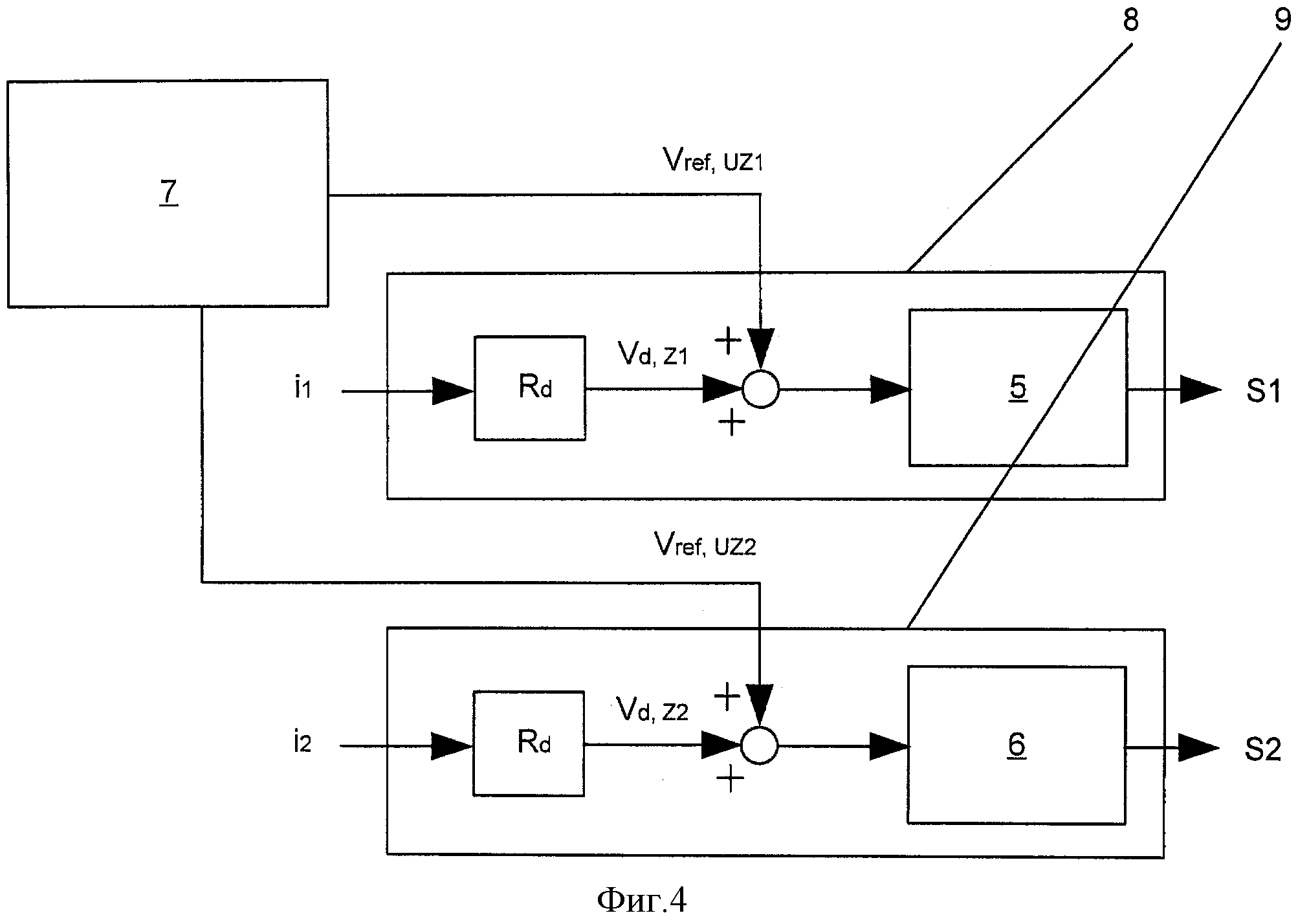

фиг.4 - третий вариант устройства для осуществления способа управления преобразовательной схемой;

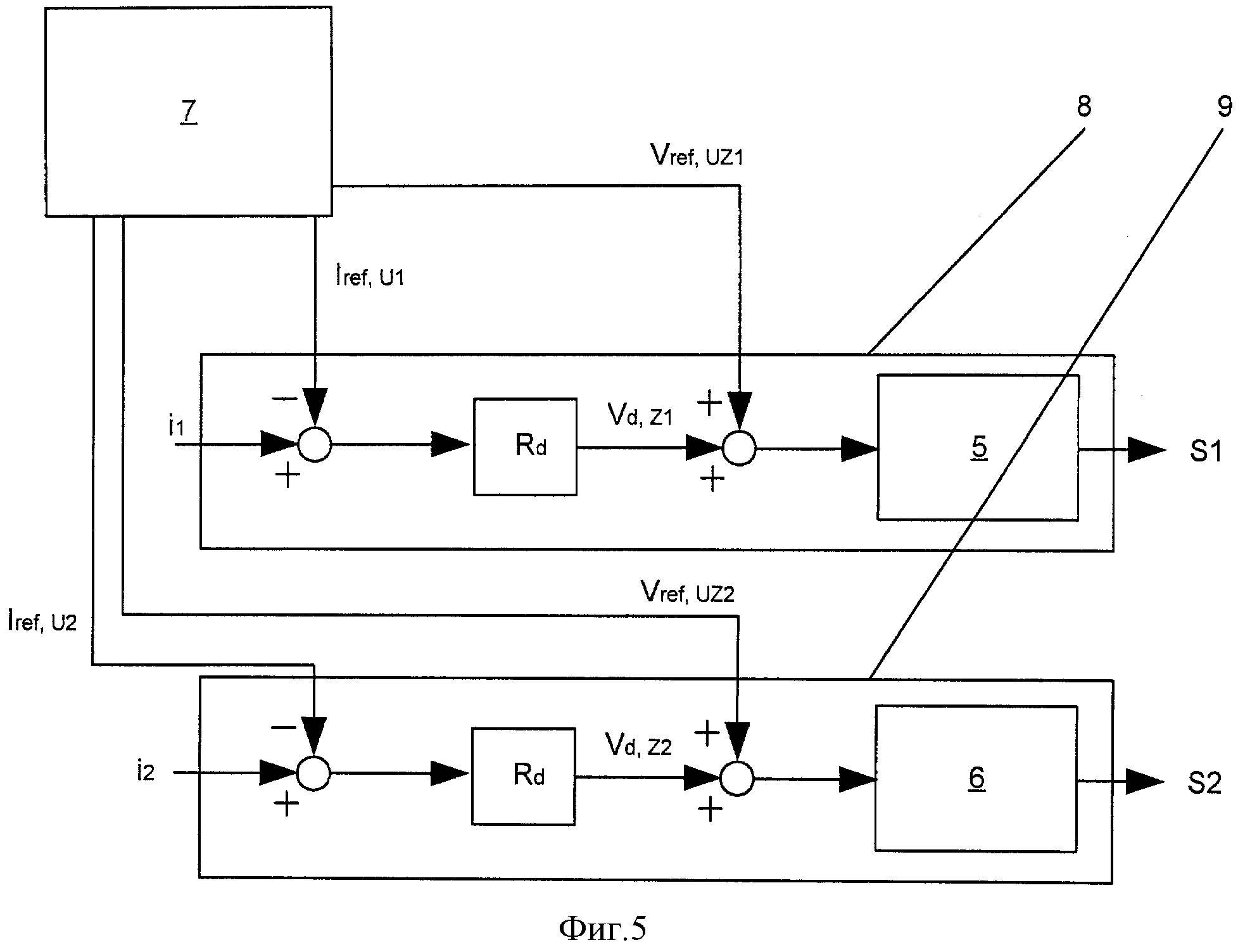

фиг.5 - четвертый вариант устройства для осуществления способа управления преобразовательной схемой;

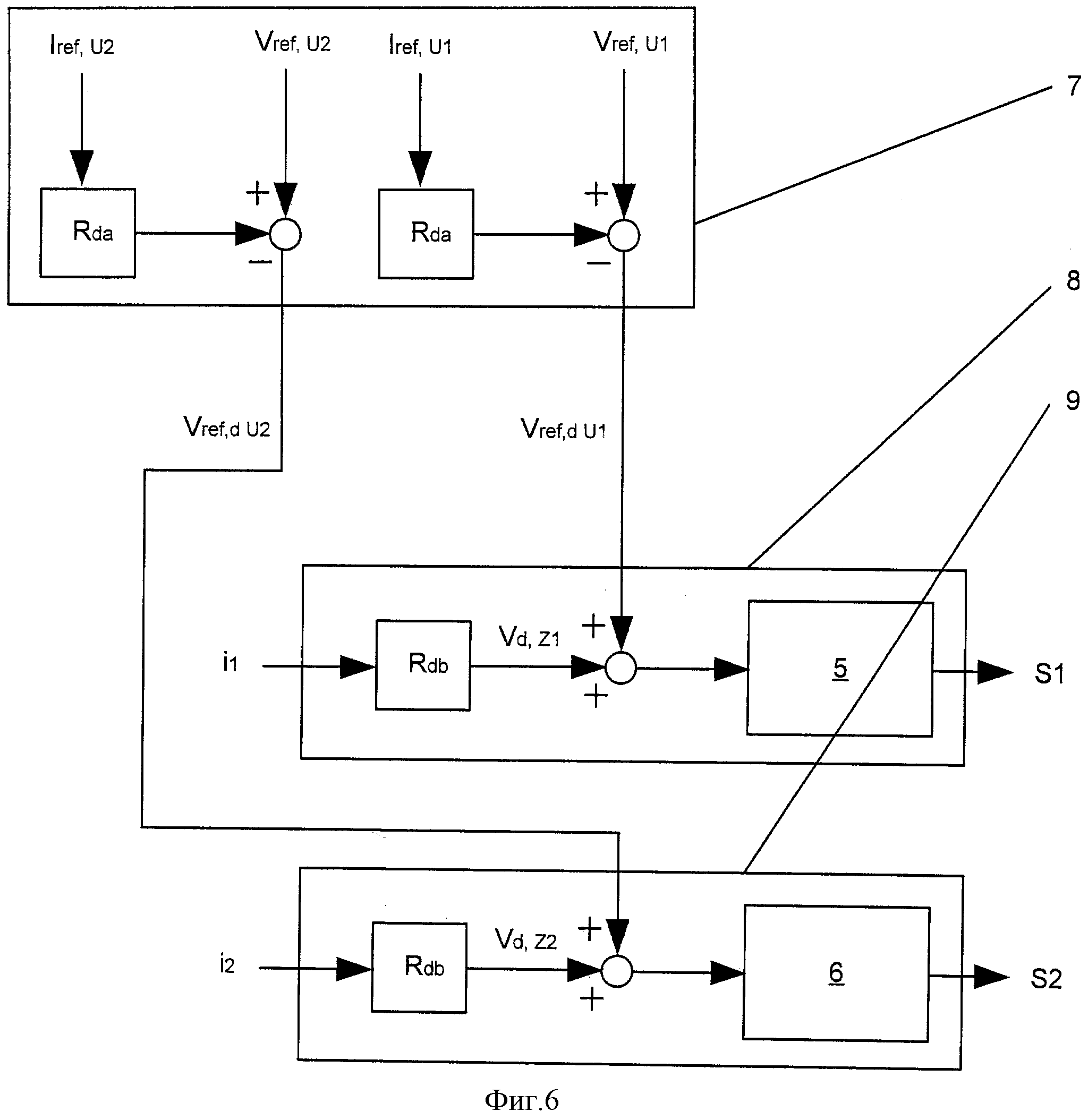

фиг.6 - пятый вариант устройства для осуществления способа управления преобразовательной схемой.

Использованные на чертежах ссылочные позиции и их значение объединены в перечне. В принципе, одинаковые элементы обозначены одинаковыми ссылочными позициями. Описанные варианты, которые следует понимать как пример объекта изобретения, и они не являются ограничивающими изобретение.

Осуществление изобретения

На фиг.1 изображен вариант преобразовательной схемы из уровня техники. Преобразовательная схема содержит по меньшей мере два фазных модуля 4, причем каждый фазный модуль 4 включает в себя первую 1 и вторую 2 частичные преобразовательные системы, и для каждого фазного модуля 4 частичные преобразовательные системы 1, 2 последовательно соединены между собой. Каждая частичная преобразовательная система 1, 2 включает в себя несколько последовательно включенных двухполюсных коммутационных ячеек 3, и каждая коммутационная ячейка 3 содержит управляемые двунаправленные силовые полупроводниковые выключатели с управляемым однонаправленным направлением прохождения тока и емкостный накопитель энергии. Кроме того, каждая частичная преобразовательная система 1, 2 может содержать индуктивность последовательно с сериесной схемой в коммутационных ячейках 3. Управляемые силовые полупроводниковые выключатели коммутационных ячеек 3 в частичных преобразовательных системах 1, 2 выполнены, в частности, в виде запираемого тиристора (ОТО) или в виде тиристора с интегрированным управлением (IGCT) соответственно со встречно-параллельно включенным диодом. Однако возможно также выполнение управляемого силового полупроводникового выключателя, например, в виде силового полевого МОП-транзистора с дополнительно встречно-параллельно включенным диодом или в виде биполярного транзистора с изолированным затвором (IGBT) с дополнительно встречно-параллельно включенным диодом. Преимущественно число коммутационных ячеек 3 первой частичной. преобразовательной системы 1 соответствует числу коммутационных ячеек 3 второй частичной преобразовательной системы 2.

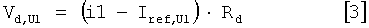

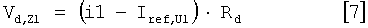

На фиг.2 изображен первый вариант устройства для осуществления способа управления преобразовательной схемой. Управление силовыми полупроводниковыми выключателями коммутационных ячеек 3 первой частичной преобразовательной системы 1 осуществляется посредством управляющего сигнала S1, а силовыми полупроводниковыми выключателями коммутационных ячеек 3 второй частичной преобразовательной системы 2 - посредством управляющего сигнала S2. Для первой частичной преобразовательной системы 1 управляющий сигнал S1 формируется из опорного сигнала Vref, U1 в отношении напряжения U1 на первой частичной преобразовательной системе 1. Для второй частичной преобразовательной системы 2 другой управляющий сигнал S2 формируется из опорного сигнала Vref, U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2. На фиг.2 управляющий сигнал S1 формируется дополнительно из демпфирующего сигнала Vd, U1 в отношении первой частичной преобразовательной системы 1, причем демпфирующий сигнал Vd, U1 формируется из измеренного тока i1 через первую частичную преобразовательную систему 1 и из задаваемого значения сопротивления Rd. Формирование демпфирующего сигнала Vd, U1 происходит по следующей формуле:

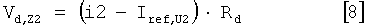

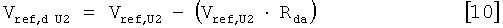

Другой управляющий сигнал S2, как показано на фиг.2, формируется дополнительно из демпфирующего сигнала Vd, U2 в отношении второй частичной преобразовательной системы 2, причем демпфирующий сигнал Vd, U2 формируется из измеренного тока i2 через вторую частичную преобразовательную систему 2 и из задаваемого значения сопротивления Rd. Формирование демпфирующего сигнала Vd U2 происходит по следующей формуле:

Каждый демпфирующий сигнал Vd, U1, Vd, U2 соответствует по своему действию падению напряжения на омическом сопротивлении в соответствующей частичной преобразовательной системе 1, 2 и, тем самым, демпфирует нужным образом токи i1, i2 через соответствующую частичную преобразовательную систему 1,2.

На фиг.2 формируется сумма из демпфирующего сигнала Vd, U1 в отношении первой частичной преобразовательной системы 1 и опорного сигнала Vref, U1 в отношении напряжения U1 на первой частичной преобразовательной системе 1 и подается на модулятор 5, который формирует из нее управляющий сигнал S1. Также на фиг.2 формируется сумма из демпфирующего сигнала Vd, U2 в отношении второй частичной преобразовательной системы 2 и опорного сигнала Vref, U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2 и подается на модулятор 6, который формирует из нее другой управляющий сигнал S2. В качестве модуляторов 5, 6 на фиг.2, а также на фиг.3-5 возможны любые модуляторы, такие как широтно-импульсные модуляторы, модуляторы несущей, пространственно-векторные модуляторы или модуляторы с гистерезисной характеристикой.

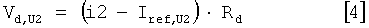

Согласно второму варианту устройства для осуществления способа управления преобразовательной схемой на фиг.3 преимущественно демпфирующий сигнал Vd, U1 в отношении первой частичной преобразовательной системы 1 дополнительно формируется из задаваемого опорного тока Iref, U1 через первую частичную преобразовательную систему 1. Формирование демпфирующего сигнала Vd, U1 происходит по следующей формуле:

На фиг.3 демпфирующий сигнал Vd, U2 в отношении второй частичной преобразовательной системы 1 дополнительно формируется из задаваемого опорного тока Iref, U2 через вторую частичную преобразовательную систему 2. Формирование демпфирующего сигнала Vd, U2 происходит по следующей формуле:

Формирование управляющих сигналов S1, S2 происходит так же, как на фиг.2.

Задавая опорный ток Iref, U1, Iref, U2 для формирования соответствующего демпфирующего сигнала Vd, U1, Vd, U2 можно демпфировать определенные составляющие колебаний токов i1, i2, проходящих через соответствующую частичную преобразовательную систему.

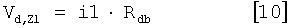

На фиг.4 изображен третий вариант устройства для осуществления способа управления преобразовательной схемой, являющийся альтернативой вариантам на фиг.2 и 3. Для первой частичной преобразовательной системы 1 управляющий сигнал S1 формируется из сформированного в центральном вычислительном блоке 7 опорного сигнала Vref, UZ1 в отношении соответствующей коммутационной ячейки 3 первой частичной преобразовательной системы 1. Для каждой коммутационной ячейки 3 первой частичной преобразовательной системы 1 предусмотрен локальный вычислительный блок 8, причем опорный сигнал Vref, UZ1 в отношении соответствующей коммутационной ячейки 3 первой частичной преобразовательной системы 1 передается на локальные вычислительные блоки 8 коммутационных ячеек 3 первой частичной преобразовательной системы 1. Далее управляющий сигнал S1 формируется в каждом локальном вычислительном блоке 8 коммутационных ячеек 3 первой частичной преобразовательной системы 1 дополнительно из демпфирующего сигнала Vd, Z1 в отношении соответствующей коммутационной ячейки 3 первой частичной преобразовательной системы 1, причем демпфирующий сигнал Vd, Z1 формируется из измеренного тока i1 через соответствующую коммутационную ячейку 3 первой частичной преобразовательной системы 1 и задаваемого значения сопротивления Rd. Формирование демпфирующего сигнала Vd, Z1 происходит по следующей формуле:

На фиг.4 для второй частичной преобразовательной системы 2 другой управляющий сигнал S2 формируется из сформированного в центральном вычислительном блоке 7 опорного сигнала Vref, UZ2 в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2. Для каждой коммутационной ячейки 3 второй частичной преобразовательной системы 2 предусмотрен локальный вычислительный блок 9, причем опорный сигнал Vref, UZ2 в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2 передается на локальные вычислительные блоки 9 коммутационных ячеек 3 второй частичной преобразовательной системы 2. Далее другой управляющий сигнал S2 формируется в каждом локальном вычислительном блоке 9 коммутационных ячеек 3 второй частичной преобразовательной системы 2 дополнительно из демпфирующего сигнала Vd, Z2 в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2, причем демпфирующий сигнал Vd, Z2 формируется из измеренного тока i2 через соответствующую коммутационную ячейку 3 второй частичной преобразовательной системы 2 и задаваемого значения сопротивления Rd. Формирование демпфирующего сигнала Vd, Z2 происходит по следующей формуле:

За счет описанной выше и показанной на фиг.4 альтернативы в коммутационных ячейках 3 происходит демпфирование токов i1, i2, проходящих через частичные преобразовательные системы 1, 2. Каждый демпфирующий сигнал Vd, Z1, Vd Z2 соответствует падению напряжения на омическом сопротивлении в каждой коммутационной ячейке 3, причем общее влияние соответствует сериесной схеме из омических сопротивлений, благодаря чему токи i1, i2 через соответствующие коммутационные ячейки 3 соответствующей частичной преобразовательной системы 1, 2 демпфируются нужным образом. За счет локального измерения токов i1, i2 через коммутационные ячейки 3 можно обеспечить дублирование и, таким образом, возможность демпфирования даже при отказе измерения тока, например в одной коммутационной ячейке 3. За счет локального формирования управляющего сигнала S1, S2 отпадает необходимость его передачи к отдельным коммутационным ячейкам 3, например от центрального или вышестоящего блока.

На фиг.4 формируется сумма из демпфирующего Vd, Z1 и опорного Vref, UZ1 сигналов в отношении соответствующей коммутационной ячейки 3 первой частичной преобразовательной системы 1 и подается на модулятор 5, который формирует из нее управляющий сигнал S 1. Также на фиг.4 формируется сумма из демпфирующего Vd, UZ2 и опорного Vref, UZ2 сигналов в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2 и подается на модулятор 6, который формирует из нее другой управляющий сигнал S2.

Согласно четвертому варианту устройства для осуществления способа управления преобразовательной схемой на фиг.5 демпфирующий сигнал Vd, Z1 формируется с учетом дополнительно задаваемого опорного тока Iref, U1 через соответствующую коммутационную ячейку 3 первой частичной преобразовательной системы 1. Задаваемый опорный ток Iref, U1 через соответствующую коммутационную ячейку 3 первой частичной преобразовательной системы 1 передается на локальные вычислительные блоки 8 коммутационных ячеек 3. Формирование демпфирующего сигнала Vd, Z1 происходит по следующей формуле:

На фиг.5 соответствующий демпфирующий сигнал Vd, Z2 в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2 формируется с учетом дополнительно задаваемого опорного тока Iref, U2 через соответствующую коммутационную ячейку 3. Задаваемый опорный ток Iref, U2 через соответствующую коммутационную ячейку 3 второй частичной преобразовательной системы 2 передается на локальные вычислительные блоки 9 коммутационных ячеек 3. Формирование демпфирующего сигнала Vd, Z2 происходит по следующей формуле:

Формирование управляющих сигналов S1, S2 происходит так же, как на фиг.4.

Предпочтительно значение сопротивления Rd задается постоянным или изменяемым по времени.

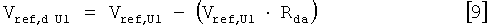

На фиг.6 изображен пятый вариант устройства для осуществления способа управления преобразовательной схемой, являющийся альтернативой вариантам, показанным на фиг.2-5. Для первой частичной преобразовательной системы 1 управляющий сигнал S1 формируется из сформированного в центральном вычислительном блоке 7 демпфирующего опорного сигнала Vref, d U1 в отношении напряжения U1 на первой частичной преобразовательной системе, причем демпфирующий опорный сигнал Vref, d U1 в отношении напряжения U1 на первой частичной преобразовательной системе 1 формируется из задаваемого опорного тока Iref, U1 через первую систему 1, задаваемого значения сопротивления Rda и опорного сигнала Vref, U1 в отношении напряжения U1 на первой частичной преобразовательной системе 1. Формирование демпфирующего сигнала Vref, d U1 происходит по следующей формуле:

Кроме того, для каждой коммутационной ячейки 3 первой частичной преобразовательной системы 1 на фиг.6 предусмотрен локальный вычислительный блок 8, причем демпфирующий опорный сигнал Vref, d U1 в отношении напряжения U1 на первой частичной преобразовательной системе 1 подается на локальные вычислительные блоки 8 коммутационных ячеек 3. Управляющий сигнал S1 формируется в каждом локальном вычислительном блоке 8 коммутационных ячеек 3 первой частичной преобразовательной системы 1 дополнительно из демпфирующего сигнала Vd, Z1 в отношении соответствующей коммутационной ячейки 3, причем демпфирующий сигнал Vd, Z1 формируется из измеренного тока i1 через соответствующую коммутационную ячейку 3 первой частичной преобразовательной системы 1 и другого задаваемого значения сопротивления Rdb. Формирование демпфирующего сигнала Vd, Z1 происходит по следующей формуле:

На фиг.6 формируется сумма из демпфирующего сигнала Vd, Z1 и демпфирующего опорного Vref, d U1 сигнала в отношении напряжения U1 на первой частичной преобразовательной системе 1 и подается на модулятор 5, который формирует из нее управляющий сигнал S1.

Для второй частичной преобразовательной системы 2 другой управляющий сигнал S2 формируется из сформированного в центральном вычислительном блоке 9 демпфирующего опорного сигнала Vref, d U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2, причем демпфирующий опорный сигнал Vref, d U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2 формируется из задаваемого опорного тока Iref, U2 через вторую систему 2, задаваемого значения сопротивления Rda и опорного сигнала Vref, U2 в отношении напряжения U2 над второй частичной преобразовательной системе 2. Формирование демпфирующего сигнала Vref, d U2 происходит по следующей формуле:

На фиг.6 для каждой коммутационной ячейки 3 второй частичной преобразовательной системы 2 предусмотрен локальный вычислительный блок 9, причем демпфирующий опорный сигнал Vref, d U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2 передается на локальные вычислительные блоки 9 коммутационных ячеек 3 системы 2. Другой управляющий сигнал S2 формируется в каждом локальном вычислительном блоке 9 коммутационных ячеек 3 второй частичной преобразовательной системы 2 дополнительно из демпфирующего сигнала Vd, Z2 в отношении соответствующей коммутационной ячейки 3, причем демпфирующий сигнал Vd, Z2 формируется из измеренного тока i2 через соответствующую коммутационную ячейку 3 второй частичной преобразовательной системы 2 и другого задаваемого значения сопротивления Rdb. Формирование демпфирующего сигнала Vd, Z2 происходит по следующей формуле:

Как показано на фиг.6, формируется сумма из демпфирующего сигнала Vd, Z2 в отношении соответствующей коммутационной ячейки 3 второй частичной преобразовательной системы 2 и демпфирующего опорного сигнала Vref, d U2 в отношении напряжения U2 на второй частичной преобразовательной системе 2 и подается на модулятор 6, который формирует из нее другой управляющий сигнал S2.

Также с помощью этого варианта изобретения, показанного на фиг.6, выборочно могут демпфироваться определенные составляющие колебаний токов i1, i2 через коммутационные ячейки 3 соответствующей частичной преобразовательной системы 1, 2. Кроме того, соответствующий опорный ток Iref, U1, Iref, U2 не передается на локальные вычислительные блоки 8, 9. Значение сопротивления Rda выбрано предпочтительно так, что оно не повышает вклад соответствующего опорного тока Iref, U1, Iref, U2 в отношении демпфирующего сигнала Vd, Z1, Vd, Z2, сформированного в соответствующем локальном вычислительном блоке 8, 9.

Преимущественно значения сопротивления Rda, Rdb задаются постоянными или изменяемыми по времени.

Также возможно, чтобы соответствующий демпфирующий сигнал Vd, U1, Vd, U2, Vd, Z1, Vd, Z2 задавался в соответствии с общей функцией, причем такая функция может содержать тогда, например, постоянную составляющую, изменяемую по времени составляющую, интегральную - составляющую, дифференциальную составляющую, опорную составляющую и прежнее значение соответствующего демпфирующего сигнала или комбинацию указанных выше вариантов.

Перечень ссылочных позиций

1 - первая частичная преобразовательная система

2 - вторая частичная преобразовательная система

3 - коммутационная ячейка

4 - фазный модуль

5, 6 - модулятор

7 - центральный вычислительный блок

8, 9 - локальный вычислительный блок