Результат интеллектуальной деятельности: ПСЕВДОДИФФЕРЕНЦИАЛЬНЫЙ КАСКОДНЫЙ ВЫХОДНОЙ БУФЕР

Вид РИД

Изобретение

Изобретение относится к области коммутационных сред для вычислительных систем и может быть использовано как выходной буферный каскад передатчика в высокоскоростных мультиканальных интерфейсах.

Известен выходной буфер, включающий в себя общий источник тока, дифференциальную пару ключей, терминирующие резисторы (US, Заявка №007446576 В2, кл. Н01Н 73/36, опублик. 2008).

Недостаток описанного буфера связан с эффектом уменьшения размаха дифференциального напряжения выходного сигнала и увеличения потерь на отражение от величины высокого уровня входного сигнала.

Наиболее близким по технической сути и достигаемому результату является псевдодифференциальный каскодный выходной буфер, состоящий из основного управляемого источника стабильного тока, формирователя основного опорного напряжения, пары основных источников тока, пары основных ключей, дублера основного ключа, пары терминирующих резисторов и пары дифференциальных катушек (US, Патент №2013/0002311, кл. Н01Н 73/36, опублик. 2013).

Недостатками описанного буфера являются: во-первых, он провоцирует дополнительное дрожание выходного сигнала, вызванное увеличением частотно-зависимого характера и деградацией таких параметров, как время разбежки между прямым и инверсным сигналом, дисбаланс фронта и среза, во-вторых, буфер неспособен формировать выходное напряжение с большим дифференциальным размахом.

Задачей данного изобретения является обеспечение работы устройства для передачи высокоскоростного потока данных.

Указанная задача решается тем, что псевдодифференциальный каскодный выходной буфер, состоящий из основного управляемого источника стабильного тока, формирователя основного опорного напряжения, пары основных источников тока, пары основных ключей, дублера основного ключа, пары терминирующих резисторов и пары дифференциальных катушек, согласно изобретению дополнительно снабжен вспомогательным источником тока и парой вспомогательных ключей, связанных с парой основных источников тока и парой основных ключей, и содержит дублер вспомогательного источника тока и дублер вспомогательного ключа, связанные с формирователем основного опорного напряжения и дублером основного ключа, при этом каскодный выходной буфер содержит вспомогательный управляемый источник стабильного тока и формирователь вспомогательного опорного напряжения, связанные с вспомогательным источником тока и дублером вспомогательного источника тока.

Технический результат от использования данного изобретения состоит в уменьшении дрожания выходного сигнала и увеличении диапазона дифференциального размаха выходного напряжения путем обеспечения возможности передачи высокоскоростного потока данных.

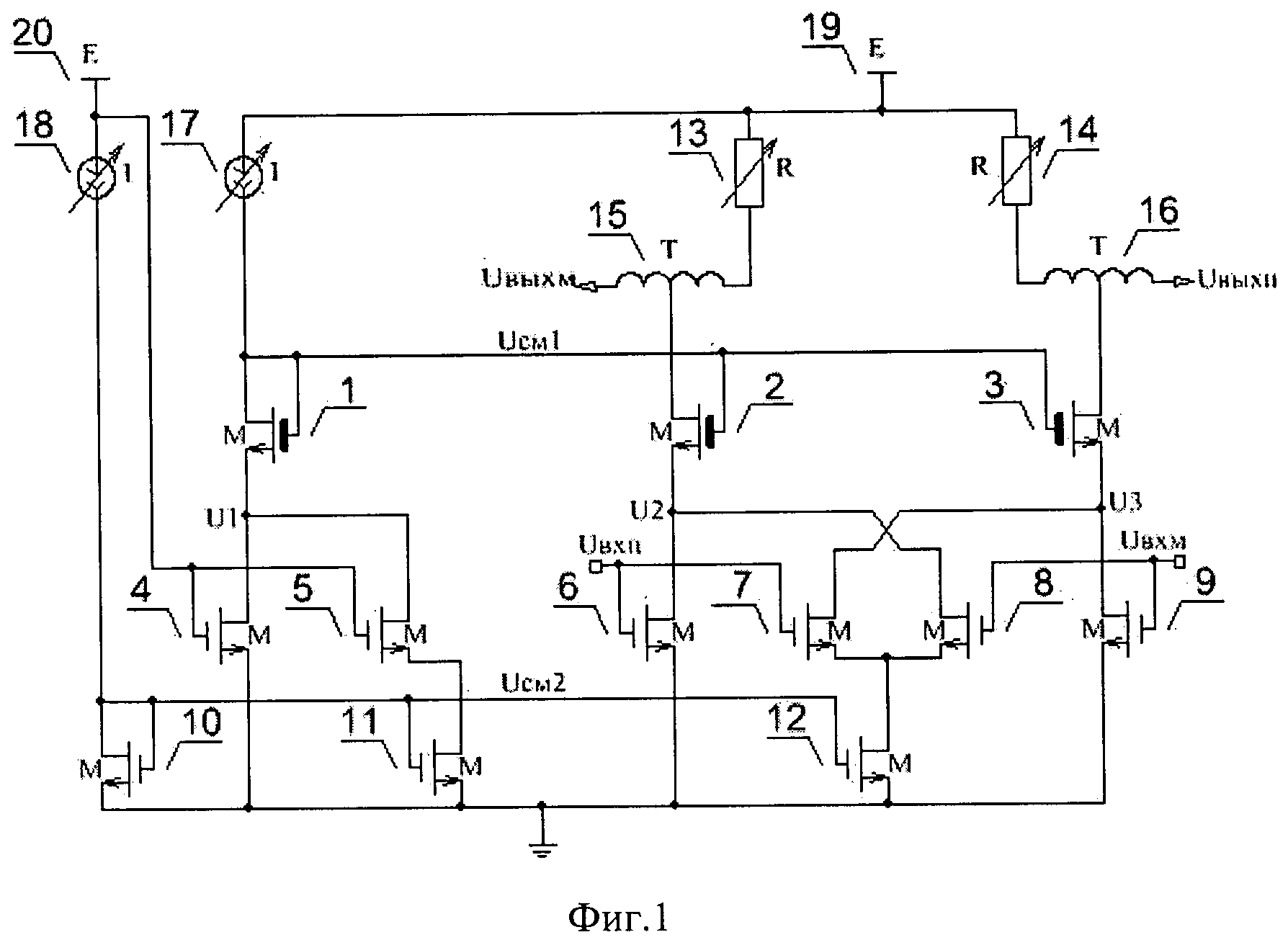

Изобретение поясняется чертежом, где на фиг.1 изображена принципиальная схема псевдодифференциального каскодного выходного буфера.

Буфер состоит из формирователя основного опорного напряжения на транзисторе 1, основного источника тока на транзисторе 2, основного источника тока на транзисторе 3, дублера основного ключа на транзисторе 4, дублера вспомогательного ключа на транзисторе 5, основного ключа на транзисторе 6, вспомогательного ключа на транзисторе 7, вспомогательного ключа на транзисторе 8, основного ключа на транзисторе 9, формирователя вспомогательного опорного напряжения на транзисторе 10, дублера вспомогательного источника тока на транзисторе 11, вспомогательного источника тока на транзисторе 12, терминирующего резистора с переменным сопротивлением 13, терминирующего резистора с переменным сопротивлением 14, дифференциальной катушки 15, дифференциальной катушки 16, основного управляемого источника стабильного тока 17, вспомогательного управляемого источника стабильного тока 18, источника питания 19, источника питания 20.

Выходной буфер работает следующим образом. Основной управляемый источник стабильного тока 17 подключен к источнику питания 19, формируя стабильный опорный ток. Формирователь основного опорного напряжения 1 преобразует стабильный опорный ток в основное опорное напряжение Uсм1. Напряжение Uсм1 подается на затворы основного источника тока на транзисторе 2 и основного источника тока на транзисторе 3, формируя основной ток, величина которого в обоих плечах буфера одинакова. Исток основного источника тока на транзисторе 2 последовательно соединен с основным ключом на транзисторе 6, формируя каскод. Исток основного источника тока на транзисторе 3 последовательно соединен с основным ключом на транзисторе 9, формируя каскод. Основной ключ на транзисторе 9 работает инверсно относительно основного ключа на транзисторе 6. Если входной сигнал Uвхп открывает основной ключ на транзисторе 6, ток основного источника тока на транзисторе 2 формирует падение напряжения на терминирующем резисторе с переменным сопротивлением 13, уменьшая потенциал на выходе Uвыхм. В то же самое время входной сигнал Uвхм закрывает основной ключ на транзисторе 9, ток основного источника тока на транзисторе 3 отсутствует, падения напряжения на терминирующем резисторе с переменным сопротивлением 14 нет, потенциал на UВЫХП подтягивается к источнику питания 19.

В процессе ухода в отсечку основного ключа на транзисторе 6 или основного ключа на транзисторе 9, в узле U2 или U3, формируется остаточный заряд. Порция этого заряда, оставшаяся к моменту открытия основного ключа на транзисторе 6 или основного ключа на транзисторе 9, зависит от времени отсечки, что увеличивает частотно-зависимый характер работы выходного буфера. Для устранения этого эффекта потенциалы в узле U2 или U3 контролируются вспомогательным источником тока на транзисторе 12. Выбор плеча, в которое будет подаваться вспомогательный ток, осуществляется вспомогательным ключом на транзисторе 7 и вспомогательным ключом на транзисторе 8. Вспомогательный ключ на транзисторе 8 работает инверсно относительно вспомогательного ключа на транзисторе 7.

Таким образом, основной ключ на транзисторе 6 и вспомогательный ключ на транзисторе 7 работают в противофазе основному ключу на транзисторе 9 и вспомогательному ключу на транзисторе 8. Когда на вход Uвхп подается логический ноль, на входе Uвмм логическая единица, основной ключ на транзисторе 6 в отсечке, вспомогательный ключ на транзисторе 8 находится в насыщении, пропуская ток вспомогательного источника тока на транзисторе 12, формируя определенный потенциал в узле U1. Одновременно вспомогательный ключ на транзисторе 7 находится в отсечке, а основной ключ на транзисторе 9 в насыщении, пропуская ток основного источника тока на транзисторе 3. Если входной сигнал Uвхп/Uвмм инвертируется на противоположный, работа осуществляется с точностью до наоборот.

Для того чтобы ток вспомогательного источника тока на транзисторе 12 не приводил к уменьшению дифференциального размаха выходного напряжения, его величина должна быть, по крайней мере, на два порядка меньше, чем величина тока основного источника тока на транзисторе 2 или основного источника тока на транзисторе 3.

Контроль потенциалов в узлах U2 или U3 дает возможность увеличить напряжение источника питания 19, увеличив толстый окисел затворов формирователя основного опорного напряжения на транзисторе 1, основного источника тока на транзисторе 2 и основного источника тока на транзисторе 3, что приведет к увеличению диапазона дифференциального размаха выходного напряжения.

Для формирования вспомогательного источника тока на транзисторе 12 используется вспомогательный управляемый источник стабильного тока 18, подключенный к источнику питания 20. Формирователь вспомогательного опорного напряжения на транзисторе 10 преобразует ток вспомогательного управляемого источника стабильного тока 18 в опорное напряжение Ucм2, которое подается на затвор вспомогательного источника тока на транзисторе 12.

Необходимо уменьшить погрешность отражения тока в токовом зеркале, состоящем из формирователя основного опорного напряжения на транзисторе 1 и основного источника тока на транзисторе 2, выровняв потенциал узла U1 с потенциалом узла U2. А также необходимо уменьшить погрешность отражения тока в токовом зеркале, состоящем из формирователя основного опорного напряжения на транзисторе 1 и основного источника тока на транзисторе 3, выровняв потенциал узла U1 с потенциалом узла U3. Для этого в цепь истока формирователя основного опорного напряжения на транзисторе 1 подключен дублер основного ключа на транзисторе 4 и последовательно соединенный дублер вспомогательного ключа на транзисторе 5 и дублер вспомогательного источника тока на транзисторе 11. Дублер основного ключа на транзисторе 4 эмитирует основной ключ на транзисторе 6 или основной ключ на транзисторе 9. Дублер вспомогательного ключа на транзисторе 5 эмитирует вспомогательный ключ на транзисторе 7 или вспомогательный ключ на транзисторе 8. Дублер вспомогательного источника тока на транзисторе 11 эмитирует вспомогательный источник тока на транзисторе 12. Затворы дублера основного ключа на транзисторе 4 и дублера вспомогательного ключа на транзисторе 5 подключены к источнику питания 20, держа их постоянно в открытом состоянии.

Дифференциальная катушка 15 и дифференциальная катушка 16 необходимы для изоляции выходной емкости стоков основного источника тока на транзисторе 2 и основного источника тока на транзисторе 3, уменьшая потери на отражение.

Таким образом, предложенное изобретение позволяет уменьшить дрожание выходного сигнала за счет уменьшения своего собственного вклада в ухудшение таких характеристик, как время разбежки между прямым и инверсным сигналом, дисбаланс фронта и среза. Также в предложенном изобретении увеличен диапазон дифференциального размаха выходного напряжения.

Псевдодифференциальный каскодный выходной буфер, состоящий из основного управляемого источника стабильного тока, формирователя основного опорного напряжения, пары основных источников тока, пары основных ключей, дублера основного ключа, пары терминирующих резисторов и пары дифференциальных катушек, отличающийся тем, что он дополнительно снабжен вспомогательным источником тока и парой вспомогательных ключей, связанных с парой основных источников тока и парой основных ключей, и содержит дублер вспомогательного источника тока и дублер вспомогательного ключа, связанные с формирователем основного опорного напряжения и дублером основного ключа, при этом каскодный выходной буфер содержит вспомогательный управляемый источник стабильного тока и формирователь вспомогательного опорного напряжения, связанные с вспомогательным источником тока и дублером вспомогательного источника тока.