Результат интеллектуальной деятельности: ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических устройств.

Известен парафазный логический элемент на КМДП транзисторах (Патент РФ №2258303, H03K 19/096 от 15.12.2003). Устройство обладает функцией сохранения результата на полутакте за счет триггера на выходе и отсутствием переключения цепей при повторении значения функции. Устройство содержит два транзистора p-типа, два проходных и один тактовый транзистора n-типа и логические ключевые цепи, выполненные на транзисторах n-типа. Недостаток этого устройства - его избыточная сложность, когда для реализации необходимо 5 МДП транзисторов, помимо логических, и дополнительно триггер на элементах 2И-НЕ.

Наиболее близким техническим решением к предлагаемому является каскадное парафазное логическое устройство (Патент США №7428568, фиг.. 1, МКИ H03K 19/096, 708/702 от 23.09.2008). Это устройство, принятое за прототип, содержит 4 МДП транзистора p-типа, тактовый транзистор n-типа и логические прямые и инверсные ключевые цепи, выполненные на транзисторах n-типа, которые включены соответственно между парафазными выходами устройства и общим выводом, который через тактовый транзистор n-типа соединен с шиной земли. Недостаток этого устройства - ограниченные функциональные возможности - отсутствие запоминания результата на полутакте и связанная с этим необходимость возврата на каждом такте в исходное состояние и далее вынужденный перезаряд внутренних емкостей устройства на каждом такте независимо от того, изменяется логическое состояние на выходах или подтверждается предыдущее.

Техническим результатом изобретения является расширение функциональных возможностей устройства.

Технический результат достигается тем, что парафазный логический элемент содержит два транзистора р-типа, первый тактовый транзистор n-типа и логический блок, содержащий прямые и инверсные ключевые цепи, выполненные каждая из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы прямых ключевых цепей подключены к прямому выходу устройства, а первые выводы инверсных ключевых цепей подключены к инверсному выходу устройства, первый и второй транзисторы р-типа включены между шиной питания и соответственно прямым и инверсным выходами устройства, а затворы тех же транзисторов р-типа соединены соответственно с инверсным и прямым выходами устройства, вторые выводы прямых ключевых цепей логического блока через первый тактовый транзистор n-типа, затвор которого подключен к тактовай шине, соединены с шиной земли, и дополнительно содержит второй тактовый транзистор n-типа, затвор которого подключен к тактовой шине, а вторые выводы инверсных ключевых цепей логического блока через второй тактовый транзистор n-типа также соединены с шиной земли.

Существенными отличительными признаками в указанной совокупности признаков является наличие второго тактового транзистора n-типа и гальваническое разделение прямых и инверсных ключевых цепей логического блока.

Наличие в предлагаемом устройстве перечисленных выше существенных отличительных признаков обеспечивает решение поставленной технической задачи - расширения функциональных возможностей устройства. В устройстве-прототипе каждый полутакт с помощью предзарядовых транзисторов р-типа сопровождается возвратом в исходное состояние (потенциал шины питания на обоих парафазных выходах устройства). Далее в рабочем полутакте при участии цепей логического блока следует вынужденный перезаряд внутренних емкостей устройства и нагрузки независимо от того, изменяется логическое состояние на выходах или подтверждается предыдущее. При этом потребляется дополнительная мощность и возрастает время самого такта.

В заявленном устройстве изменение логических входов (переменных) на полутакте осуществляется при закрытых тактовых транзисторах, прямые и инверсные логические цепи изолированы между собой. Состояния выходов устройства при этом сохраняются, а надежность обеспечивается тем, что в состоянии динамического хранения находится выход с потенциалом шины земли (отсутствуют токи утечек), а парафазный выход устройства с потенциалом шины питания поддерживается через открытый транзистор р-типа.

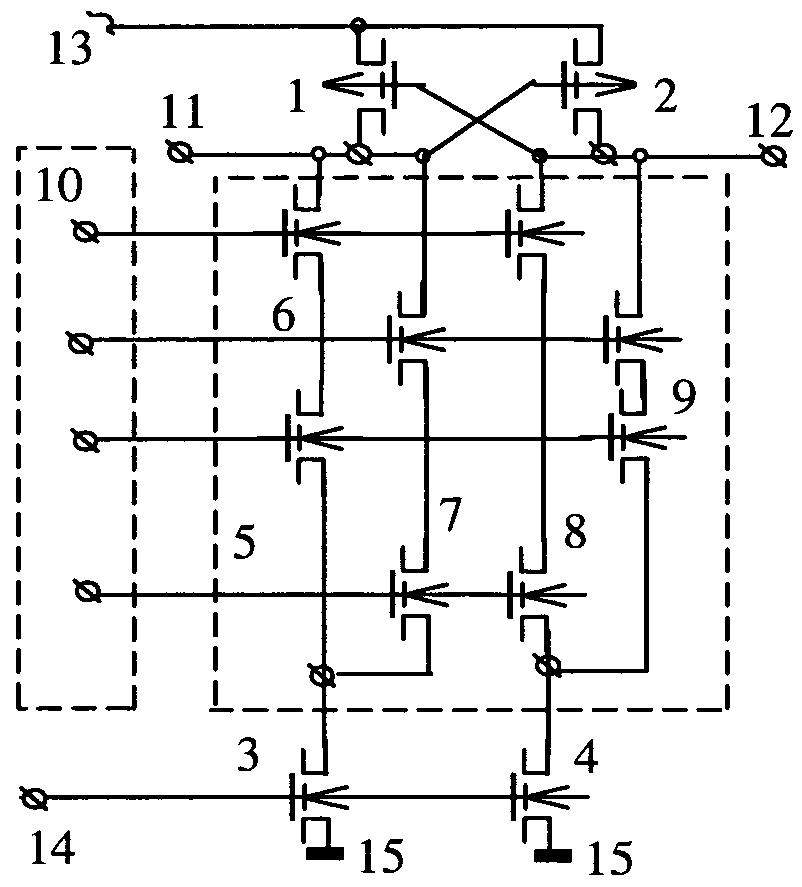

На чертеже приведена принципиальная схема заявляемого парафазного логического элемента на примере логической функции 'Исключающее ИЛИ'.

Устройство содержит два транзистора р-типа 1, 2, два тактовых транзистора 3, 4 n-типа и логический блок 5, содержащий прямые 6, 7 и инверсные 8, 9 ключевые цепи, выполненные каждая из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к парафазным логическим входам 10 устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы прямых ключевых цепей 6, 7 подключены к прямому выходу 11 устройства, а первые выводы инверсных ключевых цепей 8, 9 подключены к инверсному выходу 12 устройства, первый 1 и второй 2 транзисторы р-типа включены между шиной питания 13 и соответственно прямым 11 и инверсным 12 выходами устройства, а затворы тех же транзисторов р-типа соединены соответственно с инверсным 12 и прямым 11 выходами устройства, затворы первого 3 и второго 4 тактовых транзисторов n-типа подключены к тактовой шине 14, вторые выводы прямых 6, 7 и инверсных 8, 9 ключевых цепей логического блока 5 соответственно через первый 3 и второй 4 тактовые транзисторы n-типа соединены с шиной земли 15.

Логический блок 5 при реализации функции 'Исключающее ИЛИ' содержит 8 логических транзисторов n-типа, которые включены попарно последовательно и составляют две прямые 6, 7 и две инверсные 8, 9 ключевые цепи. Количество ключевых цепей соответствует числу логических состояний элемента - в данном случае 4 от двух парафазных переменных. Ключевые цепи формируются по правилам Булевой алгебры для парафаэных логических сигналов. Ключевая цепь является проводящей, когда на затворы транзисторов, ее составляющих, подаются сигналы логической 1, т.е. напряжения положительного питания.

Устройство функционирует следующим образом. На первом полутакте тактовая шина 14 имеет нулевой потенциал и оба тактовых транзистора 3-4 закрыты, прямые 6-7 и инверсные 8-9 ключевые цепи изолированы как между собой, так и от шины земли 15. На парафазных логических входах 10 устанавливаются новые значения переменных. Например, при равенстве переменных X=Y=1 проводящей является первая прямая ключевая цепь 6, а при X=Y=0 - вторая прямая ключевая цепь 7. При неравенстве переменнх X≠Y проводящей является первая 8 или вторая 9 инверсная ключевая цепь. Состояние выходов 11 и 12 устройства соответствует логическим входам 10 на предыдущем такте, например, прямой выход 11 устройства имеет высокий потенциал, а инверсный выход 12 устройства - низкий потенциал.

На втором полутакте тактовая шина 14 приобретает единичный потенциал и оба тактовых транзистора 3-4 открываются. При равенстве переменных X=Y=1 проводящей является первая прямая ключевая цепь 6 и потенциал прямого выхода 11 устройства начинает снижаться, как в резистивном делителе напряжения. Для срабатавания обратной связи через транзисторы 1-2 р-типа необходимо, чтобы проводимость проводящей ключевой цепи была больше, чем проводимость транзисторов 1-2 р-типа, что обеспечивается за счет ширины каналов транзисторов n-типа логического блока 5 и тактовых транзисторов 3-4 n-типа. При снижении потенциала прямого выхода 11 устройства на величину порогового напряжения транзисторов р-типа транзистор 4 р-типа открывается и потенциал инверсного выхода 12 при непроводящих инверсных ключевых цепях 8-9 повышается, что ведет к постепенному запиранию первого 3 транзистора р-типа. Таким образом срабатавание обратной связи через транзисторы 1-2 р-типа ведет к формированию низкого потенциала (шины земли) прямого выхода 11 и высокого потенциала инверсного выхода 12, т.е. к логическому изменению функции. При этом процесс нарастания потенциала инверсного выхода 12 может продолжаться при переходе к очередному полупериоду, т.к. транзистор 4 р-типа остается открытым. Тем самым снижается эффективное время полного такта, поскольку транзисторы р-типа имеют более низкую проводимость, чем n-типа.

В следующем такте при повторении значения логической функции (изменение логических входов осуществляется при закрытых тактовых транзисторах - проводящей становится вторая прямая ключевая цепль 7) прямые и инверсные логические цепи изолированы между собой. Состояния выходов устройства при этом сохраняются, а надежность обеспечивается тем, что в состоянии динамического хранения находится выход с потенциалом шины земли (отсутствуют токи утечек), а парафазный выход устройства с потенциалом шины питания поддерживается через открытый транзистор р-типа. При этом не происходит перезаряда емкостей нагрузок на выходах устройства и уменьшается потребляемая мощность в расчете на один такт.

Парафазный логический элемент, содержащий два транзистора р-типа, первый тактовый транзистор n-типа и логический блок, включающий прямые и инверсные ключевые цепи, выполненные каждая из последовательно соединённых логических транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы прямых ключевых цепей подключены к прямому выходу устройства, а первые выводы инверсных ключевых цепей подключены к инверсному выходу устройства, первый и второй транзисторы р-типа включены между шиной питания и соответственно прямым и инверсным выходами устройства, а затворы тех же транзисторов р-типа соединены соответственно с инверсным и прямым выходами устройства, вторые выводы прямых ключевых цепей логического блока через первый тактовый транзистор n-типа, затвор которого подключён к тактовой шине, соединены с шиной земли, отличающийся тем, что содержит второй тактовый транзистор n-типа, затвор которого подключён к тактовой шине, а вторые выводы инверсных ключевых цепей логического блока через второй тактовый транзистор n-типа также соединены с шиной земли.