Результат интеллектуальной деятельности: ЯДРО СОПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ РЕАЛЬНОГО ВРЕМЕНИ

Вид РИД

Изобретение

Изобретение относится к области цифровой обработки сигналов, а именно к ядрам сопроцессора быстрого преобразования Фурье реального времени, и может быть использовано для цифровой обработки сигналов в области радиолокации, гидроакустики, связи, телерадиовещания, спутниковой ретрансляции, сжатия информации и обработки изображений.

К настоящему времени в области программирования и микроэлектроники для цифровой обработки сигналов существует несколько способов реализации алгоритма быстрого преобразования Фурье (БПФ), отличающихся между собой основанием преобразования (radix2, radix4 и т.д.), количеством отсчетов преобразования (от 4 до 1048576 и выше), порядком входных и выходных данных, а также временем исполнения операции.

Наиболее близким к заявленному изобретению является процессор быстрого преобразования Фурье, описанный в патенте RU 2290687. Данный процессор выбран в качестве прототипа заявленного изобретения.

Недостатком прототипа является то, что в нем присутствует большое количество памяти, а именно несколько блоков памяти, кроме того, в нем отсутствует возможность исполнения сопутствующих операций, а также наращивания матрицы Фурье.

Задачей заявленного изобретения является создание ядра сопроцессора быстрого преобразования Фурье реального времени для автономного, параллельного с работой DSP - процессора (процессора цифровой обработки сигнала), выполнения быстрых преобразований Фурье комплексных массивов и некоторых сопутствующих операций, которое имеет следующие преимущества: ввод/вывод выполняются в реальном времени, параллельно с обработкой; входные/выходные данные для пользователя входных/выходных данных располагаются в прямом порядке; для расчетов и хранения данных в прямом порядке дополнительная память не требуется; форматы действительных/мнимых компонент входных и выходных данных: 32-разрядная плавающая точка (стандарт IEEE-754), 32-разрядная фиксированная точка (целое число, дополнительный код), 16-разрядная фиксированная точка (целое число, дополнительный код); формат вычислений: 32-разрядная плавающая точка; максимальный размер непосредственно выполняемого преобразования - 8192 К, минимальный - 16 К, предельный размер наращиваемого преобразования - 256 К. Модуль формирования коэффициентов заявленного ядра сопроцессора выполнен с возможностью расчета поворачивающих коэффициентов для быстрого преобразования Фурье, что позволяет сократить объем необходимой памяти для устройства, а также ускорить обработку больших массивов до 256 К отсчетов. Первый и второй преобразователи адреса чтения и преобразователь адреса записи заявленного ядра сопроцессора выполнены с возможностью конвертации адреса запроса на соответственно чтение/запись в зависимости от выбранного алгоритма, что позволяет сохранить высокий паралеллизм исполнения обработки и ее осуществления без задействования дополнительной памяти результатов (результат вычисления сохраняется в том же месте, что и входные данные).

Поставленная задача решена путем создания ядра сопроцессора быстрого преобразования Фурье реального времени, содержащего модуль управления, выполненный с возможностью непосредственного управления работой ядра сопроцессора посредством записи параметров вычислений и команд в регистры сопроцессора; вычислительный модуль, выполненный с возможностью осуществления основных вычислений с предварительно загруженными в память сопроцессора данными; адресный генератор основных данных и адресный генератор дополнительных данных, выполненные с возможностью формирования адреса для чтения из внутренней памяти сопроцессора данных, необходимых для осуществления заданной операции, а также формирования адреса для записи в память результата вычислений; память сопроцессора, которая состоит из двух секций, что позволяет ядру сопроцессора работать в двухбуферном режиме: с одним буфером работает сопроцессор, с другим внешний контроллер прямого доступа в память (через шину AXI), выполненный с возможностью выгрузки результата и загрузки новых данных; модуль формирования коэффициентов, выполненный с возможностью расчета поворачивающих коэффициентов для быстрого преобразования Фурье; конвейер управления, выполненный с возможностью формирования управляющих сигналов для всех модулей обработки в соответствии с заданным алгоритмом обработки; контроллер AXI шины, выполненный с возможностью обеспечения доступа со стороны внешнего контроллера прямого доступа в память; преобразователь входных/выходных данных, выполненный с возможностью преобразования входных данных и выходных данных из одного формата в другой; арбитр порта А, выполненный с возможностью коммутации запросов на чтение/запись контроллера AXI шины и на запись результата преобразования; арбитр порта В, выполненный с возможностью коммутации запросов на чтение основных и дополнительных данных для вычислительного модуля; первый преобразователь адреса чтения, второй преобразователь адреса чтения и преобразователь адреса записи, выполненные с возможностью конвертации адреса запроса на соответственно чтение/запись в зависимости от выбранного алгоритма; шину параметров, которая соединяет между собой модуль управления, вычислительный модуль, адресный генератор основных данных, адресный генератор дополнительных данных, контроллер AXI шины и преобразователь входных/выходных данных; кроме того, контроллер AXI шины соединен с AXI шиной и с преобразователем входных/выходных данных, который соединен с арбитром порта А, выход которого соединен с входом преобразователя адреса записи, выход которого соединен с входом памяти, которая соединена с первым преобразователем адреса чтения, который соединен с арбитром порта А, вход которого соединен с выходами конвейера управления и вычислительного модуля, вход которого соединен с памятью и преобразователем адреса записи; первый выход адресного генератора основных данных соединен с входом конвейера управления и с входом модуля формирования коэффициентов, выход которого соединен с входом вычислительного модуля, а второй выход адресного генератора основных данных соединен с первым входом арбитра порта В; выход адресного генератора дополнительных данных соединен со вторым входом арбитра порта В, выход которого соединен с входом второго преобразователя адреса чтения, выход которого соединен с входом памяти.

В предпочтительном варианте осуществления ядра сопроцессора вычислительный модуль выполнен в виде многофункционального устройства.

В предпочтительном варианте осуществления ядра сопроцессора для различных задач, выполняемых сопроцессором, адресные генераторы выполнены с возможностью формирования адреса по различным алгоритмам.

В предпочтительном варианте осуществления ядра сопроцессора преобразователь входных/выходных данных выполнен с возможностью преобразования входных данных в следующих соответствиях: integer32 в float32, integer16 в float32; и выходных данных из float32 в integer32.

В предпочтительном варианте осуществления ядра сопроцессора при отключенном преобразователе входных/выходных данных форматом входных и выходных данных является float32.

В предпочтительном варианте осуществления ядра сопроцессора модуль управления соединен с шиной управления АНВ.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

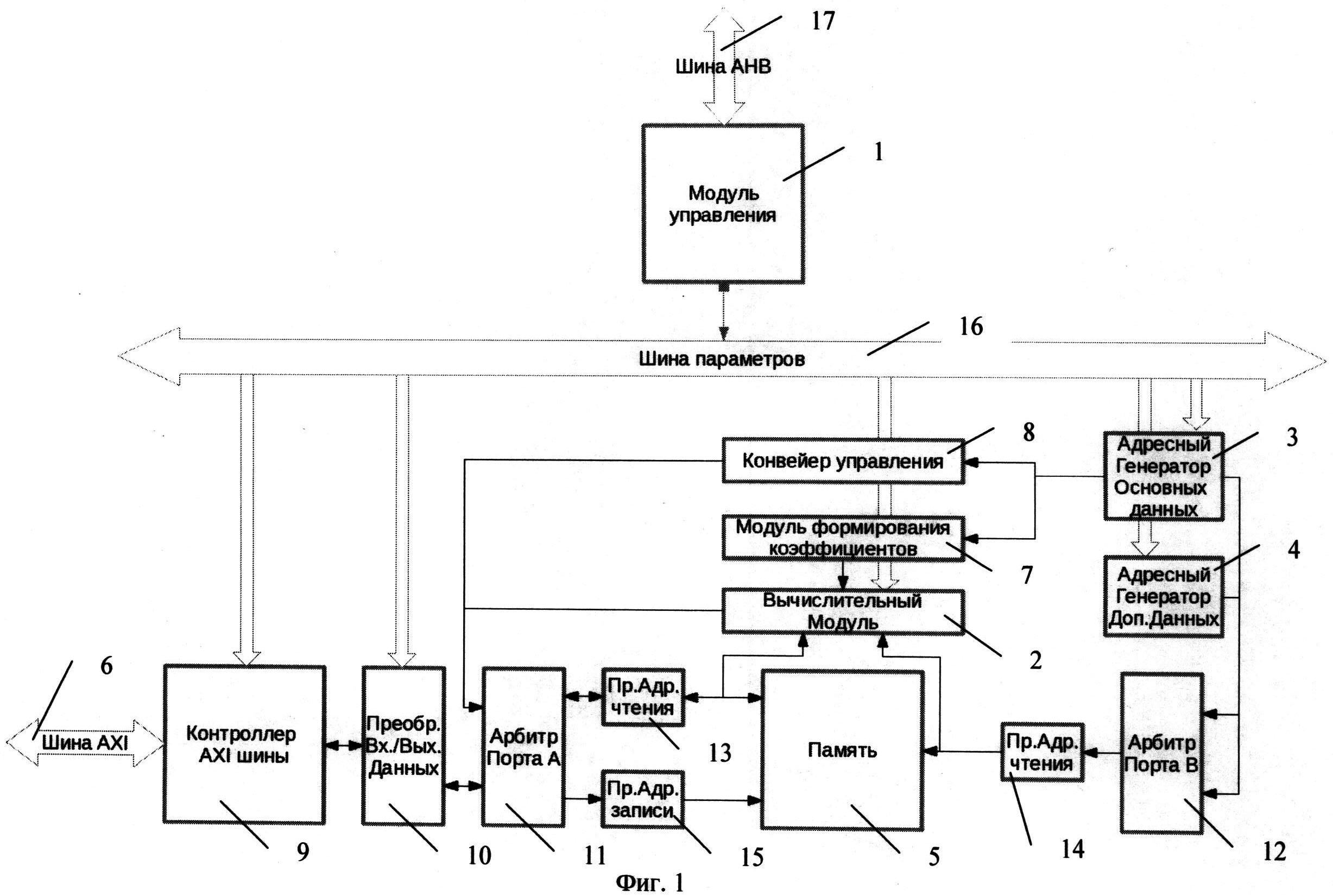

Фиг.1. Общая функциональная схема ядра сопроцессора быстрого преобразования Фурье реального времени согласно изобретению.

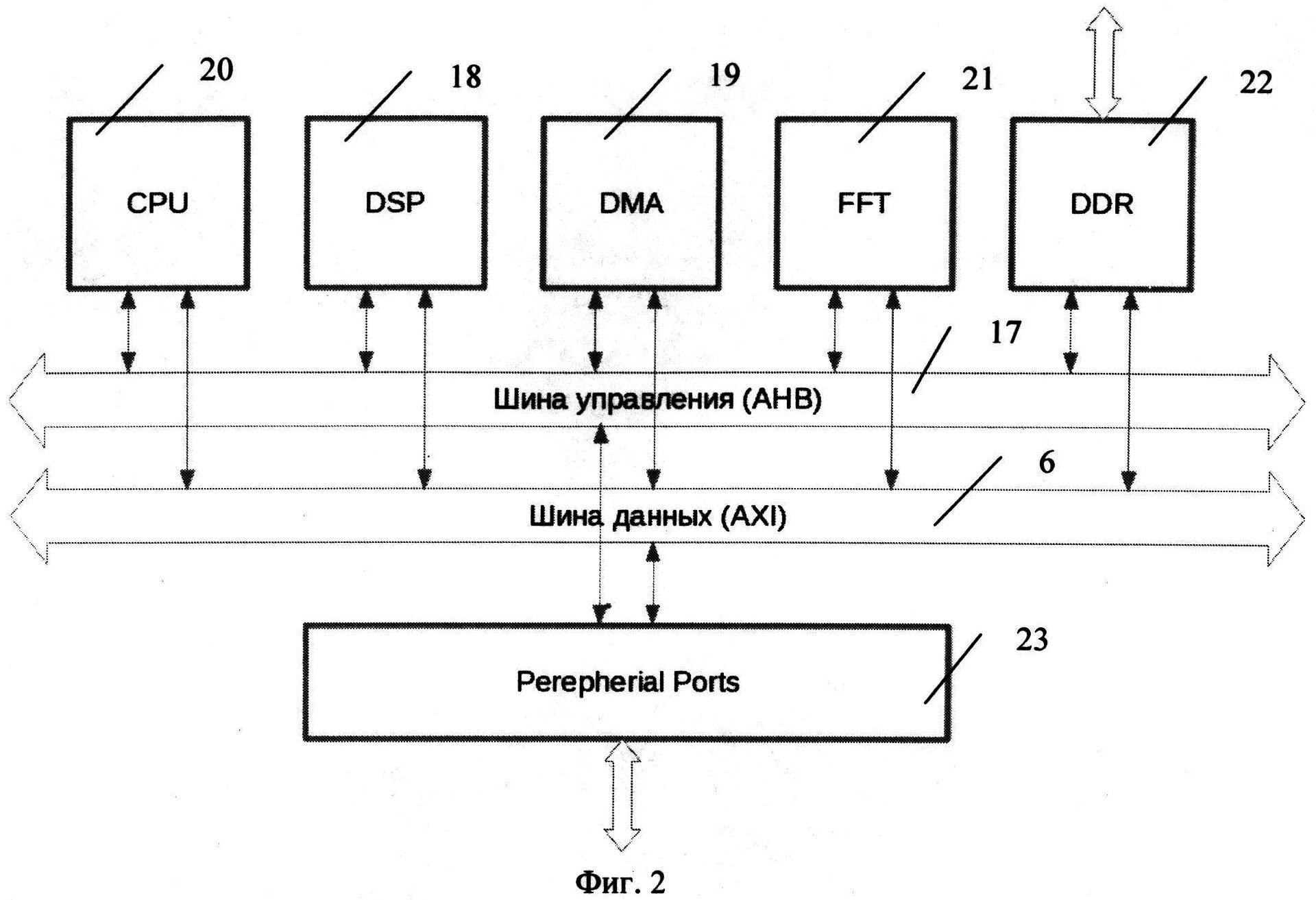

Фиг.2. Схема интеграции ядра сопроцессора быстрого преобразования Фурье реального времени в общую вычислительную систему согласно изобретению.

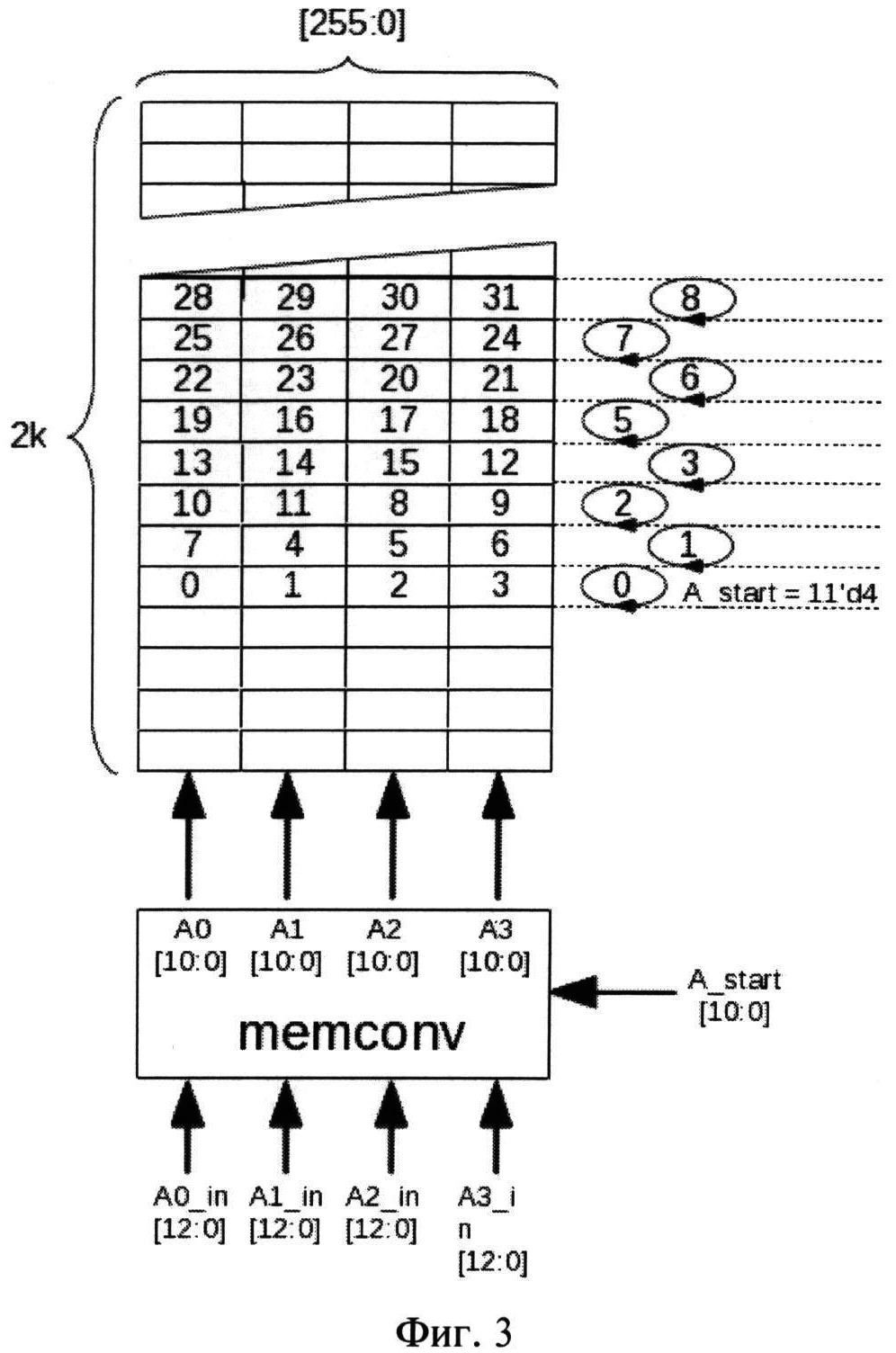

Фиг.3. Схема принципа работы преобразователя адреса в памяти ядра сопроцессора быстрого преобразования Фурье реального времени согласно изобретению.

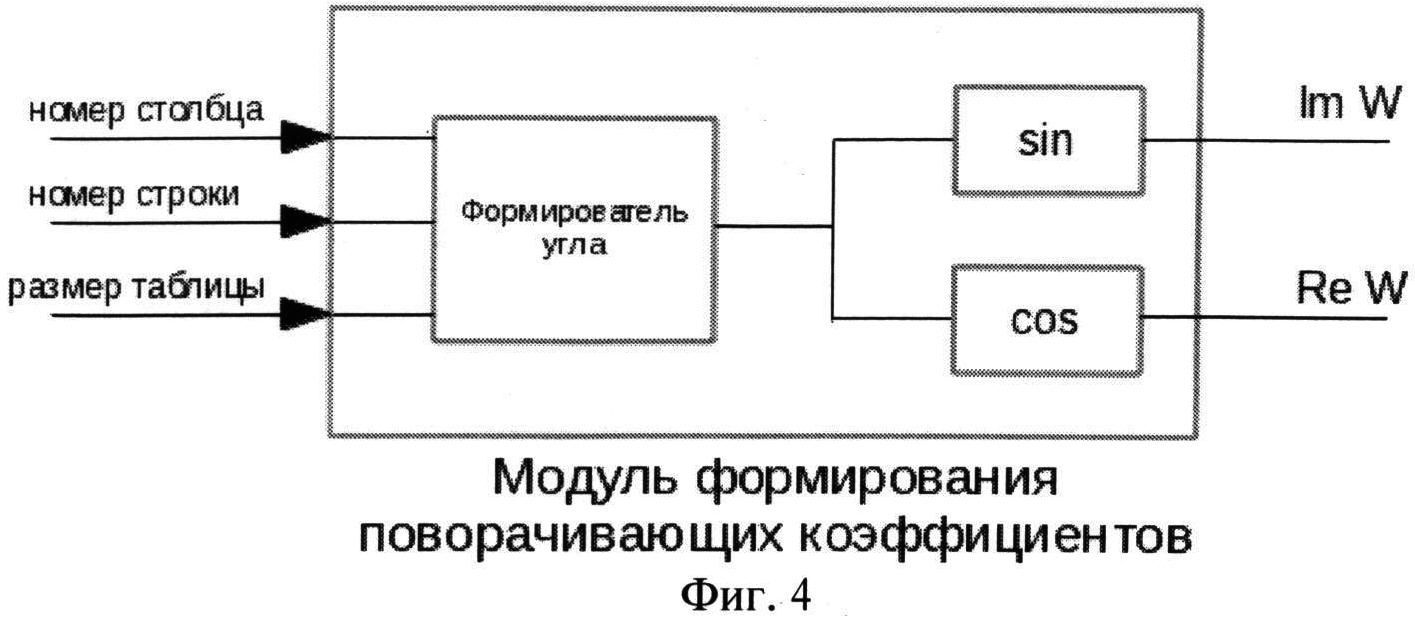

Фиг.4. Схема функционирования модуля формирования коэффициентов согласно изобретению.

Рассмотрим вариант выполнения заявленного изобретения, представленный на Фиг.1. Ядро сопроцессора быстрого преобразования Фурье реального времени содержит следующие элементы. Модуль управления 1, выполненный с возможностью непосредственного управления работой ядра сопроцессора посредством записи параметров вычислений и команд в регистры сопроцессора. Вычислительный модуль 2, выполненный с возможностью осуществления основных вычислений с предварительно загруженными в память сопроцессора данными. Адресный генератор 3 основных данных и адресный генератор 4 дополнительных данных, выполненные с возможностью формирования адреса для чтения из внутренней памяти 5 сопроцессора данных, необходимых для осуществления заданной операции, а также формирования адреса для записи в память результата вычислений. Память 5 сопроцессора, которая состоит из двух секций, что позволяет заявленному ядру сопроцессора работать в двухбуферном режиме: с одним буфером работает сопроцессор, с другим внешний контроллер прямого доступа в память (через AXI шину 6), выполненный с возможностью выгрузки результата и загрузки новых данных. Модуль 7 формирования коэффициентов, выполненный с возможностью расчета поворачивающих коэффициентов для быстрого преобразования Фурье, что позволяет сократить объем необходимой памяти для устройства, а также ускорить обработку больших массивов до 256 К отсчетов. Конвейер управления 8, выполненный с возможностью формирования управляющих сигналов для всех модулей обработки в соответствии с заданным алгоритмом обработки. Контроллер 9 AXI шины, выполненный с возможностью обеспечения доступа со стороны внешнего контроллера прямого доступа в память. Преобразователь 10 входных/выходных данных, выполненный с возможностью преобразования входных данных и выходных данных из одного формата в другой. Арбитр 11 порта А, выполненный с возможностью коммутации запросов на чтение/запись контроллера 9 AXI шины и на запись результата преобразования. Арбитр 12 порта В, выполненный с возможностью коммутации запросов на чтение основных и дополнительных данных для вычислительного модуля 2. Первый преобразователь 13 адреса чтения, второй преобразователь 14 адреса чтения и преобразователь 15 адреса записи, выполненные с возможностью конвертации адреса запроса на соответственно чтение/запись в зависимости от выбранного алгоритма, что позволяет сохранить высокий параллелизм исполнения обработки и ее осуществления без задействования дополнительной памяти результатов (результат вычисления сохраняется в том же месте что и входные данные).

Шина 16 параметров соединяет между собой модуль 1 управления, вычислительный модуль 2, адресный генератор 3 основных данных, адресный генератор 4 дополнительных данных, контроллер 9 AXI шины и преобразователь 10 входных/выходных данных. Модуль управления 1 соединен с шиной 17 управления АНВ. Контроллер 9 AXI шины соединен с AXI шиной 6 данных и с преобразователем 10 входных/выходных данных, который соединен с арбитром 11 порта А, выход которого соединен с входом преобразователя 15 адреса записи, выход которого соединен с входом памяти 5, которая соединена с первым преобразователем 13 адреса чтения, который соединен с арбитром 11 порта А, вход которого соединен с выходами конвейера управления 8 и вычислительного модуля 2, вход которого соединен с памятью 5 и преобразователем 15 адреса записи. Первый выход адресного генератора 3 основных данных соединен с входом конвейера управления 8 и с входом модуля 7 формирования коэффициентов, выход которого соединен с входом вычислительного модуля 2, а второй выход адресного генератора 3 основных данных соединен с первым входом арбитра 12 порта В. Выход адресного генератора 4 дополнительных данных соединен со вторым входом арбитра 12 порта В, выход которого соединен с входом второго преобразователя 14 адреса чтения, выход которого соединен с входом памяти 5.

Данные, подлежащие обработке, загружают в заявленное ядро сопроцессора в прямом порядке. Результаты обработки выгружают также в прямом порядке. Действительным компонентам соответствуют нечетные адреса памяти, квадратурным (мнимым) - четные. Размер памяти 5 заявленного ядра сопроцессора составляет 16k×64 разрядных слов.

Память 5 может использоваться в двухбуферном режиме, граница буферов соответствует середине памяти. Двухбуферный режим предназначен для непрерывного выполнения преобразований в реальном времени. Он позволяет внешним устройствам (Фиг.2), например DSP - процессору 18 (процессору цифровой обработки сигнала), DMA - каналу 19 (каналу прямого доступа в память), RISC - ядру CPU 20 (процессора общего назначения с сокращенным набором команд) параллельно с текущим преобразованием данных одного буфера памяти 5 заявленного ядра 21 сопроцессора работать с другим буфером памяти 5, например выгрузить результаты предыдущего преобразования во внешнюю память с помощью контроллера DDR 22, загрузить данные для последующего преобразования, например через периферийные порты 23 (Perepherial Ports). Максимальный размер преобразования в двухбуферном режиме равен 8192 К.

При неработающем заявленном ядре сопроцессора вся его память 5 доступна внешним устройствам.

Тригонометрические коэффициенты формируют во встроенных блоках заявленного ядра сопроцессора. Они обеспечивают как фазовые повороты выполняемого преобразования Фурье, так и матричные фазовые повороты для матричного наращивания размера преобразования. Предельный размер наращиваемого преобразования составляет 256 К.

Заявленное ядро сопроцессора обеспечивает следующую производительность: за один такт выполняются максимально 40 арифметических операций с плавающей точкой (24 сложения/вычитания и 16 умножений). Например, при тактовой частоте 160 МГц производительность заявленного ядра сопроцессора составит 6400 Мфлоп/с.

Рассмотрим процесс функционирования описанного выше варианта выполнения заявленного ядра сопроцессора быстрого преобразования Фурье реального времени (Фиг.1). Изначально пользователь устанавливает исходные параметры заявленного ядра сопроцессора, в соответствии с поставленной задачей. При этом задают такие параметры как: тип преобразования, размер преобразования, количество массивов, адрес первого массива и т.д. После этого заявленное ядро сопроцессора запускают на исполнение путем записи команды в регистр памяти 5. Также посредством пользователя загружают все необходимые для вычислений данные в память 5 сопроцессора.

После запуска заявленного ядра сопроцессора адресный генератор 3 основных данных и адресный генератор 4 дополнительных данных (в зависимости от задачи) формируют адреса на чтение входных и запись выходных данных в память 5. При исполнении различных алгоритмов, а также при одновременной работе заявленного ядра сопроцессора и внешнего контроллера прямого доступа в память 5 через контроллер 9 АХI шины могут возникнуть конфликтные ситуации при обращении к памяти 5. Чтобы не нарушить ход вычислений, приоритет отдают заявленному ядру сопроцессора. Арбитр 11 порта А осуществляет коммутацию запросов между первым и вторым буфером памяти 5, а также арбитраж конфликтных ситуаций. Далее запрос поступает в блок преобразования адреса (13, 14, 15 в зависимости от типа запроса), который производит конвертацию адреса в соответствии с выбранным алгоритмом. После чего запрос поступает в память 5.

Так как чтение из памяти занимает определенное количество циклов тактовой частоты, в соответствии с каждым адресом в конвейер управления 8 поступают параметры. В частности в конвейер управления 8 поступают генерируемые параметры для модуля 7 формирования коэффициентов, которые на определенном цикле ввода данных в конвейер управления 8 осуществляют запуск модуля 7 формирования коэффициентов.

Данные из памяти 5 поступают в вычислительный модуль 2, который также представляет собой конвейерную структуру. В тот момент, когда данные должны перемножаться с коэффициентами или дополнительными данными, они поступают на вход вычислительного модуля 2.

Во время прохождения данных по конвейеру вычислительного модуля 2, по конвейеру управления 8 проходят параметры, адрес записи результата и сигнал валидности данных. В тот момент, когда эти значения выходят из блока конвейера управления 8, на выходе вычислительного модуля 2 появляется результат вычислений, соответствующий данным параметрам.

Далее результат записывают в память 5. Таким образом, в зависимости от поставленной задачи обрабатывают заданный массив данных. После окончания работы в регистре заявленного ядра сопроцессора выставляют сигнал готовности данных к выгрузке во внешнюю память и готовности устройства обрабатывать следующий массив.

Заявленное ядро сопроцессора быстрого преобразования Фурье реального времени имеет возможность выполнять следующие сопутствующие операции: обратное быстрое преобразование Фурье; нормировка результатов преобразования; фазовые матричные повороты результатов преобразования; расчет мощностей результатов преобразования; одновременное преобразование М=2m комплексных массивов; поэлементное перемножение (с сопряжением) двух комплексных массивов; быстрая БПФ - свертка (ковариация); вычисление скалярного произведения комплексных массивов.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.