Результат интеллектуальной деятельности: РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

Вид РИД

Изобретение

Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении надежных вычислительно-управляющих систем.

Известна устойчивая к отказам вычислительная система [1] (аналог). Вычислительная система состоит из двух процессоров (каналов), схемы начальной установки, подключенной к входу процессора каждого канала, системного генератора, выход которого подключен к входу процессора каждого канала и схемы управления. Каждый процессор может работать в режиме главного процессора и в режиме подчиненного процессора, контролирующего работу другого процессора. В подчиненном режиме процессор выполняет те же инструкции, что и главный процессор, только все линии, по которым осуществляется вывод данных, отключены. Кроме того, в подчиненном режиме схема сравнения, встроенная в процессор, сверяет результаты выходных данных обоих процессоров. Схема управления через определенные интервалы времени осуществляет переключение режимов работы процессоров для контроля процессорами друг друга. Если возникает несоответствие, то подчиненный процессор сигнализирует схеме управления об ошибке. Схема управления пытается восстановить синхронность работы процессоров, вызывая в обоих процессорах внешнее прерывание. Если же процессор вышел из строя и был в это время подчиненным процессором, то в таком случае схема будет работать без подчиненного процессора в течение времени, равного периоду переключения режимов работы процессоров. Затем неисправный процессор будет переведен в режим главного, а исправный - в режим подчиненного, где неисправность главного процессора уже будет обнаружена.

Недостаток системы в том, что при отказе системного генератора, который является общим для двух процессоров, отказывает вся система. В случае использования отдельных генераторов возникнет несинхронность в работе процессоров, которая также может наступить при неодновременном поступлении входных данных от приемных устройств.

Кроме того, основной недостаток системы заключается в том, что подчиненный процессор только контролирует работоспособность главного и не выполняет его функции в случае отказа.

Известно вычислительное устройство смешанного резервирования [2] (аналог). Устройство смешанного резервирования состоит из двух включенных вычислительных каналов и одного выключенного, находящегося в холодном резерве. При отказе в одном из работающих каналов автоматически включается третий канал, находившийся в холодном резерве, и сигналы трех каналов мажоритируются. При отказе двух работающих каналов включается третий канал, находящийся в холодном резерве, который формирует выходной сигнал.

Недостаток устройства смешанного резервирования заключается в том, что в условиях несанкционированных воздействий (электромагнитные наводки, электрический разряд, радиационные воздействия) сбой может произойти одновременно в двух работающих каналах и в результате мажоритирования может сформироваться несанкционированный сигнал. В случае отказа двух работающих каналов и подключении третьего, находившегося в холодном резерве, формирование выходного сигнала происходит без мажоритации.

Известна резервированная двухпроцессорная вычислительная система [3] (прототип), содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу первого коммутатора; системный генератор, выход которого подключен к первому входу процессора; триггер, выход которого подключен к первому входу элемента ИЛИ-НЕ, выход которого подключен ко второму входу первого коммутатора; импульсный генератор, подключенный через временной анализатор исправности к первому входу триггера и первому входу счетчика сбоев, первый выход которого подключен ко второму входу элемента ИЛИ-НЕ; схему начальной установки, выход которой подключен ко второму входу процессора, второму входу счетчика сбоев, первому входу элемента ИЛИ, причем выходы элемента ИЛИ подключены ко второму входу временного анализатора исправности и второму входу триггера; схему сравнения, первый вход которой подключен ко второму выходу счетчика сбоев первого канала, второй вход - ко второму выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, а второй - к третьему входу элемента ИЛИ-НЕ второго канала; устройство аварийного запуска, первый вход которого подключен к выходу схемы начальной установки, второй вход подключен ко второму выходу процессора, а выходы - к второму входу импульсного генератора и второму входу элемента ИЛИ; второй и третий коммутаторы и устройство памяти, при этом первый вход второго коммутатора первого канала подключен к третьему выходу процессора первого канала, четвертый выход которого подключен к первому входу третьего коммутатора второго канала, выход первого коммутатора первого канала подключен ко второму входу третьего коммутатора второго канала, второму входу второго коммутатора первого канала и является выходом первого канала системы; выход второго коммутатора первого канала подключен к выходу третьего коммутатора первого канала и входу устройства памяти первого канала; первый вход второго коммутатора второго канала подключен к третьему выходу процессора второго канала, четвертый выход которого подключен к первому входу третьего коммутатора первого канала; выход первого коммутатора второго канала подключен ко второму входу второго коммутатора второго канала, второму входу третьего коммутатора первого канала и является выходом второго канала системы; выход второго коммутатора второго канала подключен к выходу третьего коммутатора второго канала и входу устройства памяти второго канала.

В известной резервированной двухпроцессорной вычислительной системе [3], после поступления сигнала RES от схемы начальной установки, все устройства системы устанавливаются в исходное состояние и к выходу подключается процессор первого канала, а второй канал отключается коммутатором. В каждом канале совместно с основной задачей периодически в фиксированные интервалы времени решается диагностическая задача (осуществляется самодиагностика работоспособности устройств системы). В случае успешного выполнения диагностики формируются короткие импульсы исправности TestOK, которые обнуляют (устанавливают в исходное состояние) временной анализатор исправности. При этом сигналы с импульсного генератора на счетчик сбоев не поступят. В случае отсутствия сигналов TestOK (отказа в работе канала) счетчик сбоев будет заполняться сигналами импульсного генератора. Схема сравнения, анализируя коды счетчиков сбоев, формирует сигналы, которые поступают на коммутаторы. При этом подключается к выходу работоспособный процессор (канал), и отключается вышедший из строя. Промежуточные результаты вычислений периодически записываются в устройства памяти обоих каналов. Второй канал, являющийся резервным, в случае выхода из строя основного, начинает выполнение задачи, используя информацию, записанную в устройство памяти резервного канала. Это позволяет продолжить решение задачи без потери информации. При работоспособных каналах, в случае многократных сбоев, переключение осуществляется на тот канал, в котором меньше сбоев. Принятие решения на переключение возлагается на устройство резервирования, которое реализовано на логических элементах в составе базового матричного кристалла, обладающего высокой надежностью, и происходит после поступления с импульсного генератора на временной анализатор исправности не менее двух импульсов.

Известная резервированная двухпроцессорная вычислительная система [3] обладает повышенной надежностью, минимальным временем переключения на резервный канал и сохраняет работоспособность при коротком замыкании на выходе одного из каналов.

Недостаток системы [3] заключается в том, что в системе, в случае отказа одного канала, отсутствует возможность уменьшения вероятности ложной выдачи результата вычислений (команды), так как выдача результата осуществляется на основе вычислений только одного канала.

Технический результат - повышение надежности, отказоустойчивости и достоверности результата вычислений за счет введения в систему третьего канала и дополнительных устройств и связей.

Технический результат достигается тем, что в резервированную двухпроцессорную вычислительную систему, содержащую два идентичных канала, введены третий канал, элемент ИЛИ и устройство формирования сигналов выборки канала. В каждом канале первый выход процессора подключен к первому входу первого коммутатора. К первому входу процессора подключен системный генератор. Импульсный генератор подключен к временному анализатору исправности. Выход схемы начальной установки подключен к первому входу импульсного генератора, первому входу устройства аварийного запуска, ко второму входу процессора и первому входу элемента ИЛИ. Выход элемента ИЛИ подключен ко второму входу временного анализатора исправности. Второй выход процессора подключен ко второму входу устройства аварийного запуска. Первый выход устройства аварийного запуска подключен ко второму входу импульсного генератора, а второй выход - ко второму входу элемента ИЛИ. Первый вход второго коммутатора подключен к третьему выходу процессора. Выход первого коммутатора подключен ко второму входу второго коммутатора и является выходом соответствующего канала. Выходы второго и третьего коммутаторов соединены и подключены к входу устройства памяти. Четвертый выход процессора первого канала подключен к первому входу третьего коммутатора второго канала, а четвертый выход процессора второго канала подключен к первому входу третьего коммутатора первого канала. Выход первого коммутатора первого канала подключен ко второму входу третьего коммутатора второго канала, а выход первого коммутатора второго канала подключен ко второму входу третьего коммутатора первого канала. Дополнительно в каждый канал введен четвертый коммутатор, выход которого соединен с выходами второго и третьего коммутаторов и с входом устройства памяти соответствующего канала. Выход временного анализатора исправности первого, второго и третьего каналов подключены соответственно к первому, второму и третьему входам введенного элемента ИЛИ, выход которого подключен к первому входу устройства формирования сигналов выборки канала. Вторые выходы процессоров первого, второго и третьего каналов подключены соответственно к второму, третьему и четвертому входам устройства формирования сигналов выборки. Первый, второй и третий выходы устройства формирования сигналов выборки канала подключены ко вторым входам первых коммутаторов соответствующих каналов и являются управляющими выходами для подключения напряжения питания на соответствующие каналы от источников вторичного питания. Пятый выход процессора первого канала подключен к первому входу четвертого коммутатора третьего канала. Пятый выход процессора второго канала подключен к первому входу третьего коммутатора третьего канала. Третий выход процессора третьего канала подключен к первому входу второго коммутатора третьего канала. Четвертый выход процессора третьего канала подключен к первому входу четвертого коммутатора первого канала. Пятый выход процессора третьего канала подключен к первому входу четвертого коммутатора второго канала. Выход первого коммутатора первого канала дополнительно подключен ко второму входу четвертого коммутатора третьего канала. Выход первого коммутатора второго канала дополнительно подключен ко второму входу третьего коммутатора третьего канала. Выход первого коммутатора третьего канала дополнительно подключен ко второму входу четвертого коммутатора второго канала, второму входу четвертого коммутатора первого канала и является выходом третьего канала.

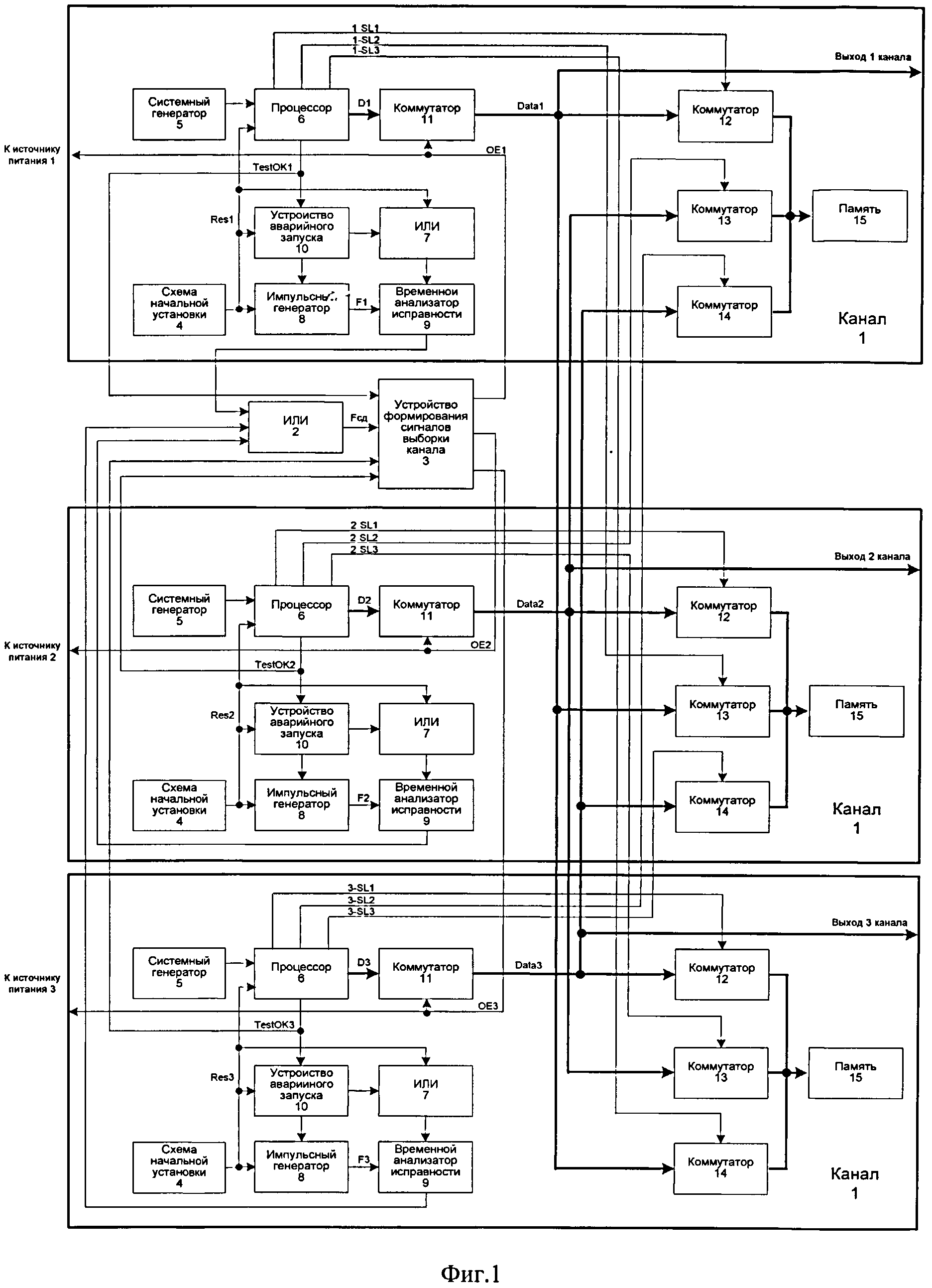

На фиг.1 приведена структурная схема предлагаемой многоканальной системы.

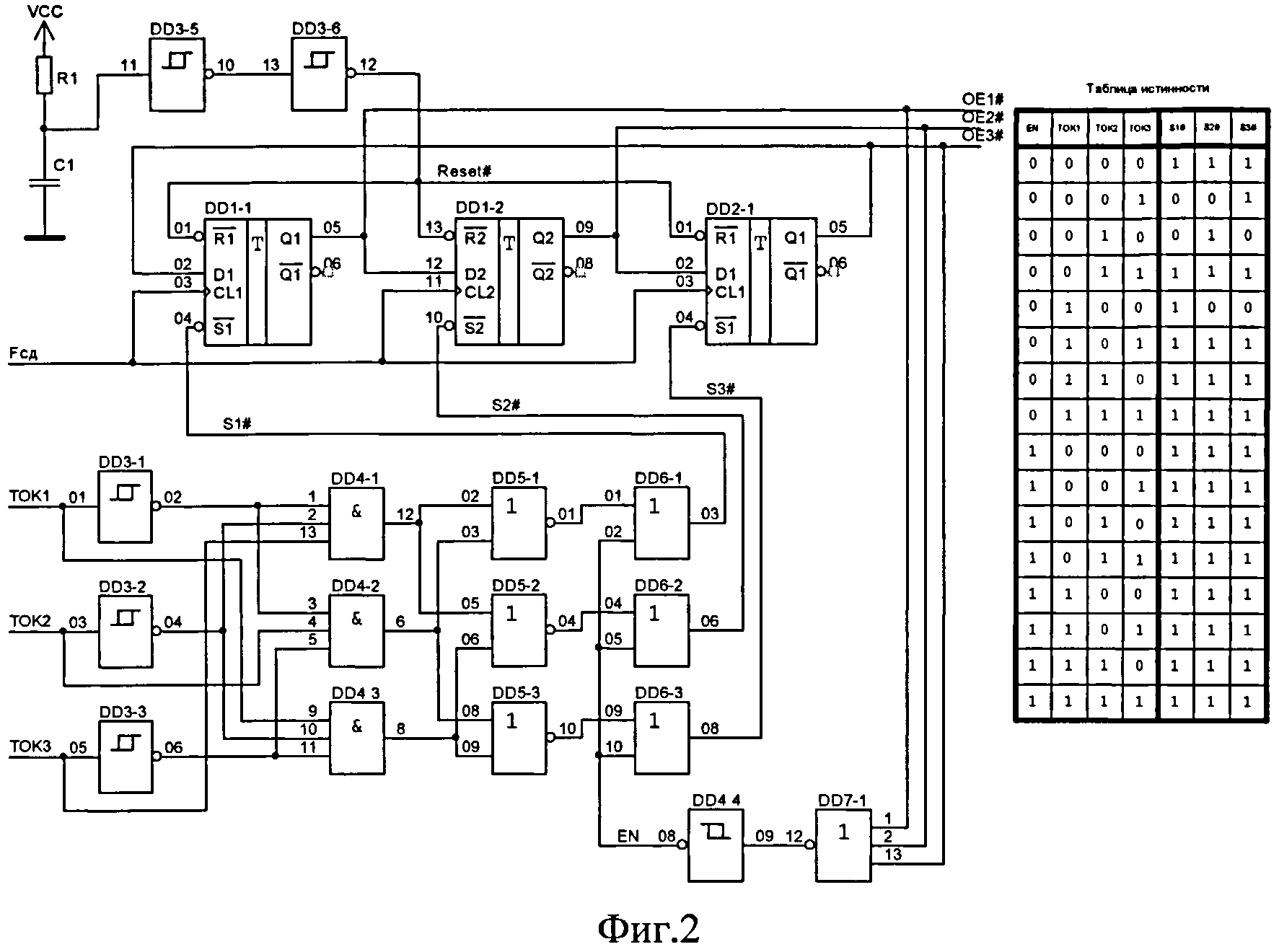

На фиг.2 приведен вариант реализации устройства формирования сигналов выборки канала.

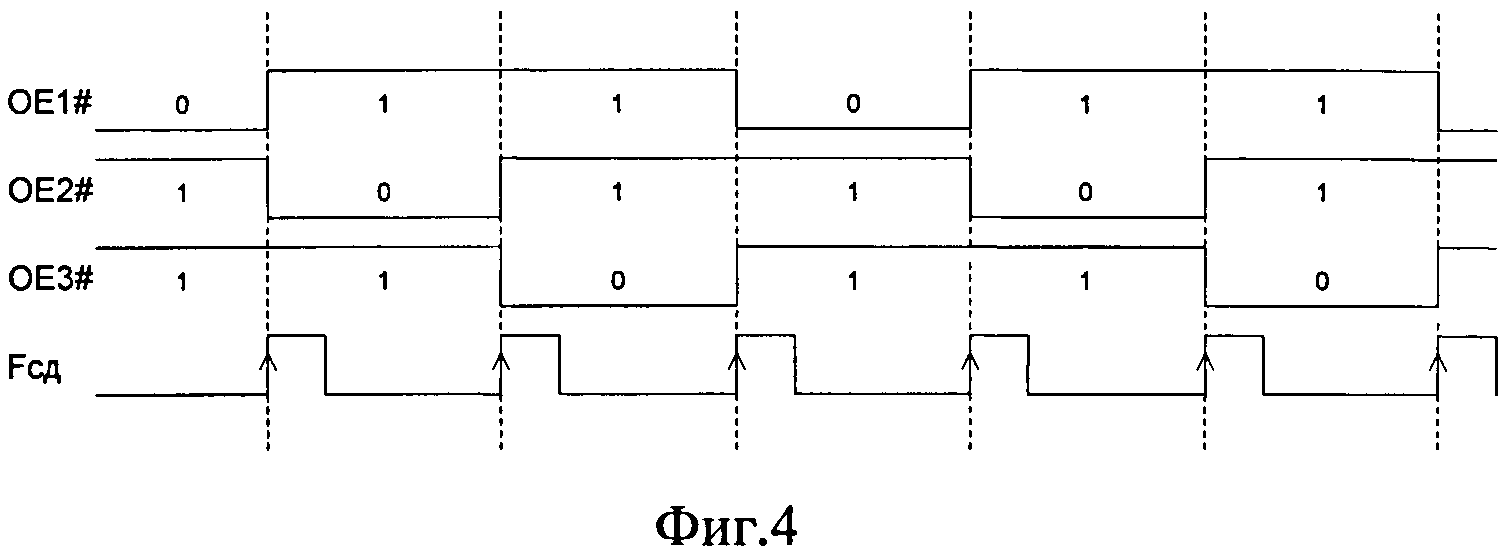

На фиг.3 приведена временная диаграмма работы устройства формирования сигналов выборки канала.

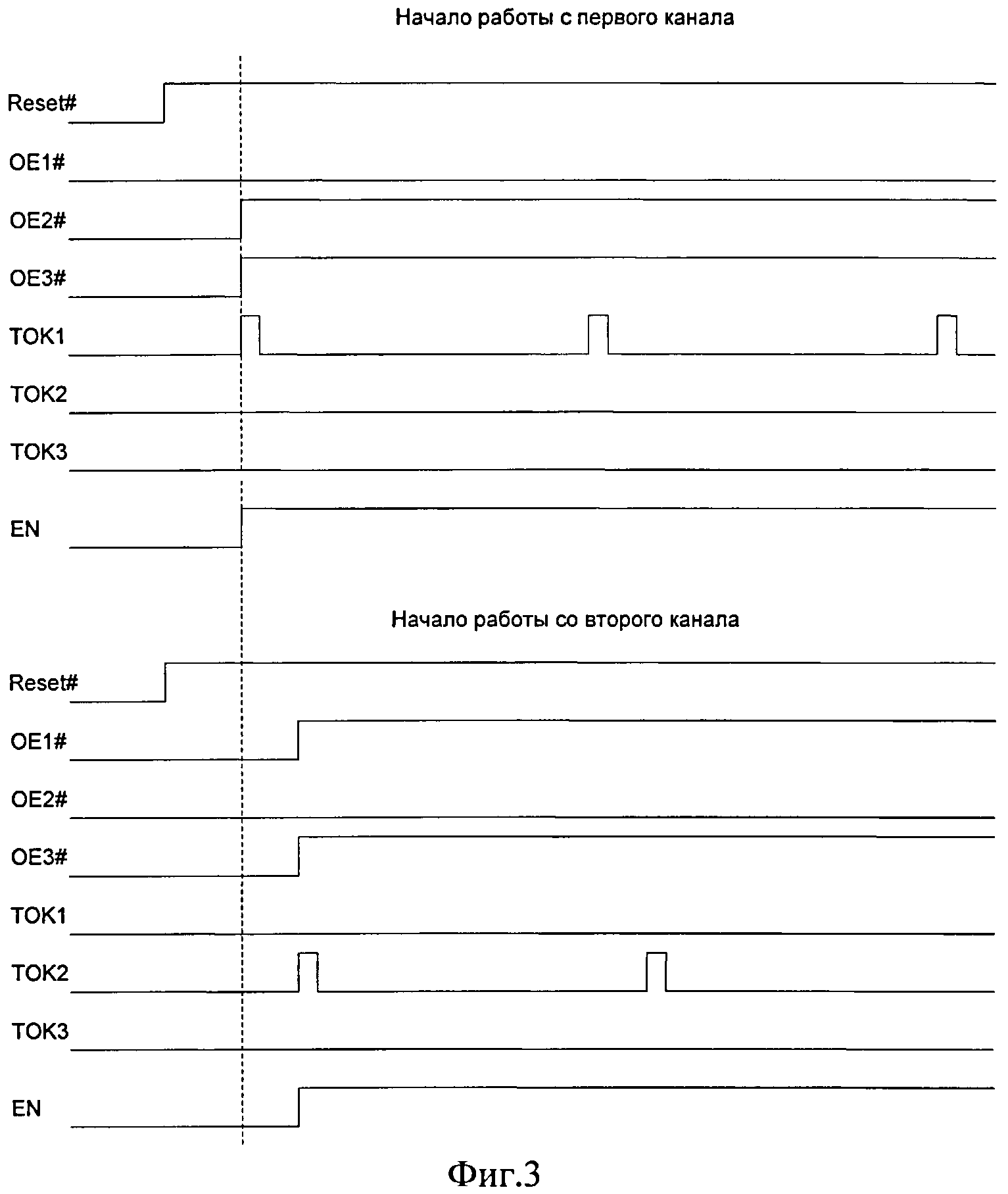

На фиг.4 приведена временная диаграмма работы многоканальной системы.

Резервированная многоканальная вычислительная система, представленная на фиг.1, содержит три идентичных канала 1, элемент ИЛИ 2, устройство формирования сигналов выборки канала 3. Каждый канал содержит схему начальной установки 4, системный генератор 5, процессор 6, элемент ИЛИ 7, импульсный генератор 8, временной анализатор исправности 9, устройство аварийного запуска 10, первый коммутатор 11, второй коммутатор 12, третий коммутатор 13, четвертый коммутатор 14, устройство памяти 15. Выходы коммутаторов 12, 13, 14 соединены и подключены к устройству памяти 15. Импульсный генератор 8 подключен к схеме начальной установки 4, временному анализатору исправности 9, устройству аварийного запуска 10, которое подключено к схеме начальной установки 4, процессору 6, элементу ИЛИ 7, соединенному со схемой начальной установки 4, процессором 6 и временным анализатором исправности 9. Процессор 6 соединен с системным генератором 5, первым коммутатором 11, вторым коммутатором 12. В системе, кроме того, процессор 6 первого канала соединен с третьим коммутатором 13 второго канала и четвертым коммутатором 14 третьего канала; процессор 6 второго канала соединен со вторым коммутатором 12 второго канала и с третьими коммутаторами 13 первого и третьего каналов; процессор 6 третьего канала соединен со вторым коммутатором 12 третьего канала и четвертыми коммутаторами 14 первого и второго каналов; временные анализаторы 9 каждого канала подключены к элементу ИЛИ 2, который соединен с устройством формирования сигналов выборки канала 3, которое соединено с первыми коммутаторами 11 первого, второго и третьего каналов и управляющими выходами для подключения напряжения питания на каждый из каналов от источников вторичного питания каждого канала. Кроме того, устройство формирования сигналов выборки канала 3 соединено с процессорами 6 каждого канала. Выход первого коммутатора 11 каждого канала подключен ко второму коммутатору 12 и является выходом соответствующего канала. Выход первого коммутатора 11 первого канала подключен к третьему коммутатору 13 второго канала и к четвертому коммутатору 14 третьего канала. Выход первого коммутатора 11 второго канала подключен к третьим коммутаторам 13 первого и третьего каналов. Выход первого коммутатора 11 третьего канала подключен к четвертым коммутаторам 14 первого и второго каналов.

Источник питания каждого канала содержит в своем составе управляемые и неуправляемые преобразователи напряжения. Управляемые преобразователи позволяют с помощью сигналов ОЕ от устройства формирования сигналов выборки канала 3 отключать или подключать напряжения питания канала (системный генератор 5, процессор 6, коммутатор 11, схема начальной установки 4, устройство аварийного запуска 10, импульсный генератор 8, элемент ИЛИ 7, временной анализатор исправности 9). Неуправляемые преобразователи необходимы для подачи напряжения питания на устройства, которые не допускают по своему функциональному назначению снятие напряжения в процессе функционирования (элемент ИЛИ 2, устройство формирования сигналов выборки канала 3, коммутаторы 12-14, память 15). Неуправляемые преобразователи каждого канала объединены по выходам через развязывающие диоды.

В момент подачи напряжения на систему схема начальной установки 4 формирует сигнал Res# (изменение состояния из логического нуля в логическую единицу). При этом разрешается работа процессорам 6, устройствам аварийного запуска 10, импульсным генераторам 8, временным анализаторам исправности 9, а устройство формирования сигналов выборки канала 3 устанавливает сигналы ОЕ в состояние, при котором на все каналы подается напряжение питания от вторичных источников. Время выхода на режим процессоров каналов за счет выбора задержки разнесено. В этом случае тот процессор, который первым выйдет на режим и сформирует сигнал исправности TestOK, при помощи устройства формирования сигналов выборки канала 3 оставит напряжение питания на своем канале и отключит снимаемые напряжения питания от двух других (фиг.3). Таким образом, данный канал перейдет в рабочий режим, а два других будут в холодном резерве. При отказе в работающем канале (отсутствии импульсов TestOK) временной анализатор 9 сформирует импульс Fсд, который поступит на устройство формирования сигналов выборки канала 3. При этом устройство 3 подключит питание к следующему каналу и отключит питание от двух других (фиг.4). Следует отметить, что в случае отказа канала, на который произошло переключение, аналогично подключится следующий канал и отключатся два других. Особенностью предлагаемой системы является то, что импульсы TestOK можно прерывать программно, что позволит с требуемой периодичностью выбирать работающие каналы. Количество переключений между каналами не ограничено.

Промежуточные результаты вычислений периодически записываются в устройства памяти всех каналов. Это позволяет продолжить решение задачи на резервном канале без потери информации.

Следует отметить, что если в резервированной многоканальной вычислительной системе в качестве памяти каналов использовать трехпортовые ОЗУ, то можно упростить систему за счет исключения связей устройств памяти с процессорами. Если использовать энергонезависимую память и подключать ее по команде от процессора, то можно снизить энергопотребление и дополнительно повысить надежность системы.

Принципиальное отличие предлагаемой резервированной многоканальной процессорной системы, представленной на фиг.1, от прототипа заключается во введении третьего канала 1, элемента ИЛИ 2, устройства формирования сигналов выборки канала 3, введении в каждый канал дополнительных коммутаторов 14 и введении дополнительных связей, что позволило повысить надежность и отказоустойчивость системы и снизить вероятность выдачи ложного результата вычислений (ложных команд). Для получения достоверного результата в системе можно осуществляется программное переключение по каналам, а результаты решений задач каждого канала, сохраненные в памяти каналов, сравнивать, анализировать и выдавать по любому из трех независимых каналов.

Предложенная система возможно не будет иметь недостатков для особо ответственных применений. Ограничением может быть только время выхода на рабочий режим подключаемого канала. При использовании быстродействующих процессоров, например, типа 1892ВМ8Я (АЕЯР.431280.767 ТУ) время переключения может быть сведено к минимуму.

Вновь введенные коммутаторы могут быть реализованы на микросхемах приемопередатчиков типа 5584АП7Т со схемой удержания информации на входе. Вновь введенные устройства памяти могут быть реализованы на оперативно запоминающих устройствах (СОЗУ) типа 1658РУ1У, обладающих требуемыми объемом памяти, быстродействием. Логический элемент ИЛИ и схема формирования сигналов выборки каналов могут быть реализованы на микросхемах серии 1594Т (1594ЛИ3Т, 1594ЛЕ4Т, 1594ТЛ2Т, 1594ТМ2Т), либо на логических элементах в составе базового матричного кристалла.

Список источников

1. Патент 94296302, США, МКИ G06F 11/00, 1994 г. (аналог).

3. Патент №2339994, РФ, МКИ G06F 11/18, 2006 г. (аналог).

3. Патент №2460121, РФ, МКИ G06F 11/20, 2012 г. (прототип).

Резервированная многоканальная вычислительная система, содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу первого коммутатора; системный генератор, выход которого подключен к первому входу процессора; импульсный генератор, подключенный к временному анализатору исправности; схема начальной установки, выход которой подключен к первому входу импульсного генератора, первому входу устройства аварийного запуска, ко второму входу процессора, первому входу элемента ИЛИ, выход которого подключен ко второму входу временного анализатора исправности; второй выход процессора подключен ко второму входу устройства аварийного запуска, первый выход которого подключен ко второму входу импульсного генератора, а второй выход - ко второму входу элемента ИЛИ; первый вход второго коммутатора подключен к третьему выходу процессора, выход первого коммутатора подключен ко второму входу второго коммутатора и является выходом соответствующего канала; выходы второго и третьего коммутаторов соединены и подключены к входу устройства памяти; четвертый выход процессора первого канала подключен к первому входу третьего коммутатора второго канала, четвертый выход процессора второго канала подключен к первому входу третьего коммутатора первого канала; выход первого коммутатора первого канала подключен ко второму входу третьего коммутатора второго канала, выход первого коммутатора второго канала подключен ко второму входу третьего коммутатора первого канала; отличающаяся тем, что в систему введены третий канал, элемент ИЛИ и устройство формирования сигналов выборки канала, а в каждый канал введен четвертый коммутатор, выход которого соединен с выходами второго и третьего коммутаторов и с входом устройства памяти соответствующего канала; выход временного анализатора исправности первого, второго и третьего каналов подключены соответственно к первому, второму и третьему входам введенного элемента ИЛИ, выход которого подключен к первому входу устройства формирования сигналов выборки канала; вторые выходы процессоров первого, второго и третьего каналов подключены соответственно к второму, третьему и четвертому входам устройства формирования сигналов выборки; первый, второй и третий выходы устройства формирования сигналов выборки канала подключены к вторым входам первых коммутаторов соответствующих каналов и являются управляющими выходами для подключения напряжения питания на соответствующие каналы от источников вторичного питания; пятый выход процессора первого канала подключен к первому входу четвертого коммутатора третьего канала, пятый выход процессора второго канала подключен к первому входу третьего коммутатора третьего канала, третий выход процессора третьего канала подключен к первому входу второго коммутатора третьего канала; четвертый выход процессора третьего канала подключен к первому входу четвертого коммутатора первого канала; пятый выход процессора третьего канала подключен к первому входу четвертого коммутатора второго канала; выход первого коммутатора первого канала дополнительно подключен ко второму входу четвертого коммутатора третьего канала; выход первого коммутатора второго канала дополнительно подключен ко второму входу третьего коммутатора третьего канала; выход первого коммутатора третьего канала дополнительно подключен ко второму входу четвертого коммутатора второго канала, второму входу четвертого коммутатора первого канала и является выходом третьего канала.