Результат интеллектуальной деятельности: КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических устройств.

Известно каскадное логическое устройство (Патент США №6211704, FIG.7, Н(А)03К 19/096, НКИ 326/121 от 03.04.2001). Это устройство содержит в каждом каскаде два инвертора с обратными связями, логический блок в виде ключевых цепей, выполненных на последовательно соединенных транзисторах n-типа, два входных и выходной инверторы, элемент контроля на двух транзисторах n-типа и транзисторе p-типа, а также тактовый и ключевой транзисторы n-типа. Недостаток этого устройства - его избыточная сложность, когда для реализации необходимо 4 входных и 4 выходных управляющих сигнала и 15 МДП транзисторов, помимо логических.

Наиболее близким техническим решением к предлагаемому является каскадное парафазное логическое устройство (Патент РФ №2349028, Н03К 19/0948 от 10.03.2009). Устройство содержит в каждом каскаде входной и выходной тактирующие элементы, два транзистора сброса n-типа, два КМДП инвертора, включенных по схеме триггера, и логический блок, содержащий, по меньшей мере, две ключевые цепи, выполненные каждая из последовательно соединенных транзисторов n-типа. Недостатком устройства является ограниченное быстродействие, что обусловлено распространением сигнала с тремя временными задержками соответственно в входном и выходном тактирующих элементах и в логической триггерной части.

Техническим результатом изобретения является повышение быстродействия устройства.

Технический результат достигается тем, что каскадное парафазное логическое устройство, содержащее тактовый КМДП инвертор и в каждом каскаде первый и второй транзисторы сброса n-типа, первый и второй КМДП инверторы, включенные между соответствующими клеммами питания и шиной земли, и логический блок, содержащий по меньшей мере две ключевые цепи, выполненные каждая из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам каскада таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы ключевых цепей подключены к шине земли, а вторые являются соответственно прямым и инверсным выходами каскада, которые подключены к одному из парафазных логических входов последующего каскада, прямой выход каскада соединен с выходом первого и с входом второго КМДП инверторов, а инверсный выход каскада соединен с выходом второго и с входом первого КМДП инверторов, первый и второй транзисторы сброса n-типа включены между шиной земли и соответственно прямым и инверсным выходами каскада, вход тактового КМДП инвертора и затворы транзисторов сброса n-типа в первом каскаде подключены к тактовой шине, клемма питания в первом каскаде подключена к выходу тактового КМДП инвертора, который включен между шиной питания и шиной земли, а также содержит в каждом каскаде элемент задержки, содержащий первый и второй инвертирующие элементы, каждый из которых содержит транзистор p-типа и транзистор n-типа, которые включены последовательно между шиной питания и шиной земли, затворы транзисторов p- и n-типа первого инвертирующего элемента соединены соответственно с выходом тактового КМДП инвертора и с клеммой питания данного каскада, затвор транзистора n-типа второго инвертирующего элемента подключен к тактовой шине, точка соединения транзисторов p- и n-типов первого инвертирующего элемента подключена к затвору транзистора p-типа второго инвертирующего элемента, точка соединения транзисторов p- и n-типов второго инвертирующего элемента является выходом элемента задержки и подключена к клемме питания последующего каскада, затворы транзисторов сброса n-типа во втором и последующих каскадах также подключены к тактовой шине.

Существенными отличительными признаками в указанной совокупности признаков является наличие в каждом каскаде элемента задержки, который включен между клеммами питания соседних каскадов, подключение затворов транзисторов сброса n-типа во всех каскадах к тактовой шине и выполнение элемента задержки в виде двух последовательно включенных тактируемых инвертирующих элементов.

Наличие в предлагаемом устройстве перечисленных выше существенных отличительных признаков обеспечивает решение поставленной технической задачи - повышения быстродействия устройства. В устройстве-прототипе временная задержка на каскад является суммой задержек входного и выходного тактирующих элементов и задержки в триггерной части - КМДП инверторах при участии цепей логического блока. В заявленном устройстве тактовый инвертор один на все каскады и его вклад в общую задержку незначителен. Процесс формирования парафазного состояния в такой же триггерной части происходит синхронно с переключением элемента задержки. Напряжение на клемме питания последующего каскада формируется одновременно с появлением парафазных сигналов на выходах предыдущего каскада. Поэтому при соответствующем выборе параметров транзисторов элемента задержки и при заданной емкостной нагрузке на выходах каскада временная задержка на каскад может соответствовать только одной задержке установления парафазного сигнала в триггерной части, состоящей из КМДП инверторов и ключевых цепей логического блока.

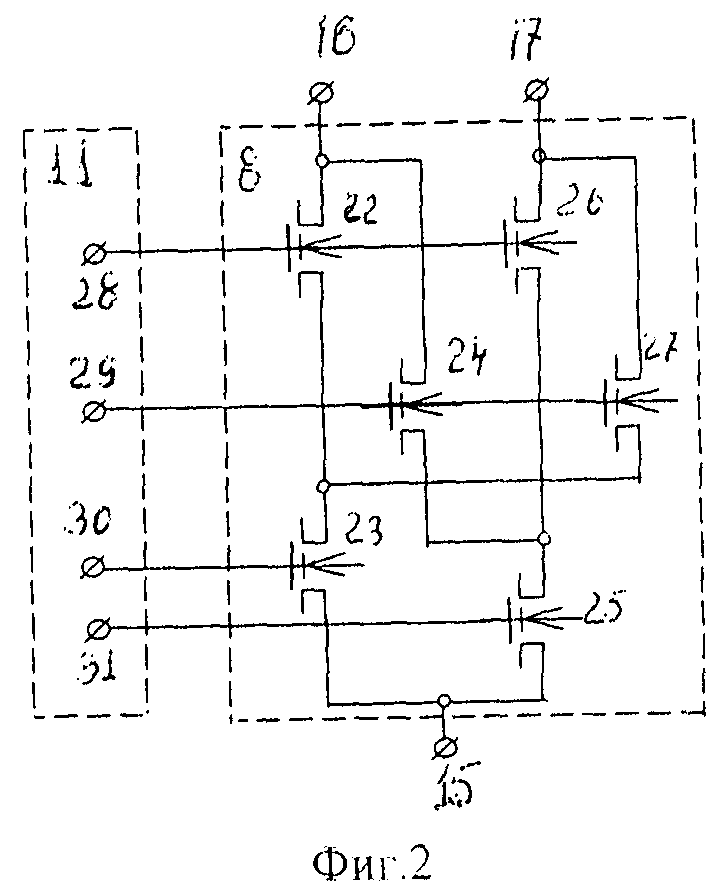

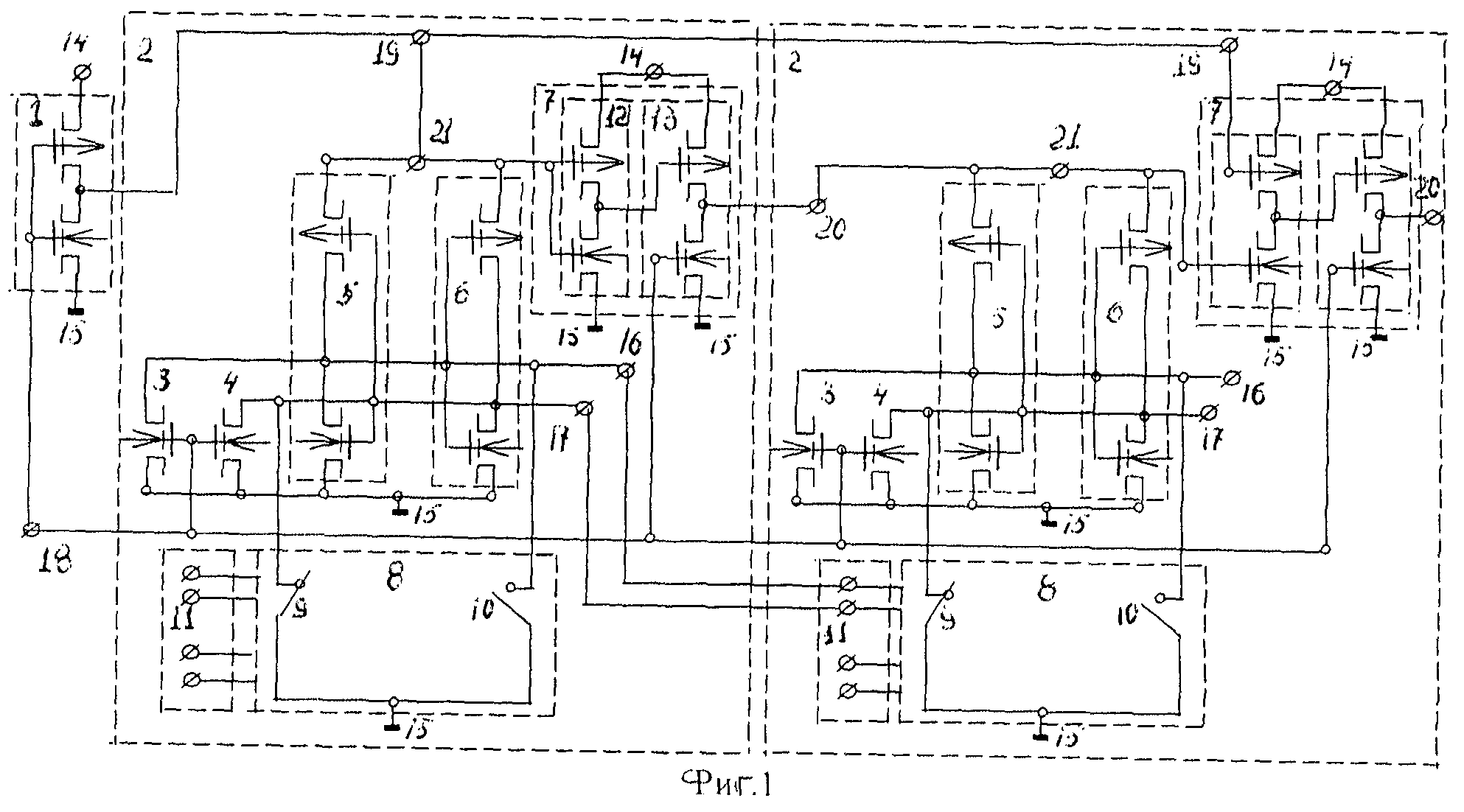

На фиг.1 приведена принципиальная схема заявляемого каскадного парафазного логического устройства на примере двух каскадов. На фиг.2 приведена в качестве примера принципиальная схема логического блока для реализации функции 'Исключающее ИЛИ'.

Каскадное парафазное логическое устройство (Фиг.1) содержит тактовый КМДП инвертор 1 и в каждом каскаде 2 первый 3 и второй 4 транзисторы сброса n-типа, первый 5 и второй 6 КМДП инверторы, элемент задержки 7 и логический блок 8, который содержит по меньшей мере две ключевые цепи 9, 10, выполненные из последовательно соединенных транзисторов n-типа каждая, затворы которых подключены к парафазным логическим входам 11 каскада таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты. Элемент задержки 7 содержит первый 12 и второй 13 инвертирующие элементы, каждый из которых содержит транзистор p-типа и транзистор n-типа, которые включены последовательно между шиной питания 14 и шиной земли 15.

Первые выводы ключевых цепей 9, 10 подключены к шине земли 15, а вторые являются соответственно прямым 16 и инверсным 17 выходами каскада, которые подключены к одному из парафазных логических входов 11 последующего каскада. Прямой выход 16 каскада соединен с выходом первого 5 и с входом второго 6 КМДП инверторов, а инверсный выход 17 каскада соединен с выходом второго 6 и с входом первого 5 КМДП инверторов. Первый 3 и второй 4 транзисторы сброса n-типа включены между шиной земли 15 и соответственно прямым 16 и инверсным 17 выходами каскада.

Вход тактового КМДП инвертора 1 и затворы транзисторов сброса 3, 4 n-типа подключены к тактовой шине 18.

Затвор транзистора p-типа первого инвертирующего элемента 12 подключен к выходу 19 тактового КМДП инвертора 1, который включен между шиной питания 14 и шиной земли 15, а затвор транзистора n-типа второго инвертирующего элемента 13 подключен к тактовой шине 18, точка соединения транзисторов p- и n-типов первого инвертирующего элемента 12 подключена к затвору транзистора p-типа второго инвертирующего элемента 13, точка соединения транзисторов p- и n-типов которого является выходом 20 элемента задержки. Первый 5 и второй 6 КМДП инверторы включены между клеммой питания данного каскада 21 и шиной земли 15, причем в первом каскаде клемма питания 21 соединена с выходом 19 тактового КМДП инвертора 1, а во втором и последующих каскадах клемма питания 21 соединена с выходом 20 элемента задержки предыдущего каскада, затвор транзистора n-типа первого 12 инвертирующего элемента соединен с клеммой питания 21 данного каскада и является входом элемента задержки.

Логический блок 8 при реализации функции 'Исключающее ИЛИ' (Фиг.2) содержит 6 транзисторов 22-27 n-типа, которые включены попарно последовательно и составляют 4 ключевые цепи логического блока: первая содержит первый 22 и второй 23 транзисторы n-типа, вторая - третий 24 и четвертый 25 транзисторы n-типа, третья - пятый 26 и четвертый 24 транзисторы n-типа, четвертая - второй 23 и шестой 27 транзисторы n-типа. Количество ключевых цепей соответствует числу логических состояний элемента - в данном случае 4 от двух переменных. Затворы первого 22 и пятого 26 транзисторов n-типа подключены к первому 28 логическому входу каскада, затворы третьего 24 и шестого 27 транзисторов n-типа подключены к второму 29 логическому входу, затворы второго 23 и четвертого 25 подключены соответственно к третьему 30 и четвертому 31 логическим входам каскада. Первая и вторая ключевые цепи включены между прямым 16 выходом каскада и шиной земли 15, а третья и четвертая цепи включены между инверсным 17 выходом каскада и шиной земли 15.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при единичном сигнале на тактовой шине 18 напряжение на выходе 19 тактового КМДП инвертора 1, на выходах 20 элементов задержки 7, клеммах питания 21 всех каскадов равно нулю, транзисторы сброса 3 и 4 открыты и сигналы на выходах 16 и 17 каскадов 2 также нулевые. Все ключевые цепи 9, 10 логических блоков 8 находятся поэтому в выключенном состоянии. На других логических входах 11 каскадов устанавливаются парафазные сигналы, соответствующие входным переменным. Например, на первый 28 и второй 29 логические входы для заданной, в данном случае функции 'Исключающее ИЛИ' поданы соответственно прямой и логически дополняющий сигналы первой переменной X, а на третий 30 и четвертый 31 логические входы поданы соответственно прямой и логически дополняющий сигналы второй переменной Y. При равенстве переменных X=Y в замкнутом состоянии находится первая ключевая цепь логического блока. При логическом неравенстве переменных в замкнутом состоянии находятся третья или четвертая ключевые цепи. Причем транзисторы n-типа ключевых цепей работают в режиме переключателей на разряд узловых емкостей выходов каскада. Ключевые цепи формируются по правилам булевой алгебры для парафазных сигналов.

Рабочий полутакт начинается с подачи на тактовую шину 18 нулевого сигнала, при этом на все его логические входы 11 подаются сигналы от внешних устройств или от предыдущего каскада. Транзисторы сброса 3 и 4 n-типа закрываются, а на выходе 19 входного тактового инвертора 1 и клемме питания 21 первого каскада напряжение нарастает до величины напряжения на шине питания 14. Одновременно через открытые транзисторы p-типа КМДП инверторов 5 и 6 начинает расти напряжение на емкостях нагрузок, связанных с выходами этих инверторов. При поступлении на тактовую шину 18 нулевого сигнала транзистор n-типа второго инвертирующего элемента 13 и транзистор p-типа первого инвертирующего элемента 12 всех элементов задержки 7 закрываются, но напряжения в точках соединения транзисторов этих элементов сохраняются, что подготавливает их переключение с малой задержкой за счет уменьшения узловых емкостей. Если в замкнутом состоянии находится первая ключевая цепь, то благодаря току через транзисторы этой цепи напряжение на выходе первого КМДП инвертора 5 растет медленнее, чем на выходе второго КМДП инвертора 6. Поскольку данные инверторы объединены обратными связями по схеме триггера, процесс приводит к формированию нулевого напряжения на выходе первого инвертора 5 и на прямом выходе 16 каскада, а на выходе второго инвертора 6 и инверсном выходе 17 каскада - положительного напряжения, равного напряжению на шине питания 14, соответствующего логической 1 при X=Y.

Одновременно с нарастанием сигнала на выходе 19 тактового КМДП инвертора 1 начинает открываться транзистор n-типа первого инвертирующего элемента 12 и напряжение в точке соединения транзисторов этого элемента убывает до 0 с задержкой, определяемой скоростью формирования напряжения на выходе тактового КМДП инвертора 1, которая определяется величиной нагрузки на выходах 16 и 17 каскада. На выходе 20 элемента задержки 7 и на клемме питания 21 последующего каскада при этом также с задержкой начинает повышаться напряжение. Таким образом одновременно с установкой КМДП инверторов 5, 6 первого каскада в парафазное состояние синхронно, но с задержкой подготавливается включение последующего каскада устройства.

Завершается полный такт при срабатывании последнего каскада устройства единичным сигналом на тактовом входе 13 первого каскада. Напряжение на выходе тактового КМДП инвертора 1 и на клемме питания 21 убывает, а транзисторы сброса 3, 4 n-типа открываются и независимо от состояния проводимости ключевых цепей логического блока 8 напряжения на выходах 16, 17 каскадов падает до нуля, что ведет к установке в исходное состояния устройства.

За счет выбора соответствующих параметров транзисторов элемента задержки 7 при заданной емкостной нагрузке на выходах 16, 17 каскада временная задержка на каскад может соответствовать задержке установления парафазного сигнала в триггерной части, состоящей из КМДП инверторов 5, 6 и ключевых цепей 9, 10 логического блока 8.

Каскадное парафазное логическое устройство, содержащее тактовый КМДП инвертор и в каждом каскаде первый и второй транзисторы сброса n-типа, первый и второй КМДП инверторы, включенные между соответствующими клеммами питания и шиной земли, и логический блок, содержащий по меньшей мере две ключевые цепи, выполненные каждая из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам каскада таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы ключевых цепей подключены к шине земли, а вторые являются соответственно прямым и инверсным выходами каскада, которые подключены к одному из парафазных логических входов последующего каскада, прямой выход каскада соединен с выходом первого и с входом второго КМДП инверторов, а инверсный выход каскада соединен с выходом второго и с входом первого КМДП инверторов, первый и второй транзисторы сброса n-типа включены между шиной земли и соответственно прямым и инверсным выходами каскада, вход тактового КМДП инвертора и затворы транзисторов сброса n-типа в первом каскаде подключены к тактовой шине, клемма питания в первом каскаде подключена к выходу тактового КМДП инвертора, который включен между шиной питания и шиной земли, отличающийся тем, что содержит в каждом каскаде элемент задержки, содержащий первый и второй инвертирующие элементы, каждый из которых содержит транзистор p-типа и транзистор n-типа, которые включены последовательно между шиной питания и шиной земли, затворы транзисторов p- и n-типа первого инвертирующего элемента соединены соответственно с выходом тактового КМДП инвертора и с клеммой питания данного каскада, затвор транзистора n-типа второго инвертирующего элемента подключен к тактовой шине, точка соединения транзисторов p- и n-типов первого инвертирующего элемента подключена к затвору транзистора p-типа второго инвертирующего элемента, точка соединения транзисторов p- и n-типов второго инвертирующего элемента является выходом элемента задержки и подключена к клемме питания последующего каскада, затворы транзисторов сброса n-типа во втором и последующих каскадах также подключены к тактовой шине.