Результат интеллектуальной деятельности: ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

Вид РИД

Изобретение

Изобретение относится к области микроэлектроники и может быть использовано в ячейках памяти статического оперативного запоминающего устройства (ОЗУ) специализированных полупроводниковых интегральных схем.

Известны радиационно стойкие ячейки оперативных запоминающих устройств, в основе которых используются два КМОП инвертора, образующих триггер для запоминания логического состояния сигнала. Каждый инвертор выполняется на двух полевых транзисторах разного типа проводимости, при этом ко входу каждого инвертора подключены транзисторы выборки n-типа, которые соединяют запоминающий триггер с парой разрядных шин. Таким образом, основу ячеек памяти указанного типа составляет 6-транзисторное ядро. В условиях воздействия ионизирующего излучения при прохождении частицы через область закрытого транзистора заряд, генерированный этой частицей, способен вызвать переключение транзистора в открытое состояние. Следствием этого будет изменение хранящихся в триггере данных. Поэтому известные аналоги изобретения используют 6-транзисторную ячейку памяти, расширенную за счет добавления в связи между инверторами разных электрических компонентов.

В ячейке памяти, устойчивой к единичным отказам, по патенту США №5905290 (опубл. 18.05.1999 г.), для повышения стабильности работы таких устройств между инверторами включены вносящие задержку RC-цепи. Такое решение позволяет задержать «ложный» сигнал, предотвращая переключение запоминающего триггера.

Известны ячейки памяти, в которых с аналогичной целью применяются включенные между входами инверторов транзисторы n-типа (заявка США №4912675, опубл. 27.03.1990 г., патент США №4956815, опубл. 11.09.1990 г., патент США №7233518, опубл. 19.06.2007 г.), диоды (патент США №4805148, опубл. 14.02.1989 г.), конденсаторы (патент США №7110281, опубл.09.19.2006, патент США №7397692, опубл.08.07.2008 г.), резисторы (патент США №7768810, опубл.09. 08.2010 г.).

Преимуществами таких ячеек ОЗУ является малая занимаемая площадь, высокое быстродействие. Недостатками являются наличие состязательности данных в процессе записи в триггер и чтения из него, высокая вероятность переключения триггера из-за увеличения тока утечки в проходных транзисторах при изменении порогового напряжения в жестких условиях эксплуатации, а также необходимость предварительной зарядки обеих разрядных шин до высокого логического состояния перед процессом считывания, следствием чего является увеличение тока потребления устройства. Высокий температурный коэффициент сопротивления резисторов и конденсаторов влечет температурную чувствительность полученной схемы.

Устойчивость ячейки памяти к воздействию внешних факторов может быть повышена за счет введения в схему обратной связи для восстановления поврежденных данных. Известны ячейки памяти, в которых для хранения данных используется два параллельно соединенных триггера. Такое решение применяется в радиационно-стойкой ячейке памяти (патент США US 6573773, опубл. 03.06.2003 г., заявка Франции FR 2876490 опубл. 14.04.2006 г.), в которых в состав инверторов добавлены вносящие смещение транзисторы р-типа. Известна радиационно стойкая ячейка ОЗУ, патент США №6147899 опубл. 14.11.2000 г., в которой дублируется запоминающий элемент, при этом в первом триггере на резисторы заменены транзисторы n-типа, во втором триггере -транзисторы р-типа. Известна защищенная от внешних воздействий логическая ячейка (европейская заявка ЕР 1892719, опубл. от 27.02.2008 г.), в которой применяется электрическая изоляция входа одного инвертора от выхода второго инвертора в составе триггера. Преимуществом таких ячеек является повышение стойкости к воздействию внешних факторов, являющегося следствием сохранения «правильного» логического состояния в одном из триггеров. Недостаток заключается в увеличении занимаемой площади и состязательности «правильного» и «ложного» сигналов. При этом сохраняется необходимость предварительной зарядки разрядных шин до высокого логического состояния перед процессом считывания, а также существует опасность разрушающего считывания в случае скопления на разрядной шине емкостного заряда.

Наиболее близким к изобретению является техническое решение ячейки оперативного запоминающего устройства со схемой контроля считывания (патент США №4441169, опубл. 03.04.1984 г.). Ячейка содержит триггер на основе двух инверторов, терминал напряжения питания и адресную шину считывания, разрядную шину, ключ для записи данных, подключенный между разрядной шиной и входом первого инвертора, схему контроля считывания.

Первый инвертор в триггере состоит из пары МОП транзисторов n- и р-типа, при этом затворы транзисторов объединены и образуют первый входной терминал, стоки объединены в первый выходной терминал. Второй инвертор также состоит из комплементарной пары МОП транзисторов, затворы которых соединены с первым выходным терминалом, стоки транзисторов объединены во второй выходной терминал. Первый проходной ключ схемы контроля считывания образован первым МОП транзистором, затвор которого соединен с первым выходным терминалом. Второй ключ схемы образован вторым МОП транзистором, его затвор соединен с адресной шиной считывания. Для обеспечения режима записи используется тактируемый (динамический) второй инвертор, сформированный комплементарной парой МОПтранзисторов n- и р-типа и двумя переключательными МОП транзисторами, управляемыми комплементарными адресными шинами записи. Переключательный транзистор n-типа соединен с транзистором n-типа инвертора, переключательный транзистор р-типа соединен с транзистором р-типа инвертора.

Данная ячейка имеет в своем составе независимые схемы для записи и считывания данных. Схема контроля считывания включает в себя первый МОП транзистор n-типа, который управляется хранящимися в триггере данными, и второй МОП транзистор n-типа, который управляется адресной шиной считывания. Проходной ключ для записи данных в ячейку образован третьим МОП транзистором, который подключен между разрядной шиной и первым входным терминалом, затвор транзистора соединен с адресной шиной записи. Разрядная шина через транзистор дотяжки соединена с «землей», затвор транзистора дотяжки управляется сигналом предзаряда.

Данные в ячейку записываются через проходной ключ, управляемый адресным сигналом записи. Когда адресная шина записи заряжена до низкого логического уровня и шина чтения заряжена до высокого логического уровня, проходной ключ для записи закрыт и образованный инверторами триггер отделен от разрядной шины. Таким образом, данные в триггере сохраняются. Когда данные из триггера считываются, работает только схема контроля считывания, поскольку проходной ключ записи отсекает триггер от разрядной шины.

Когда данные из ячейки считываются, поток данных между разрядной шиной и запоминающим элементом не допускается. Таким образом, обеспечивается неразрушающее считывание данных при сравнительно небольшом увеличении занимаемой площади. К недостаткам ячейки следует отнести необходимость предварительной зарядки разрядной шины и отсутствие защиты от единичных сбоев в случае попадания отдельных ядерных частиц.

В основе изобретения лежит задача создания ячейки ОЗУ, обладающей повышенной стойкостью к воздействию внешних факторов при минимальном увеличении занимаемой площади, без необходимости предварительной зарядки разрядных шин и применения резисторов и конденсаторов.

Технический результат заключается в повышении надежности, отказе- и сбоеустойчивости ОЗУ в связи с отсутствием состязательности сигналов, уменьшении энергопотребления ввиду исключения необходимости предварительной зарядки разрядной шины, повышении радиационной стойкости за счет защиты от единичных сбоев в случае попадания отдельных ядерных частиц.

Для достижения вышеуказанного технического результата ячейка памяти статического оперативного запоминающего устройства содержит три последовательно соединенных КМОП инвертора, включенных между шиной питания и шиной земли; первый проходной ключ, состоящий из двух последовательно соединенных адресных транзисторов, затворы которых соединены с адресной шиной записи и адресной шиной выбора столбца; второй проходной ключ в виде адресного транзистора, затвор которого соединен с адресной шиной считывания; схему подтверждения записанных данных, состоящую из двух параллельно соединенных комплементарных проходных ключей, один из которых соединен с адресной шиной записи и ее инверсным входом, а другой - с адресной шиной выбора столбца и ее инверсным входом, при этом вход первого КМОП инвертора соединен через первый проходной ключ с первой разрядной шиной; выход первого КМОП инвертора соединен с входом второго КМОП инвертора; выход второго КМОП инвертора соединен с входом третьего инвертора и через схему подтверждения записанных данных с входом первого КМОП инвертора; выход третьего КМОП инвертора соединен через второй проходной ключ со второй разрядной шиной.

В схеме подтверждения записанных данных первый проходной ключ состоит из двух транзисторов, затворы которых соединены соответственно с адресной шиной записи и ее инверсным входом, а второй проходной ключ состоит из двух транзисторов, затворы которых соединены соответственно с адресной шиной выбора столбца и ее инверсным входом.

От прототипа указанный способ отличает: наличие схемы подтверждения между входом первого инвертора и выходом второго инвертора, выполненной в виде двух параллельно включенных КМОП ключей, содержащей два параллельно соединенных комплементарных проходных ключа, один из которых соединен с прямым и инверсным входами шиной записи, а другой - с прямым и инверсным входами адресной шиной выбора столбца; наличие третьего инвертора, который исполняет роль развязывающего усилителя; наличие второго транзистора записи n-типа, который соединен с адресной шиной выбора столбца и соединен с первым транзистором записи, подключенным к первой разрядной шине, и входом первого инвертора; наличие второго проходного ключа в виде транзистора считывания n-типа, соединяющего выход третьего инвертора и вторую разрядную шину.

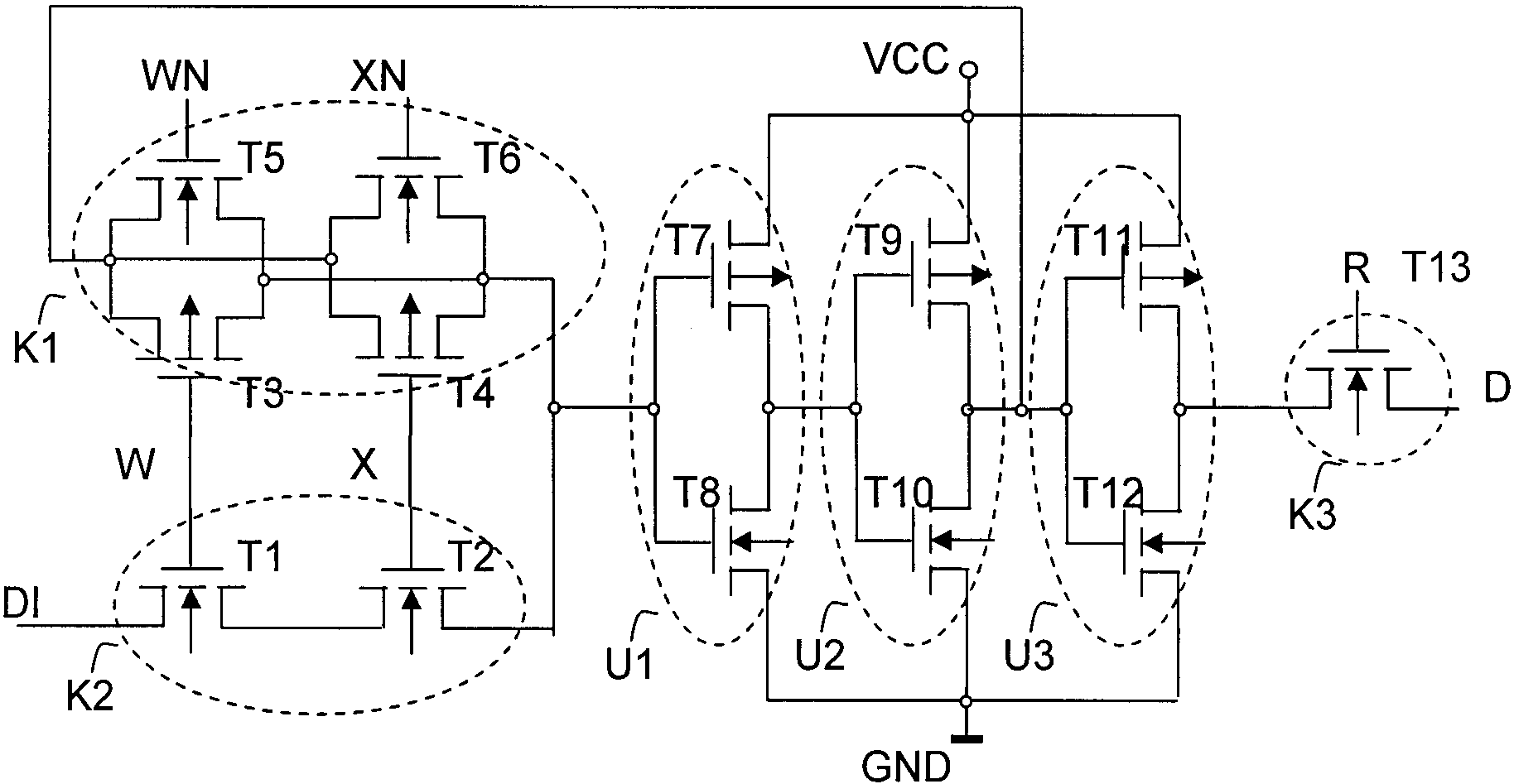

На чертеже приведена принципиальная схема заявляемой ячейки ОЗУ.

Ячейка памяти статического оперативного запоминающего устройства содержит три последовательно соединенных КМОП инвертора: первый инвертор (U1), второй инвертор (U2), третий инвертор (U3), соединенных с шиной питания и шиной земли; схему подтверждения записанных данных (К1), первый проходной ключ (К2) для записи данных в ячейку; второй проходной ключ (К3) для считывания данных из ячейки. Три последовательно соединенных КМОП инвертора:

первый инвертор (U1), второй инвертор (U2), третий инвертор (U3) образуют триггер для хранения двоичного значения сигнала.

Первый проходной ключ (К2) состоит из последовательно соединенных первого транзистора (Т1) n-типа и второго транзистора (Т2) n-типа, при этом затвор первого транзистора соединен с адресной шиной записи (W), затвор второго транзистора (Т2) соединен с адресной шиной выбора столбца (X).

Схема подтверждения (К1) состоит из двух параллельно включенных комплементарных проходных ключей, при этом первый ключ образован параллельно включенными третьим (Т3) и пятым (Т5) транзисторами р- и n-типа соответственно, второй ключ образован параллельно включенными четвертым (Т4) и шестым (Т6) транзисторами р- и n-типа соответственно. Третий транзистор (Т3) соединен с прямым входом адресной шины записи W, пятый транзистор (Т5) соединен с инверсным входом адресной шины записи WN. Четвертый транзистор (Т4) соединен с прямым входом адресной шины выбора столбца X, а шестой транзистор (Т6) - с ее инверсным входом XN.

Первый инвертор (U1) состоит из транзисторов (Т7) и (Т8), второй инвертор (U2) состоит из транзисторов (Т9) и (Т10), третий инвертор (U3) состоит из транзисторов (Т11) и (Т12).

Второй проходной ключ (К3) выполнен в виде адресного транзистора n-типа (Т13), при этом затвор транзистора (Т13) соединен с адресной шиной считывания (R).

Инверторы (U1), (U2), (U3) включены между шиной питания (VCC) и шиной земли (GND). Вход первого инвертора (U1) соединен через схему подтверждения (К1) с выходом второго инвертора (U2) и через первый проходной ключ (К2) с первой разрядной шиной (DI). Выход первого инвертора (U1) является входом второго инвертора (U2). Выход второго инвертора (U2) является входом третьего инвертора (U3). Выход третьего инвертора U3 через второй проходной ключ (К3) соединен со второй разрядной шиной (DO).

Устройство работает следующим образом. В состоянии хранения информации выходы первого и второго инверторов находятся в парафазном состоянии. Схема подтверждения (К1) в этом случае исполняет роль вносящего задержку элемента, обеспечивая защиту от одиночных сбоев. Первая разрядная шина может быть заряжена до высокого или низкого логического состояния или находиться в состоянии высокого импеданса. Вторая разрядная шина в режиме хранения находится в состоянии высокого импеданса.

При записи на разрядной шине (DI) формируется определенное логическое состояние. Адресный сигнал записи (W) и сигнал выбора столбца (X) заряжаются до высокого потенциала. Данные с первой разрядной шины (DI) через проходной ключ (К2) поступают на вход первого инвертора. При этом схема подтверждения (К1) разрывает обратную связь триггера, исключая появление состязательности сигналов с разрядной шины (DI) и выхода второго инвертора (U2). Как только один из адресных сигналов записи (W) или выбора столбца (X) разряжается до низкого потенциала, схема подтверждения (К1) включает обратную связь триггера, первый проходной ключ (К2) закрывается, отсекая разрядную шину от триггера, наступает состояние хранения.

В режиме считывания адресный сигнал чтения заряжается до высокого логического состояния, открывая второй проходной ключ (К3). Схема подтверждения (К1) замкнута, триггер через обратную связь хранит информацию. Первый проходной ключ (К2) разомкнут. Хранимая в триггере информация через третий инвертор (U3) и проходной ключ (К3) поступает на вторую разрядную шину (DO). Предварительная зарядка второй разрядной шины не требуется. Применение третьего инвертора (U3) в качестве развязывающего усилителя позволяет увеличить мощность считываемого сигнала и, как следствие, увеличить нагрузку второй разрядной шины (DO). Поскольку считывание осуществляется с выхода третьего инвертора, который не связан с входами первого и второго инверторов, состояние триггера остается неизменным, т.е. происходит неразрушающее считывание. Как только адресный сигнал чтения разряжается до низкого потенциала, наступает состояние хранения.