Результат интеллектуальной деятельности: УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА И СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА

Вид РИД

Изобретение

Область техники

Настоящее изобретение имеет отношение к способу передачи и приема сигнала и к устройству для передачи и приема сигнала и, в частности, к способу передачи и приема сигнала и устройству для передачи и приема сигнала, которые способны улучшить эффективность передачи данных.

Уровень техники

По мере совершенствования технологии цифрового широковещания пользователи получили динамическое изображение высокой четкости (HD). При непрерывном развитии алгоритма сжатия и производительности оборудования в будущем пользователям будут предоставлены улучшенные условия. Система цифрового телевидения (DTV) может принимать сигнал цифрового широковещания и предоставлять пользователям множество дополнительных услуг, а также видеосигнал и аудиосигнал.

С развитием технологии цифрового широковещания возрастают требования для таких служб, как передача видеосигнала и аудиосигнала, и постепенно увеличивается размер данных, ожидаемых пользователем, или количество каналов широковещания.

Раскрытие изобретения

Техническая проблема

В соответствии с этим настоящее изобретение направлено на способ передачи и приема сигнала и устройство для передачи и приема сигнала, которые в значительной степени устраняют одну или более проблем вследствие ограничений и недостатков предшествующего уровня техники.

Задача настоящего изобретения состоит в том, чтобы обеспечить способ передачи и приема сигнала и устройство для передачи и приема сигнала, которые способны улучшить эффективность передачи данных.

Другая задача настоящего изобретения состоит в том, чтобы обеспечить способ передачи и приема сигнала и устройство для передачи и приема сигнала, которые способны улучшить возможности коррекции ошибок битов, формирующих службу.

Техническое решение

Для решения задачи настоящее изобретение обеспечивает способы передачи и приема сигнала и устройство для передачи и приема сигнала.

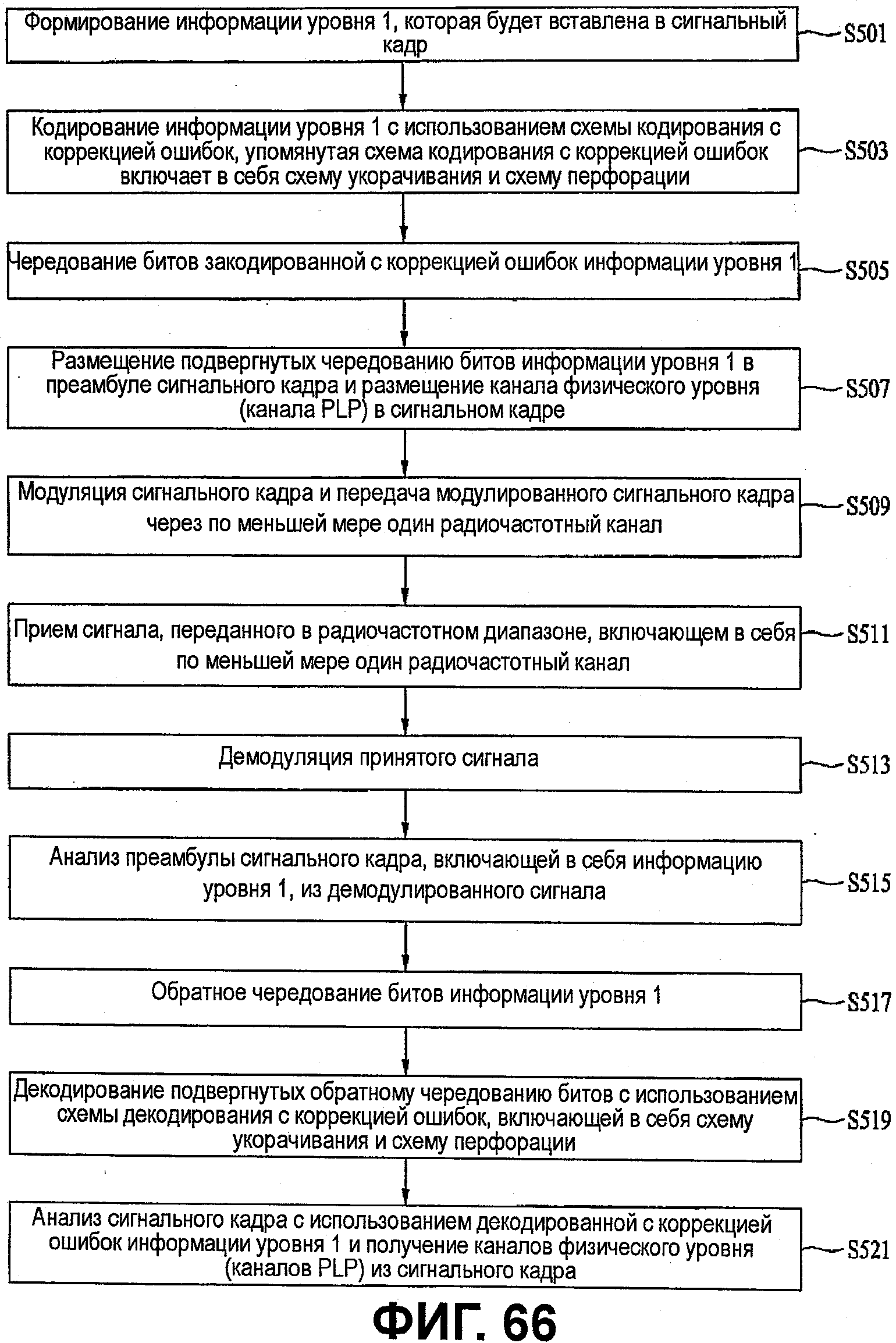

В одном аспекте настоящего изобретения способ передачи сигнала содержит этапы, на которых формируют информацию уровня 1, предназначенную для вставки в сигнальный кадр, кодируют информацию уровня 1 посредством схемы кодирования с коррекцией ошибок, упомянутая схема кодирования с коррекцией ошибок включает в себя схему укорачивания и схему перфорации, чередуют биты закодированной с коррекцией ошибок информации уровня 1, размещают подвергнутые чередованию биты информации уровня 1 в преамбуле сигнального кадра и размещают канал физического уровня (канал PLP) в сигнальном кадре и модулируют сигнальный кадр и передают модулированный сигнальный кадр через по меньшей мере один радиочастотный канал.

В другом аспекте настоящего изобретения способ приема сигнала содержит этапы, на которых принимают сигнал, переданный в радиочастотном диапазоне, включающем в себя по меньшей мере один радиочастотный канал, демодулируют принятый сигнал, анализируют преамбулу сигнального кадра, включающую в себя информацию уровня 1, из демодулированного сигнала, подвергают обратному чередованию биты информации уровня 1, декодируют подвергнутые обратному чередованию биты с использованием схемы декодирования с коррекцией ошибок, включающую в себя схему укорачивания и схему перфорации, и получают каналы физического уровня (каналы PLP) из сигнального кадра с использованием декодированной с коррекцией ошибок информации уровня 1.

В другом аспекте настоящего изобретения устройство для передачи сигнала содержит генератор информации, выполненный с возможностью формировать информацию уровня 1, предназначенную для вставки в сигнальный кадр, кодер информации, выполненный с возможностью выполнять кодирование с коррекцией ошибок информации уровня 1 с использованием кодирования с коррекцией ошибок, включающего в себя схему укорачивания и схему перфорации, и чередовать биты закодированной с коррекцией ошибок информации уровня 1, модуль построения кадров, выполненный с возможностью размещать подвергнутые чередованию биты информации уровня 1 в преамбуле сигнального кадра и распределять канал физического уровня (канал PLP) в сигнальном кадре, и модулятор, выполненный с возможностью модулировать сигнальный кадр, и модуль передачи, выполненный с возможностью передавать модулированный сигнальный кадр через по меньшей мере один радиочастотный канал.

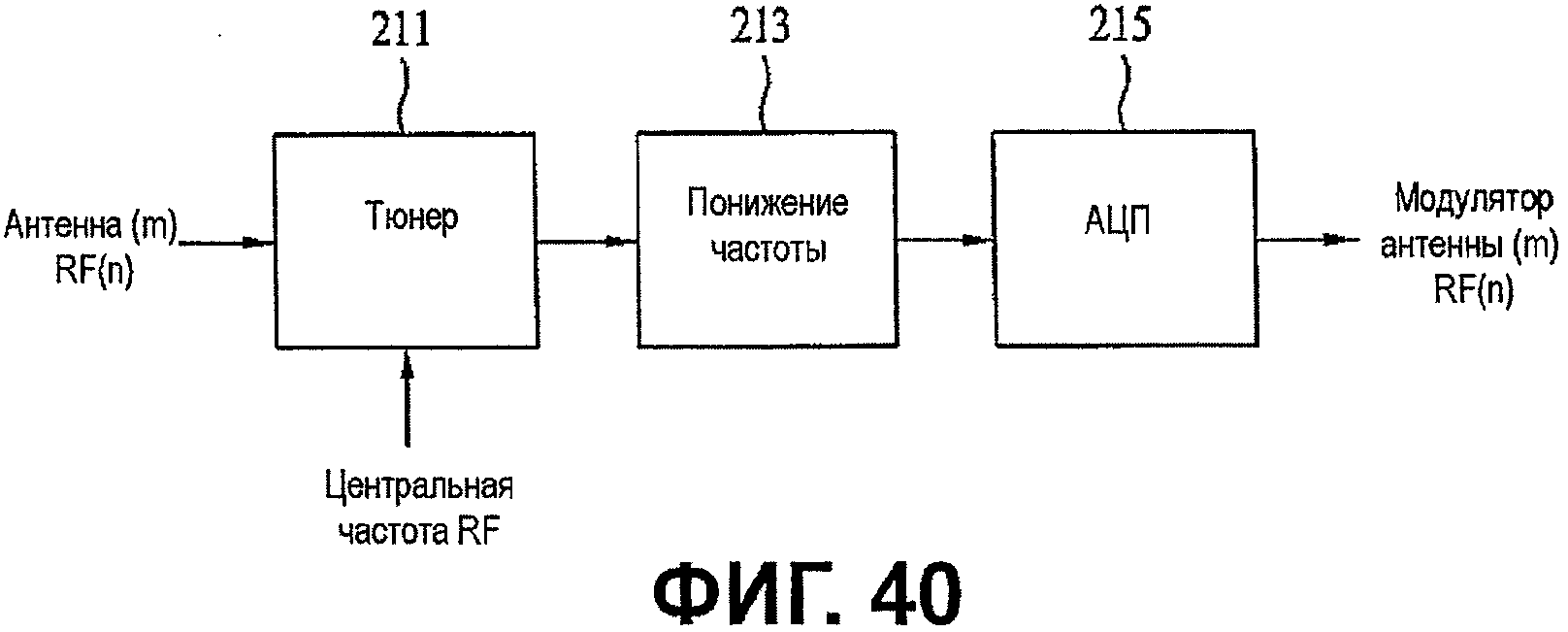

В другом аспекте настоящего изобретения устройство для приема сигнала содержит приемник, выполненный с возможностью принимать сигнал, переданный в радиочастотном диапазоне, включающем в себя по меньшей мере один радиочастотный канал, демодулятор, выполненный с возможностью демодулировать принятый сигнал, декодер информации, выполненный с возможностью подвергать обратному чередованию биты информации уровня 1, проанализированные из сигнального кадра принятого сигнала, и выполнять декодирование с коррекцией ошибок подвергнутых обратному чередованию битов в соответствии со схемой декодирования с коррекцией ошибок, включающей в себя схему укорачивания и схему перфорации, модуль извлечения информации, выполненный с возможностью извлекать закодированную с коррекцией ошибок информацию уровня 1, и анализатор кадра, выполненный с возможностью анализировать сигнальный кадр с использованием извлеченной информацию уровня 1 и получать каналы физического уровня (каналы PLP) из сигнального кадра.

Схема кодирования коррекции ошибок и схема декодирования с коррекцией ошибок включают в себя схему кодирования с коррекцией ошибок с малой плотностью проверок на четность (LDPC).

Информация уровня 1 может быть закодирована и декодирована с использованием схем кодирования и декодирования с коррекцией ошибок, включающим в себя короткий режим кодирования LDPC.

Информация уровня 1 может являться по меньшей мере одним элементом множества, состоящего из длины защитного интервала, количества закодированных с коррекцией ошибок блоков в каждом сигнальном кадре, информации модуляции службы и идентификатора соты.

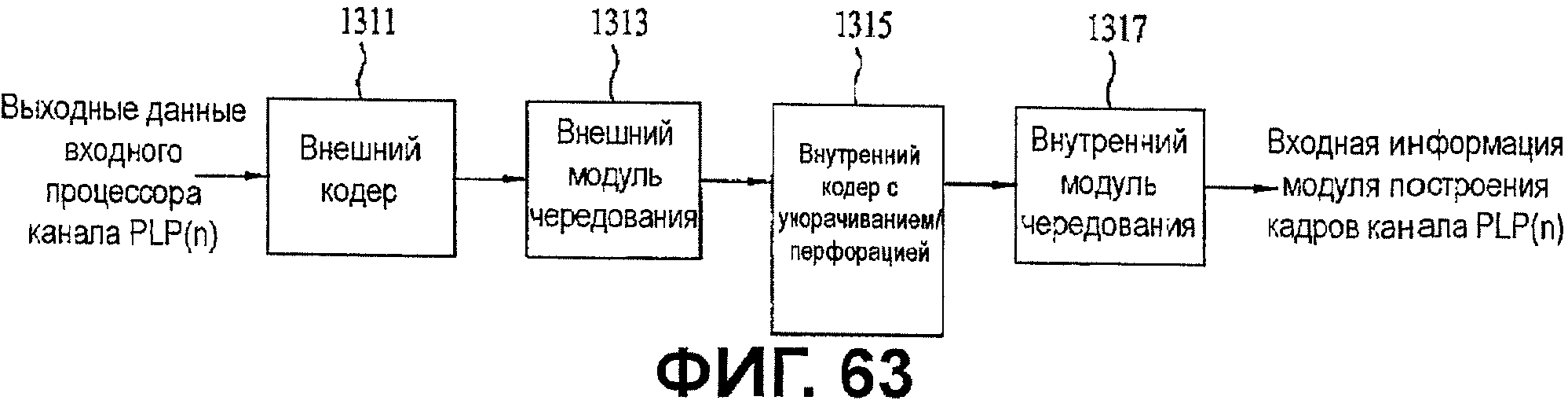

Кодер информации может включать в себя первый кодер, выполненный с возможностью выполнять первое кодирование с коррекцией ошибок относительно битов информации уровня 1, первый модуль чередования, выполненный с возможностью чередовать первые закодированные с коррекцией ошибок биты, второй кодер, выполненный с возможностью выполнять второе кодирование с коррекцией ошибок подвергнутых чередованию битов в соответствии с упомянутой схемой укорачивания и упомянутой схемой перфорации, и второй модуль чередования, выполненный с возможностью чередовать вторые закодированные с коррекцией ошибок биты.

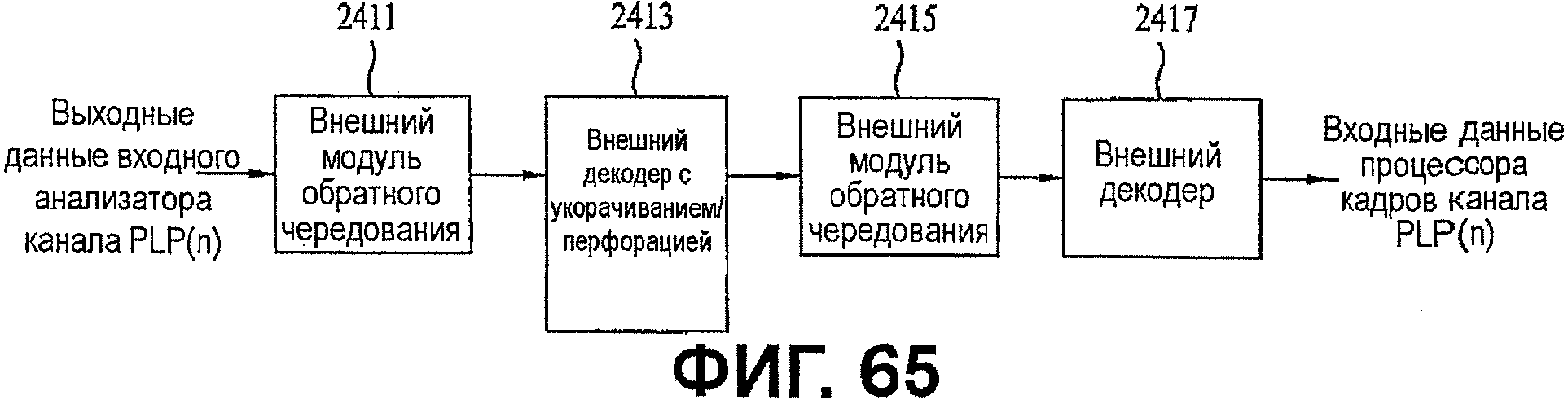

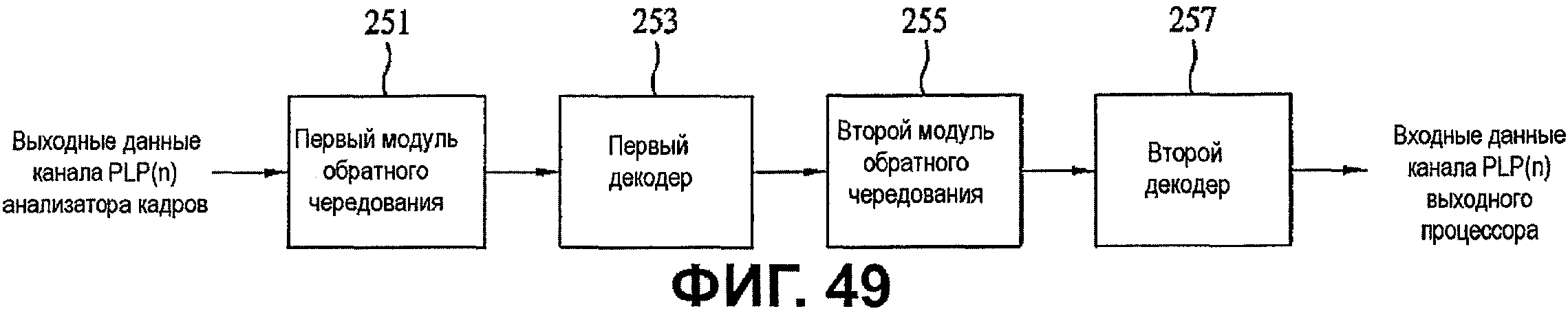

Декодер информации может включать в себя первый модуль обратного чередования, выполненный с возможностью подвергать обратному чередованию биты информации уровня 1, первый декодер, выполненный с возможностью выполнять декодирование с коррекцией ошибок относительно подвергнутых обратному чередованию битов в соответствии со схемами, обратными схеме укорачивания и схеме перфорации, второй модуль обратного чередования, выполненный с возможностью подвергать обратному чередованию декодированные с коррекцией ошибок биты, и второй декодер, выполненный с возможностью выполнять декодирование с коррекцией ошибок относительно подвергнутых обратному чередованию битов.

Полезные эффекты

В соответствии с устройством для передачи и приема сигнала и способом передачи и приема сигнала изобретения, если символ данных, формирующий канал PLP, и символы, формирующие преамбулу, модулируются в одном и том же режиме преобразования FFT, вероятность того, что символ данных обнаруживается посредством преамбулы, является низкой, и уменьшается вероятность того, что преамбула обнаруживается ошибочно. Если содержатся помехи незатухающего колебания (CW), как аналоговый телевизионный сигнал, уменьшается вероятность того, что преамбула ошибочно обнаруживается посредством шумового компонента постоянного тока (DC), сформированного во время корреляции.

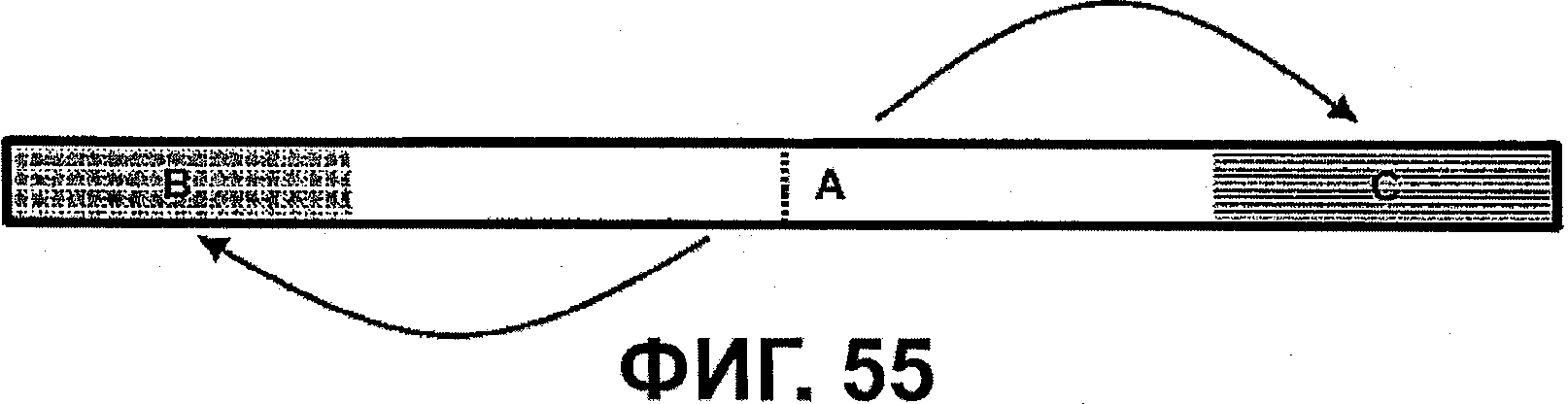

В соответствии с устройством для передачи и приема сигнала и способом передачи и приема сигнала изобретения, если размер преобразования FFT, примененного к символу данных, формирующему канал PLP, больше размера преобразования FFT, примененного к преамбуле, рабочие характеристики обнаружения преамбулы могут быть улучшены даже в канале с задержкой распространения, имеющем длину, равную или больше длины полезной части символа преамбулы. Поскольку в преамбуле используется и циклический префикс (B), и циклический суффикс (C), может быть оценено дробное смещение несущей частоты.

Поскольку кодирование с коррекцией ошибок выполняется относительно преамбулы сигнального кадра, и посредством этого не может быть получено усиление разнесения, возможно корректировать ошибку информации, включенной в преамбулу. В соответствии с этим возможно улучшить производительность приема информации, включенной в верную преамбулу.

Краткое описание чертежей

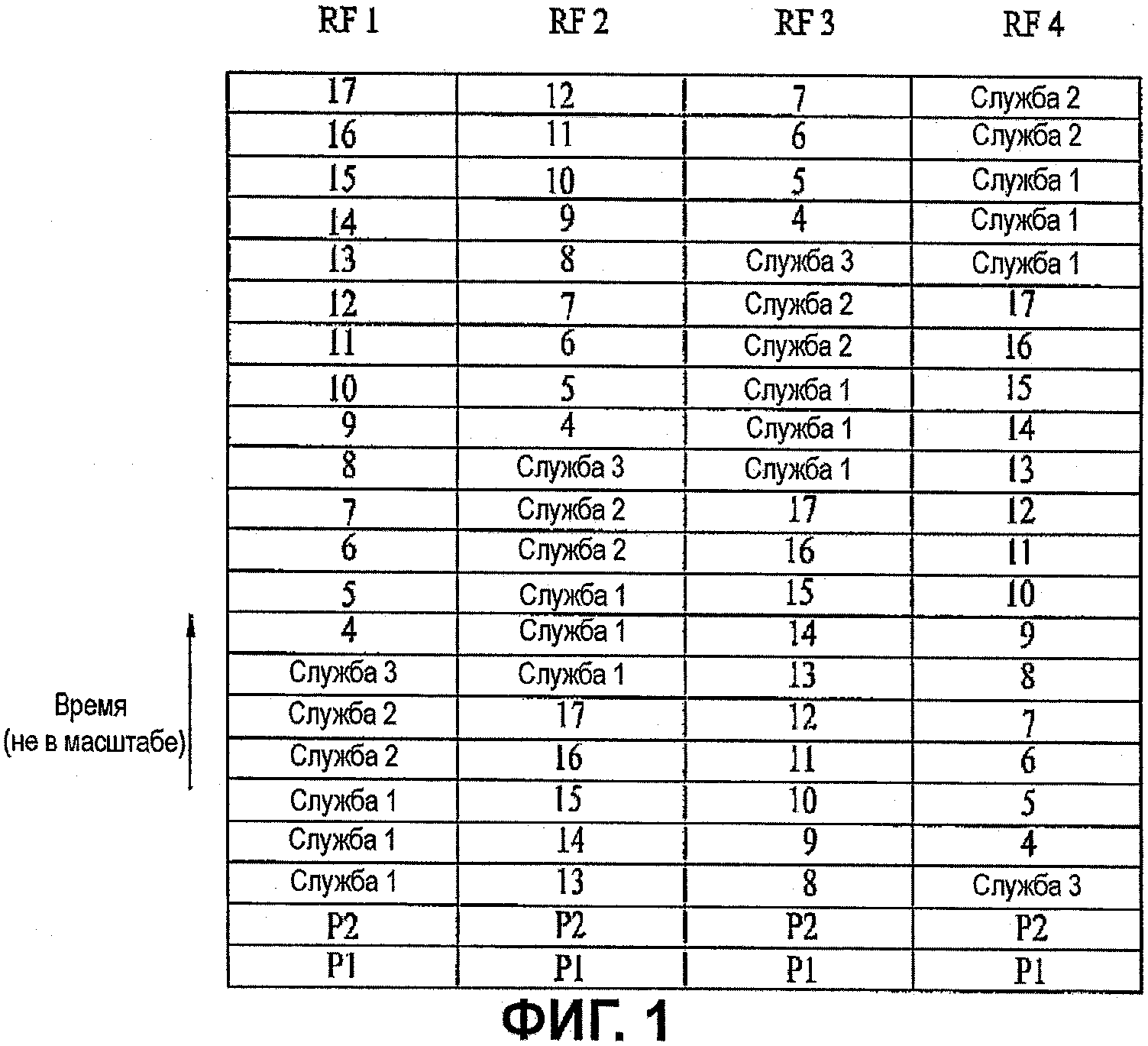

Фиг.1 - изображение, показывающее сигнальный кадр для передачи службы;

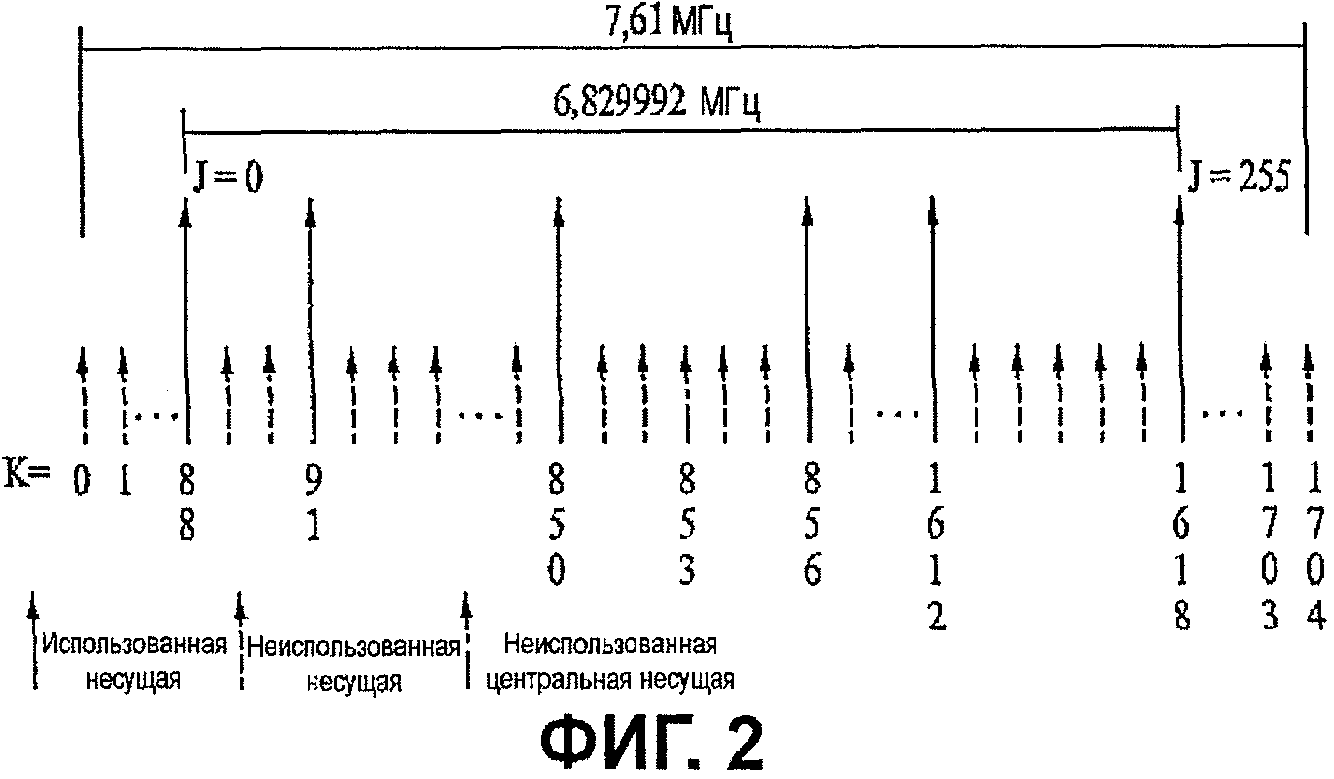

Фиг.2 - изображение, показывающее структуру первого контрольного сигнала P1 сигнального кадра;

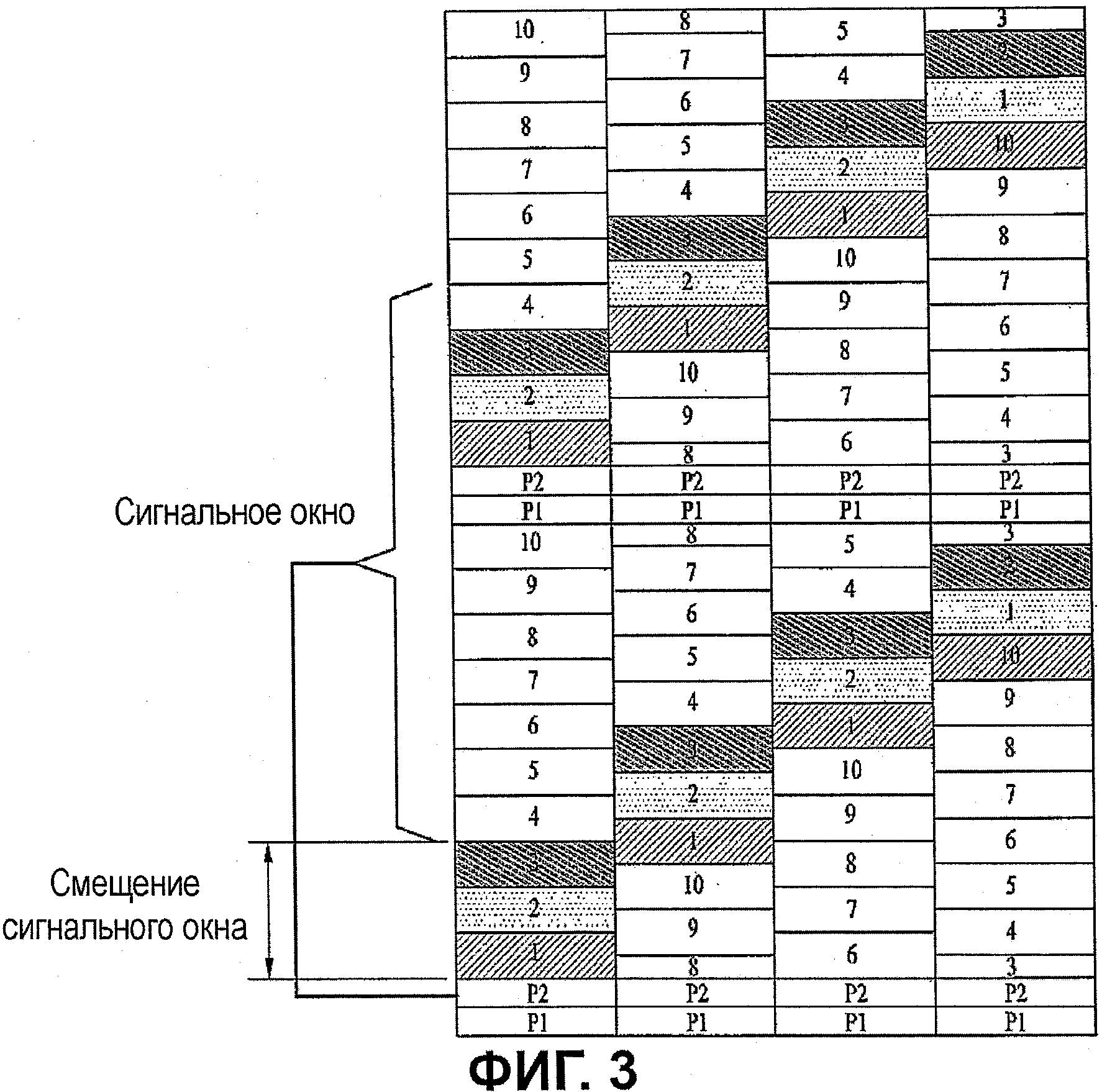

Фиг.3 - изображение, показывающее сигнальное окно;

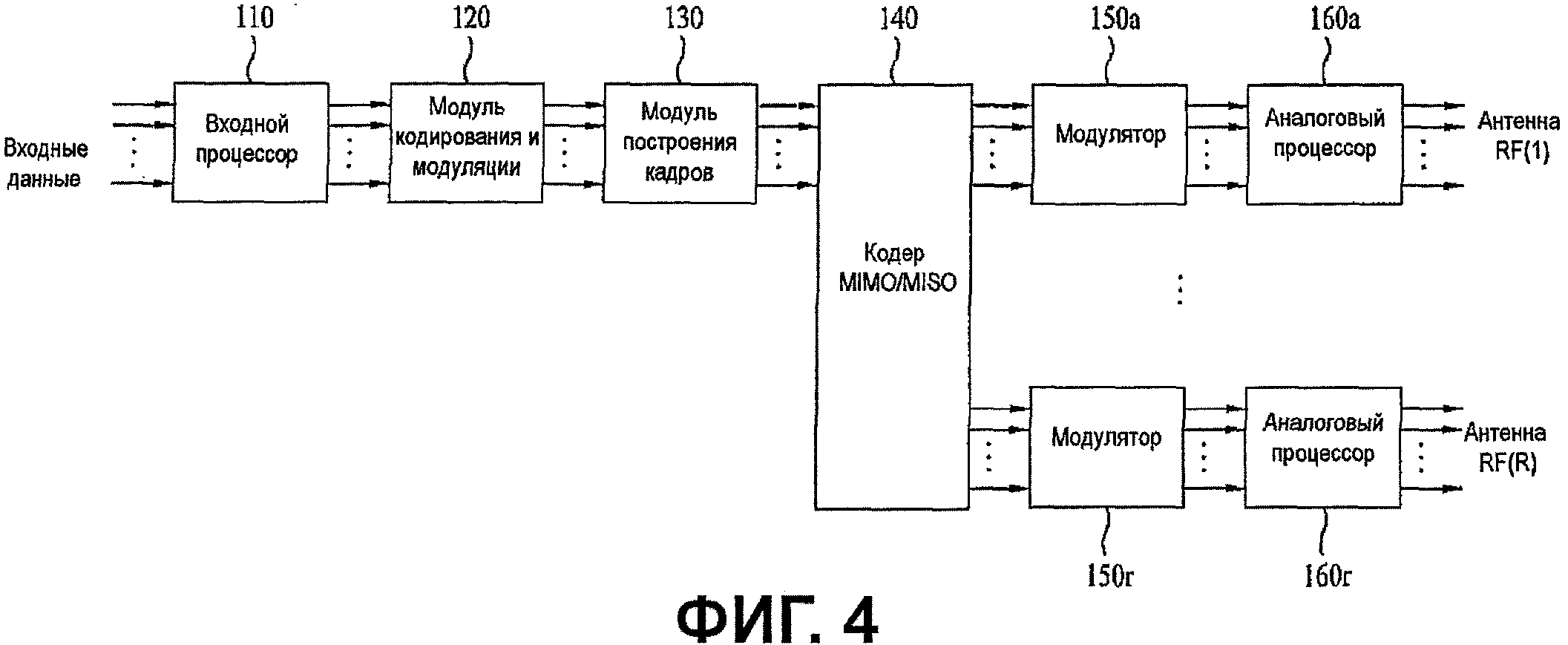

Фиг.4 - схематическое изображение, показывающее вариант воплощения устройства для передачи сигнала;

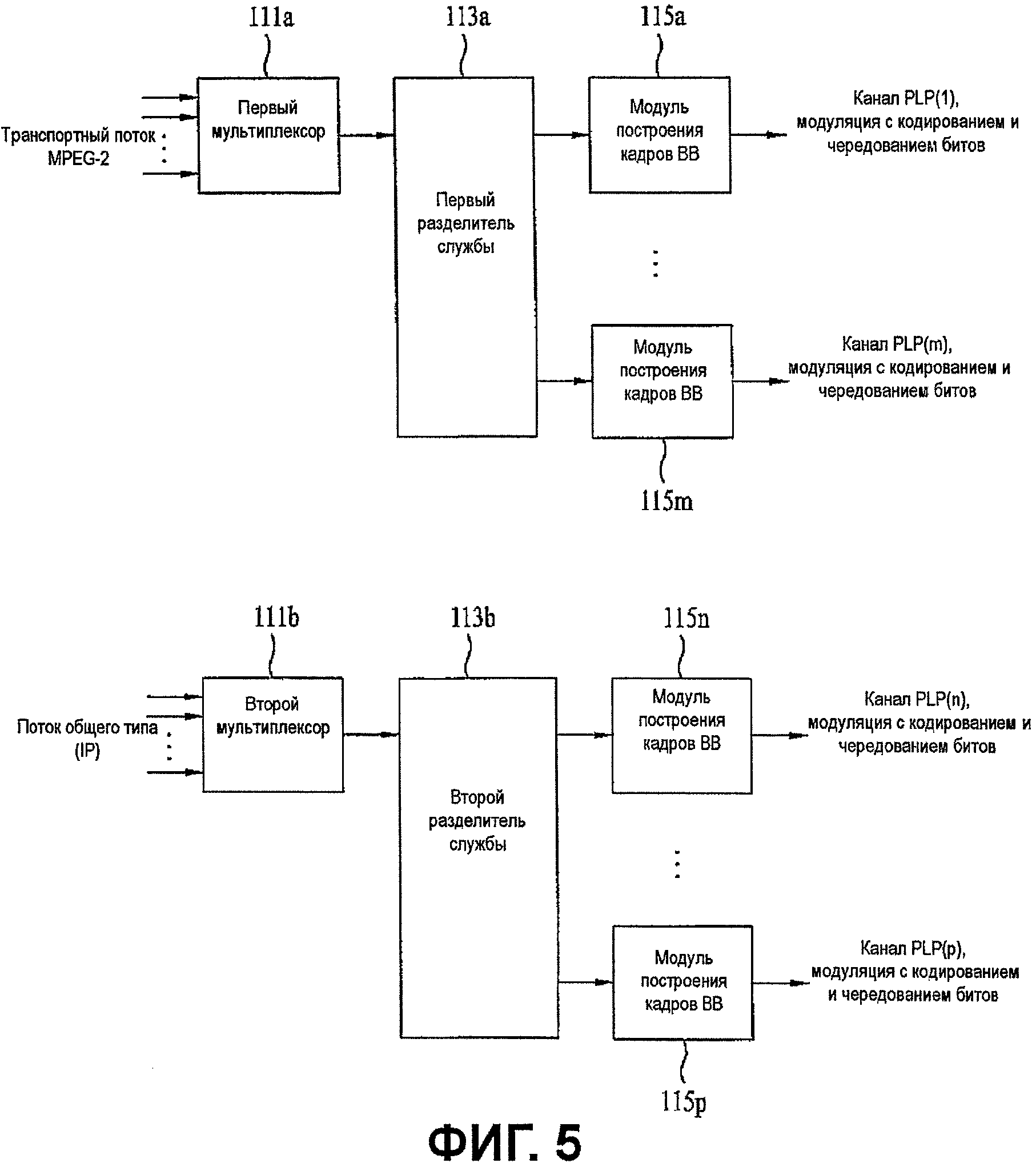

Фиг.5 - изображение, показывающее пример входного процессора 110;

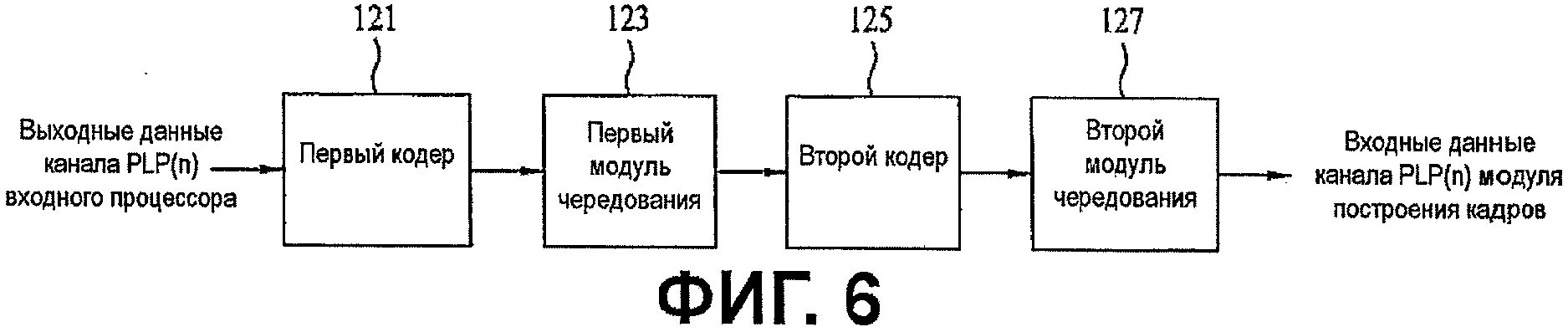

Фиг.6 - изображение, показывающее вариант воплощения модуля кодирования и модуляции;

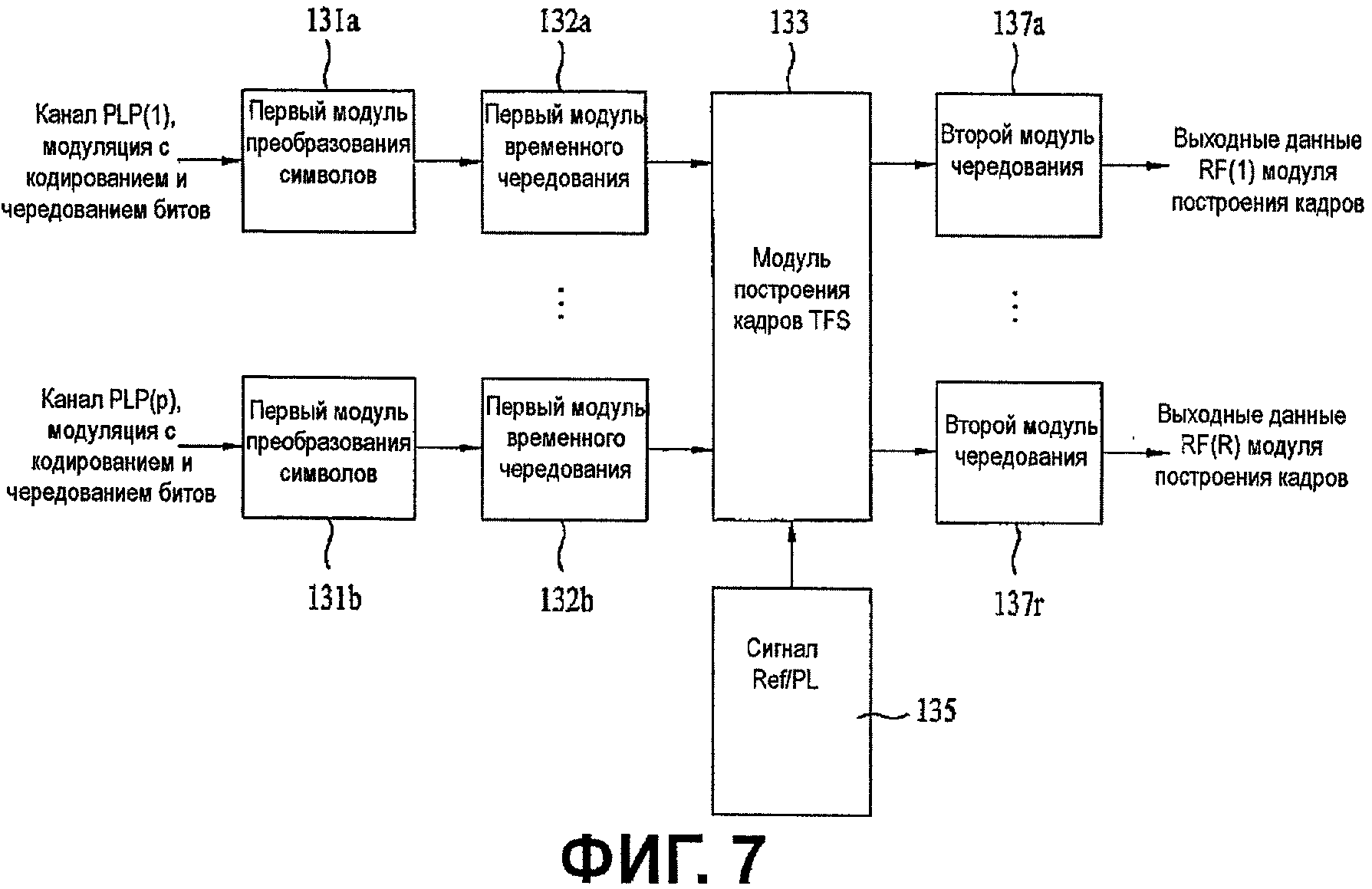

Фиг.7 - изображение, показывающее вариант воплощения модуля построения кадров;

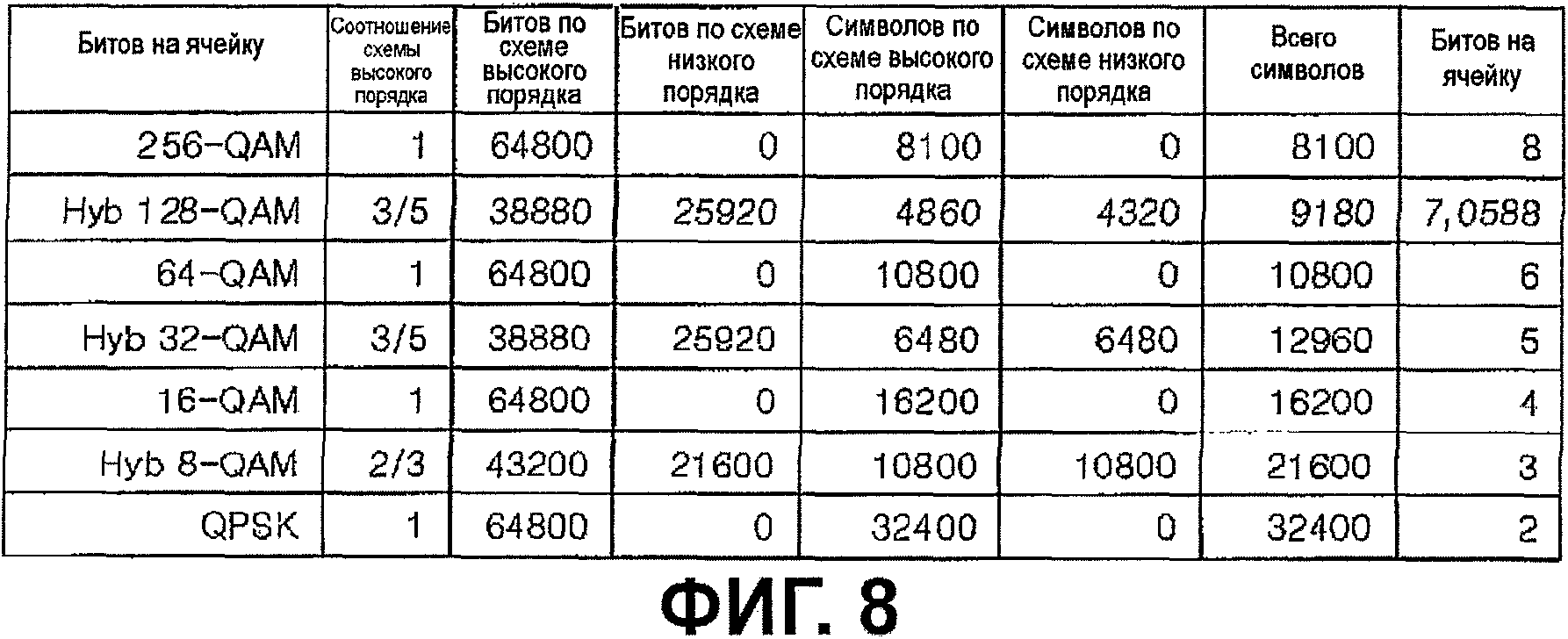

Фиг.8 - изображение, показывающее первый пример отношения символов, когда модули 131a и 131b преобразования выполняют гибридное символьное преобразование;

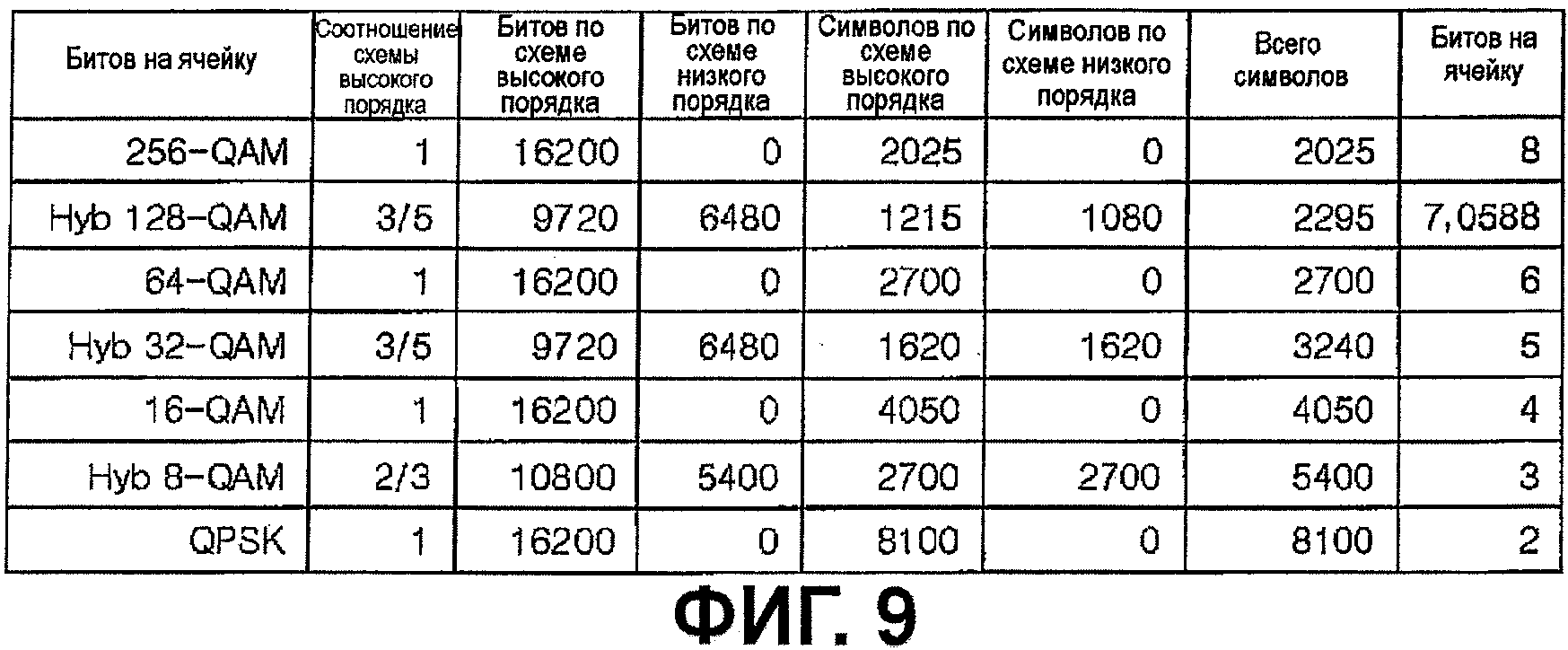

Фиг.9 - изображение, показывающее второй пример отношения символов, когда модули 131a и 131b преобразования выполняют гибридное символьное преобразование;

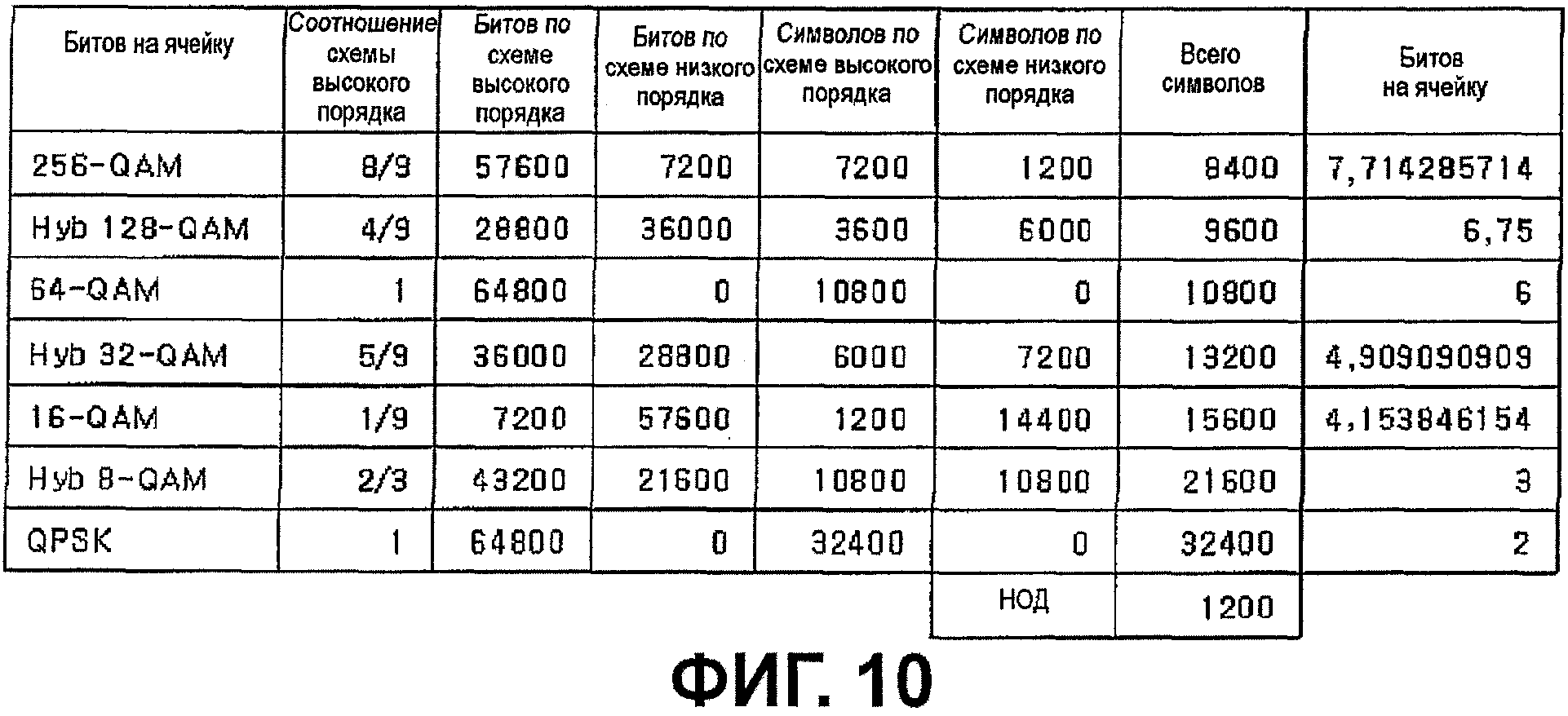

Фиг.10 - изображение, показывающее количество символов и количество битов на каждое слово ячейки в соответствии со схемой символьного преобразования в нормальном режиме кодирования LDPC;

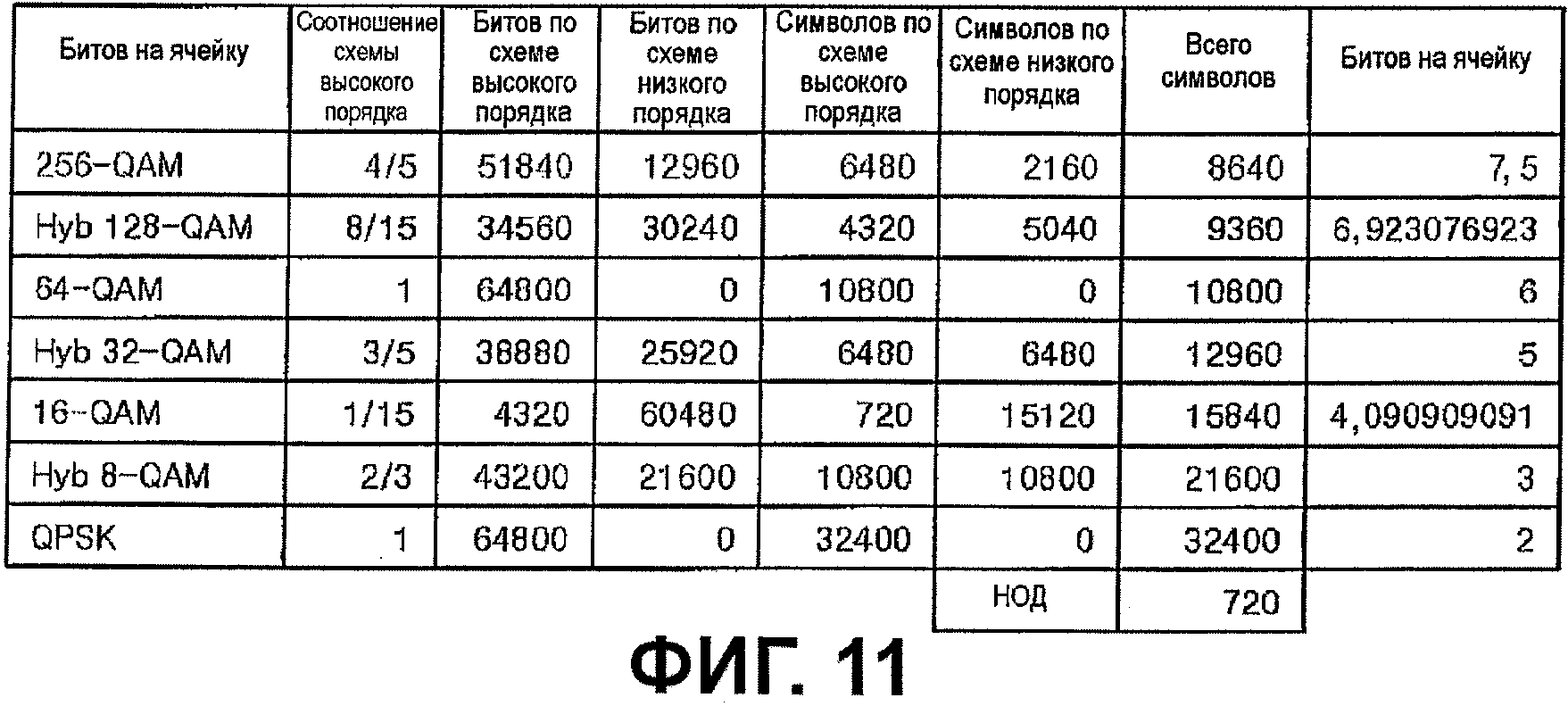

Фиг.11 - изображение, показывающее другой пример количества символов в соответствии со схемой символьного преобразования в нормальном режиме кодирования LDPC;

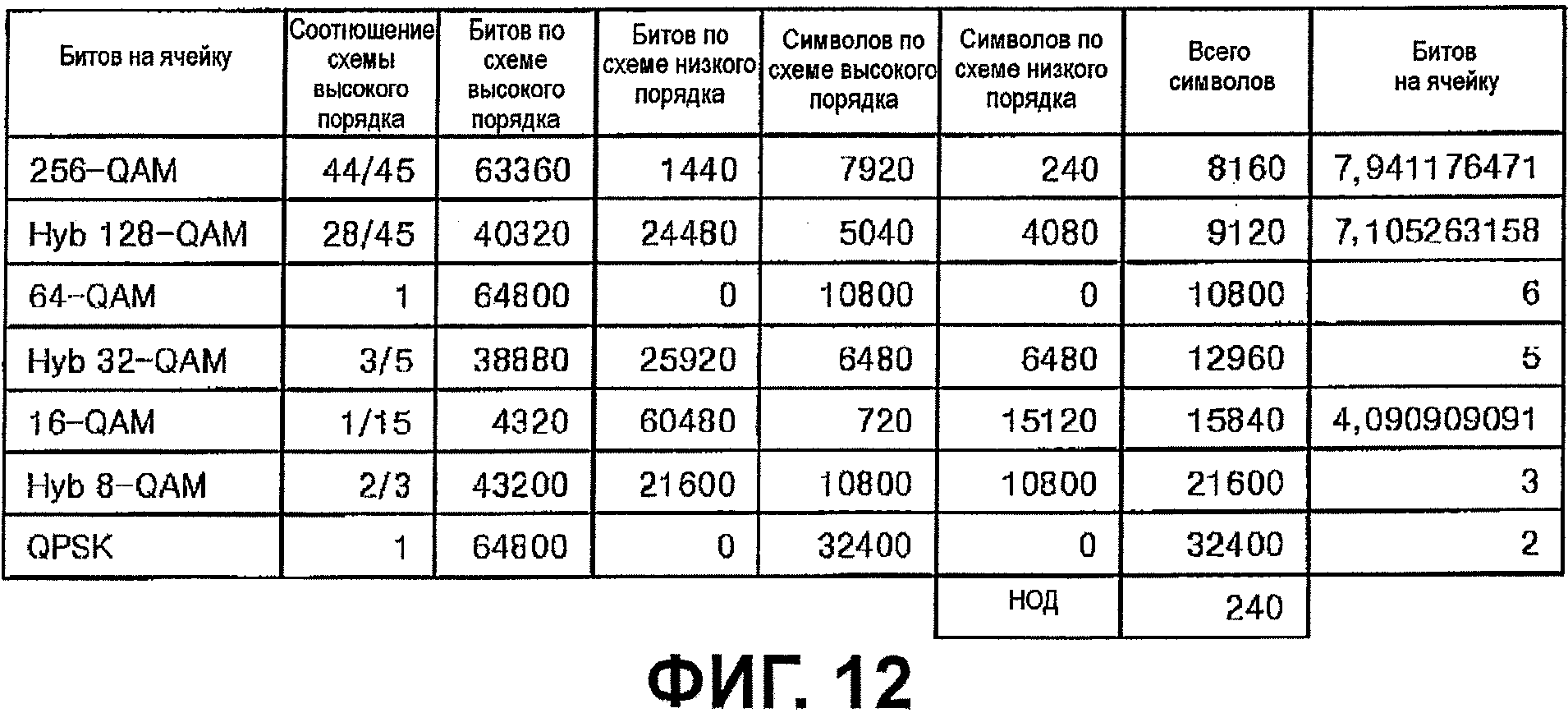

Фиг.12 - изображение, показывающее другой пример количества символов в соответствии со схемой символьного преобразования в нормальном режиме кодирования LDPC;

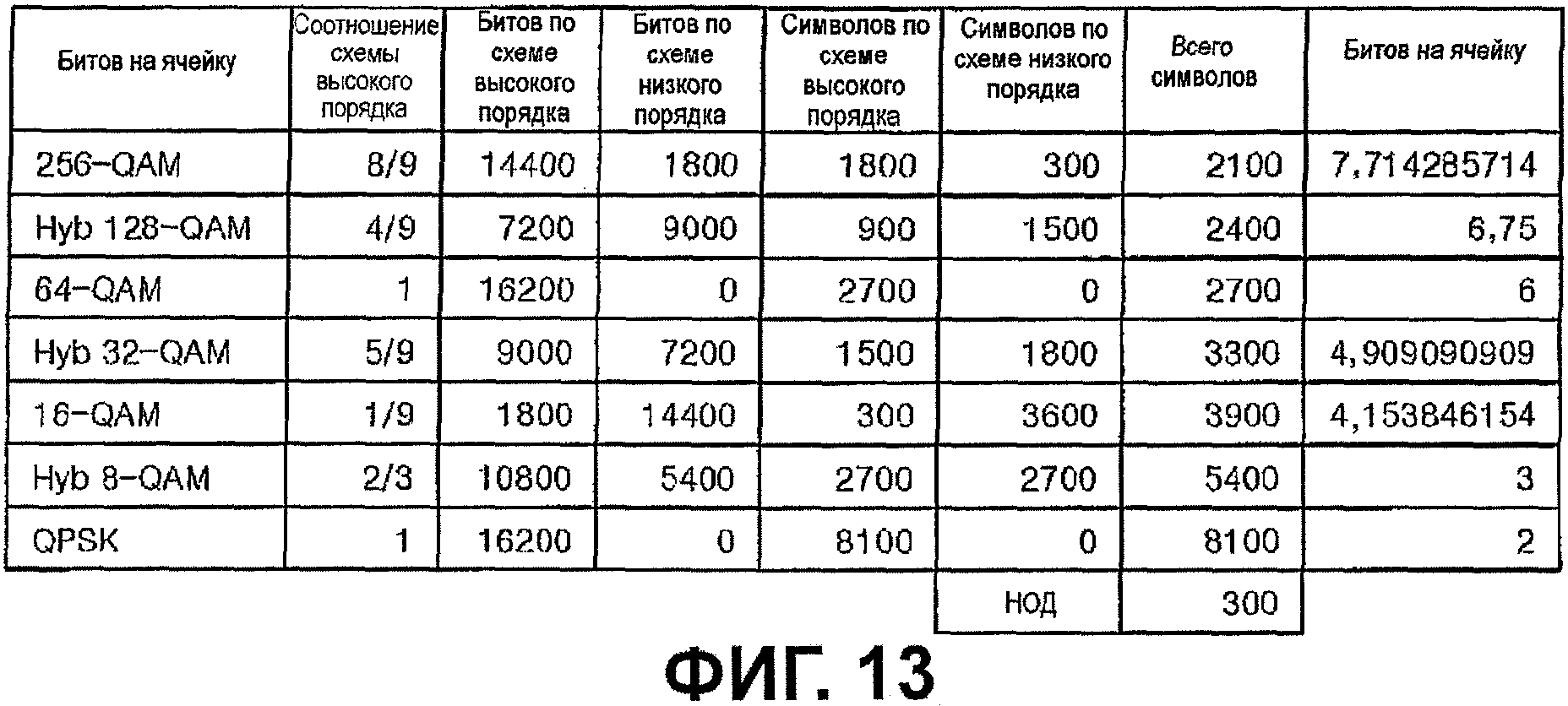

Фиг.13 - изображение, показывающее количество символов в соответствии со схемой символьного преобразования в коротком режиме кодирования LDPC;

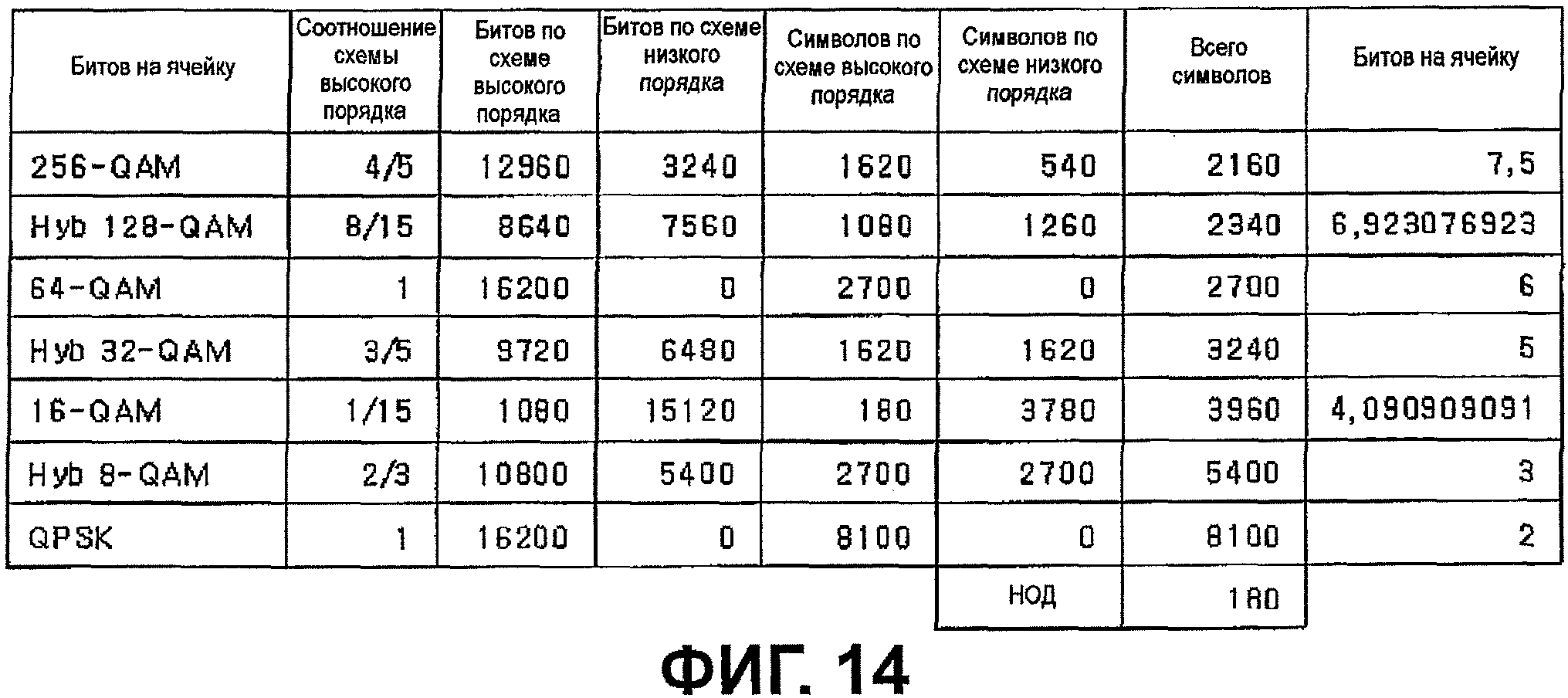

Фиг.14 - изображение, показывающее пример количества символов в соответствии со схемой символьного преобразования в коротком режиме кодирования LDPC;

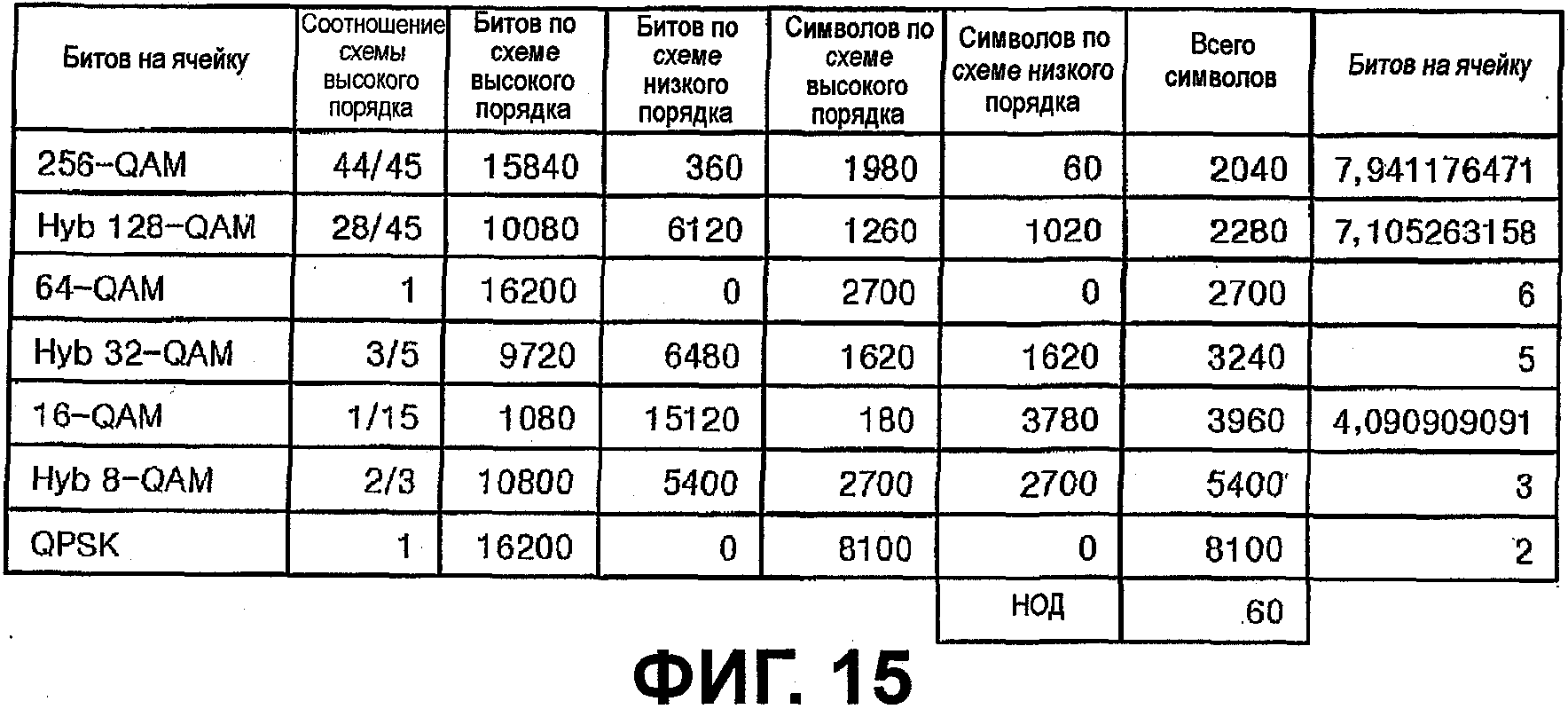

Фиг.15 - изображение, показывающее другой пример количества символов в соответствии со схемой символьного преобразования в коротком режиме кодирования LDPC;

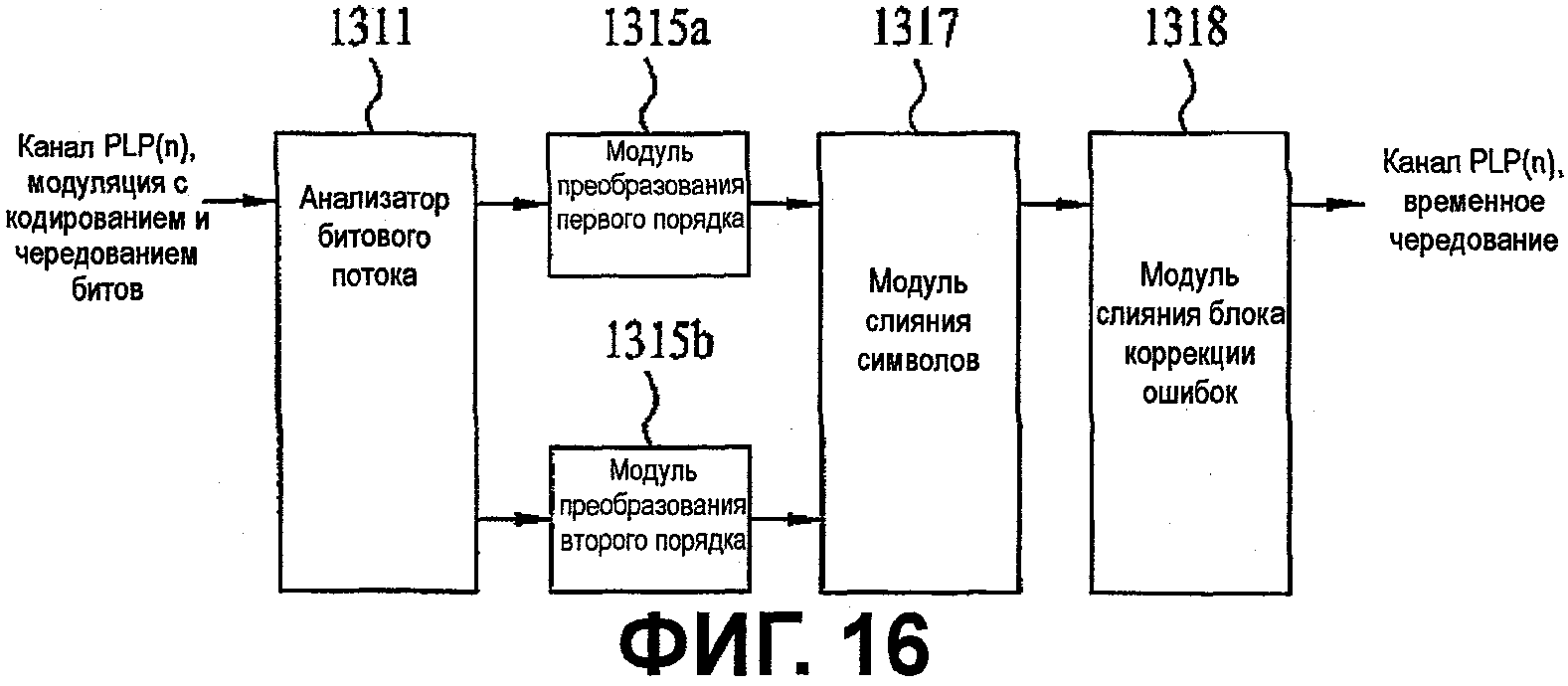

Фиг.16 - изображение, показывающее вариант воплощения каждого из модулей 131a и 131b преобразования символов, показанных на фиг.7;

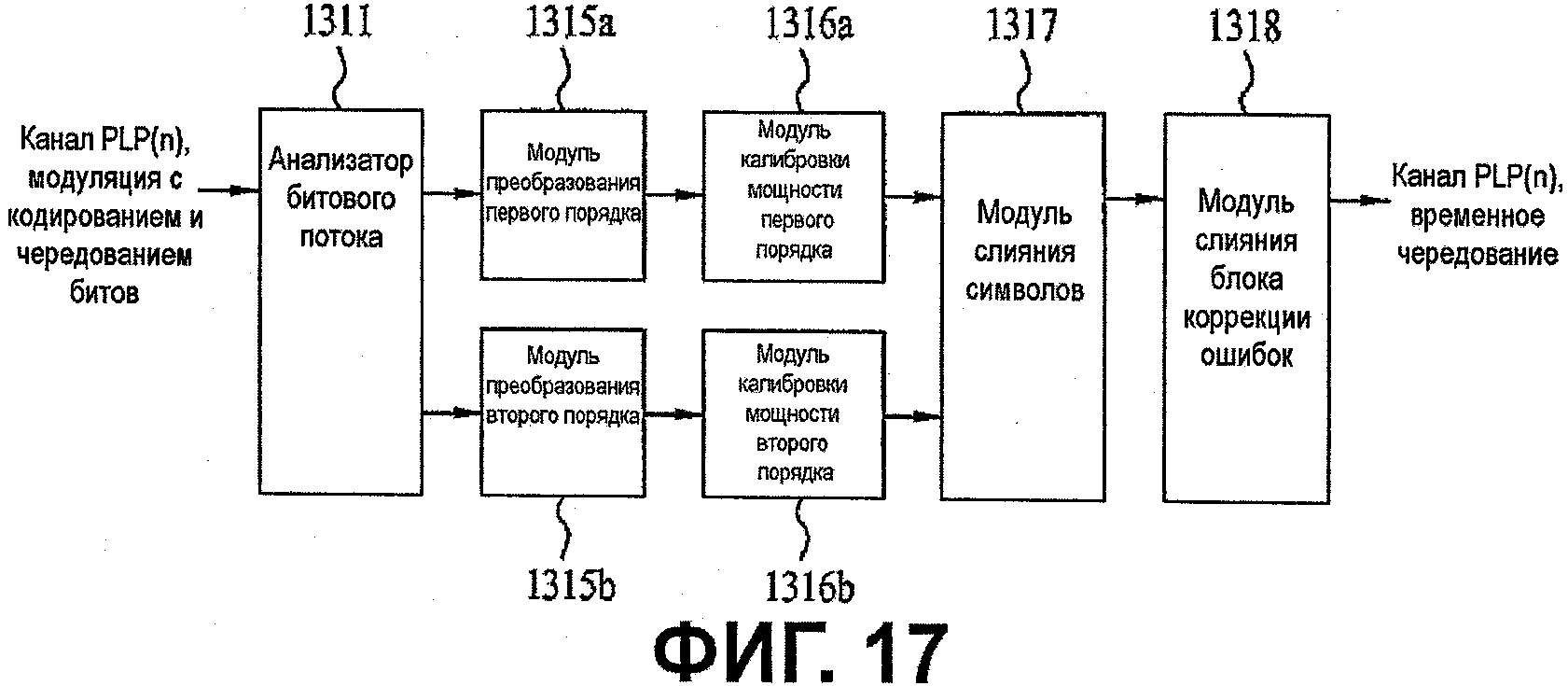

Фиг.17 - изображение, показывающее другой вариант воплощения каждого из модулей 131a и 131b преобразования символов;

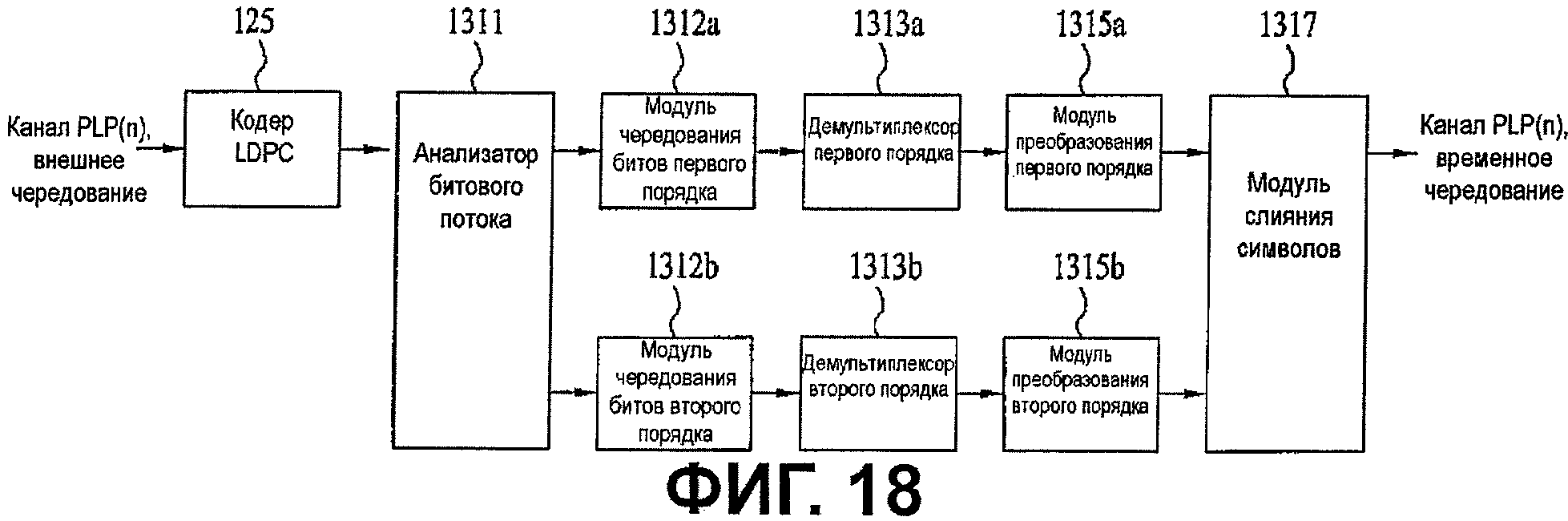

Фиг.18 - изображение, показывающее другой вариант воплощения модуля преобразования символов;

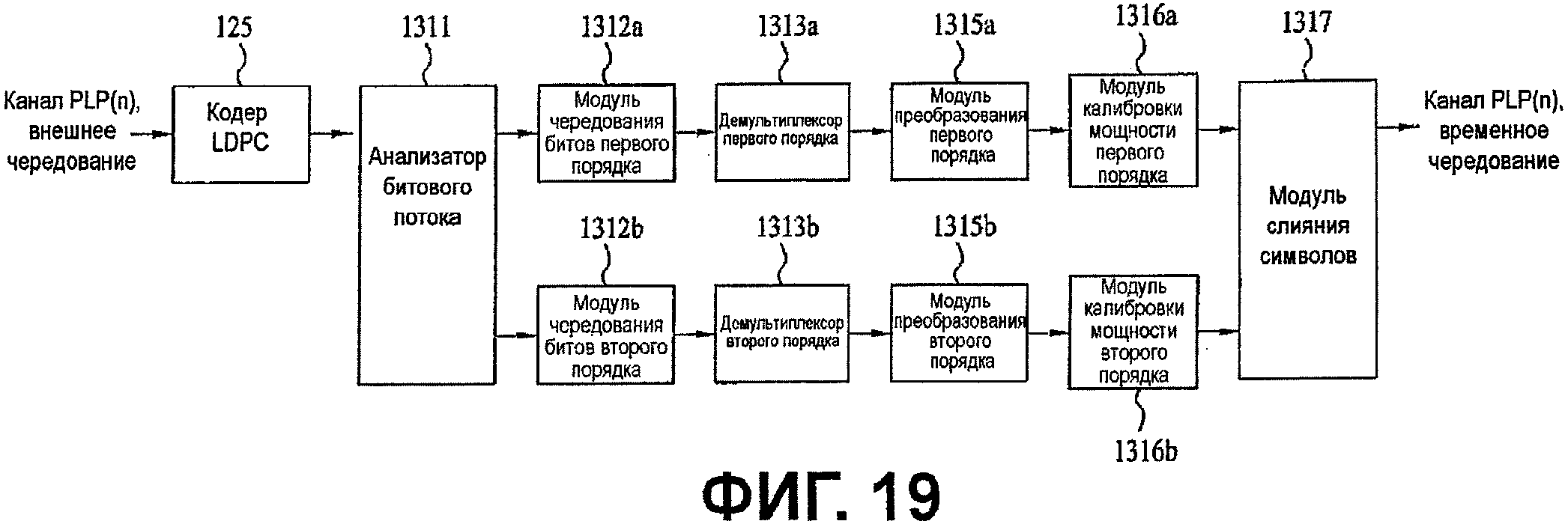

Фиг.19 - изображение, показывающее другой вариант воплощения каждого из модулей 131a и 131b преобразования символов;

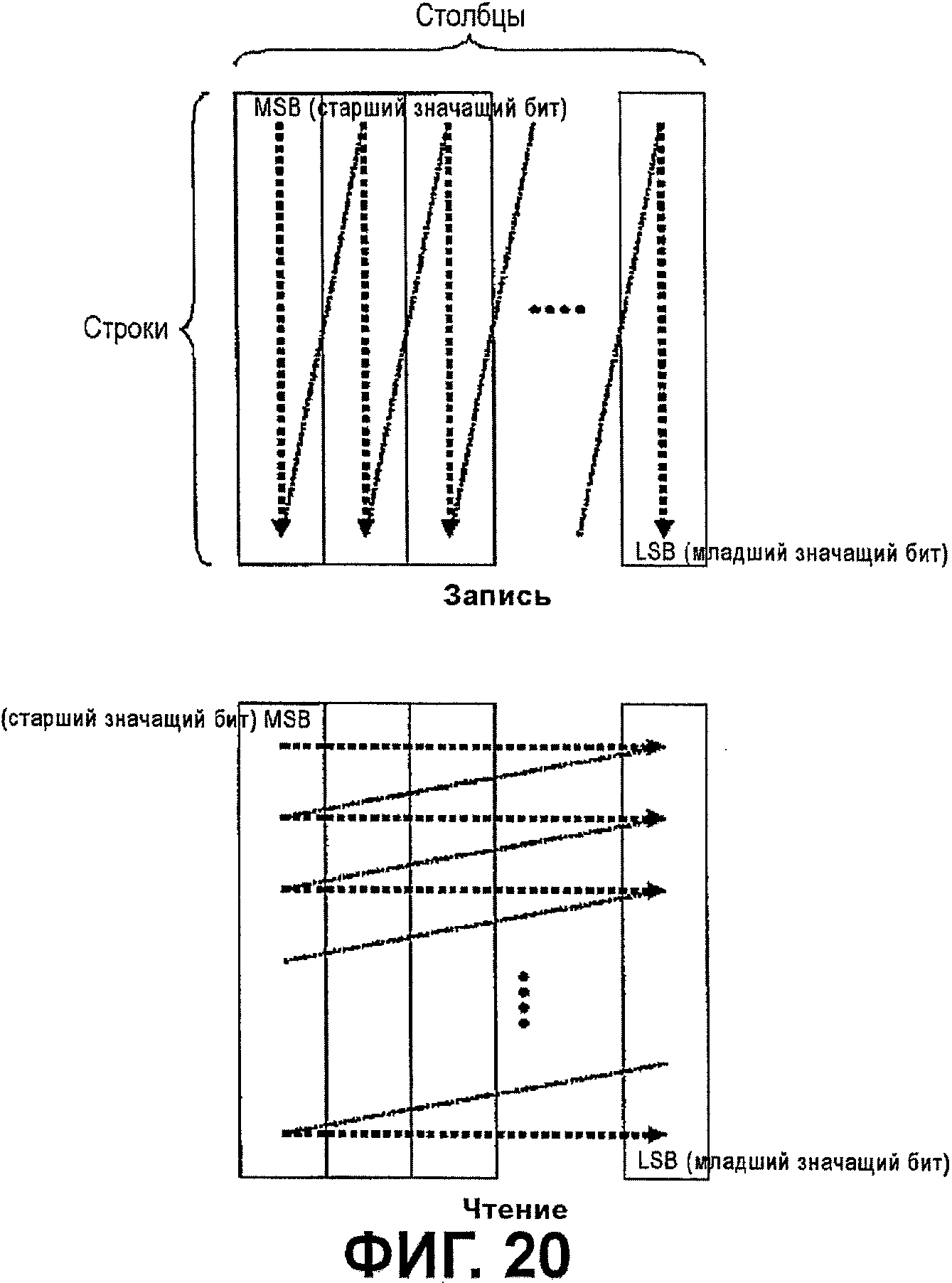

Фиг.20 - изображение, показывающее концепцию чередования битов посредством модулей 1312a и 1312b чередования битов;

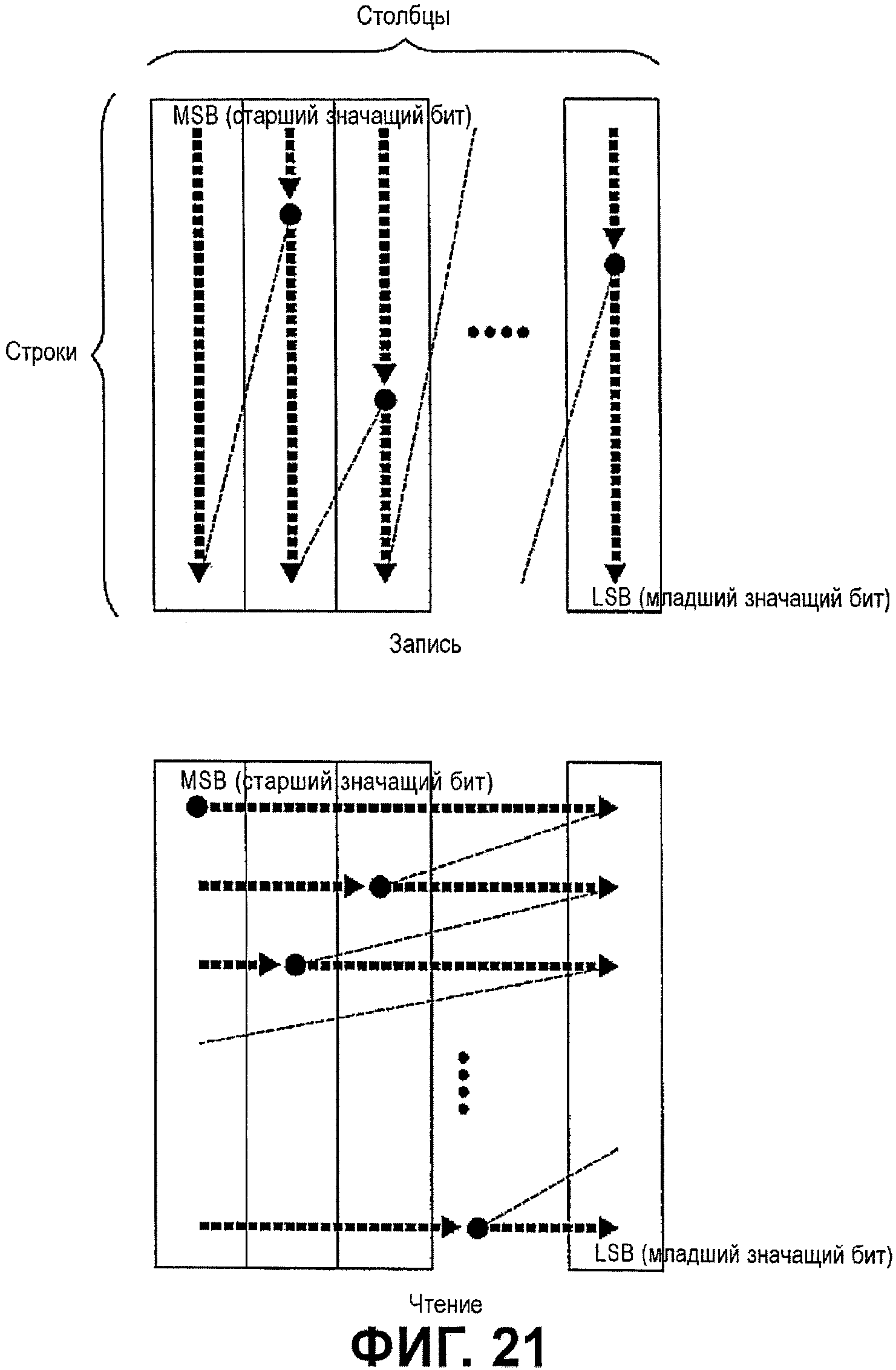

Фиг.21 иллюстрирует другой пример модулей чередования битов, которые выполняют чередование;

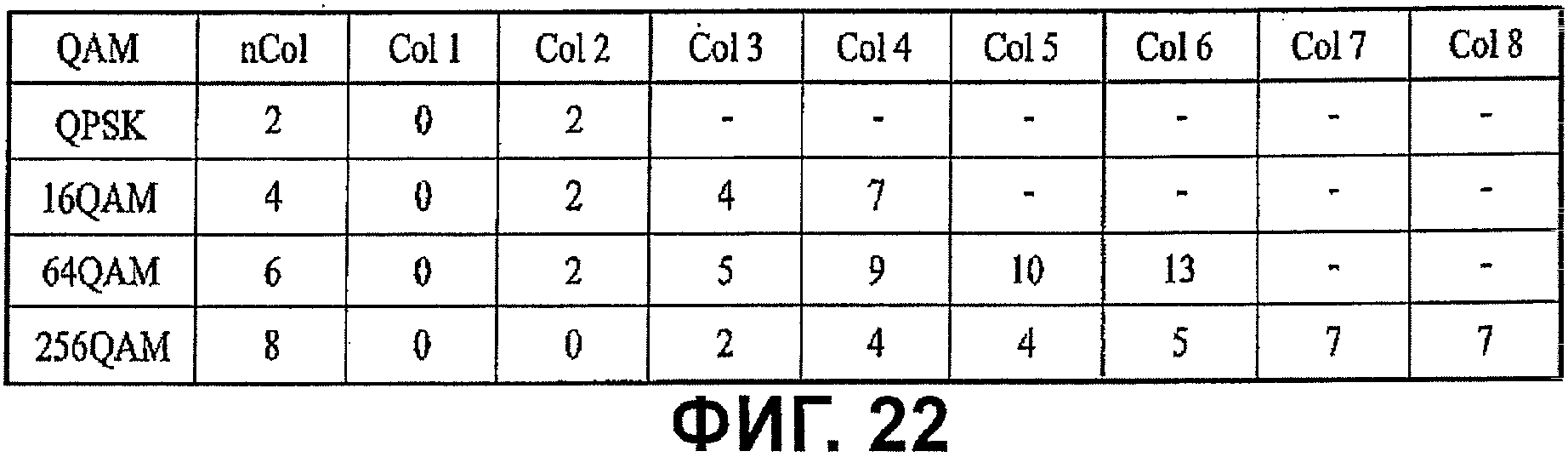

Фиг.22 иллюстрирует смещение, используемое при чередовании битов в соответствии со способом символьного преобразования;

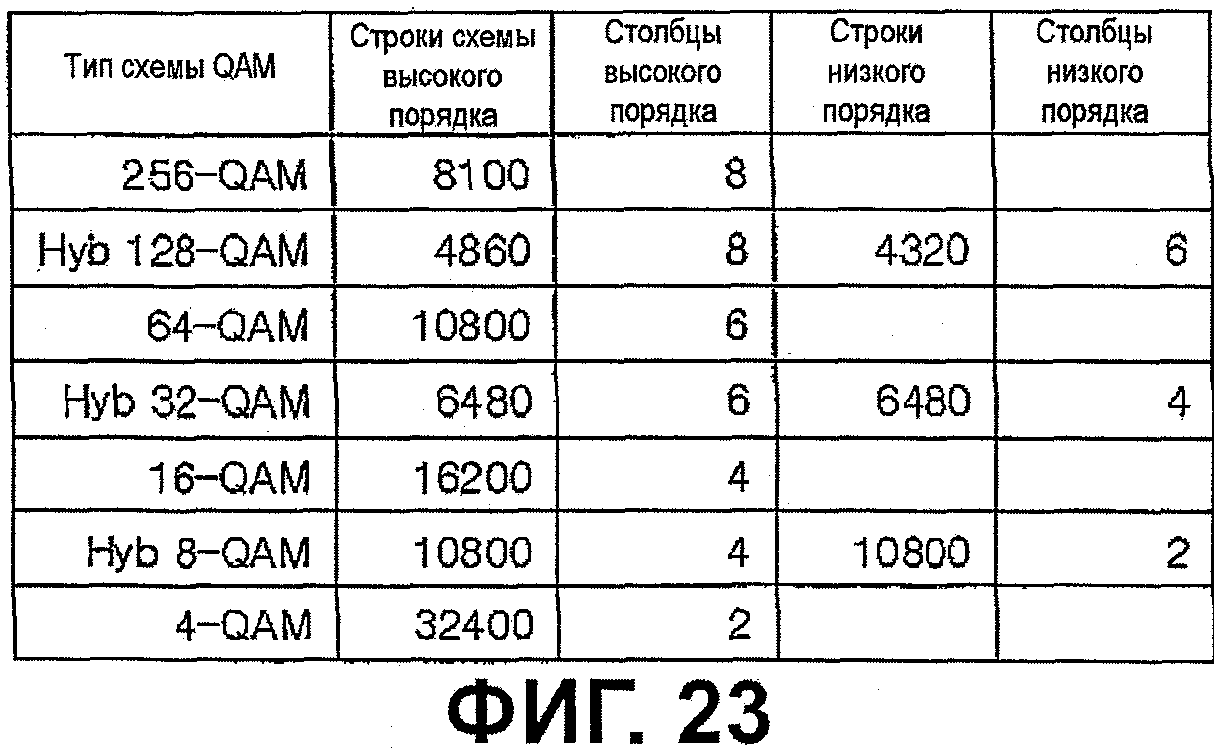

Фиг.23 - изображение, показывающее первый пример количества строк и столбцов блоков памяти модулей 1312a и 1312b чередования битов в соответствии с типами модулей 1315a и 1315b преобразования символов;

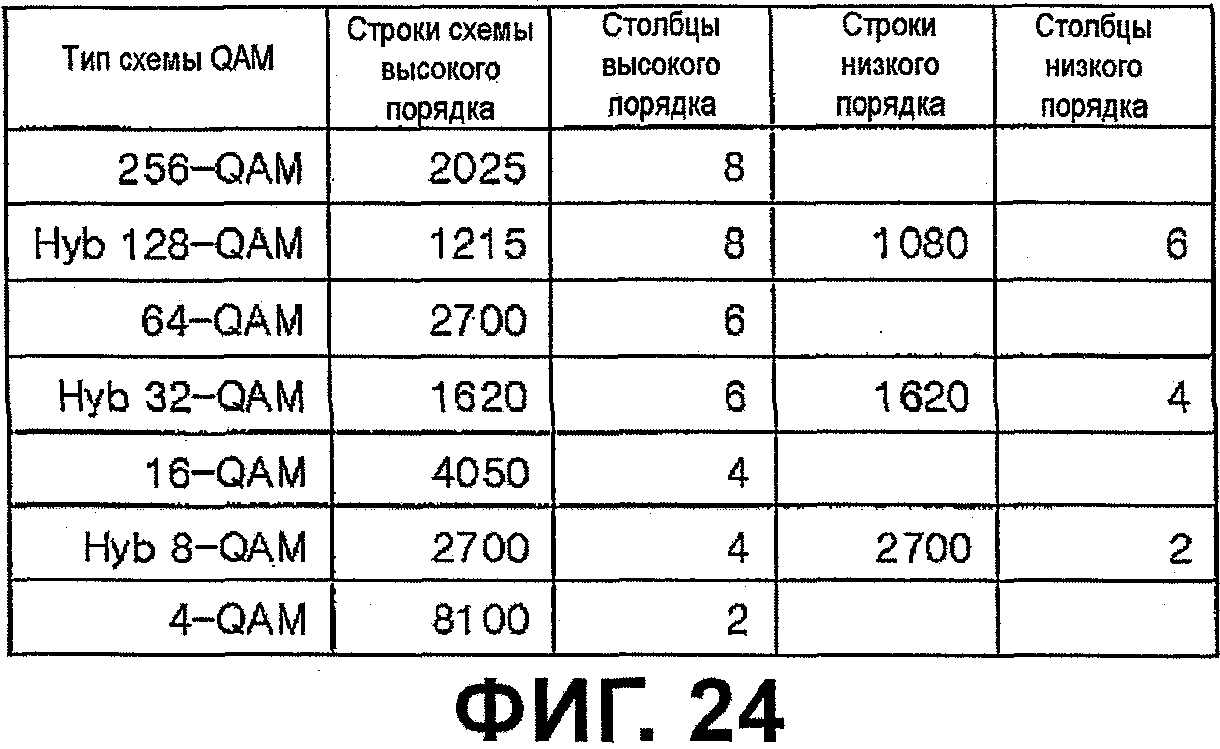

Фиг.24 - изображение, показывающее второй пример количества строк и столбцов блоков памяти модулей 1312a и 1312b чередования битов в соответствии с типами модулей 1315a и 1315b преобразования символов;

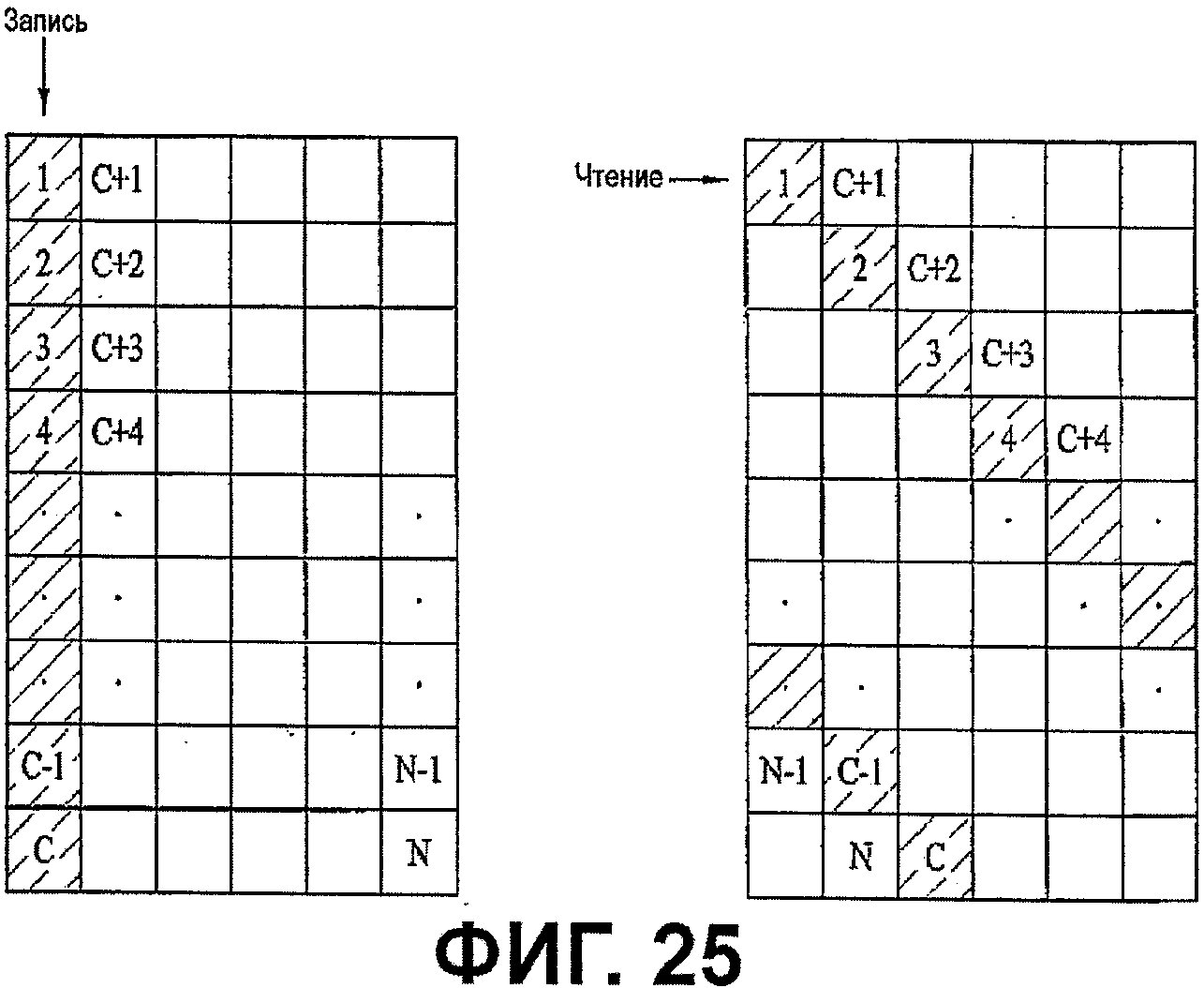

Фиг.25 - схема, показывающая концепцию другого варианта воплощения чередования модуля чередования битов;

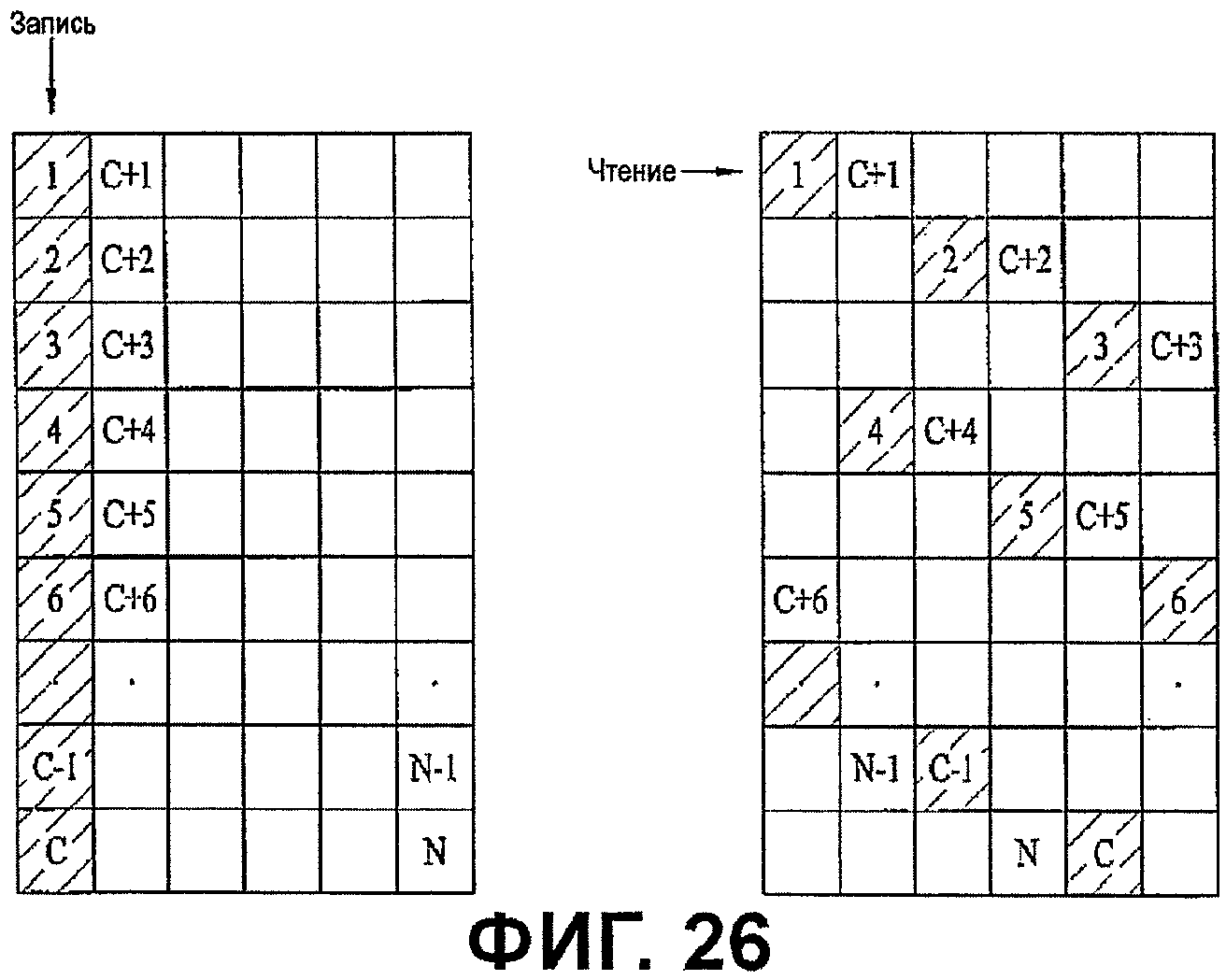

Фиг.26 - изображение, показывающее другой вариант воплощения чередования битов;

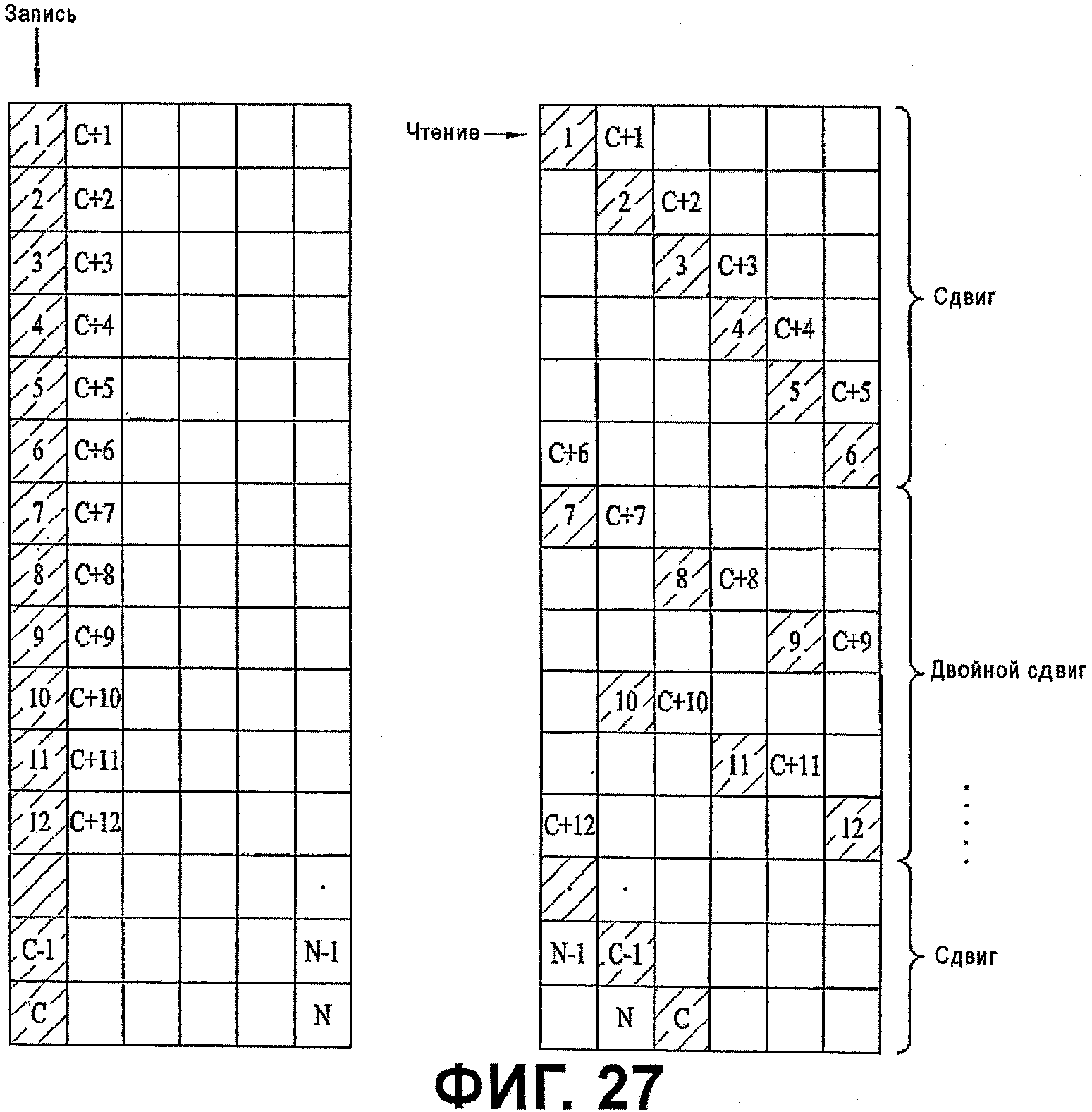

Фиг.27 - изображение, показывающее другой вариант воплощения чередования битов;

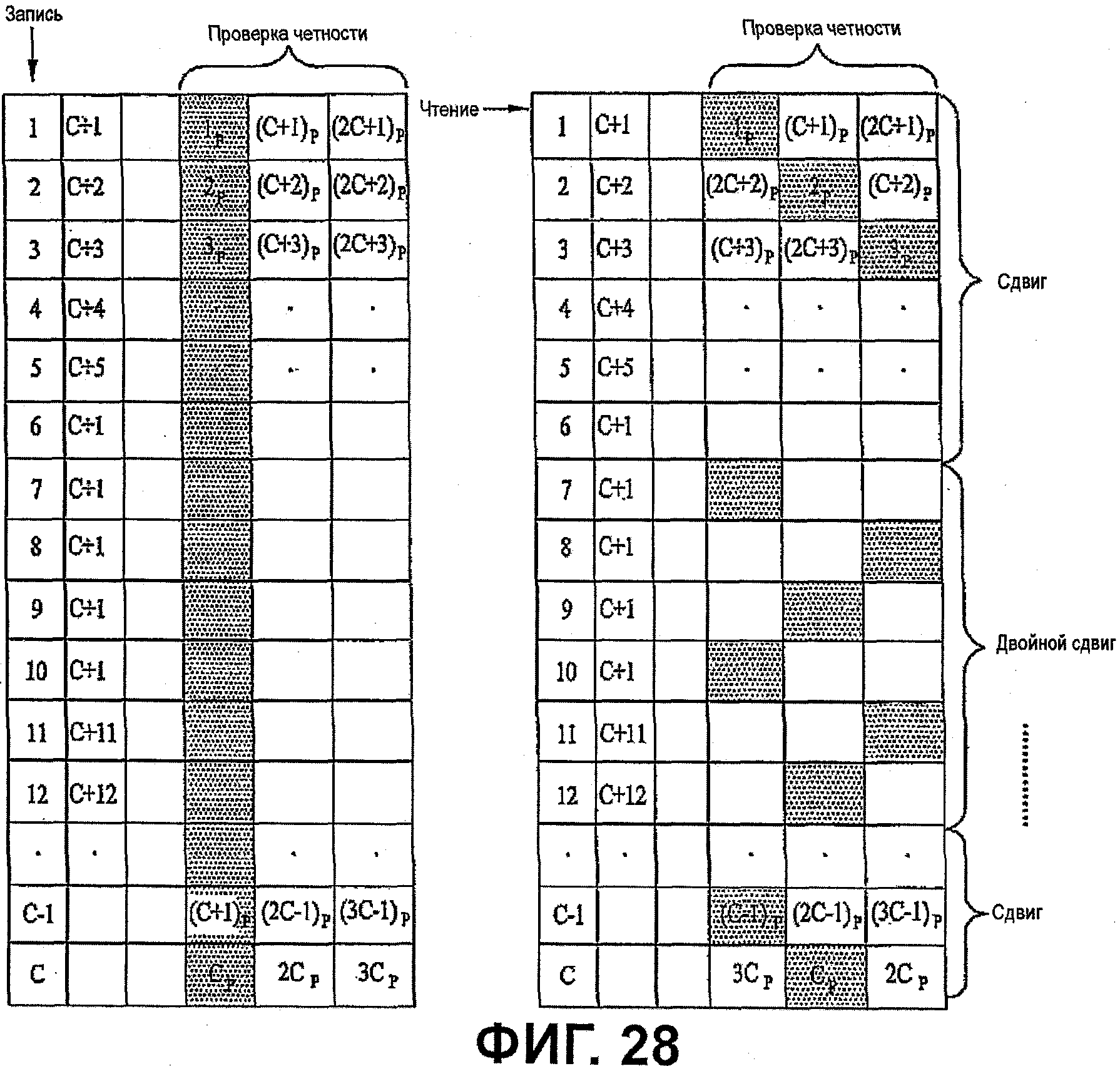

Фиг.28 - изображение, показывающее другой вариант воплощения чередования битов;

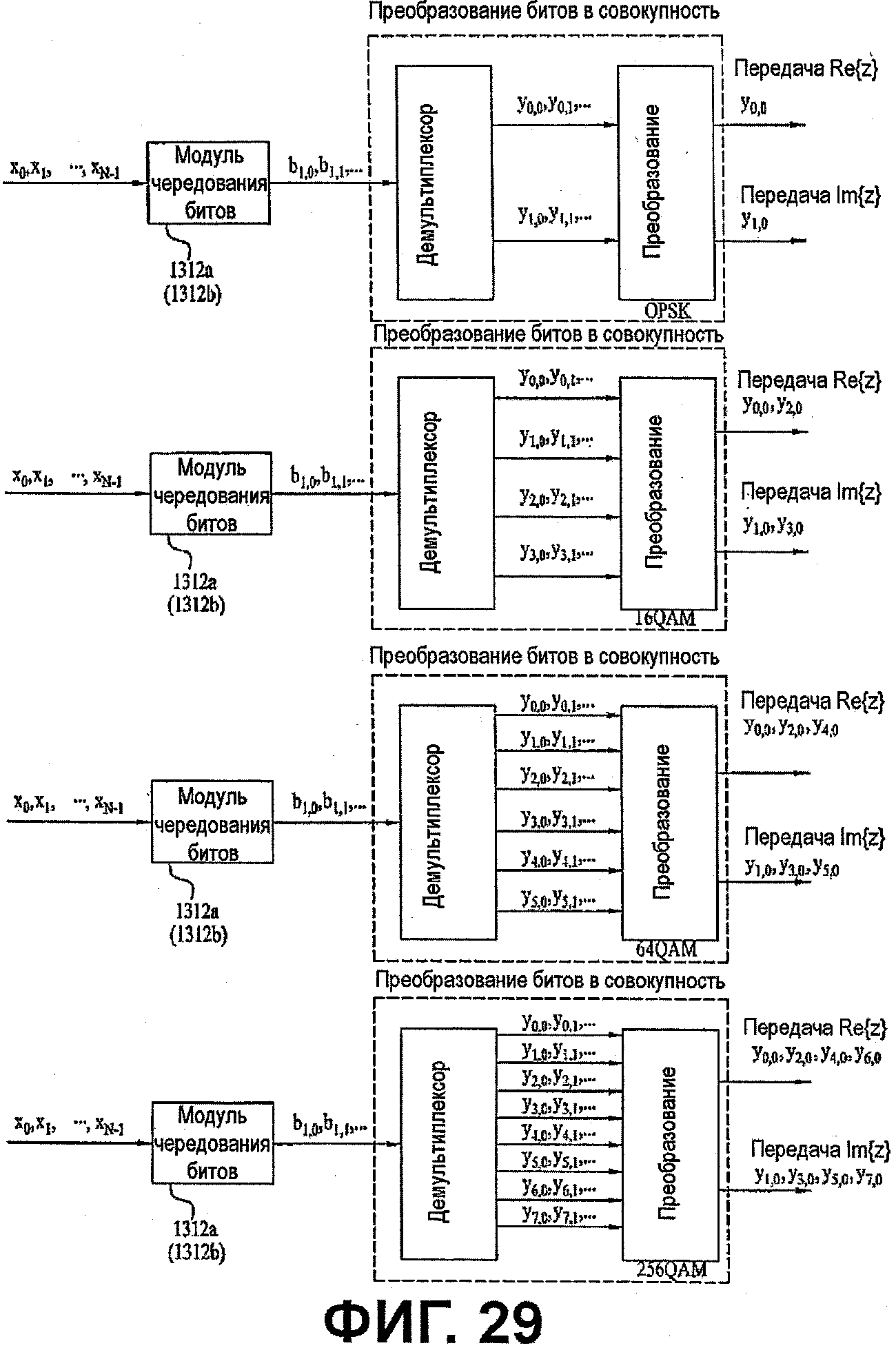

Фиг.29 - изображение, показывающее концепцию демультиплексирования входных битов демультиплексоров 1313a и 1313b;

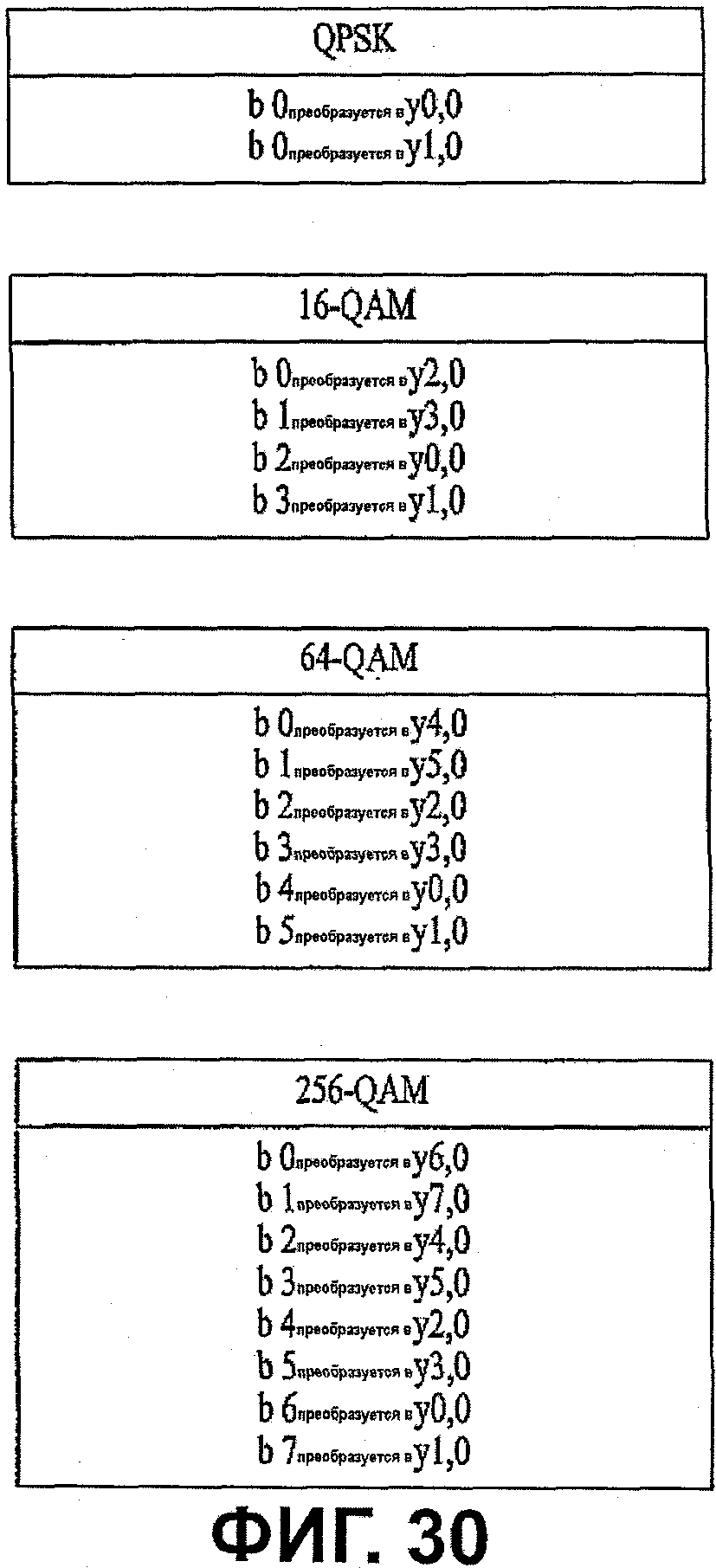

Фиг.30 - изображение, показывающее вариант воплощения демультиплексирования входного потока демультиплексором;

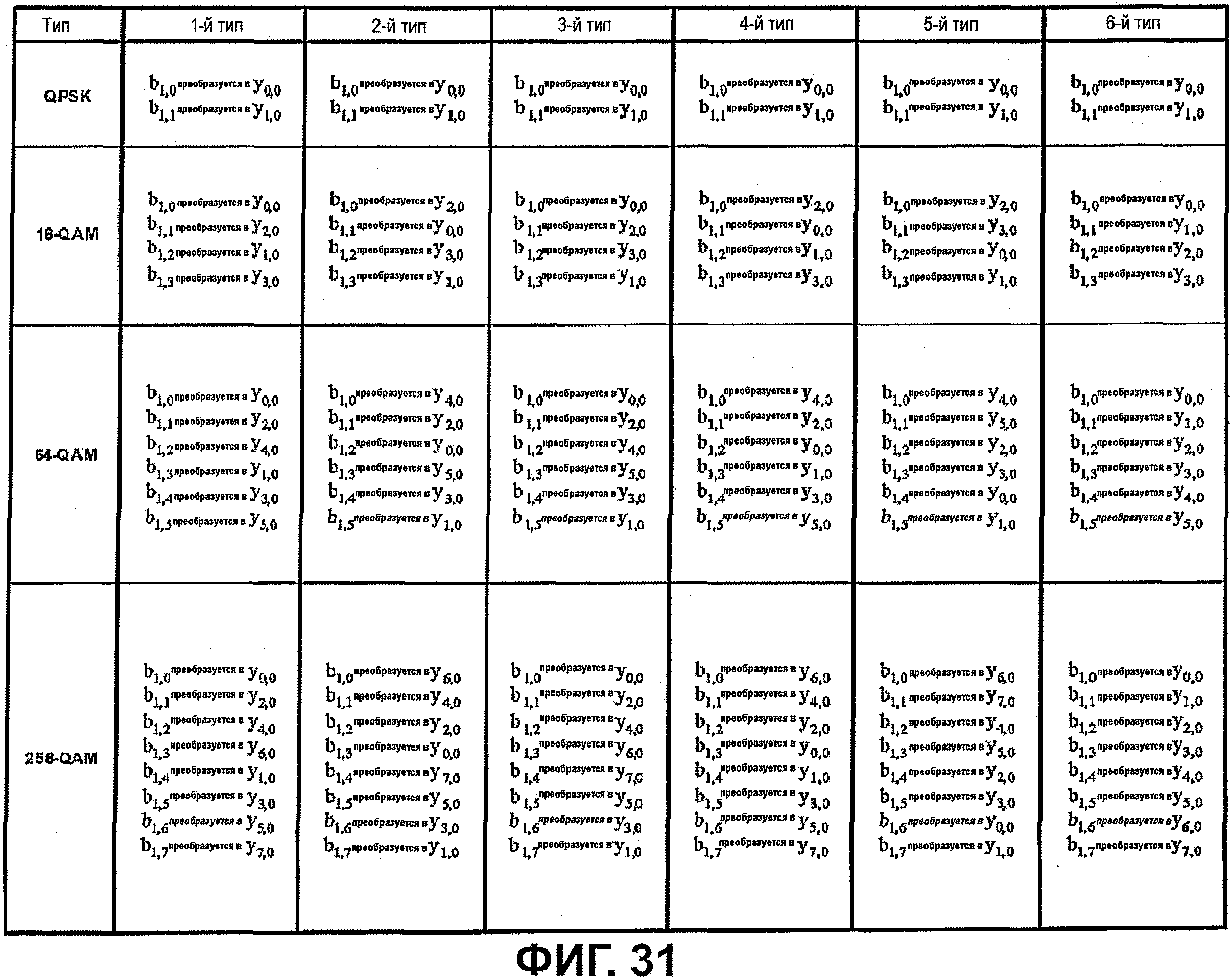

Фиг.31 - изображение, показывающее пример типа демультиплексирования в соответствии со способом символьного преобразования;

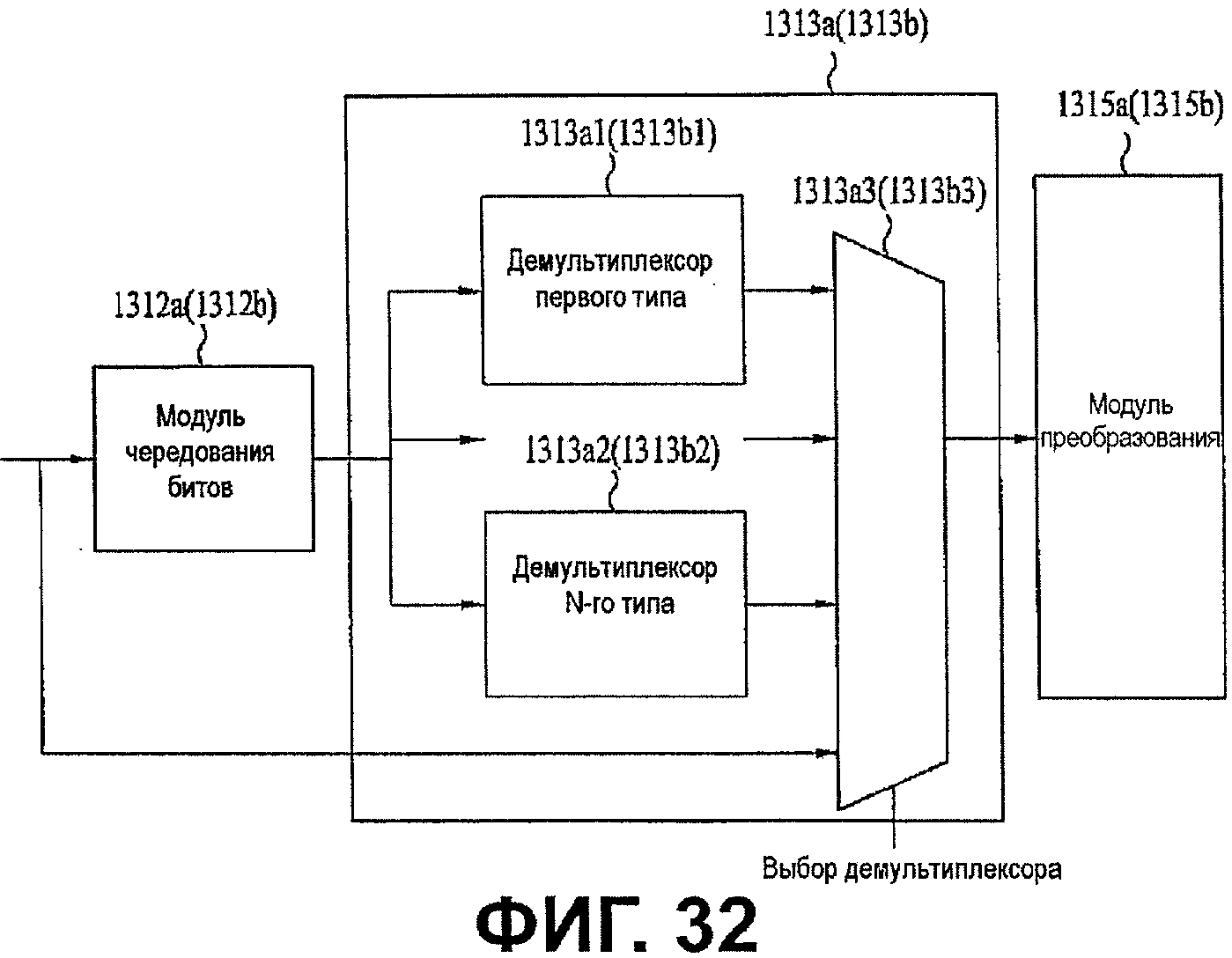

Фиг.32 - изображение, показывающее вариант воплощения демультиплексирования входного битового потока в соответствии с типом демультиплексирования;

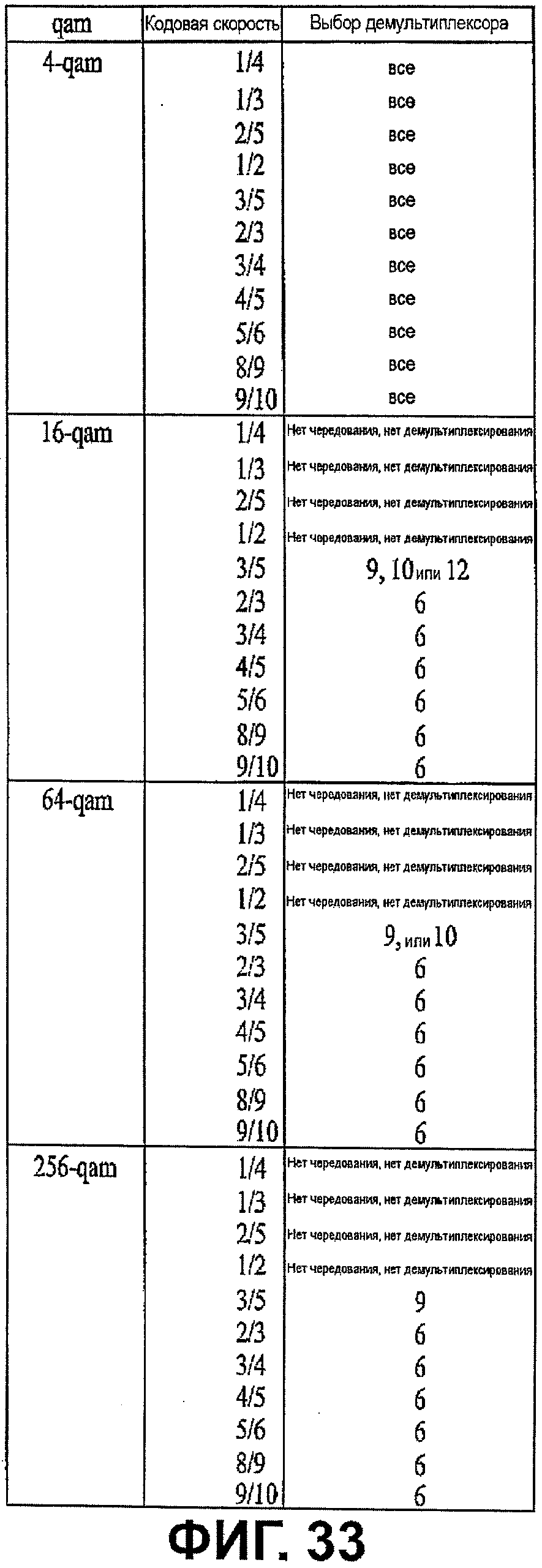

Фиг.33 - изображение, показывающее тип демультиплексирования, который определяется в соответствии с кодовой скоростью кодирования с коррекцией ошибок и способом символьного преобразования;

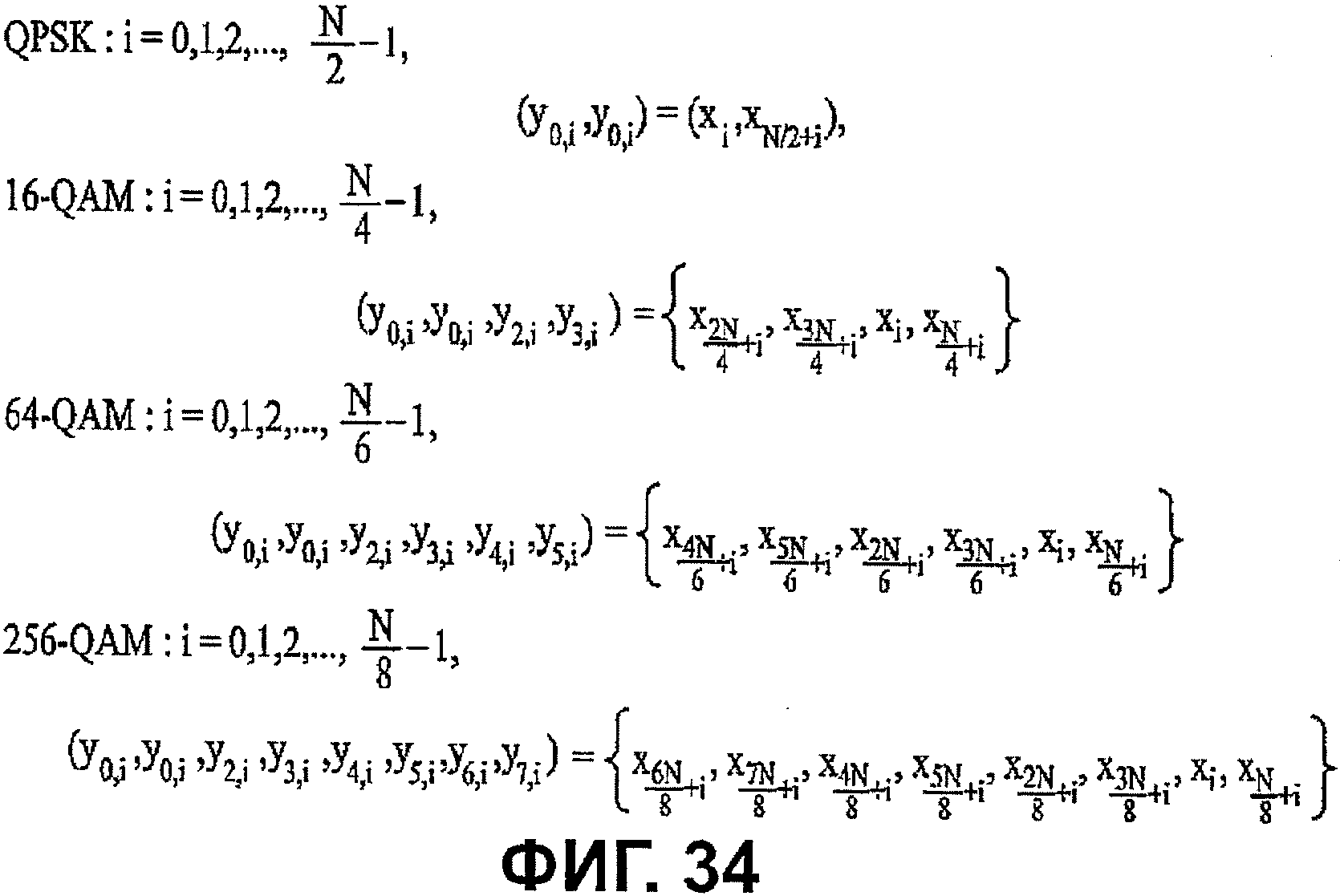

Фиг.34 - изображение, показывающее пример выражения способа демультиплексирования посредством уравнения;

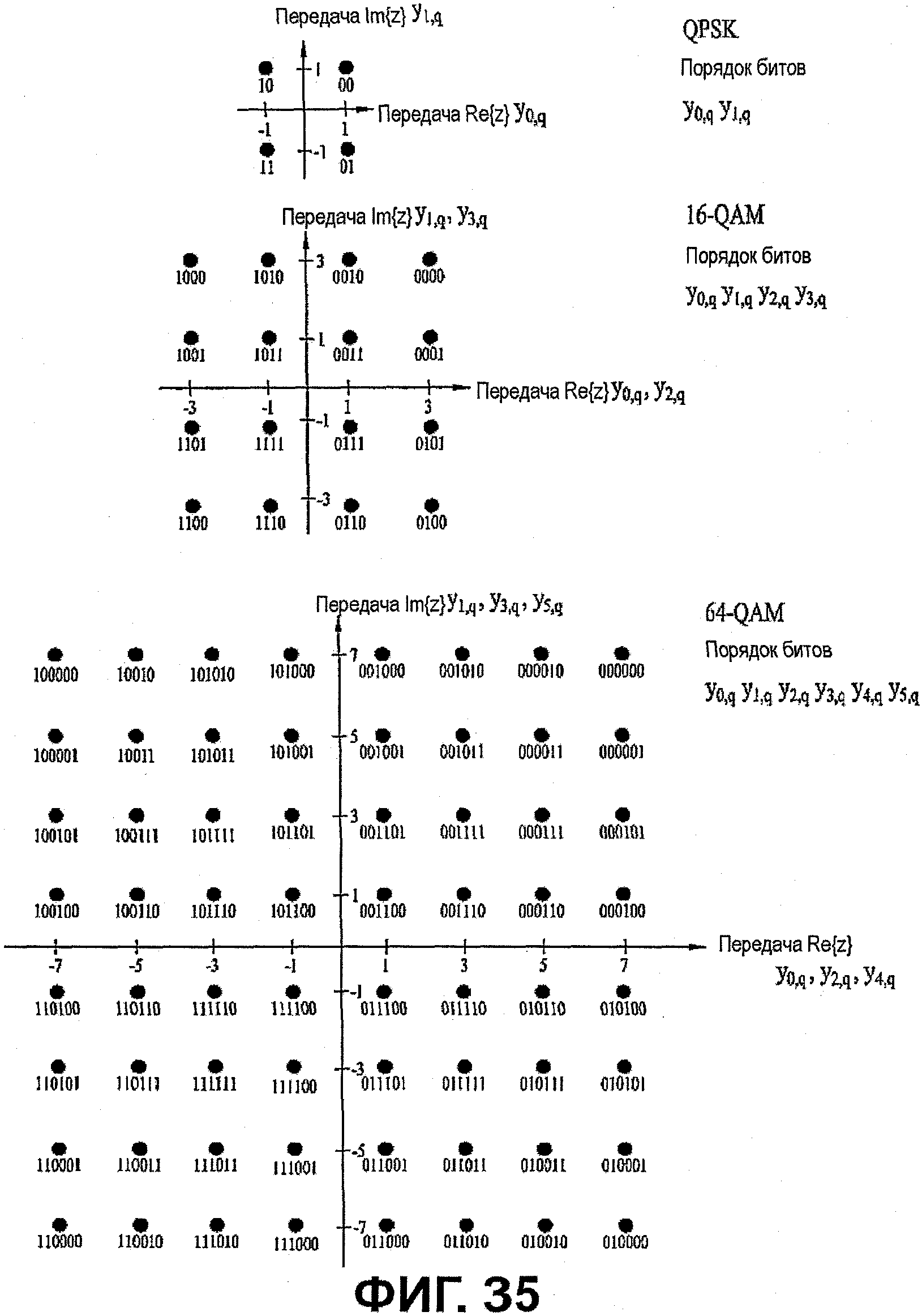

Фиг.35 - изображение, показывающее пример преобразования символа посредством модуля преобразования символов;

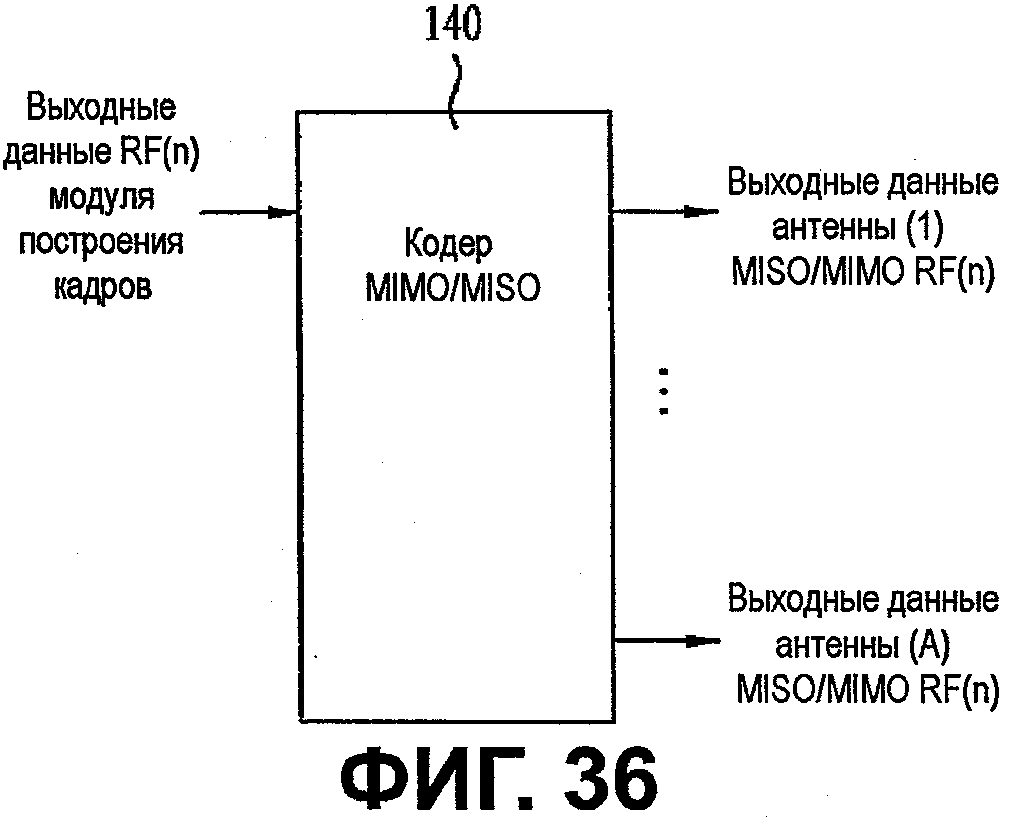

Фиг.36 - изображение, показывающее пример кодера сигнала многолучевого распространения;

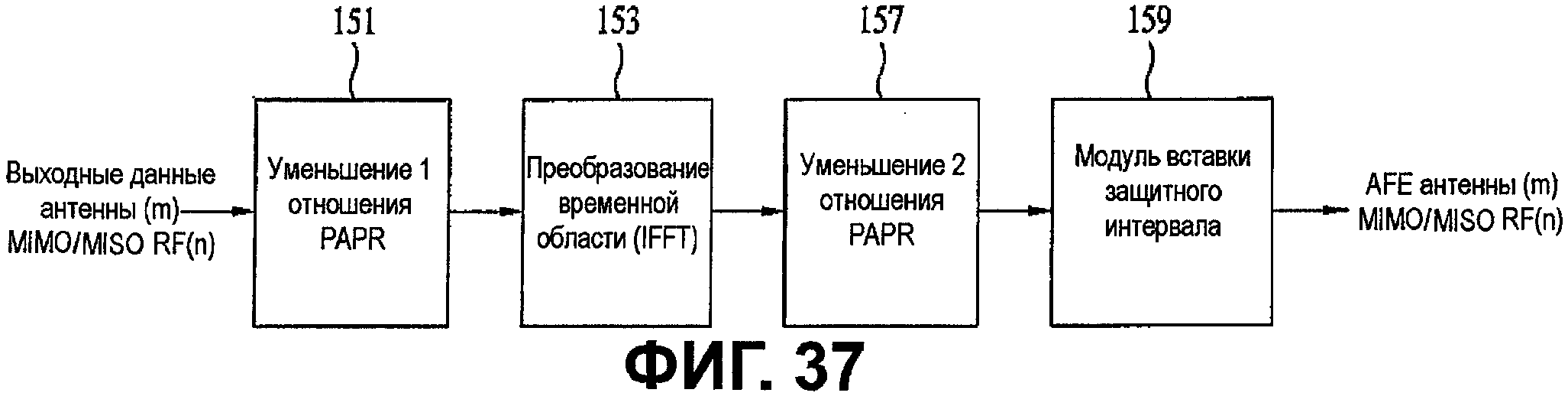

Фиг.37 - изображение, показывающее вариант воплощения модулятора;

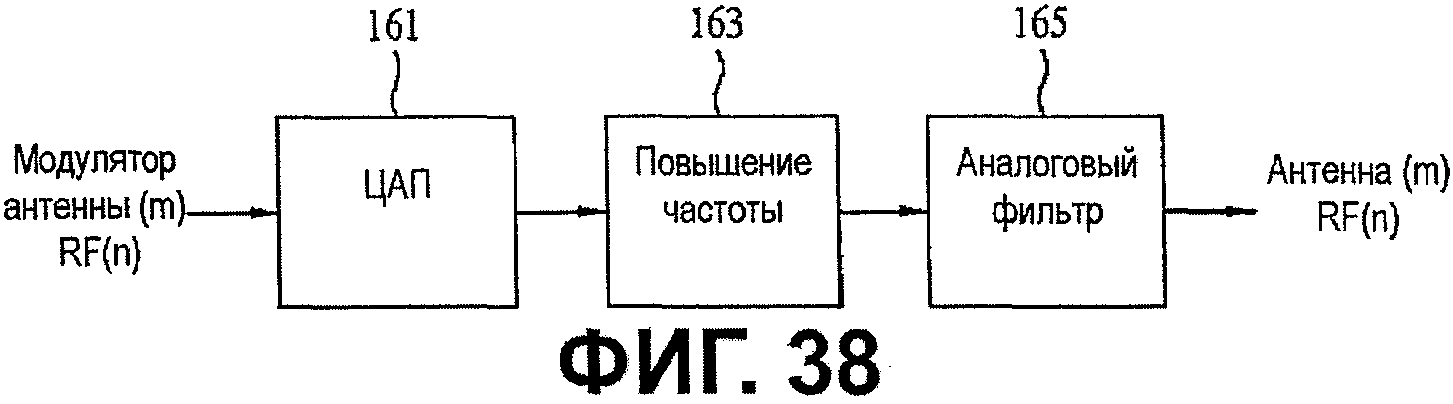

Фиг.38 - изображение, показывающее вариант воплощения аналогового процессора 160;

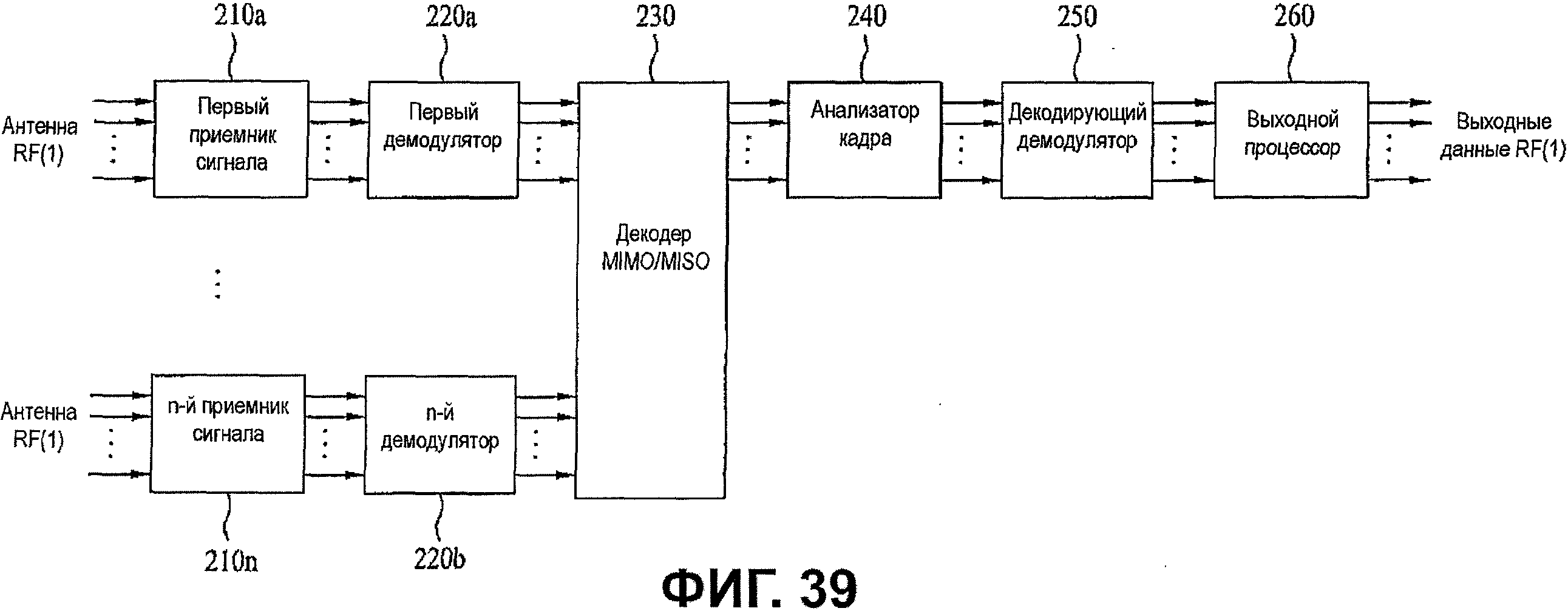

Фиг.39 - изображение, показывающее вариант воплощения устройства приема сигнала, способного принимать сигнальный кадр;

Фиг.40 - изображение, показывающее вариант воплощения приемника сигнала;

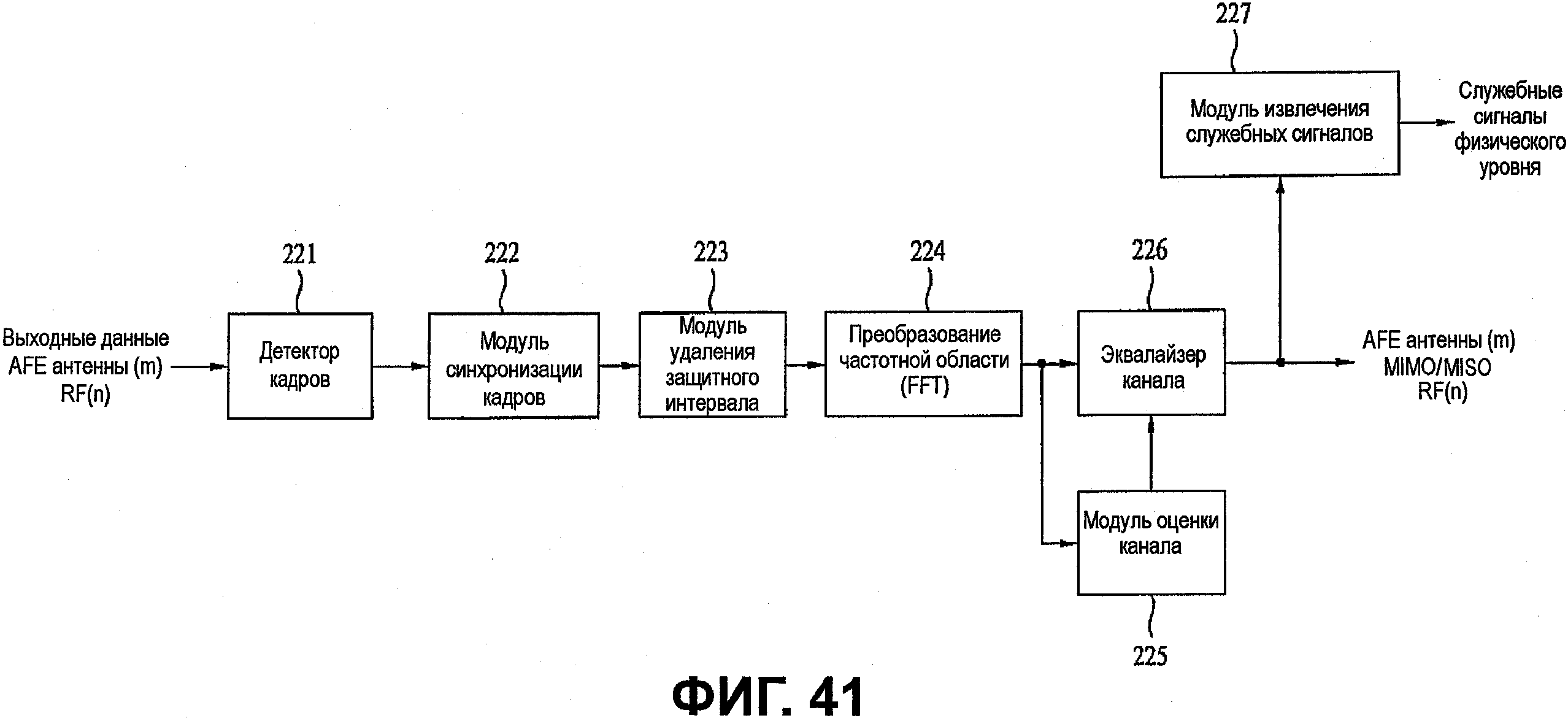

Фиг.41 - изображение, показывающее вариант воплощения демодулятора;

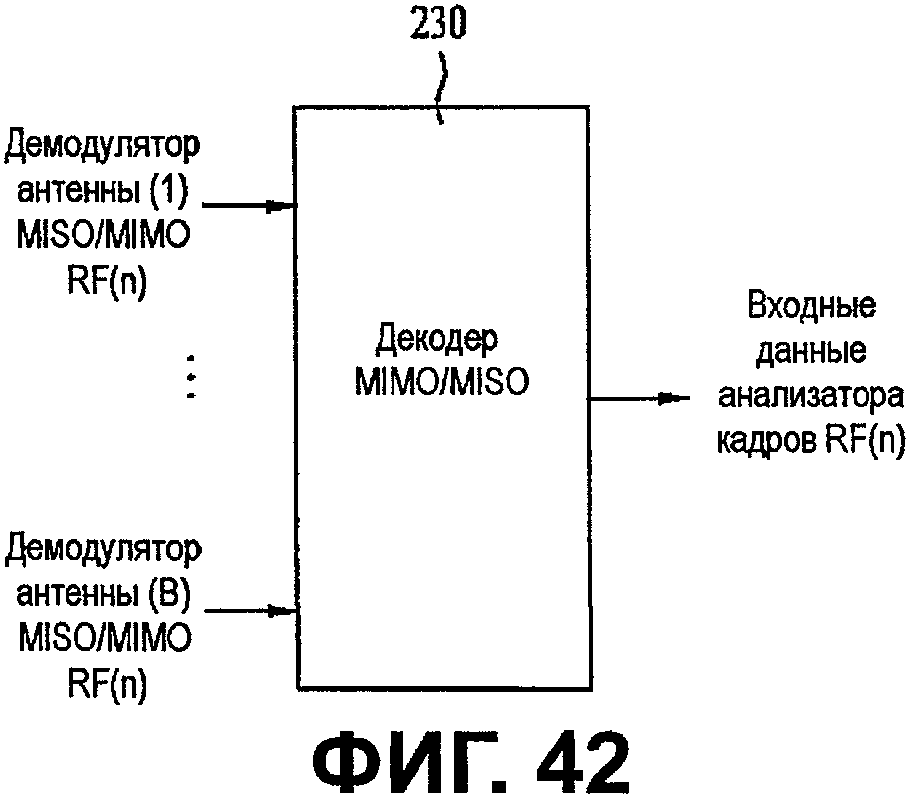

Фиг.42 - изображение, показывающее декодер сигнала многолучевого распространения;

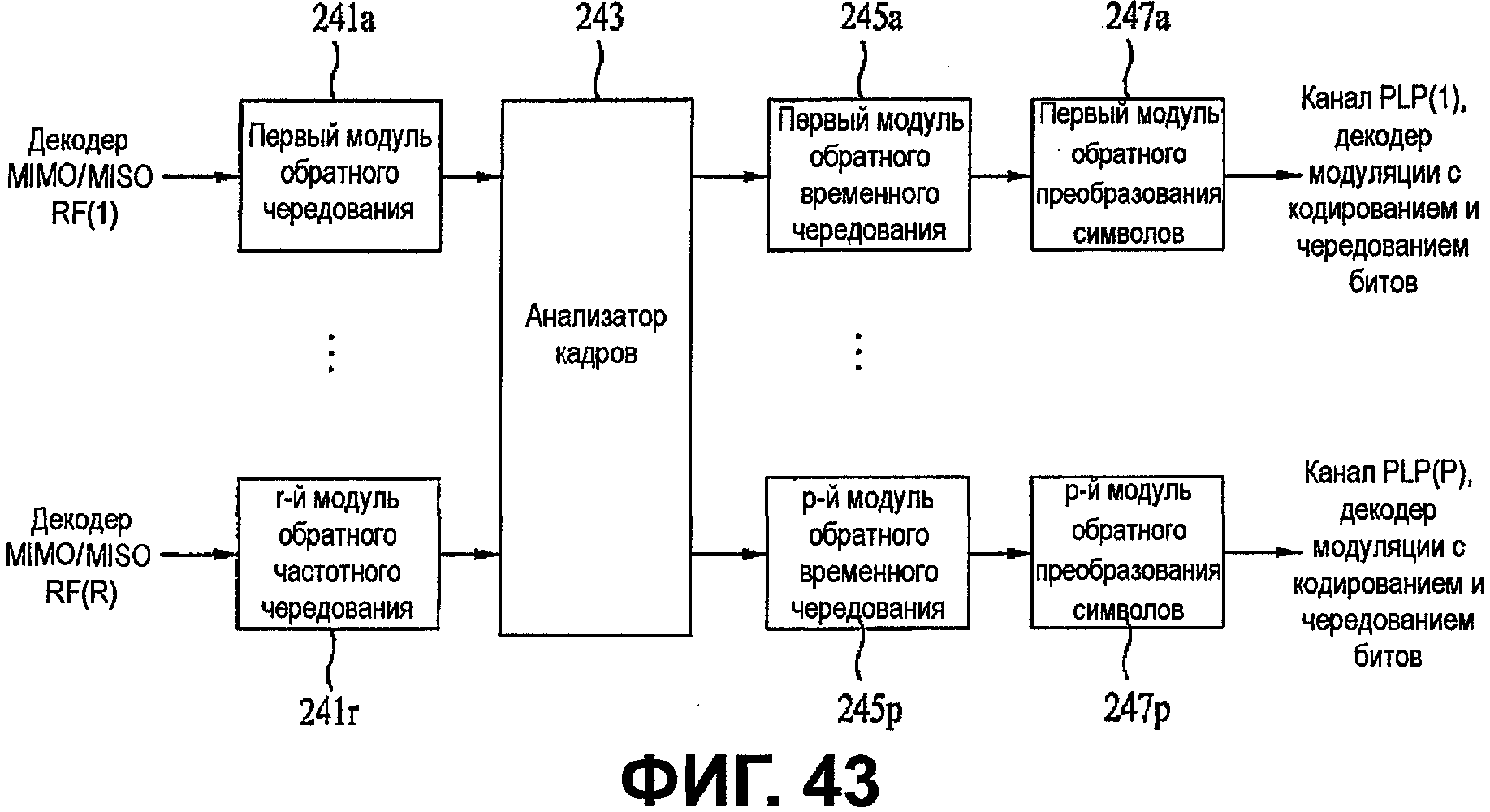

Фиг.43 - изображение, показывающее вариант воплощения анализатора кадра;

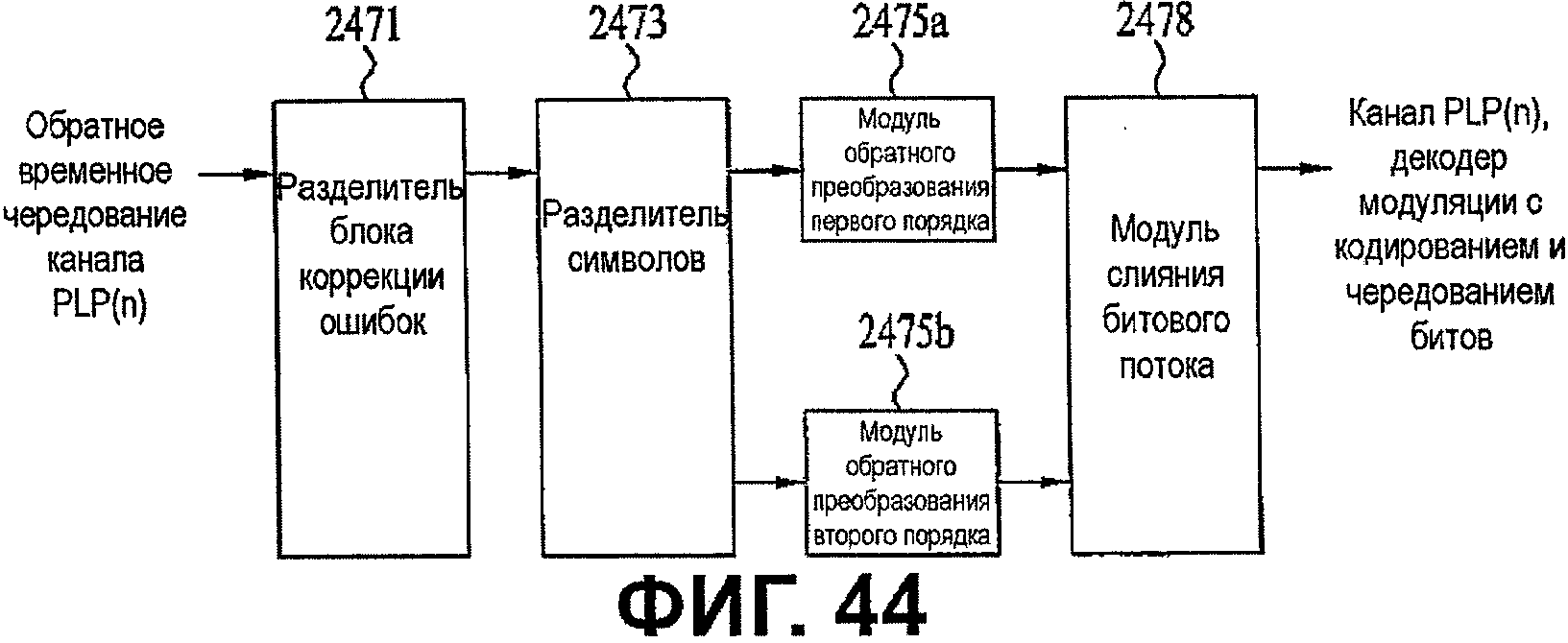

Фиг.44 - изображение, показывающее вариант воплощения каждого из модулей 247a и 247p обратного преобразования символов;

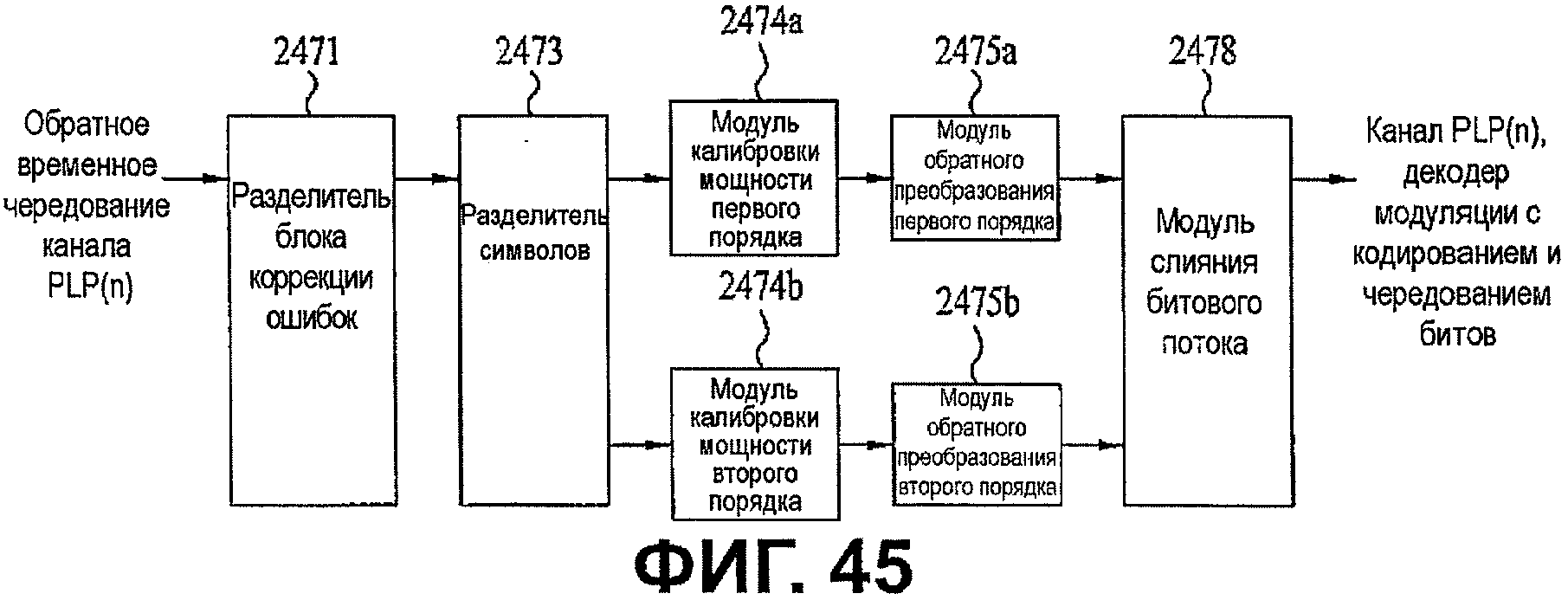

Фиг.45 - изображение, показывающее другой вариант воплощения каждого из модулей 247a и 247p обратного преобразования символов;

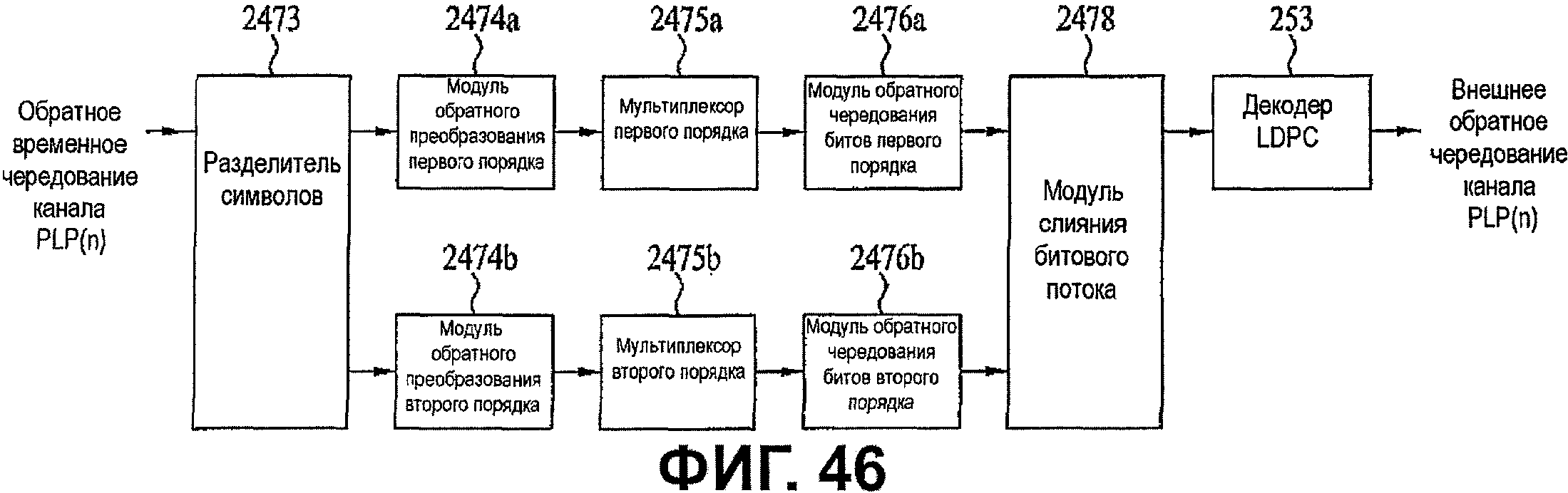

Фиг.46 - изображение, показывающее другой вариант воплощения каждого из модулей 247a и 247p обратного преобразования символов;

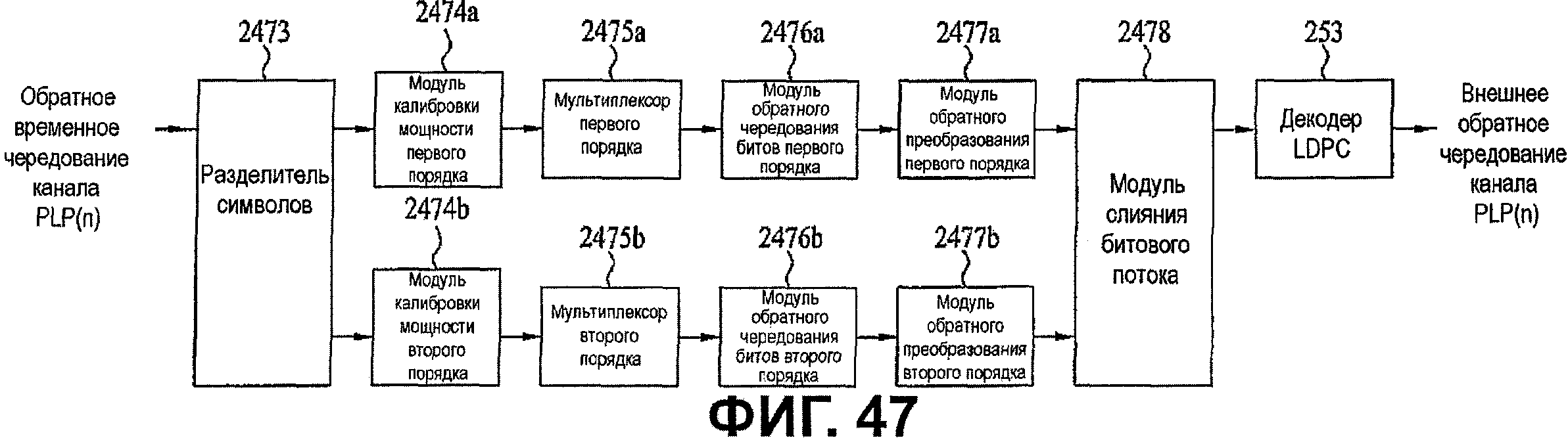

Фиг.47 - изображение, показывающее другой вариант воплощения каждого из модулей 247a и 247p обратного преобразования символов;

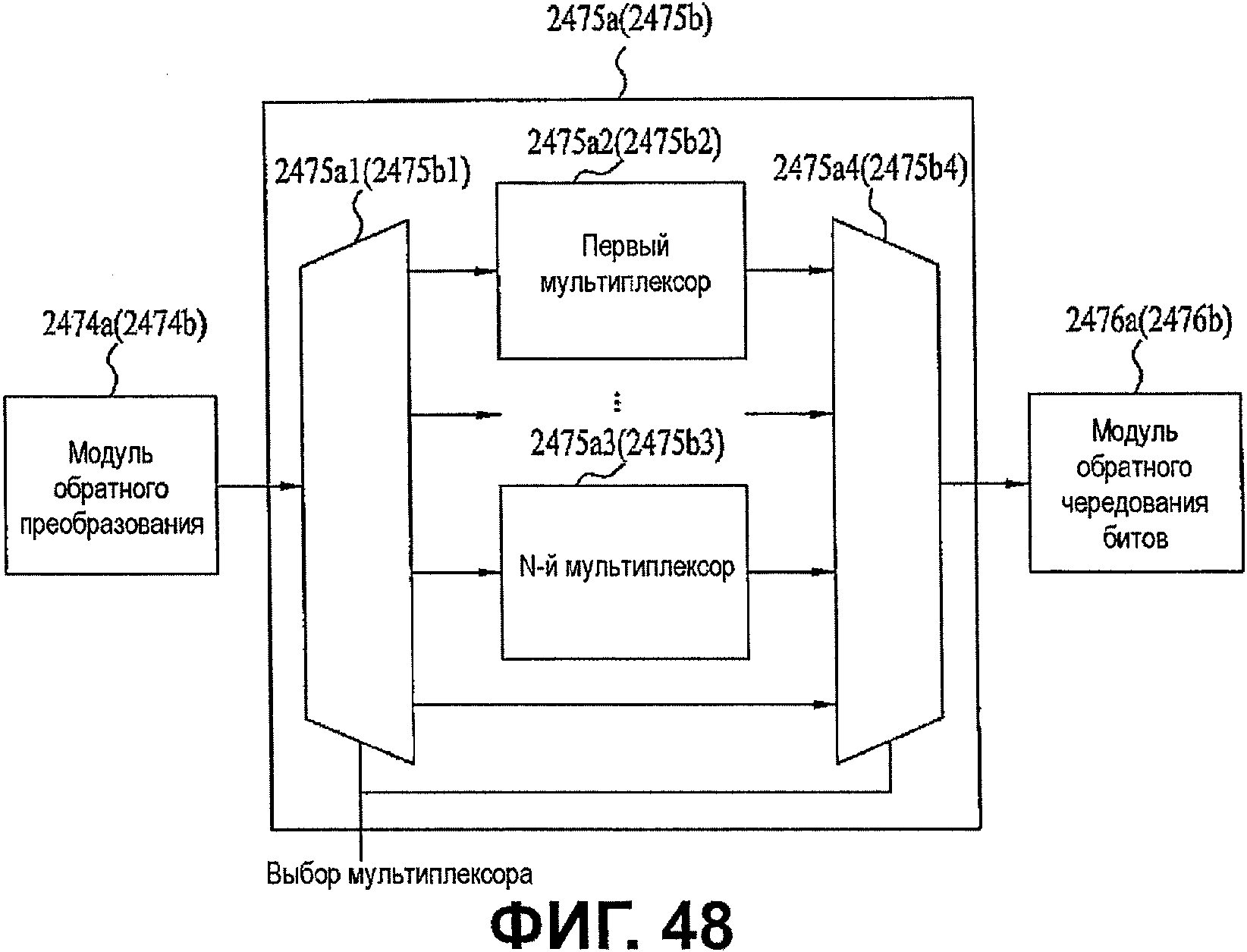

Фиг.48 - изображение, показывающее вариант воплощения мультиплексирования демультиплексированного подпотока;

Фиг.49 - изображение, показывающее пример модуля декодирования и демодуляции;

Фиг.50 - изображение, показывающее вариант воплощения выходного процессора;

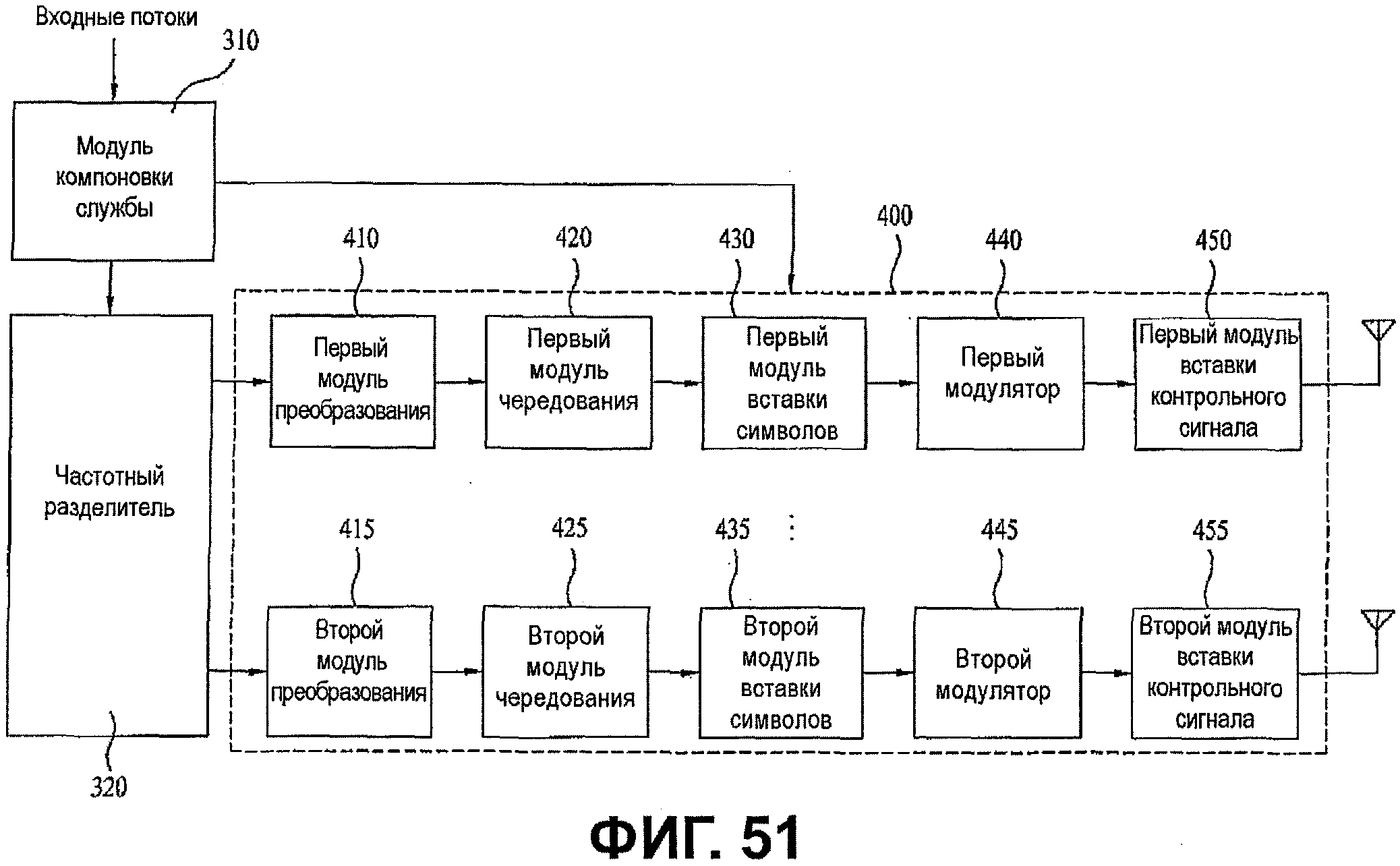

Фиг.51 - изображение, показывающее другой вариант воплощения устройства передачи сигнала для передачи сигнального кадра;

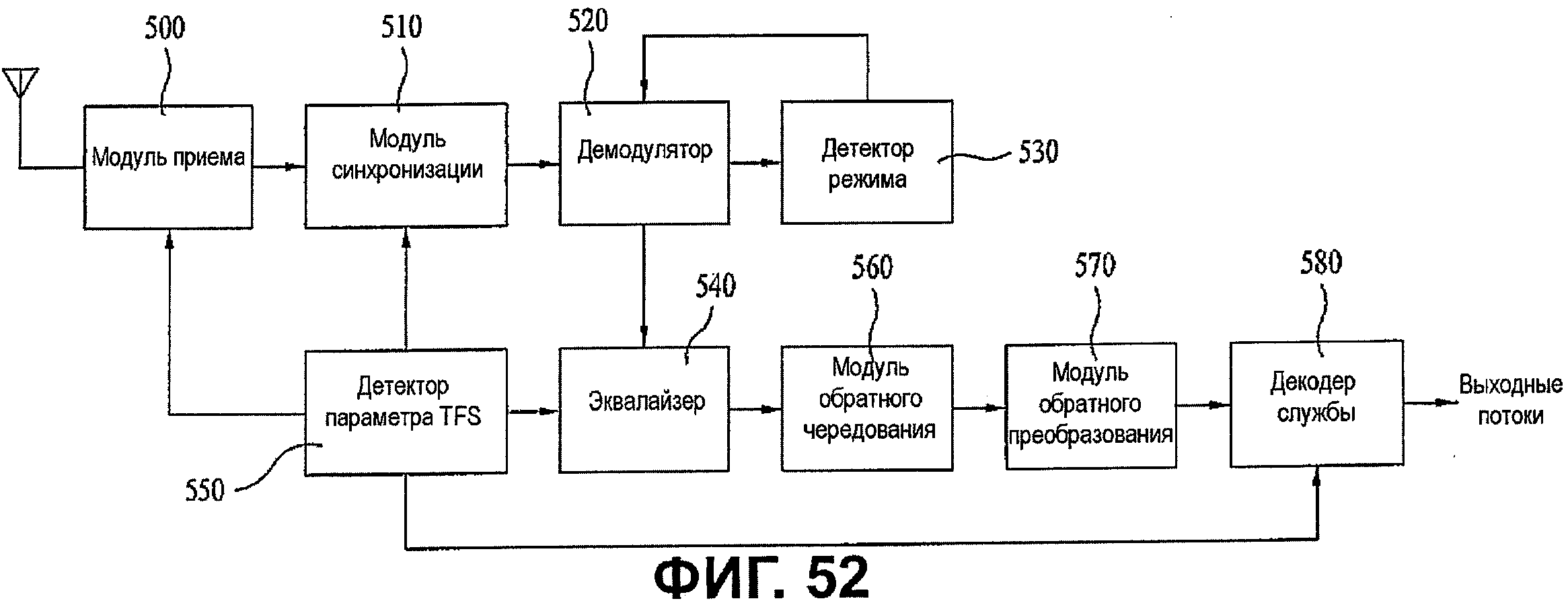

Фиг.52 - изображение, показывающее другой вариант воплощения устройства приема сигнала для приема сигнального кадра;

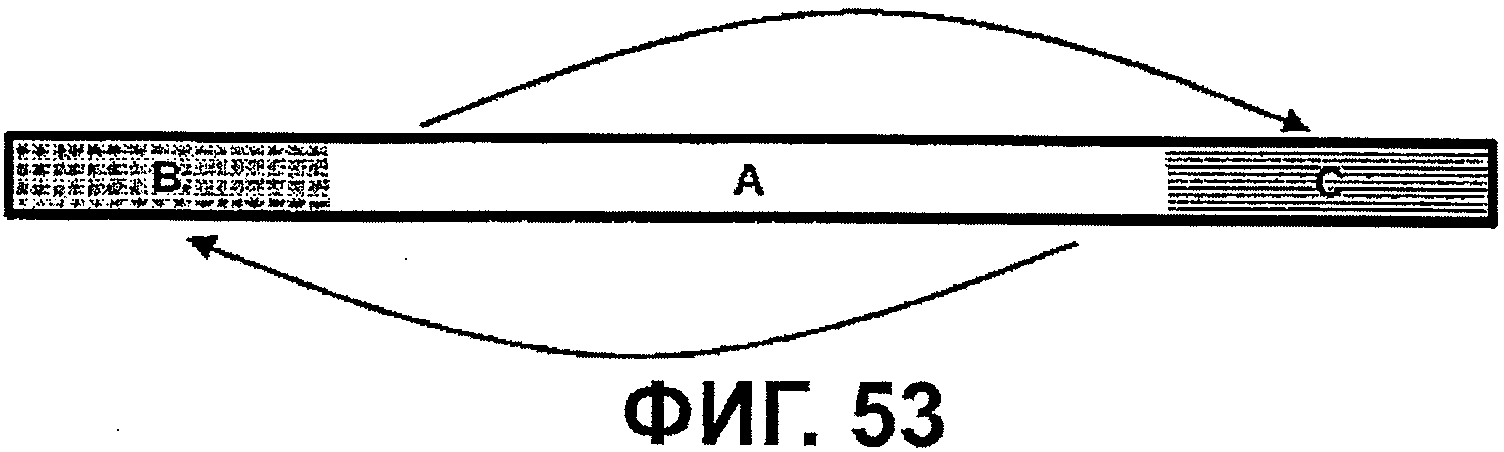

Фиг.53 - изображение, показывающее вариант воплощения структуры первого контрольного сигнала;

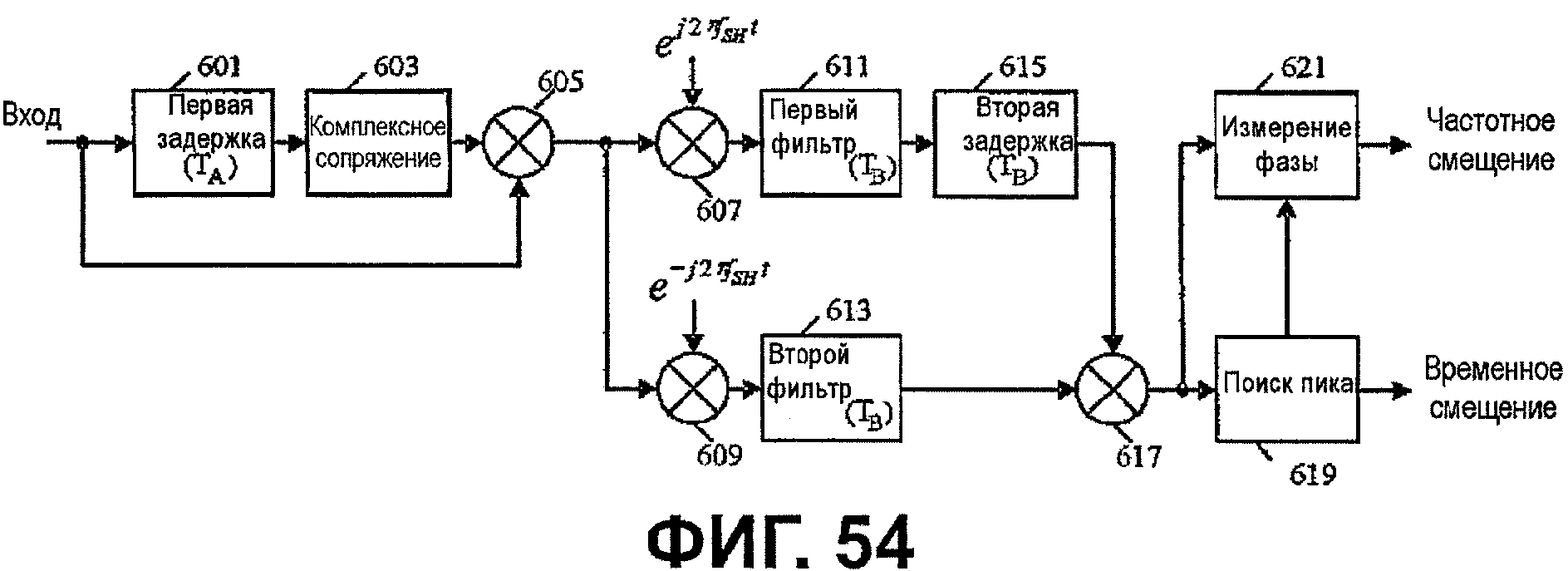

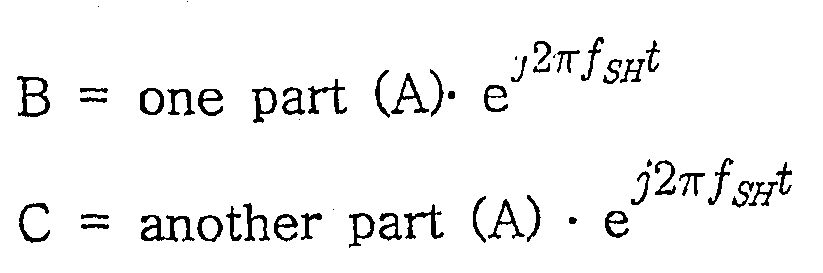

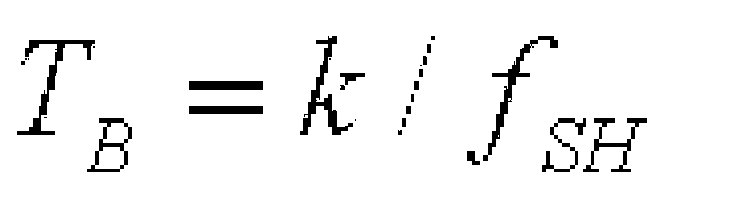

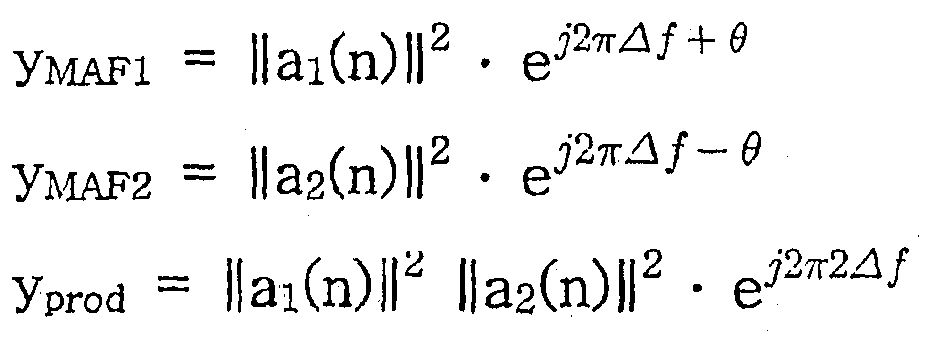

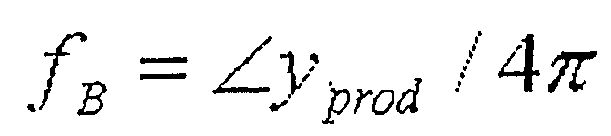

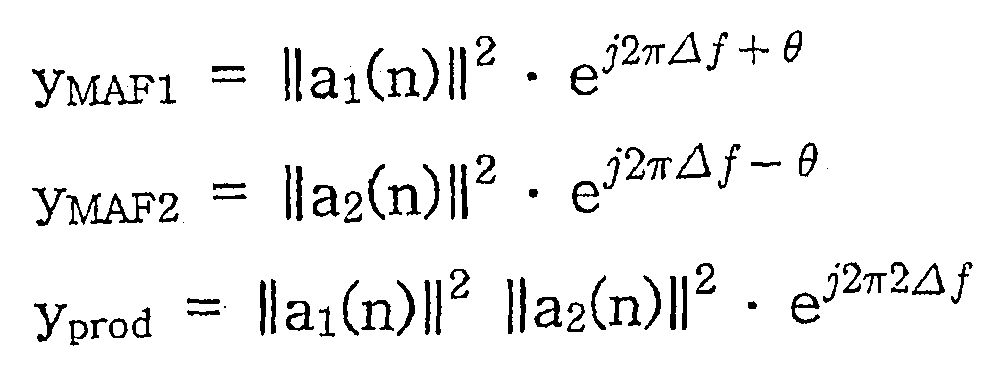

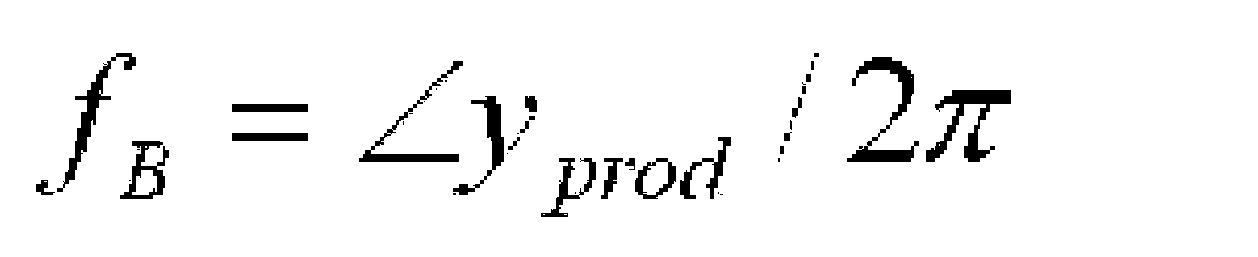

Фиг.54 - изображение, показывающее вариант воплощения обнаружения сигнала преамбулы, показанного на фиг.53, и оценки временного смещения и частотного смещения;

Фиг.55 - изображение, показывающее другой вариант воплощения структуры первого контрольного сигнала;

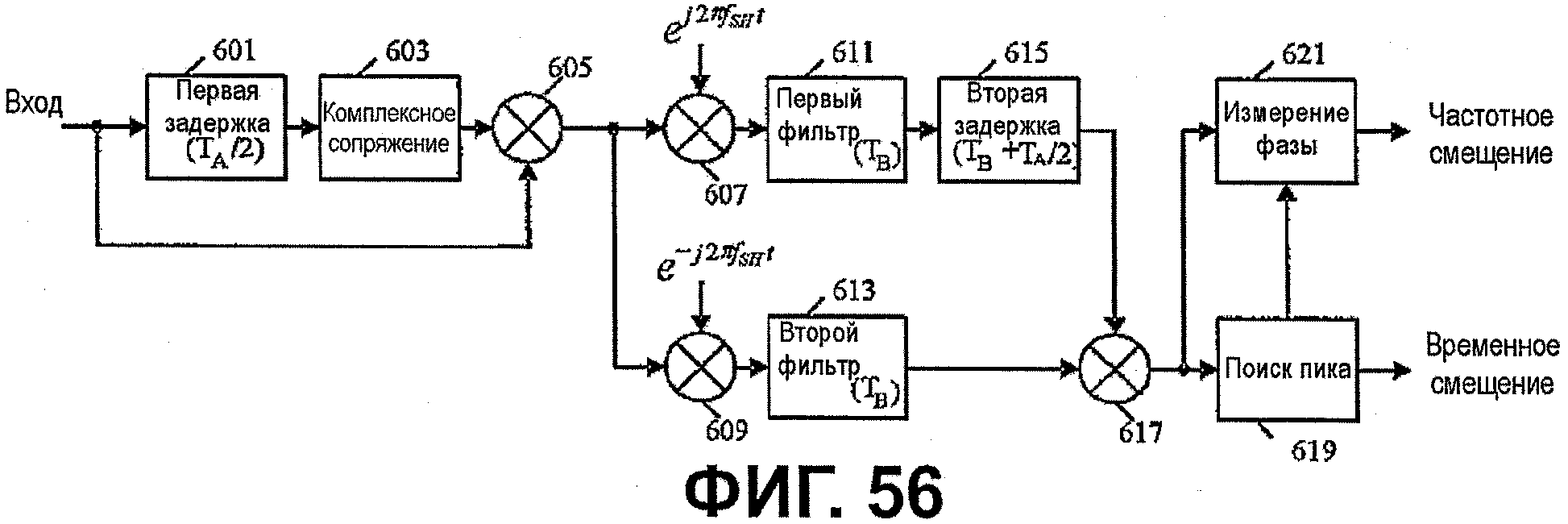

Фиг.56 - изображение, показывающее вариант воплощения обнаружения первого контрольного сигнала, показанного на фиг.55, и измерения временного смещения и частотного смещения;

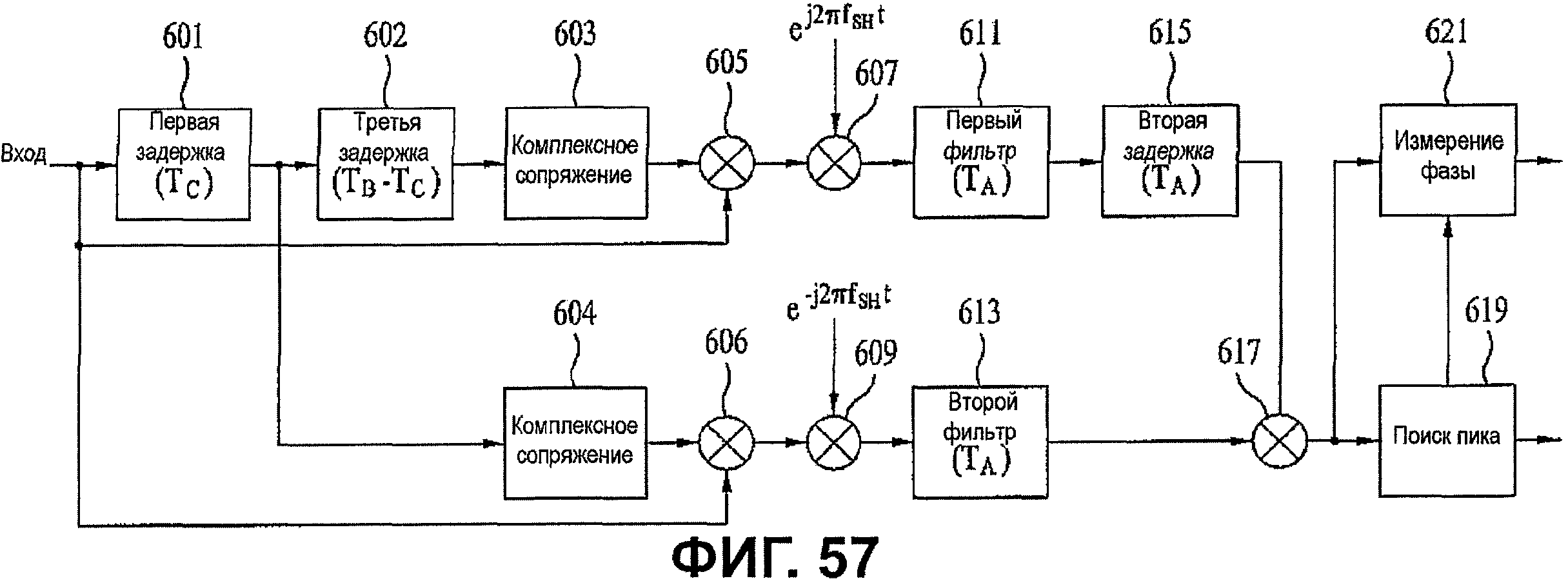

Фиг.57 - изображение, показывающее вариант воплощения обнаружения первого контрольного сигнала и измерения временного смещения и частотного смещения с использованием обнаруженного результата;

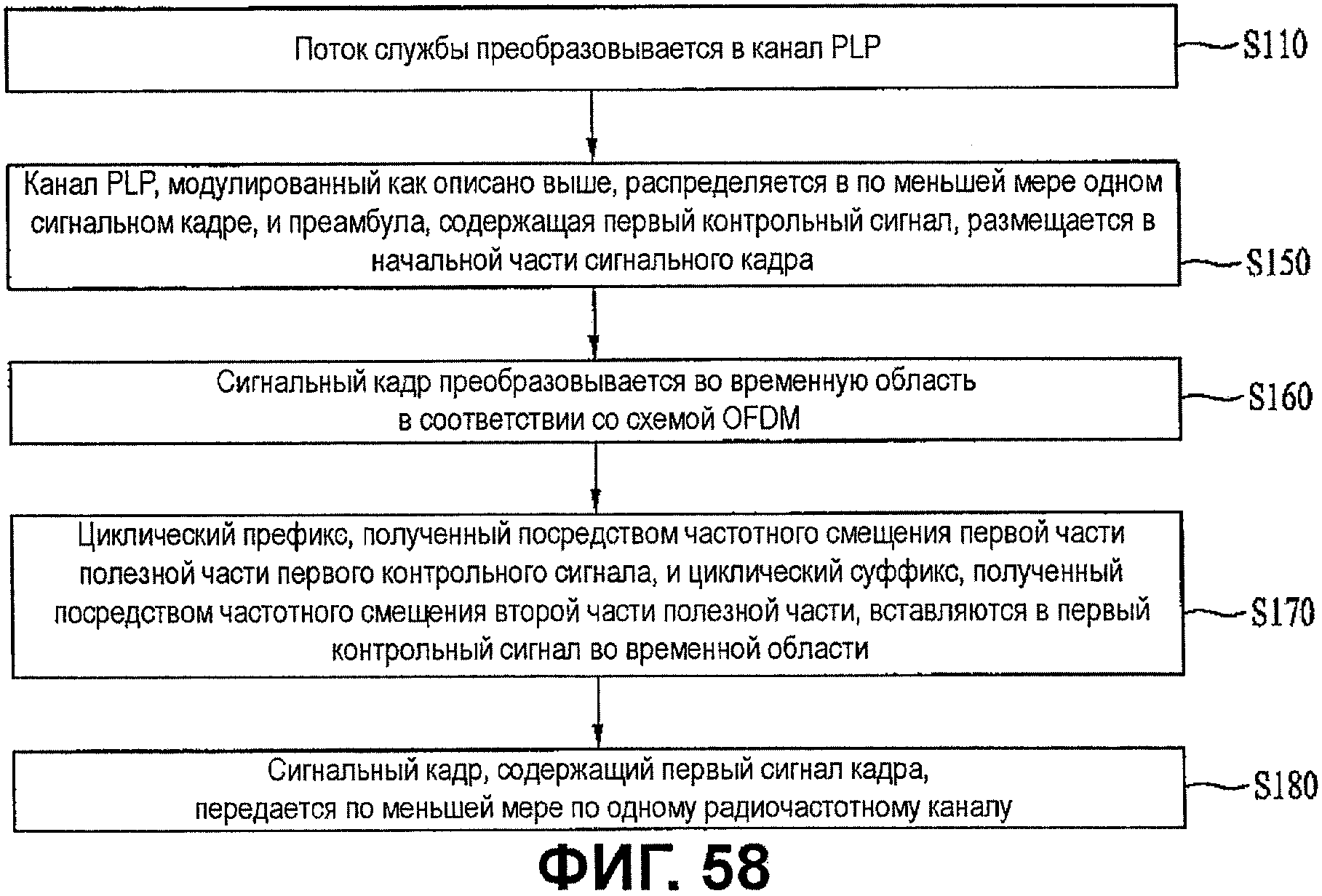

Фиг.58 - изображение, показывающее вариант воплощения способа передачи сигнала;

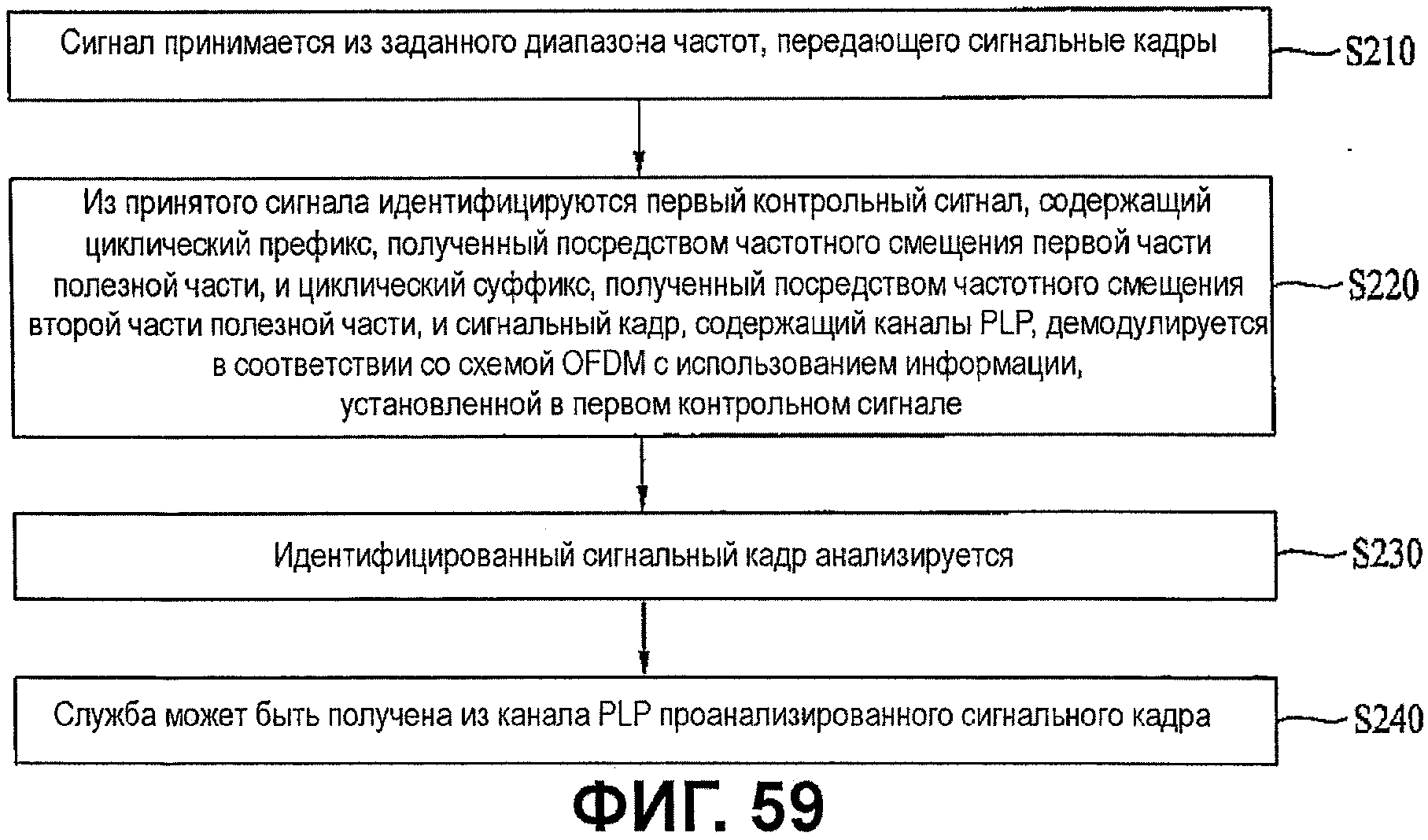

Фиг.59 - изображение, показывающее вариант воплощения способа приема сигнала; и

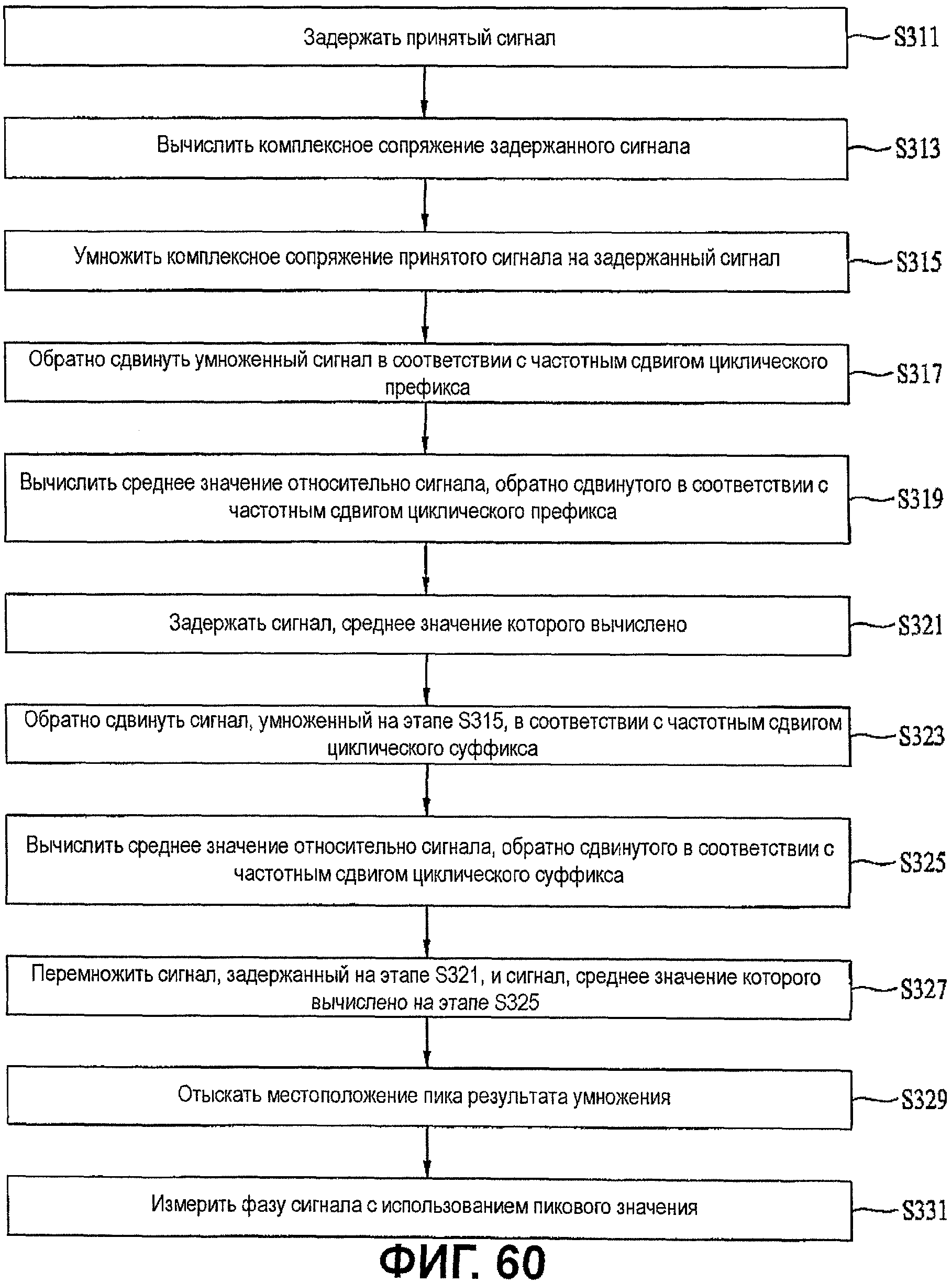

Фиг.60 - блок-схема последовательности операций, иллюстрирующая вариант воплощения идентификации первого контрольного сигнала и оценки смещения в процессе демодуляции.

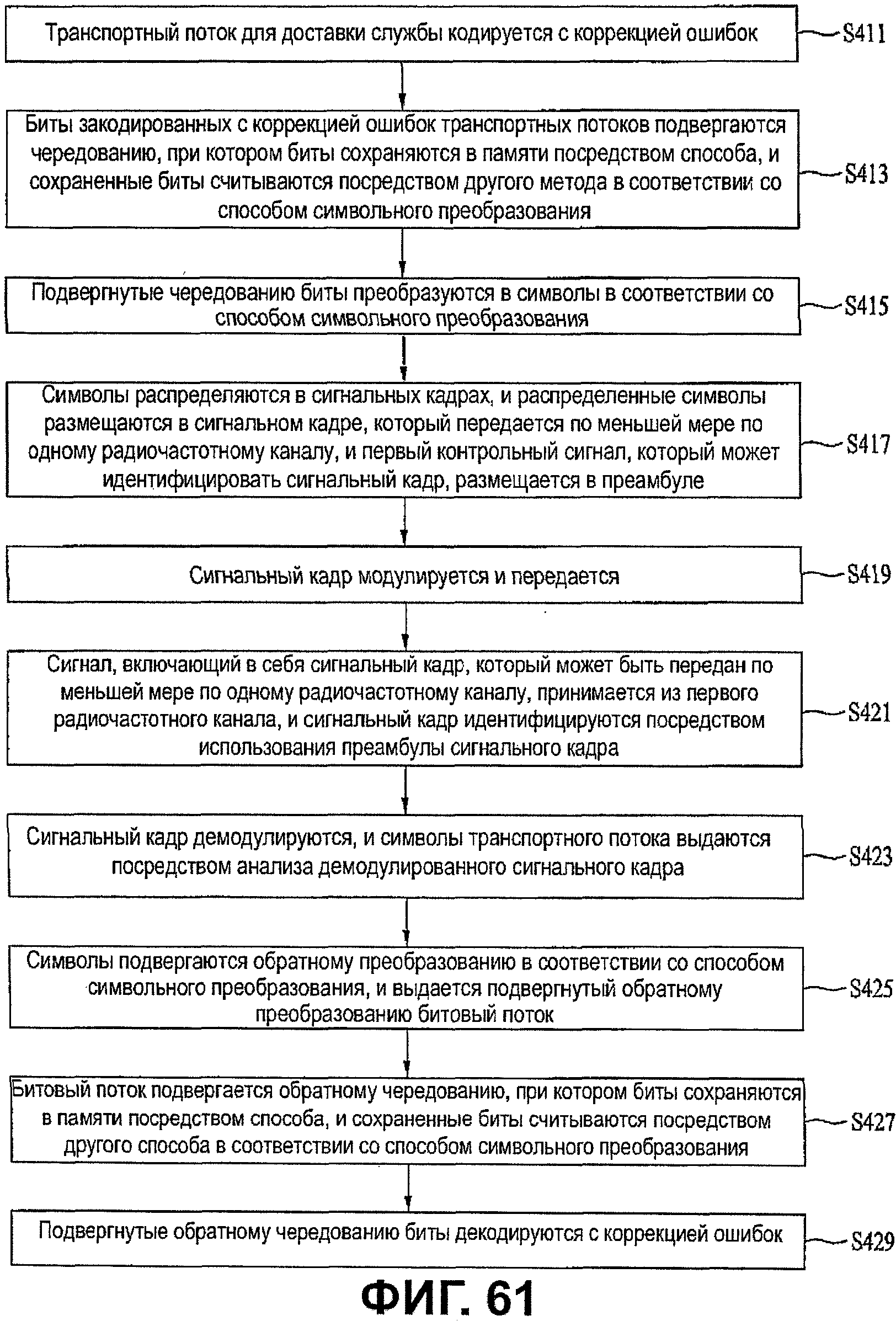

Фиг.61 иллюстрирует другой пример способа передачи и приема сигналов в соответствии с настоящим изобретением.

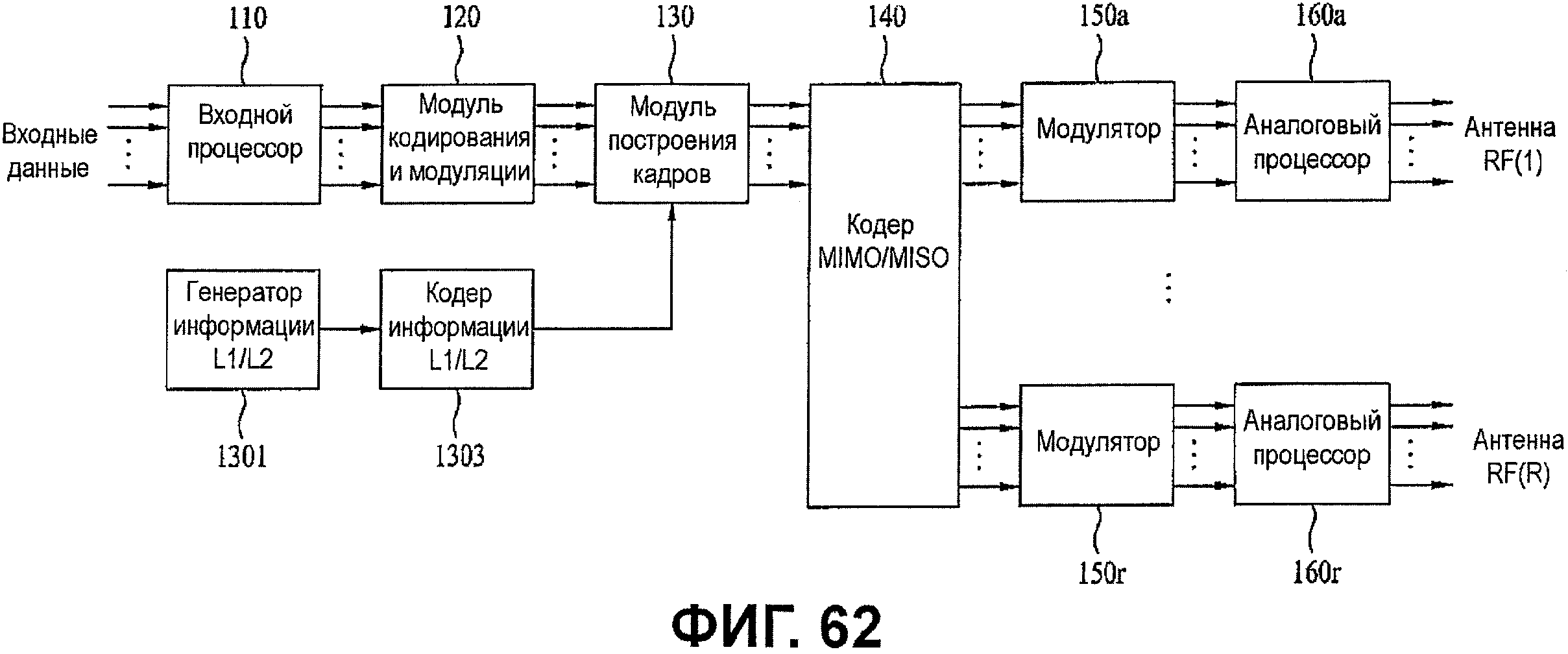

Фиг.62 - изображение, показывающее другой вариант воплощения устройства для передачи сигнала;

Фиг.63 - изображение, показывающее вариант воплощения кодера 1303 информации;

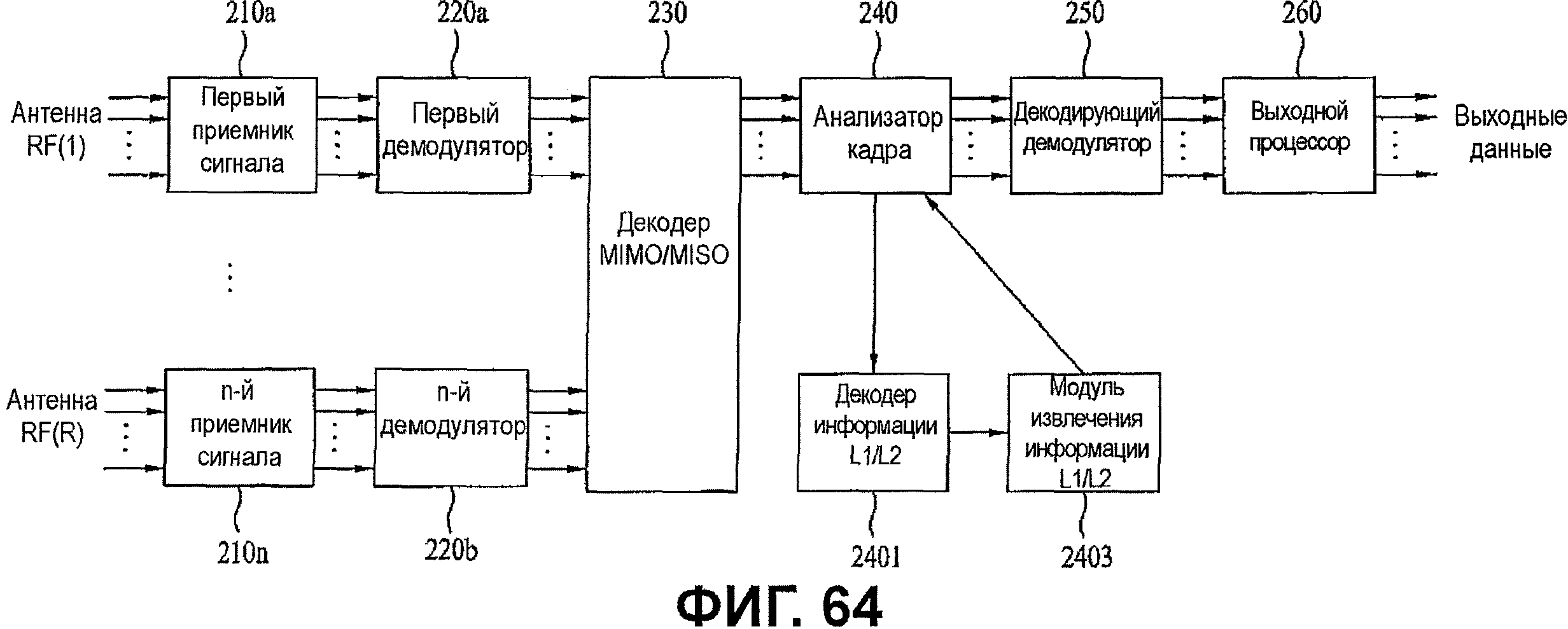

Фиг.64 - изображение, показывающее другой вариант воплощения устройства для приема сигнала;

Фиг.65 - изображение, показывающее подробный вариант воплощения декодирования информации уровня 1 и информации уровня 2; и

Фиг.66 - блок-схема последовательности операций, иллюстрирующая способ передачи и приема сигнала.

Предпочтительный вариант воплощения изобретения

Теперь будут подробно описаны предпочтительные варианты воплощения настоящего изобретения, примеры которых проиллюстрированы на сопроводительных чертежах. Везде, где возможно, одни и те же номера для ссылок будут использоваться на всех чертежах для обозначения одних и тех же или сходных частей.

В последующем описании термин "служба" обозначает либо информационное содержание широковещания, которое может быть передано/принято устройством передачи/приема сигнала, либо предоставление информационного содержания.

Перед описанием устройства для передачи и приема сигнала в соответствии с вариантом воплощения настоящего изобретения будет описан сигнальный кадр, который передается и принимается устройством для передачи и приема сигнала в соответствии с вариантом воплощения настоящего изобретения.

Фиг.1 показывает сигнальный кадр для передачи службы в соответствии с вариантом воплощения настоящего изобретения.

Сигнальный кадр, показанный на фиг.1, показывает иллюстративный сигнальный кадр для передачи службы широковещания, включающей в себя аудио/видео (A/V) потоки. В этом случае одна служба мультиплексируется во временных и частотных каналах, и мультиплексированная служба передается. Упомянутая выше схема передачи сигнала называется схемой частотно-временного разделения (TFS). По сравнению со случаем, в котором одна служба передается только по одному радиочастотному (RF) диапазону, устройство передачи сигнала в соответствии с вариантом воплощения настоящего изобретения передает службу сигнала через по меньшей мере один радиочастотный диапазон (возможно, несколько радиочастотных диапазонов), и тем самым оно может достичь эффекта статистического мультиплексирования, имея возможность передавать еще много служб. Устройство передачи/приема сигнала передает/принимает одну службу по нескольким радиочастотным каналам, и тем самым оно может достичь эффекта частотного разнесения.

Службы с первой по третью (службы 1-3) передаются по четырем радиочастотным диапазонам (RF1-RF4). Однако это количество радиочастотных диапазонов и это количество служб раскрыто только в иллюстративных целях, таким образом, при необходимости могут быть использованы другие количества. Два опорных сигнала (то есть первый контрольный сигнал (P1) и второй контрольный сигнал (P2)) располагаются в начальной части сигнального кадра. Например, в случае диапазона RF1 первый контрольный сигнал (P1) и второй контрольный сигнал (P2) располагаются в начальной части сигнального кадра. Диапазон RF1 включает в себя три слота, соответствующие службе 1, два слота, соответствующие службе 2, и один слот, соответствующий службе 3. Слоты, соответствующие другим службам, также могут быть расположены в других слотах (слоты 4-17), расположенных после одного слота, соответствующего службе 3.

Диапазон RF2 включает в себя первый контрольный сигнал (P1), второй контрольный сигнал (P2) и другие слоты 13-17. Кроме того диапазон RF2 включает в себя три слота, соответствующие службе 1, два слота, соответствующие службе 2, и один слот, соответствующий службе 3.

Службы 1-3 мультиплексируются и затем передаются по диапазонам RF3 и RF4 в соответствии со схемой частотно-временного разделения (TFS). Схема модуляции для передачи сигнала может быть основана на схеме мультиплексирования с ортогональным частотным разделением сигналов (OFDM).

В сигнальном кадре индивидуальные службы сдвигаются по радиочастотным диапазонам (в случае, когда в сигнальном кадре имеется множество радиочастотных диапазонов) и оси времени.

Если сигнальные кадры, равные упомянутому выше сигнальному кадру, последовательно упорядочиваются по времени, из нескольких сигнальных кадров может быть составлен суперкадр. Будущий кадр расширения также может быть расположен среди нескольких сигнальных кадров. Если будущий кадр расширения располагается среди нескольких сигнальных кадров, суперкадр может быть завершен в будущем кадре расширения.

Фиг.2 показывает первый контрольный сигнал (P1) содержащийся в сигнальном кадре, показанном на фиг.1, в соответствии с вариантом воплощения настоящего изобретения.

Первый контрольный сигнал P1 и второй контрольный сигнал P2 располагаются в начальной части сигнального кадра. Первый контрольный сигнал P1 модулируется посредством режима 2K FFT и может передаваться одновременно, включая в себя защитный интервал 1/4. На фиг.2 диапазон с шириной 7,61 МГц первого контрольного сигнала P1 включает в себя диапазон с шириной 6,82992 МГц. Первый контрольный сигнал использует 256 несущих из 1705 активных несущих. В среднем используется одна активная несущая из каждых шести несущих. Интервалы носителя данных могут быть нерегулярно размещены в порядке 3, 6 и 9. На фиг.2 сплошная линия указывает местоположение используемой несущей, тонкая пунктирная линия указывает местоположение неиспользуемой несущей, и штрихпунктирная линия указывает центральное местоположение неиспользуемой несущей. В первом контрольном сигнале используемая несущая может быть преобразована в символ посредством двоичной фазовой манипуляции (BPSK), и может быть модулирована псевдослучайная битовая последовательность (PRBS). Размер преобразования FFT, используемый для второго контрольного сигнала, может быть обозначен несколькими последовательностями PRBS.

Устройство приема сигнала обнаруживает структуру контрольного сигнала и распознает частотно-временное разделение (TFS) с использованием обнаруженной структуры. Устройство приема сигнала получает размер преобразования FFT второго контрольного сигнала, компенсирует грубое частотное смещение сигнала приема и приобретает синхронизацию по времени.

В первом контрольном сигнале могут быть установлены тип передачи сигнала и параметр передачи.

Второй контрольный сигнал P2 может быть передан с таким же размером преобразования FFT и интервалом защиты, как у символа данных. Во втором контрольном сигнале одна несущая используется как несущая контрольного сигнала с интервалом в три несущие. Устройство приема сигнала компенсирует точное смещение частотной синхронизации с использованием второго контрольного сигнала и выполняет точную синхронизацию по времени. Второй контрольный сигнал передает информацию первого уровня (L1) из уровней модели взаимодействия открытых систем (OSI). Например, второй контрольный сигнал может включать в себя физический параметр и информацию построения кадра. Второй контрольный сигнал передает значение параметра, посредством которого приемник может получить доступ к потоку службы канала физического уровня (PLP).

Информация уровня L1 (уровня 1), содержащаяся во втором контрольном сигнале P2, является следующей.

Информация уровня 1 (L1) включает в себя индикатор длины, указывающий длину данных, включающих в себя информацию L1, и, таким образом она может легко использовать каналы сигнализации уровней 1 и 2 (L1 и L2). Информация уровня 1 (L1) включает в себя индикатор частоты, длину защитного интервала, максимальное количество блоков упреждающей коррекции ошибок (FEC) для каждого кадра, соответствующего индивидуальным физическим каналам, и количество фактических блоков FEC, которые будут содержаться в буфере блоков FEC, соответствующем текущему/предыдущему кадру в каждом физическом канале. В этом случае индикатор частоты указывает информацию частоты, соответствующую радиочастотному каналу.

Информация уровня 1 (L1) может включать в себя множество информации, соответствующей индивидуальным слотам. Например, информация уровня 1 (L1) включает в себя количество кадров, соответствующих службе, начальный адрес слота, имеющего точность несущей OFDM, содержащейся в символе OFDM, длину слота, слоты, соответствующие несущей OFDM, количество битов дополнения в последней несущей OFDM, информацию модуляции службы, информацию скорости режима службы и информацию схемы с множественным входом и множественным выходом (MIMO).

Информация уровня 1 (L1) может включать в себя идентификатор соты, флаг для такой службы, как служба сообщений уведомления (например, экстренных сообщений), количество текущих кадров и количество дополнительных битов для будущего использования. В этом случае идентификатор соты указывает область широковещания, передаваемую передатчиком широковещания.

Второй контрольный сигнал P2 выполнен с возможностью выполнять оценку канала для декодирования символа, содержащегося в сигнале P2. Второй контрольный сигнал P2 может использоваться в качестве начального значения для оценки канала для следующего символа данных. Второй контрольный сигнал P2 также может передавать информацию уровня 2 (L2). Например, второй контрольный сигнал может описать информацию, соответствующую службе передачи в информации уровня 2 (L2). Устройство передачи сигнала декодирует второй контрольный сигнал, чтобы получить информацию службы, содержащуюся в кадре с частотно-временным разделением (TFS), и может эффективно выполнить сканирование канала. Тем временем эта информация уровня 2 (L2) может быть включена в особый канал PLP кадра TFS. В соответствии с другим случаем информация уровня L2 может быть включена в особый канал PLP, и информация описания службы также может быть передана в особом канале PLP.

Например, второй контрольный сигнал может включать в себя два символа OFDM режима 8K FFT. В общем случае второй контрольный сигнал может являться любым элементом из множества, содержащего один символ OFDM режима 32K FFT, один символ OFDM режима 16K FFT, два символа OFDM режима 8K FFT, четыре символа OFDM режима 4K FFT и восемь символов OFDM режима 2K FFT.

Другими словами, один символ OFDM, имеющий размер большого FFT, или несколько символов OFDM, каждый из которых имеет размер маленького FFT, может содержаться во втором контрольном сигнале P2, и, таким образом, может поддерживаться емкость, которая может быть передана в контрольном сигнале.

Если информация, которая должна быть передана во втором контрольном сигнале, превышает емкость символа OFDM второго контрольного сигнала, могут дополнительно использоваться символы OFDM после второго контрольного сигнала. Информация уровня L1 (уровня 1) и уровня L2 (уровня 2), содержащаяся во втором контрольном сигнале, кодируется с помощью кода с коррекцией ошибок и затем подвергается чередованию, и, таким образом, восстановление данных выполняется, хотя происходят импульсные помехи.

Как описано выше, информация уровня L2 также может быть включена в особый канал PLP, передающий информацию описания службы.

Фиг.3 показывает сигнальное окно в соответствии с настоящим изобретением. Кадр с частотно-временным разделением (TFS) иллюстрирует концепцию смещения для служебных сигналов. Информация уровня 1 (L1), содержащаяся во втором контрольном сигнале, включает в себя информацию построения кадра и информацию физического уровня, требуемую устройством приема сигнала, декодирующим символ данных. Таким образом, если информация последующих символов данных, расположенных после второго контрольного сигнала, содержится во втором контрольном сигнале и передается результирующий второй контрольный сигнал, устройство приема сигнала может быть не способно немедленно декодировать упомянутые выше последующие символы данных из-за времени декодирования второго контрольного сигнала.

Таким образом, как показано на фиг.3, информация уровня L1, содержащаяся во втором контрольном сигнале (P2), включает в себя информацию размера одного кадра с частотно-временным разделением (TFS) и включает в себя информацию, содержащуюся в сигнальном окне в местоположении, отстоящем от второго контрольного сигнала на смещение сигнального окна.

Тем временем, чтобы выполнить оценку канала символа данных, создающего службу, символ данных может включать в себя контрольный сигнал рассеяния и непрерывный контрольный сигнал.

Далее будет описана система передачи/приема сигнала, которая может передавать/принимать сигнальные кадры, показанные на фиг.1-3. Индивидуальные службы могут быть переданы и приняты по нескольким радиочастотным каналам. Тракт для передачи каждой из служб или поток, передаваемый через этот тракт, называется каналом PLP. Канал PLP может быть распределен среди разделенных по времени слотов в нескольких радиочастотных каналах или одном радиочастотном диапазоне. Этот сигнальный кадр может передавать разделенный по времени канал PLP на по меньшей мере одном радиочастотном канале. Другими словами, один канал PLP может быть передан через по меньшей мере один радиочастотный канал с разделенными по времени областями. В дальнейшем будут раскрыты системы передачи/приема сигнала, передающие/принимающие сигнальный кадр через по меньшей мере один радиочастотный диапазон.

Фиг.4 является блок-схемой, иллюстрирующей устройство для передачи сигнала в соответствии с одним вариантом воплощения настоящего изобретения. На фиг.4 показано, что устройство передачи сигнала включает в себя входной процессор 110, модуль 120 кодирования и модуляции, модуль 130 построения кадров, кодер 140 MIMO/MISO, множество модуляторов (150a, ..., 150r) кодера 140 MIMO/MISO и множество аналоговых процессоров (160a, ..., 160r).

Входной процессор 110 принимает потоки, снабженные несколькими службами, формирует P кадров основной полосы частот (P - натуральное число), которые включают в себя информацию модуляции и кодирования, соответствующую трактам передачи индивидуальных служб, и выдает P кадров основной полосы частот.

Модуль 120 кодирования и модуляции принимает кадры основной полосы частот от входного процессора 110, выполняет кодирование канала и чередование над каждым из кадров основной полосы частот и выдает результат кодирования канала и чередования.

Модуль 130 построения кадров формирует кадры, которые передают кадры основной полосы частот, содержащиеся в P каналах PLP, по R радиочастотным каналам (где R - натуральное число), разделяет сформированные кадры и выдает разделенные кадры на тракты, соответствующие R радиочастотным каналам. Несколько служб могут быть мультиплексированы в одном радиочастотном канале по времени. Сигнальные кадры, сформированные модулем 130 построения кадров, могут включать в себя структуру с частотно-временным разделением (TFS), в которой служба мультиплексируется во временной и частотной областях.

Кодер 140 MIMO/MISO кодирует сигналы, которые должны быть переданы по R радиочастотным каналам, и выдает кодированные сигналы на тракты, соответствующие A антеннам (где A - натуральное число). Кодер 140 MIMO/MISO выдает кодированный сигнал, в котором сигнал, который должен быть передан по одному радиочастотному каналу, закодирован для A антенн таким образом, что сигнал передается/принимается в структуре MIMO (множественный вход и множественный выход) или MISO (множественный вход и один выход).

Модуляторы (150a, ..., 150r) модулируют сигналы частотной области, введенные через тракт, соответствующий каждому радиочастотному каналу, в сигналы временной области. Модуляторы (150a, ..., 150r) модулируют входные сигналы в соответствии со схемой мультиплексирования с ортогональным частотным разделением сигналов (OFDM) и выдают модулированные сигналы.

Аналоговые процессоры (160a, ..., 160r) преобразовывают входные сигналы в радиочастотные сигналы таким образом, что радиочастотные сигналы могут быть выданы на радиочастотные каналы.

Устройство передачи сигнала в соответствии с этим вариантом воплощения может включать в себя предопределенное количество модуляторов (150a, ..., 150r), соответствующее количеству радиочастотных каналов, и предопределенное количество аналоговых процессоров (160a, ..., 160r), соответствующее количеству радиочастотных каналов. Однако в случае использования схемы MIMO количество аналоговых процессоров должно быть равным произведению R (то есть, количества радиочастотных каналов) и A (то есть, количества антенн).

Фиг.5 является блок-схемой, иллюстрирующей входной процессор 110 в соответствии с вариантом воплощения настоящего изобретения. На фиг.5 показано, что входной процессор 110 включает в себя первый потоковый мультиплексор 111a, первый разделитель 113a службы и множество первых модулей (115a, ..., 115m) построения кадров основной полосы частот (BB). Входной процессор 110 включает в себя второй потоковый мультиплексор 111b, второй разделитель 113b службы и множество вторых модулей (115n, ..., 115p) построения кадров основной полосы частот (BB).

Например, первый потоковый мультиплексор 111a принимает несколько транспортных потоков (TS) MPEG-2, мультиплексирует принятые транспортные потоки MPEG-2 и выдает мультиплексированные транспортные потоки MPEG-2. Первый разделитель 113a службы принимает мультиплексированные потоки, разделяет входные потоки индивидуальных служб и выдает разделенные потоки. Как описано выше, при условии, что служба, передаваемая через тракт физического канала называется каналом PLP, первый разделитель 113a службы разделяет службу, которая должна быть передана по каждому каналу PLP, и выдает разделенную службу.

Первые модули (115a, ..., 115m) построения кадров BB формируют данные, содержащиеся в службе, которая должна быть передана по каждому каналу PLP, в виде отдельного кадра и выдают форматированные в виде отдельного кадра данные. Первые модули (115a, ..., 115m) построения кадров BB формируют кадр, включающий в себя заголовок и полезную нагрузку, снабженную данными службы. Заголовок каждого кадра может включать в себя информацию режима, основанную на модуляции и кодировании данных службы, и значение счетчика, основанное на тактовой частоте модулятора для синхронизации входных потоков.

Второй потоковый мультиплексор 111b принимает несколько потоков, мультиплексирует входные потоки и выдает мультиплексированные потоки. Например, второй потоковый мультиплексор 111b может мультиплексировать потоки протокола Интернета (IP) вместо транспортных потоков MPEG-2. Эти потоки могут быть инкапсулированы посредством схемы инкапсуляции потоков общего типа (GSE). Потоки, мультиплексированные вторым потоковым мультиплексором 111b, могут быть любыми потоками. Поэтому упомянутые выше потоки, отличающиеся от транспортных потоков MPEG-2, называются потоками общего типа (GS).

Второй разделитель 113b службы принимает мультиплексированные потоки общего типа, разделяет принятые потоки общего типа в соответствии с индивидуальными службами (то есть, типами канала PLP) и выдает разделенные потоки GS.

Вторые модули (115n, ..., 115p) построения кадров BB формируют данные службы, которые должны быть переданы по индивидуальным каналам PLP, в виде отдельного кадра, используемого как единица обработки сигнала, и выдает полученные в результате данные службы. При необходимости формат кадра, сформированного вторыми модулями (115n, ..., 115p) построения кадров BB, может быть таким же, как у первых модулей (115a, ..., 115m) построения кадров BB. Если требуется, также может быть предложен другой вариант воплощения. В другом варианте воплощения формат кадра, сформированного вторыми модулями (115n, ...., 115p) построения кадров BB, может отличаться от формата первых модулей (115a, ..., 115m) построения кадров BB. Заголовок транспортного потока MPEG-2 дополнительно включает в себя пакетную синхрогруппу, которая не содержится в потоке GS, что приводит к появлению разных заголовков.

Фиг.6 является блок-схемой, иллюстрирующей модуль кодирования и модуляции в соответствии с вариантом воплощения настоящего изобретения. Модуль кодирования и модуляции включает в себя первый кодер 121, первый модуль 123 чередования, второй кодер 125 и второй модуль 127 чередования.

Первый кодер 121 функционирует как внешний кодер входного кадра основной полосы частот и может выполнять кодирование с коррекцией ошибок. Первый кодер 121 выполняет кодирование с коррекцией ошибок входного кадра основной полосы частот с использованием схемы кодирования Боуза-Чоудхури-Хоквингхема (BCH). Первый модуль 123 чередования выполняет чередование закодированных данных таким образом, что он препятствует формированию пакета ошибок в сигнале передачи. Первый модуль 123 чередования может не содержаться в упомянутом выше варианте воплощения.

Второй кодер 125 функционирует как внутренний кодер или выходных данных первого кодера 121 или выходных данных первого модуля 123 чередования и может выполнять кодирование с коррекцией ошибок. В качестве схемы кодирования с коррекцией ошибок может быть использована схема кодирования с малой плотностью проверок на четность (LDPC). Второй модуль 127 чередования смешивает закодированные с коррекцией ошибок данные, сформированные вторым кодером 125, и выдает смешанные данные. Первый модуль 123 чередования и второй модуль 127 чередования могут выполнять побитное чередование.

Модуль 120 кодирования и модуляции имеет отношение к одному потоку канала PLP. Поток канала PLP кодируется с коррекцией ошибок и модулируется модулем 120 кодирования и модуляции и затем передается модулю 130 построения кадров.

Фиг.7 является блок-схемой, иллюстрирующей модуль построения кадров в соответствии с вариантом воплощения настоящего изобретения. На фиг.7 показано, что модуль 130 построения кадров принимает потоки нескольких трактов от модуля 120 кодирования и модуляции и размещает принятые потоки в одном сигнальном кадре. Например, модуль построения кадров может включать в себя первый модуль 131a преобразования и первый модуль 132a временного чередования в первом тракте, и может включать в себя второй модуль 131b преобразования и второй модуль 132b временного чередования во втором тракте. Количество входных трактов равно количеству каналов PLP для передачи службы или количеству потоков, передаваемых через каждый канал PLP.

Первый модуль 131a преобразования выполняет преобразование данных, содержащихся во входном потоке в соответствии с первой схемой символьного преобразования. Например, первый модуль 131a преобразования может выполнять преобразование входных данных с использованием схемы QAM (например, 16QAM, 64QAM и 256 QAM).

Если первый модуль 131a преобразования выполняет символьное преобразование, входные данные могут быть преобразованы в несколько видов символов в соответствии с несколькими схемами символьного преобразования. Например, первый модуль 131a преобразования классифицирует входные данные на блок кадра основной полосы частот и субблок кадра основной полосы частот. Индивидуальные классифицированные данные могут быть подвергнуты гибридному символьному преобразованию посредством по меньшей мере двух схем QAM (например, 16QAM и 64QAM). Поэтому данные, содержащиеся в одной службе, могут быть преобразованы в символы на основе разных схем символьного преобразования в индивидуальных интервалах.

Первый модуль 132a временного чередования принимает последовательность символов, преобразованных первым модулем 131a преобразования, и может выполнить чередование во временной области. Первый модуль 131a преобразования преобразует данные, которые содержатся в закодированном с коррекцией ошибок кадре, принятом от модуля 120 кодирования и модуляции 120, в символы. Первый модуль 132a временного чередования принимает последовательность символов, преобразованных первым модулем 131a преобразования, и чередует принятую последовательность символов по кадрам, закодированным с коррекцией ошибок.

Таким образом, модуль 131p преобразования с порядковым номером p или модуль 132p временного чередования с порядковым номером p принимает данные службы, которые будут переданы по каналу PLP с порядковым номером p, преобразует данные в символы в соответствии со схемой символьного преобразования с порядковым номером p. Преобразованные символы могут быть подвергнуты чередованию во временной области. Следует отметить, что эта схема символьного преобразования и эта схема чередования являются такими же, как у первого модуля 132a временного чередования и первого модуля 131a преобразования.

Схема символьного преобразования первого модуля 131a преобразования может быть такой же, как у модуля 131p преобразования с порядковым номером p, или другой. Первый модуль 131a преобразования и модуль 131p преобразования с порядковым номером p могут отобразить входные данные на индивидуальные символы с использованием одинаковых или разных гибридных схем символьного преобразования.

Данные модулей временного чередования, расположенные в индивидуальных трактах (то есть, данные службы, подвергнутые чередованию первым модулем 132a временного чередования, и данные службы, которые должны быть переданы по R радиочастотным каналам посредством модуля 132p временного чередования с порядковым номером p), подвергаются чередованию таким образом, что физический канал позволяет упомянутым выше данным чередоваться по нескольким радиочастотным каналам.

Вместе с потоками, принятыми по такому же количеству трактов, как количество каналов PLP, модуль 133 построения кадров TFS формирует сигнальный кадр TFS, такой как упомянутый выше сигнальный кадр, таким образом, что служба сдвигается по времени в соответствии с радиочастотными каналами. Модуль 133 построения кадров TFS разделяет данные службы, принятые по любому из трактов, и выдает данные службы, разделенные на данные R радиочастотных диапазонов в соответствии со схемой планирования сигнала.

Модуль 133 построения кадров TFS принимает первый контрольный сигнал и второй контрольный сигнал от модуля 135 служебных сигналов (обозначенного сигналом Ref/PL), размещает первый и второй контрольные сигналы в сигнальном кадре и вставляет сигнальный сигнал (L1 и L2) упомянутого выше физического уровня во второй контрольный сигнал. В этом случае первый и второй контрольные сигналы используются как начальные сигналы сигнального кадра, содержащегося в каждом радиочастотном канале из сигнального кадра TFS, принятого от модуля 135 служебных сигналов (сигнала Ref/PL). Как показано на фиг.2, первый контрольный сигнал может включать в себя тип передачи и основные параметры передачи, и второй контрольный сигнал может включать в себя физический параметр и информацию построения кадра. Кроме того, второй контрольный сигнал включает в себя сигнальный сигнал уровня L1 (уровня 1) и сигнальный сигнал уровня L2 (уровня 2).

R модулей (137a, ..., 137r) частотного чередования подвергают чередованию данные службы, которые должны быть переданы по соответствующим радиочастотным каналам сигнального кадра TFS, в частотной области. Модули (137a, ..., 137r) частотного чередования могут чередовать данные службы на уровне ячеек данных, содержащихся в символе OFDM.

Таким образом, данные службы, которые должны быть переданы по каждому радиочастотному каналу в сигнальном кадре TFS, обрабатываются с избирательным по частоте исчезновением таким образом, что они не могут быть потеряны в отдельной частотной области.

Фиг.8 является изображением, показывающим первый пример соотношения символов, когда модули 131a и 131b преобразования выполняют гибридное символьное преобразование. Эта фигура показывает количество битов, передаваемых одной поднесущей (ячейкой), если кодирование с коррекцией ошибок выполняется модулем кодирования и модуляции в нормальном режиме (длина закодированного с коррекцией ошибок кода составляет 64800 битов) кодирования с коррекцией ошибок LDPC.

Например, если модули 131a и 131b преобразования выполняют символьное преобразование с использованием схемы 256QAM, 64800 битов преобразуются в 8100 символов. Если модули 131a и 131b преобразования выполняют гибридное символьное преобразование (Hyb 128QAM) с использованием схем 256QAM и 64QAM с отношением 3:2, количество символов, преобразованных посредством схемы 256QAM, равно 4860, и количество символов, преобразованных посредством схемы 64QAM, равно 4320. Количество переданных битов на каждую поднесущую (ячейку) составляет 7,0588.

Если используется способ символьного преобразования 64QAM, входные данные могут быть преобразованы в 10800 символов, и могут быть переданы шесть битов на каждую ячейку. Если данные преобразуются в символы гибридным способом символьного преобразования 64QAM и 16QAM (64QAM:16QAM=3:2, Hyb32-QAM), одной поднесущей (ячейкой) могут быть переданы пять битов.

Если данные преобразуются в символы посредством способа 16QAM, данные преобразуются в 16200 символов, каждый из которых используется для передачи четырех битов.

Аналогичным образом, если данные преобразуются в символы посредством гибридного способа символьного преобразования 16QAM и QPSK (16QAM:QPSK=2:3, Hyb8-QAM), одной поднесущей (ячейкой) могут быть переданы три бита.

Если данные преобразуются в символы посредством способа QPSK, данные могут быть преобразованы в 32400 символов, каждый из которых используется для передачи двух битов.

Фиг.9 показывает способы символьного преобразования данных, закодированных посредством метода кодирования с коррекцией ошибок LDPC короткого режима (длина закодированного с коррекцией ошибок кода составляет 16200 битов), которые совпадают со способами символьного преобразования на фиг.8, и количество битов на каждую поднесущую в соответствии со способами символьного преобразования.

Количества битов, передаваемых поднесущей, равны количествам битов нормального режима (64800 битов) в соответствии с такими способами символьного преобразования, как 256QAM, Hyb 128QAM, 64QAM, Hyb 32QAM, 16QAM, Hyb8-QAM и QPSK, но общие количества переданных символов отличаются от нормального режима. Например, 16200 битов передаются посредством 2025 символов в схеме 256QAM, 16200 битов передаются посредством 1215 символов в соответствии со схемой 256QAM и 1080 символов в соответствии со схемой 64QAM (всего 2295 символов) в схеме Hyb 128QAM.

В соответствии с этим скорость передачи данных на каждую поднесущую (ячейку) для каждого канала PLP может быть скорректирована в соответствии с гибридным способом символьного преобразования или одиночным способом символьного преобразования.

Фиг.10 является изображением, показывающим количество символов и количество битов на каждое слово ячейки в соответствии со способом символьного преобразования в нормальном режиме кодирования LDPC. Если сигнальный кадр TFS включает в себя по меньшей мере один радиочастотный канал, символы, формирующие отдельный канал PLP, могут быть однородно распределены по радиочастотным каналам. Местоположения символов канала PLP, распределенных по радиочастотным каналам, могут адресоваться более эффективно. В соответствии с этим, когда устройство приема сигнала выбирает радиочастотные каналы, биты, используемые для адресации отдельного канала PLP, могут быть уменьшены.

На этом чертеже способ символьного преобразования, представленный посредством схемы 256QAM, указывает способ преобразования битов, формирующих один закодированный c коррекцией ошибок блок, в символы с отношением 256QAM:64QAM=8:1. В соответствии с этим способом символьного преобразования количество битов в одном закодированном с коррекцией ошибок блоке посредством способа 256QAM равно 57600, количество битов в одном закодированном с коррекцией ошибок блоке посредством способа 256QAM равно 1200, количество всех символов в блоке равно 8400, и количество битов на каждое слово ячейки равно 7,714285714.

Способ символьного преобразования, представленный посредством схемы Hyb 128QAM, указывает способ преобразования битов, формирующих один закодированный с коррекцией ошибок блок, в символы с отношением 256QAM:64QAM=8:7. В соответствии со способом символьного преобразования Hyb 128QAM количество всех символов в одном закодированном с коррекцией ошибок блоке равно 9600, и количество битов на каждое слово ячейки равно 6,75.

В соответствии со способом символьного преобразования, представленным схемой 64QAM, количество всех символов в одном закодированном с коррекцией ошибок блоке равно 10800, и количество битов на каждое слово ячейки равно 6.

Способ символьного преобразования, представленный схемой Hyb 32QAM, указывает способ преобразования битов, формирующих один закодированный с коррекцией ошибок блок в символы с отношением 64QAM:32QAM=5:4. В соответствии со способом символьного преобразования Hyb 32QAM количество всех символов в закодированном с коррекцией ошибок блоке равно 13200, и количество битов на каждое слово ячейки равно 4,9090909.

Способ символьного преобразования, представленный схемой 16QAM, указывает способ преобразования битов, формирующих один закодированный с коррекцией ошибок блок в символы с отношением 16QAM:QPSK=1:8. В соответствии со способом символьного преобразования 16QAM количество всех символов в одном закодированном с коррекцией ошибок блоке равно 15600, и количество битов на каждое слово ячейки равно 4,153846154.

Способ символьного преобразования, представленный схемой Hyb 8QAM, указывает способ преобразования битов, формирующих один закодированный с коррекцией ошибок блок в символы с отношением 16QAM:QPSK=2:1. В соответствии со способом символьного преобразования Hyb 8QAM количество всех символов в одном закодированном с коррекцией ошибок блоке равно 21600, и количество битов на каждое слово ячейки равно 3.

В соответствии со способом символьного преобразования, представленным схемой QPSK, количество всех символов в одном закодированном с коррекцией ошибок блоке равно 32400, и количество битов на каждое слово ячейки равно 2.

Когда символы, формирующие канал PLP, распределяются по радиочастотным каналам, коэффициент разнесения частотной области может быть максимизирован, когда количества символов, распределенных соответствующим радиочастотным каналам, равны. Если рассматривается максимум шесть радиочастотных каналов, наименьшее общее кратное чисел от 1 до 6 равно 60, и наибольший общий делитель количеств символов, преобразованных в один закодированный с коррекцией ошибок блок равен 1200. В соответствии с этим, если целое количество из 1200/60=20 символов распределяется каждому из радиочастотных каналов, символы могут быть однородно распределены по всем радиочастотным каналам. В этом случае, если 20 символов рассматриваются как одна группа и группа адресуется, накладные расходы адресации могут быть уменьшены на log2(20)=4,32 битов по сравнению со случаем, когда символы адресуются один за другим.

Фиг.11 является изображением, показывающим другой пример количества символов в соответствии со способом символьного преобразования в нормальном режиме кодирования LDPC. В примере этого чертежа в качестве способа символьного преобразования использовались способ 256QAM, использующий символы 256QAM и 64QAM (256QAM:64QAM=4:1), способ Hyb 128QAM, использующий символы 256QAM и 64QAM (256QAM:64QAM=8:7), способ 64QAM, способ Hyb 32QAM, использующие символы 64QAM и 8QAM символы (64QAM:8QAM=3:2), способ 16QAM, использующий символы 16QAM и QPSK (16QAM:QPSK=1:14), способ Hyb 8QAM, использующий символы 16QAM:QPSK=2:1, и способ QPSK. Наибольший общий делитель (НОД; GCD) количеств всех символов закодированного с коррекцией ошибок блока (нормальный режим) в соответствии со способами символьного преобразования равен 720. В соответствии с этим, если целое количество из 12 (=720/60) символов распределено для каждого из радиочастотных каналов, символы могут быть однородно распределены по всем радиочастотным каналам. В этом случае, если 12 символов рассматриваются как одна группа и группа адресуются, накладные расходы адресации могут быть уменьшены на log2(12)=3,58 битов по сравнению со случаем, когда символы адресуются один за другим. Устройство приема сигнала может собрать распределенные символы канала PLP посредством схемы адресации и получить поток службы канала PLP.

Фиг.12 является изображением, показывающим другой пример количества символов в соответствии со способом символьного преобразования в нормальном режиме кодирования LDPC. В примере на этом чертеже в качестве способа символьного преобразования использовались схема 256QAM, схема Hyb 128QAM, схема 64QAM, схема Hyb 32QAM, схема 16QAM, схема Hyb 8QAM и схема QPSK. Способ 256QAM символьного преобразования использует символы 256QAM и 64QAM (256QAM:64QAM=44:1), и способ Hyb 128QAM символьного преобразования использует символы 256QAM и 64QAM (256QAM:64QAM=28:17). Способ Hyb 32QAM использует символы 64QAM и 8QAM (64QAM:8QAM=3:2), способ 16QAM символьного преобразования использует символы 16QAM и QPSK (16QAM:QPSK=1:14), и способ Hyb 8QAM символьного преобразования использует символы 16QAM и QPSK (16QAM:QPSK=2:1). Наибольший общий делитель (GCD) количеств всех символов закодированного с коррекцией ошибок блока (нормальный режим) в соответствии со способом символьного преобразования равен 240. В соответствии с этим, если целое количество из 240/60=4 символов распределяется на каждый из радиочастотных каналов, символы могут быть однородно распределены по всем радиочастотным каналам. В этом случае, если четыре символа рассматриваются как одна группа и группа адресуются, накладные расходы адресации могут быть уменьшены на log2(4)=2 бита по сравнению со случаем, когда символы адресуются по одному. В соответствии с этим, даже когда количество радиочастотных каналов в сигнальном кадре является любым числом от 1 до 6, символы канала PLP могут быть однородно распределены по радиочастотным каналам.

Фиг.13 является изображением, показывающим количество символов в соответствии с символьным преобразованием в коротком режиме кодирования LDPC. Как описано выше, если символьное преобразование выполняется в соответствии с этим примером, символы канала PLP могут быть однородно распределены по радиочастотным каналам, и накладные расходы адресации символов канала PLP могут быть уменьшены. Способы символьного преобразования, показанные на этом чертеже, совпадают с показанными на фиг.10. Однако, поскольку количество битов в коротком режиме кодирования LDPC отличается от нормального режима, наибольший общий делитель (GDC) количеств всех символов закодированного с коррекцией ошибок блока (короткий режим) в соответствии со способам символьного преобразования равен 300 в отличие от фиг.10. В соответствии с этим, если целое количество из 300/60=5 символов распределяется на каждый из радиочастотных каналов, символы могут быть однородно распределены по всем радиочастотным каналам. В этом случае, если пять символов рассматриваются как одна группа и выполняется адресация группы, накладные расходы адресации могут быть уменьшены на log2(5) битов по сравнению со случаем, когда символы адресуются по одному. В соответствии с этим, в этом варианте воплощения экономятся log2(5) битов адресации, когда выполняется адресация разделенных символов канала PLP.

Фиг.14 является изображением, показывающим пример количества символов в соответствии со способом символьного преобразования в коротком режиме кодирования LDPC. Способы символьного преобразования на этом чертеже совпадают с показанными на фиг.11. В этом примере наибольший общий делитель (GCD) количеств всех символов закодированного с коррекцией ошибок блока (короткий режим) в соответствии со способами символьного преобразования равен 180, и это может использоваться для распределения символов канала PLP одного радиочастотного канала и для адресации распределенных символов. В этом варианте воплощения экономятся log2(3) битов адресации.

Фиг.15 является изображением, показывающим другой пример количества символов в соответствии со способом символьного преобразования в коротком режиме кодирования LDPC. Способы символьного преобразования на этом чертеже совпадают с показанными на фиг.12. В этом примере наибольший общий делитель (GCD) количеств всех символов закодированного с коррекцией ошибок блока (короткий режим) в соответствии со способами символьного преобразования равен 60. В этом варианте воплощения экономятся log2(1) битов адресации (то есть биты адресации не экономятся).

Фиг.16 является изображением, показывающим пример каждого из модулей 131a и 131b преобразования символов, показанных на фиг.7. Каждый из модулей 131a и 131b преобразования символов включает в себя первый модуль 1315a преобразования первого порядка, модуль 1315b преобразования второго порядка, модуль 1317 слияния символов и модуль 1318 слияния блока коррекции ошибок.

Анализатор 1311 битового потока принимает поток службы канала PLP от модуля кодирования и модуляции и разделяет принятый поток службы.

Модуль 1315a преобразования символов первого порядка преобразует биты потока службы, разделенные посредством способа символьного преобразования высокого порядка, в символы. Модуль 1315b преобразования символов второго порядка преобразует биты потока службы, разделенные посредством способа символьного преобразования низкого порядка, в символы. Например, в упомянутом выше примере, модуль 1315a преобразования символов первого порядка может преобразовывать битовый поток в символы в соответствии со схемой 256QAM, и модуль 1315b преобразования символов второго порядка может преобразовывать битовый поток в символы в соответствии со схемой 64QAM.

Модуль 1317 слияния символов объединяет выходные данные из модулей 1315a и 1315b преобразования символов в один поток символов и выдает поток символов. Модуль 1317 слияния символов может выдавать поток символов, включенный в один канал PLP.

Модуль 1318 слияния блока коррекции ошибок может выдавать один поток символов, объединенный посредством модуля 1317 слияния символов, в закодированном с коррекцией ошибок блоке кодовых блоков. Модуль 1318 слияния блока коррекции ошибок может выдавать блок символов таким образом, что закодированные с коррекцией ошибок кодовые блоки однородно распределяются по меньшей мере одному радиочастотному диапазону сигнального кадра TFS. Модуль 1318 слияния блока коррекции ошибок может выдавать блок символов таким образом, что длина блока символов закодированного с коррекцией ошибок блока нормального режима равна длине блока символов закодированного с коррекцией ошибок блока короткого режима. Например, четыре блока символов закодированного с коррекцией ошибок блока короткого режима могут быть объединены в один блок символов.

Модуль 1318 слияния блока коррекции ошибок может разделять поток символов в соответствии с общим кратным количества радиочастотных диапазонов, с тем чтобы модуль построения сигнальных кадров однородно размещал символы по радиочастотным диапазонам. Если максимальное количество радиочастотных диапазонов в сигнальном кадре равно 6, модуль 1318 слияния блока коррекции ошибок выдает блок символов таким образом, что общее количество символов может быть разделено на число 60, которое является общим кратным чисел 1, 2, 3, 4, 5 и 6.

Символы, включенные в выходной блок символов, могут быть размещены таким образом, чтобы они были однородно распределены по шести радиочастотным диапазонам. В соответствии с этим, хотя режим коррекции ошибок в соответствии с кодовой скоростью и способом символьного преобразования является объединенным, символы, формирующие канал PLP, однородно распределяются по радиочастотным диапазонам.

Фиг.17 является изображением, показывающим другой вариант воплощения каждого из модулей преобразования 131a и 131b символов. Вариант воплощения на этом чертеже аналогичен варианту воплощения на фиг.16 за исключением того, что в него дополнительно включены модуль 1316a калибровки мощности первого порядка и модуль 1316b калибровки мощности второго порядка.

Модуль 1316a калибровки мощности первого порядка калибрует мощность символов, преобразованных модулем 1315a преобразования символов первого порядка, в соответствии с размером совокупности и выдает калиброванные символы. Модуль 1316b калибровки мощности второго порядка калибрует мощность символов, преобразованных модулем 1315b преобразования символов второго порядка, в соответствии с размером совокупности и выдает калиброванные символы. В соответствии с этим, хотя способ символьного преобразования изменяется в одном канале PLP или изменяется в множестве каналов PLP, если мощность символа, полученного посредством способа символьного преобразования, корректируется в соответствии с размером совокупности, производительность приема сигнала для приемника может быть улучшена.

Модуль 1317 слияния символов объединяет символы, калиброванные модулями 1316a и 1316b калибровки мощности, и выдает один поток символов.

Фиг.18 является изображением, показывающим другой вариант воплощения модуля преобразования символов. В варианте воплощения на этой фигуре модуль преобразования символов включает в себя второй кодер 125 и второй модуль 127 чередования, включенные в модуль кодирования и модуляции. Таким образом, если используется этот вариант воплощения, модуль кодирования и модуляции может включать в себя только первый кодер 121, первый модуль 123 чередования и второй кодер 125.

Вариант воплощения модуля преобразования символов включает в себя анализатор 1311 битового потока, модуль 1312a чередования битов первого порядка, модуль 1312b чередования битов второго порядка, демультиплексор 1313a первого порядка, демультиплексор 1313b второго порядка, модуль 1315a преобразования символов первого порядка, модуль 1315b преобразования символов второго порядка и модуль 1317 слияния символов.

Когда второй кодер 125 выполняет кодирование LDPC с коррекцией ошибок, длина закодированного с коррекцией ошибок блока (например, длина в 64800 битов и длина в 16200 битов) может изменяться в соответствии с режимом LDPC. Если биты, включенные в закодированный с коррекцией ошибок блок, преобразуются в символы, возможности коррекции ошибок битов, включенных в слово ячейки, формирующее символ, могут изменяться в соответствии с местоположениями битов. Например, слово ячейки, которое является символом, может быть определено в соответствии с кодовой скоростью кодирования с коррекцией ошибок и способом символьного преобразования (является ли способ символьного преобразования способом символьного преобразования высокого порядка или способом символьного преобразования низкого порядка). Если код с коррекцией ошибок является кодом LDPC, возможности коррекции ошибок битов изменяются в соответствии с местоположениями битов в закодированном с коррекцией ошибок блоке. Например, надежности битов, закодированных в соответствии с характеристиками H-матрицы, используемой в способе нерегулярного кодирования LDPC с коррекцией ошибок, могут изменяться в соответствием с местоположениями битов. В соответствии с этим, порядок битов, формирующих слово ячейки, преобразованных в символ, изменяется таким образом, что корректируются возможности коррекции ошибок битов, которые являются слабыми по сравнению с коррекцией ошибок в закодированном с коррекцией ошибок блоке, и может быть скорректирована устойчивость против ошибок на уровне битов.

Сначала второй кодер 125, например, выполняет кодирование с коррекцией ошибок относительно потока, включенного в один канал PLP, посредством способа кодирования LDPC с коррекцией ошибок.

Анализатор 1311 битового потока принимает поток службы в соответствии с каналом PLP и разделяет принятый поток службы.

Модуль 1312a чередования битов первого порядка выполняет чередование битов, содержащихся в первом битовом потоке из разделенных потоков службы. Аналогичным образом модуль 1312b чередования битов второго порядка выполняет чередование битов, содержащихся во втором битовом потоке из разделенных потоков службы.

Модуль 1312a чередования битов первого порядка и модуль 1312b чередования битов второго порядка могут соответствовать второму модулю 127 чередования, используемому в качестве внутреннего модуля чередования. Способ чередования модуля 1312a чередования битов первого порядка и модуля 1312b чередования битов второго порядка будет описан позже.

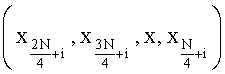

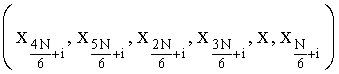

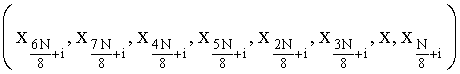

Демультиплексор 1313a первого порядка и демультиплексор 1313b второго порядка демультиплексируют биты битовых потоков, подвергнутых чередованию посредством модуля 1312a чередования битов первого порядка и модуля 1312b чередования битов второго порядка. Демультиплексоры 1313a и 1313b делят входной битовый поток на битовые подпотоки, которые будут преобразованы на действительную ось и мнимую ось совокупности, и выдают битовые подпотоки. Модули 1315a и 1315b преобразования символов преобразуют битовые подпотоки, демультиплексированные демультиплексорами 1313a и 1313b, на соответствующие символы.

Модули 1312a и 1312b чередования битов и демультиплексоры 1313a и 1313b могут объединять характеристики кодового слова LDPC и характеристики надежности совокупности символьного преобразования в соответствии с совокупностью. Подробный вариант воплощения мультиплексоров 1313a и 1313b будет описан позже.

Модуль 1315a преобразования символов первого порядка выполняет символьное преобразование первого порядка, например, символьное преобразование высокого порядка, и модуль 1315b преобразования символов второго порядка выполняет символьное преобразование второго порядка, например, символьное преобразование низкого порядка. Модуль 1315a преобразования символов первого порядка преобразует битовые подпотоки, выданные из демультиплексора 1313 первого порядка, в символы, и модуль 1315b преобразования символов второго порядка преобразует битовые подпотоки, выданные из демультиплексора 1313b второго порядка, в символы.

Модуль 1317 слияния символов объединяет символы, преобразованные модулем 1315a преобразования символов первого порядка и модулем 1315b преобразования символов второго порядка, в один поток символов и выдает поток символов.

Как описано выше, в кодировании LDPC возможности коррекции ошибок битов могут быть изменены в соответствии с местоположениями битов в закодированном с коррекцией ошибок блоке. В соответствии с этим, если модуль чередования битов и демультиплексор управляются в соответствии с характеристиками кодера 125 LDPC таким образом, чтобы изменить порядок битов, формирующих слово ячейки, возможность коррекции ошибок на уровне битов может быть максимизирована.

Фиг.19 является изображением, показывающим другой вариант воплощения каждого из модулей 131a и 131b преобразования символов. Вариант воплощения на этом чертеже аналогичен варианту воплощения на фиг.18 за исключением того, что в него дополнительно включены модуль 1316a калибровки мощности первого порядка и модуль 1316b калибровки мощности второго порядка.

Модуль 1316a калибровки мощности первого порядка калибрует мощность символов, преобразованных модулем 1315a преобразования символов первого порядка, в соответствии с размером совокупности и выдает калиброванные символы. Модуль 1316b калибровки мощности второго порядка калибрует мощность символов, преобразованных модулем 1315b преобразования символов второго порядка, в соответствии с размером совокупности и выдает калиброванные символы. В соответствии с этим, хотя схема символьного преобразования изменяется в одном канале PLP или изменяется в множестве каналов PLP, если мощность символа корректируется в соответствии с размером совокупности, производительность приема сигнала может быть улучшена.

Модуль 1317 слияния символов объединяет символы, калиброванные модулями 1316a и 1316b калибровки мощности, и выдает один поток символов.

Фиг.20 является изображением, показывающим концепцию чередования битов посредством модулей 1312a и 1312b чередования битов, показанных на фиг.18 и 19.

Например, входные биты сохраняются в памяти в виде матрицы, имеющей предопределенное количество строк и столбцов, и считываются из нее. Когда входные биты сохраняются, сначала они сохраняются в первом столбце в направлении строк, и если первый столбец заполняется, биты сохраняются в другом столбце в направлении строк. Когда сохраненные биты считываются, они считываются в направлении столбцов, и если считаны все биты, сохраненные в первой строке, считываются биты в другой строке в направлении столбцов. Другими словами, когда биты сохраняются, они сохраняются по строкам таким образом, что столбцы заполняются последовательно. И когда сохраненные биты считываются, они считываются по столбцам последовательно от первой строки до последней строки. На этой фигуре MSB обозначает старший значащий бит, и LSB обозначает младший значащий бит.

Чтобы отобразить биты, закодированные с коррекцией ошибок с помощью кода LDPC, в символы с одной и той же длиной блока коррекции ошибок при различных кодовых скоростях, модули 1312a и 1312b чередования битов могут изменять количество строк и столбцов памяти в соответствии с типами модулей 1315a и 1315b преобразования символов.

Фиг.21 иллюстрирует другой пример модулей чередования битов, которые выполняют чередование. Если модули 1312a и 1312b чередования битов сохраняют биты по столбцам, они могут сохранять биты для формирования смещения местоположения, где сохраняются биты, в каждом столбце. Если модули 1312a и 1312b чередования битов считывают сохраненные биты по строкам, они могут сохранять столько битов, на сколько смещено местоположение, где считываются биты, в каждой строке.

В примере на фиг.21 жирные точки соответственно представляют местоположение смещения. Например, модули чередования битов сохраняют биты по столбцам. В первом столбце биты сохраняются с первой строки до n-й строки (n - количество строк памяти) в обычном порядке. Во втором столбце биты сохраняются со строки (обозначенной как строка с номером r1) с жирной точкой до n-й строки, и затем биты сохраняются с первой строки до строки с номером r1-1. В третьем столбце биты сохраняются со строки с номером r2 с жирной точкой до n-й строки, и затем биты сохраняются с первой строки до строки с номером r2-1. Таким образом, биты сохраняются в каждом столбце в соответствии с циклической адресацией строк со строки, сдвинутой на смещение местоположения сохранения.

Если модули 1312a и 1312b чередования битов считывают сохраненные биты, они считывают биты из каждой строки в соответствии с циклической адресацией столбцов из местоположения, сдвинутого на смещение. Например, в первой строке модули чередования битов считывают сохраненные биты с первого столбца до m-го столбца (m - количество столбцов памяти) в обычном порядке. Во второй строке модули чередования битов считывают сохраненные биты со столбца (обозначенного как столбец с номером C1) с жирной точкой до m-го столбца и затем с первого столбца до столбца с номером С1-1. В третьей строке модули чередования битов считывают сохраненные биты от столбца (обозначенного как столбец с номером C2) с жирной точкой до m-го столбца и считывают биты от первого столбца до столбца с номером С2-1 в соответствии с циклической адресацией столбцов.

Фиг.22 иллюстрирует смещение, используемое при чередовании битов в соответствии со способом символьного преобразования. nCol представляет количество столбцов памяти модуля чередования битов. Если способ символьного преобразования представляет собой схему QPSK, количество столбцов памяти может быть равно двум (2). Модуль чередования битов может сохранять и считывать биты с использованием смещения, соответствующего второй строке во втором столбце Col2.

Если способ символьного преобразования представляет собой схему 16QAM, количество столбцов памяти может быть равным четырем (4). Модуль чередования битов может сохранять и считывать биты в соответствии со смещением, соответствующим второй строке во втором столбце Col2, четвертой строке в третьем столбце Col3 и седьмой строке в четвертом столбце Col4.

Если способ символьного преобразования представляет собой схему 64QAM, количество столбцов памяти может быть равным шести (6). Модуль чередования битов может сохранять и считывать биты в соответствии со смещением, соответствующим второй строке во втором столбце Col2, пятой строке в третьем столбце Col3, девятой строке в четвертом столбце Col4, десятой строке в пятом столбце Col5 и тринадцатой строке в шестом столбце Col6.

Если способ символьного преобразования представляет собой схему 256QAM, количество столбцов памяти может быть равным восьми (8). Модуль чередования битов может сохранять и считывать биты в соответствии со смешением, соответствующим второй строке в третьем столбце Col3, четвертой строке в четвертом столбце Col4, четвертой строке в пятом столбце Col5, пятой строке в шестом столбце Col6, седьмой строке в седьмом столбце Col7 и седьмой строке в восьмом столбце Col8.

Как описано выше, количество столбцов в памяти модуля чередования битов изменяется в зависимости от способа символьного преобразования, и модуль чередования битов может сохранять и считывать биты посредством изменения смещения в зависимости от количества столбцов. Количество битов, включенных в один символ в соответствии со способом символьного преобразования, может быть идентичным количеству столбцов. В соответствии с этим, после считывания битов модуль чередования битов может отобразить считанные биты на один символ в соответствии со способом преобразования. В этом случае биты, преобразованные в символ, могут быть переставлены. Кроме того, хотя даже возможность коррекции ошибок битов в конкретном местоположении понижается в соответствии со способом коррекции ошибок символа, поскольку биты, преобразованные в символ, переставляются в модуле чередования битов, возможность коррекции ошибок способа коррекции ошибок символа может быть максимизирована.

Фиг.23 является изображением, показывающим пример количества строк и столбцов блоков памяти модулей 1312a и 1312b чередования битов в соответствии с типами модулей 1315a и 1315b преобразования символов, если режим кодирования LDPC является нормальным режимом.

Например, если модуль 1315a преобразования символов преобразует биты в символы схемы 256QAM, модуль 1312a чередования первого порядка выполняет чередование битов с помощью памяти, имеющей 8100 строк и 8 столбцов. Если символы преобразуются посредством схемы 64QAM, модуль 1312a чередования первого порядка выполняет чередование битов с помощью памяти, имеющей 10800 строк и 6 столбцов. Если символы преобразуются посредством схемы 16QAM, модуль 1312a чередования первого порядка выполняет чередование битов с помощью памяти, имеющей 16200 строк и 4 столбца.

Например, если модули 1315a и 1315b преобразования символов преобразуют биты в символы схемы Hyb 128QAM, модуль 1312a чередования первого порядка выполняет чередование битов с использованием памяти, имеющей 4860 строк и 8 столбцов, и модуль 1312b чередования второго порядка выполняет чередование битов с использованием памяти, имеющей 4320 строк и 6 столбцов.

Аналогичным образом, если модули 1315a и 1315b преобразования символов преобразуют символы посредством схемы Hyb 32QAM, модуль 1312a чередования первого порядка выполняет чередование битов с использованием памяти, имеющей 6480 строк и 6 столбцов, и модуль 1312b чередования второго порядка выполняет чередование битов с использованием памяти, имеющей 6480 строк и 4 столбца.

Фиг.24 является изображением, показывающим пример количества строк и столбцов блоков памяти модулей 1312a и 1312b чередования битов в соответствии с типами модулей 1315a и 1315b преобразования символов, если режим кодирования LDPC является коротким режимом.

Например, если модуль 1315a преобразования символов преобразует биты в символы схемы 256QAM, модуль 1312a чередования первого порядка выполняет чередованием битов с помощью памяти, имеющей 2025 строк и 8 столбцов. Если модули 1315a и 1315b преобразования символов преобразуют символы посредством схемы Hyb 128QAM, модуль 1312a чередования первого порядка выполняет чередование битов с использованием памяти, имеющей 1215 строк и 8 столбцов, и модуль 1312b чередования второго порядка выполняет чередование битов с использованием памяти, имеющей 1080 строк и 6 столбцов.

Если чередование битов выполняется относительно закодированного с коррекцией ошибок блока, местоположения битов в закодированном с коррекцией ошибок блоке могут быть изменены.

Фиг.25 является схемой, показывающей концепцию другого варианта воплощения чередования модуля чередования битов. В варианте воплощения, показанном на этом чертеже, когда биты записываются в память, они записываются в направлении столбцов. Когда записанные биты считываются, биты циклически сдвинутых местоположений считываются в направлении строк. В каждой строке биты, записанные в каждой строке, циклически сдвигаются. Если биты записываются или считываются посредством способа циклического сдвига относительно строки или столбца памяти, это называется чередованием битов со смещением. Этот вариант воплощения имеет отношение к способу чередования битов со смещением, использующему способ чтения битов после того, как биты сдвигаются на один столбец в направлении строки. Вместо того, чтобы сдвигать записанные биты в памяти, может быть сдвинута точка считывания битов в памяти или точка записи битов в памяти.

В этом варианте воплощения N обозначает длину закодированного с коррекцией ошибок блока, и C обозначает длину столбца. Когда биты записываются, они записываются в первом столбце (заштрихован) в порядке 1, 2, 3, 4, ... и C, и биты записываются во втором столбце в порядке C+1, C+2, C+3, ...

Записанные биты сдвигаются в направлении строки столбец за столбцом.

Если записанные биты считываются, сдвинутые биты считываются в направлении строк. Например, в этом варианте воплощения биты считываются в первой строке в порядке 1, C+1, ..., и биты считываются во второй строке в порядке X1, 2, C+2, ... (X1 представляет собой бит в первом столбце второй строки). Биты считываются строка за строкой, и считываются циклически сдвинутые биты. Безусловно, вместо сдвига записанных битов в памяти может сдвигаться точка считывания записанных в памяти битов.

Фиг.26 является изображением, показывающим другой вариант воплощения чередования битов. В этом варианте воплощения N обозначает длину закодированного с коррекцией ошибок блока, и C обозначает длину столбца. Когда биты записываются, они записываются в первом столбце в порядке 1, 2, 3, 4, ..., C-1 и C, и биты записываются во втором столбце в порядке C+1, C+2, C+3, ... .

Записанные биты дважды сдвигаются в направлении строк через два столбца. Если записанные биты читаются, биты, циклически сдвинутые на два столбца, считываются в направлении столбцов в каждой строке. Этот способ можно назвать способом чередования битов с двойным смещением.

Фиг.27 является изображением, показывающим другой вариант воплощения чередования битов. В этом варианте воплощения N обозначает длину закодированного с коррекцией ошибок блока, и C обозначает длину столбца. Биты записываются в первом столбце в порядке 1, 2, 3, 4, ..., C-1 и C, и биты записываются во втором столбце в порядке C+1, C+2, C+3.

Когда записанные биты считываются, в первой области строк биты могут считываться посредством способа чередования битов со смещением.

Во второй области строк биты могут считываться посредством способа чередования с двойным смещением.

В третьей области строк биты могут считываться посредством способа чередования битов со смещением.

Если биты чередуются посредством по меньшей мере одного способа из способа чередования битов со смещением и способа чередования с двойным смещением, биты в закодированном с коррекцией ошибок блоке могут быть смешаны более случайно.