Результат интеллектуальной деятельности: ОДНОРАЗРЯДНЫЙ ПОЛНЫЙ СУММАТОР С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ

Вид РИД

Изобретение

Предполагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются суммирующие устройства, реализованные на основе одноразрядных сумматоров. Каждый из них складывает два текущих разряда суммируемых чисел, обеспечивает и перенос из предыдущего разряда, а также формирует на выходах текущий разряд суммы и перенос в следующий старший разряд [1-12]. Входные и выходные сигналы в классических сумматорах представляют собой высокий или низкий потенциалы, соответствующие логической «1» или логическому «0» булевой алгебры.

В работе [13], а также монографиях соавтора настоящей заявки [14-15] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство относится к этому типу вычислительных устройств.

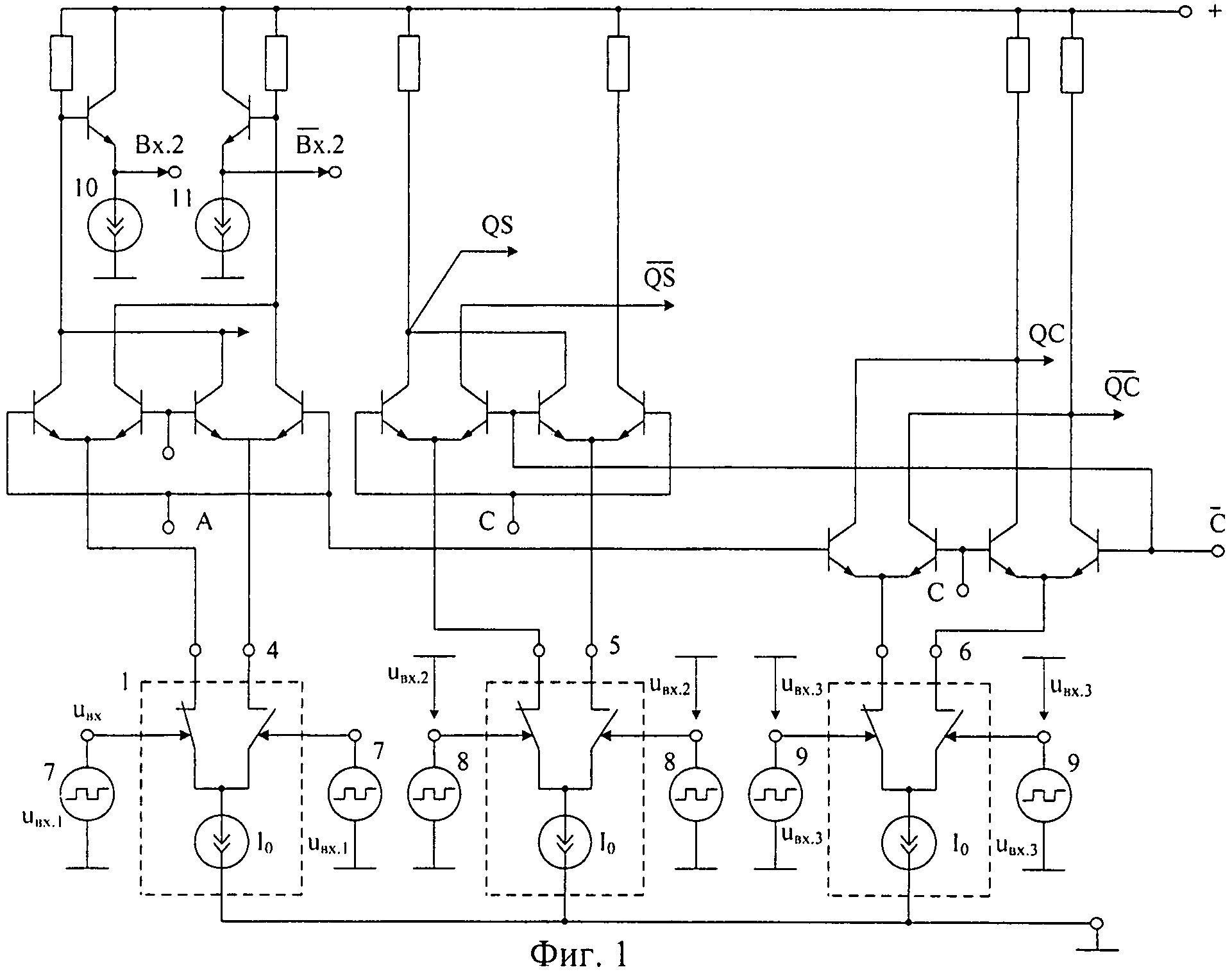

Ближайшим прототипом заявляемого устройства является полный сумматор, представленный в патенте US 4.831.579, fig.1. Он содержит (фиг.1) первый 1, второй 2 и третий 3 входные коммутаторы квантов тока I0 с первым 4, вторым 5 и третьим 6 токовыми выходами, первый 7, второй 8 и третий 9 источники входных логических сигналов, управляющие состоянием соответствующих 1, 2, 3 коммутаторов квантов тока I0, первый 10 и второй 11 вспомогательные источники опорного тока.

Существенный недостаток известного полного сумматора (ПС) состоит в том, что он, используя потенциальные двоичные сигналы, обладает усложненной структурой связей, нелинейностью рабочих режимов элементов и критичностью параметров структуры ПС, а также входных сигналов, что в конечном итоге приводит к снижению его быстродействия.

Основная задача предполагаемого изобретения состоит в создании устройства, в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов, определяемое состоянием входных потенциальных двоичных сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [14-15].

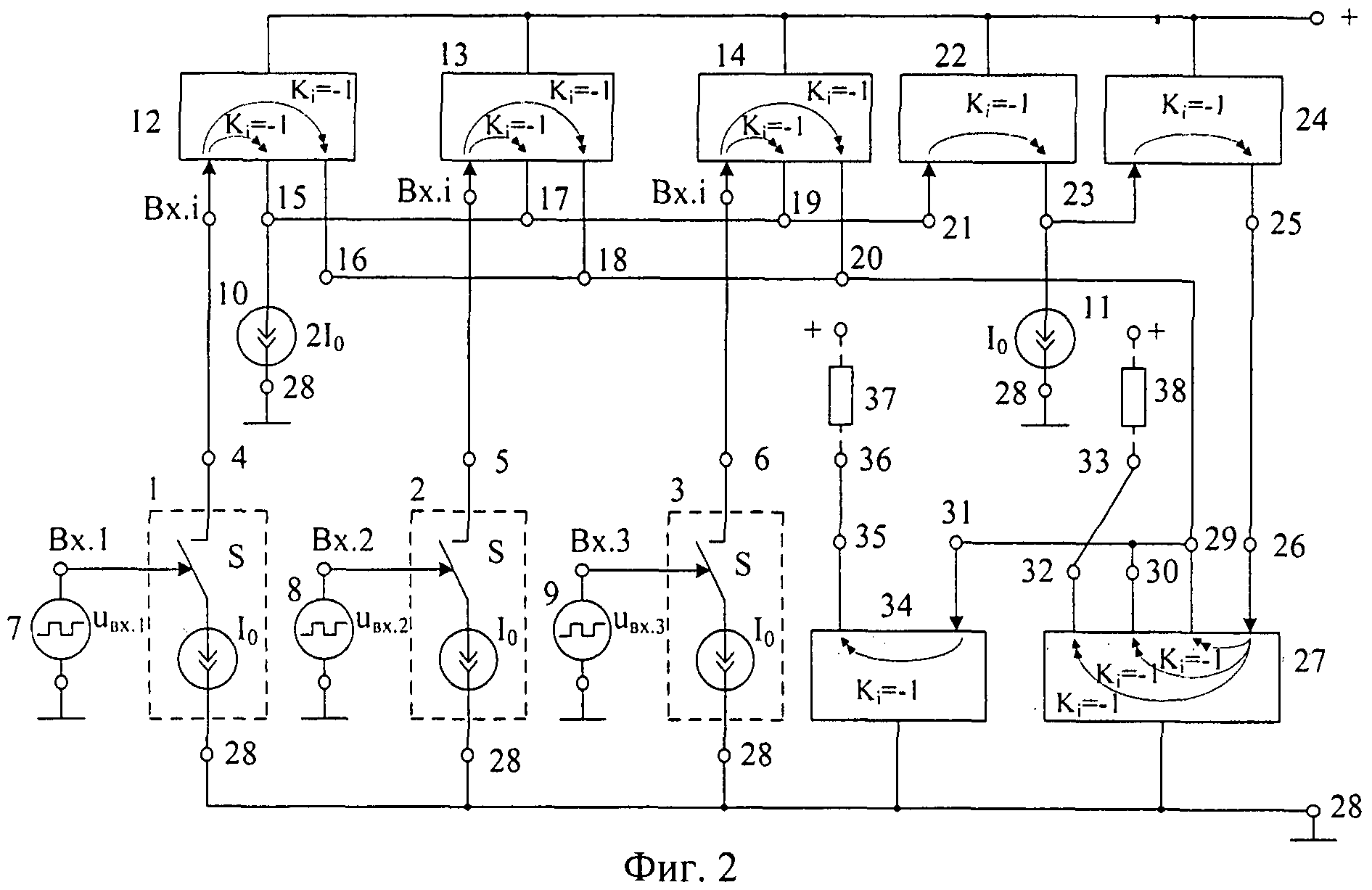

Поставленная задача решается тем, что в одноразрядном полном сумматоре с многозначным внутренним представлением сигналов (фиг.1), содержащем первый 1, второй 2 и третий 3 входные коммутаторы квантов тока I0 с первым 4, вторым 5 и третьим 6 токовыми выходами, первый 7, второй 8 и третий 9 источники входных логических сигналов, управляющие состоянием соответствующих 1, 2, 3 коммутаторов квантов тока I0, первый 10 и второй 11 вспомогательные источники опорного тока, предусмотрены новые элементы и связи - в схему введены первое 12, второе 13 и третье 14 токовые зеркала, каждое из которых имеет по два инвертирующих идентичных токовых выхода (15 и 16, 17 и 18, 19 и 20), токовый вход первого 12 токового зеркала соединен с токовым выходом 4 первого 1 входного коммутатора кванта тока I0, токовый вход второго 13 токового зеркала соединен с токовым выходом 5 второго 2 входного коммутатора кванта тока I0, токовый вход третьего 14 токового зеркала соединен с токовым выходом 6 третьего 3 входного коммутатора кванта тока I0, первая группа из трех 15, 17 и 19 идентичных токовых выходов первого 12, второго 13 и третьего 14 токовых зеркал связана с первым 10 источником опорного тока и соединена со входом 21 первого дополнительного токового зеркала 22, выход которого 23 связан со вторым 11 вспомогательным источником опорного тока и подключен ко входу второго 24 дополнительного токового зеркала, выход 25 второго дополнительного токового зеркала 24 соединен со входом 26 третьего дополнительного токового зеркала 27, согласованного с общей шиной источника питания 28, вторая группа из трех 16, 18, 20 идентичных токовых выходов первого 12, второго 13 и третьего 14 токовых зеркал подключена к первому 29 и второму 30 токовым выходам третьего 27 дополнительного токового зеркала и связана с первым 31 выходом устройства, а третий 32 токовый выход третьего 27 дополнительного токового зеркала соединен со вторым токовым выходом 33 устройства.

Схема одноразрядного полного сумматора-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 формулы изобретения.

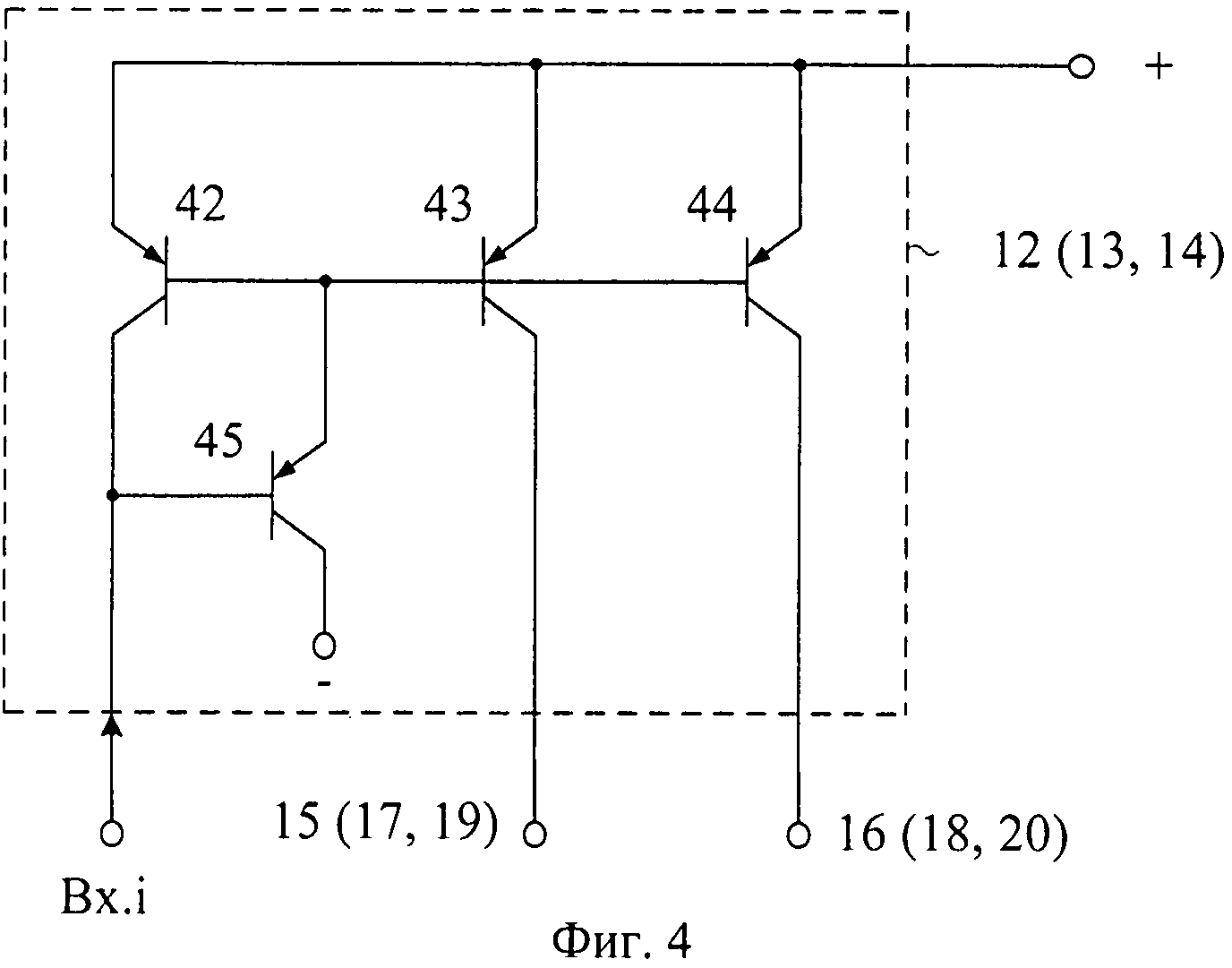

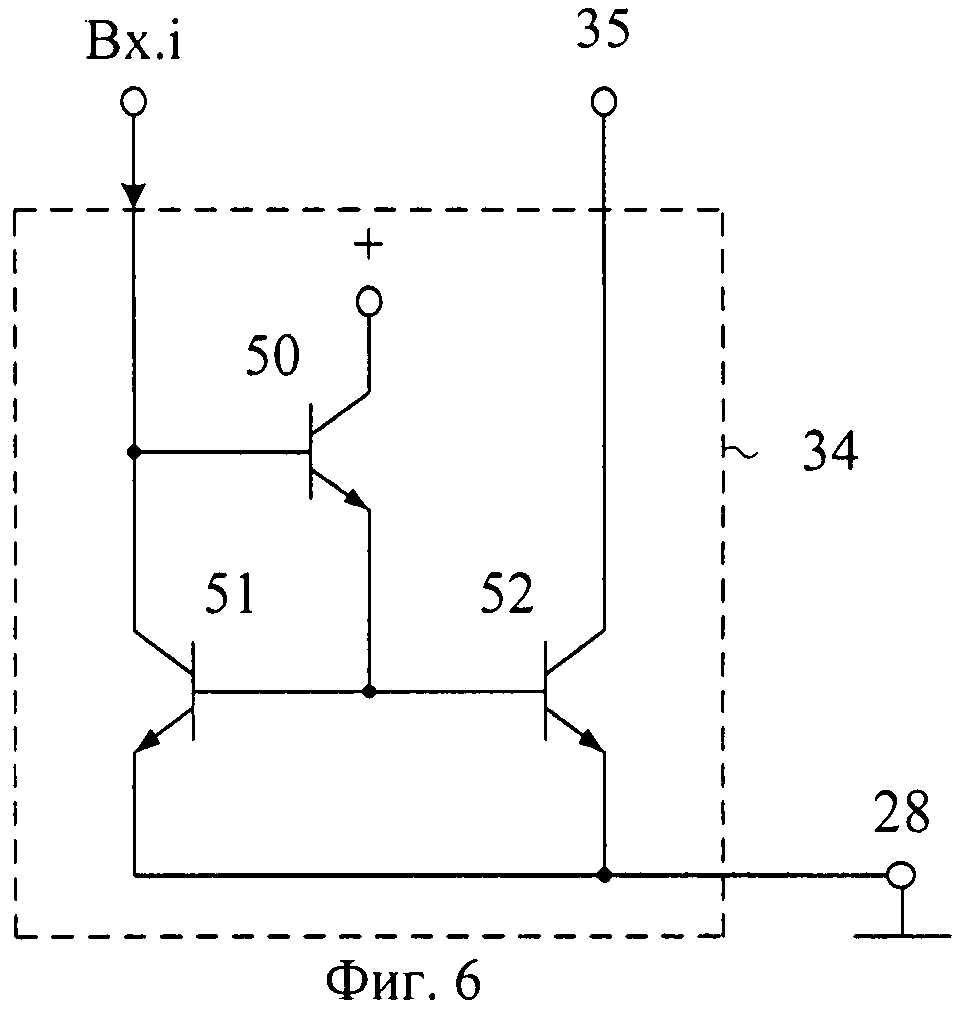

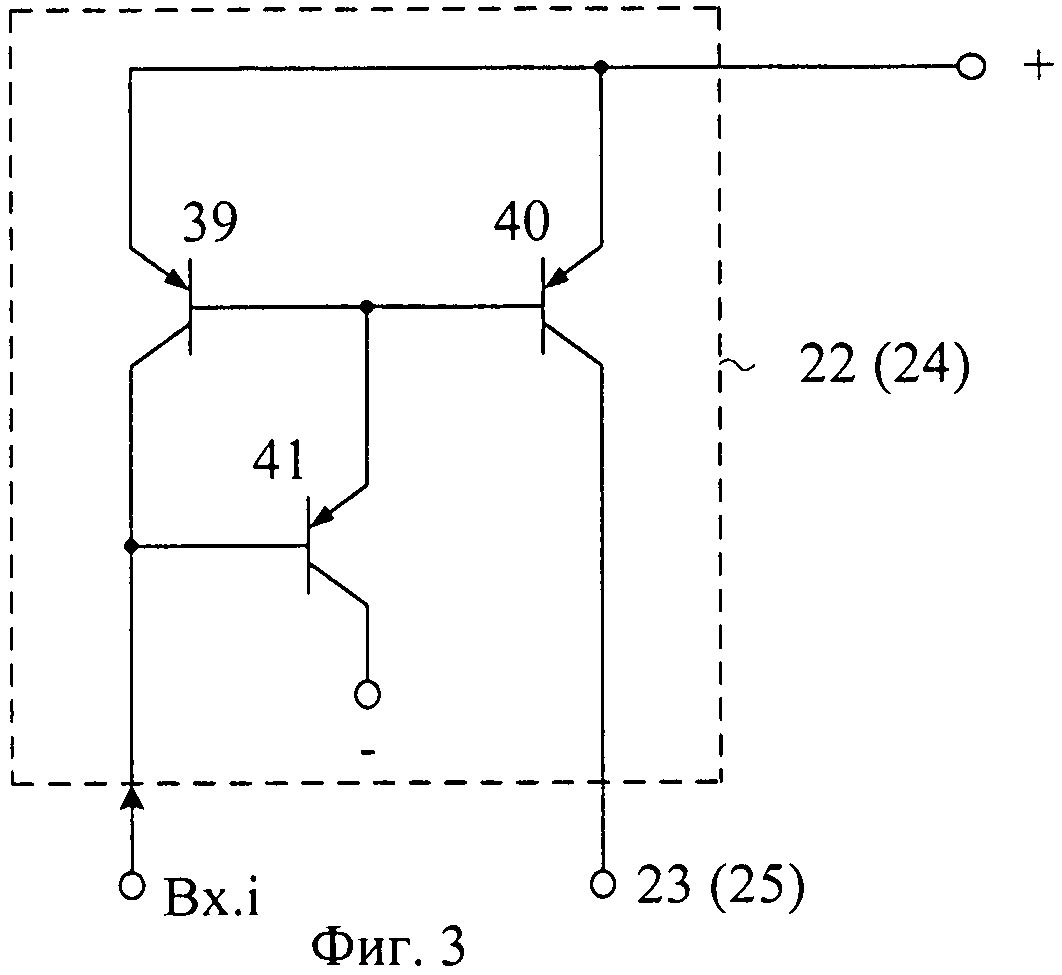

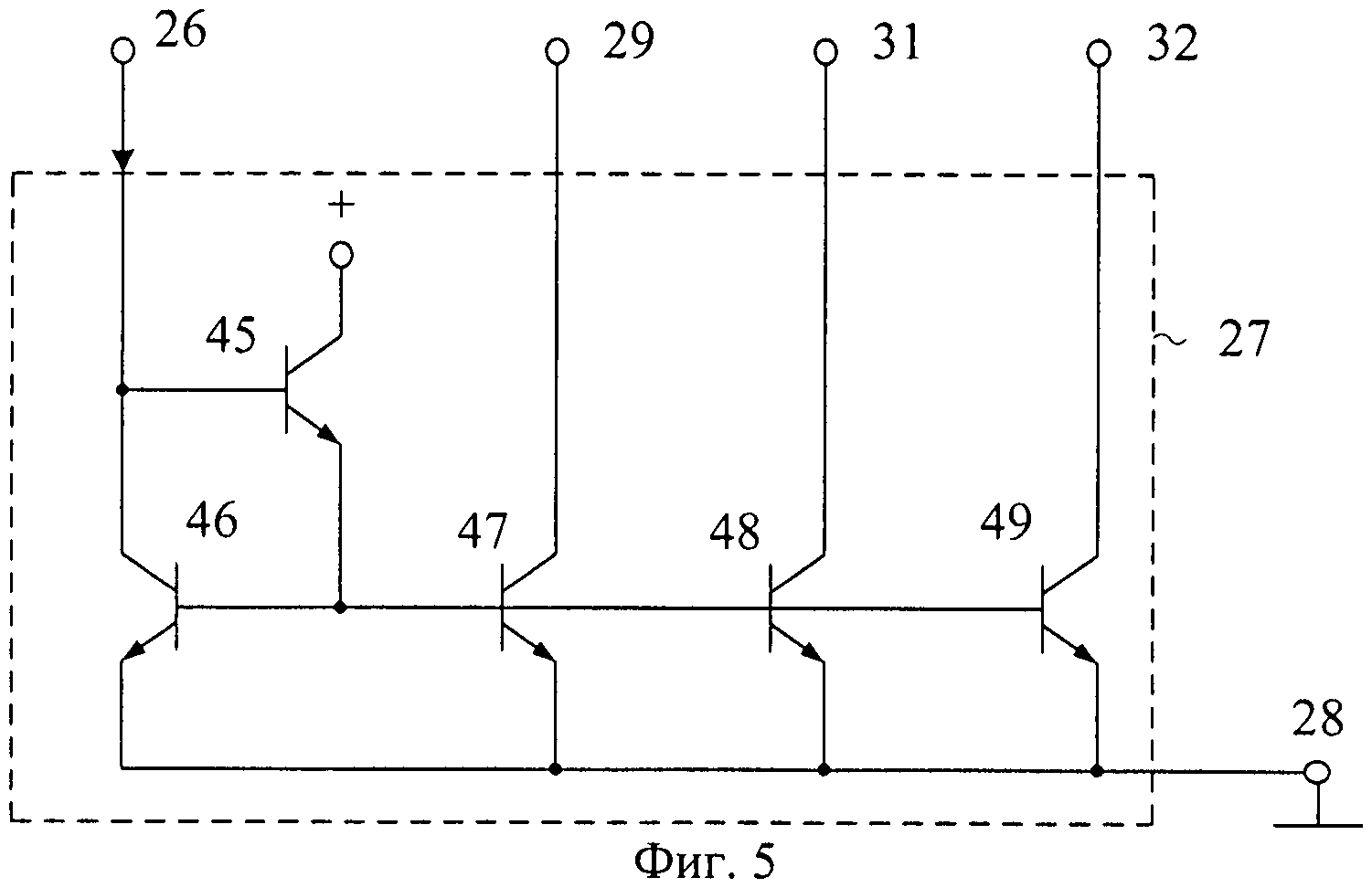

На чертеже фиг.3, фиг.4, фиг.5, фиг.6 показаны варианты построения соответствующих первого 22 и второго 24 дополнительных токовых зеркал (фиг.3), первого 12, второго 13, третьего 14 токовых зеркал (фиг.4), а также третьего 27 (фиг.5) и четвертого (34) (фиг.6) дополнительных токовых зеркал.

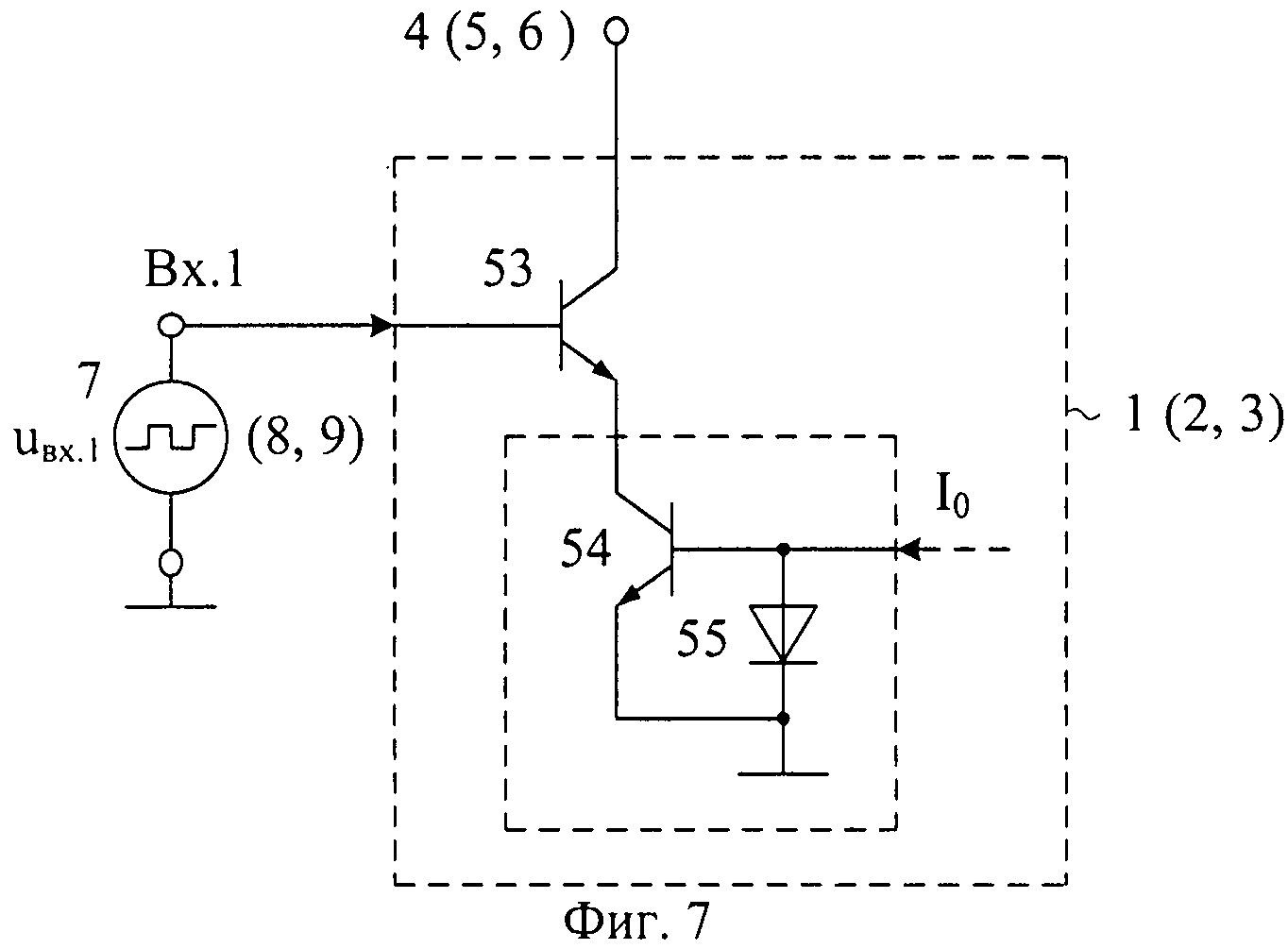

На чертеже фиг.7 приведена одна из возможных схем первого 1, второго 2 и третьего 3 входных коммутаторов кванта тока I0.

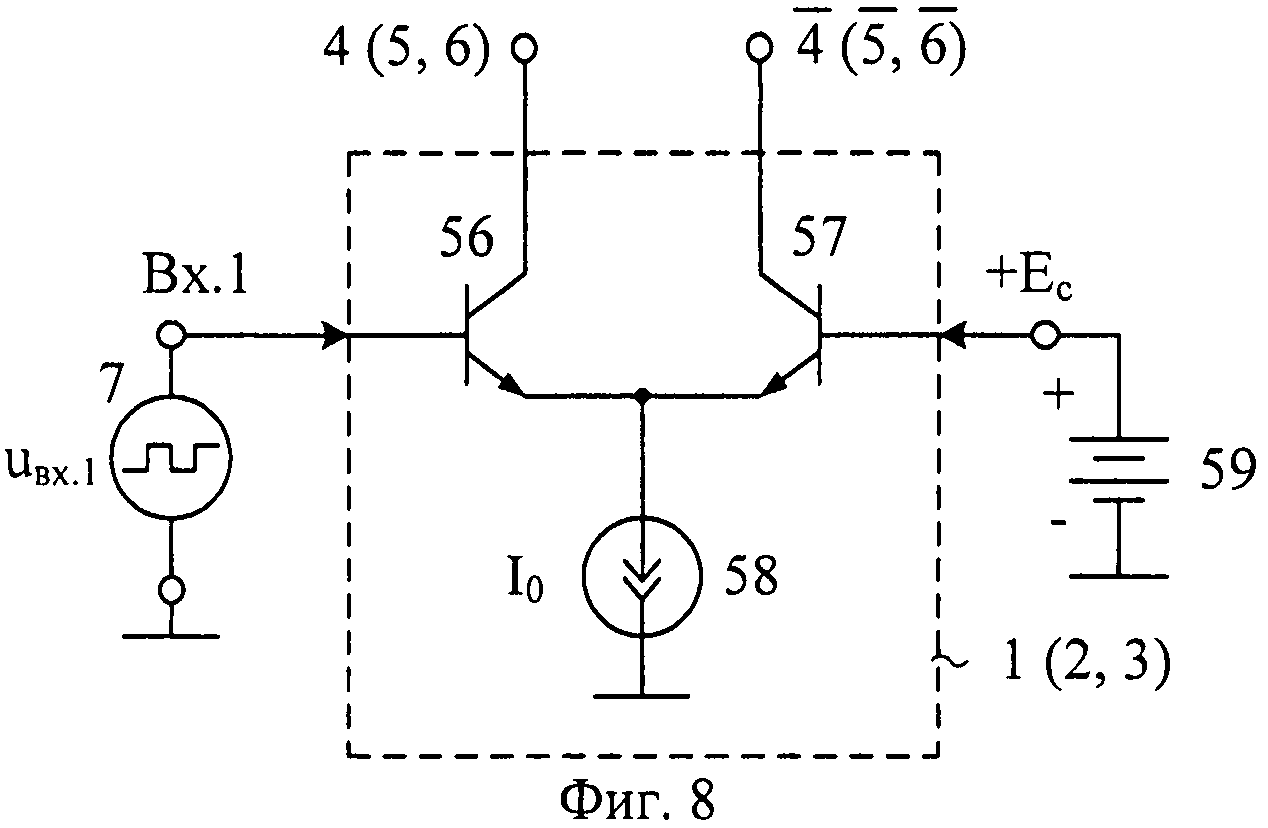

На чертеже фиг.8 приведена возможная схема входных коммутаторов 1, 2, 3 квантов тока I0, реализованных на основе дифференциальных каскадов (элементы 56, 57, 58).

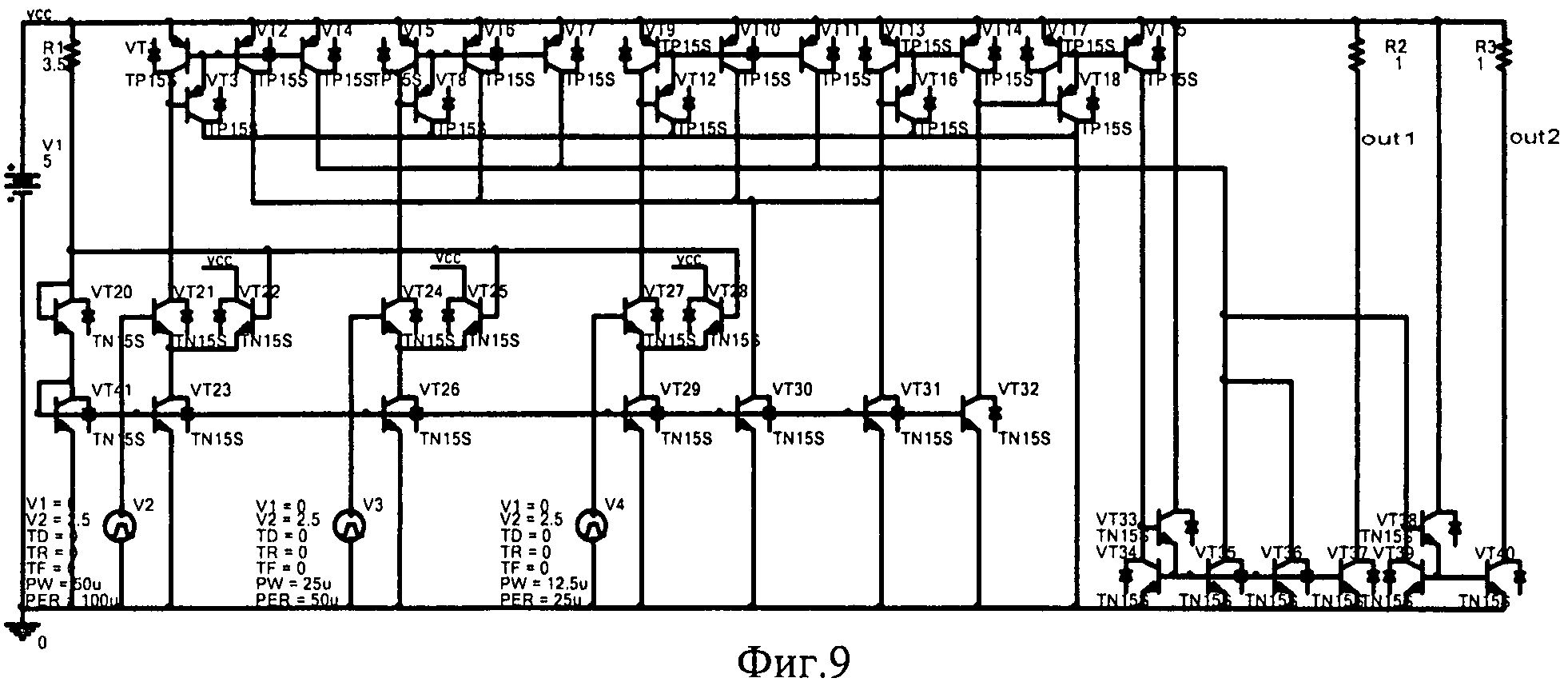

На чертеже фиг.9 показана схема полного сумматора фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» с использованием коммутаторов квантов тока фиг.8.

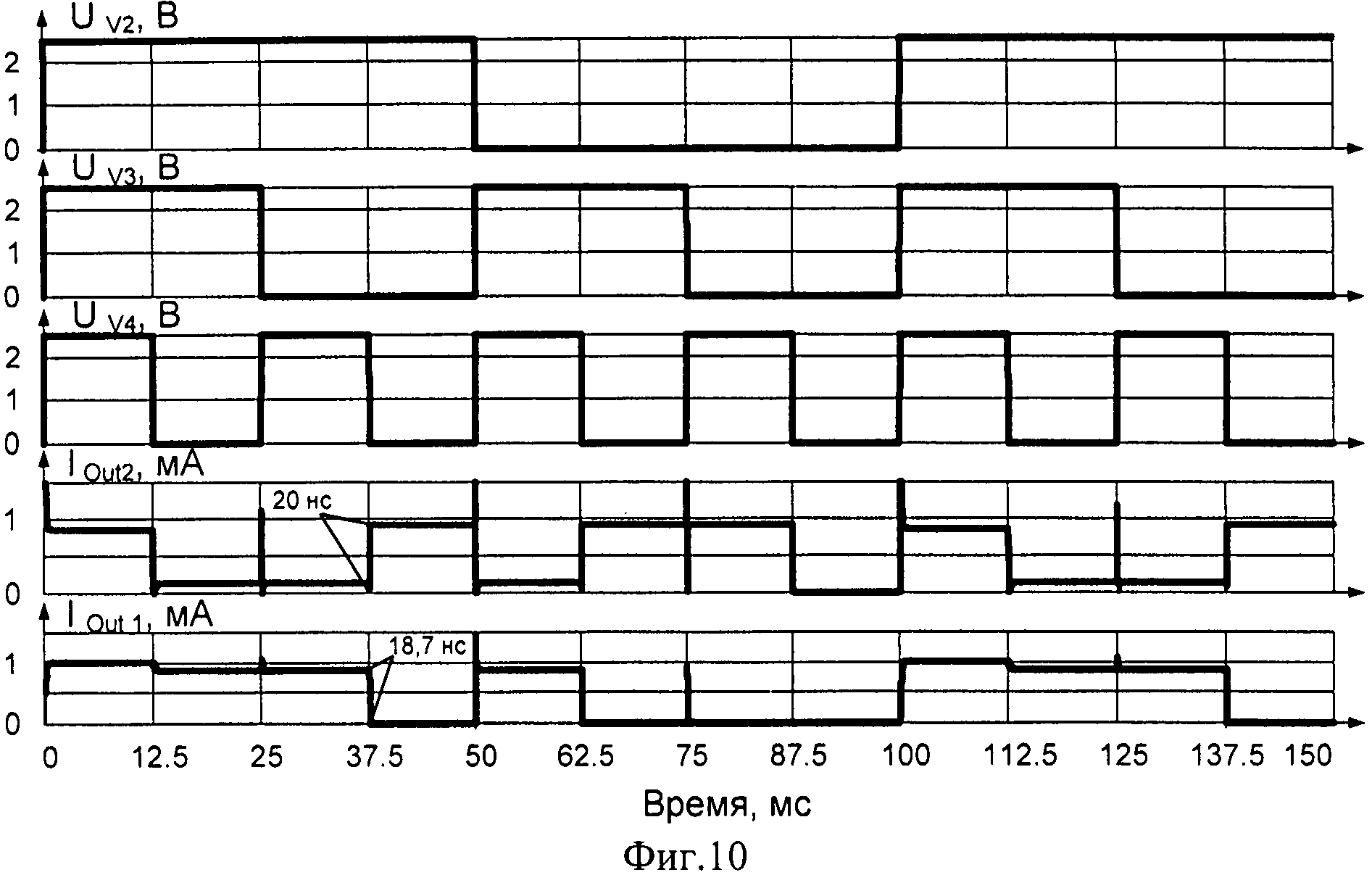

На чертеже фиг.10 представлен переходный процесс на логических входах и токовых выходах полного сумматора фиг.9.

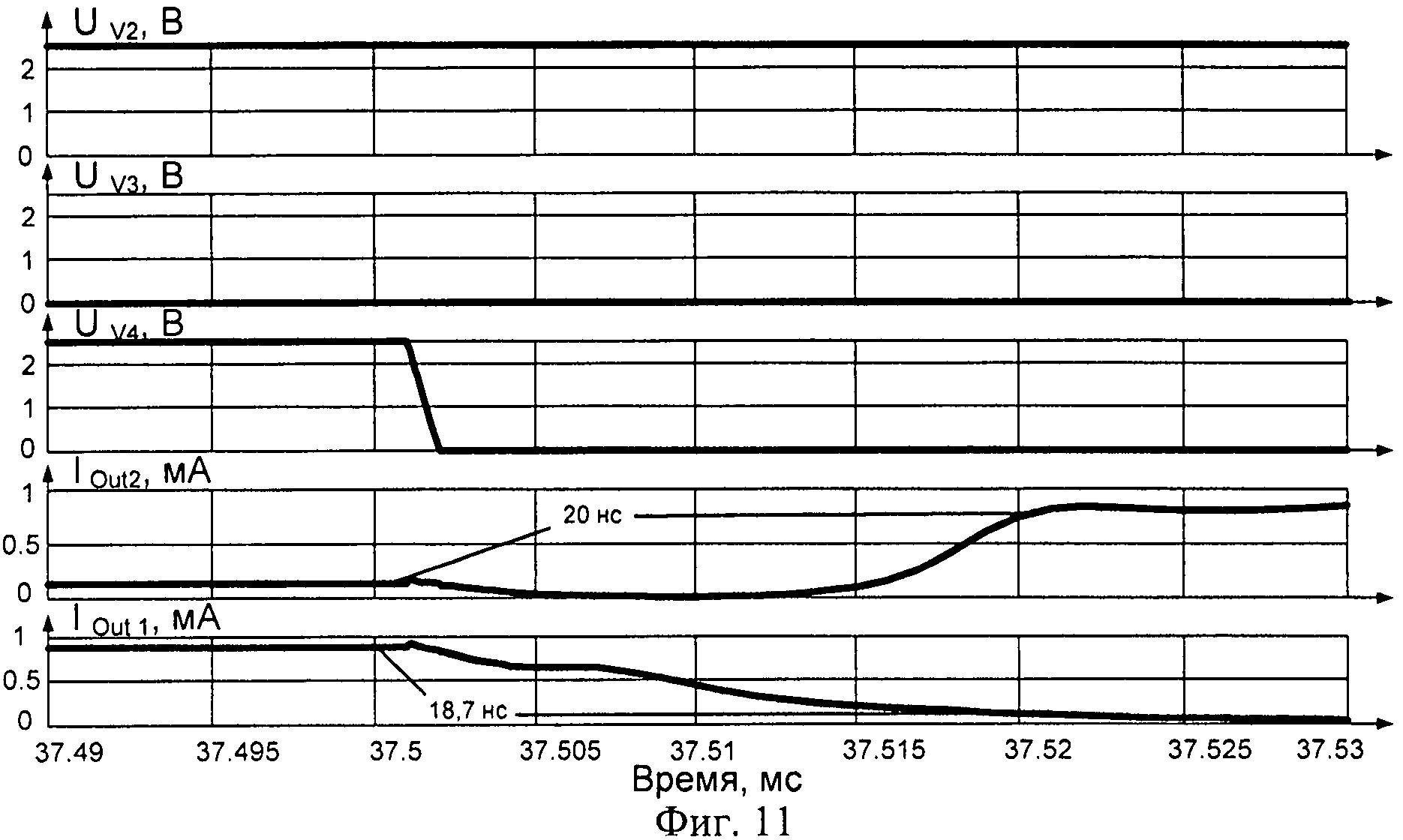

На чертеже фиг.11 показан переходный процесс на входах и выходах полного сумматора фиг.9 в увеличенном масштабе.

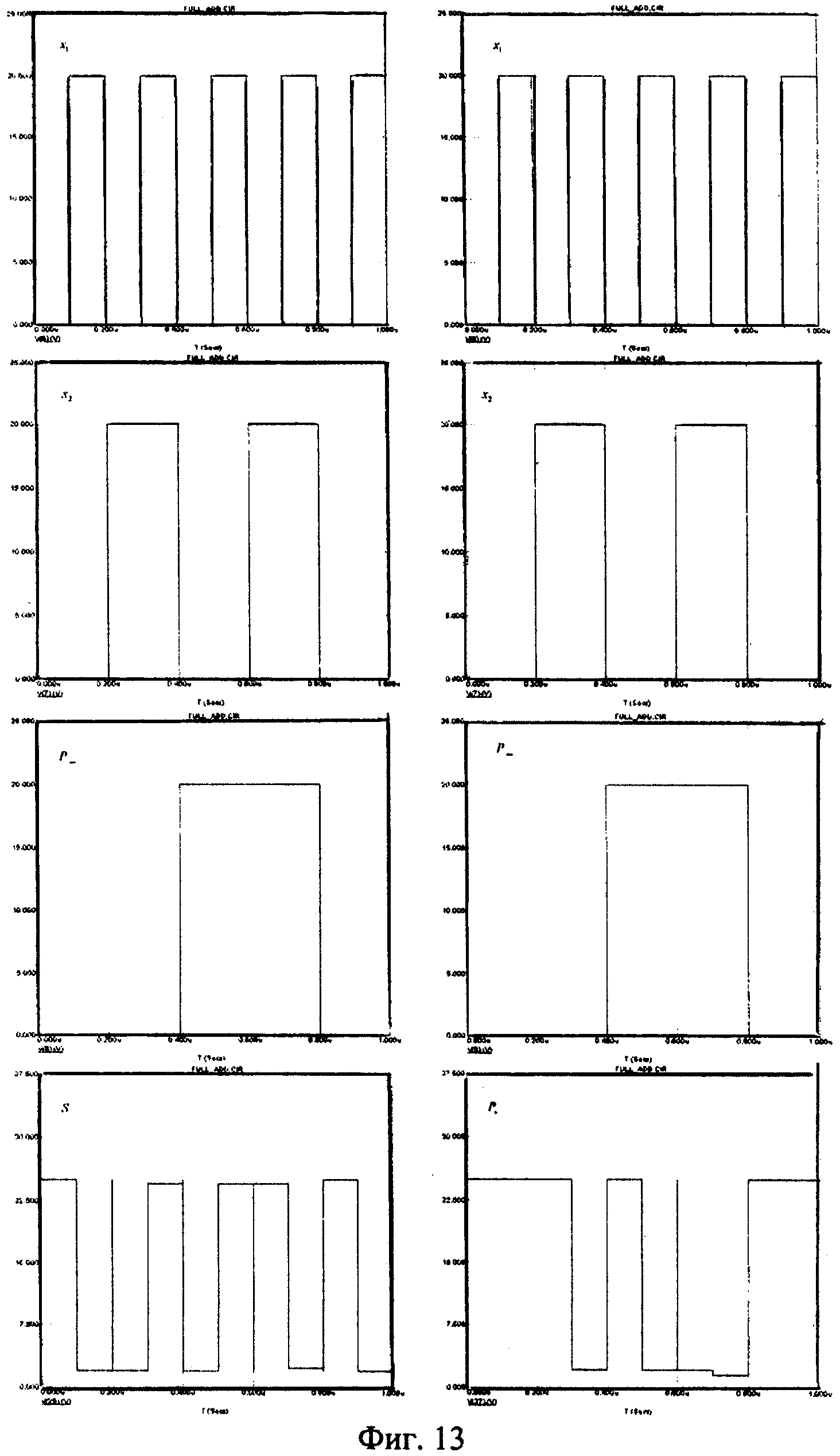

На чертеже фиг.12 показана схема полного сумматора фиг.2 в среде Micro-Cap с реализацией коммутаторов квантов тока 1, 2, 3 I0 в соответствии с чертежом фиг.7, а на чертеже фиг.13 - зависимость выходных токовых сигналов ПС фиг.12 от входных логических напряжений.

Одноразрядный полный сумматор с многозначным внутренним представлением сигналов фиг.2 содержит первый 1, второй 2 и третий 3 входные коммутаторы квантов тока I0 с первым 4, вторым 5 и третьим 6 токовыми выходами, первый 7, второй 8 и третий 9 источники входных логических сигналов, управляющие состоянием соответствующих 1, 2, 3 коммутаторов квантов тока I0, первый 10 и второй 11 вспомогательные источники опорного тока. В схему введены первое 12, второе 13 и третье 14 токовые зеркала, каждое из которых имеет по два инвертирующих идентичных токовых выхода (15 и 16, 17 и 18, 19 и 20), токовый вход первого 12 токового зеркала соединен с токовым выходом 4 первого 1 входного коммутатора кванта тока I0, токовый вход второго 13 токового зеркала соединен с токовым выходом 5 второго 2 входного коммутатора кванта тока I0, токовый вход третьего 14 токового зеркала соединен с токовым выходом 6 третьего 3 входного коммутатора кванта тока I0, первая группа из трех 15, 17 и 19 идентичных токовых выходов первого 12, второго 13 и третьего 14 токовых зеркал связана с первым 10 источником опорного тока и соединена со входом 21 первого дополнительного токового зеркала 22, выход которого 23 связан со вторым 11 вспомогательным источником опорного тока и подключен ко входу второго 24 дополнительного токового зеркала, выход 25 второго дополнительного токового зеркала 24 соединен со входом 26 третьего дополнительного токового зеркала 27, согласованного с общей шиной источника питания 28, вторая группа из трех 16, 18, 20 идентичных токовых выходов первого 12, второго 13 и третьего 14 токовых зеркал подключена к первому 29 и второму 30 токовым выходам третьего 27 дополнительного токового зеркала и связана с первым 31 выходом устройства, а третий 32 токовый выход третьего 27 дополнительного токового зеркала соединен со вторым токовым выходом 33 устройства.

Кроме этого, на чертеже фиг.2, в соответствии с п.2 формулы изобретения, первый 31 токовый выход устройства соединен со входом четвертого 34 дополнительного токового зеркала, выход которого 35 связан с третьим 36 токовым выходом устройства, нагрузкой которого является двухполюсник 37, моделирующий свойства некоторого логического элемента с токовым входным сигналом. Нагрузкой ПС по выходу 33 является аналогичный двухполюсник 38.

На чертеже фиг.3 показаны схемы токовых зеркал 22 и 24, которые реализованы на транзисторах 39, 40, 41.

На чертеже фиг.4 приведены схемы первого 12, второго 13 и третьего 14 токовых зеркал, которые реализованы на транзисторах 42, 43, 44. 45.

На чертеже фиг.5 показана схема третьего 27 дополнительного токового зеркала, которая содержит транзисторы 45, 46, 47, 48, 49.

На чертеже фиг.6 приведена схема четвертого 34 дополнительного токового зеркала на транзисторах 50, 51, 52.

На чертеже фиг.7 приведены варианты построения первого 1, второго 2 и третьего 3 входных коммутаторов квантов тока I0 на элементах 53, 54, 55.

На чертеже фиг.8 показан вариант построения первого 1, второго 2 и третьего 3 входных коммутаторов квантов тока I0 на основе дифференциальных каскадов, содержащих элементы 56, 57, 58, а также источник опорного напряжения 59.

На чертеже фиг.9 каждый из входных коммутаторов 1, 2, 3 кванта тока I0, управляемых источниками входных логических напряжений V2, V3, V4, выполнен в виде дифференциальных каскадов в соответствии с чертежом фиг.8.

На чертеже фиг.12 показан частный случай построения полного сумматора фиг.2 с использованием входных коммутаторов 1, 2, 3 квантов тока I0, которые реализованы на транзисторах 53, 54 и р-n переходе 55 (фиг.7).

Рассмотрим работу предлагаемой схемы полного сумматора фиг.2.

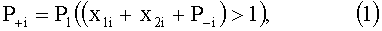

Синтез логической функции суммы S и переноса в следующий разряд Р+ производится на основе их представления в линейной алгебре [14-15]. В предикатной форме эти функции могут быть описаны следующим образом:

где P+i - сигнал переноса в следующий разряд;

P-i - сигнал переноса из предыдущего разряда;

x1i, x2i - сигналы i-x разрядов складываемых чисел;

Pi(x1,х2) - предикаты [14-15].

Реализация функции переноса в следующий разряд Р+i производится «монтажным» суммированием квантов токов I0 с первых выходов 15, 17, 19 токовых зеркал 12, 13, 14 и вычитанием из этой суммы кванта тока I0 источника тока 11. Результат снимается с узла суммирования 23 и подается на вход дополнительного токового зеркала 24, с которого токовый сигнал через выход 25 поступает на вход 26 токового зеркала 27.

Реализация функции суммы производится «монтажным» суммированием квантов токов с выходов 16, 18 и 20 токовых зеркал 12, 13 и 14 и вычитанием из этой суммы удвоенного значения переноса с выходов 30 и 29 токового зеркала 27. Результат алгебраического суммирования поступает на первый выход устройства 31, а при необходимости на вход токового зеркала 34 для формирования выходного кванта тока, соответствующего логической сумме.

Как видно из приведенного описания реализация логических функций суммы и переноса здесь производится формированием алгебраической суммы квантов тока I0 и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Особенностью полного сумматора по схеме фиг.9 является реализация входных коммутаторов квантов тока 1, 2 и 3 в виде дифференциальных каскадов фиг.8. Здесь каждый дифференциальный каскад производит коммутацию кванта тока I0. При этом источник тока I0 при любом состоянии входного логического сигнала не выходит из активного режима, что повышает быстродействие схемы.

Показанные на чертежах фиг.10, фиг.11, фиг.13 результаты моделирования подтверждают указанные свойства заявляемой схемы, которая может также реализовываться в базисе КМОП транзисторов. Следует отметить, что кратковременные импульсы на выходе сумматора, возникающие в момент переключения входных сигналов, характерные и для других известных сумматоров, определяются различными временами переключения входных коммутаторов квантов тока 1, 2, 3 и могут быть устранены в реальных схемах средствами технологии.

Таким образом, рассмотренные схемотехнические решения одноразрядного полного сумматора характеризуются многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Авторское свидетельство СССР SU 892729

2. Патентная заявка WO 2004/112247

3. Патент US 4.001.603

4. Патент US 4.359.653

5. Патент US 6.157.693; fig.5

6. Патент US 5.216.295

7. Патент US 3.758.791, fig.5

8. Патент US 4.593.211

9. Патент US 4.347.446

10. Патент US 4.516.039, fig.5

11. Патент US 4.970.416

12. Патент US 4.605.871, fig.2

13. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С.84-93.

14. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

15. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие. - Таганрог: ТРТУ, 2004 г. - 118 с.