Результат интеллектуальной деятельности: УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ

Вид РИД

Изобретение

Изобретение относится к технике организации интервальных вычислений в формате с плавающей запятой и направлено на повышение точности оценивания интервальных границ при заданной разрядности кода, хранимого в памяти ЭВМ. Предполагается, что промежуточные вычисления могут выполняться с большей разрядностью, чем разрядность чисел сохраняемых в памяти ЭВМ. Предлагаемое устройство для совместного кодирования двух границ интервала использует 64 разряда.

Известны метод и аппаратура для представления арифметических интервалов в вычислительной системе (US 6658443 В1, 02.12.2003).

При выполнении арифметических операций система выполняет считывание из памяти двух интервалов. Каждый из интервалов представлен первым числом в формате с плавающей запятой, являющимся первой границей интервала, и вторым числом в формате с плавающей запятой, являющимся второй границей интервала. Затем система выполняет вычислительные операции по правилам интервальной арифметики, получая результат вычислений в виде интервала. Результирующий интервал также представлен двумя числами в формате с плавающей запятой.

Сущность технического решения проявляется в ситуациях, когда интервалы становятся очень большими, что соответствует потере значимости результата.

Недостатком системы является низкая точность метода, провоцирующая ситуацию получения больших интервалов представляющих результаты расчетов.

Известна вычислительная система для интервальных вычислений, наиболее близкая по своей технической сущности к предлагаемому изобретению и выбранная в качестве прототипа (RU 2006929 С1, 30.01.1994).

Данная вычислительная система содержит первый и второй модули памяти для хранения чисел, являющихся верхней и нижней границами интервалов, два арифметических устройства для вычисления верхних и нижних границ интервалов, группу мультиплексоров, осуществляющих коммутацию выбираемых из памяти в арифметические блоки и записываемых из арифметических блоков в память кодов интервалов.

В процессе вычислений из двух модулей памяти одновременно извлекаются верхняя и нижняя границы первого интервала, затем одновременно извлекаются верхняя и нижняя границы второго интервала. Считанные из памяти числа направляются в операционные блоки, осуществляющие вычисления по правилам интервальной арифметики. Получившийся в результате вычислений интервал записывается в память в виде двух чисел, представленных в формате с плавающей запятой.

Недостаток устройства системы, выбранного в качестве прототипа, - малая разрядность мантисс верхней и нижней граней, хранимых в памяти. Это приводит к быстрому увеличению интервалов при вычислениях, что в свою очередь приводит к чрезмерно пессимистическим оценкам точности результатов вычислений.

Технический результат изобретения - увеличение точности интервальных вычислений в формате с плавающей запятой при сохранении суммарной разрядности сохраняемого в памяти кода верхней и нижней границ интервала. Технический результат достигается за счет совместного кодирования запоминаемых в памяти значений верхней и нижней границ интервала результата вычислений и декодирования считываемых из памяти кодов, представляющих собой совместно закодированные границы арифметических интервалов. При этом для задания мантиссы чисел, не подвергавшихся округлению, используется 42 разряда (в прототипе всего 23 разряда). Повышенная точность границ интервала обеспечивается до тех пор, пока одна из границ не превысит по абсолютному значению другую границу в 32 раза. Таким образом, всегда, когда результаты вычислений можно еще считать достоверными, предлагаемое устройство обеспечивает повышенную точность оценивания результатов вычислений.

Технический результат достигается тем, что предлагаемое устройство декодирования совместно хранимых границ при интервальных вычислениях содержит шифратор и блок дешифраторов, в состав которого входит первый и второй дешифраторы, вход разрешения первого дешифратора подключен к первому разряду, а информационный вход - ко второму и третьему разрядам шестидесятичетырехразрядного входа устройства, первый выход первого дешифратора подключен к входу разрешения второго дешифратора, а второй выход подключен к сорок четвертому разряду входа шифратора, информационный вход второго дешифратора подключен к четвертому разряду входа устройства, а выходы подключены к сорок третьему и сорок первому разрядам входа шифратора; третий дешифратор, вход разрешения которого подключен к третьему выходу первого дешифратора, информационный вход подключен к четвертому и пятому разрядам входа устройства, а первый и второй выходы подключены к сорок второму и сороковому разрядам входа шифратора; четвертый дешифратор, вход разрешения которого подключен к третьему выходу третьего дешифратора, информационный вход подключен к шестому и седьмому разрядам входа устройства, а выходы подключены к тридцать восьмому, тридцать шестому, тридцать четвертому и тридцать второму разрядам входа шифратора; пятый дешифратор, вход разрешения которого подключен к четвертому выходу третьего дешифратора, информационный вход подключен к шестому и седьмому разрядам входа устройства, а выходы с первого по третий подключены к тридцатому, двадцать восьмому, двадцать шестому и двадцать четвертому разрядам входа шифратора; шестой дешифратор, вход разрешения которого подключен к четвертому выходу пятого дешифратора, информационный вход подключен к восьмому и девятому разрядам входа устройства, а выходы с первого по третий подключены к двадцать четвертому, двадцать второму и двадцатому разрядам входа шифратора; седьмой дешифратор, вход разрешения которого подключен к четвертому выходу шестого дешифратора, информационный вход подключен к десятому и одиннадцатому разрядам входа устройства, а первый и второй выходы подключены к восемнадцатому и шестнадцатому разрядам входа шифратора; восьмой дешифратор, вход разрешения которого подключен к третьему выходу седьмого дешифратора, информационный вход подключен к двенадцатому и тринадцатому разрядам входа устройства, а выходы подключены к четырнадцатому, двенадцатому, десятому и восьмому разрядам входа шифратора; девятый дешифратор, вход разрешения которого подключен к четвертому выходу седьмого дешифратора, информационный вход подключен к двенадцатому и тринадцатому разрядам входа устройства, а выходы подключены к шестому, четвертому, второму и первому разрядам входа шифратора; десятый дешифратор, вход разрешения которого подключен к четвертому выходу первого дешифратора, информационный вход подключен к четвертому, пятому и шестому разрядам входа устройства, а семь младших выходов подключены к тридцать девятому, тридцать седьмому, тридцать пятому, тридцать третьему, тридцать первому, двадцать девятому и двадцать седьмому разрядам входа шифратора; одиннадцатый дешифратор, вход разрешения которого подключен к восьмому выходу десятого дешифратора, информационный вход подключен к седьмому и восьмому разрядам входа устройства, а три младших выхода подключены к двадцать пятому, двадцать третьему и двадцать первому разрядам входа шифратора; двенадцатый дешифратор, вход разрешения которого подключен к четвертому выходу одиннадцатого дешифратора, информационный вход подключен к девятому и десятому разрядам входа устройства, а первый и второй выходы подключены к девятнадцатому и семнадцатому разрядам входа шифратора; тринадцатый дешифратор, вход разрешения которого подключен к третьему выходу двенадцатого дешифратора, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа устройства, а выходы подключены к пятнадцатому, тринадцатому, одиннадцатому и девятому разрядам входа шифратора; четырнадцатый дешифратор, вход разрешения которого подключен к четвертому выходу двенадцатого дешифратора, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа устройства, первый, второй и третий выходы подключены к седьмому, пятому и третьему разрядам входа шифратора, а четвертый выход является первым выходом устройства; сорок пятый разряд входа шифратора подключен к выходу инвертора, вход которого подключен к первому разряду входа устройства, выход шифратора подключен к адресным входам первого и второго ПЗУ, выход второго ПЗУ подключен к пятиразрядному управляющему входу первого сдвигателя, двадцатипятиразрядный информационный вход которого подключен к выходам первой группы элементов «И», первые входы которых подключены к выходу первого ПЗУ, а вторые входы подключены к разрядам с пятого по двадцать девятый информационного входа устройства, сорокаодноразрядный выход первого сдвигателя подключен к первым входам группы элементов «ИЛИ», подключение вторых входов которых соответствует подключению сорока одного младших разрядов входа шифратора, младшие разряды второго входа вычитателя подключены к выходам группы элементов «ИЛИ», а подключение старшего разряда соответствует подключению сорок второго разряда входа шифратора; шестнадцать младших разрядов первого входа первого вычитателя подключены к выходам второй группы элементов «И», входы которых подключены к разрядам, с четырнадцатого по двадцать девятый, информационного входа устройства, а инверсные входы подключены к шестнадцати младшим разрядам выхода первого ПЗУ, старшие разряды первого входа первого вычитателя подключены к разрядам, с тридцатого по шестьдесят третий, информационного входа устройства, подключение пятидесяти разрядов второго выхода устройства соответствует подключению разрядов первого входа первого вычитателя, к которым, в качестве старшего разряда, добавлен старший разряд входа устройства; информационный вход второго сдвигателя подключен к сорока двум младшим разрядам выхода первого вычитателя, управляющий вход второго сдвигателя подключен к выходу первого элемента суммирования по модулю, два входа которого подключены к пятьдесят шестому разряду входа устройства и сорок третьему разряду выхода первого вычитателя, а сорокадвухразрядный выход второго сдвигателя соединен с первым входом первого мультиплексора, шестнадцать младших разрядов второго входа первого мультиплексора обнулены, старшие разряды упомянутого входа подключены к разрядам, с пятнадцатого по двадцать девятый, входа устройства, остальные одиннадцать разрядов упомянутого входа подключены к выходам третьей группы элементов «И», первые входы которых подключены к разрядам, с четвертого по четырнадцатый, входа устройства, младший разряд второго входа третьей группы элементов «И» подключен к младшему разряду входа устройства, следующие два разряда упомянутого входа подключены к выходу первого элемента «ИЛИ», старшие восемь разрядов упомянутого входа подключены к выходу второго элемента «ИЛИ», входы первого элемента «ИЛИ» подключены к первому, третьему и четвертому разрядам входа устройства; входы второго элемента «ИЛИ» подключены к выходу первого элемента «ИЛИ», а также к пятому и шестому разрядам входа устройства, к выходу первого элемента «ИЛИ» также подключены управляющий вход второго мультиплексора и вход обнуления выхода третьего мультиплексора, а к выходу второго элемента «ИЛИ» подключены управляющие входы третьего и четвертого мультиплексоров; первый информационный вход второго мультиплексора подключен к пятому и шестому разрядам входа устройства, а второй информационный вход второго мультиплексора подключен к третьему и четвертому разрядам входа устройства; на первый и второй информационные входы третьего мультиплексора поданы константные значения «шесть» и «три», соответственно, первый информационный вход четвертого мультиплексора подключен к разрядам с седьмого по четырнадцатый входа устройства, младшие два разряда второго информационного входа четвертого мультиплексора подключены к выходу второго мультиплексора, а старшие разряды упомянутого входа обнулены; первый вход сумматора подключен к выходу четвертого мультиплексора, второй вход сумматора подключен к выходу третьего мультиплексора, а выход сумматора соединен с входом вычитаемого второго вычитателя; первый информационный вход пятого мультиплексора, как и вход уменьшаемого второго вычитателя, подключен к разрядам с пятьдесят шестого по шестьдесят третий входа устройства, второй информационный вход пятого мультиплексора подключен к выходу второго вычитателя, а управляющий вход пятого мультиплексора подключен к выходу инвертора; первый информационный вход шестого мультиплексора подключен к разрядам, с сорок третьего по пятидесятый, выхода первого вычитателя, второй информационный вход подключен к выходу пятого мультиплексора, управляющие входы первого и шестого мультиплексоров подключены к выходу третьего элемента «ИЛИ», один из входов которого подключен к выходу инвертора, а подключение второго соответствует подключению сорок третьего разряда входа шифратора, младшие разряды третьего выхода устройства подключены к сорока двум младшим разрядам выхода первого мультиплексора, старший разряд третьего выхода устройства подключен к выходу второго элемента суммирования по модулю два, остальные восемь разрядов упомянутого выхода подключены к выходу шестого мультиплексора; один из входов второго элемента суммирования по модулю два подключен к старшему разряду входа устройства, а другой - к выходу элемента «И», один из входов которого подключен к выходу третьего элемента «ИЛИ», а другой - ко второму разряду входа устройства.

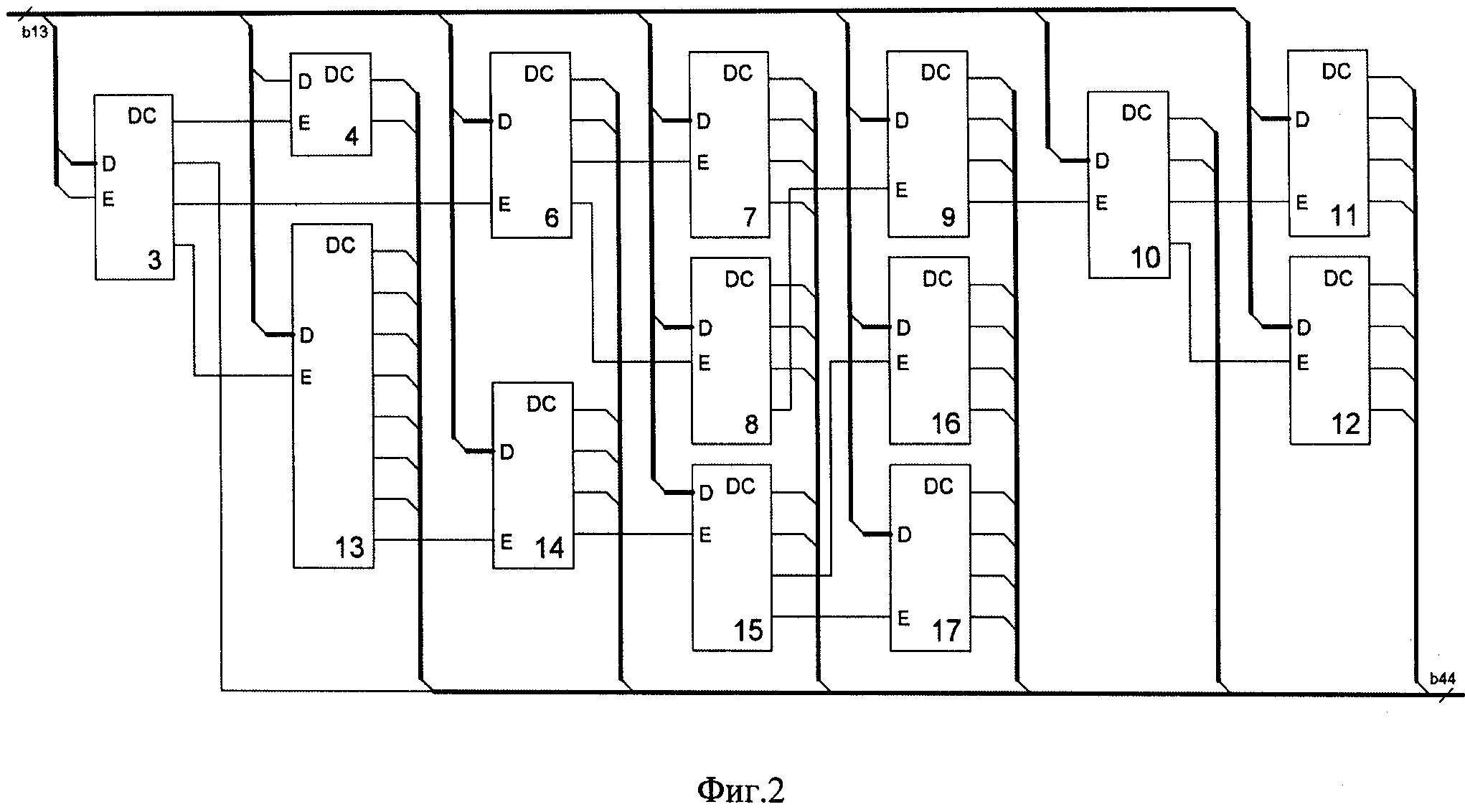

На фиг.1 приведена общая схема предлагаемого устройства декодирования совместно хранимых границ при интервальных вычислениях.

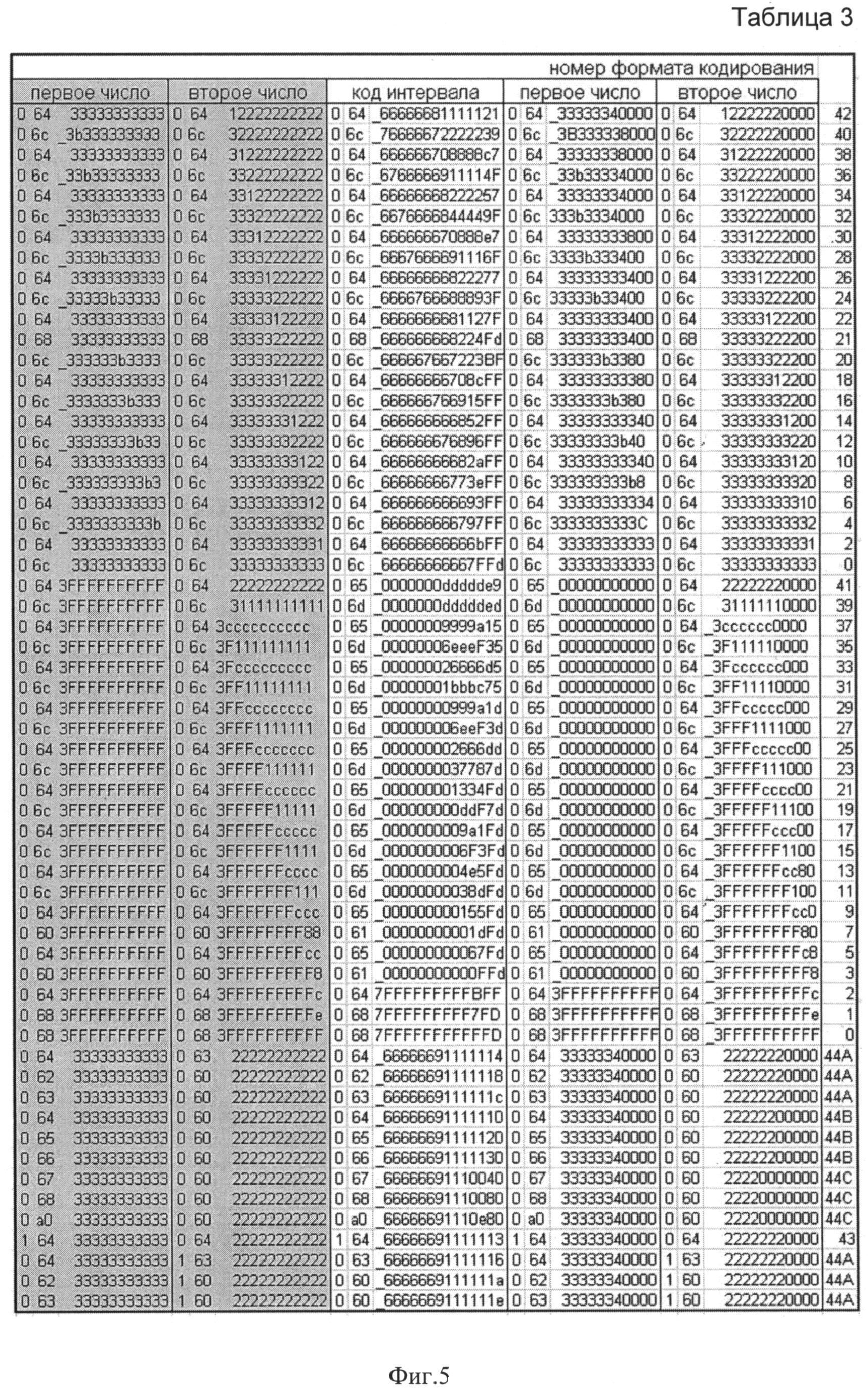

На фиг.2 раскрыта функциональная схема блока дешифраторов.

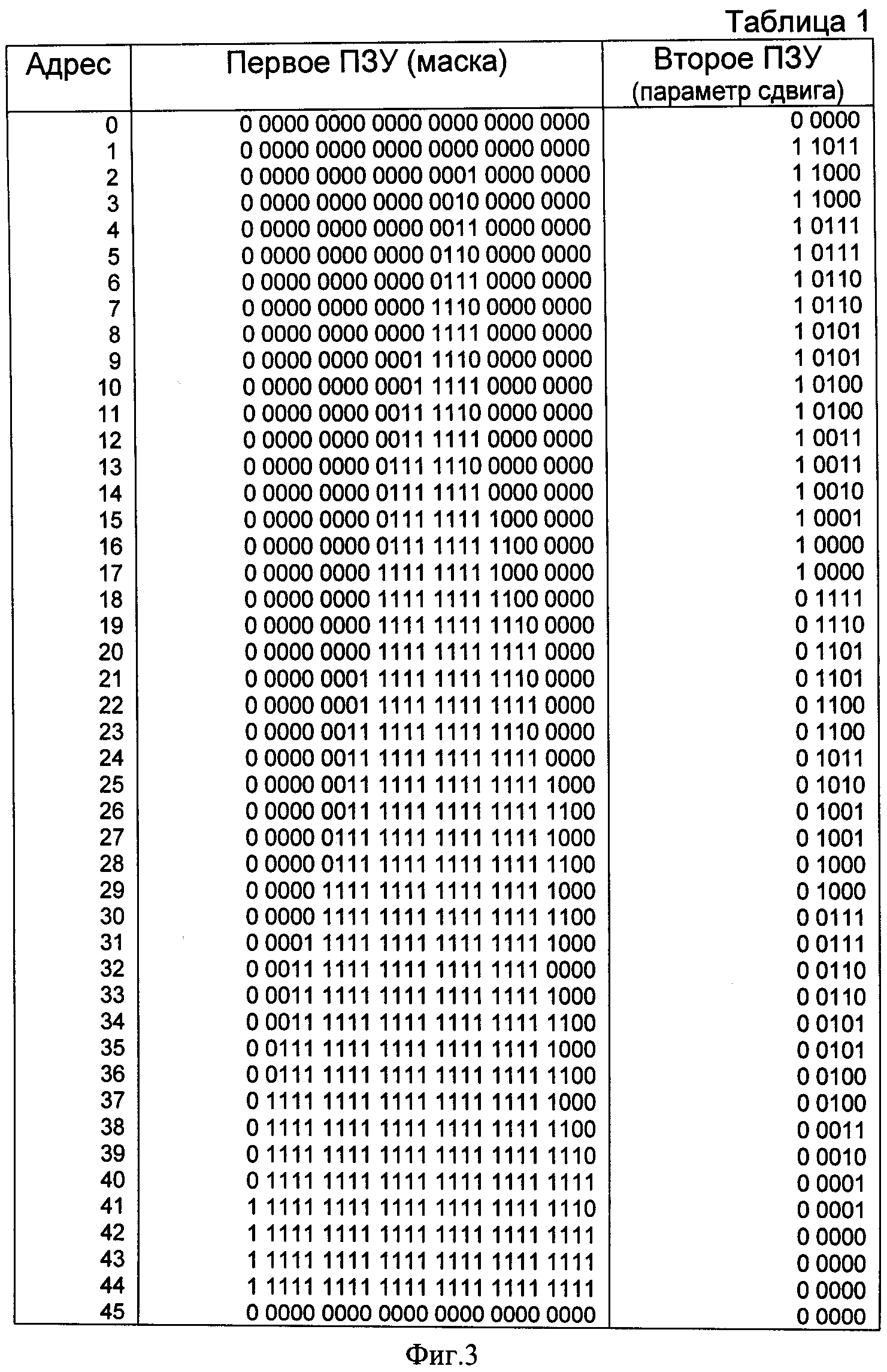

На фиг.3 представлена таблица, отражающая содержимое блоков ПЗУ предлагаемого устройства.

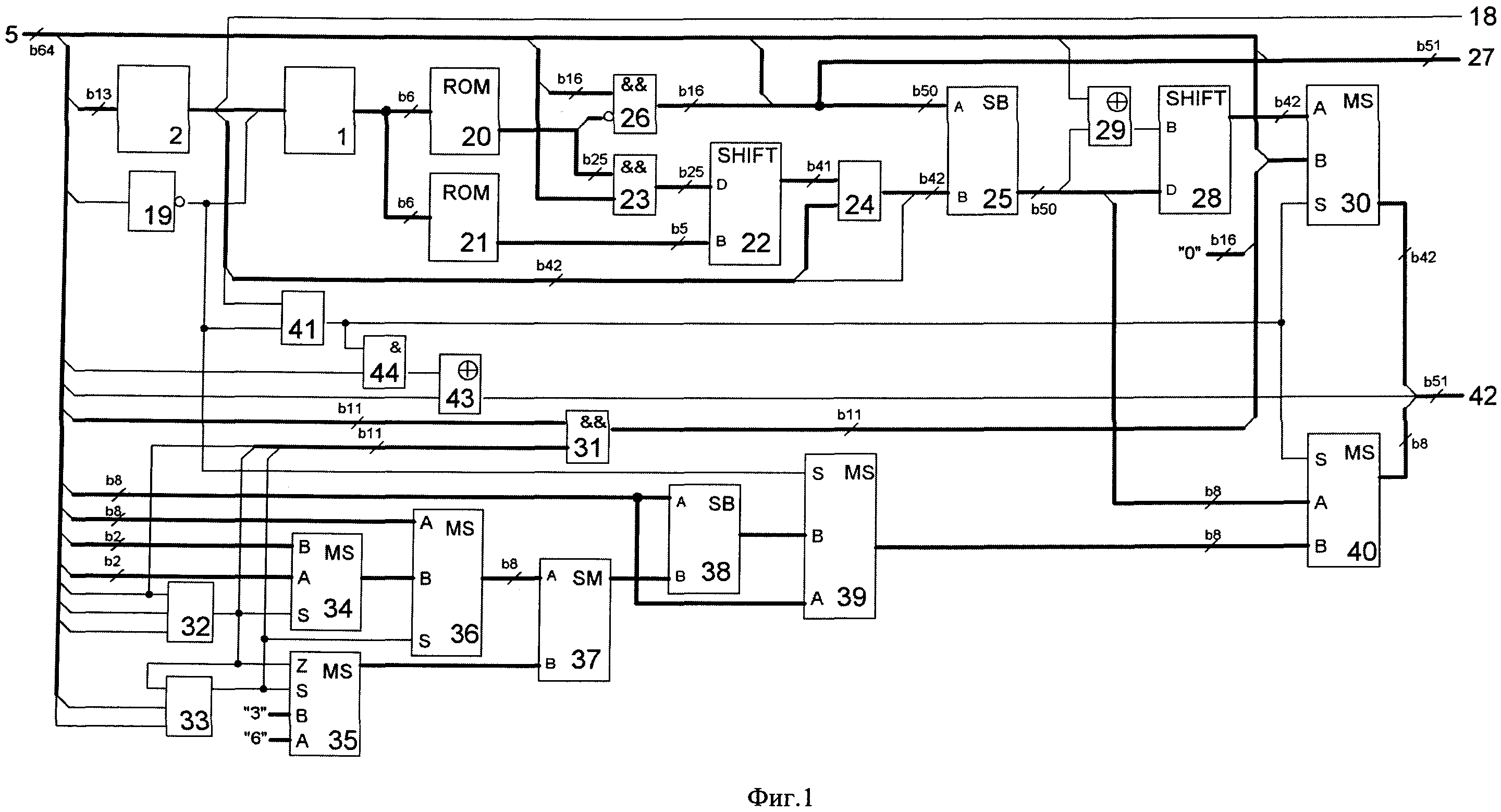

На фиг.4 приведена таблица, иллюстрирующая форматы кодов, подлежащих декодированию.

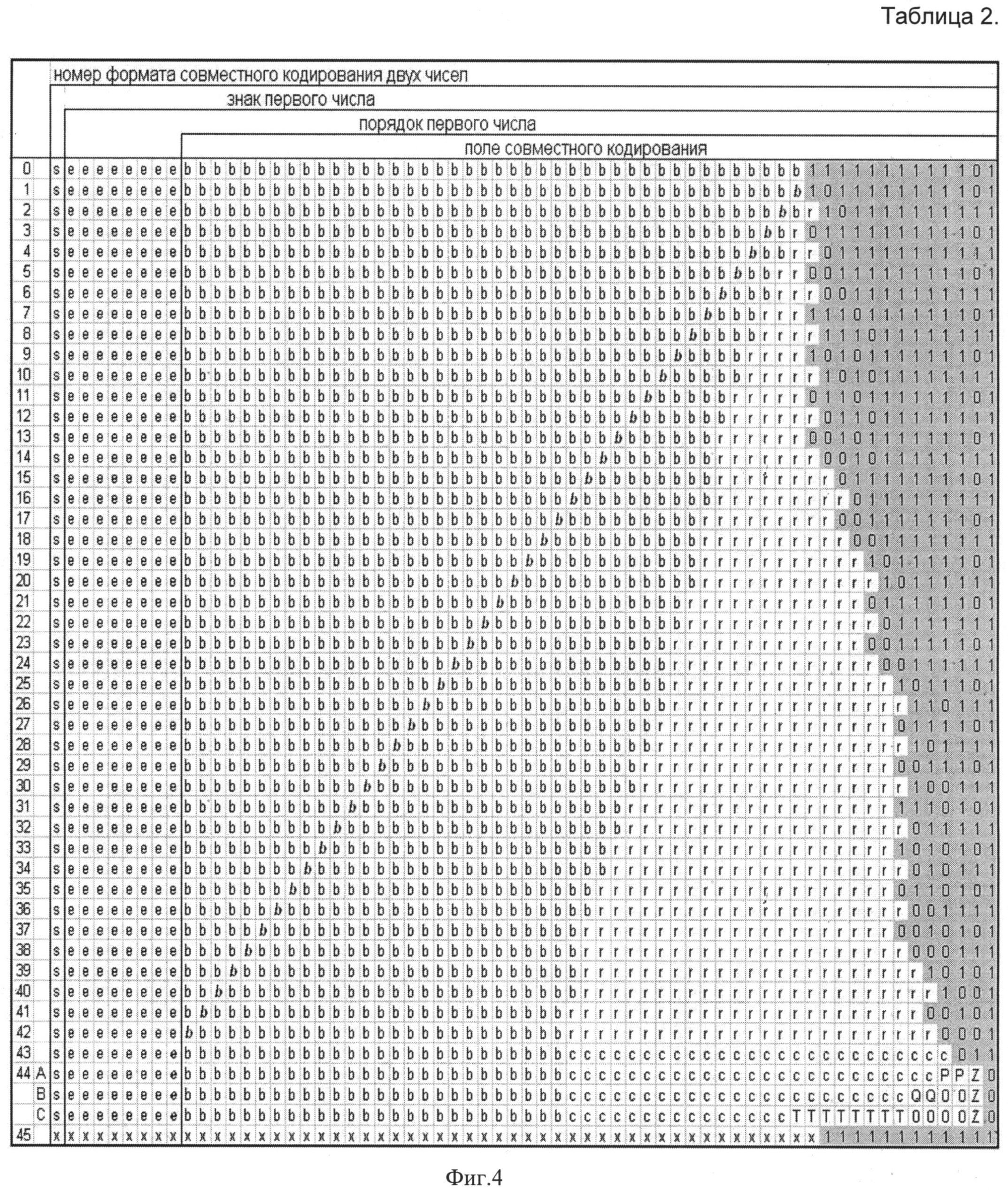

На фиг.5 приведена таблица, содержащая примеры декодирования шестидесятичетырехразрядных кодов.

На фиг.1 и фиг.2 справочно приведены разрядности шин, соединяющих элементы и блоки устройства. Например, надпись /b12 означает, что шина имеет двенадцать разрядов.

Предлагаемое устройство декодирования совместно хранимых границ при интервальных вычислениях содержит шифратор 1 и блок дешифраторов 2, в состав которого входит первый 3 и второй 4 дешифраторы, вход разрешения первого дешифратора 3 подключен к первому разряду, а информационный вход - ко второму и третьему разрядам шестидесятичетырехразрядного входа 5 устройства, первый выход первого дешифратора подключен к входу разрешения второго дешифратора 4, а второй выход подключен к сорок четвертому разряду входа шифратора 1, информационный вход второго дешифратора 4 подключен к четвертому разряду входа 5 устройства, а выходы подключены к сорок третьему и сорок первому разрядам входа шифратора 1; третий дешифратор 6, вход разрешения которого подключен к третьему выходу первого дешифратора 3, информационный вход подключен четвертому и пятому разрядам входа 5 устройства, а первый и второй выходы подключены к сорок второму и сороковому разрядам входа шифратора 1; четвертый дешифратор 7, вход разрешения которого подключен к третьему выходу третьего дешифратора 6, информационный вход подключен к шестому и седьмому разрядам входа 5 устройства, а выходы подключены к тридцать восьмому, тридцать шестому, тридцать четвертому и тридцать второму разрядам входа шифратора 1; пятый дешифратор 8, вход разрешения которого подключен к четвертому выходу третьего дешифратора 6, информационный вход подключен к шестому и седьмому разрядам входа 5 устройства, а выходы с первого по третий подключены к тридцатому, двадцать восьмому, двадцать шестому и двадцать четвертому разрядам входа шифратора 1; шестой дешифратор 9, вход разрешения которого подключен к четвертому выходу пятого дешифратора 8, информационный вход подключен к восьмому и девятому разрядам входа 5 устройства, а выходы с первого по третий подключены к двадцать четвертому, двадцать второму и двадцатому разрядам входа шифратора 1; седьмой дешифратор 10, вход разрешения которого подключен к четвертому выходу шестого дешифратора 9, информационный вход подключен к десятому и одиннадцатому разрядам входа 5 устройства, а первый и второй выходы подключены к восемнадцатому и шестнадцатому разрядам входа шифратора 1; восьмой дешифратор 11, вход разрешения которого подключен к третьему выходу седьмого дешифратора 10, информационный вход подключен к двенадцатому и тринадцатому разрядам входа 5 устройства, а выходы подключены к четырнадцатому, двенадцатому, десятому и восьмому разрядам входа шифратора 1; девятый дешифратор 12, вход разрешения которого подключен к четвертому выходу седьмого дешифратора 10, информационный вход подключен к двенадцатому и тринадцатому разрядам входа 5 устройства, а выходы подключены к шестому, четвертому, второму и первому разрядам входа шифратора 1; десятый дешифратор 13, вход разрешения которого подключен к четвертому выходу первого дешифратора 3, информационный вход подключен к четвертому, пятому и шестому разрядам входа 5 устройства, а семь младших выходов подключены к тридцать девятому, тридцать седьмому, тридцать пятому, тридцать третьему, тридцать первому, двадцать девятому и двадцать седьмому разрядам входа шифратора 1; одиннадцатый дешифратор 14, вход разрешения которого подключен к восьмому выходу десятого дешифратора 13, информационный вход подключен к седьмому и восьмому разрядам входа 5 устройства, а три младших выхода подключены к двадцать пятому, двадцать третьему и двадцать первому разрядам входа шифратора 1; двенадцатый дешифратор 15, вход разрешения которого подключен к четвертому выходу одиннадцатого дешифратора 14, информационный вход подключен к девятому и десятому разрядам входа 5 устройства, а первый и второй выходы подключены к девятнадцатому и семнадцатому разрядам входа шифратора 1; тринадцатый дешифратор 16, вход разрешения которого подключен к третьему выходу двенадцатого дешифратора 15, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа 5 устройства, а выходы подключены к пятнадцатому, тринадцатому, одиннадцатому и девятому разрядам входа шифратора 1; четырнадцатый дешифратор 17, вход разрешения которого подключен к четвертому выходу двенадцатого дешифратора 15, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа 5 устройства, первый, второй и третий выходы подключены к седьмому, пятому и третьему разрядам входа шифратора 1, а четвертый выход является первым выходом 18 устройства; сорок пятый разряд входа шифратора 1 подключен к выходу инвертора 19, вход которого подключен к первому разряду входа устройства 5, выход шифратора подключен к адресным входам первого 20 и второго 21 ПЗУ, выход второго 21 ПЗУ подключен к пятиразрядному управляющему входу первого сдвигателя 22, двадцатипятиразрядный информационный вход которого подключен к выходам первой группы элементов «И» 23, первые входы которых подключены к выходу первого 20 ПЗУ, а вторые входы подключены к разрядам с пятого по двадцать девятый информационного входа 5 устройства, сорокаодноразрядный выход первого сдвигателя 22 подключен к первым входам группы элементов «ИЛИ» 24, подключение вторых входов которых соответствует подключению сорока одного младших разрядов входа шифратора 1, младшие разряды второго входа вычитателя 25 подключены к выходам группы элементов «ИЛИ», а подключение старшего разряда соответствует подключению сорок второго разряда входа шифратора 1; шестнадцать младших разрядов первого входа первого вычитателя 25 подключены к выходам второй группы элементов «И» 26, входы которых подключены к разрядам, с четырнадцатого по двадцать девятый, информационного входа устройства 5, а инверсные входы подключены к шестнадцати младшим разрядам выхода первого ПЗУ 20, старшие разряды первого входа первого вычитателя 25 подключены к разрядам, с тридцатого по шестьдесят третий, информационного входа 5 устройства, подключение пятидесяти разрядов второго выхода 27 устройства соответствует подключению разрядов первого входа первого вычитателя 25, к которым, в качестве старшего разряда, добавлен старший разряд входа 5 устройства; информационный вход второго сдвигателя 28 подключен к сорока двум младшим разрядам выхода первого вычитателя 25, управляющий вход второго сдвигателя 28 подключен к выходу первого элемента суммирования по модулю два 29, входы которого подключены к пятьдесят шестому разряду входа 5 устройства и сорок третьему разряду выхода первого вычитателя 25, а сорокадвухразрядный выход второго сдвигателя 28 соединен с первым входом первого мультиплексора 30, шестнадцать младших разрядов второго входа первого мультиплексора обнулены, старшие разряды упомянутого входа подключены к разрядам, с пятнадцатого по двадцать девятый, входа устройства 5, остальные одиннадцать разрядов упомянутого входа подключены к выходам третьей группы элементов «И» 31, первые входы которых подключены к разрядам, с четвертого по четырнадцатый, входа 5 устройства, младший разряд второго входа третьей группы элементов «И» 31 подключен к младшему разряду входа 5 устройства, следующие два разряда упомянутого входа подключены к выходу первого элемента «ИЛИ» 32, старшие восемь разрядов упомянутого входа подключены к выходу второго элемента «ИЛИ» 33, входы первого элемента «ИЛИ» 32 подключены к первому, третьему и четвертому разрядам входа 5 устройства; входы второго элемента «ИЛИ» 33 подключены к выходу первого элемента «ИЛИ» 32, а также к пятому и шестому разрядам входа 5 устройства, к выходу первого элемента «ИЛИ» 32 также подключены управляющий вход второго мультиплексора 34 и вход обнуления выхода третьего мультиплексора 35, а к выходу второго элемента «ИЛИ» 33 подключены управляющие входы третьего 35 и четвертого 36 мультиплексоров; первый информационный вход второго мультиплексора 34 подключен к пятому и шестому разрядам входа 5 устройства, а второй информационный вход второго мультиплексора 34 подключен к третьему и четвертому разрядам входа 5 устройства; на первый и второй информационные входы третьего мультиплексора 35 поданы константные значения «шесть» и «три», соответственно, первый информационный вход четвертого мультиплексора 36 подключен к разрядам с седьмого по четырнадцатый входа 5 устройства, младшие два разряда второго информационного входа четвертого мультиплексора 36 подключены к выходу второго мультиплексора 34, а старшие разряды упомянутого входа обнулены; первый вход сумматора 37 подключен к выходу четвертого мультиплексора 36, второй вход сумматора 37 подключен к выходу третьего мультиплексора 35, а выход сумматора 37 соединен с входом вычитаемого второго вычитателя 38; первый информационный вход пятого мультиплексора 39, как и вход уменьшаемого второго вычитателя 38, подключен к разрядам с пятьдесят шестого по шестьдесят третий входа 5 устройства, второй информационный вход пятого мультиплексора 39 подключен к выходу второго вычитателя 38, а управляющий вход пятого мультиплексора 39 подключен к выходу инвертора 19; первый информационный вход шестого мультиплексора 40 подключен к разрядам, с сорок третьего по пятидесятый, выхода первого вычитателя 25, второй информационный вход подключен к выходу пятого мультиплексора 39, управляющие входы первого 30 и шестого 40 мультиплексоров подключены к выходу третьего элемента «ИЛИ» 41, один из входов которого подключен к выходу инвертора 19, а подключение второго соответствует подключению сорок третьего разряда входа шифратора 1, младшие разряды третьего выхода 42 устройства подключены к сорока двум младшим разрядам выхода первого мультиплексора; старший разряд третьего выхода 45 устройства подключен к выходу второго элемента суммирования по модулю два 43, остальные восемь разрядов упомянутого выхода подключены к выходу шестого мультиплексора 40; один из входов второго элемента суммирования по модулю два 43 подключен к старшему разряду входа 5 устройства, а другой - к выходу элемента «И» 44, один из входов которого подключен к выходу третьего элемента «ИЛИ» 41, а другой ко второму разряду входа 5 устройства.

При работе устройства на его вход 5 подается 64-разрядный код. Устройство определяет, является ли поступивший код арифметическим интервалом. Если код не является интервалом, на первом выходе 18 устройства выставляется сигнал активного уровня. Это имеет место, если все 12 младших разрядов кода содержат единицы. Если код является арифметическим интервалом, устройство осуществляет его декодирование и формируют 51-разрядные первое и второе числа на втором 27 и третьем 42 выходах. Как первое, так и второе число имеют знак, восьмиразрядный порядок и сорокадвухразрядную мантиссу.

Первое число на втором выходе 27 устройства по абсолютной величине всегда не меньше второго числа на третьем выходе 42. Если первое число положительное, оно является верхней границей арифметического интервала. Если первое число отрицательное, оно является нижней границей интервала. Блок устройства 2 дешифрирует формат записи кода интервала, а шифратор 1 формирует адрес обращения к ПЗУ, являющийся одновременно номером формата кодирования арифметического интервала. Формат определяется младшими битами кода, которые в таблице 2 затенены. Используемые форматы проиллюстрированы таблицей 2 на фиг.4, каждому формату соответствует строка таблицы, исключением является формат «44», который представлен тремя строками.

Старший разряд кода интервала s соответствует знаку первого числа. Порядок этого числа определяется восемью битами и в таблице 2 обозначен как «ееееееее». Для кодирования мантиссы первого числа, в зависимости от формата, используется от сорока двух до двадцати шести бит, обозначенных буквой b.

Для выделения из кода интервала мантиссы первого числа достаточно обнулить биты, не обозначенные буквой b. Эта операция маскирования осуществляется второй группой элементов «И» 26 с использованием кода маски, записанного в первом ПЗУ 20. Содержимое ПЗУ проиллюстрировано таблицей 2 на фиг.3.

Если код интервала соответствует формату, имеющему номер «0», первое и второе число равны.

Если код интервала соответствует формату, имеющему номер от «1» до «42», первое и второе число имеют одинаковые знаки и порядок первого числа не может отличаться от порядка второго числа больше чем на единицу.

Если код интервала соответствует формату номер «43», первое и второе число имеют разные знаки, но одинаковые порядки.

Если код интервала соответствует формату номер «44», первое и второе число имеют, либо разные знаки, либо разные порядки.

При декодировании по форматам «1-42» для формирования мантиссы второго числа в первом вычитателе 25 выполняется вычитание из кода первого числа, числа сформированного при помощи первой группы элементов «И» 23 и первого сдвигателя 22 из разрядов обозначенных буквой г с добавлением, при помощи группы элементов «ИЛИ» 24, подразумеваемой единицы, сформированной блоком дешифраторов 2. Первый сдвигатель 22 управляется кодом, выбираемым из блока 21 ПЗУ.

В случае, если порядок числа на выходе первого вычитателя 25 меньше порядка первого числа, нормализация мантиссы второго числа осуществляется при помощи второго сдвигателя 28, управляемого первым элементом суммирования по модулю два 29.

При декодировании по форматам «43» и «44» мантисса второго числа формируется из разрядов кода интервала, обозначенных через с, при участии первого 32 и второго 33 элементов «ИЛИ». При этом порядок второго числа формируется при участии сумматора 37, второго вычитателя 38, второго 34, третьего 35, четвертого 36 и пятого 39 мультиплексоров.

Окончательное формирование второго числа осуществляется первым 30 и шестым 40 мультиплексорами, управляемыми третьим элементом «ИЛИ» 41, а также элементом «И» 44 и вторым элементом суммирования по модулю два, определяющими знак второго числа. Если при декодировании по формату «44» второй разряд входа устройства равен единице, то знак второго числа будет противоположен знаку первого числа. В противном случае знаки первого и второго чисел равны.

Формат «44А» подразумевает, что разность порядков первого и второго чисел равна 1, 2 или 3. Эта разность кодируется битами, обозначенными как PP. Формат «44В» подразумевает разность порядков первого и второго чисел от 4 до 6. Эта разность кодируется битами, обозначенными как QQ, с добавлением подразумеваемого числа 3. Формат «44С» применяется при разности порядков первого и второго чисел более 6. Эта разность кодируется восемью битами, обозначенными как ТТТТТТТТ, с добавлением подразумеваемого числа 6.

Заметим, что при кодировании по формату «44» количество значащих разрядов мантиссы первого числа равно двадцати шести. В формате «44А» разрядность мантиссы второго числа равна двадцати пяти, при двадцати трех разрядах в противопоставляемых устройствах. В форматах «44В» и «44С» разрядность мантиссы второго числа составляет 23 и 15 соответственно. Следовательно, только при кодировании по формату «44С» точность представления арифметических интервалов, по числу значащих разрядов, может оказаться меньше, чем в противопоставляемых устройствах.

В таблице 3, на фиг.5, приведены примеры работы устройства. В затененной области таблицы 3 представлены подразумеваемые исходные значения первого и второго чисел, подвергнутых кодированию. Кодированный шестидесятичетырехразрядный арифметический интервал имеет знак, совпадающий со знаком первого числа, восьмиразрядный порядок, совпадающий с порядком округленного первого числа, и пятидесятипятиразрядный совместный код. Порядок и совместный код записаны в шестнадцатеричной системе. Декодированные первое и второе числа представлены знаком, восьмибитным порядком и сорокадвухразрядной мантиссой. Порядок и мантисса записаны в шестнадцатеричной системе.

Устройство декодирования совместно хранимых границ при интервальных вычислениях, характеризующееся тем, что содержит шифратор и блок дешифраторов, в состав которого входит первый и второй дешифраторы, вход разрешения первого дешифратора подключен к первому разряду, а информационный вход - ко второму и третьему разрядам шестидесятичетырехразрядного входа устройства, первый выход первого дешифратора подключен к входу разрешения второго дешифратора, а второй выход подключен к сорок четвертому разряду входа шифратора, информационный вход второго дешифратора подключен к четвертому разряду входа устройства, а выходы подключены к сорок третьему и сорок первому разрядам входа шифратора; третий дешифратор, вход разрешения которого подключен к третьему выходу первого дешифратора, информационный вход подключен к четвертому и пятому разрядам входа устройства, а первый и второй выходы подключены к сорок второму и сороковому разрядам входа шифратора; четвертый дешифратор, вход разрешения которого подключен к третьему выходу третьего дешифратора, информационный вход подключен к шестому и седьмому разрядам входа устройства, а выходы подключены к тридцать восьмому, тридцать шестому, тридцать четвертому и тридцать второму разрядам входа шифратора; пятый дешифратор, вход разрешения которого подключен к четвертому выходу третьего дешифратора, информационный вход подключен к шестому и седьмому разрядам входа устройства, а выходы с первого по третий подключены к тридцатому, двадцать восьмому, двадцать шестому и двадцать четвертому разрядам входа шифратора; шестой дешифратор, вход разрешения которого подключен к четвертому выходу пятого дешифратора, информационный вход подключен к восьмому и девятому разрядам входа устройства, а выходы с первого по третий подключены к двадцать четвертому, двадцать второму и двадцатому разрядам входа шифратора; седьмой дешифратор, вход разрешения которого подключен к четвертому выходу шестого дешифратора, информационный вход подключен к десятому и одиннадцатому разрядам входа устройства, а первый и второй выходы подключены к восемнадцатому и шестнадцатому разрядам входа шифратора; восьмой дешифратор, вход разрешения которого подключен к третьему выходу седьмого дешифратора, информационный вход подключен к двенадцатому и тринадцатому разрядам входа устройства, а выходы подключены к четырнадцатому, двенадцатому, десятому и восьмому разрядам входа шифратора; девятый дешифратор, вход разрешения которого подключен к четвертому выходу седьмого дешифратора, информационный вход подключен к двенадцатому и тринадцатому разрядам входа устройства, а выходы подключены к шестому, четвертому, второму и первому разрядам входа шифратора; десятый дешифратор, вход разрешения которого подключен к четвертому выходу первого дешифратора, информационный вход подключен к четвертому, пятому и шестому разрядам входа устройства, а семь младших выходов подключены к тридцать девятому, тридцать седьмому, тридцать пятому, тридцать третьему, тридцать первому, двадцать девятому и двадцать седьмому разрядам входа шифратора; одиннадцатый дешифратор вход, разрешения которого подключен к восьмому выходу десятого дешифратора, информационный вход подключен к седьмому и восьмому разрядам входа устройства, а три младших выхода подключены к двадцать пятому, двадцать третьему и двадцать первому разрядам входа шифратора; двенадцатый дешифратор, вход разрешения которого подключен к четвертому выходу одиннадцатого дешифратора, информационный вход подключен к девятому и десятому разрядам входа устройства, а первый и второй выходы подключены к девятнадцатому и семнадцатому разрядам входа шифратора; тринадцатый дешифратор, вход разрешения которого подключен к третьему выходу двенадцатого дешифратора, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа устройства, а выходы подключены к пятнадцатому, тринадцатому, одиннадцатому и девятому разрядам входа шифратора; четырнадцатый дешифратор, вход разрешения которого подключен к четвертому выходу двенадцатого дешифратора, информационный вход подключен к одиннадцатому и двенадцатому разрядам входа устройства, первый, второй и третий выходы подключены к седьмому, пятому и третьему разрядам входа шифратора, а четвертый выход является первым выходом устройства; сорок пятый разряд входа шифратора подключен к выходу инвертора, вход которого подключен к первому разряду входа устройства, выход шифратора подключен к адресным входам первого и второго ПЗУ, выход второго ПЗУ подключен к пятиразрядному управляющему входу первого сдвигателя, двадцатипятиразрядный информационный вход которого подключен к выходам первой группы элементов «И», первые входы которых подключены к выходу первого ПЗУ, а вторые входы подключены к разрядам с пятого по двадцать девятый информационного входа устройства, сорокаодноразрядный выход первого сдвигателя подключен к первым входам группы элементов «ИЛИ», подключение вторых входов которых соответствует подключению сорока одного младших разрядов входа шифратора, младшие разряды второго входа вычитателя подключены к выходам группы элементов «ИЛИ», а подключение старшего разряда соответствует подключению сорок второго разряда входа шифратора; шестнадцать младших разрядов первого входа первого вычитателя подключены к выходам второй группы элементов «И», входы которых подключены к разрядам, с четырнадцатого по двадцать девятый, информационного входа устройства, а инверсные входы подключены к шестнадцати младшим разрядам выхода первого ПЗУ, старшие разряды первого входа первого вычитателя подключены к разрядам, с тридцатого по шестьдесят третий, информационного входа устройства, подключение пятидесяти разрядов второго выхода устройства соответствует подключению разрядов первого входа первого вычитателя, к которым, в качестве старшего разряда, добавлен старший разряд входа устройства; информационный вход второго сдвигателя подключен к сорока двум младшим разрядам выхода первого вычитателя, управляющий вход второго сдвигателя подключен к выходу первого элемента суммирования по модулю, два входа которого подключены к пятьдесят шестому разряду входа устройства и сорок третьему разряду выхода первого вычитателя, а сорокадвухразрядный выход второго сдвигателя соединен с первым входом первого мультиплексора, шестнадцать младших разрядов второго входа первого мультиплексора обнулены, старшие разряды упомянутого входа подключены к разрядам, с пятнадцатого по двадцать девятый, входа устройства, остальные одиннадцать разрядов упомянутого входа подключены к выходам третьей группы элементов «И», первые входы которых подключены к разрядам, с четвертого по четырнадцатый, входа устройства, младший разряд второго входа третьей группы элементов «И» подключен к младшему разряду входа устройства, следующие два разряда упомянутого входа подключены к выходу первого элемента «ИЛИ», старшие восемь разрядов упомянутого входа подключены к выходу второго элемента «ИЛИ», входы первого элемента «ИЛИ» подключены к первому, третьему и четвертому разрядам входа устройства; входы второго элемента «ИЛИ» подключены к выходу первого элемента «ИЛИ», а также к пятому и шестому разрядам входа устройства, к выходу первого элемента «ИЛИ» также подключены управляющий вход второго мультиплексора и вход обнуления выхода третьего мультиплексора, а к выходу второго элемента «ИЛИ» подключены управляющие входы третьего и четвертого мультиплексоров; первый информационный вход второго мультиплексора подключен к пятому и шестому разрядам входа устройства, а второй информационный вход второго мультиплексора подключен к третьему и четвертому разрядам входа устройства; на первый и второй информационные входы третьего мультиплексора поданы константные значения «шесть» и «три», соответственно, первый информационный вход четвертого мультиплексора подключен к разрядам с седьмого по четырнадцатый входа устройства, младшие два разряда второго информационного входа четвертого мультиплексора подключены к выходу второго мультиплексора, а старшие разряды упомянутого входа обнулены; первый вход сумматора подключен к выходу четвертого мультиплексора, второй вход сумматора подключен к выходу третьего мультиплексора, а выход сумматора соединен с входом вычитаемого второго вычитателя; первый информационный вход пятого мультиплексора, как и вход уменьшаемого второго вычитателя, подключен к разрядам с пятьдесят шестого по шестьдесят третий входа устройства, второй информационный вход пятого мультиплексора подключен к выходу второго вычитателя, а управляющий вход пятого мультиплексора подключен к выходу инвертора; первый информационный вход шестого мультиплексора подключен к разрядам, с сорок третьего по пятидесятый, выхода первого вычитателя, второй информационный вход подключен к выходу пятого мультиплексора, управляющие входы первого и шестого мультиплексоров подключены к выходу третьего элемента «ИЛИ», один из входов которого подключен к выходу инвертора, а подключение второго соответствует подключению сорок третьего разряда входа шифратора, младшие разряды третьего выхода устройства подключены к сорока двум младшим разрядам выхода первого мультиплексора, старший разряд третьего выхода устройства подключен к выходу второго элемента суммирования по модулю два, остальные восемь разрядов упомянутого выхода подключены к выходу шестого мультиплексора; один из входов второго элемента суммирования по модулю два подключен к старшему разряду входа устройства, а другой - к выходу элемента «И», один из входов которого подключен к выходу третьего элемента «ИЛИ», а другой - ко второму разряду входа устройства.