Результат интеллектуальной деятельности: МУЛЬТИПЛЕКСИРОВАНИЕ АДРЕСОВ В ПСЕВДО ДВУХПОРТОВОЙ ПАМЯТИ

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Данное раскрытие относится в общем случае к схемам памяти. Более конкретно, данное раскрытие относится к управлению адресом для псевдо двухпортовой памяти.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Двухпортовая память обычно имеет два порта и массив ячеек памяти. К массиву памяти можно одновременно обращаться от обоих портов при условии, что ячейки памяти, к которым обращаются от одного порта, не являются теми же самыми ячейками памяти, к которым обращаются от другого порта. Ячейки памяти обычного типа, используемые в таких двухпортовых блоках памяти, содержат восемь полевых транзисторов (FET).

Ячейки памяти в однопортовой памяти обычно включают в себя только шесть транзисторов. Ячейка памяти с шестью транзисторами обычно использует только приблизительно половину той площади интегральной схемы, которую использует ячейка с восемью транзисторами, когда два типа ячеек памяти изготавливаются, используя один и тот же процесс. Однако, многие приложения требуют функциональных возможностей двухпортовой памяти, т.е. памяти, которая может обрабатывать операции и чтения, и записи в пределах одного тактового цикла.

Для использования преимуществ меньшего размера ячейки памяти с шестью транзисторами, все еще удовлетворяя требования тех приложений, которые требуют функциональных возможностей двухпортовой памяти, часто используется устройство памяти, называемое псевдо двухпортовой памятью. В одном из примеров псевдо двухпортовая память имеет один массив памяти, в котором каждая ячейка памяти массива является ячейкой памяти с шестью транзисторами, которая может быть выборочно связана с одной парой разрядных линий (например, с разрядной линией В и разрядной линией штрих BN).

Массив памяти работает как однопортовая память, потому что единовременно выполняется только один доступ к памяти. Псевдо двухпортовая память, однако, имитирует двухпортовую память, потому что у нее есть два порта. В одном из примеров псевдо двухпортовая память имеет схему, иногда называемую мультиплексором с временной задержкой (TDM). В псевдо двухпортовой памяти принимают один входной сигнал синхронизации, и этот один входной сигнал синхронизации используется для фиксации вводимого адреса чтения, вводимого адреса записи и вводимого значения данных. Передний фронт входного сигнала синхронизации используется для инициирования операции чтения, используя вводимый адрес чтения. Операция чтения заканчивается. После этого появляется задний фронт входного сигнала синхронизации. TDM использует задний фронт входного сигнала синхронизации для инициирования операции записи. Вводимый адрес записи используется для обращения к массиву памяти во время операции записи, а данные, записываемые в массив памяти, являются входным значением данных. Хотя в одном цикле входного сигнала синхронизации выполняются две операции обращения к памяти, эти две операции обращения к памяти в действительности выполняются одна за другой. Снаружи псевдо двухпортовой памяти, однако кажется, что псевдо двухпортовая память предоставляет возможность двух доступов к массиву памяти одновременно или по существу одновременно, т.е. в пределах одного тактового цикла.

Количество времени, требуемое для выполнения первой операции чтения из памяти, может не быть равно количеству времени, требуемому для выполнения второй операции записи в память. Использование обычного подхода TDM увеличивает общее время доступа к памяти, потому что относительное количество времени, доступное для этих двух операций, определяют с помощью времени возникновения переднего фронта тактового цикла и времени возникновения заднего фронта тактового цикла. Если, например, сигнал синхронизации является низким также же долго, как и высоким в тактовом цикле (т.е. сигнал синхронизации имеет коэффициент заполнения 50/50), то одинаковое количество времени должно быть разрешено для выполнения и более быстрой операции чтения, и более медленной операции записи. Результатом является напрасно потраченное время, которое начинается после того, как операция чтения закончена, и заканчивается с задним фронтом сигнала синхронизации.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Согласно одному из вариантов осуществления настоящего раскрытия, система мультиплексирования адресов псевдо двухпортовой памяти имеет триггер адреса порта чтения, триггер адреса порта записи, схему управления и мультиплексор. Триггер адреса порта чтения предназначен для сохранения адреса чтения в ответ на внешний сигнал синхронизации. Триггер адреса порта записи предназначен для сохранения адреса записи в ответ на внешний сигнал синхронизации. Схема управления управляет доступом к памяти на чтение/запись, основываясь на контроле первой операции обращения к памяти. Мультиплексор переключается между сохраненным адресом чтения и сохраненным адресом записи в ответ на сигнал переключения от схемы управления.

В другом варианте осуществления настоящего изобретения способ управляет применением сигнала адреса к памяти. Способ включает в себя обнаружение запросов записи и чтения. В ответ на запрос чтения в отсутствии запроса записи способ включает в себя доставку адреса чтения в компонент памяти. В ответ на запрос записи в отсутствии запроса чтения способ включает в себя подачу адреса записи в компонент памяти.

В ответ и на запрос чтения, и на запрос записи, которые будут выполняться во время одного тактового цикла, способ включает в себя доставку адреса чтения в компонент памяти. Основываясь на контроле операции чтения, способ дополнительно включает в себя определение времени в пределах одного тактового цикла для доставки адреса записи в компонент памяти. Способ также включает в себя переключение между адресом чтения и адресом записи для доставки адреса записи в компонент памяти в упомянутое определенное время.

Преимущество раскрытых вариантов осуществления состоит в том, что мультиплексирование адресов обеспечивают в псевдо двухпортовой памяти, не влияя на время доступа для чтения. Кроме того, мультиплексирование выполняют с минимальными потерями в плане площади и производительности.

Приведенное выше описывает в общих чертах довольно широко особенности и технические преимущества для лучшего понимания последующего подробного описания. Далее будут описаны дополнительные особенности и преимущества, которые формируют то, что заявляется в формуле изобретения. Специалисты должны признать, что концепцию и конкретный раскрытый вариант осуществления можно легко использовать как основу для изменения или разработки других структур для выполнения тех же самых целей настоящего изобретения. Специалистам также должно быть понятно, что такие эквивалентные конструкции не отступают от объема и сущности изобретения, которые определяются прилагаемой формулой изобретения. Новые признаки, которые, как полагается, характеризуют изобретение, по отношению и к его организации, и к способу работы, вместе с дополнительными задачами и преимуществами, будут лучше понятны из последующего описания, при его рассмотрении в связи с сопроводительными фигурами. Нужно явно подразумевать, однако, что каждая из фигур предусмотрена только с целью иллюстрации и описания, и они не предназначены для определения объема настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более согласованного понимания настоящего раскрытия отсылка теперь будет сделана на последующее описание, которое рассматривается вместе с сопроводительными чертежами.

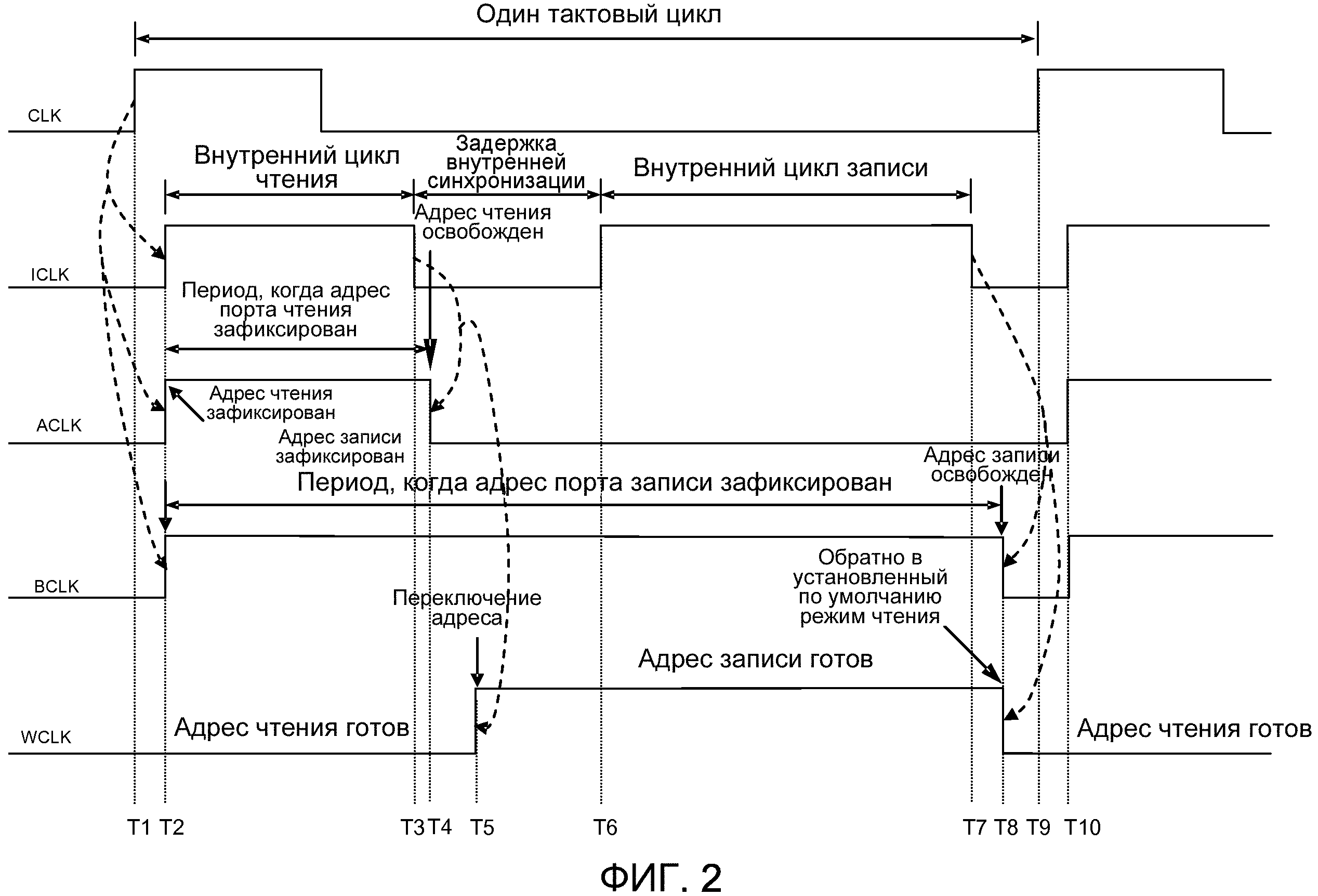

Фиг.1 - высокоуровневая структурная схема системы мультиплексирования адресов для использования с и/или как часть псевдо двухпортовой памяти.

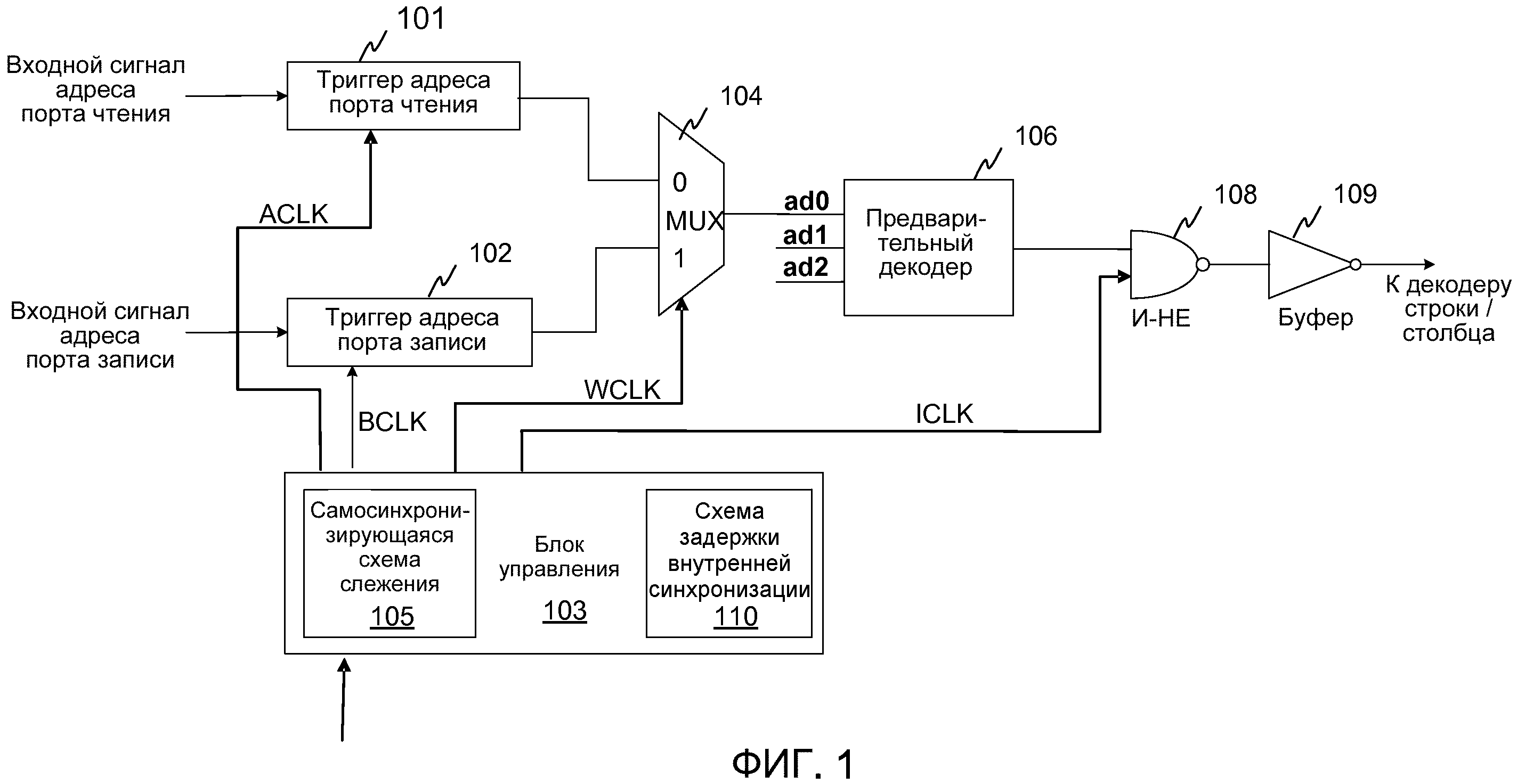

Фиг.2 - временная диаграмма, которая показывает первый сценарий (случай #1) работы системы мультиплексирования адресов по фиг.1.

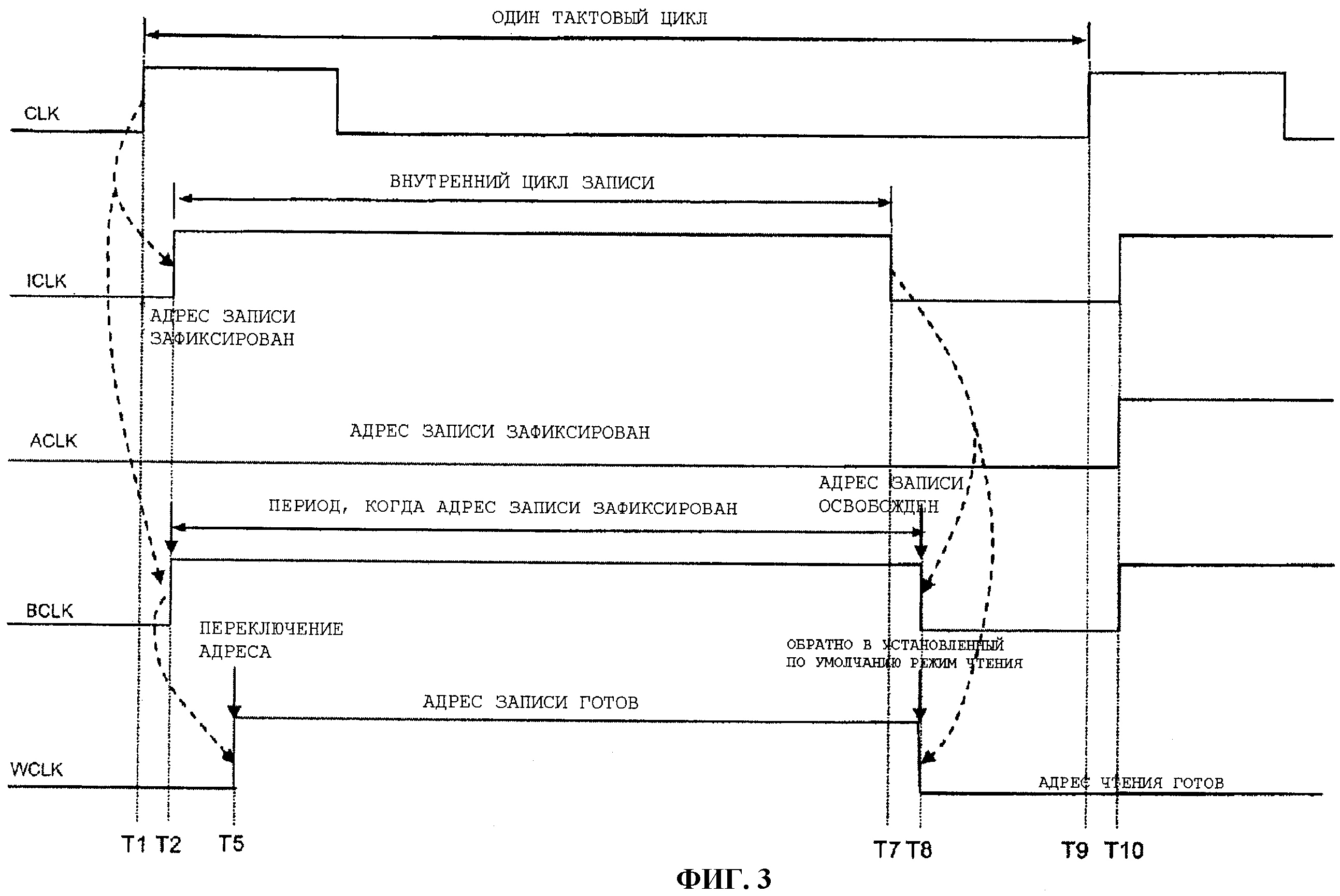

Фиг.3 - временная диаграмма, которая показывает третий сценарий (случай #3) работы системы мультиплексирования адресов по фиг.1.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Фиг.1 - высокоуровневая структурная схема системы 10 мультиплексирования адресов в соответствии с одним из вариантов осуществления для использования с и/или как часть псевдо двухпортовой памяти. Хотя внешним образом предусмотрены два порта, внутри псевдо двухпортовая память имеет только один единственный порт. Таким образом, требуется переключение адреса, когда и операцию чтения, и операцию записи выполняют во время одного входного тактового цикла, т.е. тактовый цикл, внешний к памяти, здесь называется внешним системным тактовым циклом. Варианты осуществления настоящего изобретения направлены на обеспечение мультиплексирования адресов для и/или в псевдо двухпортовой конструкции с минимальными потерями в плане площади и производительности.

Согласно вариантам осуществления изобретения, операцию чтения устанавливают как заданную по умолчанию операцию и, когда требуется, ее выполняют первой, что приводит к быстрому времени доступа для чтения. Когда и операцию чтения, и операцию записи необходимо выполнять во время одного тактового цикла, операцию записи выполняют немедленно после завершения (или по существу завершения) операции чтения, используя внутренне сохраненный и зафиксированный адрес записи. Хотя завершение операции чтения часто определяют с помощью правильного внешнего выходного сигнала считывания, настоящее раскрытие не требует такого условия. Например, формирование сигнала на фиктивной разрядной линии является одним из возможных событий, которое может указывать «завершение» операции чтения.

В системе 10 мультиплексирования адресов адрес чтения сохраняют в триггере 101, в то время как адрес записи сохраняют в триггере 102. В одном из вариантов осуществления память является статической оперативной памятью (SRAM).

Мультиплексор 104 предназначен для выборочного обеспечения адреса чтения и/или адреса записи на предварительный декодер 106. Работа мультиплексора 104 зависит от предыдущей операции чтения. В пределах блока 103 управления, например, самосинхронизирующаяся схема 105 слежения может использоваться для обнаружения завершения чтения для побуждения мультиплексора 104 переключать и доставлять адрес записи на предварительный декодер 106. Если требуются и операция чтения, и операция записи, то операцию записи выполняют по существу немедленно после завершения операции чтения. Контроль операции чтения для определения того, когда операция чтения закончена (или по существу закончена), происходит, используя известные способы, такие как отслеживание фиктивной разрядной линии.

Активный фронт (передний/задний) внешнего системного сигнала синхронизации CLK может использоваться для запуска инициирования внутреннего сигнала синхронизации ICLK через блок 103 управления. Также в ответ на активный фронт внешнего системного сигнала синхронизации блок 103 управления генерирует оба сигнала - сигнал фиксации чтения ACLK и сигнал фиксации записи BCLK, для того, чтобы по существу одновременно фиксировать соответствующие адреса чтения и записи (в тех случаях, когда и операция чтения, и операция записи должны выполняться во время одного и того же внешнего тактового цикла). Сигнал переключения адреса записи WCLK поддерживают в первом (например, низком) состоянии, побуждая мультиплексор 104 обеспечивать адрес чтения на адресную шину (например, на предварительный декодер 106, декодер строки/столбца, линии слова и т.д.), в течение этого времени память запускает и завершает внутренний цикл чтения.

Когда операция чтения закончена или по существу закончена, внутренний сигнал синхронизации ICLK автоматически сбрасывают с помощью самосинхронизирующейся схемы 105 слежения, чтобы освободить триггер 101 адреса порта чтения, предоставляя ему возможность принимать новый адрес чтения, в то время как ранее принятый адрес записи сохраняют зафиксированным с помощью» триггера 102 адреса порта записи. Кроме того, после того, как определено, что операция чтения закончена (или по существу закончена), сигнал переключения адреса WCLK переключает состояние (например, становится высоким), и адрес записи, сохраненный в триггере 102 адрес порта записи, переключают с помощью мультиплексора 104 на предварительный декодер 106 для ожидания начала следующей операции записи.

Уровень внутреннего сигнала синхронизации ICLK снова устанавливается с помощью блока 103 управления, на этот раз для запуска операции записи. Интервал между этими двумя импульсами внутреннего сигнала синхронизации ICLK формируется схемой 110 задержки внутренней синхронизации не только для гарантирования, чтобы операция записи не оказывала воздействия на предшествующую операцию чтения, но также и для того, чтобы адрес записи, доставляемый через предварительный декодер 106, достигал выхода предварительного декодера 106 и обеспечивался к входу триггера (например, И-НЕ (NAND) 108) перед появлением переднего фронта второго цикла внутреннего сигнала синхронизации ICLK. Наличие адреса записи, доступного на входе триггера 108 до второго внутреннего тактового цикла, необходимо для того, чтобы избежать возможности генерации ошибки на выходе триггера адреса (например, И-НЕ 108), когда входной сигнал к схеме 108 изменяется или еще не стабилизировался.

В одном из вариантов осуществления схему 110 задержки внутренней синхронизации настраивают с помощью моделирования после топологической компоновки. После того, как определено, что операция чтения закончена (или по существу закончена), достаточную задержку обеспечивают для предотвращения конфликтов адресов чтения и записи. Задержка также должна быть достаточной, чтобы дать возможность стабилизироваться разрядным линиям перед операцией записи. Задержка является статической задержкой, программируемой с помощью металлической маски.

После того, как операция записи закончена (или по существу закончена), внутренний сигнал синхронизации ICLK снова сбрасывают, и триггер 102 адреса порта записи освобождают для приема любого нового адреса записи. Сигнал переключения адреса записи WCLK также сбрасывают (например, устанавливают в низкий логический уровень, такой как «0»), таким образом, что условие или состояние доступа к памяти восстанавливают в заданный по умолчанию режим чтения, ожидая следующего внешнего системного тактового цикла. Завершение операции записи определяют с помощью самосинхронизирующейся схемы 105 слежения известным способом, например, с помощью отслеживания фиктивной разрядной линии.

Работа мультиплексора (MUX) 104 дополнительно обеспечивает операции только чтения и только записи в память/доступа во время конкретного внешнего цикла. В случае операции чтения работает только сигнал фиксации чтения ACLK, а не сигнал фиксации записи BCLK, последний поддерживается в некотором неактивном состоянии (например, в низком или нулевом состоянии). В случае только операции записи (например, когда никакая операция чтения не выполняется во время конкретного внешнего цикла синхронизации), сигнал переключения адреса записи устанавливают в высокий уровень во время начальной операции схемы так, чтобы адрес записи был обеспечен на предварительный декодер 106 при первой возможности.

При работе и в отношении фиг.1, входной сигнал адреса порта чтения подают на триггер 101 адреса порта чтения. Аналогично, входной сигнал адреса порта записи подают на триггер 102 адреса порта записи. Блок 103 управления обеспечивает соответствующие управляющие сигналы (т.е. сигнал фиксации чтения ACLK и сигнал фиксации записи BCLK) к триггерам 101 и 102 адреса портов чтения и записи, соответственно, чтобы побудить триггеры 101, 102 принимать и хранить соответствующие входные сигналы адреса порта. Блок 103 управления дополнительно генерирует и обеспечивает внутренний сигнал синхронизации ICLK к схеме, такой как элемент И-НЕ 108. Переключение адреса выполняют с помощью мультиплексора 104, который принимает оба зафиксированные адреса портов чтения и записи от триггеров 101 и 102 адреса портов чтения и записи и, в зависимости от сигнала переключения адреса записи WCLK от блока 103 управления, выборочно обеспечивает один или другой на предварительный декодер 106. Самосинхронизирующуюся схему 105 слежения можно обеспечивать в пределах блока 103 управления, и она может принимать участие в принятии решения относительно того, когда переключать сигнал переключения адреса записи WCLK. Хотя предварительный декодер 106 изображен, как обычный компонент адресации памяти, который принимает сигнал адреса, можно использовать другие и/или альтернативные компоненты, такие как буфер адреса, дешифратор адреса и т.д.

В настоящем варианте осуществления двоично-кодированный сигнал адреса доставляют в предварительный декодер 106, что приводит к активации конкретной выходной линии, при этом данный сигнал доставляют к соответствующей схеме И-НЕ 108. Схема И-НЕ 108 принимает внутренний сигнал синхронизации ICLK для того, чтобы пропустить выходной сигнал от предварительного декодера 106, чтобы таким образом обеспечить инвертированный выходной сигнал на буфер 109. Выходной сигнал буфера 109 затем передают на декодер строки/столбца (не показан) и/или на другие компоненты памяти.

Фиг.2 временная диаграмма первого сценария (случай #1), в котором требуются операции и чтения, и записи, и они должны выполняться во время одного внешнего системного тактового цикла. Фиг.3 изображает только операцию записи, которая будет выполняться во время внешнего системного тактового цикла.

Обращаясь к фиг.2, о начале следующего внешнего системного тактового цикла сообщает передний фронт внешнего системного сигнала синхронизации CLK в момент времени Т1. В ответ на то, что внешний системный сигнал синхронизации CLK становится высоким, внутренний сигнал синхронизации ICLK генерируется блоком 103 управления, и он становится высоким в момент времени Т2, с задержкой распространения после момента времени Т1. Кроме того, в ответ на то, что внешний системный сигнал синхронизации CLK становится высоким, сигнал фиксации чтения ACLK и сигнал фиксации записи BCLK становятся высокими в момент времени Т2, таким образом фиксируя и сохраняя вводимые адреса чтения и записи.

Операция чтения контролируется самосинхронизирующейся схемой 105 слежения для определения того, когда она закончена (или по существу закончена). После того, как операция чтения закончена (или по существу закончена), в момент времени Т4 внутренний сигнал синхронизации ICLK становится низким, чтобы инициировать переход в режим записи. Следует отметить, что этот переход независим от внешнего системного сигнала синхронизации CLK. Время, когда внутренний сигнал синхронизации ICLK становится низким, определяется самосинхронизирующейся схемой 105 слежения, которая контролирует операцию чтения. В одном из вариантов осуществления, контролируют время прохождения всей разрядной линии и линии слова памяти. Например, фиктивная разрядная линия может использоваться для отслеживания операции чтения, как известно из предшествующего уровня техники.

В ответ на то, что внутренний сигнал синхронизации ICLK становится низким в момент времени Т3, сигнал фиксации чтения ACLK становится низким в момент времени Т4 так, чтобы триггер 101 адреса порта чтения был освобожден и мог реагировать на подачу нового входного сигнала адреса порта чтения. В момент времени Т5 и в ответ на то, что сигнал фиксации чтения ACLK становится низким, сигнал переключения адреса записи WCLK становится высоким. Высокий сигнал WCLK указывает, что адрес записи готов, и он побуждает мультиплексор 104 переключаться и таким образом выборочно передавать адрес записи, сохраненный в триггере 102 адреса порта записи, на предварительный декодер 106 (вместо ранее переданного адреса чтения).

Задержка внутренней синхронизации начинается в момент времени Т3. Задержку внутренней синхронизации обеспечивают с помощью схемы 110 задержки внутренней синхронизации. Хотя описание обсуждает запуск задержки внутренней синхронизации в ответ на то, что внутренний сигнал синхронизации ICLK становится низким в момент времени Т3, в дополнительном варианте осуществления задержка внутренней синхронизации начинается, когда сигнал фиксации чтения ACLK становится низким в момент времени Т4.

После задержки внутренней синхронизации внутренний сигнал синхронизации ICLK становится высоким в момент времени Т6, чтобы таким образом инициировать следующий доступ к памяти в форме внутреннего цикла записи. Когда внутренний цикл записи заканчивается, внутренний сигнал синхронизации ICLK возвращают в низкий уровень в момент времени Т7. Как отмечено выше, самосинхронизирующаяся схема 105 слежения контролирует операцию записи, используя известную технологию, такую как контроль фиктивных разрядных линий для определения того, когда операция записи закончена.

Когда завершилась операция записи и в ответ на то, что внутренний сигнал синхронизации ICLK становится низким, в момент времени Т8 сигнал записи BCLK становится низким, таким образом освобождая триггер 102 адреса порта записи и давая возможность ему принимать любой новый адрес записи, который будет использоваться во время следующего внешнего системного тактового цикла. Также в ответ на то, что внутренний сигнал синхронизации ICLK становится низким, сигнал переключения адреса записи WCLK становится низким, чтобы сбросить мультиплексор 104 в начальное состояние, посредством чего выходной сигнал триггера 101 адреса порта чтения передают на предварительный декодер 106, чтобы он был готов к любому следующему запросу чтения. В момент времени Т9 внешний системный сигнал синхронизации CLK становится высоким, указывая начало следующего цикла доступа к системной памяти, так что внутренний сигнал синхронизации ICLK, сигнал фиксации считывания ACLK и сигнал фиксации записи BCLK становятся высокими в момент времени Т10, повторяя ранее подробно описанные процедуры (по меньшей мере до той степени, что операции доступа и для чтения, и для записи требуются и должны выполняться во время этого следующего внешнего системного периода синхроимпульсов).

Согласно еще одному варианту осуществления, должна выполняться только операция чтения, т.е. никакая операция записи не требуется или не должна выполняться во время конкретного внешнего системного тактового цикла. Становится известно, что операция чтения требуется, но операция записи не требуется, с помощью контроля контактов выбора чипа. Один контакт выбора чипа предусмотрен для операции чтения, в то время как второй контакт выбора чипа предусмотрен для операции записи.

Когда адрес записи не доставлен (т.е. соответствующий контакт выбора чипа не выбран), сигнал фиксации записи BCLK может сохраняться низким, чтобы он был готов принимать любой подаваемый сигнал, который может приходить (хотя варианты осуществления изобретения могут также включать в себя те варианты, которые не запрещают переключение сигнала BCLK, как ранее показано на фиг.2). Аналогично, при отсутствии запроса записи, сигнал переключения адреса записи WCLK также поддерживают низким, т.е. в состоянии чтения, для побуждения мультиплексора 104 непрерывно передавать входной сигнал адреса порта чтения, зафиксированный и сохраненный с помощью триггера 101 адреса порта чтения, на предварительный декодер 106. Иначе, сигналы, требуемые для осуществления операции чтения, отправляют между моментами времени Т1 и Т4, как объяснено выше в отношении фиг.2. Сигналы, необходимые для поддержки осуществления операций записи в память, которые происходят во время Т5-Т8, как показано на фиг.2, можно удалять как ненужные.

Фиг.3 - временная диаграмма третьего сценария, в котором должна выполняться только операция записи, т.е. никакая операция чтения не требуется или не должна выполняться во время конкретного внешнего системного тактового цикла (контакт выбора чипа операции чтения не выбран). Когда адрес чтения не доставлен, сигнал фиксации чтения ACLK может сохраняться низким, чтобы быть готовым принимать любой подаваемый сигнал, который может прибыть. Следует отметить, что варианты осуществления изобретения могут также включать в себя те варианты, которые не запрещают переключение сигнала фиксации чтения ACLK, как ранее показано на фиг.2. При отсутствии запроса чтения сигнал переключения адреса записи WCLK можно устанавливать в высокий уровень в ответ на повышение (в момент времени Т5) сигнала фиксации записи BCLK, чтобы побудить мультиплексор 104 передавать входной сигнал адреса порта записи, зафиксированный и сохраненный триггером 102 адреса порта записи, на предварительный декодер 106.

В общем случае, игнорируя сигналы, необходимые только для чтения, сигналы, необходимые для выполнения операции записи, можно продвигать вперед, т.е. их можно инициировать раньше во время цикла внешнего системного сигнала синхронизации CLK, чем тогда, когда и операция чтения, и операция записи требуются и должны выполняться. Аналогично, как во втором сценарии операции только чтения, внутренний сигнал синхронизации ICLK должен включать в себя только один цикл, во время которого, в этом третьем сценарии, выполняют операцию записи. Таким образом, в момент времени Т2 внутренний сигнал синхронизации ICLK становится высоким, как сигнал фиксации записи BCLK. Поскольку операции записи в общем случае требуют больше времени для завершения, чем операции чтения, ширину импульса внутреннего сигнала синхронизации ICLK расширяют, чтобы он оставался высоким до момента времени Т7. В ответ на задний фронт внутреннего сигнала синхронизации ICLK как сигнал фиксации записи BCLK, так и сигнал переключения адреса записи WCLK возвращаются в низкий уровень для подготовки схемы для приема нового адреса записи.

Хотя были приведены конкретные схемы, специалисты должны признать, что не все из раскрытых схем требуются для практического применения изобретения. Кроме того, некоторые широко известные схемы не были описаны, чтобы сфокусироваться на изобретении. Точно так же, хотя данное описание относится к логическому «0» и логической «1» в определенных местах, специалисты должны признать, что логические значения можно изменять, причем с соответствующей корректировкой остальных схем, что не влияет на работу настоящего изобретения.

Хотя выше в целях обучения описаны некоторые конкретные варианты осуществления, настоящее изобретение не ограничено ими. Схему управления псевдо двухпортовой памятью можно использовать в вариантах осуществления, где первая операция доступа к памяти - операция записи, а вторая операция доступа к памяти - операция чтения, первая операция доступа к памяти - операция записи, а вторая операция доступа к памяти - операция записи, и первая операция доступа к памяти - операция чтения, а вторая операция доступа к памяти - операция чтения. Соответственно, различные изменения, усовершенствования и комбинации различных признаков описанных конкретных вариантов осуществления можно осуществлять, не отступая от объема изобретения, который определяется формулой изобретения.