Результат интеллектуальной деятельности: СДВИГОВЫЙ РЕГИСТР, СХЕМА УПРАВЛЕНИЯ ДИСПЛЕЕМ, ПАНЕЛЬ ОТОБРАЖЕНИЯ И УСТРОЙСТВО ОТОБРАЖЕНИЯ

Вид РИД

Изобретение

Область техники, к которой относится изобретение

Настоящее изобретение относится к сдвиговому регистру и различным устройствам управления дисплеем.

Уровень техники

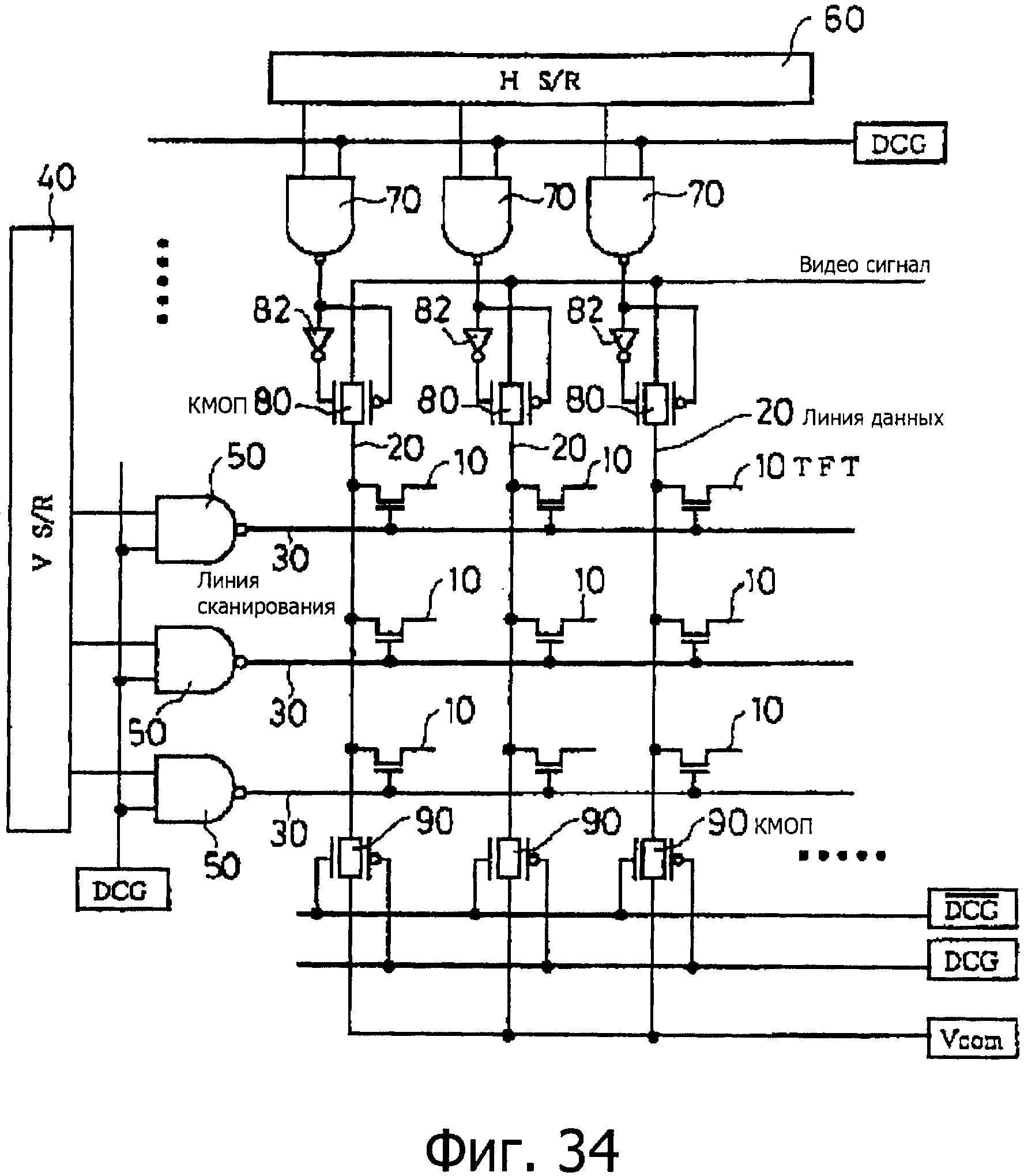

В Патентной литературе 1 (см. фиг.34) раскрыта компоновка, в которой на элементы NAND (НЕ-И) подают (i) соответствующие выходные сигналы из соответствующих каскадов сдвигового регистра, включенного в схему управления затвором, и (И) сигнал DCG (цифрового генератора сигнала), и в которой элементы (НЕ-И) подают свои соответствующие выходные сигналы в соответствующие линии развертки. Такая компоновка позволяет (i) одновременно выбирать все линии сигнала развертки, делая сигнал DCG активным, когда устройство жидкокристаллического дисплея включают и выключают, и, таким образом, (ii) записывают Vcom (потенциал общего электрода) во все пиксели.

Список литературы

Патентная литература 1

Публикация, Tokukai №2000-347627 заявки на патент Японии (Дата публикации: 15 декабря 2000 г.)

Раскрытие изобретения

Техническая задача

Описанная выше обычная компоновка, к сожалению, требует использовать (i) элементы (НЕ-И), на которые подают соответствующие выходные сигналы от сдвигового регистра, и сигнал DCG и (ii) компоненты, которые инициализируют сдвиговый регистр после одновременного выбора всех линий сигнала развертки (например, (i) схему для генерирования сигнала инициализации и (ii) линию передачи). Это требование не позволяет уменьшить размеры схемы управления затвором.

Цель настоящего изобретения состоит в том, чтобы обеспечить сдвиговый регистр, который позволяет уменьшить размеры схемы управления дисплеем (различные схемы управления дисплеем).

Решение задачи

Сдвиговый регистр в соответствии с настоящим изобретением представляет собой сдвиговый регистр для схемы управления дисплеем, который одновременно выбирает линии сигнала, например, в заданные моменты времени, сдвиговый регистр, содержит в его каскаде: триггер, включающий в себя вывод инициализации; и схему генерирования сигнала, которая принимает сигнал одновременного выбора и которая генерирует выходной сигнал упомянутого каскада, с использованием выходного сигнала триггера, причем выходной сигнал упомянутого каскада становится активным в результате активации сигнала одновременного выбора, оставаясь активным в течение периода одновременного выбора; в то время как вывод инициализации триггера является активным, выходной сигнал триггера является неактивным, независимо от состояния другого входного вывода (триггера); и на вывод инициализации поступает одновременный сигнал выбора.

Представленная выше компоновка позволяет использовать сигнал одновременного выбора, в качестве сигнала для инициализации сдвигового регистра, и, таким образом, исключается необходимость дополнительно генерировать такой сигнал и подавать этот сигнал в каждый каскад. Это позволяет уменьшить размеры схемы управления дисплеем (то есть, различных схем управления дисплеем), включающий в себя сдвиговый регистр.

Полезные эффекты изобретения

Настоящее изобретение позволяет уменьшить размер схемы управления дисплеем (устройства управления дисплеем).

Краткое описание чертежей

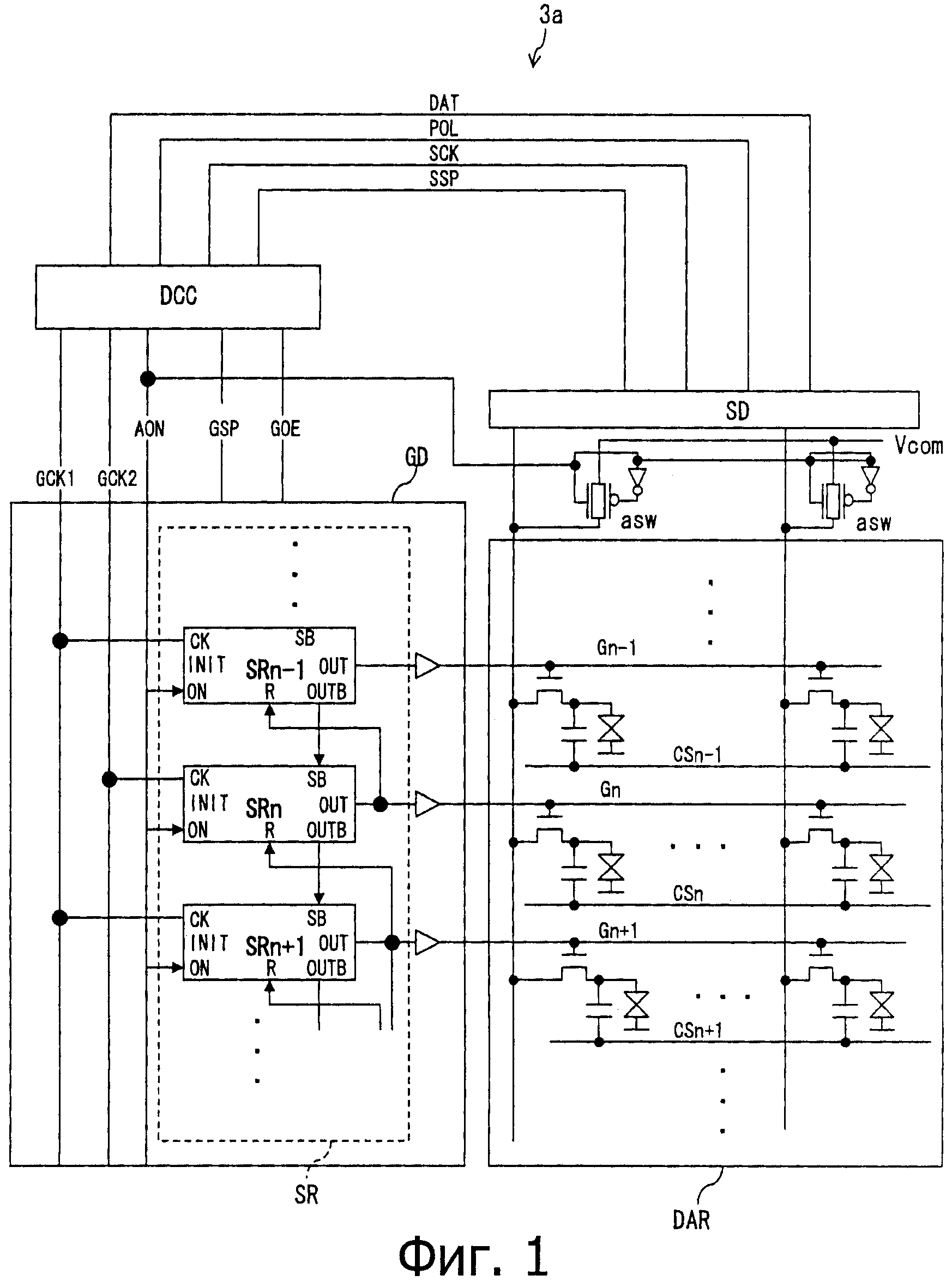

На фиг.1 показана схема, схематично иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

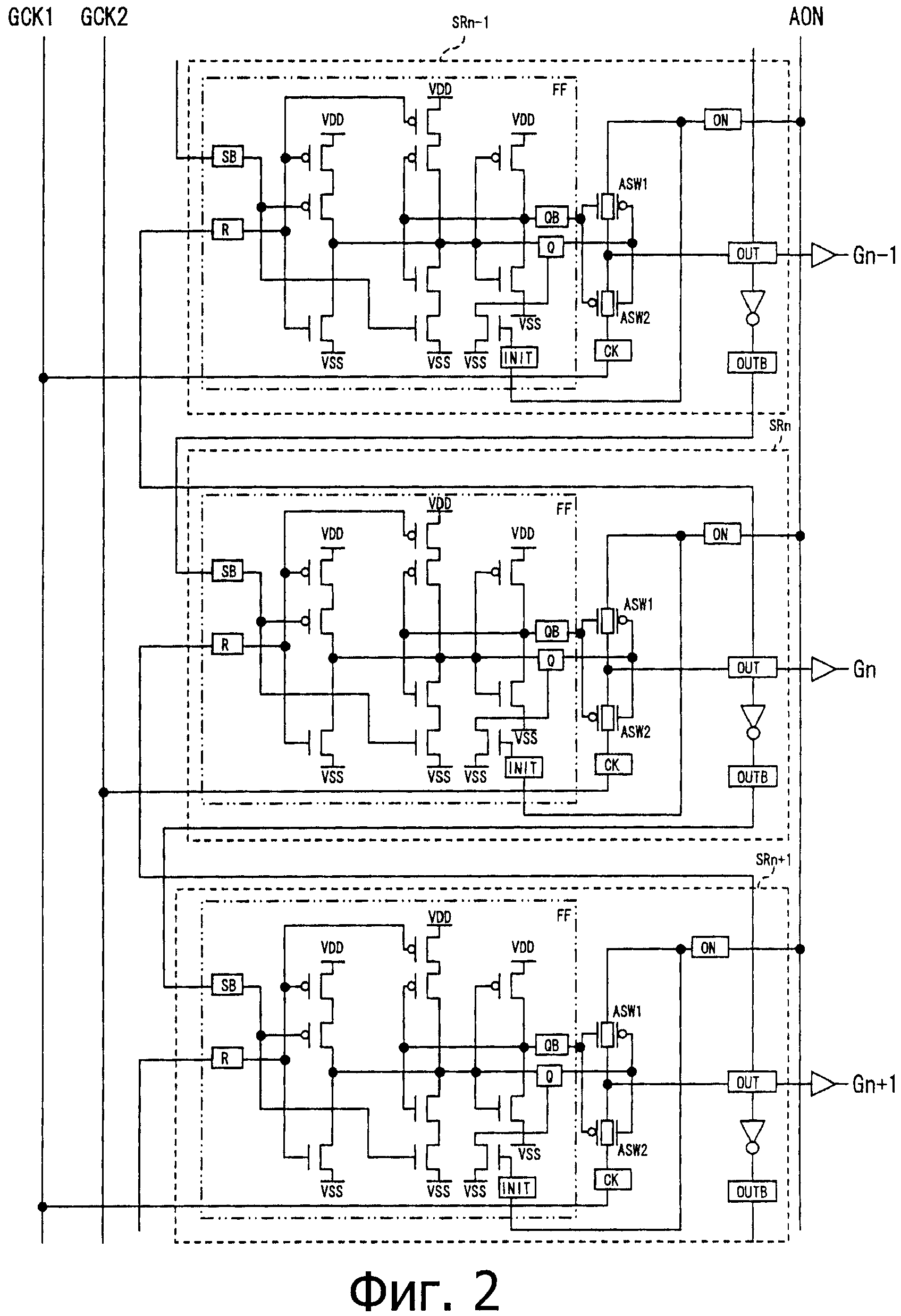

На фиг.2 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.1.

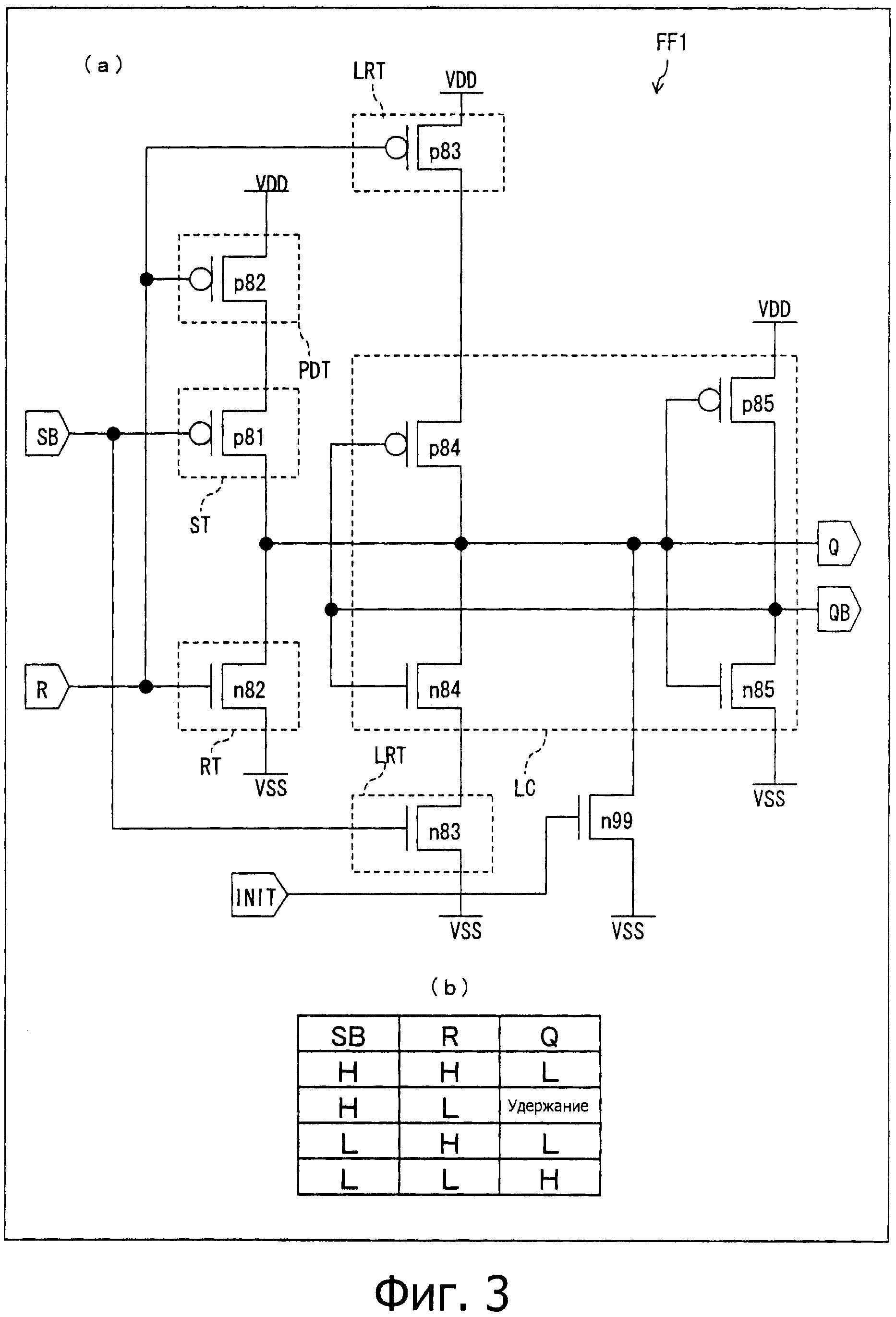

На фиг.3(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.2, и (b) показана таблица истинности для триггера.

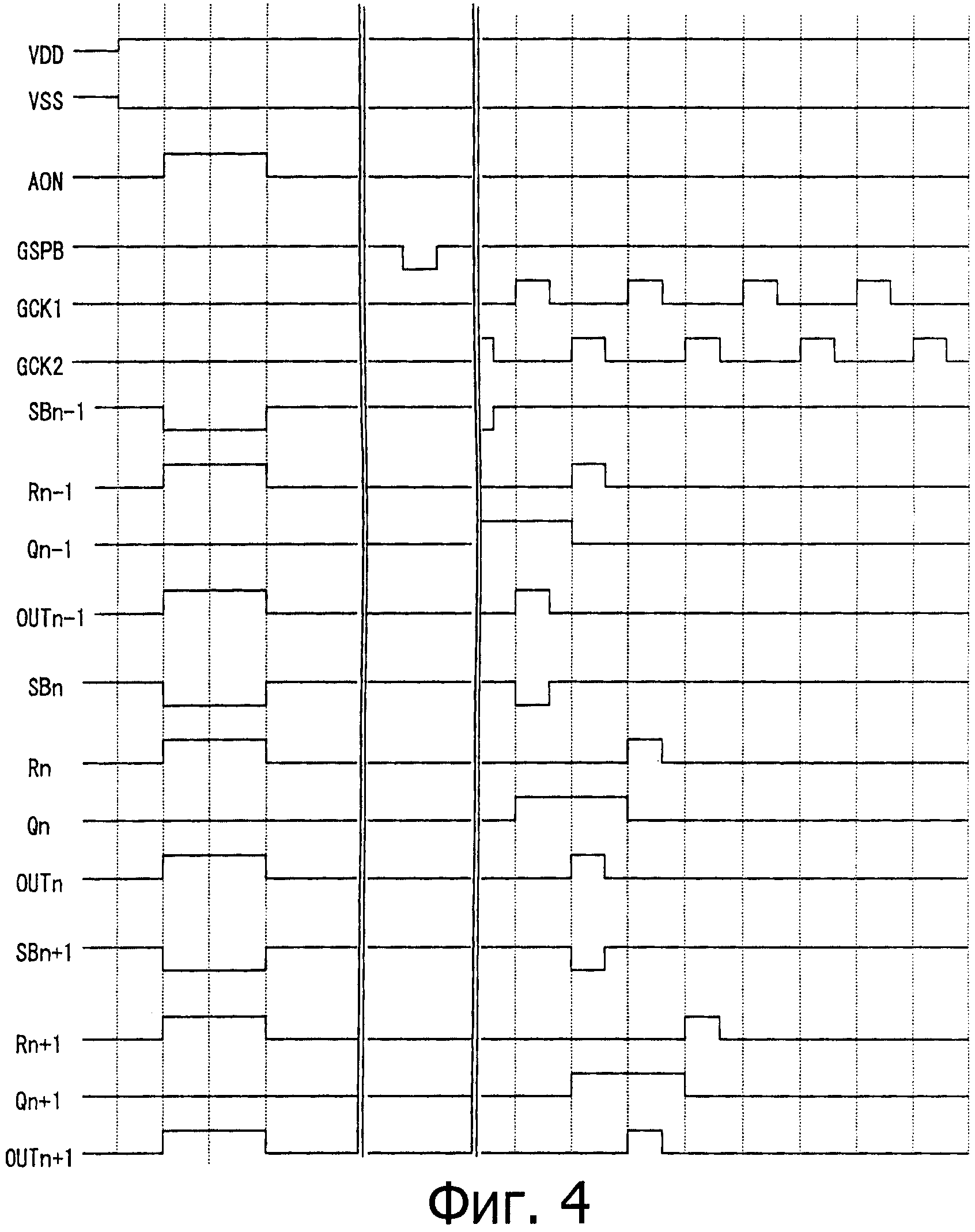

На фиг.4 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.1 при включении.

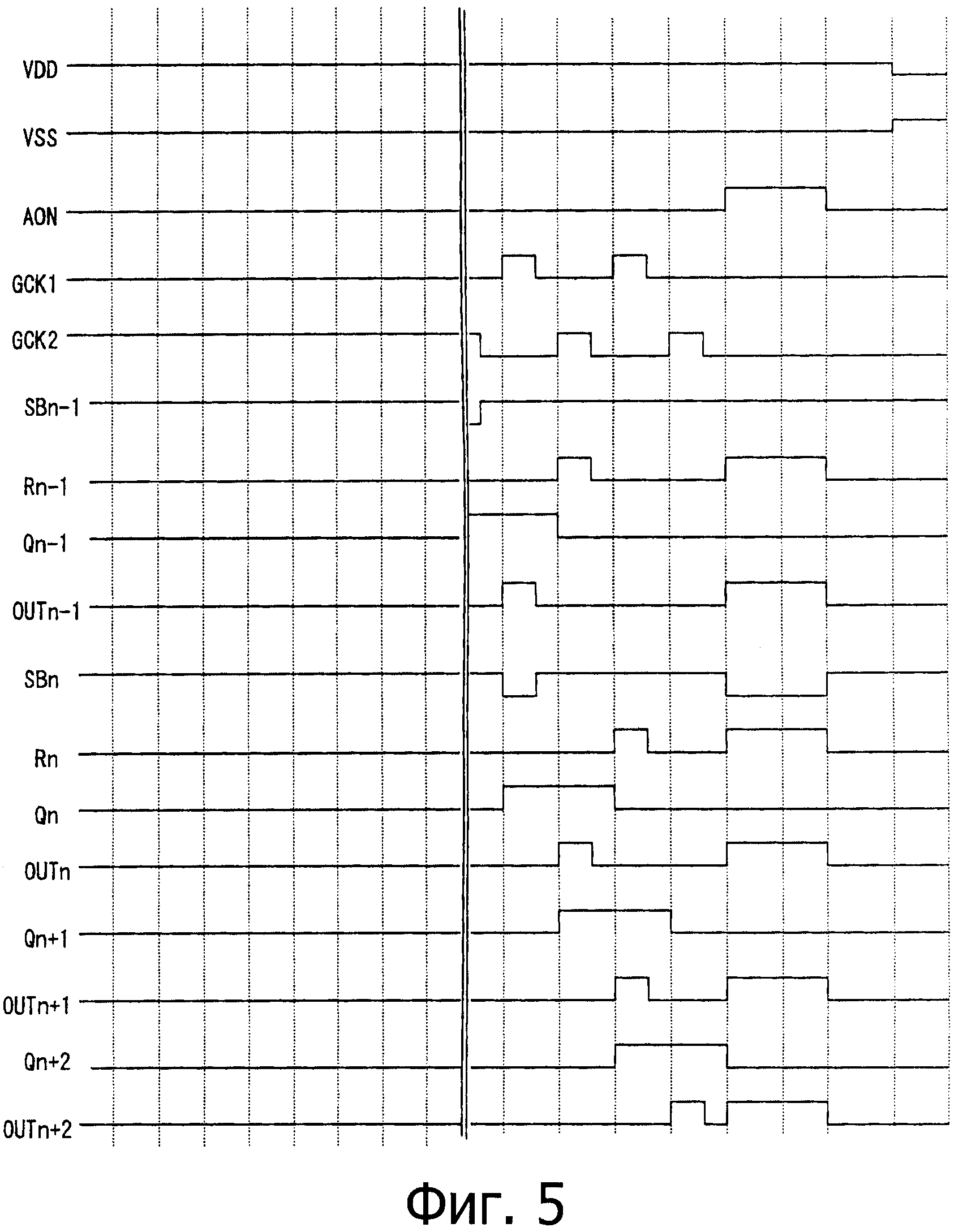

На фиг.5 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.1 при выключении.

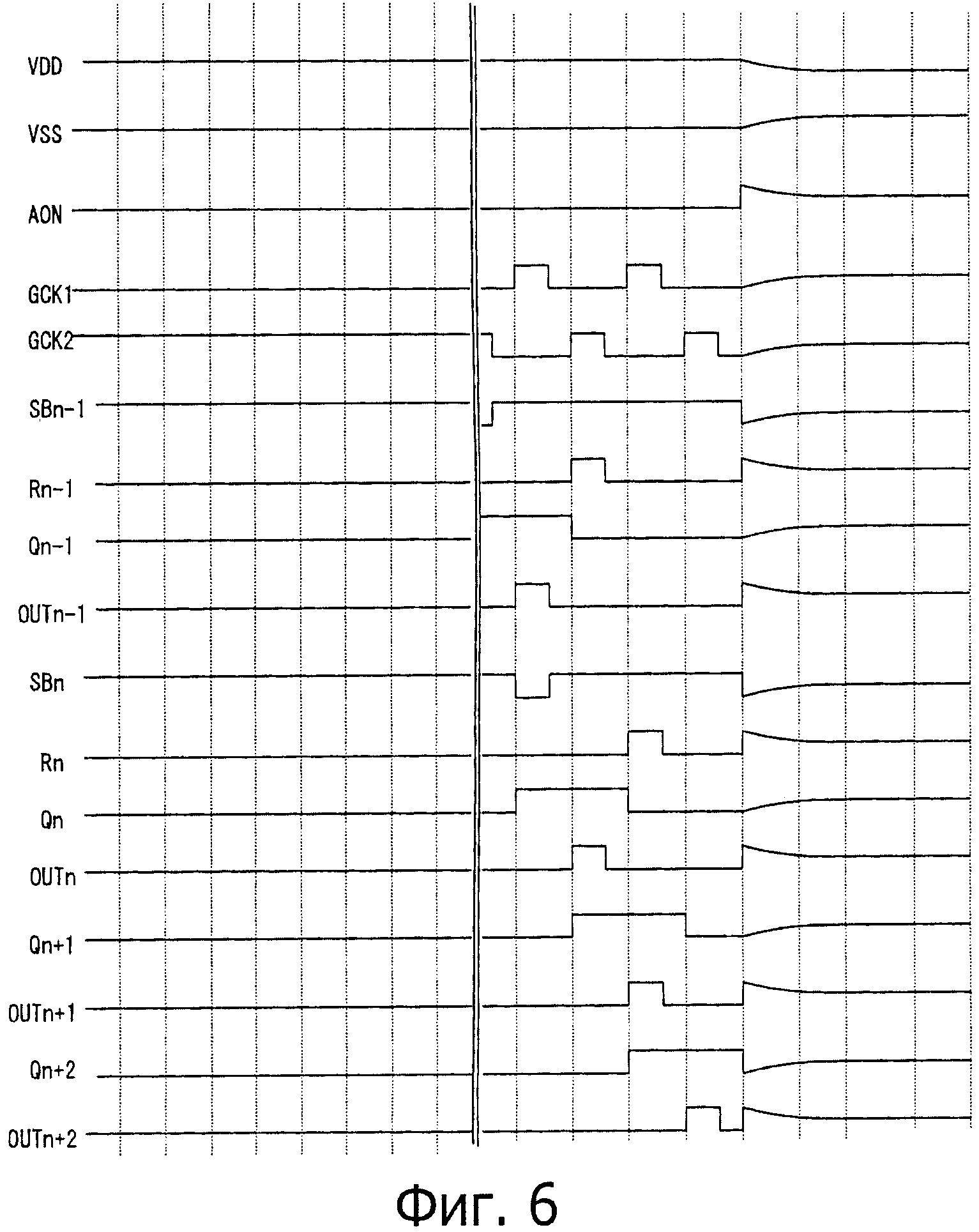

На фиг.6 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея фиг.1 при принудительном выключении.

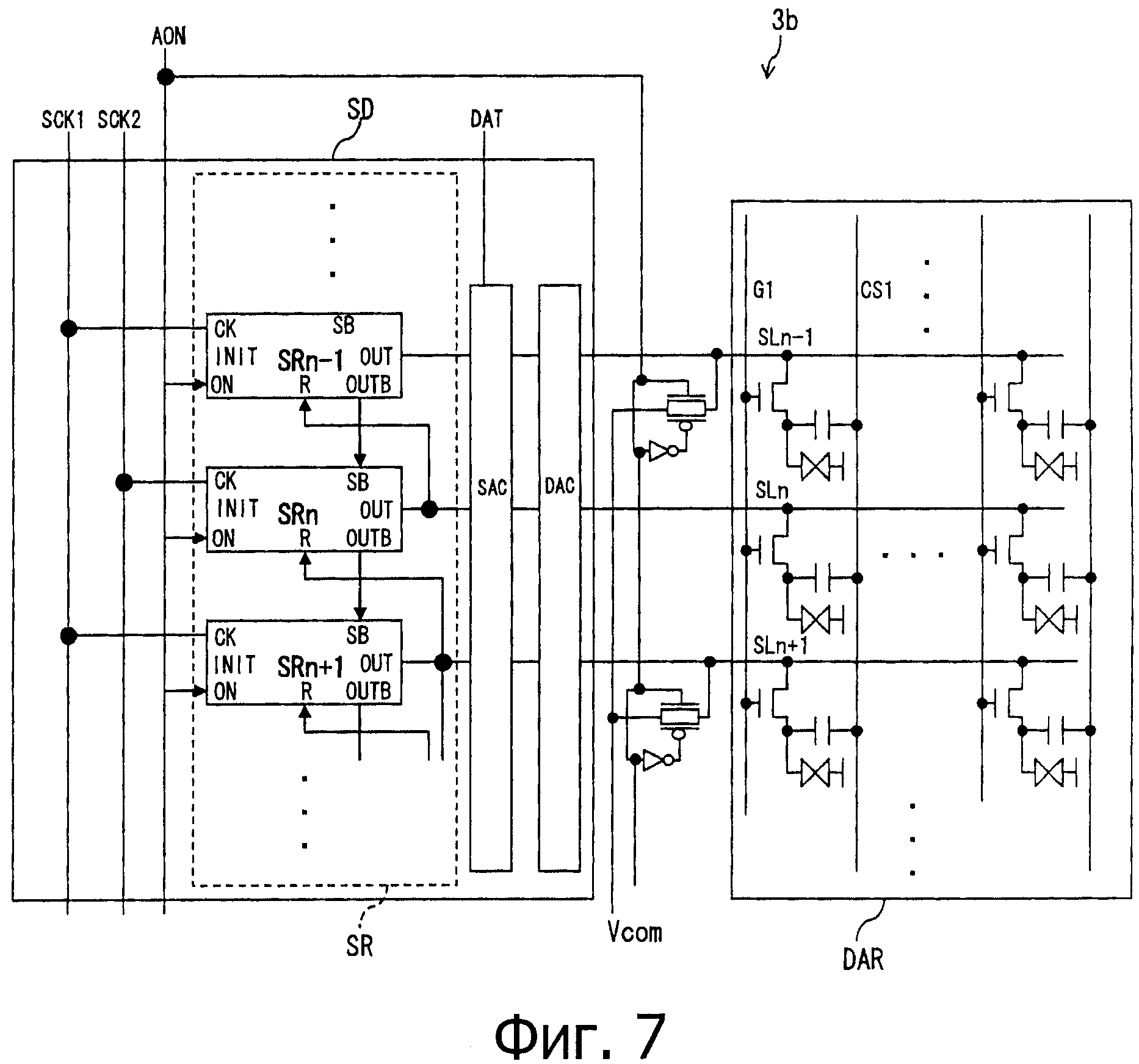

На фиг.7 показана схема, иллюстрирующая другую конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

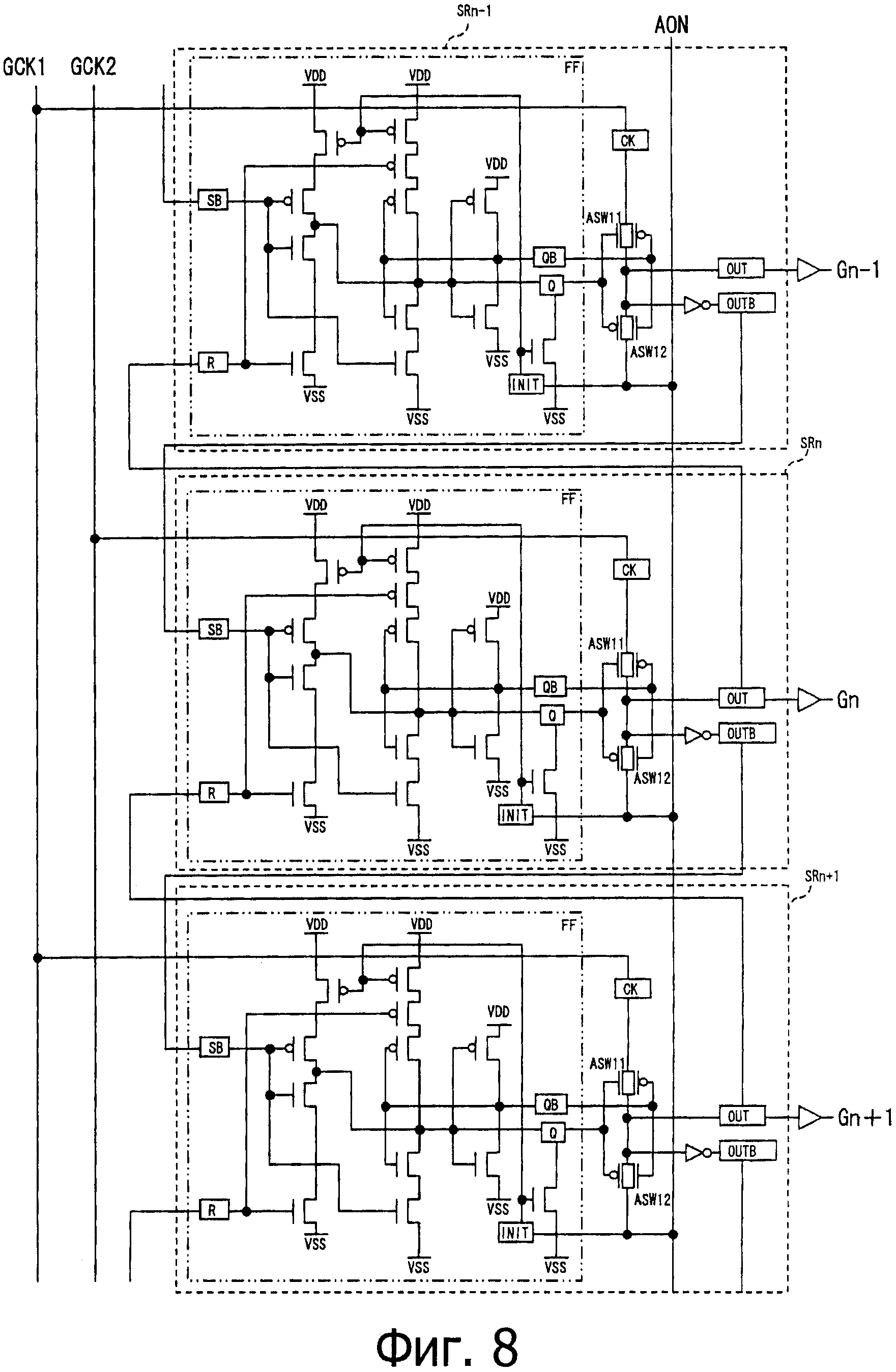

На фиг.8 показана принципиальная схема, иллюстрирующая вариант сдвигового регистра, представленного на фиг.2.

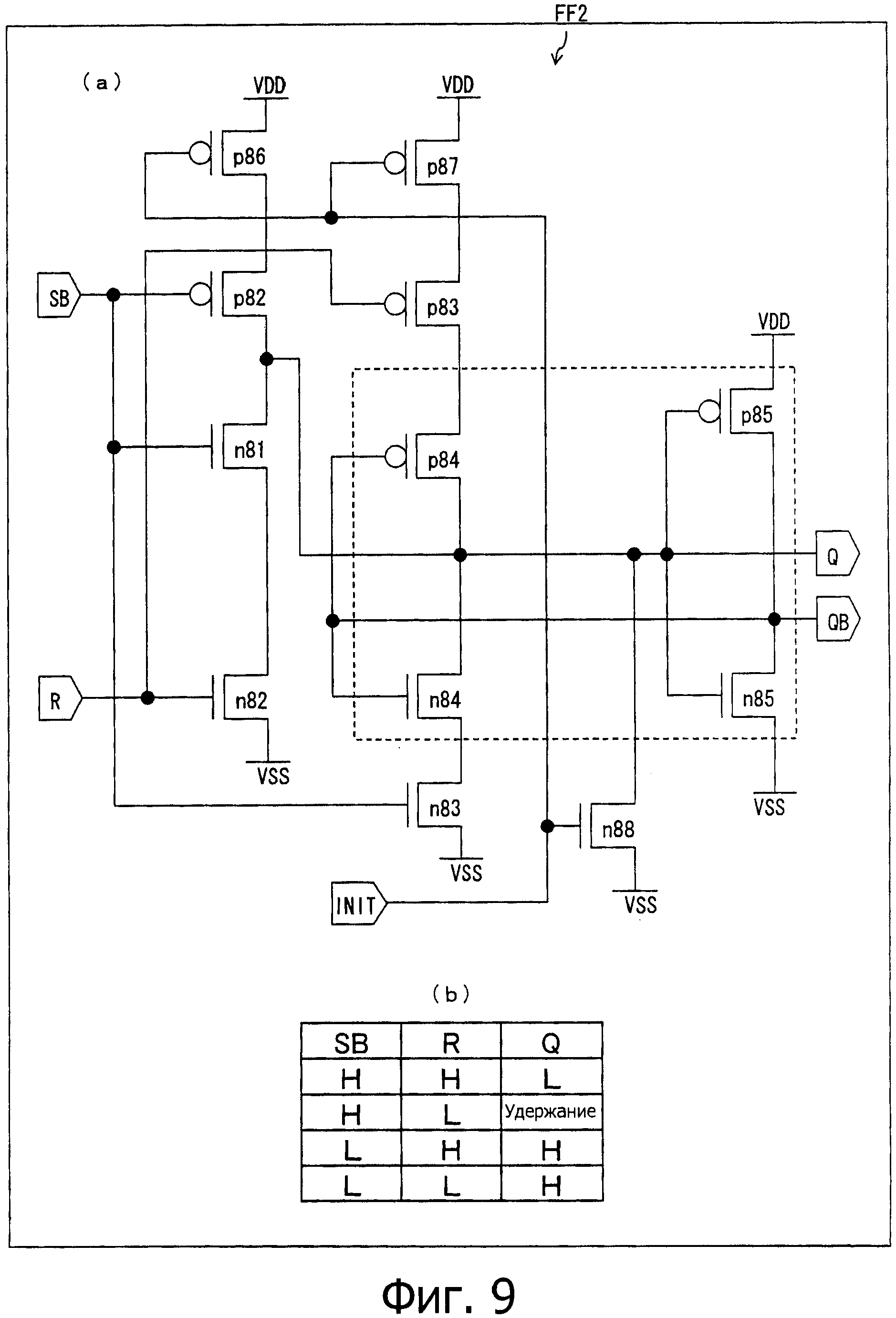

На фиг.9(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.8, и (b) показана таблица истинности для триггера.

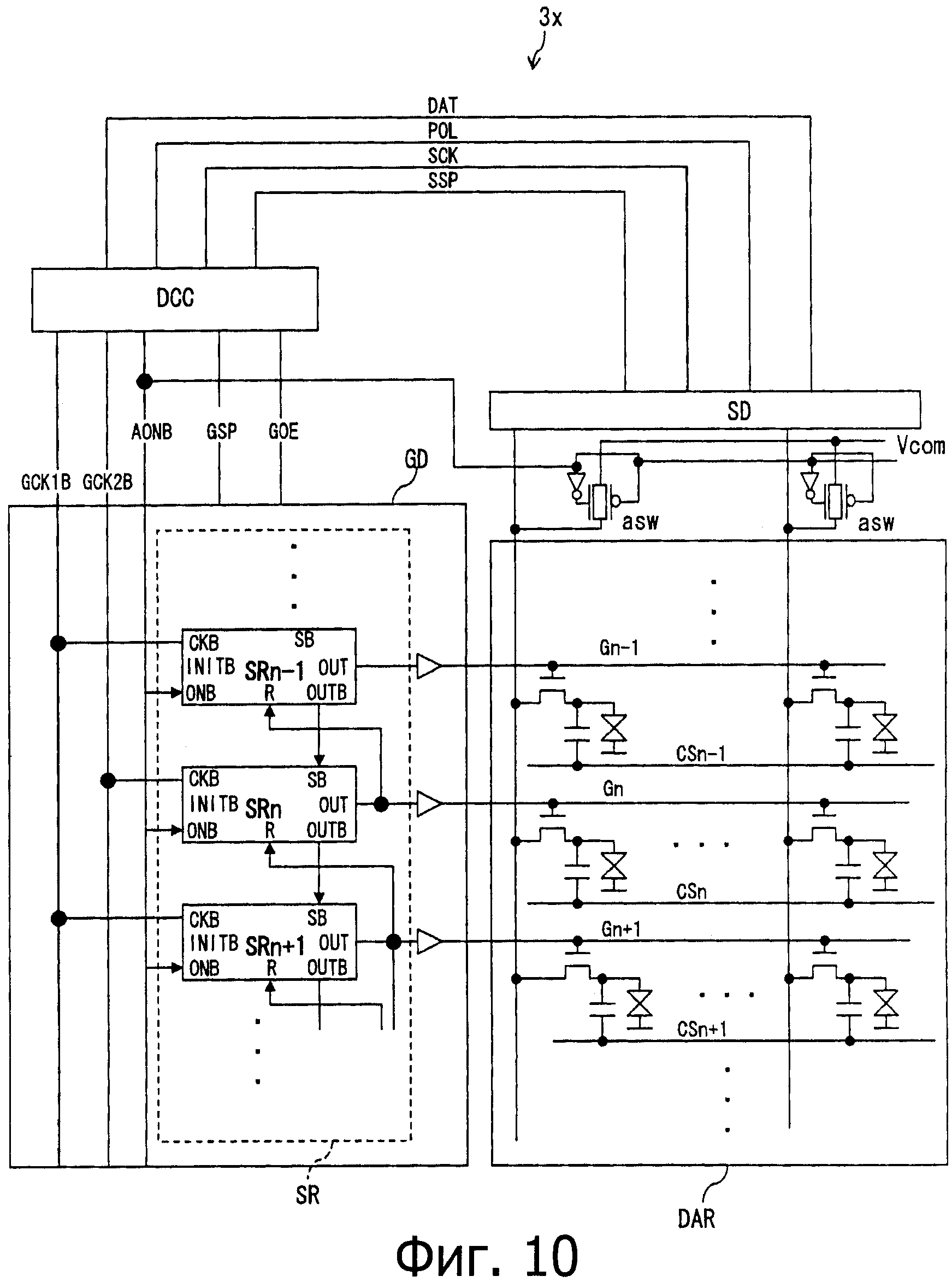

На фиг.10 показана схема, иллюстрирующая еще одну другую конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

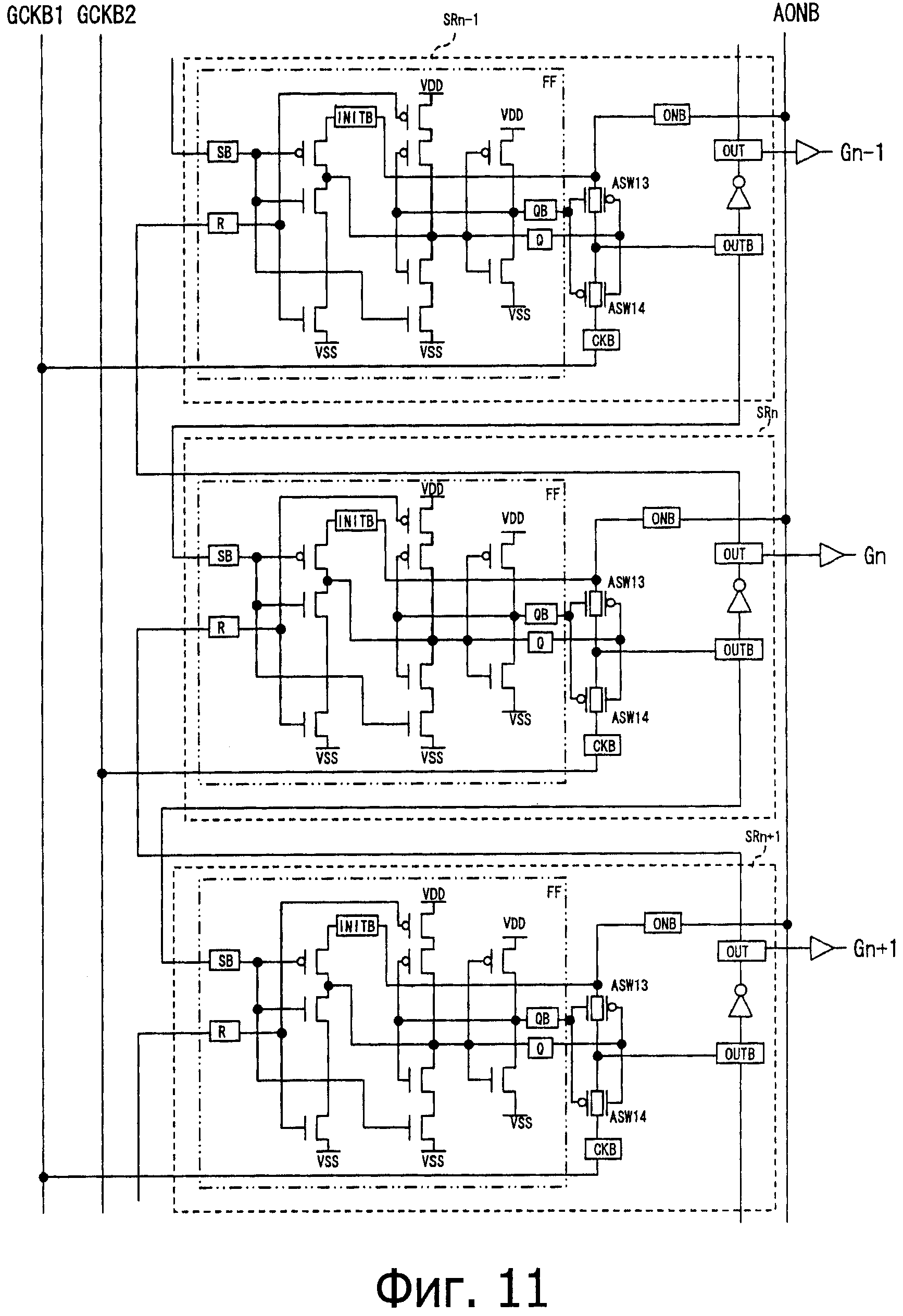

На фиг.11 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.10.

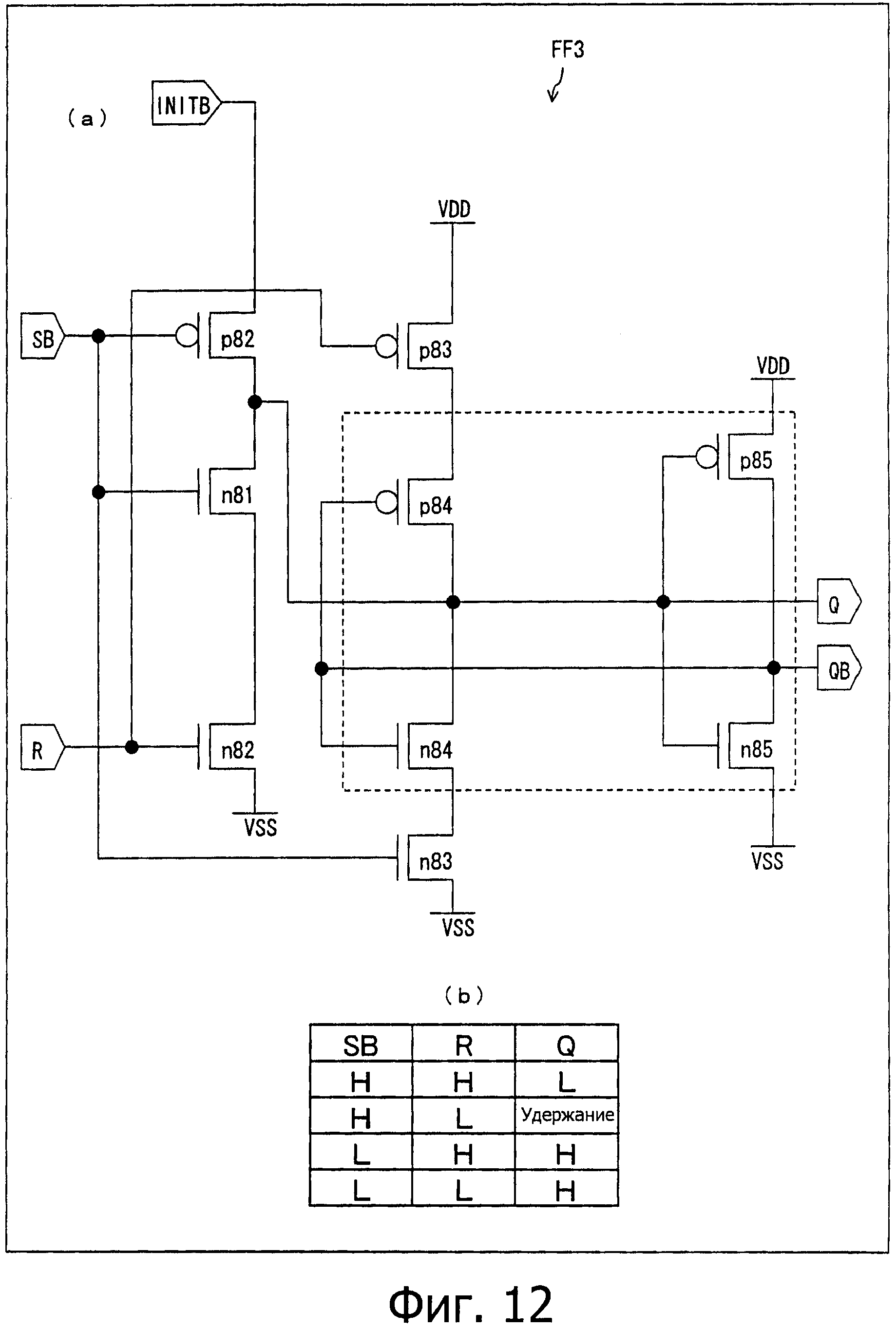

На фиг.12(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.11, и (b) показана таблица истинности для триггера.

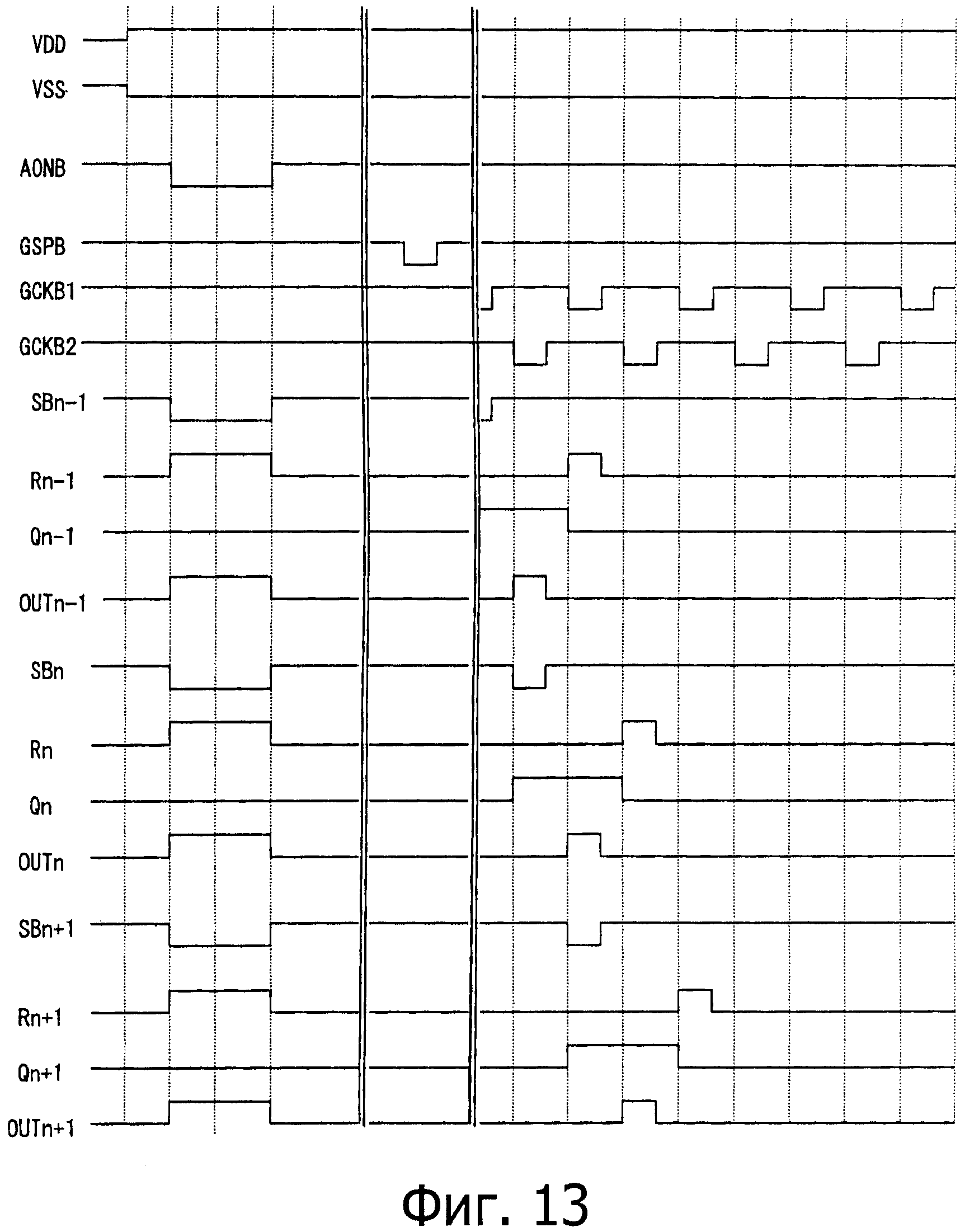

На фиг.13 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.10 при включении.

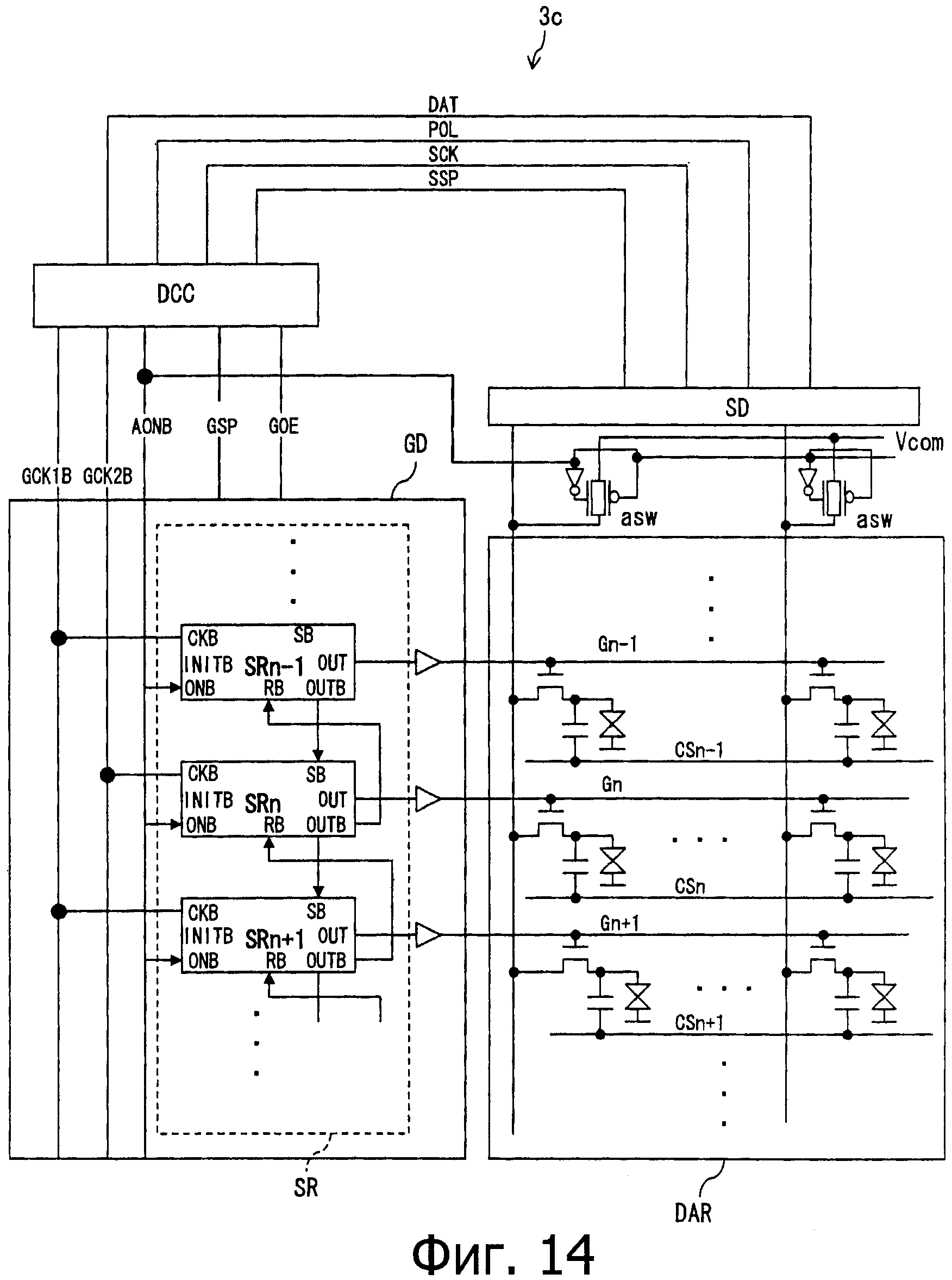

На фиг.14 показана схема, иллюстрирующая еще одну конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

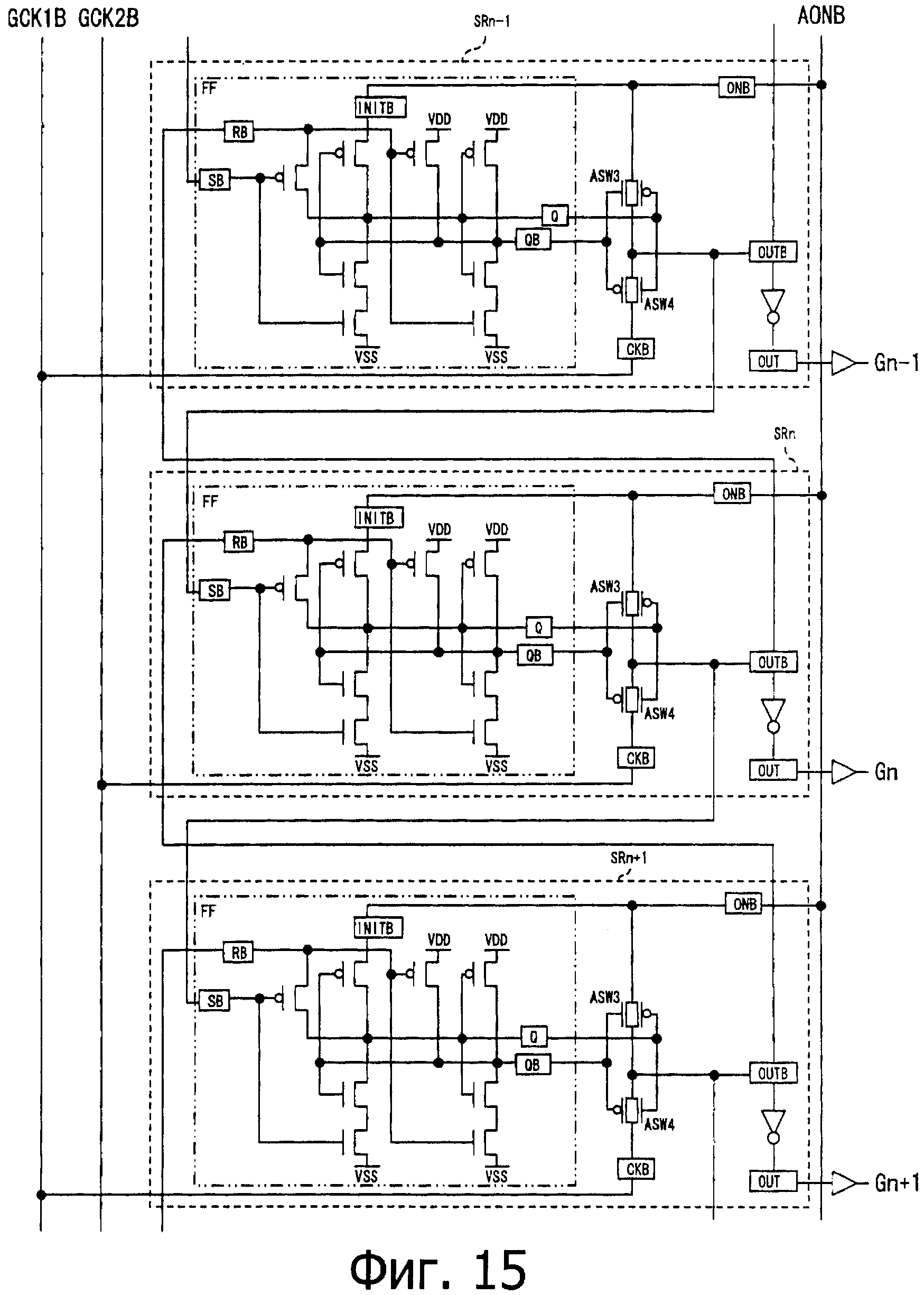

На фиг.15 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.14.

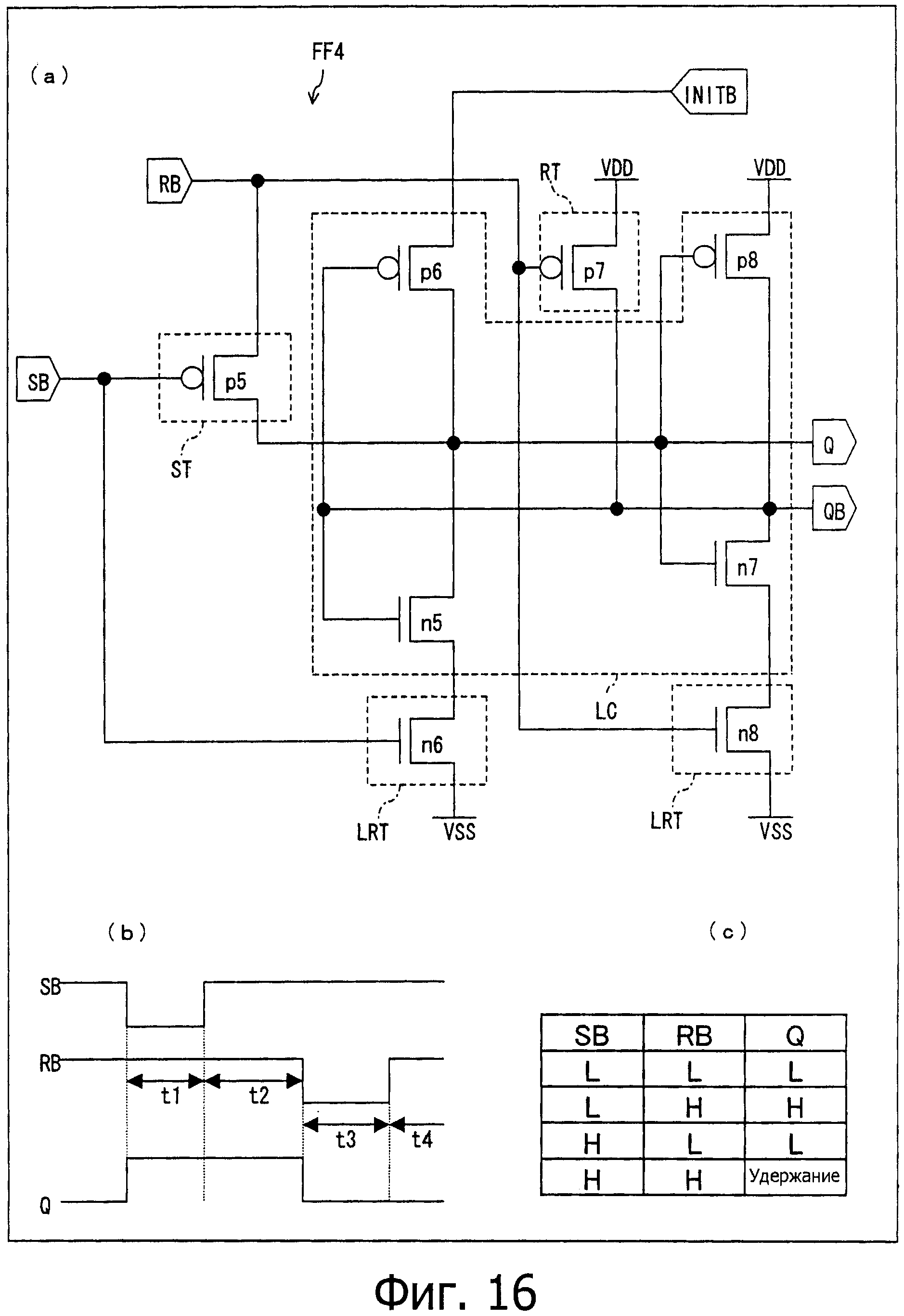

Фиг.16(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.15, (b) показана временная диаграмма операций, и (с) показана таблица истинности для триггера.

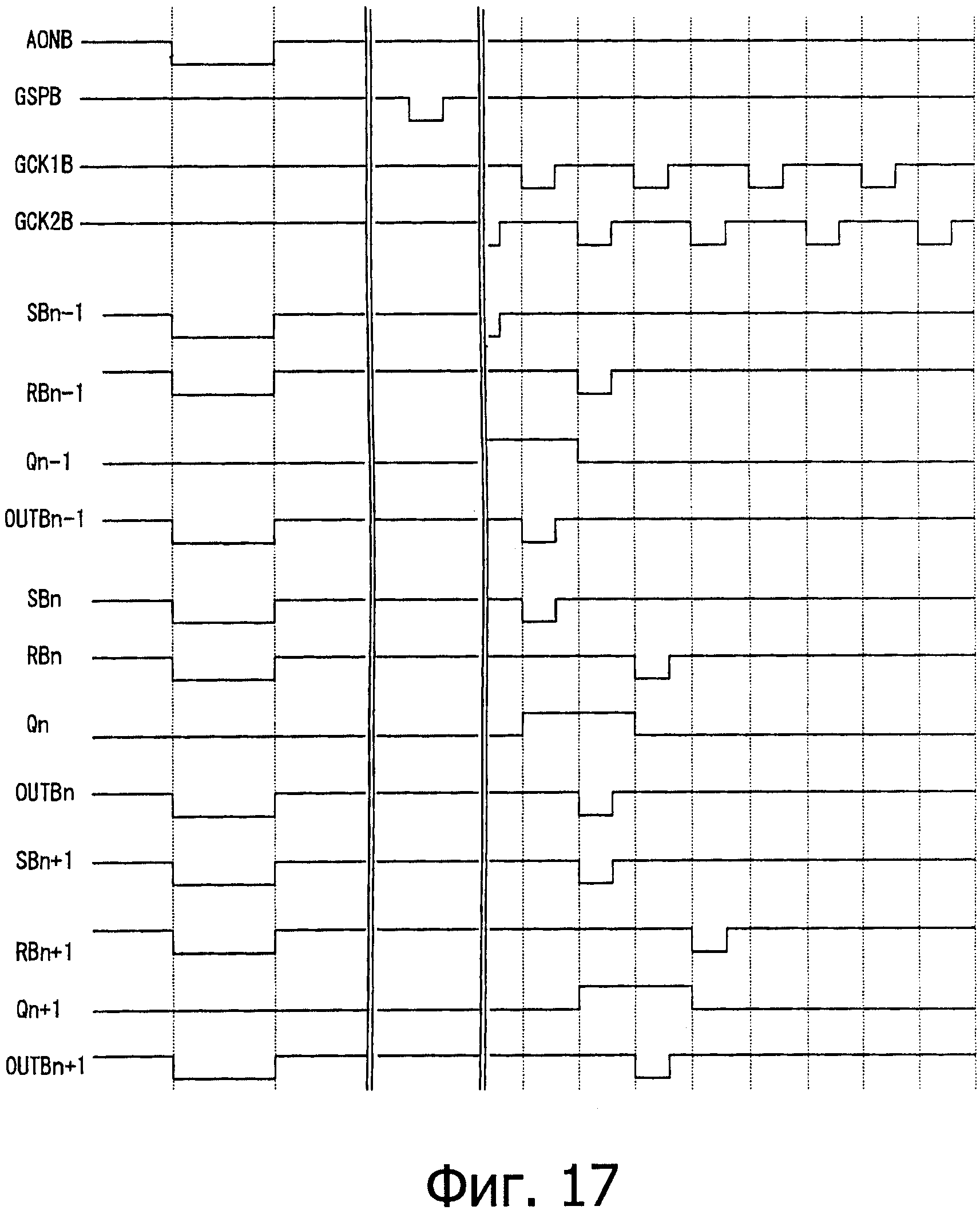

На фиг.17 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.14 при включении.

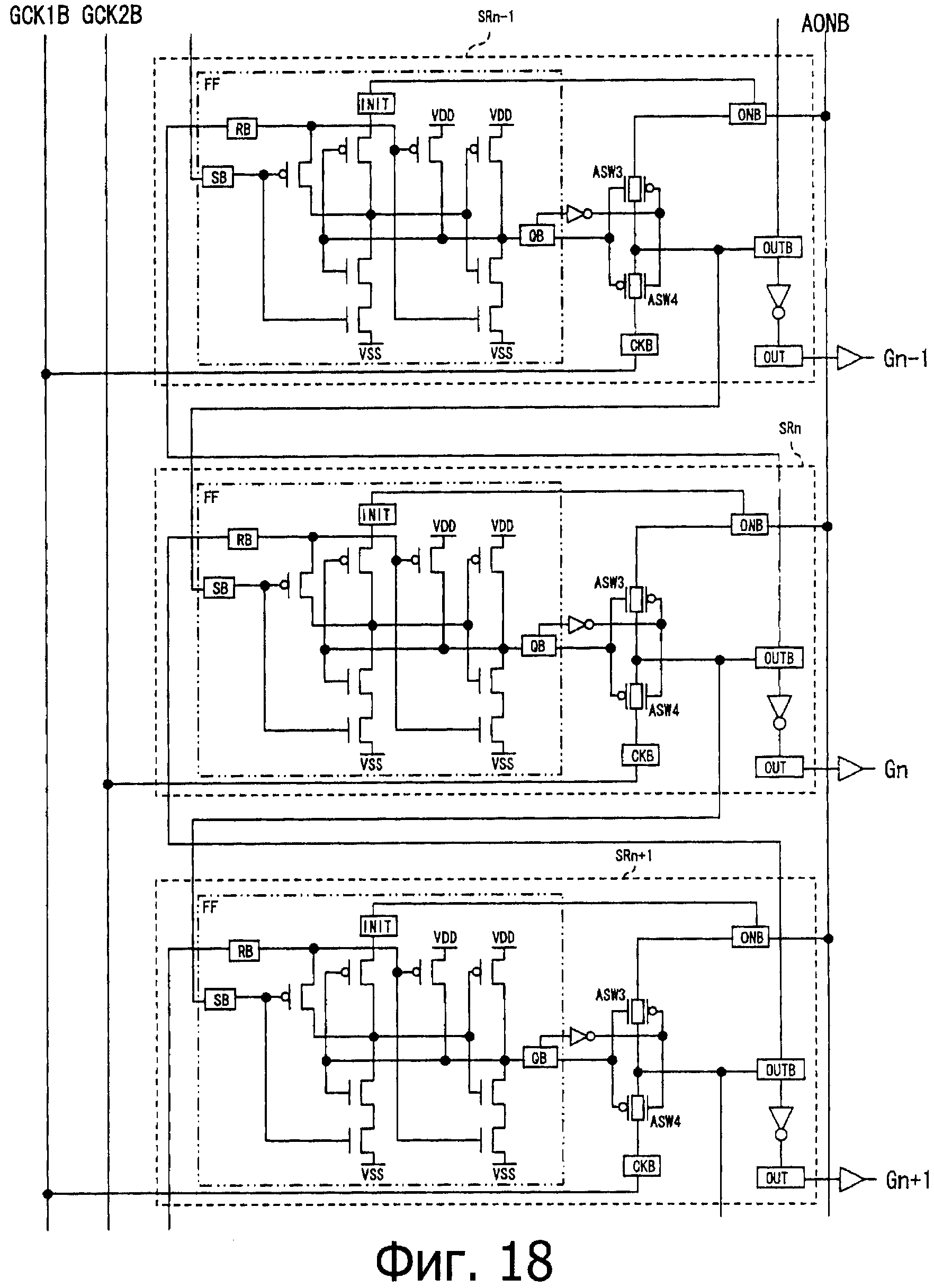

На фиг.18 показана принципиальная схема, иллюстрирующая вариант сдвигового регистра, представленного на фиг.15.

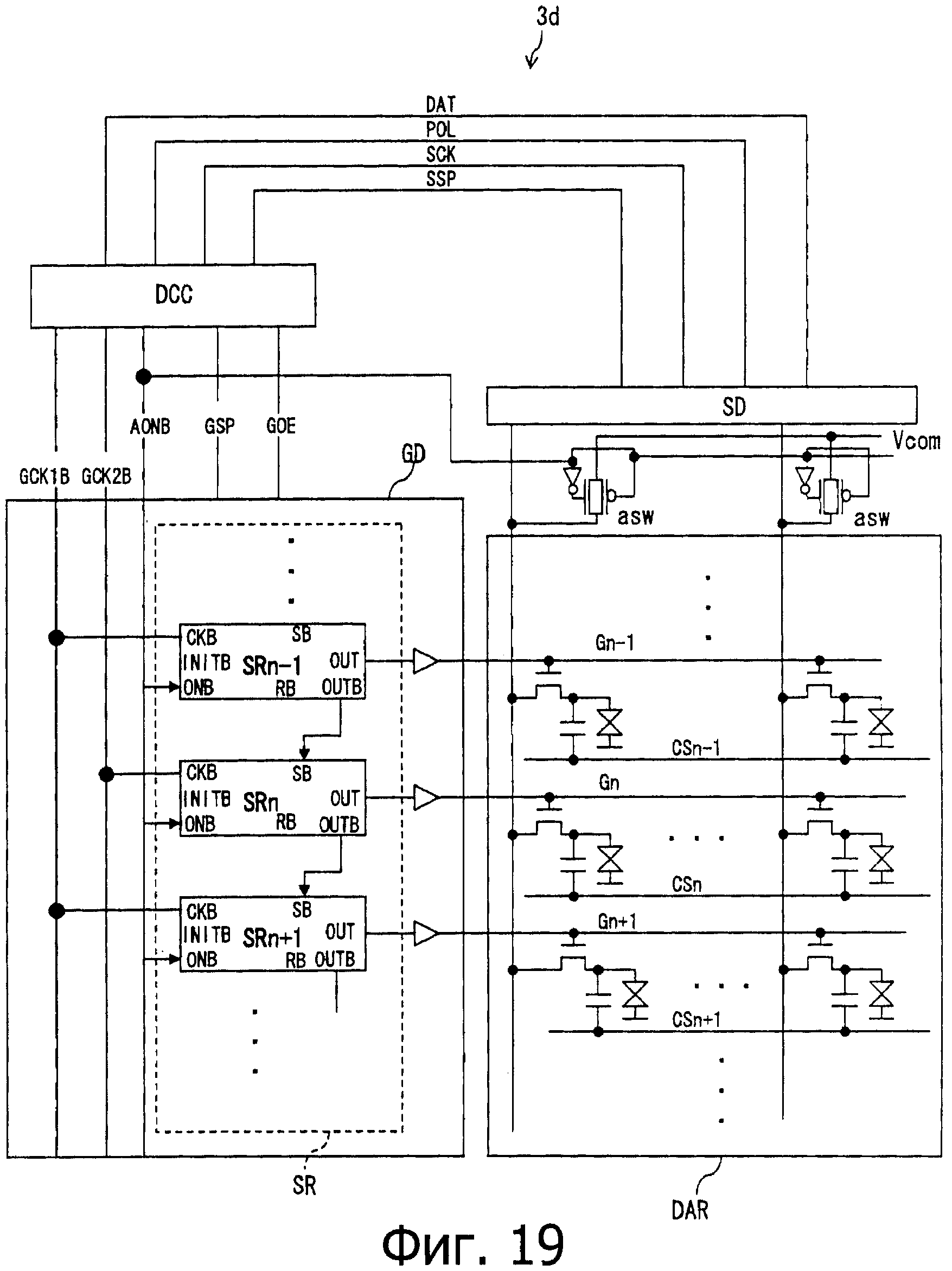

На фиг.19 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 2 осуществления.

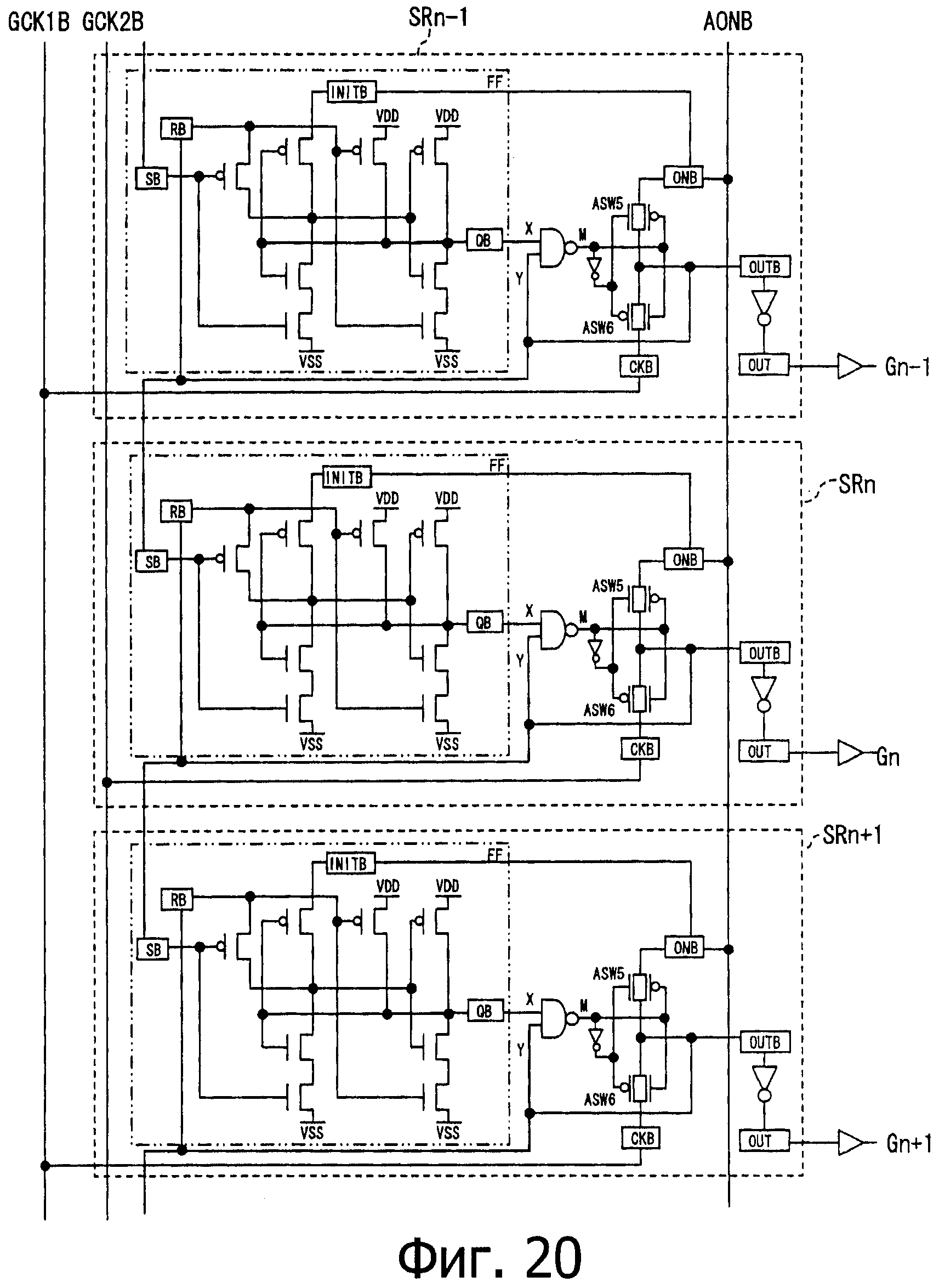

На фиг.20 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.19.

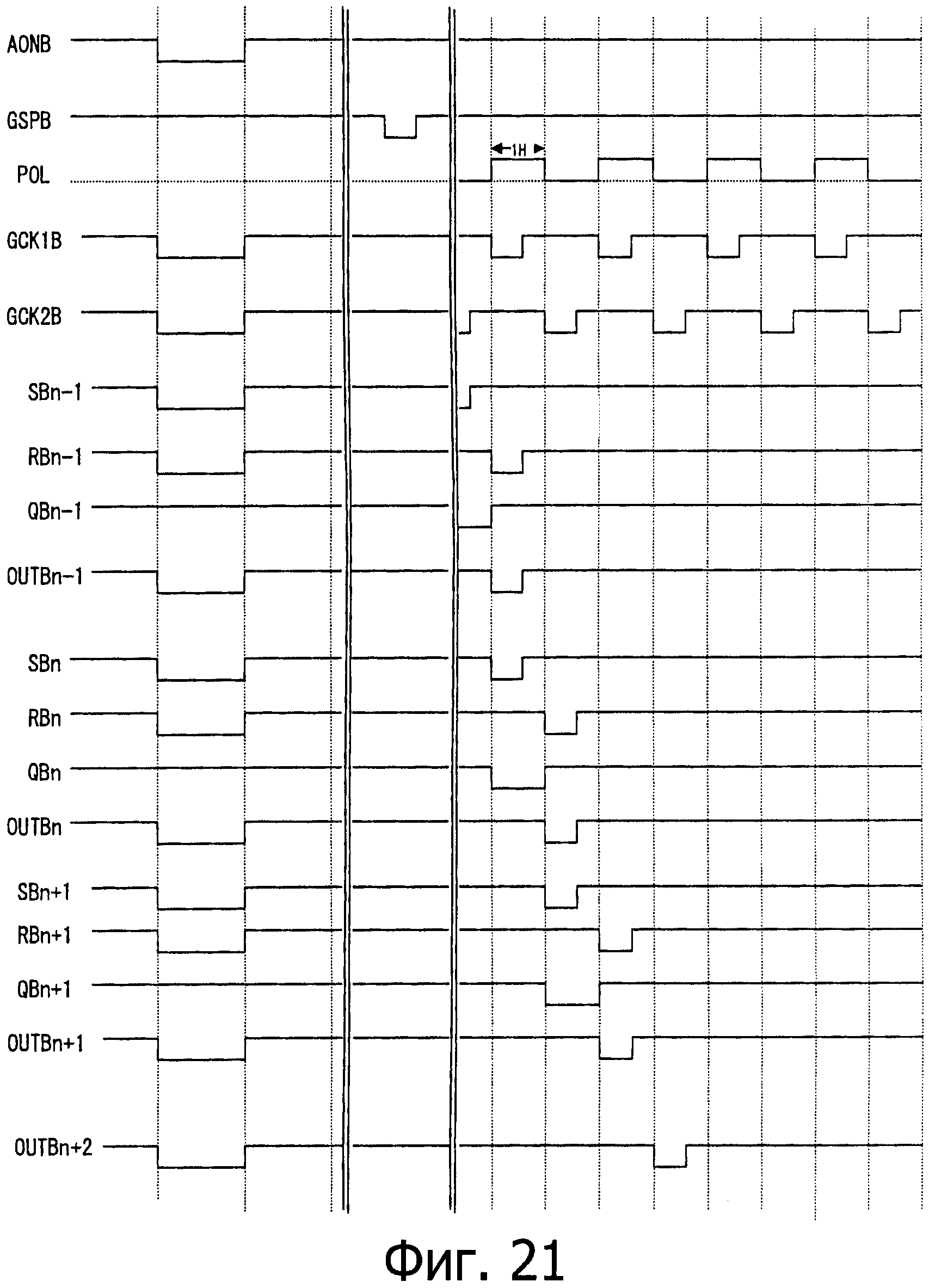

На фиг.21 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея фиг.19 при включении.

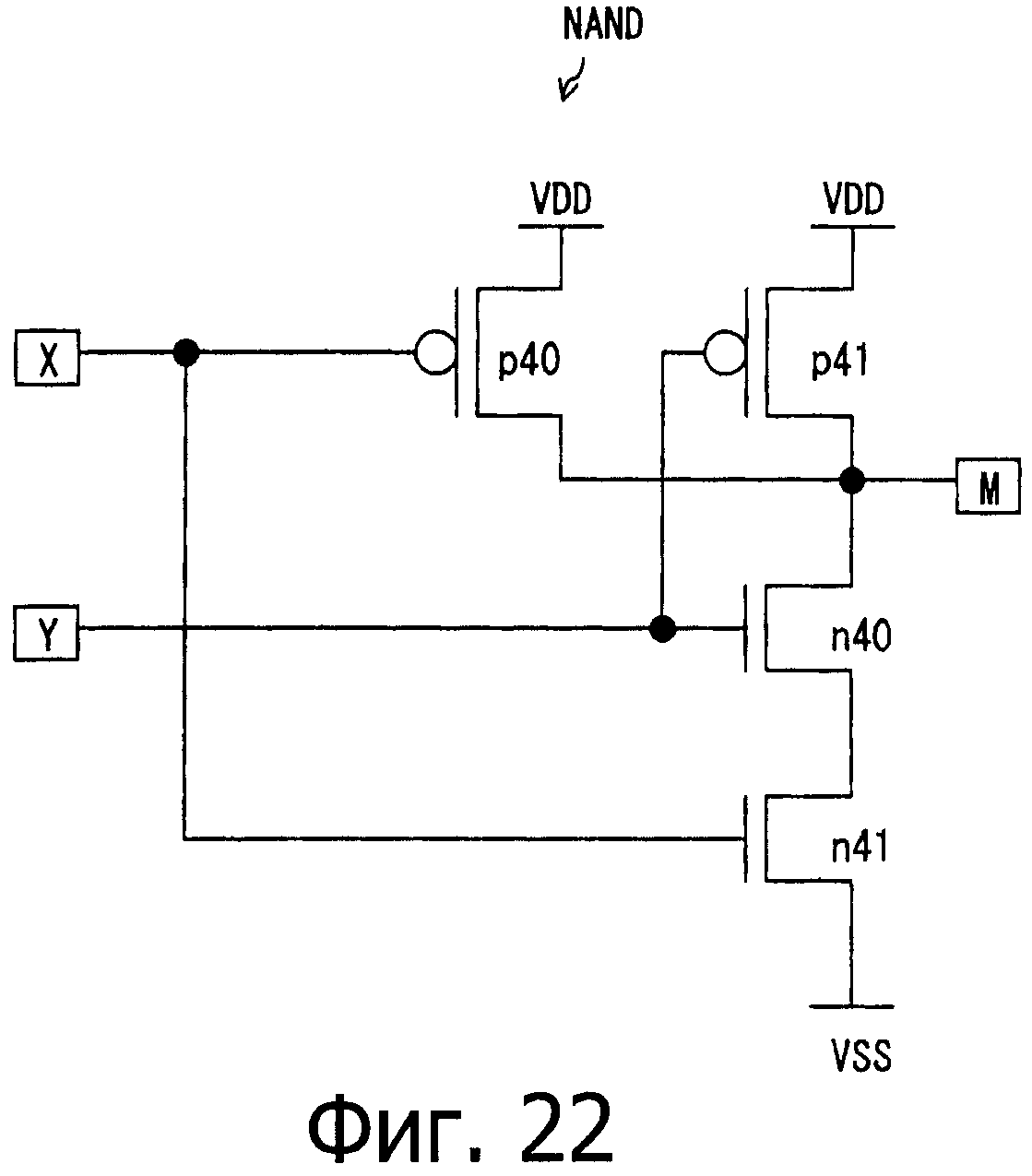

На фиг.22 показана принципиальная схема, иллюстрирующая детальную конфигурацию (НЕ-И) по фиг.20.

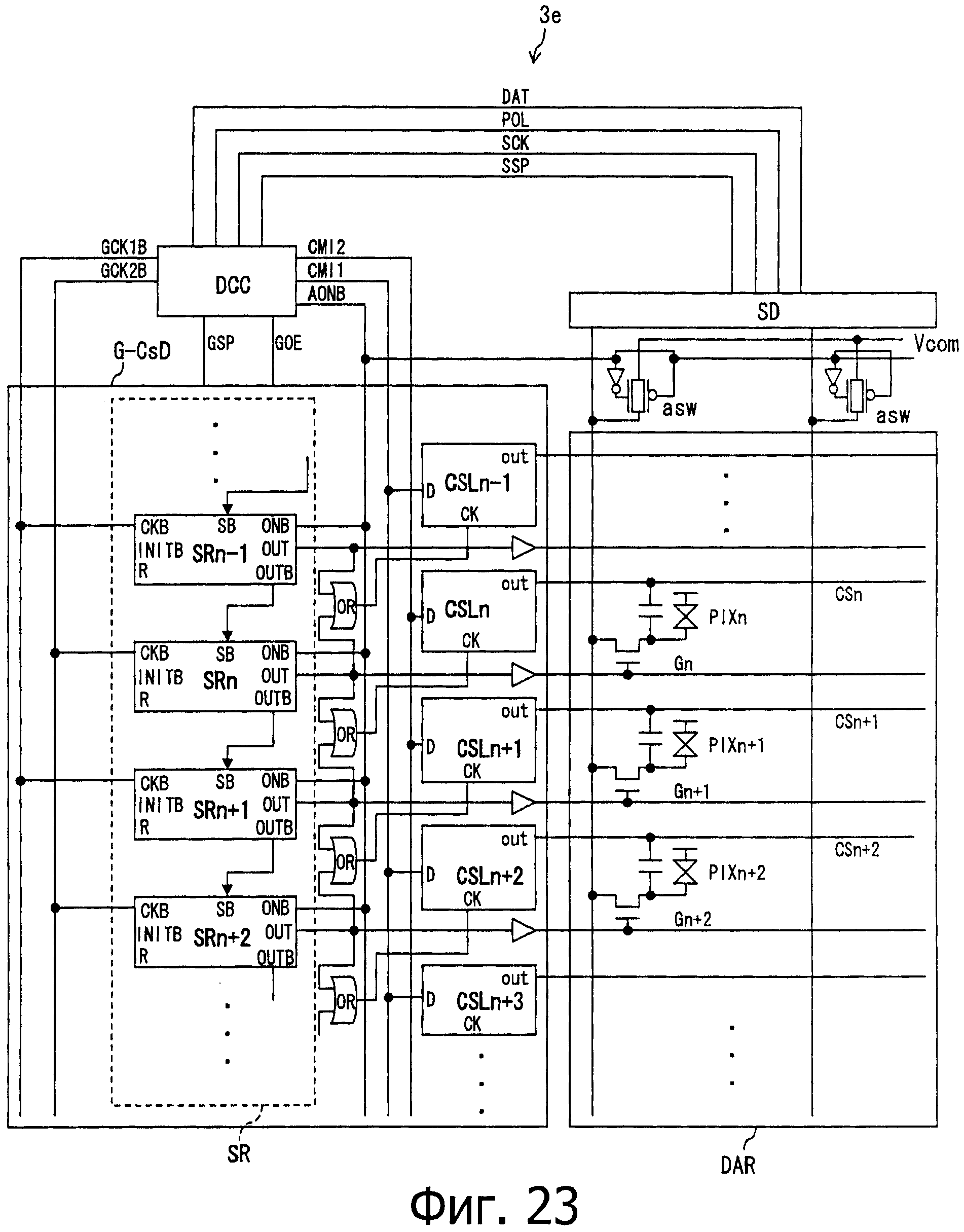

На фиг.23 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 3 осуществления.

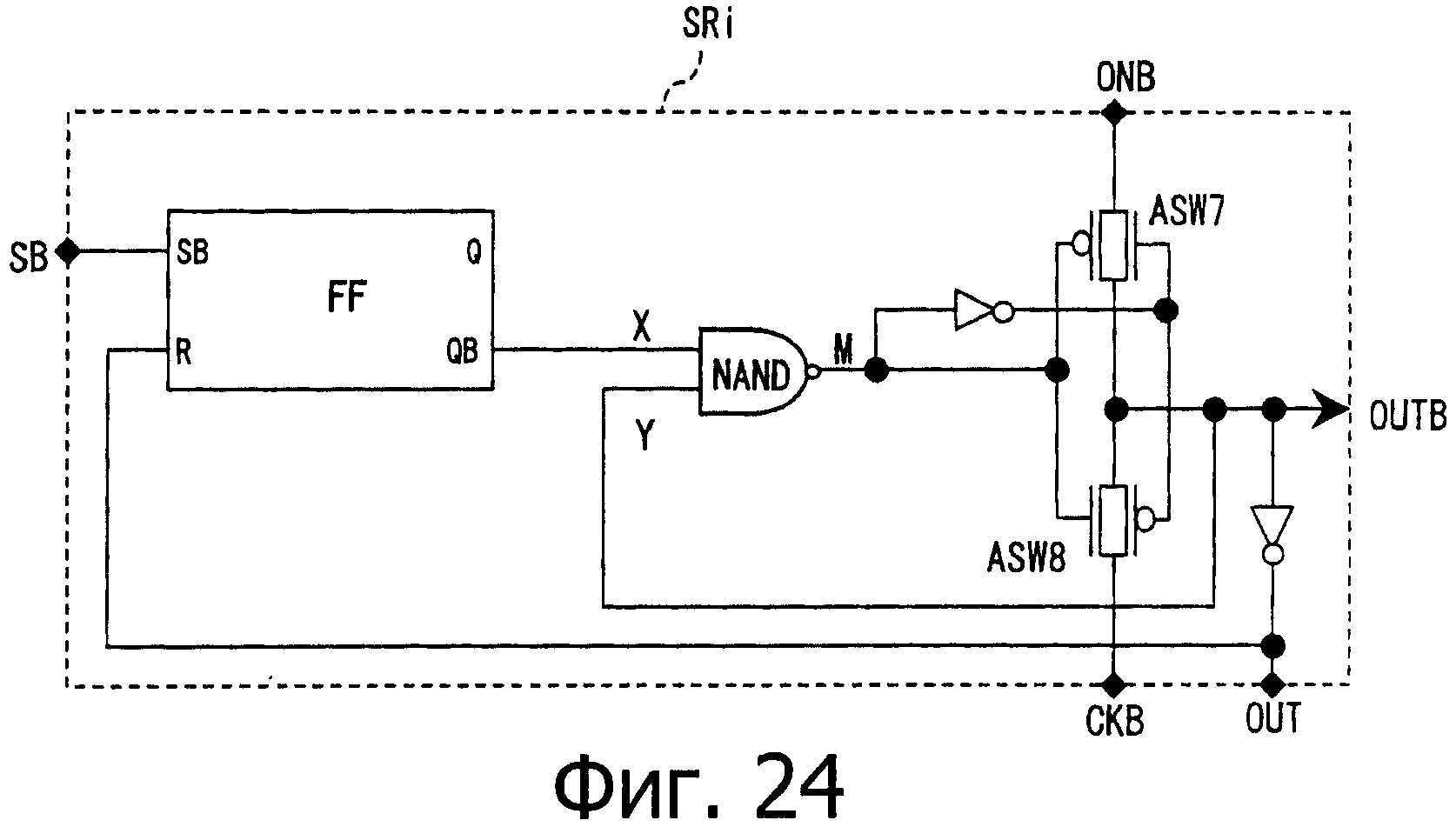

На фиг.24 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.23.

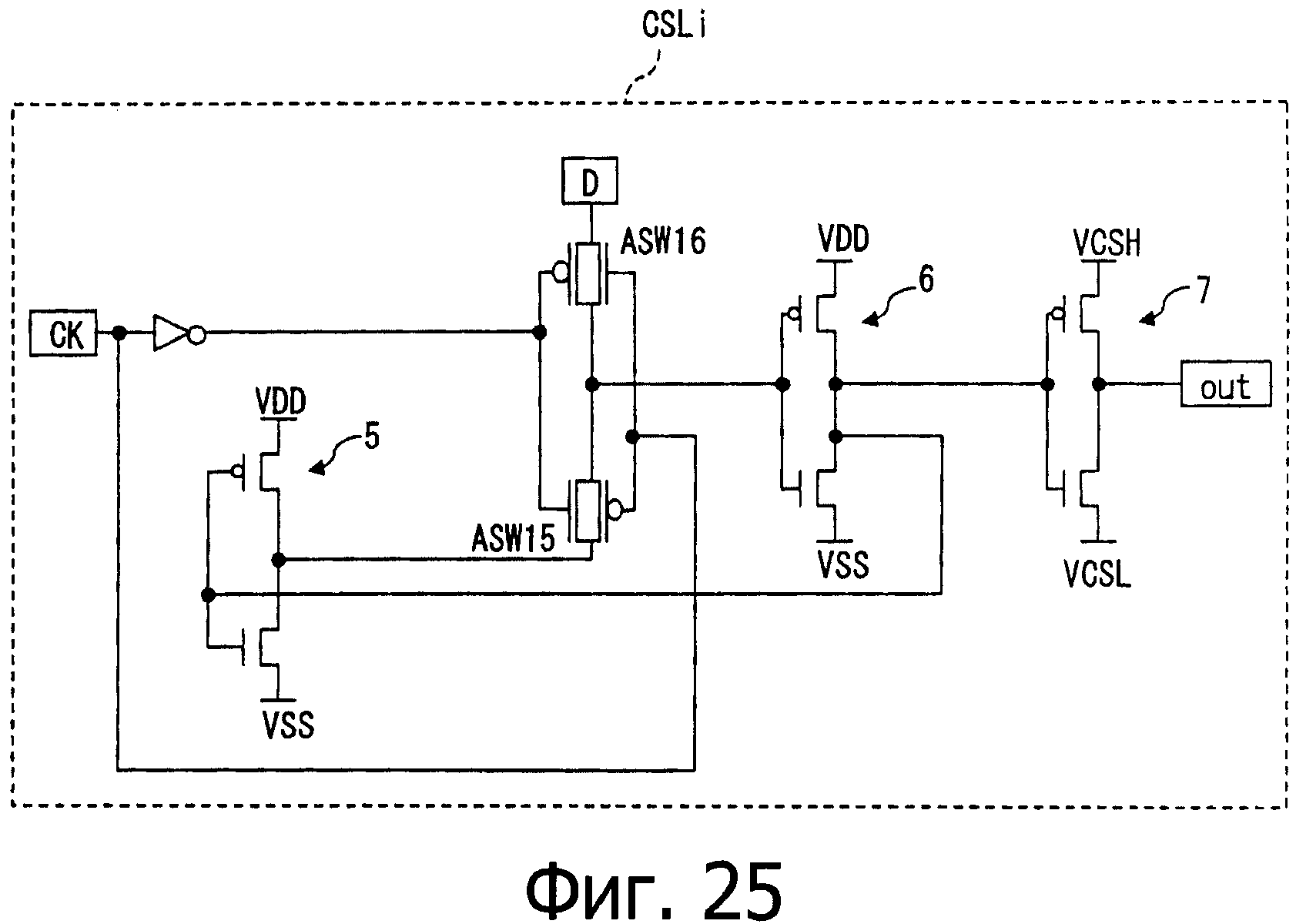

На фиг.25 показана принципиальная схема, иллюстрирующая схему D-защелки схемы G-CS (блок наведения и управления) управления устройства жидкокристаллического дисплея, представленного на фиг.23.

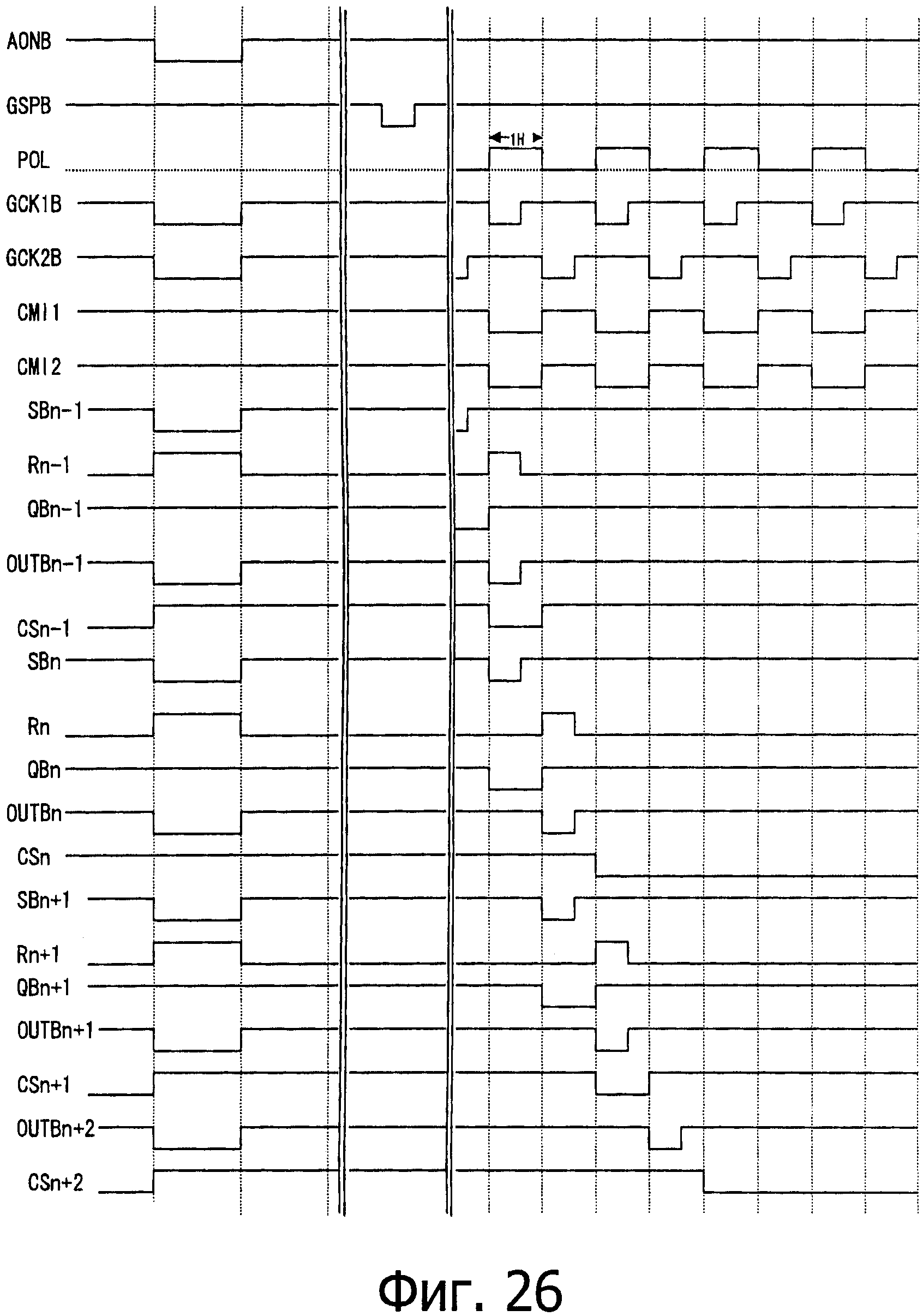

На фиг.26 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея по фиг.23.

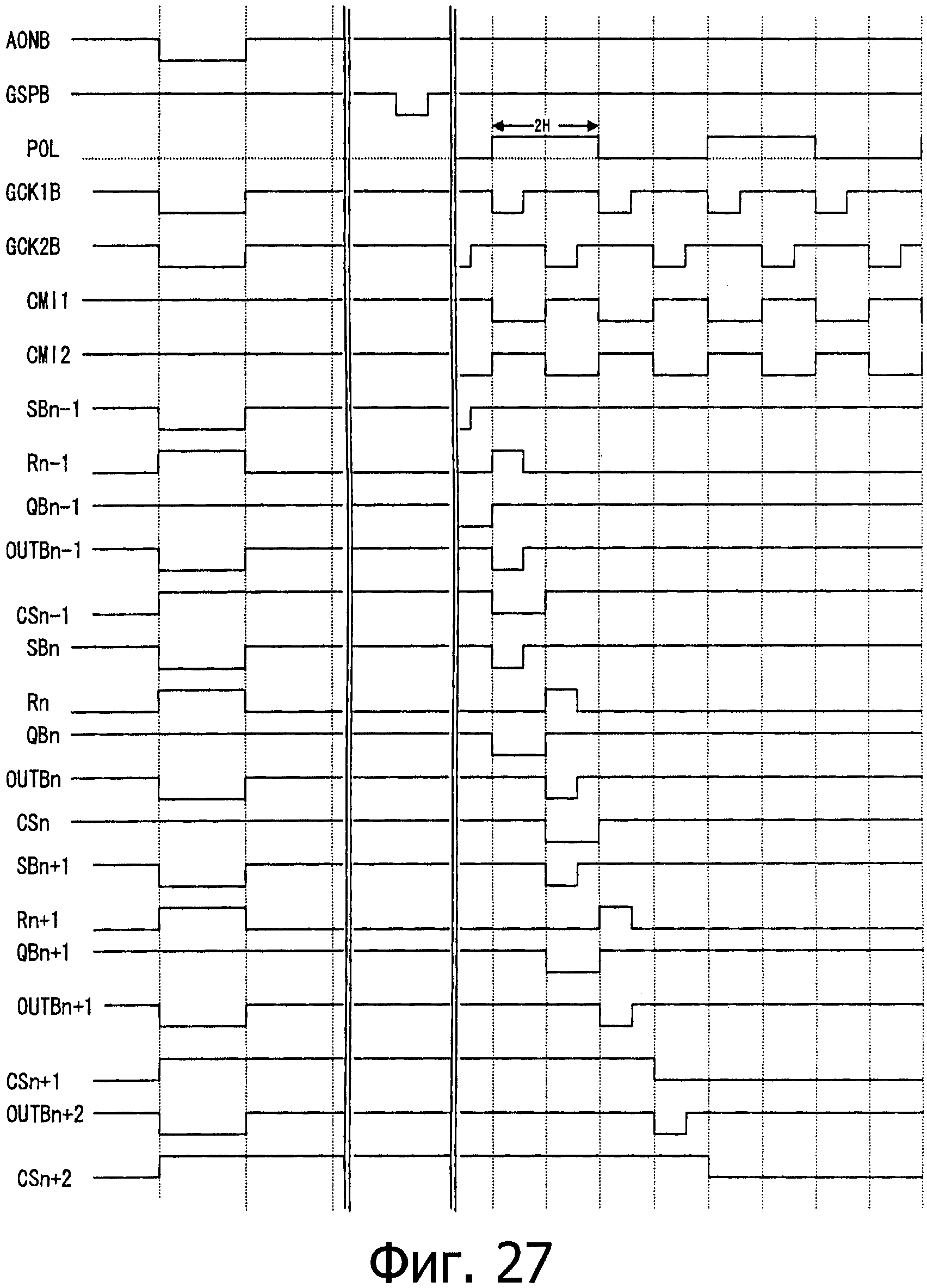

На фиг.27 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.23.

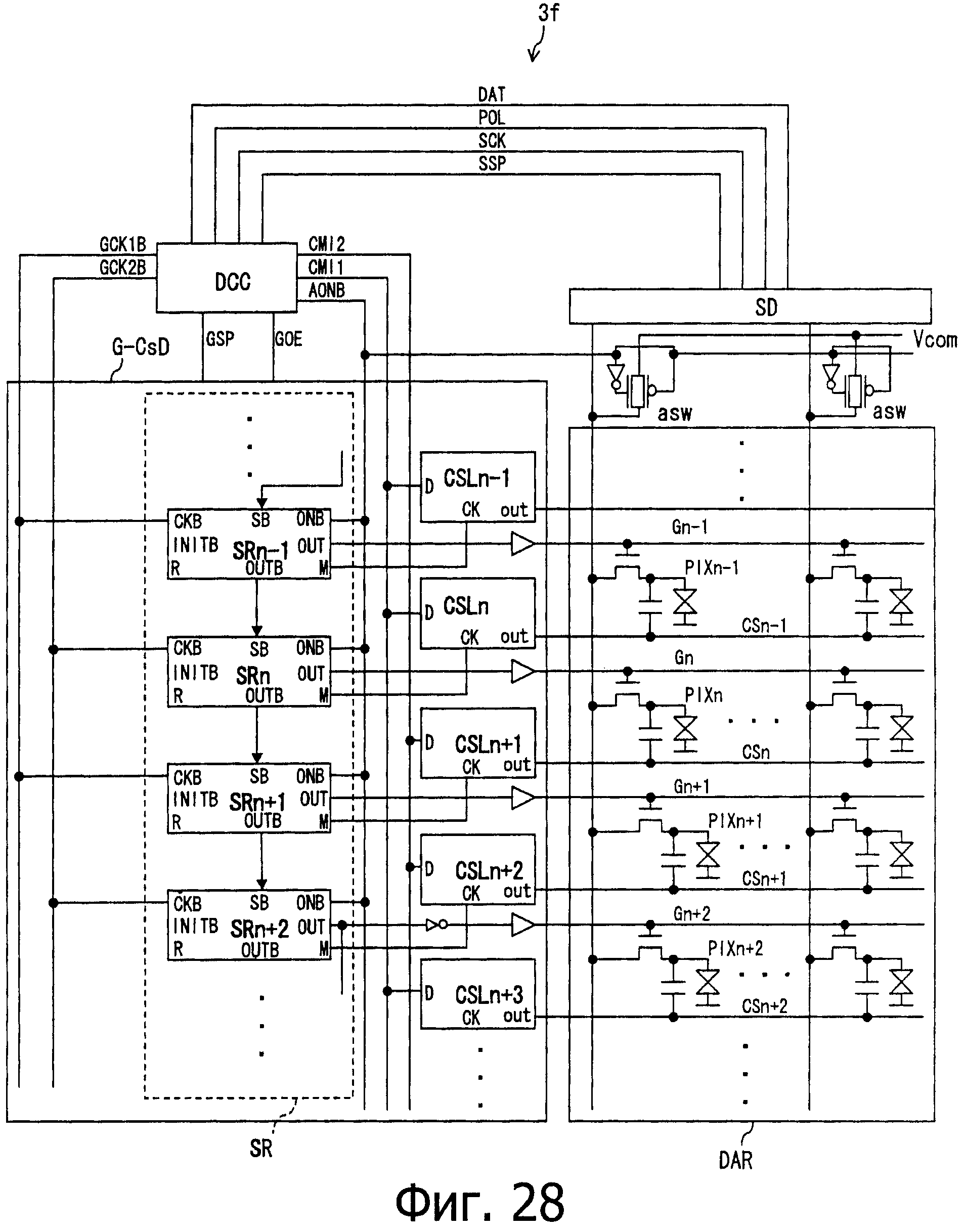

На фиг.28 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 4 осуществления.

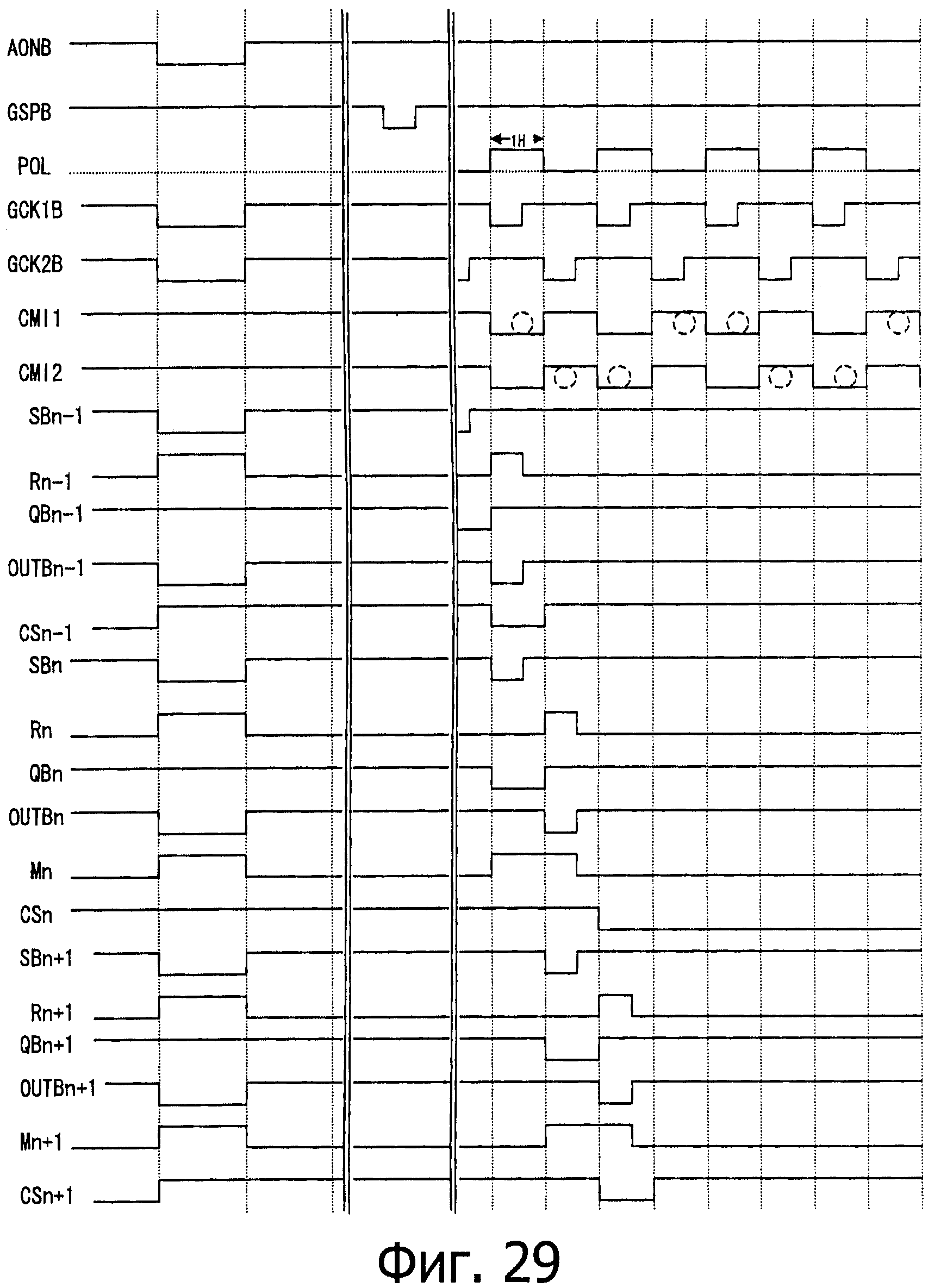

На фиг.29 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.28.

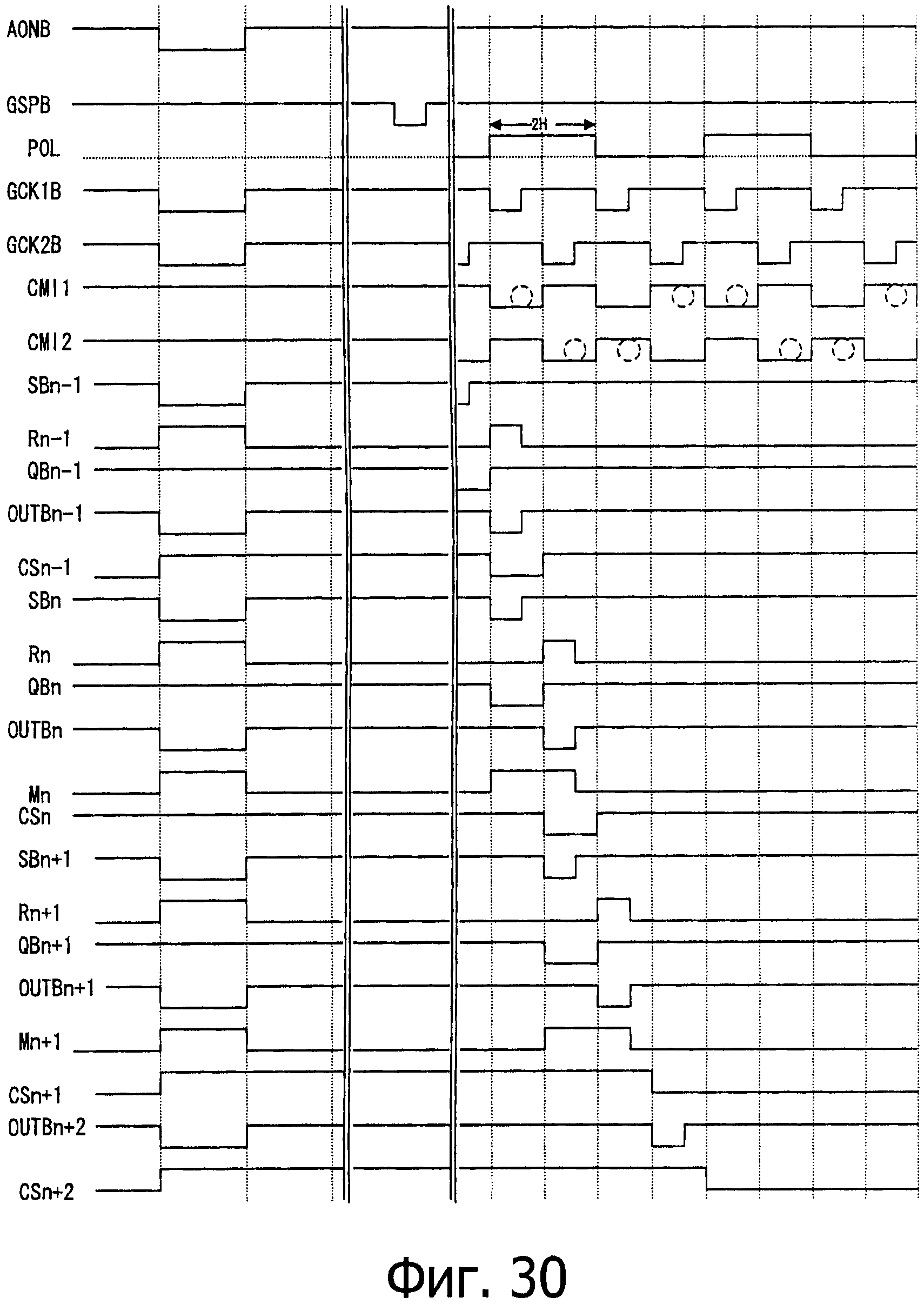

На фиг.30 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.28.

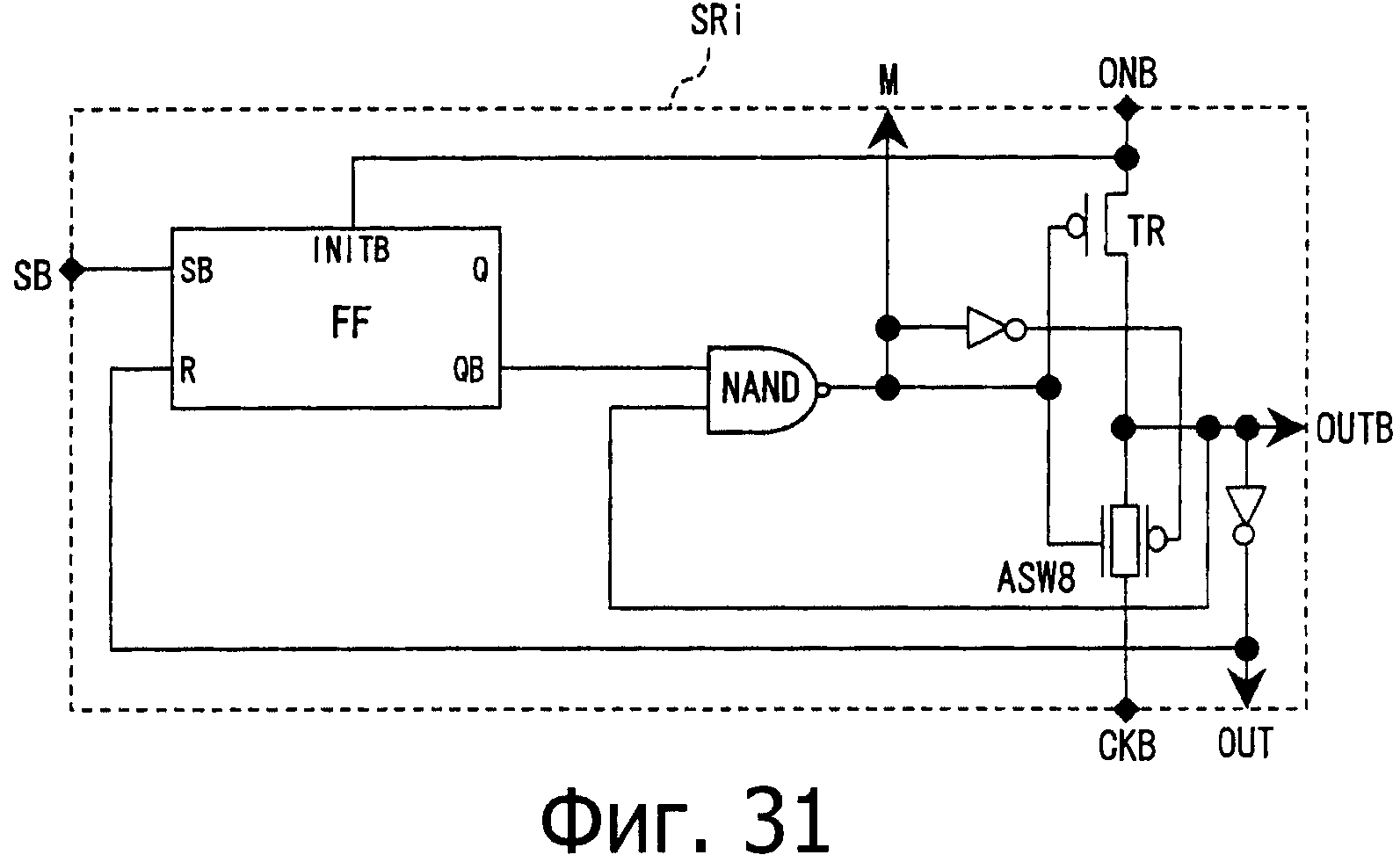

На фиг.31 показана принципиальная схема, иллюстрирующая пример конфигурации каждого каскада сдвигового регистра.

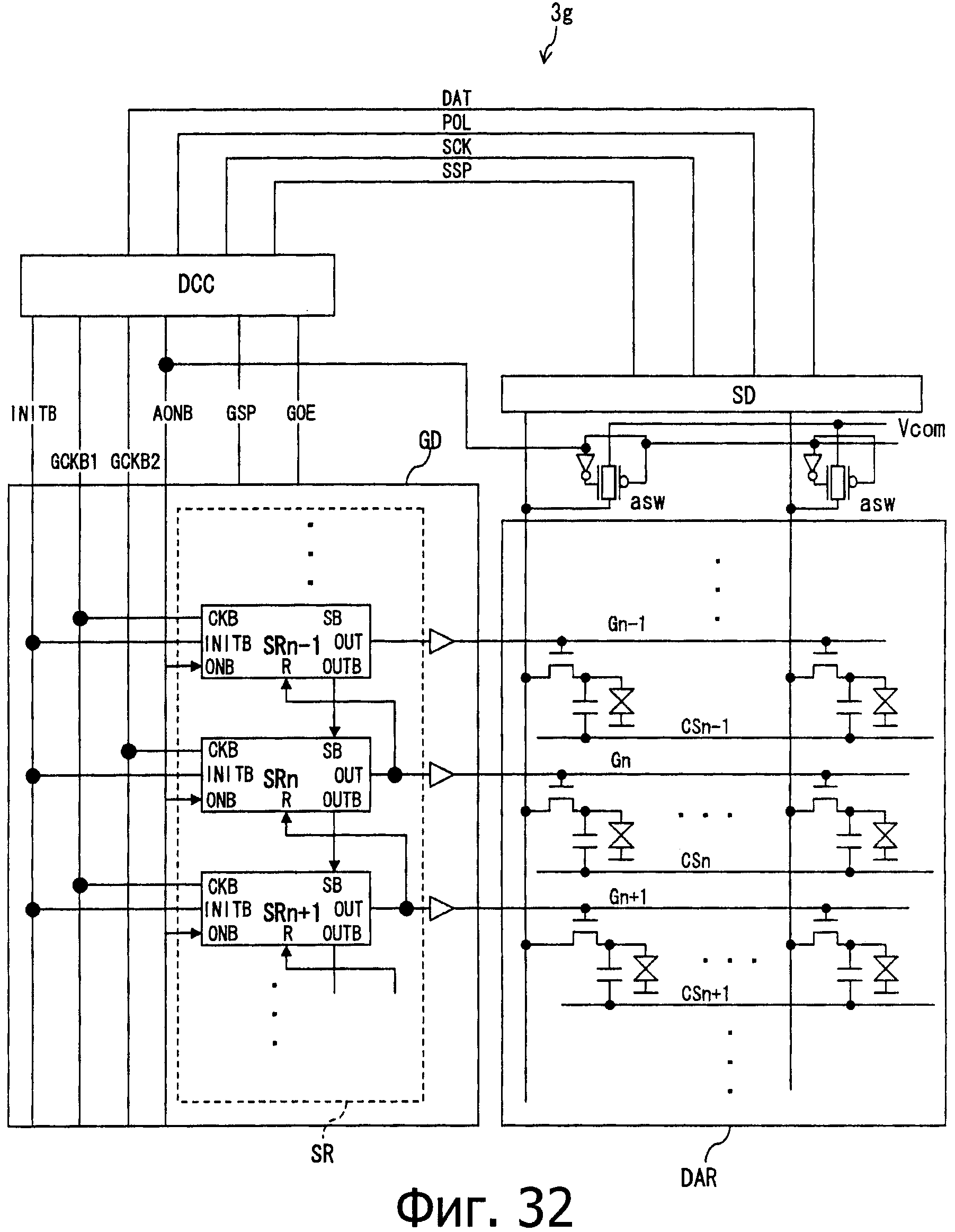

На фиг.32 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 5 осуществления.

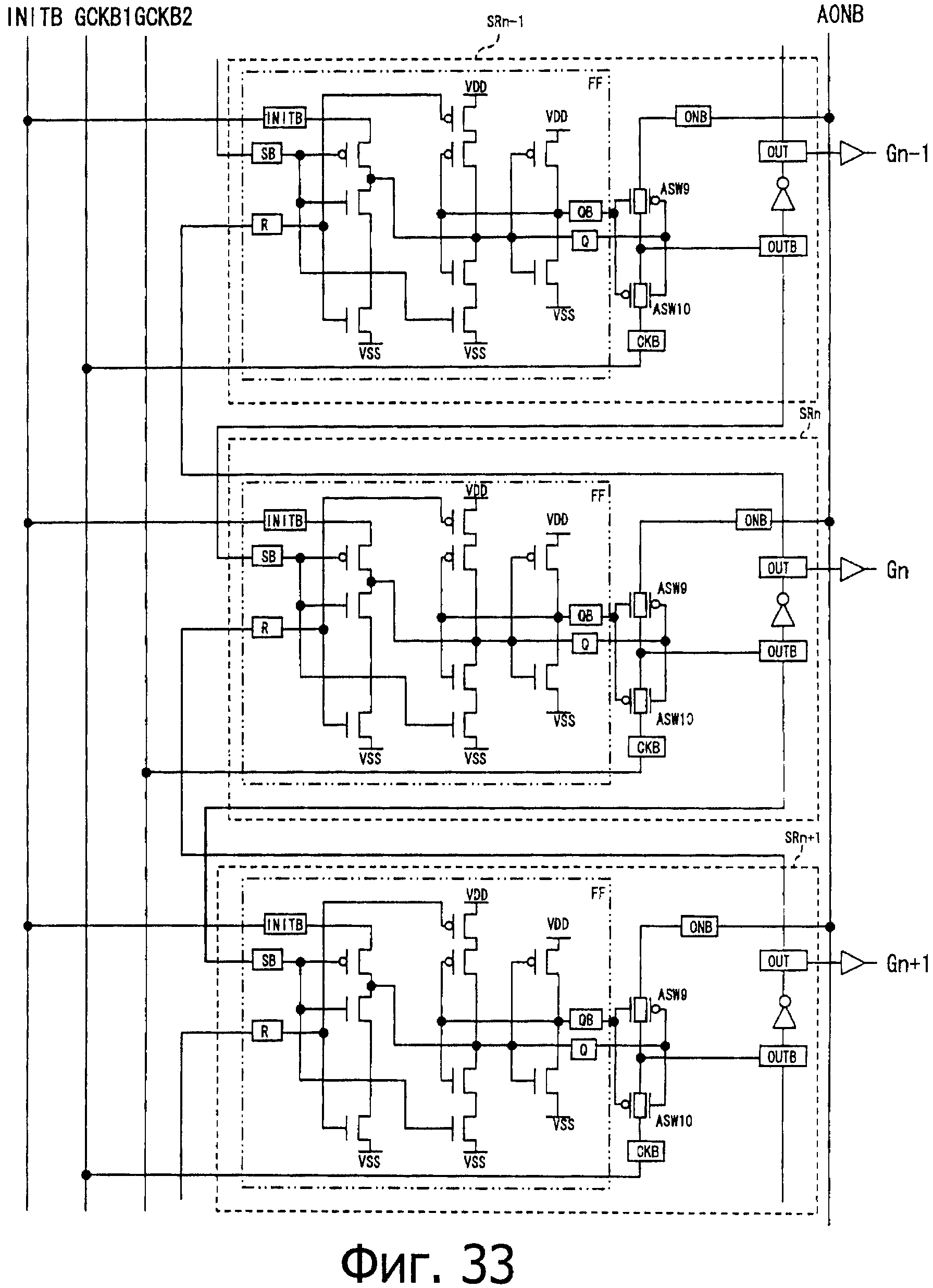

На фиг.33 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.32.

На фиг.34 показана принципиальная схема, иллюстрирующая конфигурацию обычного сдвигового регистра.

Осуществление изобретения

Варианты осуществления настоящего изобретения описаны ниже со ссылкой на фиг.1-33. В описании, представленном ниже, RS-триггер (триггер с раздельной установкой 0 и 1) (ниже обозначаемый FF, соответственно) имеет (i) вывод установки единицы (вывод S или вывод SB), на который подают сигнал установки (сигнал S или сигнал SB), (ii) вывод сброса (вывод R или вывод RB), на который подают сигнал сброса (сигнал R или сигнал RB), (iii) выходной вывод (вывод Q), на который выводят сигнал Q, и (iv) вывод инвертированного выхода (вывод QB), на который выводят сигнал QB. Представленное ниже описание относится к (i) потенциалу источника питания с высоким потенциалом (VDD), такому, как Vdd (ниже называется Высоким, соответственно) и (ii) потенциалу источника питания с низким потенциалом (VSS), такому, как Vss (ниже называется Низким, соответственно). Сигнал S (сигнал установки), сигнал R (сигнал сброса) и сигнал Q (выходной сигнал), каждый представляет собой сигнал, который имеет Высокий потенциал в течение его активного периода, тогда как сигнал SB (сигнал шины установки), сигнал RB (сигнал шины сброса) и сигнал QB (инвертированный выходной сигнал), каждый представляет сигнал, который имеет Низкий потенциал в течение его активного периода.

Вариант 1 осуществления

На фиг.1 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3а жидкокристаллического дисплея в соответствии с настоящим изобретением. Устройство 3а жидкокристаллического дисплея включает в себя: блок DAR дисплея; схему GD управления затвором; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AON (сигнал одновременного выбора), импульс GSP запуска затвора, сигнал GOE разрешения включения затвора и сигналы GCK1 и GCK2 тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвора включает в себя сдвиговый регистр SR, имеющий множество каскадов. В представленном ниже описании используется, соответственно, символ i-ого каскада Sri, для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра.

Сдвиговый регистр подает из его i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки, в блок DAR дисплея через буфер. Например, сдвиговый регистр подает со своего n-ого каскада SRn сигнал OUT в линию Gn сигнала развертки через буфер. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенного с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор), вместе с линией CSn накопительного конденсатора.

Устройство 3а жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AON. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор стороны канала Р, соединенный с выходом инвертора и (И) затвор стороны канала N, соединенный с сигнальной линией AON.

На фиг.2 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR. Как показано на фиг.2, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод R и вывод INIT; два аналоговых переключателя ASW1 и ASW2; инвертор; вывод CK; вывод ON; вывод OUT; и вывод OUTB. Вывод INIT триггера FF соединен с выводом ON. Вывод Q триггера FF соединен с затвором на стороне канала Р аналогового переключателя ASW1 и с затвором на стороне канала N аналогового переключателя ASW2. Вывод QB FF соединен с затвором на стороне канала N аналогового переключателя ASW1 и с затвором на стороне канала Р аналогового переключателя ASW2. Аналоговый переключатель ASW1 имеет первый электропроводный электрод, соединенный с выводом ON, тогда как аналоговый переключатель ASW2 имеет первый электропроводный электрод, соединенный с выводом CK. Аналоговый переключатель ASW1 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW2 и с выводом OUT, который представляет собой выходной вывод каскада. Вывод OUT соединен с выводом OUTB через инвертор.

Сдвиговый регистр SR выполнен таким образом, что вывод OUTB первого каскада соединен с выводом SB его следующего второго каскада и, что вывод OUT второго каскада соединен с выводом R первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, тогда как вывод OUT (n+1)-ого каскада SRn+1 соединен с выводом R n-ого каскада SRn. Сдвиговый регистр SR имеет свой исходный каскад SR1, имеющий вывод SB, на который подают сигнал GSPB. Схема GD управления затвором выполнена таким образом, что вывод ON каждого каскада соединен с сигнальной линией AON, и что вывод CK каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают GCK), которая отличается от линии GCK, с которой соединен вывод CK каждого каскада с четным номером. Например, вывод CK n-ого каскада SRn соединен с сигнальной линией GCK2, тогда как вывод CK (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1.

Триггер FF на фиг.2 представляет собой FF1, показанный на фиг.3. Как показано на фиг.3, FF1 включает в себя: транзистор р84 с Р каналом и транзистор п84 с N каналом, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор п85 с N каналом, составляющие схему КМОП; транзисторы р81, р82 и р83 с Р каналом; транзисторы n82, n83 и n99 с N каналом; вывод SB; вывод R; и выводы Q, и QB. р84 имеет затвор, соединенный с затвором n84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком n84, стоком р81, стоком n82, затвором р85, затвором n85, стоком n99 и выводом Q. n84 имеет исток, соединенный со стоком n83. У р84 есть исток, соединенный со стоком р83. р81 имеет исток, соединенный со стоком р82. Вывод INIT соединен с затвором n99. Вывод SB соединен с затвором р81 и затвором n83. Вывод R соединен с затвором n82, затвором р82 и затвором р83. n85 имеет исток, соединенный с VSS. р82, р83 и р85, каждый имеет исток, соединенный с VDD. n82, n99 и n83, каждый имеет исток, соединенный с VSS. В FF1 р84, n84, р85 и n85 составляют схему LC защелки;

р81 используется, как транзистор ST установки; n82 используется, как транзистор RT сброса; р83 и n83, каждый используется, как транзистор LRT освобождения защелки; и р82 используется, как транзистор PDT определения приоритета.

(b) На фиг.3 показана таблица истинности для FF1. Как показано в позиции (b) на фиг.3, сигнал Q FF1 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (ii) сохраняет текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (in) является Низким (неактивным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF1, в случае, когда сигнал SB и сигнал R оба становятся активными, в то время когда вывод INIT является Высоким (активным), n82, n99 и р85 включают так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным).

На фиг.4-6 показаны временные диаграммы, иллюстрирующие осуществление управления устройством За жидкокристаллического дисплея, когда его включают, выключают и принудительно выключают, соответственно. На фиг.4-6 AON представляет сигнал AON (сигнал одновременного выбора); GSPB представляет сигнал шины импульса запуска затвора; GCK1 представляет сигнал GCK.1; и GCK2 представляет сигнал GCK2. Кроме того, SBi, Ri, Qi и OUTi (i=n-1, n и n+1), соответственно, представляют сигнал SB (потенциал на выводе SB), сигнал R (потенциал вывода R), сигнал Q (потенциал вывода Q) и сигнал OUT (потенциал вывода OUT) i-ого каскада SRi.

Когда устройство 3а жидкокристаллического дисплея включают и выключают, выполняется операция подготовки. В частности, операция подготовки делает сигнал AON активным (Высоким) в течение заданного периода. Поскольку ASW1 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким), в результате активации, таким образом, что выбирают все линии сигнала развертки. Кроме того, аналоговый переключатель asw, соответствующий каждой линии сигнала данных, включается в результате активации сигнала AON, так, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INIT, в который подают сигнал AON, становится активным (Высоким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания описанной выше операции подготовки (то есть, после того, как сигнал AON станет неактивным), устройство 3а жидкокристаллического дисплея достигает состояния, в котором Vcom было записано в каждый PIX в блоке DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера в каждом каскаде стал неактивным).

Сдвиговый регистр SR устройства 3а жидкокристаллического дисплея выполняет следующую операцию в течение каждого периода вертикальной развертки (то есть, во время отображения каждого кадра): Когда сигнал SB, подаваемый в первый каскад, становится активным (=Низким), FF первого каскада устанавливается в единицу. Это обеспечивает Высокое (активное) состояние сигнала Q, и первый каскад в свою очередь принимает сигнал GCK через аналоговый переключатель ASW2. Когда сигнал GCK, подаваемый в первый каскад, становится активным (Высоким), сигнал OUT первого каскад становится активным (Высоким), и сигнал SB следующего второго каскада также становится активным. Это приводит к тому, что сигнал FF второго каскада становится активным, и второй каскад, в свою очередь, принимает сигнал GCK. Когда сигнал GCK второго каскада становится активным (Высоким), происходит сброс FF первого каскада. Это приводит к тому, что сигнал Q первого каскада становится Низким (неактивным) и включает аналоговый переключатель ASW1 первого каскада. Поскольку сигнал AON является Низким в этот момент времени, сигнал OUT первого каскад также становится Низким (неактивным).

Устройство 3а жидкокристаллического дисплея, когда его включают и выключают, одновременно выбирает все линии сигнала развертки таким образом, что идентичный потенциал (например, Vcom) записывают во все пиксели. Это предотвращает нарушение изображения, вызванное включением и выключением устройства 3а жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), в настоящей компоновке (i) сигнал AON подают в ASW1, для устранения элемента НЕ-И на фиг.34, который принимает выходной сигнал каждого каскада и (ii) подает сигнал AON на вывод INIT каждого FF, для устранения необходимости в компоненте, который генерирует и передает сигнал для инициализации сдвигового регистра. Это позволяет уменьшить размеры схемы управления затвором. Кроме того, в настоящей компоновке сдвиговый регистр инициализируется (то есть, инициализируется триггер каждого каскада) при одновременном выборе всех линий сигнала развертки. Настоящая компоновка, таким образом, позволяет закончить операцию подготовки более быстро, чем в обычной компоновке, в которой по-отдельности выполняется одновременный выбор всех линий сигнала развертки и инициализация сдвигового регистра.

На фиг.7 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3b жидкокристаллического дисплея, которая включает в себя сдвиговый регистр SR по фиг.1 в схеме управления истоком. Такая конфигурация обеспечивает (i) прием исходным каскадом сдвигового регистра SR импульса SSP запуска истока и (ii) прием выводом CK каждого каскада сигнала SCK1 или SCK.2 шины тактовой частоты истока. Сигнал OUT i-ого каскада SRi подают в схему SAC выборки. Затем данные, выборка которых была выполнена на основе сигнала OUT, подают в линию SLi сигнала данных блока DAR дисплея через DAC. Например, сигнал OUT n-ого каскада SRn подают в схему SAC выборки, и данные, подаваемые на основе сигнала OUT, затем подают в линию SLn сигнала данных блока DAR дисплея через DAC. Линия SLn сигнала данных в блоке DAR дисплея, соединена с истоком транзистора, который соединен с электродом пикселя в PIXn.

Каждый каскад устройства 3а жидкокристаллического дисплея может быть выполнен, как показано на фиг.8. На фиг.8 иллюстрируется триггер FF, который представляет собой FF2, показанный на фиг.9. Как показано на фиг.9, триггер FF2 включает в себя: транзистор р84 с Р каналом и транзистор n84 с N каналом, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор п85 с N каналом составляют схему КМОП; транзисторы р82, р83, р86 и р87 с Р каналом; транзисторы n81, n82, n83 и n88 с N каналом; вывод SB; вывод R; и выводы Q и QB. р84 имеет затвор, соединенный с затвором n84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком n84, стоком р82, стоком n81, затвором р85, затвором n85, стоком n88 и выводом Q. n84 имеет исток, соединенный со стоком п83. р84 имеет исток, соединенный со стоком р83. р83 имеет исток, соединенный со стоком р87. р82 имеет исток, соединенный со стоком р86. n81 имеет исток, соединенный со стоком р82. Вывод INIT соединен с соответствующими затворами п88, р86 и р87. Вывод SB соединен с затвором р82, затвором n81 и затвором n83. Вывод R соединен с затвором n82 и затвором р83. n85 имеет исток, соединенный с VSS. р86, р87 и р85, каждый имеет исток, соединенный с VDD. n82, n88 и n83, каждый имеет исток, соединенный с VSS.

В позиции (b) на фиг.9 показана таблица истинности для FF2. Как показано в позиции (b) на фиг.9, сигнал Q FF2 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (ii) сохраняет текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (iii) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF2, в случае, когда оба сигнал SB и сигнал R становятся активными, в то время как вывод INIT является Высоким (активным), р86 и р87 выключаются, и п88, и р85 включаются так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным).

Когда устройство 3а жидкокристаллического дисплея, имеющее конфигурацию по фиг.8 включают и выключают, выполняют операцию подготовки. В частности, операция подготовки делает сигнал AON активным (Высоким) в течение заданного периода. Поскольку ASW1 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким) в результате активации, таким образом, что выбирают все линии сигнала развертки. Кроме того, аналоговый переключатель asw, соответствующий каждой линии сигнала данных, включают в результате активация сигнала AON, таким образом, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INIT, на который подают сигнал AON, становится активным (Высоким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания представленной выше операции подготовки (то есть, после того, как сигнал AONB становится неактивным), устройство 3а жидкокристаллического дисплея достигает состояния, в котором Vcom было записано в каждый PIX в блоке DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера каждого каскада стал неактивным).

Компоновка, показанная на фиг.8, обеспечивает установку триггера FF так, что она имеет приоритет по сравнению с его сбросом. Таким образом, когда одновременный выбор заканчивается (то есть, когда сигнал AON возвращается из активного состояния в неактивное состояние), сигнал SB, более вероятно, становится неактивным до сигнала R. Компоновка, показанная на фиг.8, таким образом, предотвращает неправильную работу, то есть, предотвращает выполнение сдвиговым регистром, после его инициализации, операции установки, в результате того, что сигнал R становится неактивным прежде, чем сигнал SB.

На фиг.10 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3х жидкокристаллического дисплея. Устройство 3х жидкокристаллического дисплея включает в себя: блок DAR дисплея; схему GD управления затвором; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AONB (сигнал одновременного выбора), импульс GSP запуска затвора, сигнал СОЕ разрешения включения затвора и сигналы GCK1 и GCK2 тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвором включает в себя сдвиговый регистр SR, имеющий множество каскадов. Представленное ниже описание используют в качестве соответствующего символа i-ого каскада SRi для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра.

Сдвиговый регистр подает со своего i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки в блоке DAR дисплея через буфер. Например, сдвиговый регистр подает из его n-ого каскада SRn сигнал OUT в линию Gn сигнала развертки через буфер. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенным с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор), вместе с линией CSn накопительного конденсатора.

Устройство 3х жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии с каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AON. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор стороны N канала, соединенный с выходом инвертора и (n) затвор стороны Р канала, соединенный с сигнальной линией AONB.

На фиг.11 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR. Как показано на фиг.11, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод R и вывод INITB; два аналоговых переключателя ASW13 и ASW14; инвертор;

вывод CKB; вывод ONB; вывод OUT; и вывод OUTB. Вывод INITB триггера FF соединен с выводом ONB. Вывод Q FF соединен с затвором на стороне Р канала аналогового переключателя ASW13 и с затвором на стороне N канала аналогового переключателя ASW14. Вывод QB FF соединен с затвором на стороне N канала аналогового переключателя ASW13 и с затвором на стороне Р канала аналогового переключателя ASW14. Аналоговый переключатель ASW13 имеет первый электропроводный электрод, соединенный с выводом ONB, тогда как аналоговый переключатель ASW14 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW13 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW14 и с выводом OUTB, который представляет собой выходной вывод каскада. Вывод OUTB соединен с выводом через инвертор.

Сдвиговый регистр SR выполнен таким образом, что вывод OUTB первого каскада соединен с выводом SB его следующего второго каскада и, что вывод OUT второго каскада соединен с выводом R первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, тогда как вывод OUT (n+1)-ого каскада SRn+1 соединен с выводом R n-ого каскада SRn. Исходный каскад SR1 сдвигового регистра SR имеет вывод SB, который соединен сигналом GSPB. Схема GD управления затвором выполнена таким образом, что вывод ONB каждого каскада соединен с сигнальной линией AONB и, что вывод CKB каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают сигнал GCK), который отличается от линии GCK, с которой соединен вывод CKB каждого из каскада с четным номером. Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, тогда как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B.

На фиг.11 иллюстрируется триггер FF, который представляет собой FF3, показанный на фиг.12. Как показано на фиг.12, триггер FF3 включает в себя: транзистор р84 Р канала и транзистор n84 N канала, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор n85 с N каналом, составляющие схему КМОП; транзисторы р82 и р83 с Р каналом; транзисторы n81, n82 и n83 с N каналом; вывод SB; вывод R; и выводы Q, и QB. р84 имеет затвор, соединенный с затвором п84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком п84, стоком р82, стоком n81, затвором р85, затвором n85 и выводом Q. n84 имеет исток, соединенный со стоком n83. n84 имеет исток, соединенный со стоком n83. n81 имеет исток, соединенный со стоком n82. Вывод INITB соединен с истоком р82. Вывод SB соединен с затвором р82, затвором n81 и затвором n3. Вывод R соединен с затвором n82 и затвором р83. n85 имеет исток, соединенный с VSS. р83 и р85, каждый имеет исток, соединенный с VDD. n82, n83 и n85, каждый имеет исток, соединенный с VSS.

В позиции (b) на фиг.12 показана таблица истинности для FF3. Как показано в (b) на фиг.12, сигнал Q FF3 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (и) сохраняют текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (iii) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF3, в случае, когда сигнал SB и сигнал R оба становятся активными, в то время как вывод INITB является Низким (активным), р85 включается так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным). Кроме того, в течение периода одновременного выбора (то есть, в то время как сигнал INITB является Низким; сигнал SB является Низким; и сигнал R является Высоким), сигнал Q имеет Vss+Vth (то есть, пороговое напряжение р82), и сигнал QB имеет Vdd (Высокий).

На фиг.13 показана временная диаграмма, иллюстрирующая управление устройством 3х жидкокристаллического дисплея во время включения. На фиг.13 AONB представляет сигнал AONB (сигнал одновременного выбора); GSPB представляет сигнал шины импульса запуска затвора; GCK1B представляет сигнал GCK1B; и GCK2B представляет сигнал GCK2B. Кроме того, SBi, Ri, Qi и OUTi (i=n-1, n, и n+1), соответственно, представляют сигнал SB (потенциал вывода SB), сигнал R (потенциал вывода R), сигнал Q (потенциал вывода Q) и сигнал OUT (потенциал вывод OUT) i-ого каскада SRL

Когда устройство 3х жидкокристаллического дисплея включают, выполняется операция подготовки. В частности, операция подготовки приводит к тому, что сигнал AONB становится активным (Низким) в течение заданного периода. Поскольку ASW13 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким) в результате активации, так, что происходит выбор всех линий сигнала развертки. Кроме того, включают аналоговый переключатель asw, соответствующий каждой линии сигнала данных, в результате активации сигнала AON, так, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INITB, на который подают сигнал AONB, становится активным (Низким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания описанной выше операции подготовки (то есть, после того, как сигнал AONB становится неактивным), устройство 3х жидкокристаллического дисплея достигает состояния, в котором Vcom записано в каждый PIX блока DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера в каждом каскаде стал неактивным).

Устройство 3х жидкокристаллического дисплея, когда его включают и выключают, одновременно выбирает все линии сигнала развертки так, что идентичный потенциал (например, Vcom) записывают во все пиксели. Это предотвращает нарушение изображения, связанное с включением и выключением устройства 3х жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), в настоящей компоновке (i) подают сигнал AONB ASW13 для устранения необходимости в элементе НЕ-И фиг.34, который принимает выходной сигнал каждого каскада, и (И) подают сигнал AONB на вывод INITB каждого FF для устранения необходимости в компоненте, который генерирует и передает сигнал для инициализации сдвигового регистра. Это позволяет уменьшить размеры схемы управления затвором. Кроме того, настоящая компоновка инициализирует сдвиговый регистр (то есть, инициализирует триггер каждого каскада) при одновременном выборе всех линий сигнала развертки. Настоящая компоновка, таким образом, может закончить операцию подготовки быстрее, чем обычная компоновка, которая осуществляет одновременный выбор всех линий сигнала развертки и инициализацию сдвигового регистра по-отдельности. Кроме того, настоящая компоновка обеспечивает установку триггера FF так, чтобы она имела приоритет над его сбросом. Таким образом, когда одновременный выбор заканчивается (то есть, когда сигнал AONB возвращается из активного состояния в неактивное состояние), сигнал SB, более вероятно, становится неактивным прежде сигнала R. Настоящая компоновка, таким образом, предотвращает неправильную работу, то есть, предотвращает выполнение сдвиговым регистром, после его инициализации операции установки, из-за того, что сигнал R становится неактивным, до сигнала SB.

На фиг.14 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3с жидкокристаллического дисплея, которое представляет собой вариант устройства 3х жидкокристаллического дисплея.

На фиг.15 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR, включенного в устройство 3с жидкокристаллического дисплея. Как показано на фиг.15, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод RB и вывод INITB; два аналоговых переключателя ASW3 и ASW4; инвертор; вывод CKB; вывод ONB; вывод OUT; и вывод OUTB. Вывод INITB триггера FF соединен с выводом ONB. Вывод Q FF соединен с затвором на стороне Р канала аналогового переключателя ASW3 и с затвором на стороне N канала аналогового переключателя ASW4. Вывод QB FF соединен с затвором на стороне N канала аналогового переключателя ASW3 и с затвором на стороне Р канала аналогового переключателя ASW4. Аналоговый переключатель ASW3 имеет первый электропроводный электрод, соединенный с выводом ONB, в то время как аналоговый переключатель ASW4 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW3 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW4 и с выводом OUTB, который представляет собой выходной вывод каскада. Вывод OUTB соединен с выводом OUT через инвертор.

Сдвиговый регистр SR установлен так, что вывод OUTB первого каскада соединен с выводом SB следующего второго каскада, и вывод OUTB второго каскада соединен с выводом RB первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, в то время как вывод OUTB (n+1)-ого каскада SRn+1 соединен с выводом RB n-ого каскада SRn. Исходный каскад SR1 сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB. Схема GD управления затвором выполнена таким образом, что вывод ONB каждого каскада соединен с сигнальной линией AONB, и вывод CKB каждого каскада с нечетным номером соединен с линией GCKB (то есть, линией, через которую подают GCK сигнал тактовой частоты затвора), которая отличается от линии GCKB, с которой соединен вывод CKB каждого каскада с четным номером. Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, в то время как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B.

Триггер FF на фиг.15 представляет собой FF4, показанный на фиг.16. Как показано на фиг.16, FF4 включает в себя: транзистор р6 с Р каналом и транзистор n5 с каналом N, составляющие схему КМОП; транзистор р8 с Р каналом и транзистор n7 с каналом N, составляющие схему КМОП; транзисторы р5 и р7 с Р каналом; транзисторы n6 и n8 с N каналом; вывод INITB; вывод SB; вывод RB; и выводы Q, и QB. р6 имеет затвор, соединенный с затвором n5, стоком р7, стоком р8, стоком n7 и выводом QB. р6 имеет сток, соединенный со стоком n5, стоком р5, затвором р8, затвором n7 и выводом Q. n5 имеет исток, соединенный со стоком n6. n7 имеет исток, соединенный со стоком n8. Вывод SB соединен с затвором р5 и затвором n6. Вывод RB соединен с истоком р5, затвором р7 и затвором n8. Вывод INITB соединен с истоком р6. Истоки каждого р7 и р8 соединены с VDD. Истоки каждого n6 и n8 соединены с VSS. В FF4 р6, n5, р8 и n7 составляют схему LC защелки; р5 используется, как транзистор ST установки; р7 используется, как транзистор RT сброса; n6 и n8 каждый используется, как транзистор высвобождения защелки (транзистор высвобождения) LRT.

В позиции (b) на фиг.16 показана временная диаграмма, иллюстрирующая, как работает FF4. В позиции (с) на фиг.16 показана таблица истинности для FF4. Как показано в позициях (b) и (с) на фиг.16, сигнал Q FF4 (i) является Низким (неактивным), в то время как сигнал SB является Низким (активным), и сигнал RB является Низким (активным), (И) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал RB является Высоким (неактивным), (iii) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал RB является Низким (активным), и (iv) поддерживает текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал RB является Высоким (неактивным).

В течение периода t1 в позиции (b) на фиг.16, например, на вывод Q подают Vdd с вывода RB, n7 включен, и на вывод QB подают Vss (Низкий). В течение периода t2, сигнал SB является Высоким, поэтому р5 выключен и n6 включен. Это обеспечивает поддержание состояния t1. В течение периода t3, сигнал RB является Низким, так, что р7 включен, и на вывод QB подают Vdd (Высокое). Кроме того, в течение периода t3, n5 включен, поэтому, на вывод Q подают Vss. В случае, когда сигнал SB и сигнал RB оба становятся Низкими (активными), в то время как вывод INITB является Низким (активным), р7 включен, поэтому, на вывод QB подают Vdd (Высокий) и на вывод Q подают Vss+Vth (то есть, пороговое напряжение р5) через р5.

Устройством 3с жидкокристаллического дисплея, при его включении, управляют так, как показано на фиг.17. Компоновка на фиг.15 приводит к тому, что сигнал Q имеет Vss+Vth и сигнал QB имеет Vdd (Высокий) во время периода одновременного выбора (то есть, в то время, как вывод INITB является Низким; сигнал SB является Низким; и сигнал RB является Низким). Таким образом, выход каждого триггера, предпочтительно, представляет собой только сигнал QB, то есть, конфигурация, показанная на фиг.18, является предпочтительной. В частности, (i) сигнал QB и (ii) сигнал, полученный путем инвертирования сигнала QB с помощью инвертора, предпочтительно подают на аналоговые переключатели ASW3 и ASW4, соответственно.

Вариант 2 осуществления

На фиг.19 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3d жидкокристаллического дисплея, в соответствии с настоящим изобретением. Устройство 3d жидкокристаллического дисплея включает в себя: блок DAR дисплея; схему GD управления затвором; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AONB (сигнал одновременного выбора), импульс GSP запуска затвора, сигнал GOE разрешения включения затвора и сигналы GCK1B, и GCK2B тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвором включает в себя сдвиговый регистр SR, имеющий множество каскадов. В представленном ниже описании используется, соответственно, символ i-ого каскада Sri для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра.

Сдвиговый регистр подает со своего i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки, в блоке DAR дисплея через буфер. Например, сдвиговый регистр подает сигнал OUTB своего n-ого каскада SRn в линию Gn сигнала развертки через буфер. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенного с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор) вместе с линией CSn накопительного конденсатора.

Устройство 3d жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии с каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AONB. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, в то время как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор стороны N канала, соединенный с выходом инвертора и (ii) затвор стороны Р канала, соединенный с сигнальной линией AONB.

На фиг.20 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR. Как показано на фиг.20, сдвиговый регистр включает в себя, в каждом из его каскадов: триггер FF, включающий в себя вывод INITB, вывод SB и вывод RB; два аналоговых переключателя ASW5 и ASW6 (схема затвора); HE-PI (логическая схема); инвертор; вывод CKB; вывод ONB; и вывод OUTB. Вывод INITB триггера FF соединен с выводом ONB. Вывод QB FF соединен с первым входом НЕ-И. НЕ-И имеет выход, соединенный с входом инвертора, затвор стороны Р канала аналогового переключателя ASW5, и затвор стороны N канала аналогового переключателя ASW6. Инвертор имеет выход, соединенный с затвором стороны N канала аналогового переключателя ASW5, и затвором стороны Р канала аналогового переключателя ASW6. Аналоговый переключатель ASW5 имеет первый электропроводный электрод, соединенный с выводом ONB, тогда как аналоговый переключатель ASW6 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW5 имеет второй электропроводный электрод, соединенный с (i) вторым электропроводным электродом аналогового переключателя ASW6, (ii) выводом OUTB, который представляет собой выходной вывод каскада, (iii) вторым входом НЕ-И и (iv) выводом RB FF. В каждом из каскадов аналоговые переключатели ASW5 и ASW6 (схема затвора) и НЕ-И (логическая схема) составляют схему генерирования сигнала для генерирования сигнала OUTB.

Сдвиговый регистр SR выполнен так, что вывод OUTB первого каскада соединен с выводом SB его следующего второго каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, и вывод OUTB (n+1)-ого каскада SRn+1 соединен с выводом SB (n+2)-ого каскада SRn+2. Исходный каскад SR1 сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB. Схема GD управления затвором выполнена таким образом, что вывод ONB каждого каскада соединен с сигнальной линией AONB, и вывод CKB каждого каскада с нечетным номером соединен с линией GCKB (то есть, линией, через которую подают сигнал GCKB тактовой частоты затвора), который отличается от линии GCKB, с которой соединен вывод CKB каждого каскада с четным номером. Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, тогда как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B.

На фиг.21 показана временная диаграмма, иллюстрирующая, как осуществляют управление устройством 3d жидкокристаллического дисплея при его включении. Устройство 3d жидкокристаллического дисплея выполняет операцию подготовки перед отображением исходного кадра (период вертикальной развертки) отображаемого изображения. В частности, операция подготовки приводит к тому, что сигнал AONB является активным (Низким) в течение заданного периода, в течение которого каждый сигнал GCKB остается активным (Низким). Когда сигнал AONB становится активным (Низким), сигнал OUTB становится активным {Низким), поскольку ASW5 включен, таким образом, что выбирают все линии сигнала развертки. В течение этого периода аналоговый переключатель asw, соответствующий каждой линии сигнала данных включен, так, что во все линии сигнала данных подают Vcom. Кроме того, в течение этого периода, сигнал SB и сигнал RB триггера каждого каскада становятся активными, так, что сигнал QB становится Высоким (неактивным). Как только сигнал OUTB каждого каскада сдвигового регистра станет активным, сигнал обратной связи в НЕ-И становится Низким, так, что ASW5 выключается, и ASW6 включается (в каждый каскад подают либо GCK1B, или GCK2B). После того, как описанная выше операция подготовки закончится (то есть, после того, как сигнал AONB станет неактивным), устройство 3d жидкокристаллического дисплея достигает состояния, в котором Vcom было записано в каждый PIX в блоке DAR дисплея и, в котором был инициализирован сдвиговый регистр SR (то есть, выходной сигнал триггера каждого каскада стал неактивным).

Устройство 3d жидкокристаллического дисплея выполняет следующую операцию в течение каждого периода вертикальной развертки (то есть, при отображении каждого кадра). Когда сигнал SB, подаваемый в первый каскад сдвигового регистра SR, становится активным (=Низким), выход FF первого каскада устанавливают так, что его выход является активным, и первый каскад принимает сигнал GCKB. Когда сигнал GCKB первого каскада становится активным (=Низким), сигнал OUTB первого каскада становится активным (=Низким), сигнал SB следующего второго каскада также становится активным, и выполняют сброс FF первого каскада, так, что сигнал QB первого каскада становится Высоким (неактивным). В течение этого периода сигнал OUTB первого каскада является Низким (то есть, выход НЕ-И является Высоким), поэтому, первый каскад продолжает принимать сигнал GCKB. Когда сигнал GCKB становится Высоким (неактивным), сигнал OUTB первого каскада становится Высоким, и выход схемы НЕ-И становится Низким. Вывод OUTB после этого выводит сигнал AONB, таким образом, что сигнал OUTB является Высоким (неактивным).

Устройство 3d жидкокристаллического дисплея, при его включении и выключении, одновременно выбирает все линии сигнала развертки так, чтобы идентичный потенциал (например, Vcom) записывают во все пиксели. Это исключает появление неоднородного изображения при включении или выключении устройства 3d жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), в настоящей компоновке подают сигнал AONB в ASW5 для устранения необходимости в элементе НЕ-И на фиг.34, который принимает выходной сигнал каждого каскада. Это позволяет уменьшить размеры схемы управления затвором. Кроме того, настоящая компоновка инициализирует сдвиговый регистр (то есть, инициализируется триггер каждого каскада) при одновременном выборе всех линий сигнала развертки. Настоящая компоновка, таким образом, позволяет закончить операцию подготовки более быстро, чем в обычной компоновке, в которой отдельно выполняют одновременный выбор всех линий сигнала развертки и инициализацию сдвигового регистра. Кроме того, настоящая компоновка позволяет выполнить сброс каждого каскада по-отдельности. Что позволяет упростить соединение между каскадами.

В конфигурации, показанной на фиг.20 (в которой FF имеет приоритет по сбросу, и в которой выполняют сброс каждого каскада самого сдвигового регистра), сигнал OUTB может быть передан по каналу обратной связи на вывод RB триггера перед подачей его по цепи обратной связи в НЕ-И. НЕ-И на фиг.20, таким образом, предпочтительно выполнена, как представлено на фиг.22. В частности, НЕ-И предпочтительно выполнена так, что транзистор р40 с Р каналом имеет (i) исток, соединенный с VDD, (ii) затвор, используемый, как вход Х для НЕ-И, и (iii) сток, используемый, как выход М НЕ-И; транзистор р41 с Р каналом имеет (i) исток, соединенный с VDD, (ii) затвор, используемый входом Y НЕ-И, и (iii) сток, соединенный с истоком транзистора n40 с N каналом; транзистор п40 с N каналом имеет (i) затвор, соединенный с входом Y, и (ii) сток, соединенный с истоком транзистора n41 с N каналом; транзистор n41 с N каналом имеет (i) затвор, соединенный с входом X, и (ii) сток, соединенный с VSS; и транзисторы р40 и р41 с Р каналом, каждый имеет более высокую способность при управлении, чем у любого из транзисторов n40 и n41 с N каналом. Такая конфигурация обеспечивает то, сигнал OUTB остается активным (=Низким), до тех пор, пока сигнал QB не станет достаточно неактивным (Высоким), и, следовательно, предотвращает подачу по цепи обратной связи сигнала OUTB в вывод RB FF перед подачей обратно в НЕ-И.

Вариант 3 осуществления

На фиг.23 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3е жидкокристаллического дисплея в соответствии с настоящим изобретением. Устройство 3е жидкокристаллического дисплея представляет собой устройство жидкокристаллического дисплея на основе, так называемого, управления СС (с зарядовой связью), и включает в себя: блок DAR дисплея; схему G-CsD управления затвором-Cs; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором стартовый импульс GSP затвора, сигнал GOE разрешения включения затвора, сигнал AONB (сигнал одновременного полного выбора), сигналы CMI1 и CMI2 инверсии CS, и сигналы GCK1B и GCK2B тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком стартовый импульс SSP истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK. тактовой частоты истока. Схема G-CsD управления затвором-Cs включает в себя: сдвиговый регистр SR, имеющий множество каскадов; и множество схем CSL D-защелки. Схема G-CsD управления затвором-Cs включает в себя схему OR и схему CSL D-защелки, в соответствии с каждым каскадом сдвигового регистра. В представленном ниже описании используется, соответственно, символ i-ого каскада SRi для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра. Схема G-CsD управления затвором-Cs, таким образом, включает в себя схему CSLi D-защелки, в соответствии с i-ым каскадом SRi сдвигового регистра.

Сдвиговый регистр из его i-ого каскада SRi подает выходной сигнал (сигнал OUT) в линии Gi сигнала развертки в блоке DAR дисплея через буфер, и схема CSLi D-защелки, соответствующая i-ому каскаду SRi, подает выходной сигнал (то есть, выходной сигнал или сигнал CS) в линию CSi накопительного конденсатора в блоке DAR дисплея. Например, сдвиговый регистр подает из его n-ого каскада SRn сигнал OUTB в линию Gn сигнала развертки через буфер, и схема CSLn D-защелки, соответствующая n-ому каскаду SRn, подает выходной сигнал (то есть, выходной сигнал или сигнал CS) в линию CSn накопительного конденсатора в блоке DAR дисплея. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, который соединен с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор) вместе с линией CSn накопительного конденсатора.

Устройство 3е жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии с каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AONB. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор на стороне N канала, соединенный с выходом инвертора, и (ii) затвор на стороне Р канала, соединенный с сигнальной линией AONB.

На фиг.24 показана принципиальная схема, иллюстрирующая конфигурацию i-ого каскада SRi сдвигового регистра SR, показанного на фиг.23. Как представлено на фиг.24, сдвиговый регистр включает в себя, в каждом из его каскадов: триггер FF (любой из описанных выше триггеров FF1-FF4), включающих в себя вывод SB и вывод R; два аналоговых переключателя ASW7 и ASW8; НЕ-И; инвертор; вывод CKB; и вывод ONB. Вывод QB триггера FF соединен с первым входом НЕ-И. НЕ-И имеет выход (М), соединенный с (i) входом инвертора, (ii) затвором на стороне Р канала аналогового переключателя ASW7 и (iii) затвором на стороне N канала аналогового переключателя ASW8. Инвертор имеет выход, соединенный с (i) затвором на стороне N канала аналогового переключателя ASW7 и (ii) затвором на стороне Р канала аналогового переключателя ASW8. Аналоговый переключатель ASW7 имеет первый электропроводный электрод, соединенный с выводом ONB, тогда как аналоговый переключатель ASW8 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW7 имеет второй электропроводный электрод, соединенный с (i) вторым электропроводным электродом аналогового переключателя ASW8, (ii) вывод OUTB, который представляет собой выходной вывод каскада, (iii) второй вход НЕ-И и (iv) вывод R FF. Вывод OUTB соединен с выводом OUT черезинвертор.

i-ый каскад SRi установлен таким образом, что в течение периода, в который сигнал QB (то есть, первый вход Х из НЕ-И) триггера FF является Высоким (неактивным), (i) в случае, когда сигнал OUTB (то есть, второй вход Y НЕ-И) является Высоким (неактивным), выход (М) НЕ-И является Низким (то есть, аналоговый переключатель ASW7 является включенным и аналоговый переключатель ASW8 выключен), таким образом, что на вывод OUTB подают сигнал AONB (который является неактивным и имеет Vdd), и (ii) в случае, когда сигнал OUTB (то есть, второй вход Y НЕ-И), является Низким (активным), выход (М) НЕ-И является Высоким (то есть, аналоговый переключатель ASW7 выключен и аналоговый переключатель ASW8 включен), таким образом, что i-ый каскад SRi принимает сигнал GCKB и, таким образом, выводит его. Кроме того, i-ый каскад SRi выполнен так, что в течение периода, в который сигнал QB триггера FF является Низким (активным), поскольку первый вход Х НЕ-И является Низким, и второй вход Y НЕ-И является Низким, выход (М) НЕ-И является Высоким (то есть, аналоговый переключатель ASW7 выключен и аналоговый переключатель ASW8 включен), таким образом, что i-ый каскад SRi принимает сигнал GCKB и, таким образом, выводит его. Такая компоновка обозначает, что НЕ-И, инвертор и аналоговые переключатели ASW1 и ASW2 (схемы затвора) составляют схему генерирования сигнала, для генерирования сигнала OUTB, в частности, аналоговые переключатели ASW7 и ASW8 составляют схему затвора, для приема либо сигнала AONB, или сигнала тактовой частоты в соответствии с выходом М НЕ-И.

На фиг.25 показана принципиальная схема, иллюстрирующая конфигурацию схемы CSLi D-защелки, которая соответствует i-ому каскаду SRi сдвигового регистра SR, показанного на фиг.23. Как показано на фиг.25, схема CSLi D-защелки включает в себя: три схемы 5-7 КМОП; аналоговые переключатели ASW15 и ASW16; инвертор; вывод CK; вывод D; и выходной вывод. Схемы 5 и 6 КМОП каждая выполнена таким образом, что (i) один транзистор с Р каналом и один транзистор с N каналом имеют соответствующие затворы, соединенные друг с другом, и соответствующие стоки, соединенные друг с другом, и что (ii) транзистор с Р каналом имеет исток, соединенный с VDD, тогда как транзистор с N каналом имеет исток, соединенный с VSS. Схема 7 КМОП выполнена так, что (i) один транзистор с Р каналом и один транзистор с N каналом имеют соответствующие затворы, соединенные друг с другом, и соответствующие стоки, соединенные друг с другом и, что (ii) транзистор с Р каналом имеет исток, соединенный с источником VCSH питания, тогда как транзистор с N каналом имеет исток, соединенный с источником VCSL питания. Вывод ck соединен с (i) входом инвертора, (ii) затвором на стороне N канала аналогового переключателя ASW16, и (iii) затвором на стороне Р канала аналогового переключателя ASW15. Инвертор имеет выход, соединенный с (i) затвором на стороне Р канала аналогового переключателя ASW16 и (ii) затвором на стороне N канала аналогового переключателя ASW15. Схема 5 КМОП соединена, на стороне ее стока, с первым электропроводным выводом аналогового переключателя ASW15. Аналоговый переключатель ASW16 имеет первый электропроводный вывод, соединенный с выводом D. Аналоговый переключатель ASW15 имеет второй электропроводный вывод, соединенный с (i) вторым электропроводным выводом аналогового переключателя ASW16 и (и) схемой 6 CMOS на стороне ее затвора. Схема 5 КМОП соединена, на стороне ее затвора, со схемой 6 КМОП на стороне ее стока. Схема 6 КМОП соединена, на стороне ее стока, со схемой 7 КМОП на стороне ее затвора. Схема 7 КМОП соединена, на стороне ее стока, с выходным выводом.

Схема CSLi D-защелки, в то время как сигнал ck (то есть, сигнал, подаваемый на вывод ck), является активным (Высоким), принимает сигнал D (то есть, сигнал, подаваемый на вывод D), и фиксирует его. В частности, (i) в случае, когда сигнал D преобразуется с Низкого на Высокий, в то время как сигнал ck является активным, потенциал выходного сигнала (то есть, сигнала, подаваемого с выходного вывода), поднимается с потенциала источника VCSL питания до потенциала источника VCSH питания, и после этого поддерживается потенциал источника VCSH питания, и (ii) в случае, когда сигнал D преобразуется с Высокого на Низкий, в то время как сигнал ck является активным, потенциал выходного сигнала (то есть, сигнала, подаваемого с выходного вывода), падает с потенциала источника VCSH питания до потенциала источника VCSL питания, и после этого поддерживается потенциал источника VCSL питания.

Схема G-CsD устройства 3е жидкокристаллического дисплея выполнена так, что (i) вывод OUTB первого каскада соединен с выводом SB следующего второго каскада, (ii) вывод OUT первого каскада соединен с первым входным выводом схемы OR, соответствующей первому каскаду, в то время, как выходной вывод второго каскада соединен со вторым входным выводом схемы OR, соответствующей первому каскаду, и (iii) схема OR, соответствующая первому каскаду, имеет выход, соединенный с выводом ck схемы D-защелки, соответствующей первому каскаду. Например, G-CsD выполнена так, что (i) вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, (ii) вывод OUT n-ого каскада SRn соединен с первым входным выводом схемы OR, соответствующей n-ому каскаду SRn, тогда как вывод (n+1)-ого каскада SRn+1, соединен со вторым входным выводом схемы OR, соответствующей n-ому каскаду SRn, и (iii) схема OR, соответствующая n-ому каскаду SRn, имеет выход, соединенный с выводом ck схемы CSLn D -защелки, соответствующей n-ому каскаду SRn. Исходный каскад сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB.

Схема G-CsD устройства 3е жидкокристаллического дисплея дополнительно выполнена так, что (i) вывод CKB каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают GCK), которая отличается от линии GCK, с который соединен вывод CKB каждого каскада с четным номером, и что (ii) вывод ONB каждого каскада соединен с общей линией AONB (то есть, линией, через которую подают сигнал AON). Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, тогда как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B, и вывод ONB каждого n-ого каскада SRn и (n+1)-ого каскада SRn+1 соединен с общей сигнальной линией AONB. Кроме того, каждый набор из двух выводов D соответствующих двух схем D-защелки, соответствующих последовательным каскадам, соединен с линией CMI (то есть, линией, через которую подают сигнал CMI) который отличается от линии CMI, через которую соединен следующий набор. Например, схема CSLn D-защелки, соответствующая n-ому каскаду SRn, имеет вывод D, соединенный с сигнальной линией CMI2; схема CSLn+1 D-защелки, соответствующая (n+1)-ому каскаду SRn+1, имеет вывод D, соединенный с сигнальной линией CMI2; схема CSLn+2 D-защелки, соответствующая (n+2)-ому каскаду SRn+2, имеет вывод D, соединенный с сигнальной линией CMI1; и схема CSLn+3 D-защелки, соответствующая (n+3) каскаду SRn+3, имеет вывод D, соединенный с сигнальной линией CMI1.

На фиг.26 показана временная диаграмма, иллюстрирующая, как выполняется управление устройством 3е жидкокристаллического дисплея. На фиг.26 иллюстрируется способ управления, в котором (i) сигнал POL полярности имеет цикл одного периода 1Н горизонтальной развертки (то есть, в каждую линию сигнала данных подают сигнал данных, имеющий полярность, которую инвертируют через каждый 1Н) и (ii) CMI1 и CMI2 являются идентичными друг другу по фазе.

Устройство 3е жидкокристаллического дисплея выполняет операцию подготовки к отображению перед отображением исходного кадра отображаемого изображения (то есть, перед исходным периодом вертикальной развертки). В частности, операция подготовки делает сигнал AONB активным (Низким) в течение заданного периода, в течение которого каждый сигнал GCKB остается активным (Низким), и каждый сигнал CMI остается Высоким (или Низким). Это приводит к передаче сигнала AONB из вывода OUTB через ASW7 в каждый каскад сдвигового регистра SR. Сигнал OUTB каждого каскада, таким образом, становится активным (Низким), таким образом, что выбирают все линии сигнала развертки. В течение этого периода аналоговый переключатель asw, соответствующий каждой линии сигнала данных, является включенным, поэтому во все линии сигнала данных подают Vcom. Кроме того, в каждом каскаде триггера, вывод INITB, в который подают сигнал AONB, является активным (Низким), поэтому, сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). Как только сигнал OUTB каждого каскада сдвигового регистра станет активным, сигнал обратной связи в NAND становится Низким, поэтому ASW7 выключается, и ASW8 включается (каждый каскад принимает либо GCK1B, или GCK2B). Кроме того, выход схемы OR, соответствующей каждому каскаду, также является активным (Высоким). Это приводит к тому, что (i) каждая схема D-защелки, которая фиксирует, либо сигнал CMI1 (Низкий), или сигнал CMI2 (Низкий) и (ii) выходной сигнал (сигнал CS), подаваемый в каждую линию накопительного конденсатора, должна иметь потенциал источника VCSL питания. После того, как описанная выше операция подготовки к отображению заканчивается, устройство 3е жидкокристаллического дисплея находится в состоянии, в котором (i) Vcom было записано в каждый PIX в блоке DAR дисплея, (ii) FF в каждом каскаде сдвигового регистра имеет неактивный (Высокий) выход QB, и (iii) выходной сигнал каждой схемы D-защелки (то есть, потенциал каждой линии накопительного конденсатора) имеет потенциал источника VCSL питания.

Устройство 3е жидкокристаллического дисплея выполняет следующую операцию, при отображении исходного кадра (то есть, в течение его исходного периода вертикальной развертки): Когда сигнал SB, подаваемый в первый каска SR сдвигового регистра, становится активным (=Низким), выход FF первого каскада установлен так, что этот выход является активным, и первый каскад принимает сигнал GCKB. Когда сигнал GCKB первого каскада становится активным (=Низким), сигнал OUTB первого каскад становится активным (=Низким), сигнал SB следующего второго каскада также становится активным, и происходит сброс FF первого каскада, таким образом, что сигнал QB первого каскада становится Высоким (неактивным). В течение этого периода сигнал OUTB первого каскада является Низким (то есть, выход НЕ-И является Высоким), так, что первый каскад продолжает принимать сигнал GCKB. Когда сигнал GCKB становится Высоким (неактивным), сигнал OUTB первого каскада становится Высоким, и выход НЕ-И становится Низким. На вывод OUTB после этого выводят сигнал AONB так, что сигнал OUTB становится Высоким (неактивным).

Когда сигнал OUTB первого каскада становится активным (что приводит к тому, что схема OR, соответствующая первому каскаду, имеет активный выход), схема D-защелки, соответствующая первому каскаду, фиксирует либо сигнал CMI1, или сигнал CMI2. Кроме того, когда сигнал OUTB второго каскада становится активным (что приводит к тому, что схема OR, соответствующая первому каскаду, имеет активный выход), схема D-защелки, соответствующая первому каскаду, снова фиксирует либо сигнал CMI1, или сигнал CMI2. Это приводит к тому, что потенциал выходного сигнала схемы D-защелки, соответствующий первому каскаду (то есть, потенциал линии накопительного конденсатора, соответствующей первому каскаду) после того, как сигнал OUTB первого каскада становится неактивным (то есть, после выбора линии сигнала развертки, соответствующей первому каскаду, заканчивается), (i) поднимается от потенциала источника VCSL питания до потенциала VCSH источника питания (в этом случае сигнал данных, имеющий положительную полярность, записывают в пиксель, соответствующий первому каскаду или (ii) падает от потенциала источника VCSH питания до потенциала источника VCSL питания (в этом случае сигнал данных, имеющий отрицательную полярность, записывают в пиксель, соответствующий первому каскаду).

Например, когда сигнал OUTB n-ого каскада SRn становится активным (что приводит к тому, что схема OR, соответствующая n-ому каскаду SRn, имеет активный выход), схема CSLn D-защелки, соответствующая n-ому каскаду SRn, фиксирует сигнал CMI2. Кроме того, когда сигнал OUTB (n+1)-ого каскада SRn+1 становится активным (что приводит к тому, что схема OR, соответствующая n-ому каскаду SRn, имеет активный выход), схема CSLn D-защелки снова фиксирует сигнал CMI2. Это приводит к тому, что потенциал сигнал схемы CSLn D-защелки, соответствующий n-ому каскаду SRn (то есть, потенциал линии CSn накопительного конденсатора, соответствующий n-ому каскаду SRn), после того, как сигнал OUTB n-ого каскада SRn становится неактивным (то есть, после того, как выбор линии Gn сигнала развертки, соответствующей n-ому каскаду SRn, начинается и затем заканчивается), падает с потенциала VCSH источника питания до потенциала источника VCSL питания. В течение этого периода сигнал данных, имеющий отрицательную полярность, был записан в пиксель PIXn, соответствующий n-ому каскаду SRn, как обозначено "POL". Падение потенциала линии CSn накопительного конденсатора, таким образом, приводит к тому, что эффективный потенциал становится ниже, чем потенциал сигнала данных (то есть, увеличивает яркость пикселя PIXn).

Когда сигнал OUTB (n+1)-ого каскада SRn+1 становится активным, схема CSLn+1 D-защелки, соответствующая (n+1)-ому каскаду SRn+1, фиксирует сигнал CMI2. Кроме того, когда сигнал OUTB (n+2) каскада SRn+2, становится активным, схема CSLn+1 D-защелки снова фиксирует сигнал CMI2. Это приводит к тому, что потенциал входного сигнала схемы CSLn+1 D-защелки, соответствующий (n+1)-ому каскаду SRn+1 (то есть, потенциалу линии CSn+1 накопительного конденсатора), после того, как сигнал OUTB (n+1)-ого каскада SRn+1 станет неактивным (то есть, после того, как выбор линии Gn+1 сигнала развертки начнется и затем заканчивается), повышается от потенциала источника VCSL питания до потенциала источника VCSH питания. В течение этого периода сигнал данных, имеющий положительную полярность, был записан в пиксель PIXn+1, соответствующий (n+1)-ому каскаду SRn+1, как обозначено "POL". Подъем потенциала в линии CSn+1 накопительного конденсатора, таким образом, приводит к тому, что эффективный потенциал будет выше, чем потенциал сигнала данных (то есть, увеличивается яркость пикселя PIXn+1).

Когда сигнал OUTB (n+2) каскада SRn+2 становится активным, схема CSLn+2 D-защелки, соответствующая (n+2) каскаду SRn+2, фиксирует сигнал CMI1. Кроме того, когда сигнал OUTB (n+3) каскада SRn+3 становится активным, схема CSLn+2 D - защелки снова фиксирует сигнал CMI1. Это приводит к тому, что потенциал выходного сигнала схемы CSLn+2 D-защелки, соответствующей (n+2) каскаду SRn+2 (то есть, потенциал линии CSn+2 накопительного конденсатора), после того, как сигнал OUTB (n+2) каскада SRn+2 становится неактивным (то есть, после того, как выбор линии Gn+2 сигнала развертки начнется и затем заканчивается), падает с потенциала источника VCSH питания до потенциала источника VCSL питания. В течение этого периода сигнал данных, имеющий отрицательную полярность, был записан в пиксель PIXn+2, соответствующий (n+2)-ому каскаду SRn+2, как обозначено "POL". Падение потенциала линии CSn+2 накопительного конденсатора, таким образом, приводит к тому, что эффективный потенциал становится выше, чем потенциал сигнала данных (то есть, увеличивает яркость пикселя PIXn+2).

Операцию отображения, аналогичную представленной выше для исходного кадра, выполняют для второго кадра и последующих для него кадров. Поскольку, однако, POL имеет фазу, которая была сдвинута на половину цикла через каждый кадр, в каждый пиксель подают сигнал данных, имеющий полярность, которая инвертируется в каждом кадре. Подъем и падение выходного сигнала схемы CSLi D-защелки (то есть, потенциал линии CSi накопительного конденсатора) переключается через каждый кадр, соответственно.

Устройство 3е жидкокристаллического дисплея, когда его включают и выключают, одновременно выбирает все линии сигнала развертки так, что идентичный потенциал (например, Vcom) записывают во все пиксели. Это предотвращает нарушение изображения, вызванное включением и выключением устройства 3е жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), настоящая компоновка (i) подает сигнал AONB ASW7, для устранения необходимости элемента НЕ-И по фиг.34, который принимает выходной сигнал каждого каскада и (ii) подает сигнал AONB на вывод INITB каждого FF, для устранения необходимости в компоненте, который генерирует и передает сигнал, для инициализации сдвигового регистра. Это обеспечивает то, что размеры схемы управления затвором могут быть уменьшены. Кроме того, настоящая компоновка позволяет сделать установку триггера FF приоритетной по сравнению с его сбросом. Таким образом, когда одновременный выбор заканчивается (то есть, когда сигнал AONB возвращается из активного состояния в неактивное состояние), сигнал SB, более вероятно, становится неактивным до сигнала R. Таким образом, настоящая компоновка предотвращает неправильную работу, то есть, предотвращает выполнение сдвиговым регистром, после его инициализации, операции установки, в результате того, что сигнал R становится неактивным перед сигналом SB. Кроме того, настоящая компоновка инициализирует сдвиговый регистр (то есть, инициализирует триггер каждого каскада), одновременно выбирая все линии сигнала развертки. Данная компоновка, таким образом, позволяет закончить операцию подготовки быстрее, чем обычная компоновка, которая выполняет одновременный выбор всех линий сигнала развертки и отдельную инициализацию сдвигового регистра. Кроме того, настоящая компоновка позволяет для каждого каскада выполнить сброс самостоятельно. Это позволяет упростить соединение между каскадами. Кроме того, данная компоновка позволяет соответствующим образом выполнить управление СС в отношении каждого ряда пикселей, даже для исходного кадра. Это предотвращает нарушение изображения (то есть, неоднородности формы боковых полос), вызванные исходным кадром, такие нарушения изображения представляют собой проблему при обычном управлении СС.

В данной компоновке еще более предпочтительным является то, что проявляются следующие преимущества устройства 3е жидкокристаллического дисплея: Как показано на фиг.27, простой сдвиг фазы сигнала CMI2 (с фазы, показанной на фиг.26) на половину цикла переключает цикл сигнала POL полярности на 2Н (в результате чего в каждую линию сигнала данных подают сигнал данных, имеющий полярность, инвертируемую каждые 2Н), и управление СС может быть более соответствующим образом выполнено в отношении каждого ряда пикселя, даже для исходного кадра. Другими словами, в устройстве 3е жидкокристаллического дисплея, простое управление соответствующими фазами сигналов CMI1 и CMI2 инверсии CS может переключать цикл сигнала POL полярности с 1Н на 2Н, и нарушение изображения, вызванное переключением, может быть существенно уменьшено.

Вариант 4 осуществления

На фиг.28 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3f жидкокристаллического дисплея в соответствии с настоящим изобретением. Устройство 3f жидкокристаллического дисплея представляет собой устройство жидкокристаллического дисплея, основанное на, так называемом, управлении СС (с зарядовой связью), и включает в себя: блок DAR дисплея; схему G-CsD управления затвором-Cs; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором стартовый импульс GSP затвора, сигнал GOE разрешения включения затвора, сигнал AONB (сигнал одновременного выбора), сигналы CMI1 и CMI2 инверсии CS, и сигналы GCK1B и GCK2B тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема G-CsD управления затвором-Cs включает в себя: сдвиговый регистр SR, имеющий множество каскадов; и множество схем CSL D-защелки. Схема G-CsD управления затвором-Cs включает в себя инвертор, схему CSL D-защелки и буфер, в соответствии с каждым каскадом сдвигового регистра. В представленном ниже описании используется, соответственно, символ i-ого каскада Sri для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра. Схема G-CsD управления затвором-Cs, таким образом, включает в себя схему CSLi D-защелки, в соответствии i-ым каскадом SRi сдвигового регистра.

Сдвиговый регистр подает с его i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки в блоке DAR дисплея через буфер, схему CSLi и D-защелки, соответствующих i-ому каскаду SRi, подает выходной сигнал (то есть, выходной сигнал или сигнал CS) в линию CSi-1 накопительного конденсатора в блоке DAR дисплея. Например, сдвиговый регистр подает со своего n-ого каскада SRn сигнал OUTB в линию Gn сигнала развертки через буфер, и схема CSLn D-защелки, соответствующая n-ому каскаду SRn, подает выходной сигнал (то есть, выходной сигнал или сигнал CS) в линию CSn-1 накопительного конденсатора в блок DAR дисплея. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенным с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор) вместе с линией CSn накопительного конденсатора. Линия Gn-1 сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенным с электродом пикселя в PIXn-1. Электрод пикселя в PIXn-1 формирует накопительный конденсатор (вспомогательный конденсатор), вместе с линией CSn-1 накопительного конденсатора.

Устройство 3f жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии с каждой сигнальной линией данных.

Инвертор имеет вход, соединенный с сигнальной линией AONB. Конец линии сигнала данных соединен с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор на стороне N канала, соединенный с выходом инвертора, и (ii) затвор на стороне Р канала, соединенный с сигнальной линией AONB.

i-ый каскад SRi сдвигового регистра SR, показанного на фиг.28, выполнен, как показано на фиг.24, тогда как схема CSLi D-защелки выполнена так, как показано на фиг.25.

Сдвиговый регистр SR в G-CsD устройства 3f жидкокристаллического дисплея выполнен так, что (i) вывод OUTB первого каскада соединен с выводом SB следующего второго каскада, и (И) вывод М первого каскада соединен с выводом ck схемы D-защелки, соответствующей первому каскаду. Например, схема G-CsD выполнена так, что (i) вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, и (ii) вывод М n-ого каскада SRn соединен с выводом ck схемы CSLn D - защелки, соответствующей n-ому каскаду SRn. Исходный каскад сдвигового регистра SR, имеет вывод SB, на который подают сигнал GSPB.

G-CsD дополнительно выполнен так, что (i) вывод CKB каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают GCK), который отличается от линии GCK, с которой соединен вывод CKB каждого каскада с четным номером, и что (и) вывод ONB каждого каскада соединен с общей линией AONB (то есть, линией, через которую подают сигнал AON). Например, вывод CKB n-каскада SRn соединен с сигнальной линией GCK2B, в то время, как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B, и вывод ONB каждого n-ого каскада SRn и (n+1)-ого каскада SRn+1 соединен с общей сигнальной линией AONB. Кроме того, каждый набор из двух выводов D, соответствующих схеме D-защелки, соответствующих двум последовательным каскадам, соединен с линией CMI (то есть, линией, через которую подают сигнал CMI) отличающийся от линии CMI, с которой соединен следующий набор. Например, схема CSLn-1 D-защелки, соответствующая (n-1)-ому каскаду SRn-1, имеет вывод D, соединенный с сигнальной линией CMI1; схема D-защелки CSLn, соответствующая n-ому каскаду SRn, имеет вывод D, соединенный с сигнальной линией CMI1; схема CSLn+1 D-защелки, соответствующая (n+1)-ому каскаду SRn+1, имеет вывод D, соединенный с сигнальной линией CMI2; схема CSLn+2 D-защелки, соответствующая (n+2)-ому каскаду SRn+2, имеет вывод D, соединенный с сигнальной линией CMI2; и схема CSLn+3 D-защелки, соответствующая (n+3)-ому каскаду SRn+3, имеет вывод D, соединенный с сигнальной линией CMI1.

На фиг.29 показана временная диаграмма, иллюстрирующая управление устройством 3f жидкокристаллического дисплея. На фиг.29 иллюстрируется способ управления, в соответствии с которым (i) сигнал POL полярности имеет цикл одного периода 1Н горизонтальной развертки (то есть, в каждую линию сигнала данных подают сигнал данных, имеющий полярность, которую инвертируют через каждый 1Н) и (ii) CMI1 и CMI2 являются идентичными друг другу по фазе.