Результат интеллектуальной деятельности: СДВИГОВЫЙ РЕГИСТР, УСТРОЙСТВО ОТОБРАЖЕНИЯ, СНАБЖЕННОЕ ТАКОВЫМ, И СПОСОБ ВОЗБУЖДЕНИЯ СДВИГОВОГО РЕГИСТРА

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к сдвиговому регистру, предусмотренному в схеме возбуждения устройства отображения активного матричного типа, и способу для возбуждения сдвигового регистра.

УРОВЕНЬ ТЕХНИКИ

Традиционно, известно устройство отображения активного матричного типа, в котором множество линий шины затвора (линий сигнала сканирования) и множество линий шины истока (линий видеосигнала) скомпонованы в виде решетки, и множество частей формирования пикселя скомпонованы в матричном виде на соответствующих пересечениях множества линий шины затвора и множества линий шины истока. Каждая часть формирования пикселя включает в себя TFT (тонкопленочный транзистор), который является коммутационным элементом, присоединенным на своем выводе затвора к линии шины затвора, проходящей через соответствующее пересечение, и присоединенным на своем выводе истока к линии шины истока, проходящей через это пересечение; емкость пикселя для удерживания значения пикселя; и тому подобное. Устройство отображения активного матричного типа также снабжено драйвером затвора (схемой возбуждения линий сканирования), который возбуждает множество линий шины затвора, и драйвером истока (схемой возбуждения линий видеосигнала), который возбуждает множество линий шины истока.

Видеосигнал, указывающий значение пикселя, передается через линию шины истока, и каждая линия шины истока не может передавать за раз (одновременно) видеосигналы, указывающие значения пикселя для множества строк. Поэтому, запись видеосигналов в емкости пикселя в описанных выше частях формирования пикселя, скомпонованных в матричном виде, выполняется последовательно, строка за строкой. Отсюда, для того чтобы множество линий шины затвора могли последовательно выбираться в течение предварительно определенного периода, драйвер затвора является состоящим из сдвигового регистра, включающего в себя множество каскадов.

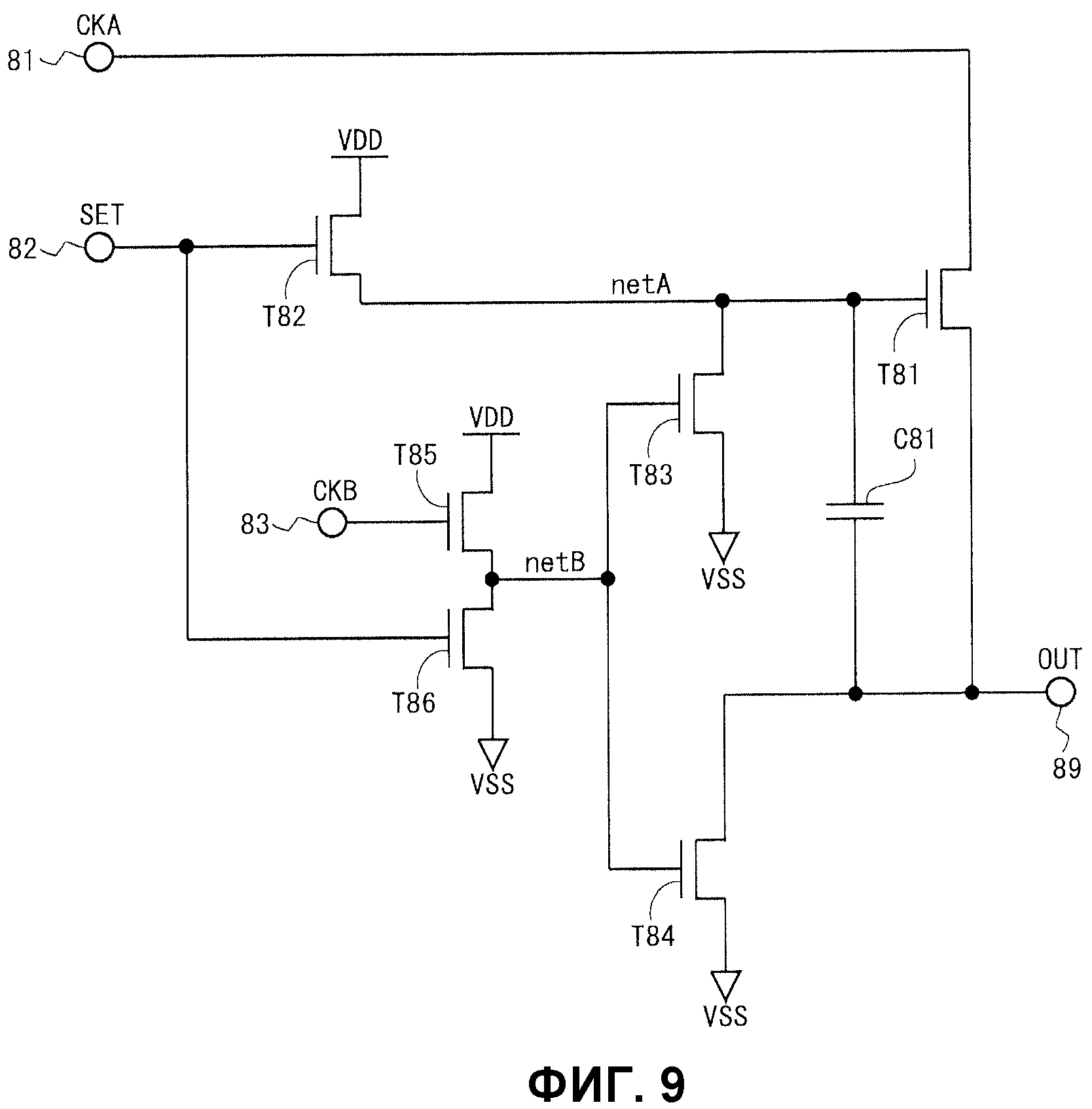

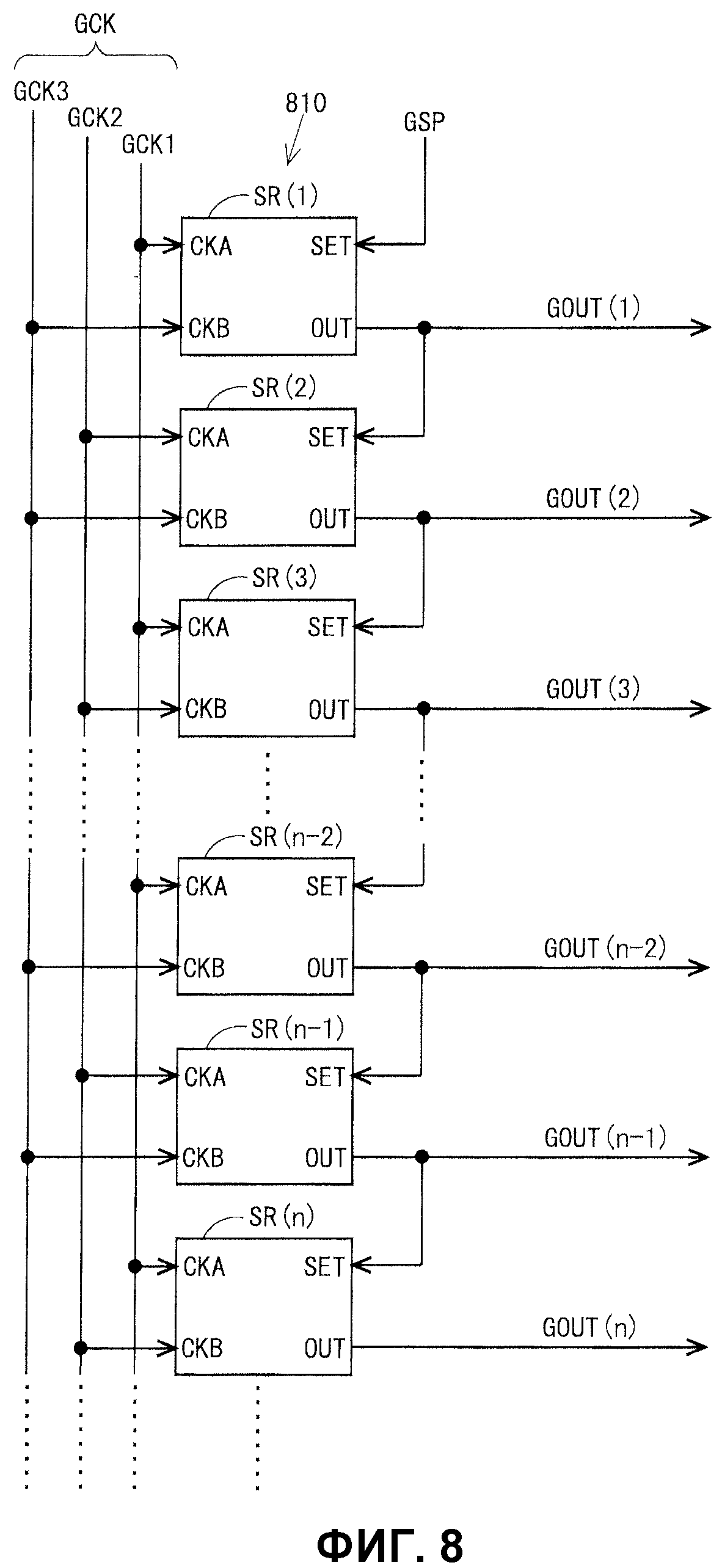

Фиг.8 - блок-схема, показывающая примерную конфигурацию сдвигового регистра 810, включенного в традиционный драйвер затвора (см. опубликованный перевод на японский язык заявки PCT № 6-505605). Как показано на Фиг.8, драйвер затвора состоит из n-каскадного сдвигового регистра 810. Каждый каскад сдвигового регистра 810 является бистабильной схемой, которая находится в любом одном из двух состояний (первого состояния и второго состояния) в каждый момент времени и выдает сигнал (сигнал состояния), указывающий состояние, в качестве сигнала GOUT сканирования. По существу, сдвиговый регистр 810 состоит из n бистабильных схем SR(1)-SR(n). На сдвиговый регистр 810 подаются трехфазные тактовые сигналы GCK1, GCK2 и GCK3, и начальный импульсный сигнал GSP затвора, который является сигналом для запуска сканирования линий шины затвора. Каждая бистабильная схема снабжена входным выводом для приема любого одного из трехфазных тактовых сигналов в качестве первого тактового сигнала CKA; входным выводом для приема любого одного из трехфазных тактовых сигналов в качестве второго тактового сигнала CKB; входным выводом для приема начального импульсного сигнала GSP затвора или сигнала OUT состояния, выдаваемого из его первого каскада, в качестве сигнала SET установки; и выходной вывод для вывода сигнала OUT состояния.

Фиг.9 - принципиальная схема, показывающая примерную конфигурацию одного каскада (одной бистабильной схемы) описанного выше традиционного сдвигового регистра 810. Бистабильная схема включает в себя шесть тонкопленочных транзисторов T81-T86 и конденсатор C81. В дополнение, бистабильная схема имеет входные выводы для линии VDD электропитания, которая питает относительно высокоуровневый потенциал VGH, и входные выводы для линии VSS электропитания, которая питает относительно низкоуровневый потенциал VGL, а также три входных вывода 81-83 и один выходной вывод 89. Отметим, что входной вывод, который принимает первый тактовый сигнал CKA, обозначен номером 81 ссылки, входной вывод, который принимает сигнал SET установки, обозначен номером 82 ссылки, а входной вывод, который принимает второй тактовый сигнал CKB, обозначен номером 83 ссылки. Также отметим, что потенциал VGH соответствует потенциалу, который помещает тонкопленочный транзистор в части формирования пикселя во включенное состояние, а потенциал VGL соответствует потенциалу, который помещает тонкопленочный транзистор в отключенное состояние.

Вывод затвора тонкопленочного транзистора T81, вывод истока тонкопленочного транзистора T82 и вывод стока тонкопленочного транзистора T83 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netA» ради удобства. В дополнение, вывод затвора тонкопленочного транзистора T83, вывод истока тонкопленочного транзистора T84 и вывод стока тонкопленочного транзистора T85 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netB» ради удобства.

Тонкопленочный транзистор T81 присоединен на своем выводе затвора к netA, присоединен на своем выводе стока к входному выводу 81 и присоединен на своем выводе истока к выходному выводу 89. Тонкопленочный транзистор T82 присоединен на своем выводе затвора к входному выводу 82, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к netA. Тонкопленочный транзистор T83 присоединен на своем выводе затвора к netB, присоединен на своем выводе стока к netA и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T84 присоединен на своем выводе затвора к netB, присоединен на своем выводе стока к выходному выводу 89 и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T85 присоединен на своем выводе затвора к входному выводу 83, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к netB. Тонкопленочный транзистор T86 присоединен на своем выводе затвора к входному выводу 82, присоединен на своем выводе стока к netB и присоединен на своем выводе истока к линии VSS электропитания. Конденсатор C81 присоединен на одном своем конце к netA и присоединен на своем другом конце к выходному выводу 89.

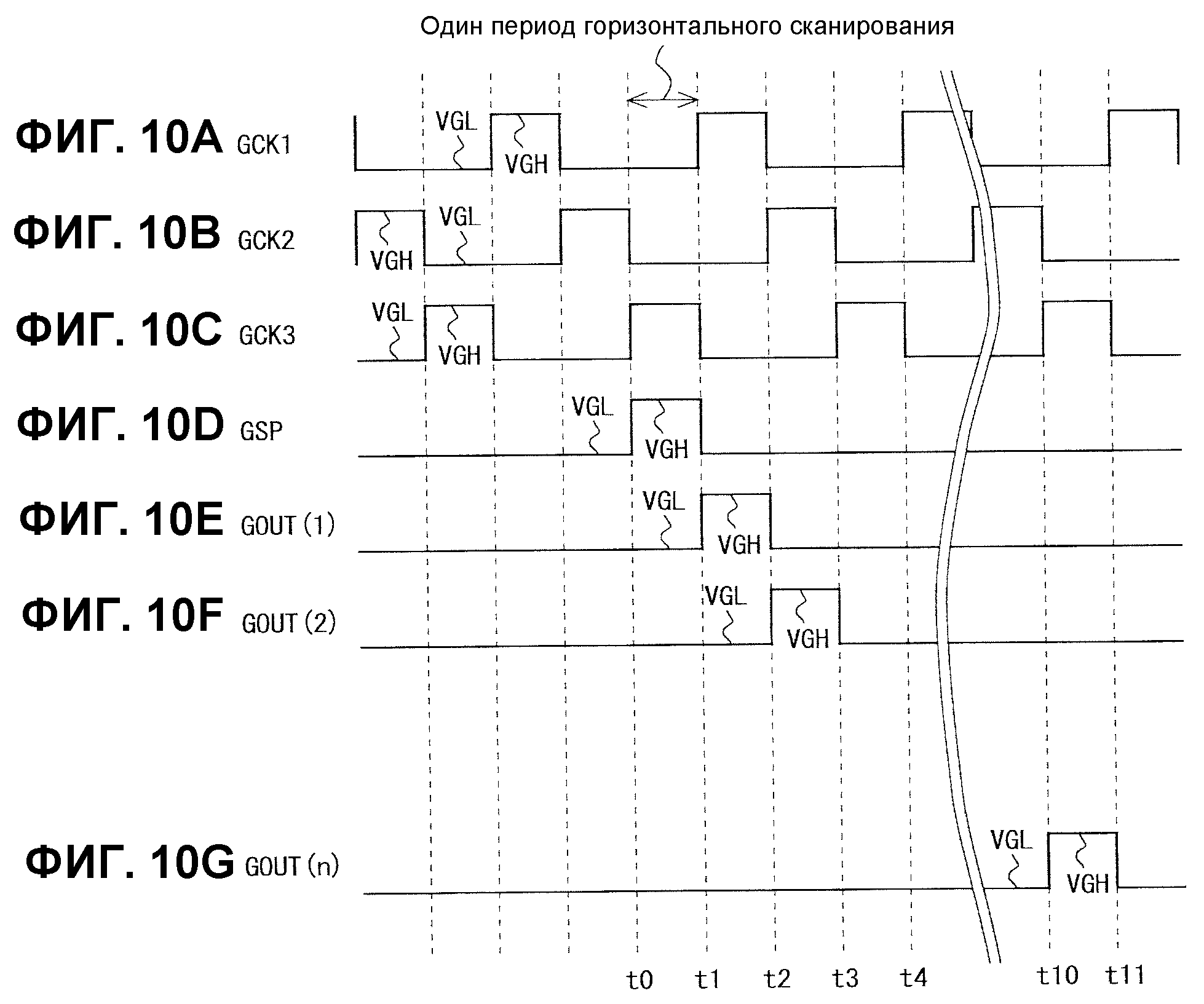

В конфигурации, такой как описанная выше, трехфазные тактовые сигналы GCK1, GCK2 и GCK3, имеющие формы сигнала, показанные на Фиг.10A-10C, и начальный импульсный сигнал GSP затвора, имеющий форму сигнала, показанную на Фиг.10D, подаются на сдвиговый регистр 810. Затем, сигналы GOUT(1)-GOUT(n) сканирования, которые последовательно переходят на высокий уровень в течение одного периода горизонтального сканирования, как показано на Фиг.10E-10G, выдаются из сдвигового регистра 810.

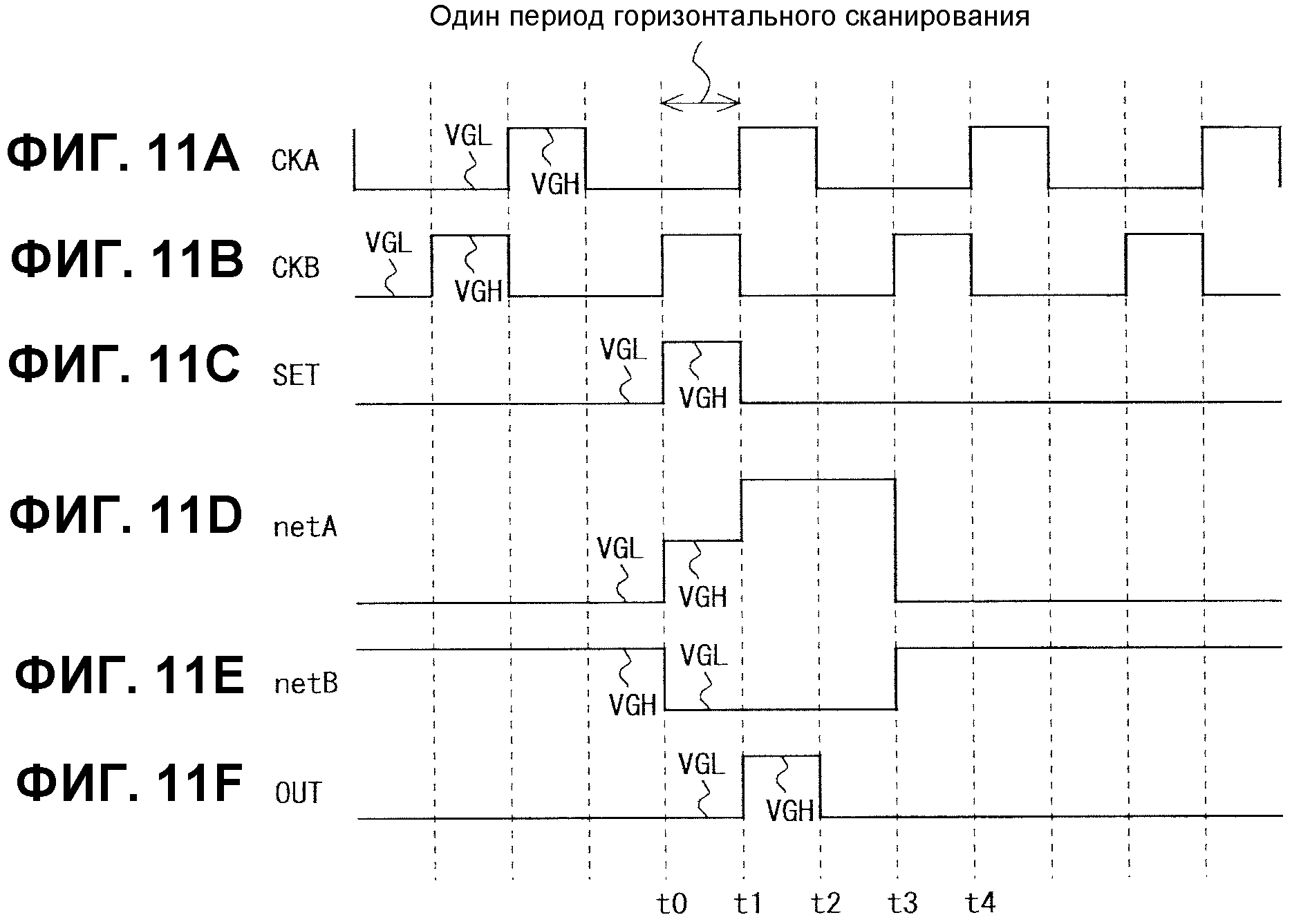

Со ссылкой на Фиг.9 и 11A-11F ниже будет описана работа каждого каскада (бистабильной схемы) сдвигового регистра 810. Отметим, что Фиг.11A-11F показывают формы сигнала для бистабильной схемы SR(1) первого каскада, а что касается бистабильных схем SR(2)-SR(n) второго и последующих каскадов, такие же формы сигнала, как показанные на Фиг.11A-11F, появляются задержанными на один период горизонтального сканирования. Другими словами, n бистабильных схем SR(1)-SR(n) выполняют одну и ту же операцию за исключением привязки по времени. Соответственно, в последующем, описание будет дано с фокусированием только на одной бистабильной схеме SR(1) первого каскада.

Во время работы устройства отображения, первый тактовый сигнал CKA, имеющий форму сигнала, показанную на Фиг.11A, подается на входной вывод 81, а второй тактовый сигнал CKB, имеющий форму сигнала, показанную на Фиг.11B, подается на входной вывод 83. Во время периодов до момента t0 времени, потенциалами сигнала SET установки, netA и сигнала OUT состояния является VGL, а потенциалом netB является VGH.

При достижении момента t0 времени, импульс сигнала SET установки подается на входной вывод 82. Соответственно, тонкопленочные транзисторы T82 и T86 помещаются во включенное состояние (проводящее состояние). В дополнение, в момент t0 времени, потенциал второго тактового сигнала CKB, подаваемого на входной вывод 83, изменяется с VGL на VGH. Соответственно, тонкопленочный транзистор T85 помещается во включенное состояние. Посредством помещения тонкопленочного транзистора T82 во включенное состояние, потенциал netA приводится к VGH и, таким образом, тонкопленочный транзистор T81 помещается во включенное состояние. В дополнение, тонкопленочный транзистор T85 помещается во включенное состояние, и тонкопленочный транзистор T86 также помещается во включенное состояние и, таким образом, ток протекает с вывода стока тонкопленочного транзистора T85 на вывод истока тонкопленочного транзистора T86. Отсюда, потенциал netB приводится к VGL. Соответственно, тонкопленочные транзисторы T83 и T84 помещаются в отключенное состояние (непроводящее состояние). Посредством помещения тонкопленочного транзистора T83 в отключенное состояние, потенциал netA не уменьшается в течение периода от t0 до t1.

Тонкопленочный транзистор T81, как описано выше, помещается во включенное состояние в момент t0 времени, но потенциал первого тактового сигнала CKA, подаваемого на входной вывод 81, имеет значение VGL в течение периода от t0 до t1. Отсюда, потенциал сигнала OUT состояния, выдаваемого с выходного вывода 89, сохраняется на VGL. В это время, напряжение с амплитудой «VGH-VGL» прикладывается между затвором и истоком тонкопленочного транзистора T81 (между двумя выводами конденсатора C81).

При достижении момента t1 времени, потенциалы сигнала SET установки и второй тактовый сигнал CKB изменяются с VGH на VGL. Соответственно, тонкопленочные транзисторы T82, T85 и T86 помещаются в отключенное состояние. В дополнение, в момент t1 времени, потенциал первого тактового сигнала CKA изменяется с VGL на VGH. В это время, поскольку напряжение между затвором и истоком тонкопленочного транзистора T81 поддерживается на «VGH-VGL» конденсатором C81, тонкопленочный транзистор T81 находится во включенном состоянии. В дополнение, формируется паразитная емкость (не показана) между затвором и стоком тонкопленочного транзистора T81. Вследствие вышеприведенного, потенциал стока тонкопленочного транзистора T81 увеличивается с увеличением потенциала на входном выводе 81 и, таким образом, потенциал netA дополнительно увеличивается от VGH из-за паразитной емкости. Как результат, большое напряжение прикладывается к выводу затвора тонкопленочного транзистора T81 и, таким образом, потенциал сигнала OUT состояния увеличивается до потенциала VGH первого тактового сигнала CKA. Соответственно, линия шины затвора, присоединенная к выходному выводу 89 бистабильной схемы, помещается в выбранное состояние. Между тем, во время периода от t1 до t2, поскольку тонкопленочный транзистор T85 находится в отключенном состоянии, потенциал netB поддерживается на VGL. Отсюда, в течение этого периода, тонкопленочный транзистор T83 поддерживается в отключенном состоянии и, таким образом, также поддерживается потенциал netA. Отметим, что для увеличения потенциала netA в момент t1 времени, потенциал в идеале увеличивается до удвоенного уровня VGH, но, на практике, потенциал не увеличивается до удвоенного уровня VGH вследствие наличия паразитных емкостей, сопротивлений, и т.д., у netA, входного вывода 81, выходного вывода 89 и тонкопленочного транзистора T81.

При достижении момента t2 времени, потенциал первого тактового сигнала CKA изменяется с VGH на VGL. В момент t2 времени, поскольку потенциал netA является более высоким, чем VGH, когда потенциал стока тонкопленочного транзистора T81 уменьшается с уменьшением потенциала на входном выводе 81, ток протекает с вывода истока на вывод стока тонкопленочного транзистора T81. Соответственно, потенциал выходного вывода 89, то есть потенциал сигнала OUT состояния, уменьшается до VGL. Соответственно, линия шины затвора, присоединенная к выходному выводу 89 бистабильной схемы, помещается в невыбранное состояние. Отметим, что, во время периода с t2 до t3, поскольку потенциал второго тактового сигнала CKB имеет значение VGL и, таким образом, тонкопленочный транзистор T85 находится в отключенном состоянии, потенциал netB поддерживается на VGL. Отсюда, в течение этого периода, тонкопленочный транзистор T83 поддерживается в отключенном состоянии, и также поддерживается потенциал netA.

При достижении момента t3 времени, потенциал второго тактового сигнала CKB изменяется с VGL на VGH. Отсюда, тонкопленочный транзистор T85 помещается во включенное состояние. Соответственно, потенциал netB приводится к VGH и, таким образом, тонкопленочные транзисторы T83 и T84 помещаются во включенное состояние. Посредством помещения тонкопленочного транзистора T83 во включенное состояние, потенциал netA приводится к VGL и, таким образом, тонкопленочный транзистор T81 помещается в отключенное состояние. В дополнение, посредством помещения тонкопленочного транзистора T84 во включенное состояние, потенциал сигнала OUT состояния поддерживается на VGL.

Работа, такая как описанная выше, последовательно выполняется на n бистабильных схемах SR(1)-SR(n), так чтобы привязка по времени задерживалась на один период горизонтального сканирования. Соответственно, в каждом периоде кадровой развертки, n линий шины затвора GL1-GLn последовательно помещаются в выбранное состояние на один период горизонтального сканирования.

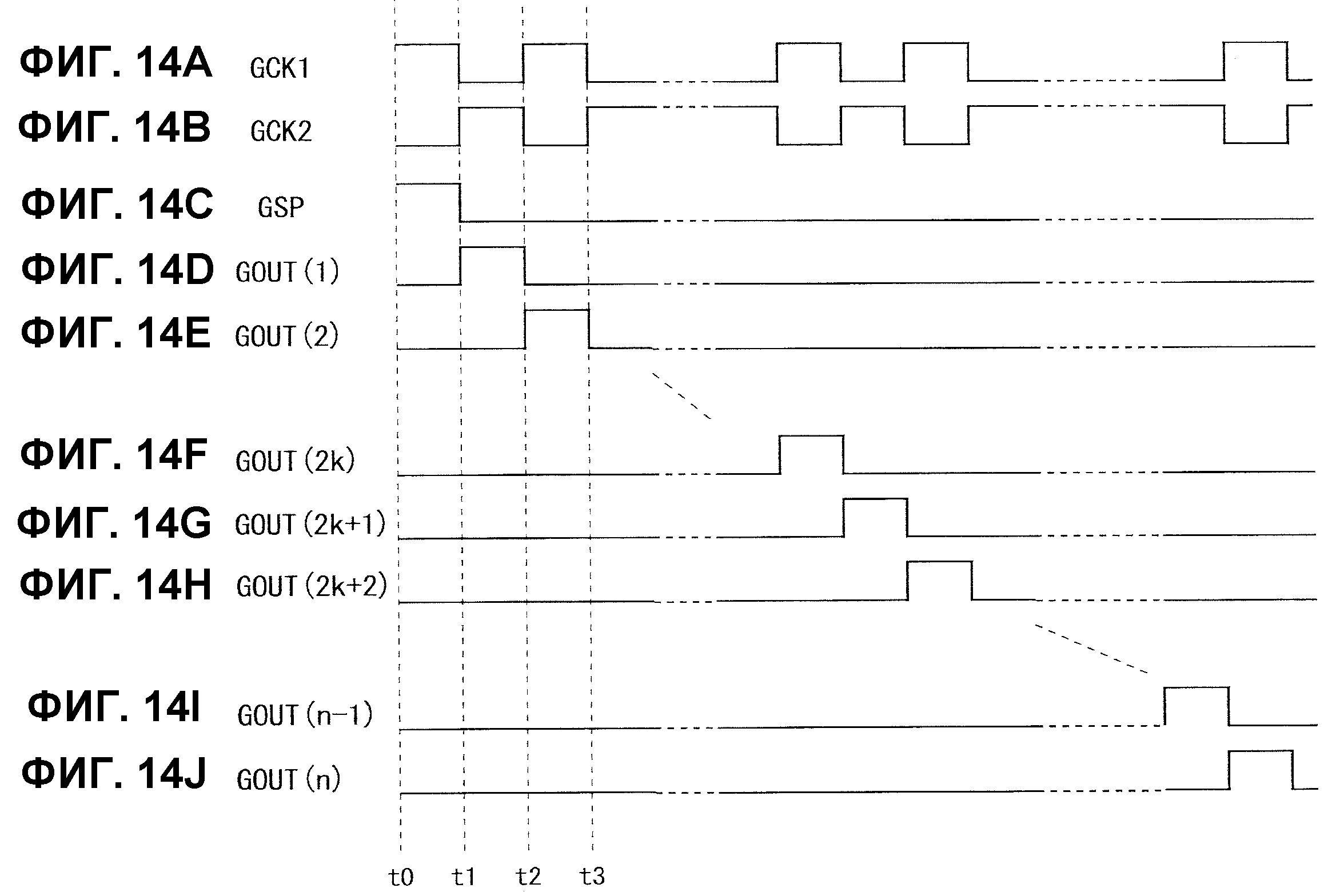

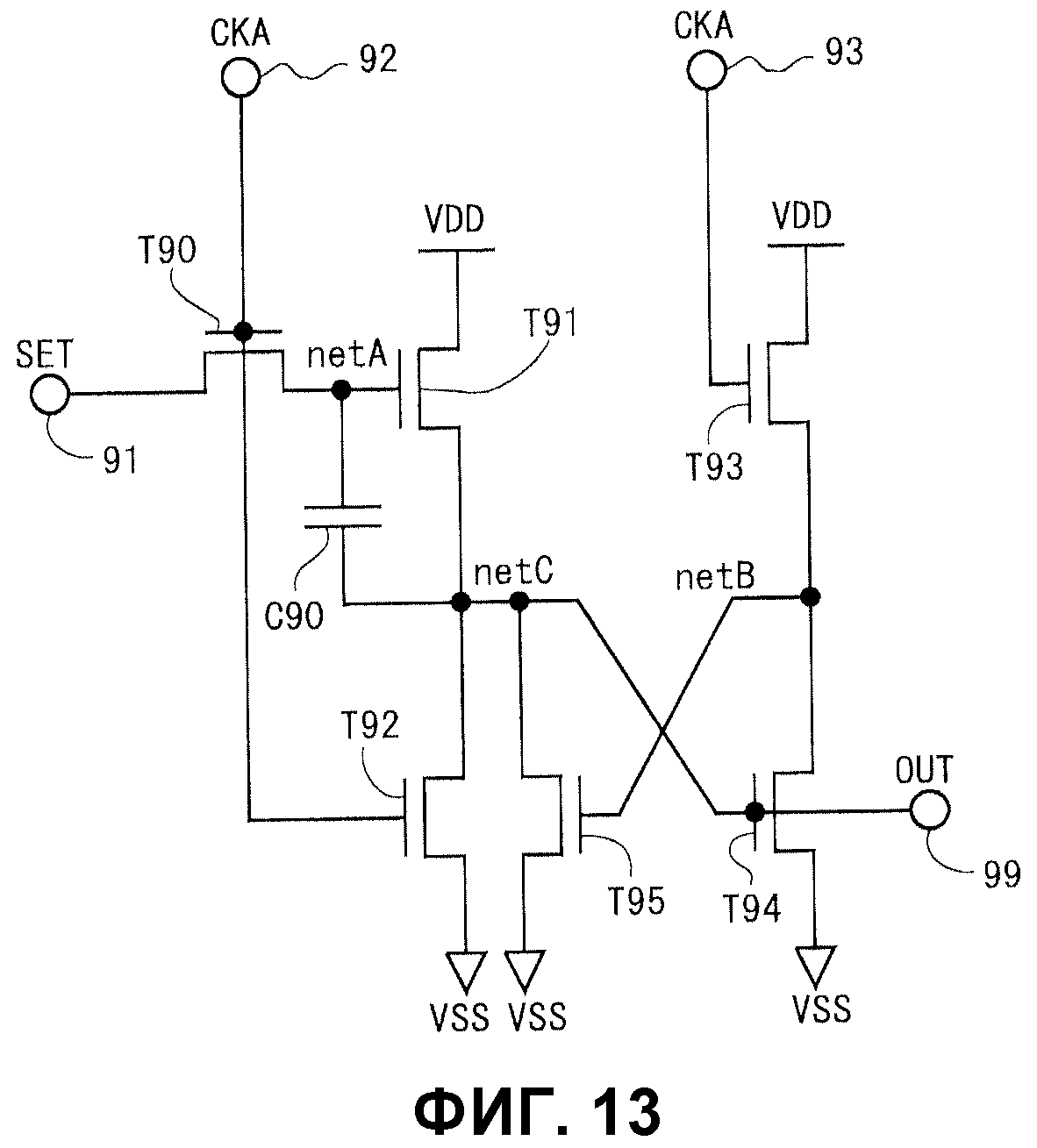

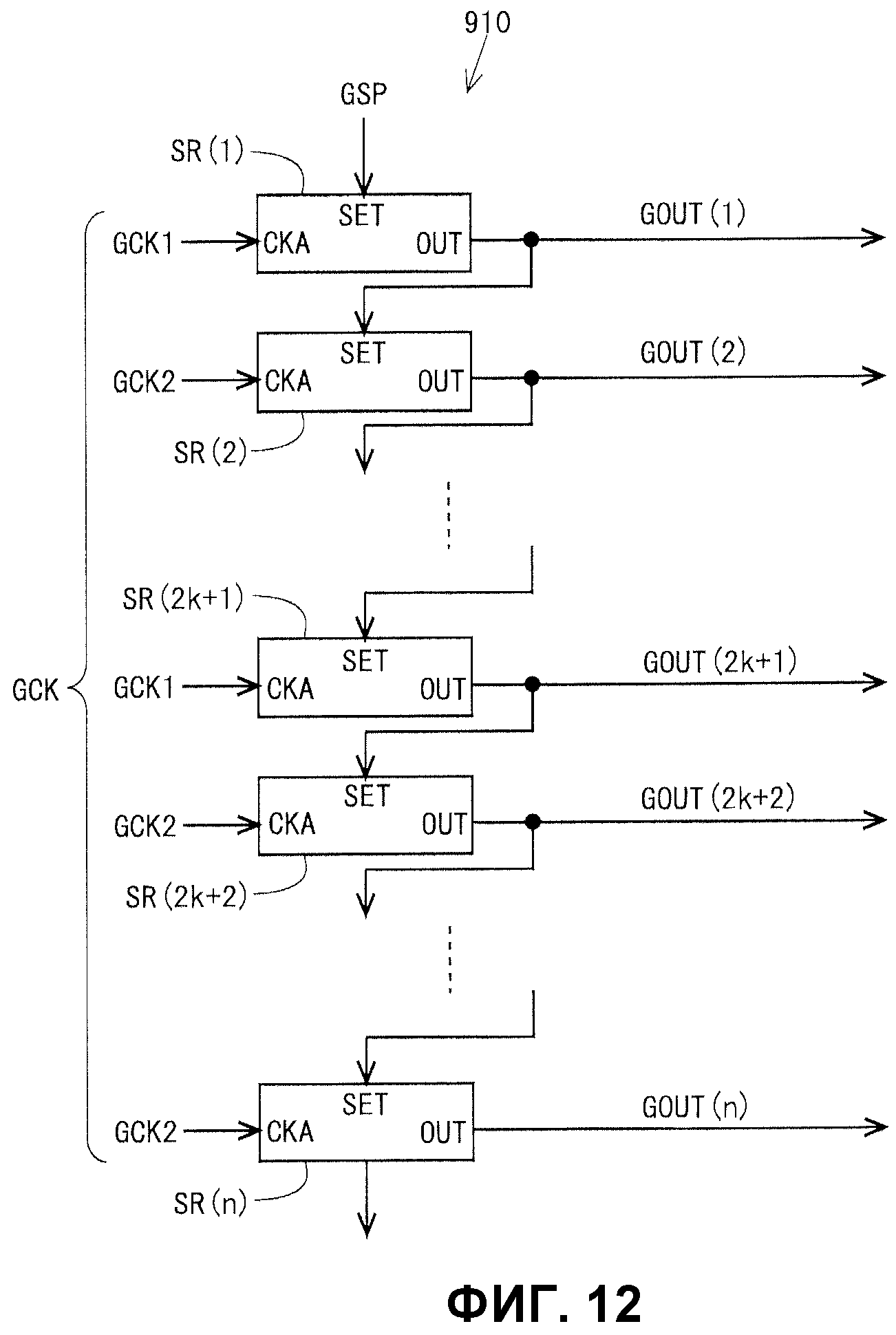

В еще одном примере, случай, в котором схема сдвигового регистра, раскрытая в выложенной заявке № 62-234298 на патент Японии, применена к драйверу затвора устройства отображения, будет описан со ссылкой на Фиг.12, 13, 14A-14J и 15A-15D. Фиг.12 - структурная схема, показывающая конфигурацию сдвигового регистра 910, включенного в драйвер затвора. Как показано на Фиг.12, сдвиговый регистр 910 состоит из n бистабильных схем SR(1)-SR(n). На сдвиговый регистр 910 подаются двухфазные тактовые сигналы GCK1 и GCK2 и начальный импульсный сигнал затвора GSP, который является сигналом для запуска сканирования линий шины затвора. Каждая бистабильная схема снабжена входным выводом для приема любого одного из двухфазных тактовых сигналов в качестве первого тактового сигнала CKA; входным выводом для приема начального импульсного сигнала затвора GSP или сигнала OUT состояния, выдаваемого из его первого каскада, в качестве сигнала SET установки; и выходной вывод для выдачи сигнала OUT состояния.

Фиг.13 - принципиальная схема, показывающая конфигурацию одного каскада (одной бистабильной схемы) сдвигового регистра 910. Бистабильная схема включает в себя шесть тонкопленочных транзисторов T90-T95 и конденсатор C90. В дополнение, бистабильная схема имеет входные выводы для линии VDD электропитания, которая питает относительно высокоуровневый потенциал VGH, и входные выводы для линии VSS электропитания, которая питает относительно низкоуровневый потенциал VGL, а также три входных вывода 91-93 и один выходной вывод 99. Отметим, что входной вывод, который принимает сигнал SET установки, обозначен номером 91 ссылки, один из входных выводов, который принимает первый тактовый сигнал CKA, обозначен номером 92 ссылки, а другой один из входных выводов, который принимает первый тактовый сигнал CKA, обозначен номером 93 ссылки.

Вывод истока тонкопленочного транзистора T90, вывод затвора тонкопленочного транзистора T91 и один конец конденсатора C90 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netA» ради удобства. В дополнение, вывод истока тонкопленочного транзистора T93, вывод стока тонкопленочного транзистора T94 и вывод затвора тонкопленочного транзистора T95 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netB» ради удобства. Более того, вывод истока тонкопленочного транзистора T91, вывод стока тонкопленочного транзистора T92, вывод затвора тонкопленочного транзистора T94, вывод стока тонкопленочного транзистора T95 и другой конец конденсатора C90 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netC» ради удобства.

Тонкопленочный транзистор T90 присоединен на своем выводе затвора к входному выводу 92, присоединен на своем выводе стока к входному выводу 91, присоединен на своем выводе истока к netA. Тонкопленочный транзистор T91 присоединен на своем выводе затвора к netA, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к netC. Тонкопленочный транзистор T92 присоединен на своем выводе затвора к входному выводу 92, присоединен на своем выводе стока к netC и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T93 присоединен на своем выводе затвора к входному выводу 93, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к netB. Тонкопленочный транзистор T94 присоединен на своем выводе затвора к netC и выходному выводу 99, присоединен на своем выводе стока к netB и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T95 присоединен на своем выводе затвора к netB, присоединен на своем выводе стока к netC и присоединен на своем выводе истока к линии VSS электропитания. Конденсатор C90 присоединен на одном своем конце к netA и присоединен на своем другом конце к netC.

В конфигурации, такой как описанная выше, двухфазные тактовые сигналы GCK1 и GCK2, имеющие формы сигнала, показанные на Фиг.14A и 14B, и начальный импульсный сигнал затвора GSP, имеющий форму сигнала, показанную на Фиг.14C, подаются на сдвиговый регистр 910. Затем, сигналы GOUT(1)-GOUT(n) сканирования, которые последовательно переходят на высокий уровень в течение одного периода горизонтального сканирования, как показано на Фиг.14D-14J, выдаются из сдвигового регистра 910.

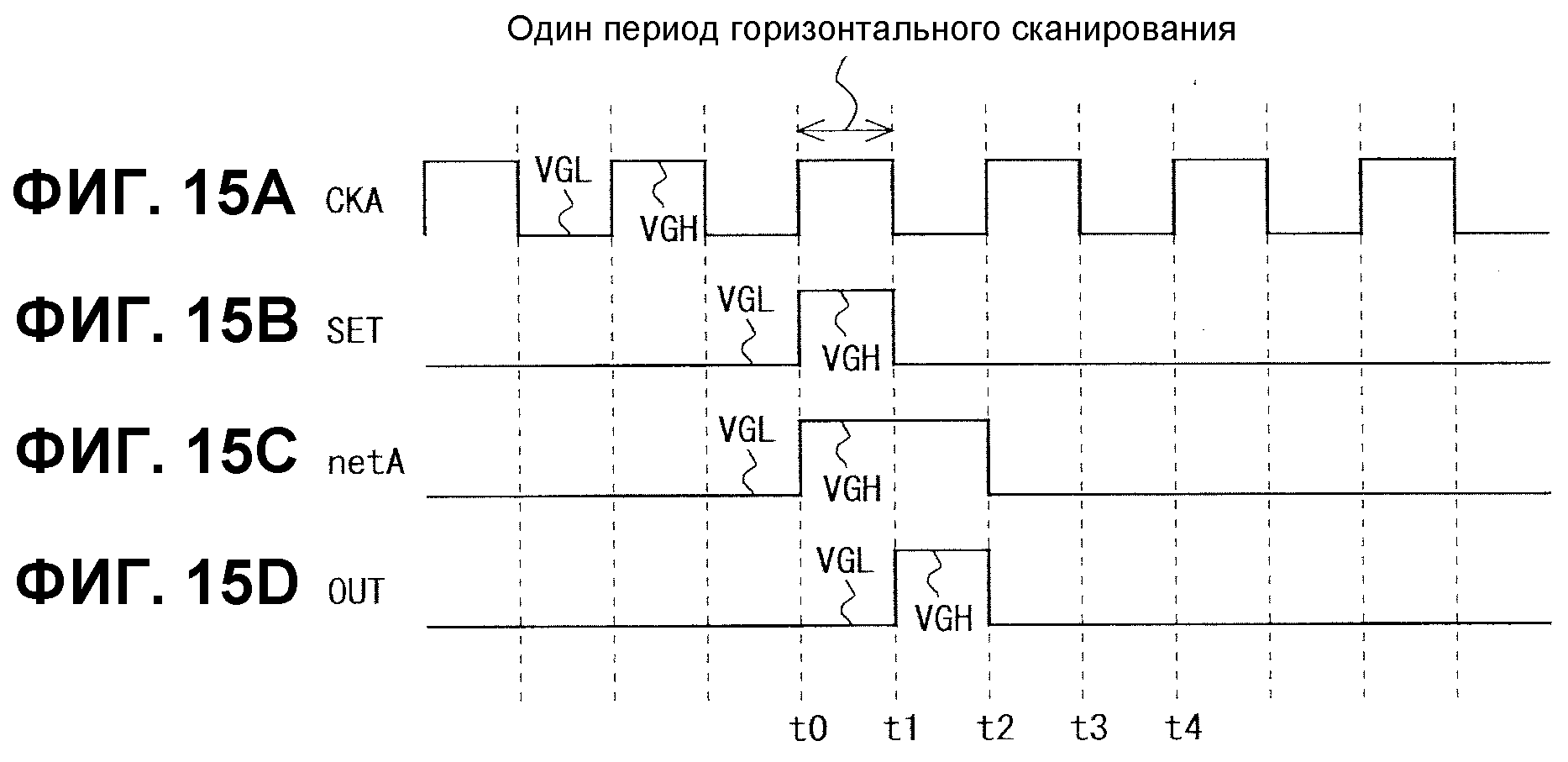

Со ссылкой на Фиг.13 и 14A-14J и 15A-15D, ниже будет описана работа каждого каскада (бистабильной схемы) сдвигового регистра 910. Отметим, что Фиг.15A-15D показывают формы сигнала для бистабильной схемы SR(1) первого каскада, а что касается бистабильных схем SR(2)-SR(n) второго и последующих каскадов, такие же формы сигнала, как показанные на Фиг.15A-15D, появляются задержанными на один период горизонтального сканирования. Другими словами, n бистабильных схем SR(1)-SR(n) выполняют одну и ту же операцию за исключением привязки по времени. Соответственно, в последующем, описание будет дано с фокусированием только на одной бистабильной схеме SR(1) первого каскада.

Во время работы устройства отображения, первый тактовый сигнал CKA, имеющий форму сигнала, показанную на Фиг.15A, подается на входной вывод 91. Во время периодов до момента t0 времени, потенциалами сигнала SET установки, netA и сигнала OUT состояния является VGL.

При достижении момента t0 времени, потенциал первого тактового сигнала CKA изменяется с VGL на VGH. Соответственно, тонкопленочные транзисторы T90, T92 и T93 помещаются во включенное состояние. Посредством помещения тонкопленочного транзистора T93 во включенное состояние, потенциал netB увеличивается до потенциала VGH линии VDD электропитания и, таким образом, тонкопленочный транзистор T95 помещается во включенное состояние. В дополнение, в момент t0 времени, потенциал сигнала SET установки изменяется с VGL на VGH. Поскольку, как описано выше, тонкопленочный транзистор T90 помещается во включенное состояние, потенциал netA увеличивается до потенциала VGH сигнала SET установки. В это время, поскольку напряжение между затвором и истоком тонкопленочного транзистора T91 (между двумя выводами конденсатора C90) имеет значение «VGH-VGL», тонкопленочный транзистор T91 помещается во включенное состояние. Однако, поскольку тонкопленочные транзисторы T92 и T95 находятся во включенном состоянии, потенциал на выходном выводе 99 (потенциал сигнала OUT состояния) поддерживается на VGL.

При достижении момента t1 времени, потенциалы сигнала SET установки и первый тактовый сигнал CKA изменяются с VGL на VGH. Соответственно, тонкопленочные транзисторы T90, T92, T93 и T95 помещаются в отключенное состояние. В это время, напряжение между затвором и истоком тонкопленочного транзистора T91 поддерживается на «VGH-VGL» конденсатором C90. Отсюда, тонкопленочный транзистор T91 поддерживается во включенном состоянии. Здесь, поскольку, как описано выше, тонкопленочные транзисторы T92 и T95 находятся в отключенном состоянии, ток не протекает между стоком и истоком тонкопленочных транзисторов T92 и T95, и, таким образом, потенциал выходного вывода 99 увеличивается до потенциала VGH линии VDD электропитания. Соответственно, линия шины затвора, присоединенная к выходному выводу 99 бистабильной схемы, помещается в выбранное состояние.

При достижении момента t2 времени, потенциал первого тактового сигнала CKA изменяется с VGL на VGH. Соответственно, тонкопленочные транзисторы T90, T92, T93 и T95 помещаются во включенное состояние. В это время, поскольку потенциал сигнала SET установки имеет значение VGL, потенциал netA уменьшается от VGH до VGL и, таким образом, тонкопленочный транзистор T91 помещается в отключенное состояние. В дополнение, поскольку, как описано выше, тонкопленочные транзисторы T92 и T95 находятся во включенном состоянии, заряд, накопленный в netC, стекает по линиям VSS электропитания через тонкопленочные транзисторы T92 и T95, и, таким образом, потенциал на выходном выводе 99 уменьшается с VGH до VGL.

Работа, такая как описанная выше, последовательно выполняется на описанных выше n бистабильных схемах SR(1)-SR(n), так чтобы привязка по времени задерживалась на один период горизонтального сканирования. Соответственно, в каждом периоде кадровой развертки, n линий затвора GL1-GLn последовательно помещаются в выбранное состояние на один период горизонтального сканирования.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[Патентный документ 1] Опубликованный перевод на японский язык заявки PCT № 6-505605

[Патентный документ 2] Выложенная заявка № 62-234298 на патент Японии

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ПРОБЛЕМЫ, РЕШАЕМЫЕ ИЗОБРЕТЕНИЕМ

Согласно конфигурации, раскрытой в опубликованном переводе на японский язык заявки PCT № 6-505605 (см. Фиг.9), однако, перекрестная помеха может возникать вследствие изменения потенциала тактового сигнала, подаваемого на сдвиговый регистр, и емкости перекрытия в тонкопленочном транзисторе. Это будет описано ниже.

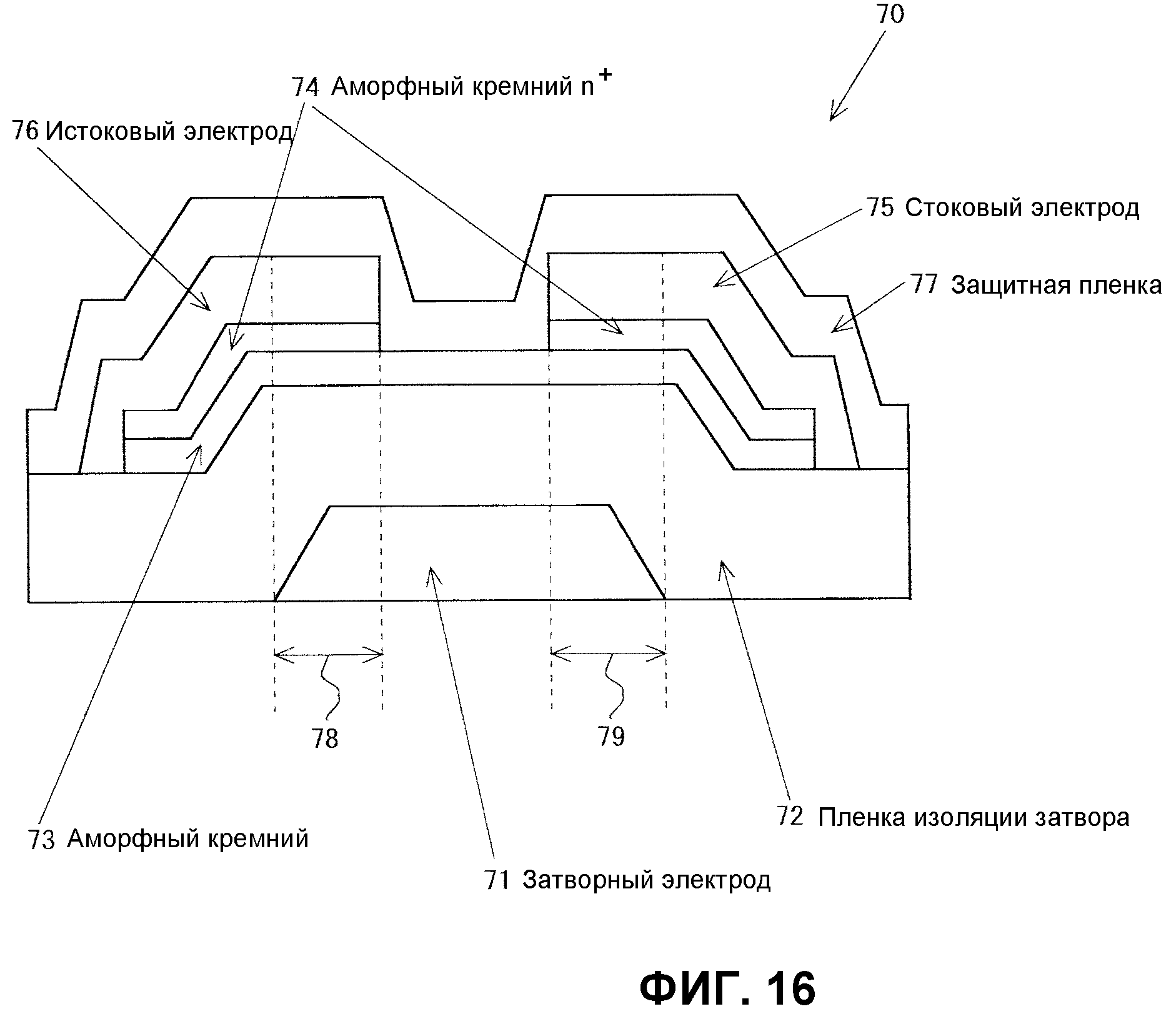

Фиг.16 - вид в поперечном разрезе обычного TFT 70 на аморфном кремнии. Как показано на Фиг.16, TFT 70 на аморфном кремнии состоит из затворного электрода 71, сформированного на стеклянной подложке (не показана); изолирующей затвор пленки 72, сформированной, чтобы покрывать затворный электрод 71; аморфного кремния 73, сформированного на изолирующей затвор пленке 72; аморфных кремниев 74 n+, сформированных на аморфном кремнии 73; стокового электрода 75 и истокового электрода 76, которые сформированы на аморфных кремниях 74 n+, соответственно; и защитной пленки 77, сформированной на стоковом электроде 75 и истоковом электроде 76. Здесь, в области, обозначенной номером 78 ссылки на Фиг.16, истоковый электрод 76 и затворный электрод 71 перекрывают друг друга на виде сверху (истоковый электрод 76 и затворный электрод 71 расположены один над другим с изолирующей затвор пленкой 72, и т.д., между ними) и, таким образом, емкость Cgs перекрытия возникает между истоковым электродом 76 и затворным электродом 71. Подобным образом, в области, обозначенной номером 79 ссылки на Фиг.16, емкость Cgd перекрытия возникает между стоковым электродом 75 и затворным электродом 71. Отметим, что величины емкостей Cgs и Cgd нормально пропорциональны площадям их каналов. Более точно, когда у длины канала, длиной, обозначенной номером 78 ссылки на Фиг.16, является Lgs, длиной, обозначенной номером 79 ссылки является Lgd, а ширина канала имеет значение W, величина емкости Cgs перекрытия пропорциональна «W×Lgs», а величина емкости Cgd перекрытия пропорциональна «W×Lgd».

Далее, в конфигурации, показанной на Фиг.9, обращено внимание на тонкопленочный транзистор T81. Потенциал первого тактового сигнала CKA подается на вывод стока тонкопленочного транзистора T81. Как показано на Фиг.11A, коэффициент заполнения первого тактового сигнала CKA (термин «коэффициент заполнения», используемый в материалах настоящей заявки, указывает ссылкой на отношение периода, в течение которого поддерживается высокоуровневый потенциал, к циклу, в котором повторяются высокоуровневый потенциал и низкоуровневый потенциал) имеет значение одной трети. Другими словами, потенциал первого тактового сигнала CKA приводится к VGH (высокому уровню) не только в течение периода, во время которого линия шины затвора, присоединенная к выходному выводу 89 бистабильной схемы, включающей в себя тонкопленочный транзистор T81, должна помещаться в выбранное состояние, но приводится к VGH каждые три периода горизонтального сканирования по всем периодам, в течение которых работает устройство отображения.

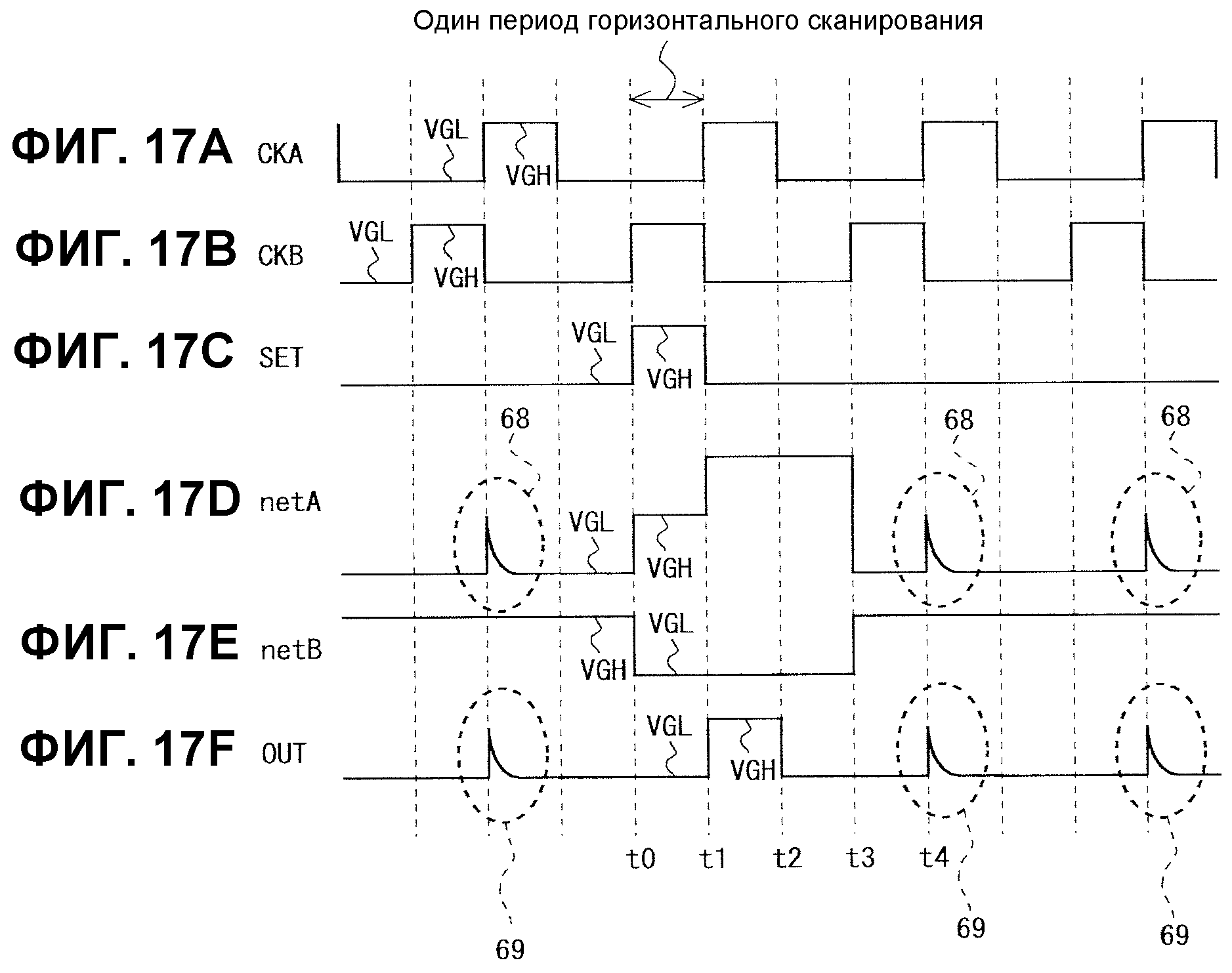

Между тем, когда потенциал первого тактового сигнала CKA изменяется с VGL на VGH, потенциал стока тонкопленочного транзистора T81 увеличивается и, таким образом, потенциал netA увеличивается из-за емкости Cgd перекрытия в тонкопленочном транзисторе T81. Однако, поскольку, как показано на Фиг.11E, в течение периодов, иных чем период с t0 до t3, потенциал netB имеет значение VGH и, таким образом, тонкопленочный транзистор T83 находится во включенном состоянии, потенциал netA немедленно уменьшается до VGL, как указано номером 68 ссылки на Фиг.17D. Однако, когда напряжение между затвором и истоком тонкопленочного транзистора T81 становится более высоким, чем пороговое напряжение, вследствие такого увеличения потенциала netA, тонкопленочный транзистор T81 помещается во включенное состояние. Соответственно, как указано номером 69 ссылки на Фиг.17F, потенциал сигнала OUT состояния временно переходит на высокий уровень в течение периодов, иных чем выбранный период (период, в течение которого линия шины затвора, присоединенная к выходному выводу каждой бистабильной схемы должна помещаться в выбранное состояние). Затем, тонкопленочные транзисторы в частях формирования пикселя, присоединенных к линии шины затвора, через которую передается высокоуровневый сигнал OUT состояния, помещаются во включенное состояние. Таким образом, перекрестная помеха возникает в устройстве отображения, ухудшая качество отображения. Отметим, что такое явление возникает не только в сдвиговом регистре, имеющем конфигурацию, показанную на Фиг.9, но может возникать в сдвиговом регистре, имеющем конфигурацию, в которой тактовый сигнал возбуждения (первый тактовый сигнал CKA в примере, показанном на Фиг.9) подается на другой проводящий вывод выходного транзистора (транзистора, который присоединен на своем одном проводящем выводе к выходному выводу в бистабильной схеме, и который управляет потенциалом сигнала состояния посредством флуктуации потенциала на управляющем выводе транзистора).

В дополнение, согласно конфигурации, раскрытой в выложенной заявке № 62-234298 на патент Японии (см. Фиг.13) постоянный высокоуровневый потенциал VDD, но не тактовый сигнал возбуждения, подается на вывод стока тонкопленочного транзистора T91, функционирующего в качестве выходного транзистора. Отсюда, перекрестная помеха вследствие флуктуаций потенциала стока тонкопленочного транзистора T91 не возникает в устройстве отображения. Однако, поскольку тонкопленочный транзистор T91 помещен во включенное состояние на всем протяжении одного периода горизонтального сканирования непосредственно перед выбранным периодом, току, протекающему с линии VDD электропитания в netC через тонкопленочный транзистор T91, необходимо течь по линиям VSS электропитания через тонкопленочные транзисторы T92 и T95 во время периода перед тем, как начинается выбранный период. Чтобы сделать так, площадям каналов тонкопленочных транзисторов T92 и T95 необходимо увеличиваться, давая в результате увеличение размера конструкции для монтажа драйвера затвора. В дополнение, поскольку ток не обязательно протекает через тонкопленочные транзисторы T92 и T95 во время периода горизонтального сканирования непосредственно перед выбранным периодом, потребляемая мощность увеличивается.

Поэтому, цель настоящего изобретения состоит в том, чтобы реализовать устройство отображения, способное к пресечению ухудшения качества отображения, вызванного перекрестной помехой, не вызывая увеличения размера конструкции или увеличения потребляемой мощности.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ПРОБЛЕМ

Первый аспект настоящего изобретения направлен на сдвиговый регистр, содержащий множество бистабильных схем, имеющих первое состояние и второе состояние, и последовательно присоединенных друг к другу, при этом множество бистабильных схем последовательно помещаются в первое состояние на основании двухфазных тактовых сигналов, включающих в себя первый и второй тактовый сигнал, при этом первый и второй тактовые сигналы подаются из внешнего источника каждой бистабильной схемы и периодически повторяют высокоуровневый потенциал и низкоуровневый потенциал, при этом, каждая бистабильная схема включает в себя:

выходной узел, который выдает сигнал состояния, указывающий любое одно из первого состояния и второго состояния;

первый транзистор, имеющий второй электрод, на который подается высокоуровневый потенциал, и третий электрод, присоединенный к выходному узлу;

второй транзистор, имеющий первый электрод, на который подается первый тактовый сигнал, и третий электрод, присоединенный к первому узлу, присоединенному к первому электроду первого транзистора;

часть заряда второго узла для заряда второго узла на основании сигнала состояния, выдаваемого из бистабильной схемы предыдущего каскада бистабильной схемы, при этом второй узел является присоединенным ко второму электроду второго транзистора;

часть разряда второго узла для разряда второго узла на основании сигнала состояния, выдаваемого из бистабильной схемы следующего каскада бистабильной схемы;

часть разряда первого узла для разряда первого узла на основании второго тактового сигнала; и

часть разряда выходного узла для разряда выходного узла на основании второго тактового сигнала.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

площадь канала первого транзистора является большей, чем у второго транзистора.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя конденсатор, присоединенный на своем одном конце ко второму узлу и присоединенный на своем другом конце к выходному узлу.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

в каждой бистабильной схеме,

часть разряда второго узла включает в себя третий транзистор, имеющий первый электрод, на который подается сигнал состояния, выдаваемый из бистабильной схемы следующего каскада бистабильной схемы, второй электрод, к которому присоединен второй узел, и третий электрод, на который выдается низкоуровневый потенциал,

часть разряда первого узла включает в себя четвертый транзистор, имеющий первый электрод, на который выдается второй тактовый сигнал, второй электрод, к которому присоединен первый узел, и третий электрод, на который выдается низкоуровневый потенциал, и

часть разряда выходного узла включает в себя пятый транзистор, имеющий первый электрод, на который выдается второй тактовый сигнал, второй электрод, к которому присоединен выходной узел, и третий электрод, на который выдается низкоуровневый потенциал.

Согласно пятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

в каждой бистабильной схеме,

часть заряда второго узла включает в себя шестой транзистор, имеющий первый электрод, на который подается сигнал состояния, выдаваемый из бистабильной схемы предыдущего каскада бистабильной схемы, второй электрод, на который подается высокоуровневый потенциал, и третий электрод, к которому присоединен второй узел.

Согласно шестому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

в каждой бистабильной схеме,

часть заряда второго узла включает в себя седьмой транзистор, имеющий первый электрод и второй электрод, на которые подается сигнал состояния, выдаваемый из бистабильной схемы предыдущего каскада бистабильной схемы, и третий электрод, к которому присоединен второй узел.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

все транзисторы, включенные в каждую бистабильную схему, являются тонкопленочными транзисторами n-канального типа.

Восьмой аспект настоящего изобретения направлен на схему возбуждения линий сигнала сканирования устройства отображения, которая возбуждает множество линий сигнала сканирования, скомпонованных в блоке отображения, при этом схема возбуждения линий сигнала сканирования содержит сдвиговый регистр согласно любому одному из с первого по седьмой аспектам настоящего изобретения, при этом,

предусмотрено множество бистабильных схем, с тем чтобы иметь соответствие один к одному с множеством линий сигнала сканирования, и

каждая бистабильная схема подает сигнал состояния, выдаваемый из выходного узла, на свою соответствующую линию сигнала сканирования в качестве сигнала сканирования.

Девятый аспект настоящего изобретения направлен на устройство отображения, включающее в себя блок отображения и содержащее схему возбуждения линий сигнала сканирования согласно восьмому аспекту настоящего изобретения.

Десятый аспект настоящего изобретения направлен на способ возбуждения сдвигового регистра, включающего в себя бистабильные схемы, имеющие первое состояние и второе состояние и последовательно соединенные друг с другом, при этом множество бистабильных схем последовательно помещаются в первом состоянии на основании двухфазных тактовых сигналов, включающих в себя первый и второй тактовый сигнал, при этом первый и второй тактовый сигналы подаются из внешнего источника каждой бистабильной схемы и периодически повторяют высокоуровневый потенциал и низкоуровневый потенциал, при этом способ содержит:

первый этап возбуждения, на котором вызывают предварительное состояние для переключения каждой бистабильной схемы из второго состояния в первое состояние;

второй этап возбуждения, на котором помещают бистабильную схему, находящуюся в предварительном состоянии, в первое состояние; и

третий этап возбуждения, на котором переключают бистабильную схему из первого состояния во второе состояние, при этом, каждая бистабильная схема включает в себя:

выходной узел, который выдает сигнал состояния, указывающий любое одно из первого состояния и второго состояния;

первый транзистор, имеющий второй электрод, на который подается высокоуровневый потенциал, и третий электрод, присоединенный к выходному узлу;

второй транзистор, имеющий первый электрод, на который подается первый тактовый сигнал, третий электрод, присоединенный к первому узлу, присоединенному к первому электроду первого транзистора, и меньшую площадь канала, чем первый транзистор;

часть заряда второго узла для заряда второго узла на основании предварительно определенного сигнала установки, при этом второй узел является присоединенным ко второму электроду второго транзистора;

часть разряда второго узла для разряда второго узла на основании предварительно определенного сигнала сброса;

часть разряда первого узла для разряда первого узла на основании второго тактового сигнала; и

часть разряда выходного узла для разряда выходного узла на основании второго тактового сигнала,

при этом на первом этапе возбуждения второй узел заряжается частью заряда второго узла на основании сигнала установки,

на втором этапе возбуждения первый узел заряжается вторым транзистором, являющимся помещенным в проводящее состояние, на основании первого тактового сигнала, и

на третьем этапе возбуждения второй узел разряжается частью разряда второго узла на основании сигнала сброса, и первый узел разряжается частью разряда первого узла, и выходной узел разряжается частью разряда выходного узла, на основании второго тактового сигнала.

Согласно одиннадцатому аспекту настоящего изобретения, в десятом аспекте настоящего изобретения, в каждой бистабильной схеме,

часть разряда второго узла включает в себя третий транзистор, имеющий первый электрод, на который подается сигнал сброса, второй электрод, к которому присоединен второй узел, и третий электрод, на который подается низкоуровневый потенциал,

часть разряда первого узла включает в себя четвертый транзистор, имеющий первый электрод, на который подается второй тактовый сигнал, второй электрод, к которому присоединен первый узел, и третий электрод, на который подается низкоуровневый потенциал, и

часть разряда выходного узла включает в себя пятый транзистор, имеющий первый электрод, на который подается второй тактовый сигнал, второй электрод, к которому присоединен выходной узел, и третий электрод, на который подается низкоуровневый потенциал, и

на третьем этапе возбуждения,

третий транзистор помещается в проводящее состояние на основании сигнала сброса, и

четвертый транзистор помещается в проводящее состояние и пятый транзистор помещается в проводящее состояние на основании второго тактового сигнала.

Согласно двенадцатому аспекту настоящего изобретения, в десятом аспекте настоящего изобретения,

часть заряда второго узла включает в себя шестой транзистор, имеющий первый электрод, на который подается сигнал установки, второй электрод, на который подается высокоуровневый потенциал, и третий электрод, к которому присоединен второй узел, и

на первом этапе возбуждения, шестой транзистор помещается в проводящее состояние на основании сигнала установки.

Согласно тринадцатому аспекту настоящего изобретения, в десятом аспекте настоящего изобретения,

часть заряда второго узла включает в себя седьмой транзистор, имеющий первый электрод и второй электрод, на который подается сигнал установки, и третий электрод, к которому присоединен второй узел, и

на первом этапе возбуждения, седьмой транзистор помещается в проводящее состояние на основании сигнала установки.

РЕЗУЛЬТАТЫ ИЗОБРЕТЕНИЯ

Согласно первому аспекту настоящего изобретения, постоянный высокоуровневый потенциал подается на второй электрод первого транзистора (обычно, стоковый электрод тонкопленочного транзистора), который функционирует в качестве выходного транзистора. Отсюда, помещение первого транзистора во включенное состояние (проводящее состояние) вследствие изменения потенциала второго электрода первого транзистора, не возникает во время периодов, иных чем выбранный период. В дополнение, первый электрод первого транзистора присоединен к первому узлу. Что касается второго транзистора, имеющего третий электрод, присоединенный к первому узлу, первый тактовый сигнал подается на первый электрод, и второй электрод присоединен ко второму узлу. Здесь, второй узел заряжается на основании сигнала состояния, выдаваемого из бистабильной схемы предыдущего каскада каждой бистабильной схемы, и разряжается на основании сигнала состояния, выдаваемого из бистабильной схемы следующего каскада каждой бистабильной схемы. Поэтому, потенциал второго узла сохраняется на низком уровне в течение большинства периодов. Отсюда, увеличение потенциала первого узла вследствие помещения второго транзистора во включенное состояние по первому тактовому сигналу, не возникает во время периодов, иных чем выбранный период. Другими словами, первый транзистор не помещается во включенное состояние во время периодов, иных чем выбранный период. Соответственно, возникновение перекрестной помехи, которая традиционно возникает вследствие изменения потенциала тактового сигнала и емкости перекрытия в транзисторе, пресекается и, таким образом, пресекается ухудшение качества отображения устройства отображения.

Согласно второму аспекту настоящего изобретения, площадь канала первого транзистора сделана меньшей, чем у второго транзистора. Отсюда, даже если емкость перекрытия возникает во втором транзисторе, влияние изменения потенциала первого тактового сигнала и емкости перекрытия во втором транзисторе первого узла относительно невелико. Соответственно, в отличие от традиционного примера, во время периодов, иных чем выбранный период, потенциал первого узла не увеличивается до уровня, который помещает первый транзистор во включенное состояние. Соответственно, возникновение перекрестной помехи, которая традиционно возникает вследствие изменения потенциала тактового сигнала и емкости перекрытия в транзисторе, надежно предотвращается и, таким образом, эффективно пресекается ухудшение качества отображения устройства отображения.

Согласно третьему аспекту настоящего изобретения, каждая бистабильная схема снабжена конденсатором, присоединенным на своем одном конце ко второму узлу и присоединенным на своем другом конце к выходному узлу. Между тем, второй узел заряжается на основании сигнала состояния, выдаваемого из бистабильной схемы предыдущего каскада каждой бистабильной схемы. В это время, необходимо только заряжать конденсатор, из условия чтобы потенциал второго узла приводился к высокоуровневому потенциалу. Таким образом, в отличие от конфигурации по традиционному примеру, нет необходимости пропускать ток через линию электропитания посредством какого-нибудь из транзисторов. Соответственно, в отличие от традиционного примера, нет необходимости предусматривать транзисторы, имеющие большую площадь канала. Вследствие вышеприведенного, реализовано устройство отображения, которое способно к пресечению ухудшения качества отображения, вызванного перекрестной помехой, не вызывая увеличения потребляемой мощности или увеличения размера конструкции.

Согласно четвертому аспекту настоящего изобретения, в конфигурации, в которой транзисторы включены в часть разряда второго узла, часть разряда первого узла и часть разряда выходного узла, получается такой же результат, как полученный в первом аспекте настоящего изобретения.

Согласно пятому аспекту настоящего изобретения, в конфигурации, в которой транзистор включен в часть заряда второго узла, получается такой же результат, как полученный в первом аспекте настоящего изобретения.

Согласно шестому аспекту настоящего изобретения, в конфигурации, в которой транзистор в диодном включении включен в часть заряда второго узла, получается такой же результат, как полученный в первом аспекте настоящего изобретения.

Согласно седьмому аспекту настоящего изобретения, по сравнению с конфигурацией, в которой скомбинированы тонкопленочный транзистор n-канального типа и тонкопленочный транзистор p-канального типа, количество фотомасок, используемых в процессе изготовления подложки матрицы TFT, может быть сокращено.

Согласно восьмому аспекту настоящего изобретения, реализована схема возбуждения линий сигнала сканирования, которая включает в себя сдвиговый регистр, с которым получается такой же результат, как полученный в любом из с первого по седьмой вариантах осуществления настоящего изобретения.

Согласно девятому аспекту настоящего изобретения, реализовано устройство отображения, которое включает в себя схему возбуждения линий сигнала сканирования, с которой получается такой же результат, как полученный в восьмом аспекте настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

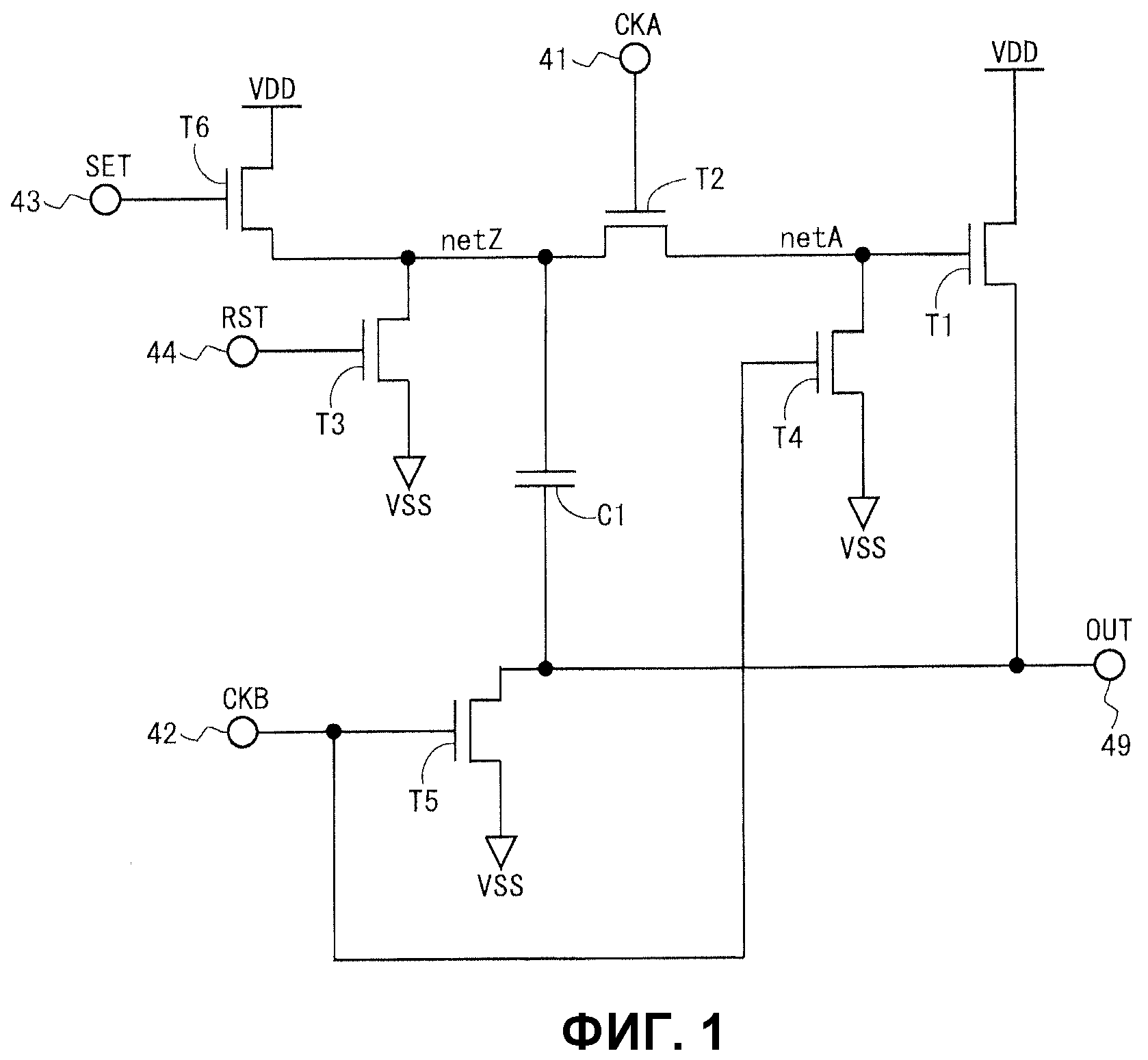

Фиг.1 - принципиальная схема, показывающая конфигурацию бистабильной схемы, включенной в сдвиговый регистр в драйвере затвора жидкокристаллического устройства отображения активного матричного типа согласно одному из вариантов осуществления настоящего изобретения.

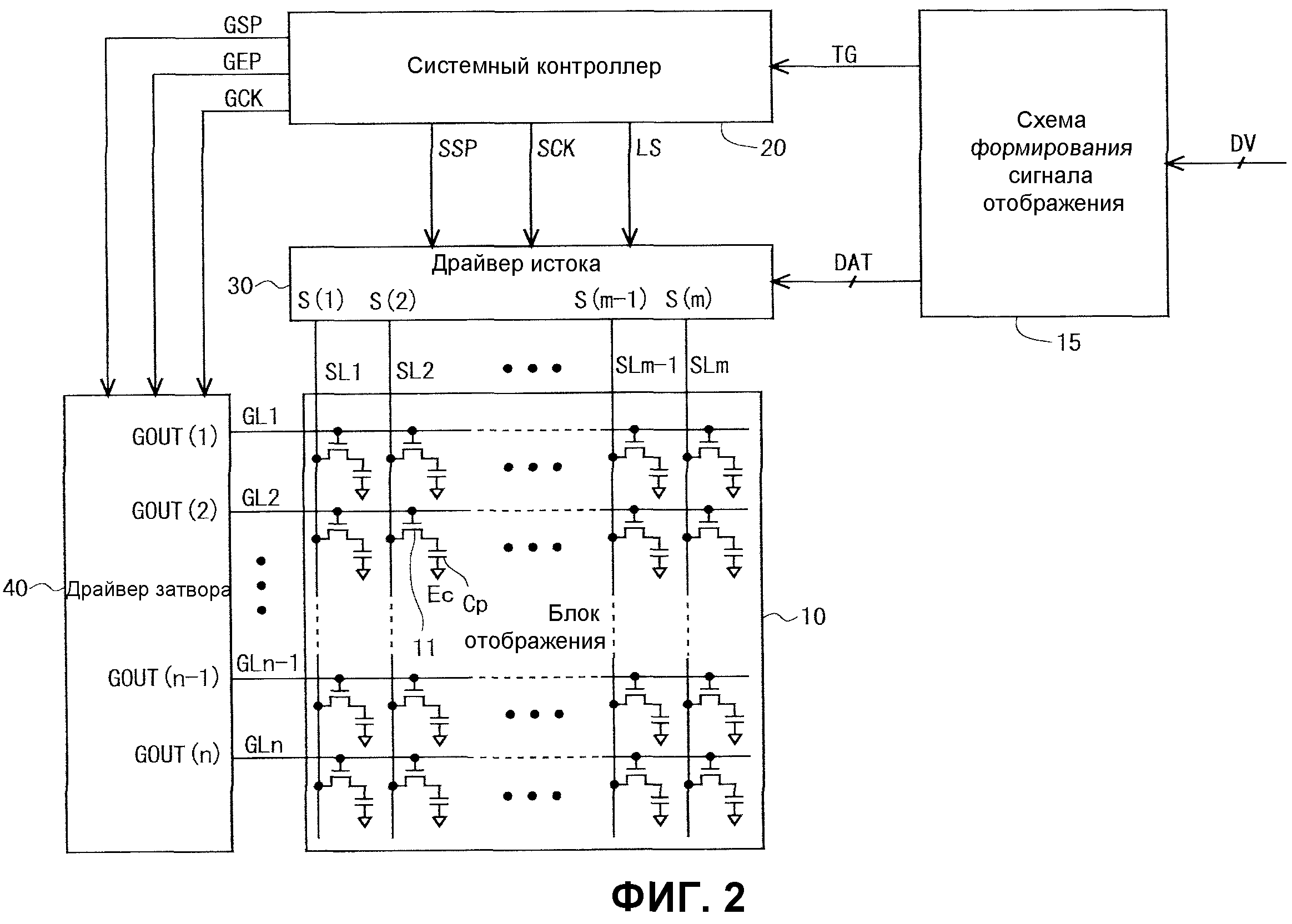

Фиг.2 - структурная схема, показывающая общую конфигурацию жидкокристаллического устройства отображения по варианту осуществления.

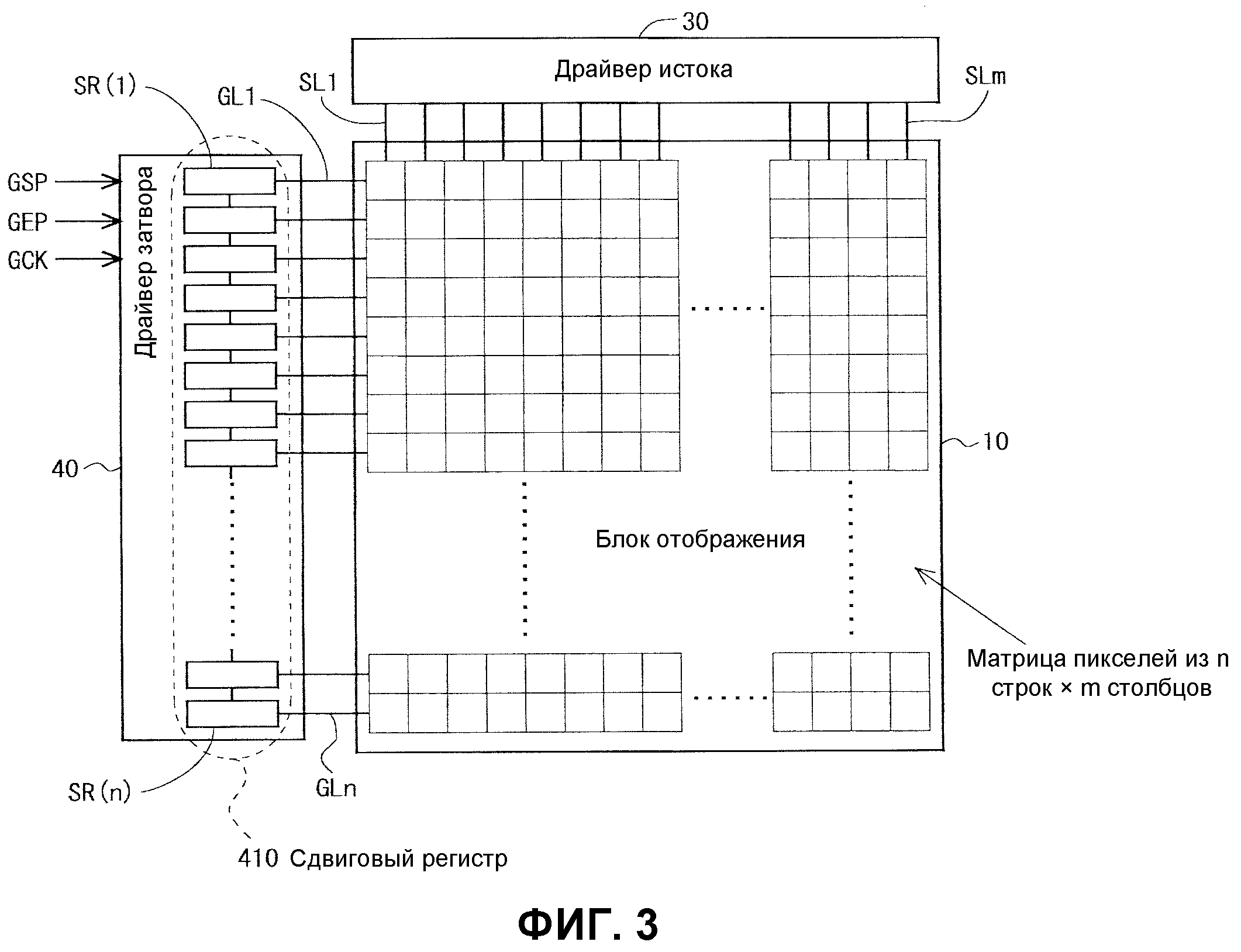

Фиг.3 - структурная схема для описания конфигурации драйвера затвора по варианту осуществления.

Фиг.4 - структурная схема, показывающая конфигурацию сдвигового регистра в драйвере затвора по варианту осуществления.

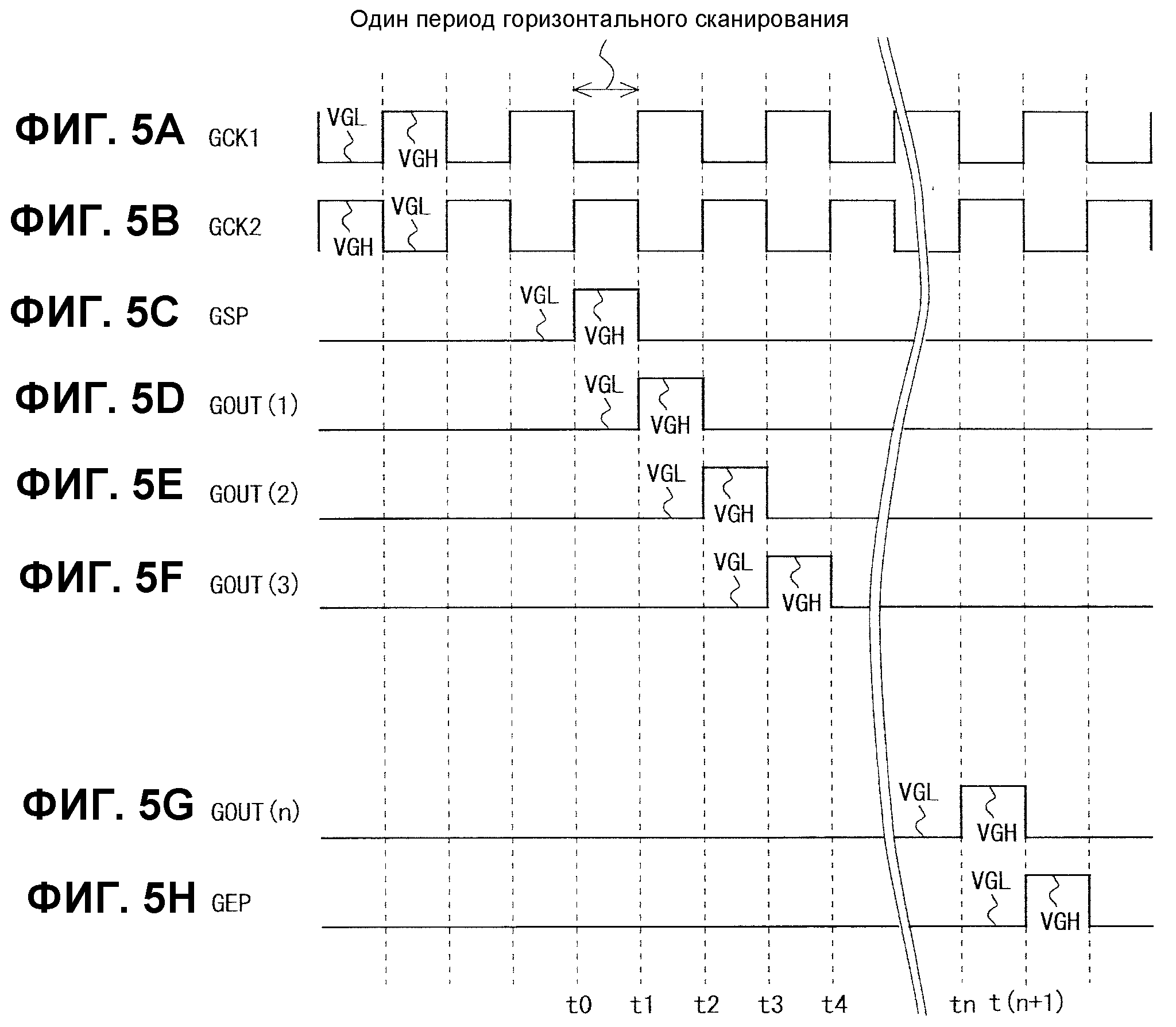

Фиг.5A-5H - временные диаграммы входных и выходных сигналов в/из сдвигового регистра по варианту осуществления.

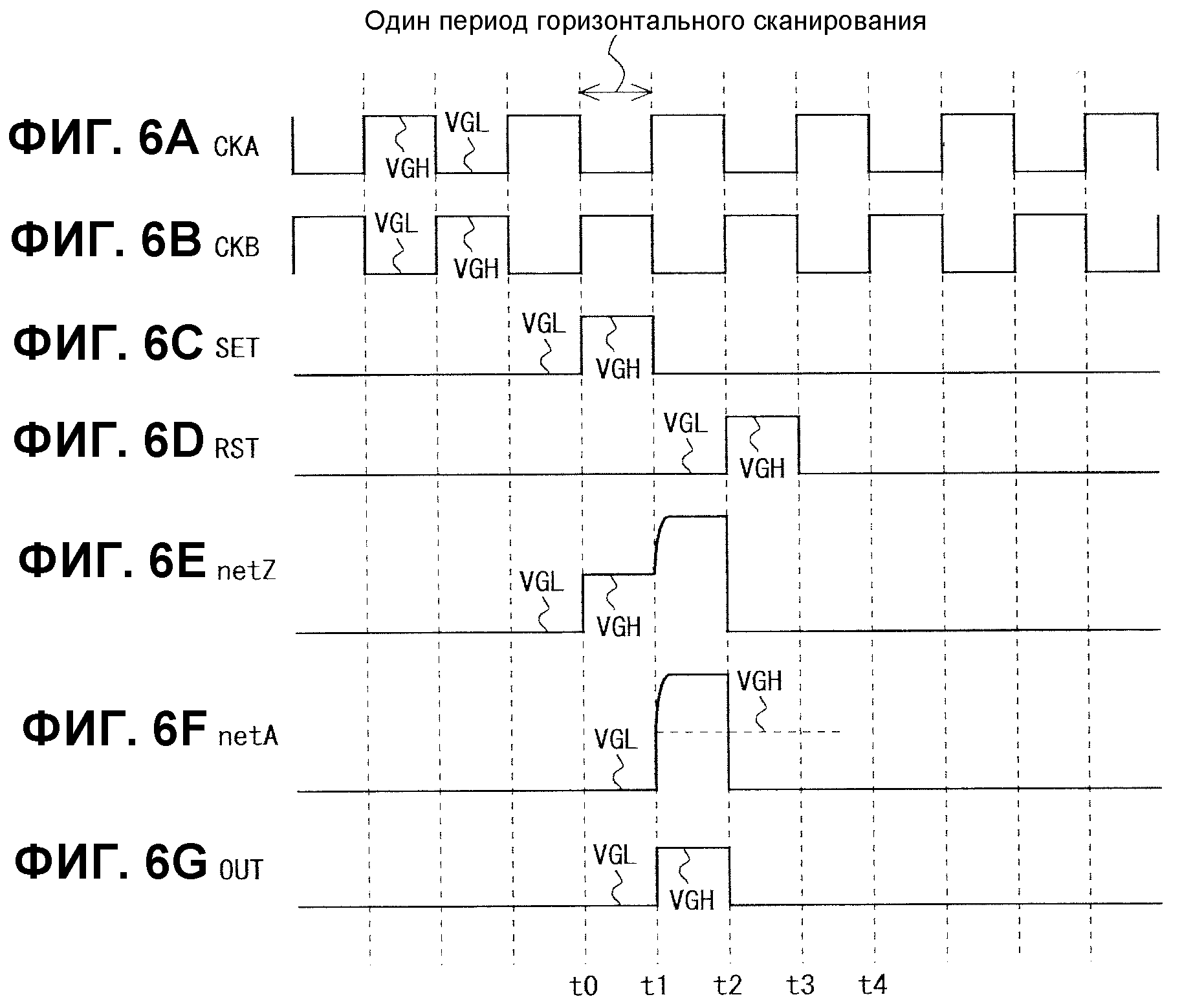

Фиг.6A-6G - временные диаграммы для описания работы каждого каскада (бистабильной схемы) сдвигового регистра по варианту осуществления.

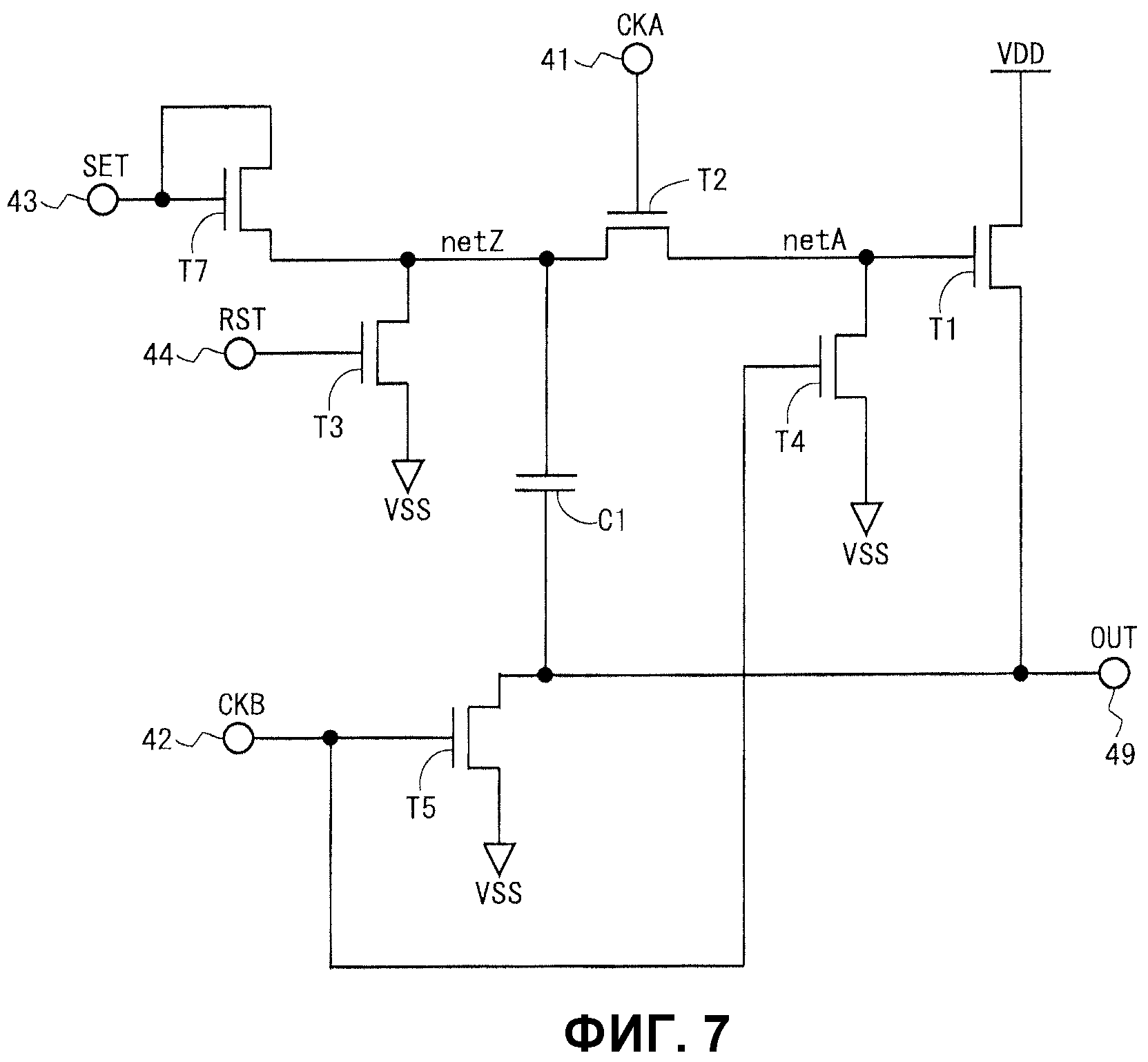

Фиг.7 - принципиальная схема, показывающая конфигурацию бистабильной схемы в разновидности варианта осуществления.

Фиг.8 - структурная схема, показывающая конфигурацию сдвигового регистра в драйвере затвора в традиционном примере.

Фиг.9 - принципиальная схема, показывающая конфигурацию бистабильной схемы, включенной в сдвиговый регистр в традиционном примере.

Фиг.10A-10G - временные диаграммы входных и выходных сигналов в/из сдвигового регистра в традиционном примере.

Фиг.11A-11F - временные диаграммы для описания работы каждого каскада (бистабильной схемы) сдвигового регистра в традиционном примере.

Фиг.12 - структурная схема, показывающая конфигурацию сдвигового регистра в драйвере затвора в еще одном традиционном примере.

Фиг.13 - принципиальная схема, показывающая конфигурацию бистабильной схемы, включенной в сдвиговый регистр в еще одном традиционном примере.

Фиг.14A-14J - временные диаграммы входных и выходных сигналов в/из сдвигового регистра в еще одном традиционном примере.

Фиг.15A-15D - временные диаграммы для описания работы каждого каскада (бистабильной схемы) сдвигового регистра в еще одном традиционном примере.

Фиг.16 - вид в поперечном разрезе обычного TFT на аморфном кремнии.

Фиг.17A-17F - схемы для описания возникновения перекрестной помехи в традиционном примере.

ВАРИАНТ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Один из вариантов осуществления настоящего изобретения будет описан ниже со ссылкой на прилагаемые чертежи. Отметим, что в последующем описании вывод затвора (затворный электрод) тонкопленочного транзистора соответствует первому электроду, вывод стока (стоковый электрод) соответствует второму электроду, а вывод истока (истоковый электрод) соответствует третьему электроду.

<1. Общая конфигурация и работа>

Фиг.2 - структурная схема, показывающая общую конфигурацию жидкокристаллического устройства отображения активного матричного типа согласно одному из вариантов осуществления настоящего изобретения. Как показано на Фиг.2, жидкокристаллическое устройство отображения включает в себя блок 10 отображения, схему 15 генерирования сигналов отображения, системный контроллер 20, драйвер 30 истока (схему возбуждения линий видеосигнала) и драйвер 40 затвора (схему возбуждения линий сигнала сканирования).

Блок 10 отображения включает в себя множество (m) линий шины истока SL1-SLm (линий видеосигнала); множество (n) линий шины затвора GL1-GLn (линий сигнала сканирования); и множество (n×m) частей формирования пикселя, предусмотренных на соответствующих пересечениях линий шины истока SL1-SLm и линий шины затвора GL1-GLn.

Множество частей формирования пикселя скомпонованы в матричном виде и, тем самым, образуют матрицу пикселей. Каждая часть формирования пикселя состоит из тонкопленочного транзистора 11 (TFT), который является коммутационным элементом, присоединенным на своем выводе затвора к линии шины затвора, проходящей через соответствующее пересечение, и присоединенным на своем выводе истока к линии шины истока, проходящей через это пересечение; пиксельный электрод, присоединенный к выводу стока тонкопленочного транзистора 11; общий электрод Ec, который является противоэлектродом, предусмотренным, с тем чтобы совместно использоваться множеством частей формирования пикселя; и жидкокристаллический слой, который предусмотрен, с тем чтобы совместно использоваться множеством частей формирования пикселя, и который вставлен между пиксельным электродом и общим электродом Ec. Посредством емкости жидкого кристалла, образованной пиксельным электродом и общим электродом Ec, сформирована емкость Cp пикселя. Отметим, что, нормально, вспомогательная емкость предусмотрена параллельно с емкостью жидкого кристалла, для того чтобы надежно удерживать напряжение на емкости Cp пикселя; однако, вспомогательная емкость не имеет прямого отношения к настоящему изобретению и, таким образом, ее изображение опущено.

Схема 15 генерирования сигнала отображения принимает цифровой видеосигнал DV, отправленный из внешнего источника, и извлекает составляющие сигнала яркости шкалы серого и составляющие сигнала синхронизации из цифрового видеосигнала DV. Затем, схема 15 генерирования сигнала отображения подает составляющие сигнала яркости шкалы серого на драйвер 30 истока в качестве данных DAT отображения и подает составляющие сигнала синхронизации в системный контроллер 20 в качестве сигнала TG синхронизации.

Системный контроллер 20 генерирует начальный импульсный сигнал истока SSP, тактовый сигнал истока SCK, сигнал LS стробирования защелки, начальный импульсный сигнал затвора GSP, конечный импульсный сигнал затвора GEP и тактовый сигнал затвора GCK, которые предназначены для управления отображением изображения на блоке 10 отображения на основании сигнала TG синхронизации, выдаваемого из схемы 15 формирования сигнала отображения, и выдает сигналы.

Драйвер 30 истока принимает данные DAT отображения, выдаваемые из схемы 15 генерирования сигнала отображения, и начальный импульсный сигнал истока SSP, тактовый сигнал истока SCK и сигнал LS стробирования защелки, которые выдаются из системного контроллера 20, и прикладывает видеосигналы S(1)-S(m) возбуждения к линии шины истока SL1-SLm, соответственно.

Драйвер 40 затвора повторяет прикладывание сигналов GOUT(1)-GOUT(n) активного сканирования к соответствующим линиям шины затвора GL1-GLn в циклах оного периода вертикального сканирования на основании начального импульсного сигнала затвора GSP, конечного импульсного сигнала затвора GEP и тактового сигнала затвора GCK, которые выдаются из системного контроллера 20. Отметим, что подробное описание драйвера 40 затвора будет сделано позже.

Описанным выше образом, видеосигналы S(1)-S(m) возбуждения прикладываются к линиям шины истока SL1-SLm, соответственно, а сигналы GOUT(1)-GOUT(n) сканирования прикладываются к линиям шины затвора GL1-GLn, соответственно, в силу чего, изображение, основанное на цифровом видеосигнале DV, отправленном из внешнего источника, отображается на блоке 10 отображения.

<2. Конфигурация и работа драйвера затвора>

Затем, со ссылкой на Фиг.3, 4 и 5(A)-5(H), будет описано общее представление конфигурации и работы драйвера 40 затвора по настоящему варианту осуществления. Как показано на Фиг.3, драйвер 40 затвора состоит из n-каскадного сдвигового регистра 410. В блоке 10 отображения, формируется матрица пикселей из n строк × m столбцов, и каскады сдвигового регистра 410 предусмотрены, с тем чтобы иметь соответствие один к одному со строками в матрице пикселей. В дополнение, каждый каскад сдвигового регистра 410 является бистабильной схемой, которая находится в любом одном из двух состояний (первого состояния и второго состояния) в каждый момент времени, и которая выдает сигнал (сигнал состояния), указывающий состояние, в качестве сигнала сканирования. По существу, сдвиговый регистр 410 состоит из n бистабильных схем SR(1)-SR(n). Отметим, что, в настоящем варианте осуществления, когда бистабильная схема находится в первом состоянии, линия шины затвора, присоединенная к бистабильной схеме, помещается в выбранное состояние, а когда бистабильная схема находится во втором состоянии, линия шины затвора, присоединенная к бистабильной схеме, помещается в невыбранное состояние.

Фиг.4 - структурная схема, показывающая конфигурацию сдвигового регистра 410 в драйвере 40 затвора. Как описано выше, сдвиговый регистр 410 состоит из n бистабильных схем SR(1)-SR(n). Как показано на Фиг.4, на сдвиговый регистр 410 подаются двухфазные тактовые сигналы затвора GCK1 (в дальнейшем указываемый ссылкой как «первый тактовый сигнал затвора») и GCK2 (в дальнейшем указываемый ссылкой как «второй тактовый сигнал затвора»), начальный импульсный сигнал затвора GSP, который является сигналом для запуска сканирования линий шины затвора, и конечный импульсный сигнал затвора GEP, который является сигналом для завершения сканирования линий шины затвора. Каждая бистабильная схема снабжена входным выводом для приема любого одного из первого тактового сигнала затвора GCK1 и второго тактового сигнала затвора GCK2 в качестве первого тактового сигнала CKA; входным выводом для приема другого одного из первого тактового сигнала затвора GCK1 и второго тактового сигнала затвора GCK2 в качестве второго тактового сигнала CKB; входного вывода для приема начального импульсного сигнала затвора GSP или сигнала OUT состояния, выдаваемого с его предыдущего каскада, в качестве сигнала SET установки; входного вывода для приема конечного импульсного сигнала затвора GEP или сигнала OUT состояния, выдаваемого из его следующего каскада, в качестве сигнала RST сброса; и выходным выводом для выдачи сигнала OUT состояния в качестве сигнала GOUT сканирования. Отметим, что первый тактовый сигнал затвора GCK1 и второй тактовый сигнал затвора GCK2 сдвинуты по фазе друг от друга на 180 градусов.

В настоящем варианте осуществления, сигналы, подаваемые на входные выводы каждого каскада (каждой бистабильной схемы), являются следующими. Что касается бистабильной схемы SR(1) первого каскада, первый тактовый сигнал затвора GCK1 предусмотрен в качестве первого тактового сигнала CKA, второй тактовый сигнал затвора GCK2 предусмотрен в качестве второго тактового сигнала CKB, начальный импульсный сигнал затвора GSP предусмотрен в качестве сигнала SET установки, и сигнал OUT состояния из его следующего каскада предусмотрен в качестве сигнала RST сброса. Что касается бистабильной схемы SR(2) второго каскада, второй тактовый сигнал затвора GCK2 предусмотрен в качестве первого тактового сигнала CKA, первый тактовый сигнал затвора GCK1 предусмотрен в качестве второго тактового сигнала CKB, сигнал OUT состояния из его предыдущего каскада предусмотрен в качестве сигнала SET установки, и сигнал OUT состояния из его следующего каскада предусмотрен в качестве сигнала RST сброса. Что касается бистабильной схемы SR(3) третьего каскада, первый тактовый сигнал затвора GCK1 предусмотрен в качестве первого тактового сигнала CKA, второй тактовый сигнал затвора GCK2 предусмотрен в качестве второго тактового сигнала CKB, сигнал OUT состояния из его предыдущего каскада предусмотрен в качестве сигнала SET установки, и сигнал OUT состояния из его следующего каскада предусмотрен в качестве сигнала RST сброса. Что касается бистабильных схем SR(4)-SR(n-1) с четвертого по (n-1)-ый каскадов, такие же конфигурации, как описанные выше конфигурации второго и третьего каскадов повторяются каждые два каскада. Что касается бистабильной схемы SR(n) n-ого каскада, второй тактовый сигнал затвора GCK2 предусмотрен в качестве первого тактового сигнала CKA, первый тактовый сигнал затвора GCK1 предусмотрен в качестве второго тактового сигнала CKB, сигнал OUT состояния из его предыдущего каскада предусмотрен в качестве сигнала SET установки, и конечный импульсный сигнал затвора GEP предусмотрен в качестве сигнала RST сброса.

Затем, будет описан сигнал, выдаваемый с выходного вывода каждого каскада (каждой бистабильной схемы). Сигнал OUT состояния, выдаваемый из бистабильной схемы SR(1) первого каскада, служит в качестве сигнала GOUT(1) сканирования для помещения линии шины затвора GL1 первой строки в выбранное состояние и подается в бистабильную схему SR(2) второго каскада в качестве сигнала SET установки. Сигнал OUT состояния, выдаваемый из бистабильной схемы SR(n) n-ого каскада, служит в качестве сигнала GOUT(n) сканирования для помещения линии шины затвора GLn n-ой строки в выбранное состояние и подается в бистабильную схему SR(n-1) (n-1)-ого каскада в качестве сигнала RST сброса. Сигналы OUT состояния, выдаваемые из других каскадов, служат в качестве сигналов сканирования для помещения линий шины затвора своих соответствующих строк в выбранное состояние и подаются на свои соответствующие последующие каскады в качестве сигналов SET установки, и подаются на свои соответствующие предыдущие каскады в качестве сигналов RST сброса.

Фиг.5A-5H - временные диаграммы входных и выходных сигналов в/из сдвигового регистра 410 в варианте осуществления. Во время работы жидкокристаллического устройства отображения, как показано на Фиг.5A и 5B, первый тактовый сигнал затвора GCK1 и второй тактовый сигнал затвора GCK2, которые сдвинуты по фазе друг от друга на 180 градусов, подаются на сдвиговый регистр 410 в драйвере 40 затвора. При достижении момента t0, импульс начального импульсного сигнала затвора GSP (см. Фиг.5C) подается в бистабильную схему SR(1) первого каскада в сдвиговом регистре 410. На основании импульса, бистабильная схема SR(1) первого каскада действует некоторым образом, описанным позже, а в момент t1 времени, сигнал состояния, выдаваемый из бистабильной схемы SR(1) первого каскада, переходит на высокий уровень. Что касается второго и следующих каскадов, на основании сигналов состояния, выдаваемых из предыдущих каскадов соответственных каскадов, сигналы состояния, выдаваемые из соответственных каскадов, переходят на высокий уровень. Соответственно, как показано на Фиг.5D-5G, сигналы состояния, которые последовательно переходят на высокий уровень за один период горизонтального сканирования, подаются на линии шины затвора GL1-GLn в блоке 10 отображения в качестве сигналов GOUT(1)-GOUT(n) сканирования. При достижении момента t(n+1) времени после того, как сигнал состояния, выдаваемый из бистабильной схемы SR(n) n-ого каскада переходит на высокий уровень в момент tn времени, импульс конечного импульсного сигнала затвора GEP (см. Фиг.5H) подается в бистабильную схему SR(n) n-ого каскада в сдвиговом регистре 410. Соответственно, работа для выполнения отображения изображения для одного кадра, завершается.

<3. Конфигурация бистабильных схем>

Фиг.1 - принципиальная схема, показывающая конфигурацию бистабильной схемы, включенной в описанный выше сдвиговый регистр 410 (конфигурацию для одного каскада сдвигового регистра 410). Как показано на Фиг.1, бистабильная схема включает в себя шесть тонкопленочных транзисторов T1-T6 (здесь TFT n-типа) (с первого по шестой транзисторы) и конденсатор C1. Тонкопленочные транзисторы T1-T6 не являются ограниченными особым образом, а, например, применяются TFT на аморфном кремнии, низкотемпературные поликремниевые TFT, TFT на кремнии CG (с непрерывной структурой), и т.д. В дополнение, бистабильная схема имеет входные выводы для линии VDD электропитания, которая питает относительно высокоуровневый потенциал VGH, и входные выводы для линии VSS электропитания, которая питает относительно низкоуровневый потенциал VGL, а также четыре входных вывода 41-44 и один выходной вывод 49 (выходной узел). Потенциал VGH соответствует потенциалу, который помещает тонкопленочный транзистор 11 в части формирования пикселя в блоке 10 отображения во включенное состояние, а потенциал VGL соответствует потенциалу, который помещает тонкопленочный транзистор 11 в отключенное состояние. Отметим, что входной вывод, который принимает первый тактовый сигнал CKA, обозначен номером 41 ссылки, входной вывод, который принимает второй тактовый сигнал CKB, обозначен номером 42 ссылки, входной вывод, который принимает сигнал SET установки, обозначен номером 43 ссылки, а входной вывод, который принимает сигнал RST сброса, обозначен номером 44 ссылки. Отношение соединения между компонентами в бистабильной схеме будет описано ниже.

Вывод затвора тонкопленочного транзистора T1, вывод истока тонкопленочного транзистора T2 и вывод стока тонкопленочного транзистора T4 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netA» (первый узел) ради удобства. Вывод стока тонкопленочного транзистора T2, вывод стока тонкопленочного транзистора T3, вывод истока тонкопленочного транзистора T6 и один конец конденсатора C1 присоединены друг к другу. Отметим, что область (линия проводного соединения), где они присоединены друг к другу, указывается ссылкой как «netZ» (второй узел) ради удобства.

Тонкопленочный транзистор T1 присоединен на своем выводе затвора к netA, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к выходному выводу 49. Тонкопленочный транзистор T2 присоединен на своем выводе затвора к входному выводу 41, присоединен на своем выводе стока к netZ, и присоединен на своем выводе истока к netA. Тонкопленочный транзистор T3 присоединен на своем выводе затвора к входному выводу 44, присоединен на своем выводе стока к netZ и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T4 присоединен на своем выводе затвора к входному выводу 42, присоединен на своем выводе стока к netA и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T5 присоединен на своем выводе затвора к входному выводу 42, присоединен на своем выводе стока к выходному выводу 49 и присоединен на своем выводе истока к линии VSS электропитания. Тонкопленочный транзистор T6 присоединен на своем выводе затвора к входному выводу 43, присоединен на своем выводе стока к линии VDD электропитания и присоединен на своем выводе истока к netZ. Конденсатор C1 присоединен на одном своем конце к netZ и присоединен на своем другом конце к выходному выводу 49.

Между тем, в настоящем варианте осуществления, конфигурация такова, что площадь канала тонкопленочного транзистора T1 является большей, чем у тонкопленочного транзистора T2. Более точно, когда ширина канала тонкопленочного транзистора T1 имеет значение W1, длина канала тонкопленочного транзистора T1 имеет значение L1, ширина канала тонкопленочного транзистора T2 имеет значение W2, и длина канала тонкопленочного транзистора T2 имеет значение L2, устанавливается следующее уравнение (1):

W1×L1>W2×L2 (1).

Отметим, что, в настоящем варианте осуществления, часть разряда второго узла реализована тонкопленочным транзистором T3, часть разряда первого узла реализована тонкопленочным транзистором T4, а часть разряда выходного узла реализована тонкопленочным транзистором T5.

<4. Работа сдвигового регистра>

Затем, со ссылкой на Фиг.1 и 6A-6G, будет описана работа каждого каскада (бистабильной схемы) сдвигового регистра 410 в настоящем варианте осуществления. Отметим, что Фиг.6A-6G показывают формы сигнала для бистабильной схемы SR(1) первого каскада, а что касается бистабильных схем SR(2)-SR(n) второго и последующих каскадов, такие же формы сигнала, как показанные на Фиг.6A-6G, появляются задержанными на один период горизонтального сканирования. Другими словами, n бистабильных схем SR(1)-SR(n) выполняют одну и ту же операцию за исключением привязки по времени. Соответственно, в последующем, описание будет дано с фокусированием только на одной бистабильной схеме SR(1) первого каскада.

Во время работы устройства отображения, первый тактовый сигнал CKA, имеющий форму сигнала, показанную на Фиг.6A, подается на входной вывод 41, а второй тактовый сигнал CKB, имеющий форму сигнала, показанную на Фиг.6B, подается на входной вывод 42. Во время периодов до момента t0 времени, как показано на Фиг.6C-6G, потенциалы сигнала SET установки, сигнала RST сброса, netZ, netA и сигнала OUT состояния все имеют значение VGL.

При достижении момента t0 времени, импульс сигнала SET установки подается на входной вывод 43. Соответственно, тонкопленочный транзистор T6 помещается во включенное состояние. Посредством помещения тонкопленочного транзистора T6 во включенном состоянии, потенциал netZ увеличивается до потенциала VGH линии VDD электропитания. В дополнение, в момент t0 времени, потенциал второго тактового сигнала CKB изменяется с VGL на VGH. Соответственно, тонкопленочные транзисторы T4 и T5 помещаются во включенное состояние. Посредством помещения тонкопленочного транзистора T4 во включенное состояние, потенциал netA поддерживается на VGL. В дополнение, посредством помещения тонкопленочного транзистора T5 во включенное состояние, потенциал выходного вывода 49, то есть потенциала сигнала OUT состояния, поддерживается на VGL. Вследствие вышеприведенного, напряжение между двумя выводами конденсатора C1 имеет значение «VGH-VGL».

При достижении момента t1 времени, потенциал сигнала SET установки изменяется с VGH на VGL. Соответственно, тонкопленочный транзистор T6 помещается в отключенное состояние. В дополнение, в момент t1 времени, потенциал второго тактового сигнала CKB изменяется с VGH на VGL. Соответственно, тонкопленочные транзисторы T4 и T5 помещаются в отключенное состояние. Более того, в момент t1 времени, потенциал первого тактового сигнала CKA изменяется с VGL на VGH. Соответственно, тонкопленочный транзистор T2 помещается во включенное состояние. Поскольку потенциал netZ имеет значение VGH в момент времени непосредственно перед моментом t1 времени, посредством помещения тонкопленочного транзистора T2 во включенное состояние, потенциал netA увеличивается до VGH. Соответственно, тонкопленочный транзистор T1 помещается во включенное состояние. Как результат, потенциал сигнала OUT состояния увеличивается до потенциала VGH линии VDD электропитания. Соответственно, линия шины затвора, присоединенная к выходному выводу 49 бистабильной схемы, помещается в выбранное состояние.

Здесь, поскольку один конец конденсатора C1 присоединен к netZ, а другой конец присоединен к выходному выводу 49, потенциал netZ также увеличивается с увеличением потенциала на выходном выводе 49. В дополнение, поскольку, как описано выше, тонкопленочный транзистор T2 находится во включенном состоянии, потенциал netA также увеличивается с увеличением потенциала netZ. Соответственно, во время периода с t1 до t2, потенциал netZ и потенциал netA увеличиваются до «2×VGH».

При достижении момента t2 времени, потенциал первого тактового сигнала CKA изменяется с VGH на VGL. Соответственно, тонкопленочный транзистор T2 помещается в отключенное состояние. В дополнение, в момент t2 времени, потенциал второго тактового сигнала CKB изменяется с VGL на VGH. Соответственно, тонкопленочные транзисторы T4 и T5 помещаются во включенное состояние. Посредством помещения тонкопленочного транзистора T2 в отключенное состояние, и помещения тонкопленочного транзистора T4 во включенное состояние, потенциал netA уменьшается до VGL. Соответственно, тонкопленочный транзистор T1 помещается в отключенное состояние. В дополнение, посредством помещения тонкопленочного транзистора T5 во включенное состояние, потенциал сигнала OUT состояния уменьшается до VGL. Соответственно, линия шины затвора, присоединенная к выходному выводу 49 бистабильной схемы, помещается в невыбранное состояние. Более того, в момент t2 времени, импульс сигнала OUT состояния, выдаваемого из бистабильной схемы следующего каскада бистабильной схемы, подается на входной вывод 44 бистабильной схемы в качестве импульса сигнала RST сброса. Соответственно, тонкопленочный транзистор T3 помещается во включенное состояние и, таким образом, потенциал netZ уменьшается до VGL.

При достижении момента t3 времени, потенциал первого тактового сигнала CKA изменяется с VGL на VGH. Соответственно, тонкопленочный транзистор T2 помещается во включенное состояние. В дополнение, в момент t3 времени, потенциал сигнала RST сброса изменяется с VGH на VGL. Соответственно, тонкопленочный транзистор T3 помещается в отключенное состояние. Здесь, потенциал сигнала SET установки поддерживается на VGL в и после момента t1 времени. Отсюда, в и после момента t1 времени, тонкопленочный транзистор T6 находится в отключенном состоянии. Потенциал сигнала OUT состояния поддерживается на VGL в и после момента t2 времени. Вследствие вышеприведенного, что касается netZ, потенциал VGL непосредственно перед моментом t3 времени сохраняется даже в и после момента t3 времени. Поэтому, даже если тонкопленочный транзистор T2 помещается во включенное состояние, потенциал netA поддерживается на VGL даже в и после момента t3 времени. Как результат, в и после момента t3 времени, тонкопленочный транзистор T1 поддерживается в отключенном состоянии, и потенциал сигнала OUT состояния также поддерживается на VGL. Что касается netZ, потенциал VGL в момент t3 времени поддерживается в течение периодов до достижения момента t0 времени следующего периода кадровой развертки. Что касается netA и сигнала состояния, потенциал VGL в момент t3 времени поддерживается в течение периодов до достижения момента t1 времени следующего периода кадровой развертки.

Работа, такая как описанная выше, последовательно выполняется на описанных выше n бистабильных схемах SR(1)-SR(n), так чтобы привязка по времени задерживалась на один период горизонтального сканирования. Соответственно, в каждом периоде кадровой развертки, n линий затвора GL1-GLn последовательно помещаются в выбранное состояние за один период горизонтального сканирования.

Отметим, что, в настоящем варианте осуществления, первый этап возбуждения реализован операцией в момент t0 времени, второй этап возбуждения реализован операцией в момент t1 времени, а третий этап возбуждения реализован операцией в момент t2 времени. Отметим, что состояние, в котором потенциал netA имеет значение VGL, а потенциал netZ имеет значение VGH, такое как в течение периода от t0 до t1, соответствует предварительному состоянию.

<5. Результаты>

Согласно настоящему варианту осуществления, в отличие от конфигурации по традиционному примеру, показанному на Фиг.9, постоянный потенциал VGH подается на вывод стока тонкопленочного транзистора T1. Отсюда, помещение тонкопленочного транзистора T1 во включенное состояние вследствие изменения потенциала вывода стока тонкопленочного транзистора T1 не происходит в течение периодов, иных чем выбранный период (период от t1 до t2). В дополнение, поскольку, как показано на Фиг.6E, потенциал netZ поддерживается на VGL в течение большинства периодов (периодов, иных чем период от t0 до t2), помещение тонкопленочного транзистора T1 во включенное состояние вследствие помещения во включенное состояние тонкопленочного транзистора T2 на основании первого тактового сигнала CKA не происходит во время периодов, иных чем выбранный период. Отметим, однако, что, принимая во внимание емкость Cgs перекрытия в тонкопленочном транзисторе T2, считается, что потенциал netA увеличивается на основании изменения потенциала первого тактового сигнала CKA. В этом смысле, настоящий вариант осуществления использует конфигурацию, в которой площадь канала тонкопленочного транзистора T1 является большей, чем у тонкопленочного транзистора T2. Отсюда, влияние изменения потенциала первого тактового сигнала CKA и емкости Cgs перекрытия в тонкопленочном транзисторе T2 на потенциал netA относительно невелико. Соответственно, в отличие от традиционного примера, увеличение потенциала netA до уровня, который помещает тонкопленочный транзистор T1, который является выходным транзистором, во включенное состояние, не происходит во время периодов, иных чем выбранный период.

Как описано выше, тонкопленочный транзистор T1, который является выходным транзистором, не помещается во включенное состояние во время периодов, иных чем выбранный период. Другими словами, согласно настоящему варианту осуществления, возникновение перекрестной помехи, которая традиционно возникает вследствие изменения потенциала тактового сигнала и емкости перекрытия в тонкопленочном транзисторе, предотвращается и, таким образом, пресекается ухудшение качества отображения устройства отображения.

В дополнение, в настоящем варианте осуществления, посредством сигнала SET установки, переходящего на высокий уровень (VGH), тонкопленочный транзистор T6 помещается во включенное состояние и, соответственно, ток из линии VDD электропитания перетекает с вывода стока на вывод истока тонкопленочного транзистора T6. В это время, необходимо только заряжать конденсатор C1, так чтобы потенциал netZ приводился к VGH вышеописанным током. Таким образом, в отличие от конфигурации по традиционному примеру, показанному на Фиг.13, нет необходимости пропускать вышеописанный ток через линию VSS электропитания посредством какого-нибудь из тонкопленочных транзисторов. Отсюда, увеличения потребляемой мощности, такого как в традиционном примере, не происходит. В дополнение, поскольку нет необходимости предусматривать тонкопленочные транзисторы, имеющие относительно большую площадь канала (тонкопленочные транзисторы T92 и T95 в примере, показанном на Фиг.13), область конструкции для монтажа драйвера затвора не нужно увеличивать в размере.

Как описано выше, согласно настоящему изобретению, реализовано устройство отображения, которое способно к пресечению ухудшения качества отображения, вызванного перекрестной помехой, не вызывая увеличения потребляемой мощности или увеличения размера конструкции.

<6. Варианты и т.д.>

Хотя в вышеописанном варианте осуществления описание сделано с использованием жидкокристаллического устройства отображения в качестве примера, настоящее изобретение не ограничено этим. До тех пор пока конфигурация включает в себя сдвиговый регистр, настоящее изобретение также может быть применено к устройствам отображения, иным чем жидкокристаллические устройства отображения, таким как устройства отображения, имеющие скомпонованные в них светоизлучающие устройства самосветоизлучающего типа, такие как EL (электролюминесцентные) устройства или светоизлучающие диоды (LED).

В дополнение, хотя в вышеописанном варианте осуществления описание сделано с использованием примера, в котором в качестве транзисторов используются TFT (тонкопленочные транзисторы) которые являются МОП (металл-оксид-полупроводниковыми) транзисторами (здесь, МОП-транзисторы, также включающие в себя МОП-структуры с кремниевым затвором, указываются ссылкой как МОП-транзисторы), сформированными на изолирующей подложке, такой как стеклянная подложка, настоящее изобретение не ограничено этим. Настоящее изобретение может быть применено к любому элементу возбуждения до тех пор, пока элемент возбуждения имеет управляемый напряжением тип, в котором выходной ток управляется управляющим напряжением, приложенным к выводу управления током, и управляющее напряжение имеет пороговое напряжение, которое определяет, есть ли выходной ток.

Более того, конфигурация тонкопленочного транзистора T6 в вышеописанном варианте осуществления может быть такой, что выводы затвора и стока тонкопленочного транзистора короткозамкнуты (то есть конфигурацией диодного включения). Другими словами, конфигурация может включать в себя тонкопленочный транзистор T7, показанный на Фиг.7, вместо тонкопленочного транзистора T6, показанного на Фиг.1. В случае этой конфигурации, когда потенциал сигнала SET установки, то есть потенциала затвора тонкопленочного транзистора T7, приводится к VGH, тонкопленочный транзистор T7 помещается во включенное состояние и, таким образом, потенциал его истока, то есть потенциал netZ приводится к VGH.

В дополнение, хотя, в вышеописанном варианте осуществления, описание сделано при условии, что потенциал линий VDD электропитания, присоединенных к выводам стока тонкопленочных транзисторов T1 и T6, и потенциал на высокоуровневой стороне первого тактового сигнала CKA и второго тактового сигнала CKB оба имеют значение VGH, такие потенциалы могут быть установлены в разные значения.

Более того, настоящее изобретение не ограничено вышеописанными вариантами осуществления, и различные изменения могут быть произведены в пределах объема, определенного формулой изобретения. Вариант осуществления, полученный надлежащим комбинированием технических средств, раскрытых в разных вариантах осуществления, также заключен в техническом объеме настоящего изобретения.

ОПИСАНИЕ ПОЗИЦИОННЫХ ОБОЗНАЧЕНИЙ

10: УСТРОЙСТВО ОТОБРАЖЕНИЯ

15: СХЕМА ГЕНЕРИРОВАНИЯ СИГНАЛА ОТОБРАЖЕНИЯ

20: СИСТЕМНЫЙ КОНТРОЛЛЕР

30: ДРАЙВЕР ИСТОКА (СХЕМА ВОЗБУЖДЕНИЯ ЛИНИЙ ВИДЕОСИГНАЛА)

40: ДРАЙВЕР ЗАТВОРА (СХЕМА ВОЗБУЖДЕНИЯ СИГНАЛА СКАНИРОВАНИЯ)

41-44: ВХОДНОЙ ВЫВОД (БИСТАБИЛЬНОЙ СХЕМЫ)

49: ВЫХОДНОЙ ВЫВОД (БИСТАБИЛЬНОЙ СХЕМЫ)

410: СДВИГОВЫЙ РЕГИСТР

SR(1)-SR(n): БИСТАБИЛЬНАЯ СХЕМА

T1-T7: ТОНКОПЛЕНОЧНЫЙ ТРАНЗИСТОР

C1: КОНДЕНСАТОР

GL1-GLn: ЛИНИЯ ШИНЫ ЗАТВОРА

SL1-SLm: ЛИНИЯ ШИНЫ ИСТОКА

GSP: НАЧАЛЬНЫЙ ИМПУЛЬСНЫЙ СИГНАЛ ЗАТВОРА

GEP: КОНЕЧНЫЙ ИМПУЛЬСНЫЙ СИГНАЛ ЗАТВОРА

GCK1: ПЕРВЫЙ ТАКТОВЫЙ СИГНАЛ ЗАТВОРА

GCK2: ВТОРОЙ ТАКТОВЫЙ СИГНАЛ ЗАТВОРА

CKA: ПЕРВЫЙ ТАКТОВЫЙ СИГНАЛ

CKB: ВТОРОЙ ТАКТОВЫЙ СИГНАЛ

GOUT(1)-GOUT(n): СИГНАЛ СКАНИРОВАНИЯ

OUT: СИГНАЛ СОСТОЯНИЯ

SET: СИГНАЛ УСТАНОВКИ

RST: СИГНАЛ СБРОСА