Результат интеллектуальной деятельности: СПОСОБ УПРАВЛЕНИЯ СКОРОСТЬЮ ПЕРЕДАЧИ БИТОВ ВИДЕО, УСТРОЙСТВО УПРАВЛЕНИЯ СКОРОСТЬЮ ПЕРЕДАЧИ БИТОВ ВИДЕО, МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ ЗАПИСИ, НА КОТОРОМ ЗАПИСАНА ПРОГРАММА УПРАВЛЕНИЯ СКОРОСТЬЮ ПЕРЕДАЧИ БИТОВ ВИДЕО

Вид РИД

Изобретение

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к: способу и устройству управления скоростью передачи битов видео, используемым в схеме кодирования видеоданных, которая выполняет процесс по определению шага квантования или подобного параметра кодируемого изображения на основании предварительно заданной выделенной скорости передачи битов; программе управления скоростью передачи битов видео, используемой для реализации способа управления скоростью передачи битов видео и машиночитаемому носителю записи, на котором записана программа.

По данной заявке испрашивается приоритет Патентной Заявки Японии №2008-147534, которая была подана 05 Июня 2008 г., и содержимое которой включено в настоящую заявку посредством ссылки.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0002] В качестве одного из способов кодирования видеоинформации с целевой скоростью передачи битов существует схема двухпроходного кодирования, в соответствии с которой один раз производят кодирование, для того чтобы вычислить характеристику видео, на основании которой получают выделенную (назначенную)скорость передачи битов для каждого изображения, а затем вновь выполняют кодирование, или схема многопроходного кодирования для многократного повторного выполнения операций. Так как эти схемы предоставляют возможность подходящим образом распределить, на основании результата кодирования выполненного в первый раз, скорости передачи битов для соответствующих изображений, то может быть достигнуто эффективное кодирование.

[0003] Даже в том случае, если итоговая выделенная скорость передачи битов для каждого изображения выделяется на основании результатов первого кодирования, существует ошибка между фактически сформированной скоростью передачи битов и выделенной скоростью передачи битов. Соответственно, для того чтобы поток уложился в целевой размер, необходимо включать ошибку скорости передачи битов в выделенную скорость передачи битов следующего изображения, чтобы тем самым каждый раз корректировать ошибки.

[0004] Способ для выделения постоянной скорости R передачи битов для множества изображений и включение ошибки скорости передачи битов в постоянную скорость R передачи битов, как предложено в Непатентном Документе 1 ниже, широко используется в том случае, когда кодирование с CBR (постоянной скоростью передачи битов) выполняется в одном проходе.

[0005] С другой стороны, в том случае, когда способ кодирования с CBR применяется в отношении многопроходного кодирования, при котором выделенная скорость передачи битов для каждого изображения определена заранее, то так как выделенная скорость передачи битов для каждого изображения определена заранее, нет необходимости в процессе выделения постоянной скорости передачи битов множеству изображений. Соответственно, в том случае, когда этот способ кодирования с CBR применяется в отношении многопроходного кодирования, коррекция выполняется посредством сложения ошибки скорости передачи битов, сформированной при кодировании каждого изображения, с выделенной скоростью передачи битов для следующего изображения.

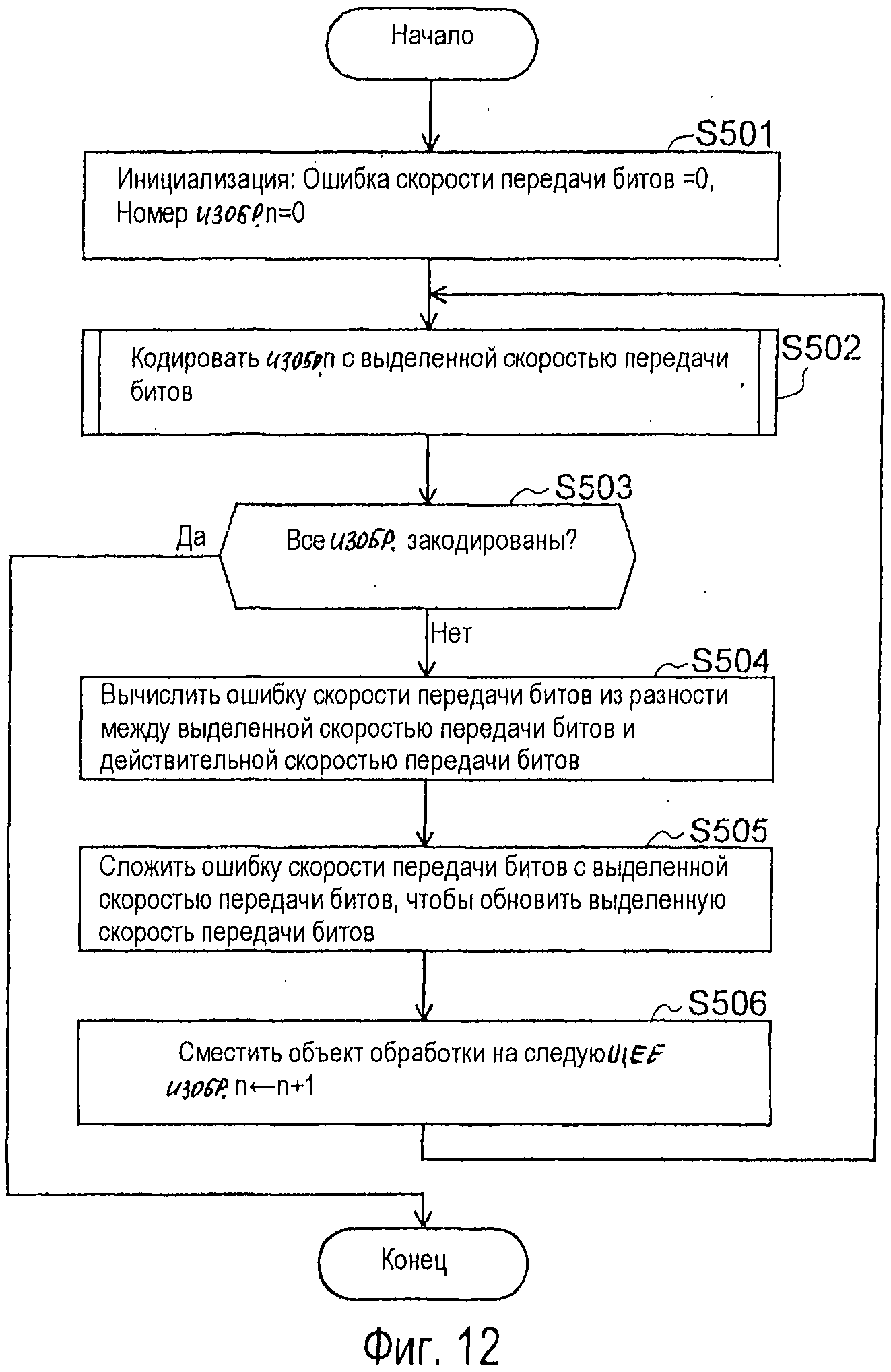

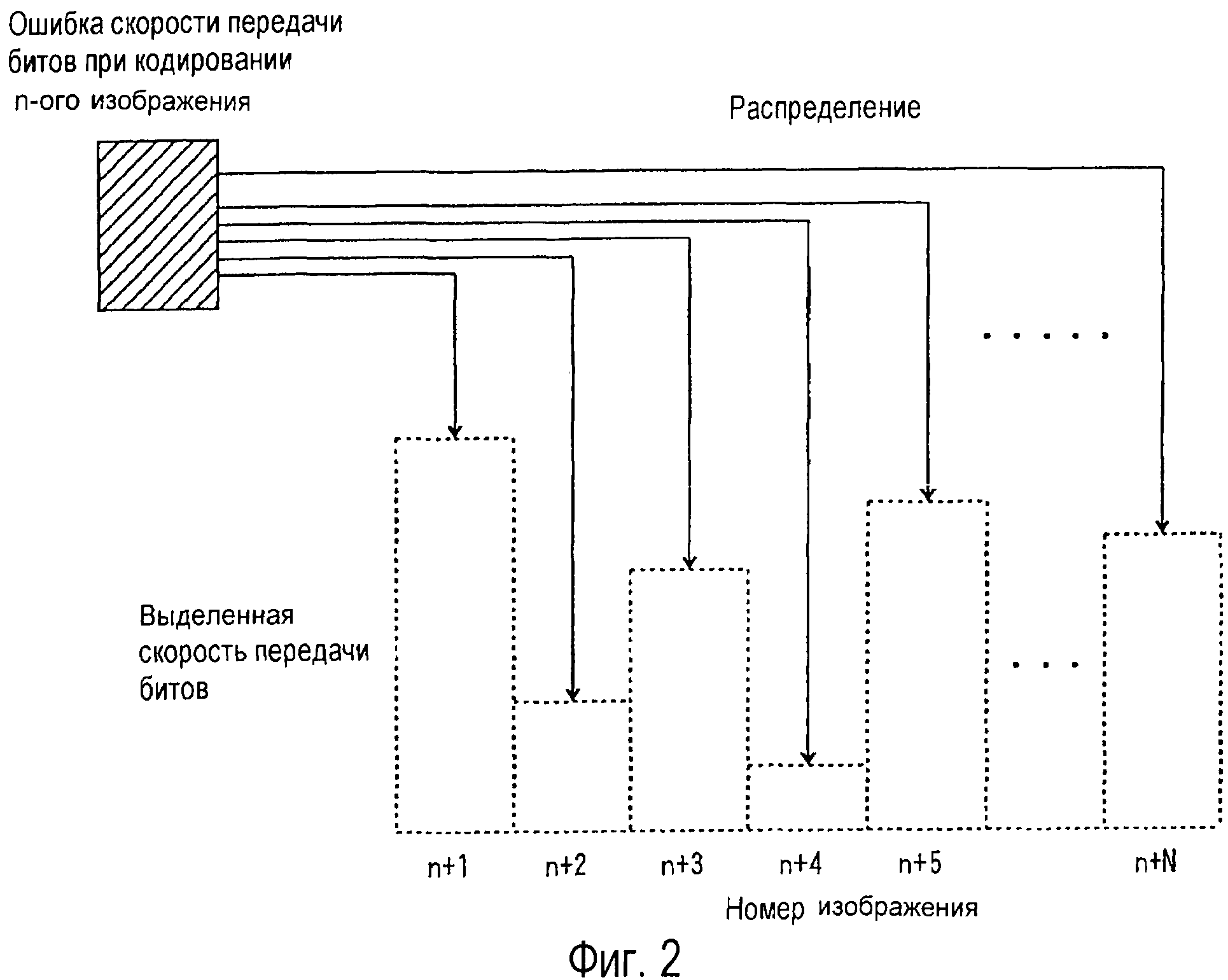

[0006] Фиг.2 показывает пример блок-схемы в соответствии с предшествующим уровнем техники, по которой после того, как на основании результатов первого кодирования, были вычислены выделенная скорость передачи битов и характеристики каждого изображения, используется вышеописанный способ (способ для выполнения коррекции посредством сложения ошибки скорости передачи битов, сформированной при кодировании каждого изображения, с выделенной скоростью передачи битов для следующего изображения).

[0007] В предшествующем уровне техники сначала на этапе S501 в качестве процесса инициализации, ошибке скорости передачи битов и номеру n изображения устанавливаются исходные значения, равные 0, как показано на этой блок-схеме.

[0008] Затем на этапе S502 в соответствии с предварительно заданной выделенной скоростью передачи битов кодируется nое изображение.

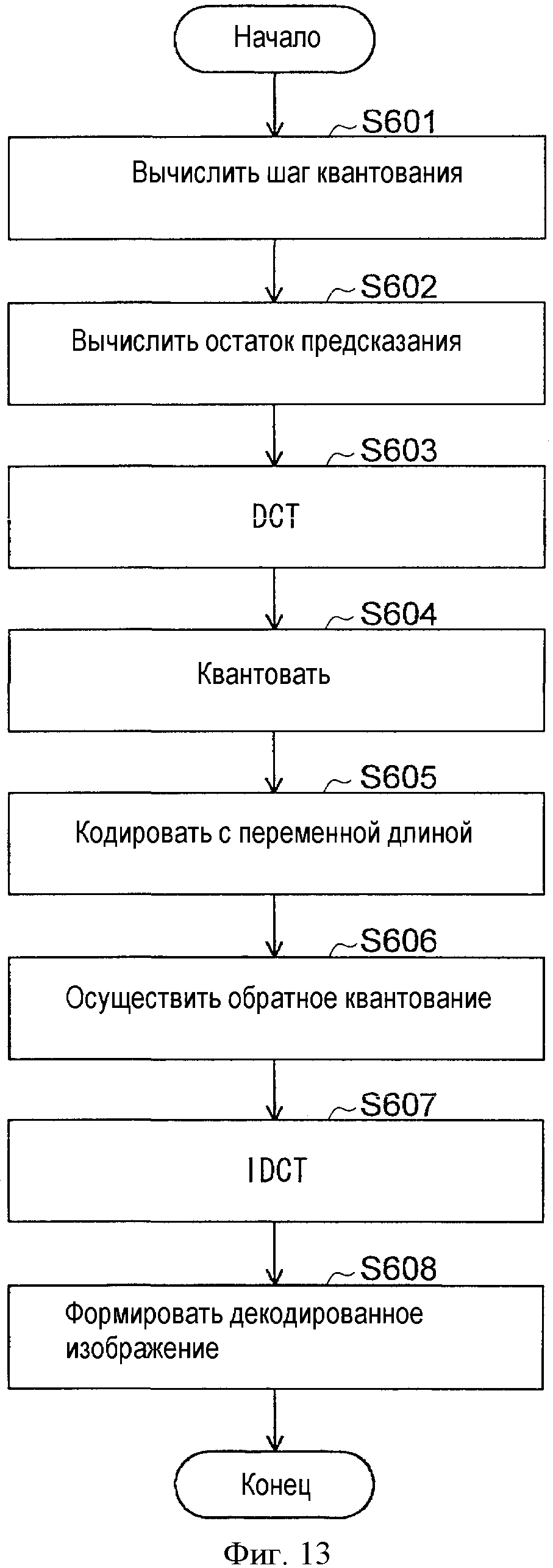

[0009] То есть выполняется процесс кодирования, показанный на блок-схеме Фиг.13. Из выделенной скорости передачи битов для nого изображения и характеристики nого изображения вычисляется шаг квантования (этап S601), вычисляется остаток предсказания (этап S602), применяется дискретное косинусное преобразование (DCT) (этап S603), и квантуется коэффициент DCT (этап S604). Затем посредством кодирования с переменной длиной формируется закодированный поток (этап S605). С другой стороны, подвергнутый квантованию коэффициент DCT подвергается обратному квантованию (этап S606) и обратному дискретному косинусному преобразованию (IDCT) (этап 607), для того чтобы создать декодированное изображение остатка предсказания, которое складывается с предсказанным изображением, для того чтобы сформировать декодированное изображение (этап S608).

[0010] Затем на этапе S503 определяют, были или нет закодированы все кадры (все изображения) и в том случае, когда были закодированы все кадры, процесс прекращается, а в том случае, когда были закодированы не все кадры, выполняется нижеследующий процесс.

[0011] То есть на следующем этапе S504, вычисляется ошибка скорости передачи битов из разности между выделенной скоростью передачи битов и фактической скоростью передачи битов, сформированным при кодировании. На следующем этапе S505 ошибка скорости передачи битов складывается с выделенной скоростью передачи битов для следующего изображения, для того чтобы обновить выделенную скорость передачи битов для следующего изображения. На следующем этапе S506 объект обработки смещается на следующее изображение, поток обработки возвращается к процессу этапа S502, и вышеописанная процедура выполняется повторно.

[0012] На протяжении вышеописанных процессов каждый раз корректируются ошибки между выделенными скоростями передачи битов и сформированными скоростями передачи битов, тем самым может быть получен закодированный поток, близкий к целевому размеру файла.

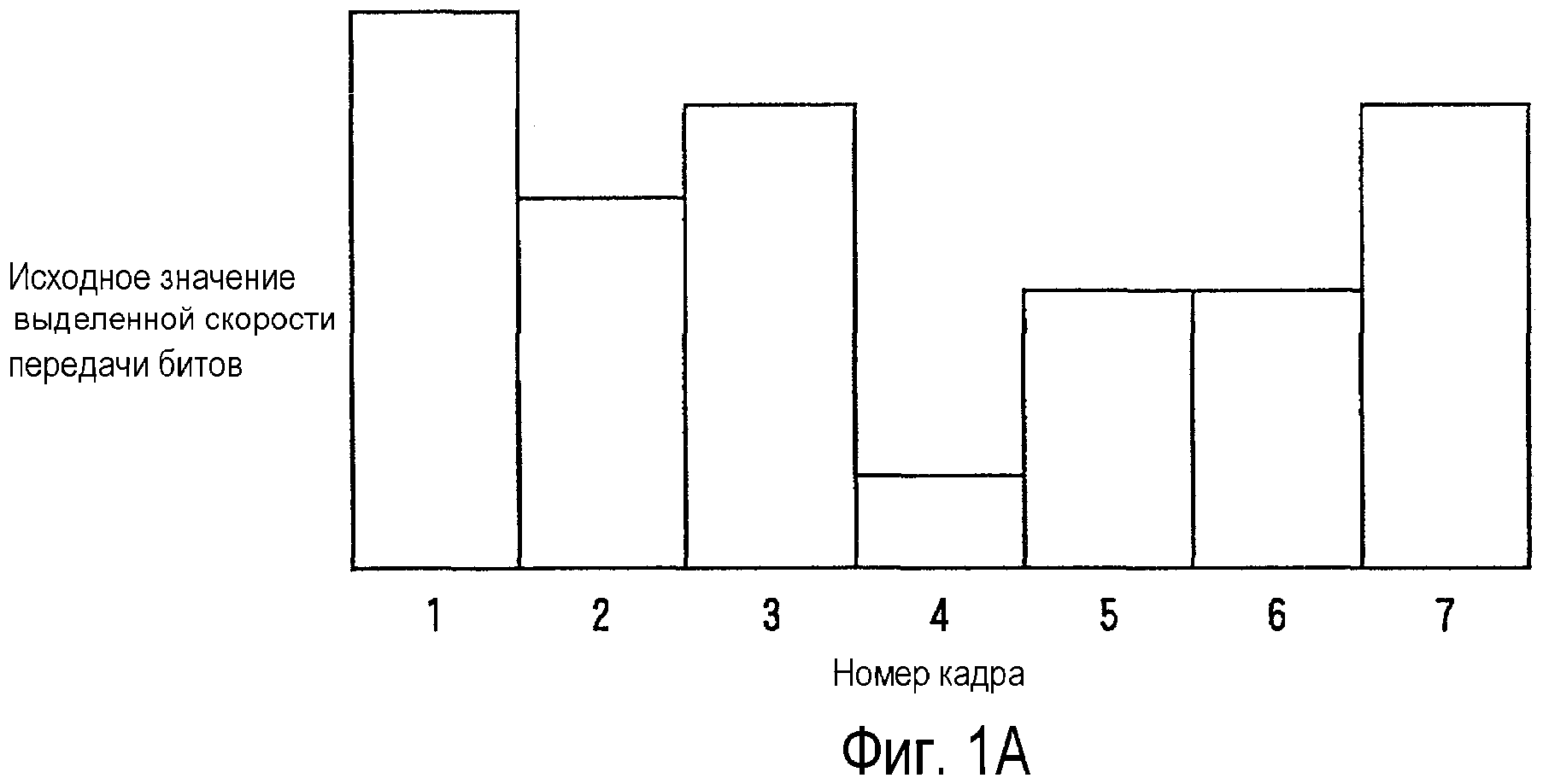

[0013] Фиг.14 иллюстрирует конфигурацию устройства для традиционного устройства кодирования видео, выполняющего процессы блок-схем, показанных на Фиг.12 и 13.

[0014] Как показано на Фиг.14, обычное устройство кодирования видео, выполняющее процессы блок-схем, показанных на Фиг.12 и 13, предоставлено с модулем 101 хранения выделенной скорости передачи битов, двумя модулями 102 и 111 сложения, двумя модулями 103 и 106 вычитания, модулем 104 хранения характеристик, модулем 105 вычисления шага квантования, модулем 107 DCT, модулем 108 квантования, модулем 109 обратного квантования, модулем 110 IDCT, буфером 112 хранения декодированного изображения, модулем 113 формирования предсказанного изображения и модулем 114 кодирования с переменной длиной.

[0015] Модуль 101 хранения выделенной скорости передачи битов хранит исходные значения выделенных скоростей передачи битов для соответствующих изображений и по одному выдает их модулю 102 сложения. Модуль 102 сложения складывает исходное значение выделенной скорости передачи битов, выданное модулем 101 хранения выделенной скорости передачи битов, с ошибкой скорости передачи битов, выданной модулем 103 вычитания, для того чтобы вычислить и выдать выделенную скорость передачи битов для кодируемого изображения. Модуль 103 вычитания вычисляет разность между выделенной скоростью передачи битов, выданной модулем 102 сложения, и сформированным скоростью передачи битов, выданным модулем 114 кодирования с переменной длиной, для того чтобы вычислить и выдать ошибку скорости передачи битов для закодированного изображения. Модуль 104 хранения характеристик хранит характеристики соответствующих изображений, полученные при кодировании первого прохода, и выдает их по одной модулю 105 вычисления шага квантования. Модуль 105 вычисления шага квантования вычисляет и выдает шаг квантования кодируемого изображения на основании характеристик, выданных модулем 104 хранения характеристик, и выделенной скорости передачи битов, выданной модулем 102 сложения.

[0016] Модуль 106 вычитания вычисляет разность между входным изображением и предсказанным изображением, выданным модулем 113 формирования предсказанного изображения, для того чтобы сформировать и выдать остаток предсказания. Модуль 107 DCT применяет DCT к остатку предсказания, выданному модулем 106 вычитания. Модуль 108 квантования применяет квантование к каждому коэффициенту DCT, выданному модулем 107 DCT, используя шаг квантования, выданный модулем 105 вычисления шага квантования. Модуль 109 обратного квантования применяет обратное квантование к значению квантования, выданному модулем 108 квантования, используя шаг квантования, выданный модулем 105 вычисления шага квантования. Модуль 110 IDCT применяет IDCT к подвергнутому обратному квантованию коэффициенту, выданному модулем 109 обратного квантования. Модуль 111 сложения складывает остаток предсказания декодированного сигнала, выданного модулем 110 IDCT, с предсказанным изображением, выданным модулем 113 формирования предсказанного изображения, для того чтобы сформировать декодированное изображение, и выдает его буферу 112 хранения декодированного изображения. Буфер 112 хранения декодированного изображения хранит декодированное изображение, выданное модулем 111 сложения. Модуль 113 формирования предсказанного изображения формирует и выдает предсказанное изображение на основании декодированного изображения, хранящегося в буфере 112 хранения декодированного изображения. Модуль 114 кодирования с переменной длиной применяет кодирование с переменной длиной в отношении подвергнутого квантованию коэффициента DCT, который выдан модулем 108 квантования, и выдает закодированный поток.

[0017] Традиционное устройство кодирования видео выполняет процессы блок-схем, показанных на Фиг.12 и 13, используя конфигурацию, показанную на Фиг.14.

[0018] Отмечено, что способ с CBR скоростью, который является основой способа, описанного в Непатентном Документе 1, объясняется в Патентном Документе 1 ниже, в котором приводится Название Документа (ISO/IEC JTC/SC29/WG11: “Test Model 5”, 1993). Тем не менее, изобретение, описанное в этом документе, является всего лишь способом в рамках CBR, даже несмотря на то, что реакция на отклонение скорости передачи битов выше в сравнении со способом, описанным в Непатентном Документе 1. Соответственно, в том случае, когда изобретение, описанное в этом документе, применяется к многопроходному кодированию, коррекция выполняется посредством сложения ошибки скорости передачи битов, сформированной после кодирования каждого изображения, с выделенной скоростью передачи битов для следующего изображения, как и в случае, когда применяется способ, описанный в Непатентном документе 1.

Документы предшествующего уровня техники

Патентный Документ

[0019] Патентный документ 1. Не прошедшая экспертизу Патентная Заявка Японии, Первая Публикация №2000-358247

Непатентный документ

[0020] Непатентный Документ 1: Hiroshi Yasuda и Hiroshi Watanabe, “Basis of Digital Image Compression,” NIKKEI BP Publishing Center, стр. 189-193, 1999.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Задачи, решаемые изобретением

[0021] Таким образом, в том случае, когда способ кодирования с CBR применяется к многопроходному кодированию, при котором выделенная (назначенная) скорость передачи битов для каждого изображения предварительно определена, коррекция выполняется посредством сложения ошибки скорости передачи битов, сформированной после кодирования каждого изображения, с выделенной скоростью передачи битов для следующего изображения, как объясняется на блок-схемах, показанных на Фиг.12 и 13.

[0022] Тем не менее, в соответствии с таким способом, ошибка скорости передачи битов предыдущего изображения уменьшается в следующем изображении и соответственно существует проблема в том, что возрастает отклонение от предварительно полученной выделенной скорости передачи битов.

[0023] Конкретно, при функционировании с переменной скоростью передачи битов (VBR), при котором подразумевается, что выделенная скорость передачи битов внутри последовательности изменяется сильно, выделенные скорости передачи битов, изначально сильно различаются от изображения к изображению. Соответственно, в том случае, когда ошибка скорости передачи битов, сформированная для предыдущего изображения, складывается с выделенной скоростью передачи битов следующего изображения, отклонение от исходной выделенной скорости передачи битов возрастает, и существует высокая опасность того, что качество изображения между изображениями будет сильно меняться.

[0024] Настоящее изобретение было получено, принимая во внимание вышеупомянутые обстоятельства, и целью настоящего изобретения является предоставить новый способ управления скоростью передачи битов видео для реализации улучшения в субъективном качестве изображения посредством снижения отклонения качества изображения между изображениями в том случае, когда реализуется кодирование видео с целевой скоростью передачи битов.

Средства Решения Задач

[0025] Для того чтобы добиться этой цели, настоящее изобретение является способом управления скоростью передачи битов видео, который управляет формируемой скоростью передачи битов кодируемого изображения на основании исходного значения выделенной скорости передачи битов, которое предварительно задано для каждого изображения. При этом способ содержит этапы, на которых: в качестве ошибки скорости передачи битов получают разность между выделенной скоростью передачи битов и фактически сформированной скоростью передачи битов закодированного изображения; выбирают для множества последующих изображений одно из максимального значения, либо минимального значения выделенной скорости передачи битов в качестве допустимого диапазона коррекции, на основании знака ошибки скорости передачи битов, при этом максимальное значение и минимальное значение выделенной скорости передачи битов вычислены из исходного значения выделения скорости передачи битов и предварительно заданной константы; в качестве допустимого отклонения скорости передачи битов получают, для множества изображений, разность между допустимым диапазоном коррекции и выделенной скорости передачи битов; в качестве величины обновления получают как величину обновления отношение суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов; и вычисляют, для множества изображений, отклонение скорости передачи битов для выделенной скорости передачи битов на основании допустимого отклонения скорости передачи битов и величины обновления, и корректируют выделенную скорость передачи битов для каждого из множества изображений на основании отклонения скорости передачи битов.

[0026] Способ управления скоростью передачи битов видео настоящего изобретения предпочтительно содержит этап, на котором для каждого изображения заранее получают максимальное значение и минимальное значение выделенной скорости передачи битов на основании исходного значения выделенной скорости передачи битов и константы.

[0027] Предпочтительно, в способе управления скоростью передачи битов видео настоящего изобретения, на этапе выбора, выбирают максимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда выделенная скорость передачи битов больше фактически сформированной скорости передачи битов, а значение ошибки скорости передачи битов указывает положительное значение, и выбирают минимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда выделенная скорость передачи битов ниже фактически сформированной скорости передачи битов, а ошибка скорости передачи битов указывает отрицательное значение.

[0028] Предпочтительно, способ управления скоростью передачи битов видео настоящего изобретения содержит этапы, на которых: ограничивают величину обновления таким образом, чтобы она была в заданном диапазоне; в качестве переноса скорости передачи битов получают разность между ошибкой скорости передачи битов и суммой отклонений скоростей передачи битов; складывают перенос скорости передачи битов с ошибкой скорости передачи битов, полученным после кодирования следующего изображения.

[0029] Предпочтительно, в способе управления скоростью передачи битов видео настоящего изобретения величина обновления является общей для множества изображений.

[0030] Дополнительно, настоящее изобретение является устройством управления скоростью передачи битов видео, которое управляет формируемой скоростью передачи битов кодируемого изображения на основании исходного значения выделенной скорости передачи битов, которое предварительно задано для каждого изображения, при этом устройство содержит: средство для получения в качестве ошибки скорости передачи битов разности между выделенной скоростью передачи битов и фактической сформированной скоростью передачи битов для закодированного изображения;

средство для выбора для множества последующих изображений одного из максимального значения либо минимального значения выделенной скорости передачи битов в качестве допустимого диапазона коррекции, на основании знака ошибки скорости передачи битов, при этом максимальное значение и максимальное значения выделенной скорости передачи битов вычисляются из исходного значения выделенной скорости передачи битов и предварительно заданной константы; средство для получения в качестве допустимого отклонения скорости передачи битов, для множества изображений, разности между допустимым диапазоном коррекции и выделенной скорости передачи битов; средство для получения в качестве величины обновления отношения суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов; и средство для вычисления, для множества изображений, отклонения скорости передачи битов для выделенной скорости передачи битов на основании допустимого отклонения скорости передачи битов и величины обновления, и коррекции выделенной скорости передачи битов для каждого из множества изображений на основании отклонения скорости передачи битов.

[0031] Предпочтительно, устройство управления скоростью передачи битов видео настоящего изобретения содержит средство для получения заранее для каждого изображения максимального значения и минимального значения выделенной скорости передачи битов на основании исходного значения выделенной скорости передачи битов и константы.

[0032] Предпочтительно, в устройстве управления скоростью передачи битов видео настоящего изобретения средство выбора выбирает максимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда значение выделенной скорости передачи битов выше фактически сформированной скорости передачи битов, а ошибка скорости передачи битов указывает положительное значение, и выбирает минимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда значение выделенной скорости передачи битов ниже, чем фактически сформированная скорость передачи битов, а ошибка скорости передачи битов указывает отрицательное значение.

[0033] Предпочтительно, устройство управления скоростью передачи битов видео настоящего изобретения содержит: средство для ограничения величины обновления таким образом, чтобы она была в заданном диапазоне; средство для получения в качестве переноса скорости передачи битов разности между ошибкой скорости передачи битов и суммой отклонений скоростей передачи битов; и средство для сложения переноса скорости передачи битов с ошибкой скорости передачи битов, полученным после кодирования следующего изображения.

[0034] Предпочтительно, в устройстве управления скоростью передачи битов видео настоящего изобретения величина обновления является единой для множества изображений.

[0035] Кроме того, настоящим изобретением является программа управления скоростью передачи битов видео, которая заставляет компьютер выполнять способ управления скоростью передачи битов видео настоящего изобретения.

[0036] Более того, настоящее изобретение является машиночитаемым носителем записи, на котором записана программа управления скоростью передачи битов видео для того, чтобы заставить компьютер выполнить способ управления скоростью передачи битов видео настоящего изобретения.

Полезные эффекты изобретения

[0037] В соответствии с настоящим изобретением, допустимые отклонения скоростей передачи битов для множества заранее определенных изображений получают на основании допустимых диапазонов коррекции выделенных скоростей передачи битов, которые определены на основании размеров исходных значений выделенных скоростей передачи битов соответствующих изображений, при этом величину обновления получают из отношения суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов, причем отклонения скоростей передачи битов, выделенные соответствующим изображениям, получают на основании допустимых отклонений скоростей передачи битов соответствующих изображений и величины обновления, а ошибка скорости передачи битов выделяется для выделенных скоростей передачи битов для множества последующих изображений в соответствии с отклонениями скоростей передачи битов.

Соответственно, ошибка скорости передачи битов, сформированная для закодированного изображения, распределяется на следующее изображение, как впрочем и на множество изображений, тем самым компенсируя отклонение выделенной скорости передачи битов следующего изображения, и так снижая отклонение качества изображения между изображениями.

[0038] Дополнительно, так как максимальные значения и минимальные значения выделенных скоростей передачи битов не являются фиксированными, а определяются на основании предварительно заданных исходных значений выделенных скоростей передачи битов, а величины распределения (отклонения скоростей передачи битов) определяются на их основании, то изменение шага квантования, вызванное коррекцией ошибки скорости передачи битов, происходит в постоянном диапазоне даже в том случае, когда отклонение выделенной скорости передачи битов между изображениями велико, подобно VBR.

[0039] Кроме того, так как величины распределения (отклонения скоростей передачи битов) получают на основании величины обновления, которая является общей для допустимых отклонений скоростей передачи битов соответствующих изображений, величина шагов квантования соответствующих изображений изменяется в той же степени и изменение качества изображения между изображениями, вызванное настоящим процессом, сохраняется малым.

[0040] Более того, так как существует механизм для переноса ошибки скорости передачи битов, которая не может быть распределена, то становится возможным непрерывно выполнять управление без сбоев даже в том случае, когда при традиционном способе вероятен сбой в управлении. Дополнительно, так как процесс ограничения для реализации этого механизма выполняется только для величины обновления, обработка может выполняться только с одним условным переходом.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

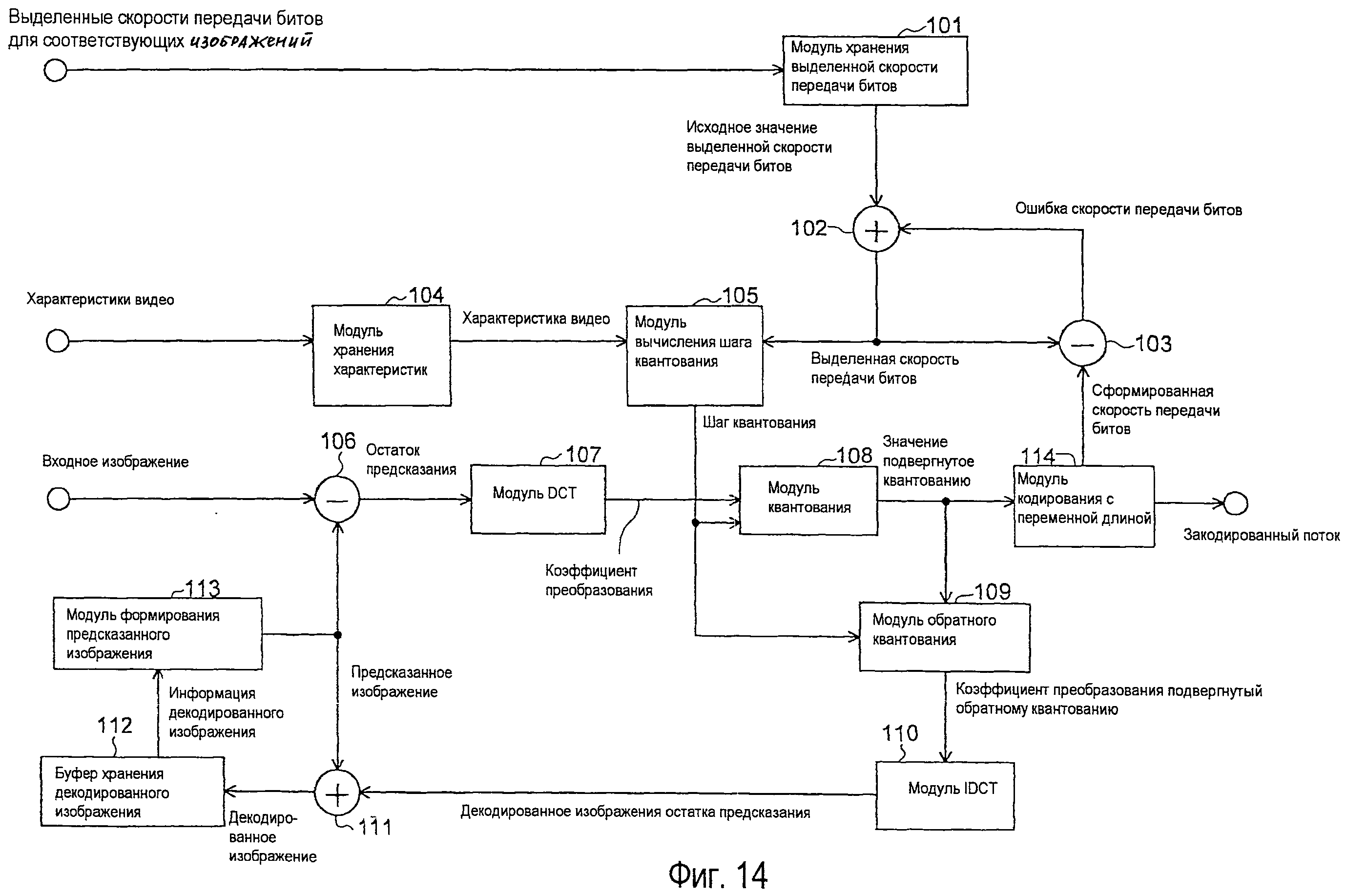

[0041] Фиг.1A является пояснительной схемой, которая показывает процесс в устройстве управления скоростью передачи битов видео, в котором применяется настоящее изобретение.

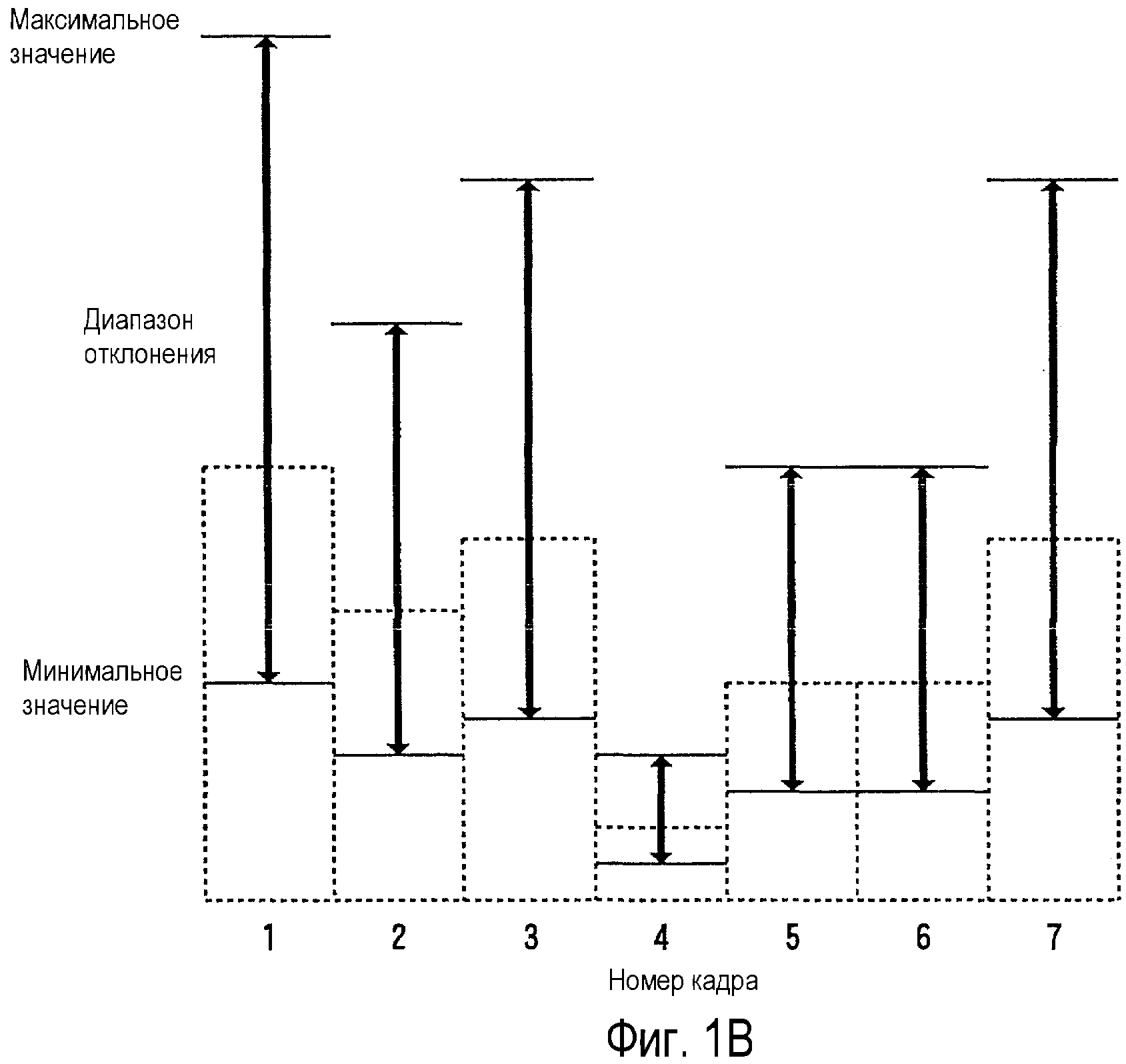

Фиг.1B является пояснительной схемой, которая показывает процесс в устройстве управления скоростью передачи битов видео, в котором применяется настоящее изобретение.

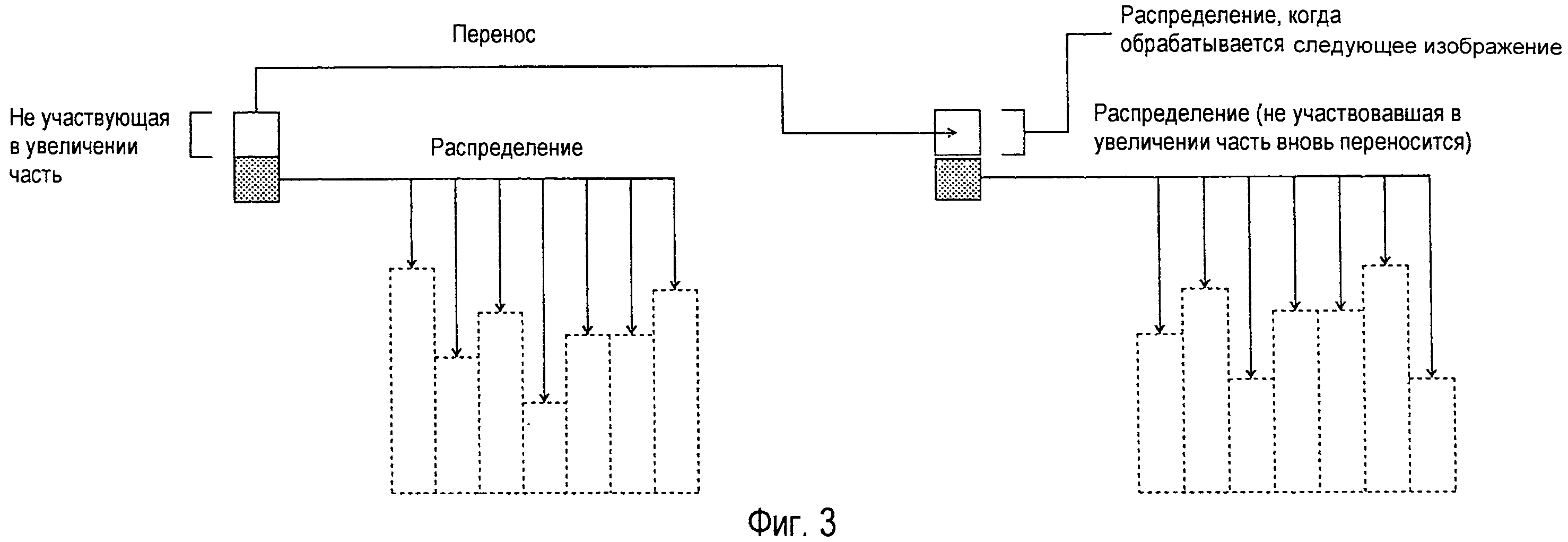

Фиг.2 является пояснительной схемой, которая показывает процесс в устройстве управления скоростью передачи битов видео, в котором применяется настоящее изобретение.

Фиг.3 является пояснительной схемой, которая показывает процесс в устройстве управления скоростью передачи битов видео, в котором применяется настоящее изобретение.

Фиг.4 является схемой, которая показывает пример конфигурации устройства для устройства кодирования видео, которое включает в себя устройство управления скоростью передачи битов видео, в котором применяется настоящее изобретение.

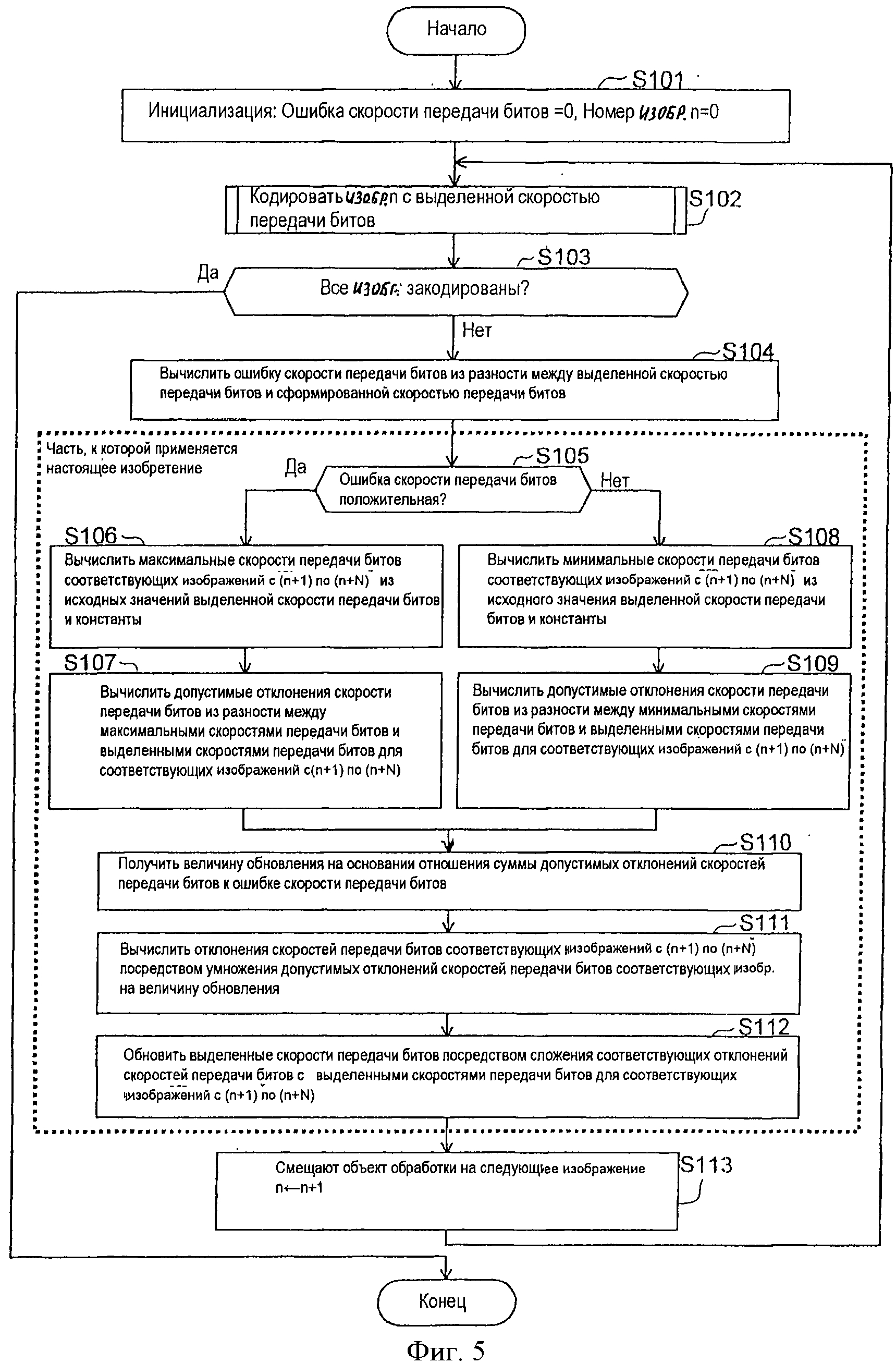

Фиг.5 является блок-схемой, которая выполняется в модуле вычисления выделенной скорости передачи битов;

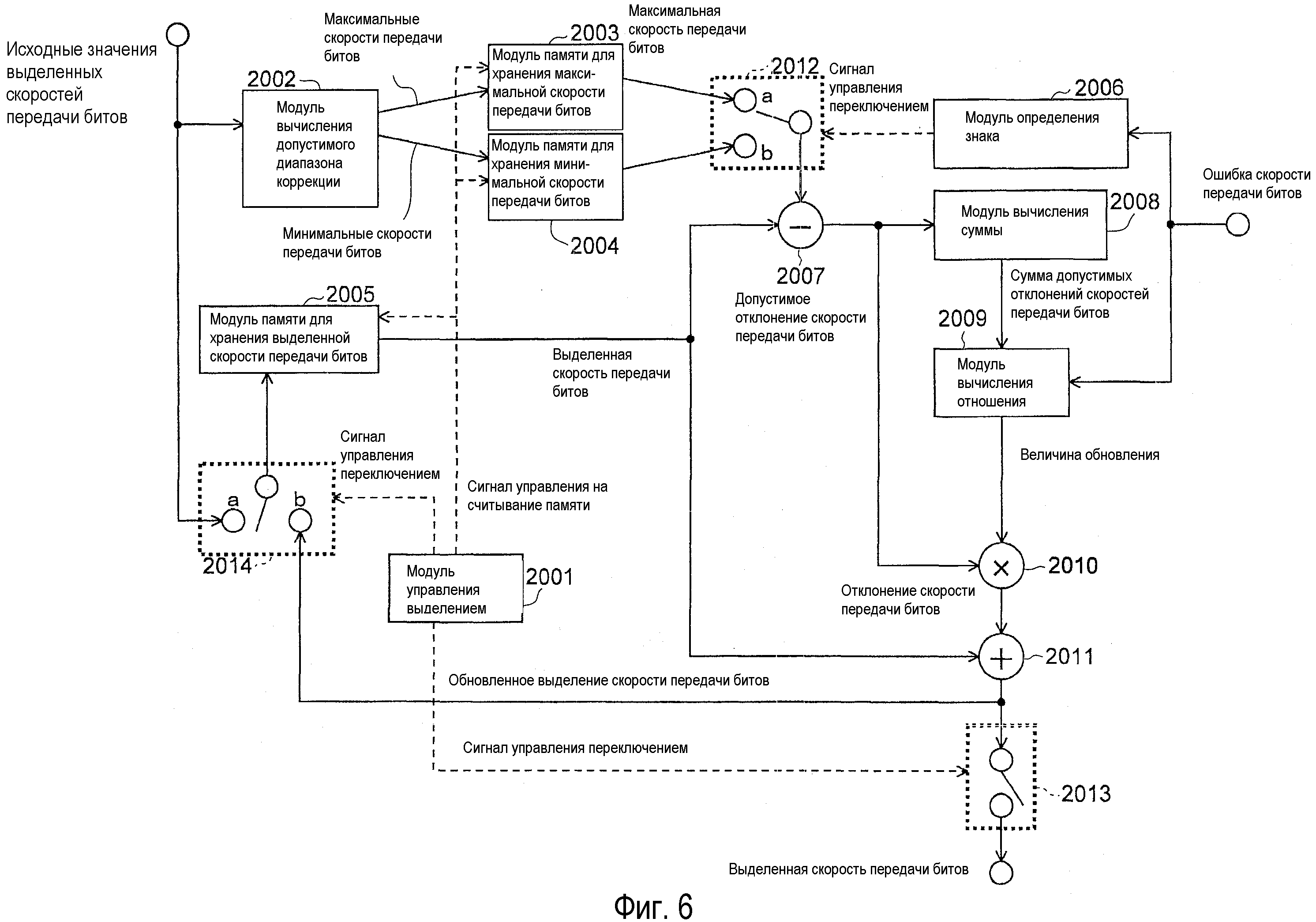

Фиг.6 является схемой, которая показывает пример конфигурации устройства для модуля вычисления выделенной скорости передачи битов;

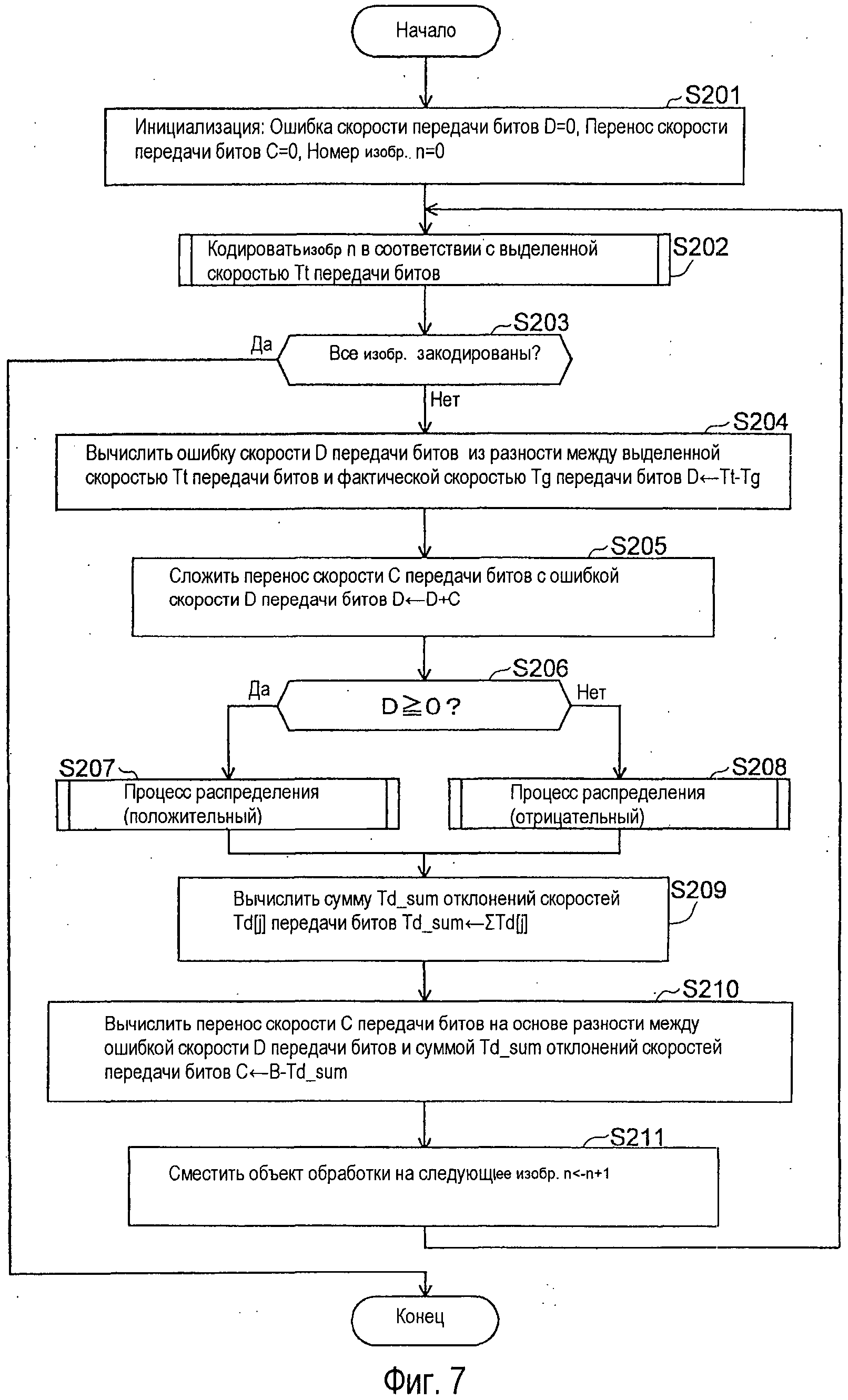

Фиг.7 является блок-схемой, которая выполняется модулем вычисления выделенной скорости передачи битов;

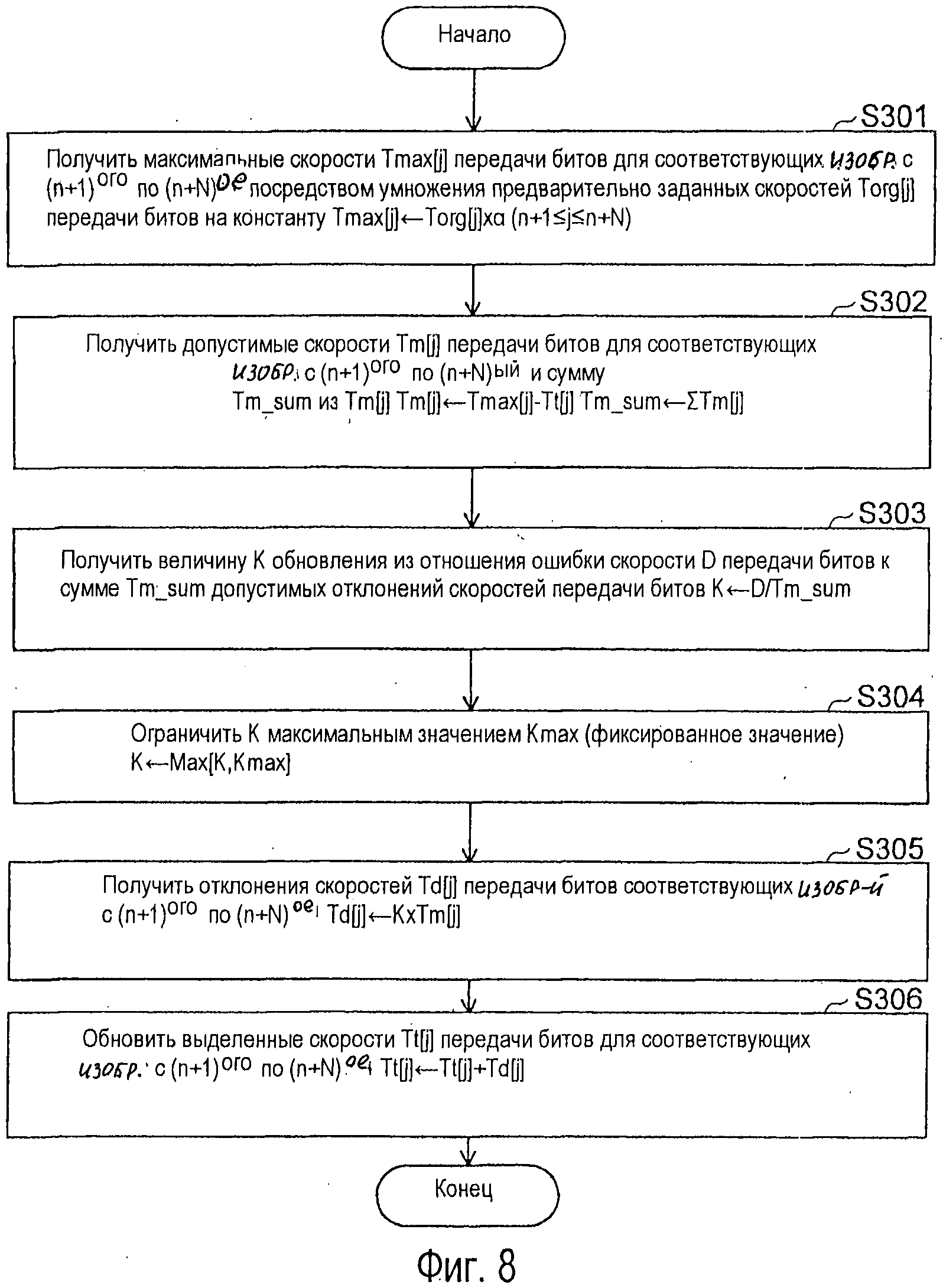

Фиг.8 является блок-схемой, которая выполняется модулем вычисления выделенной скорости передачи битов;

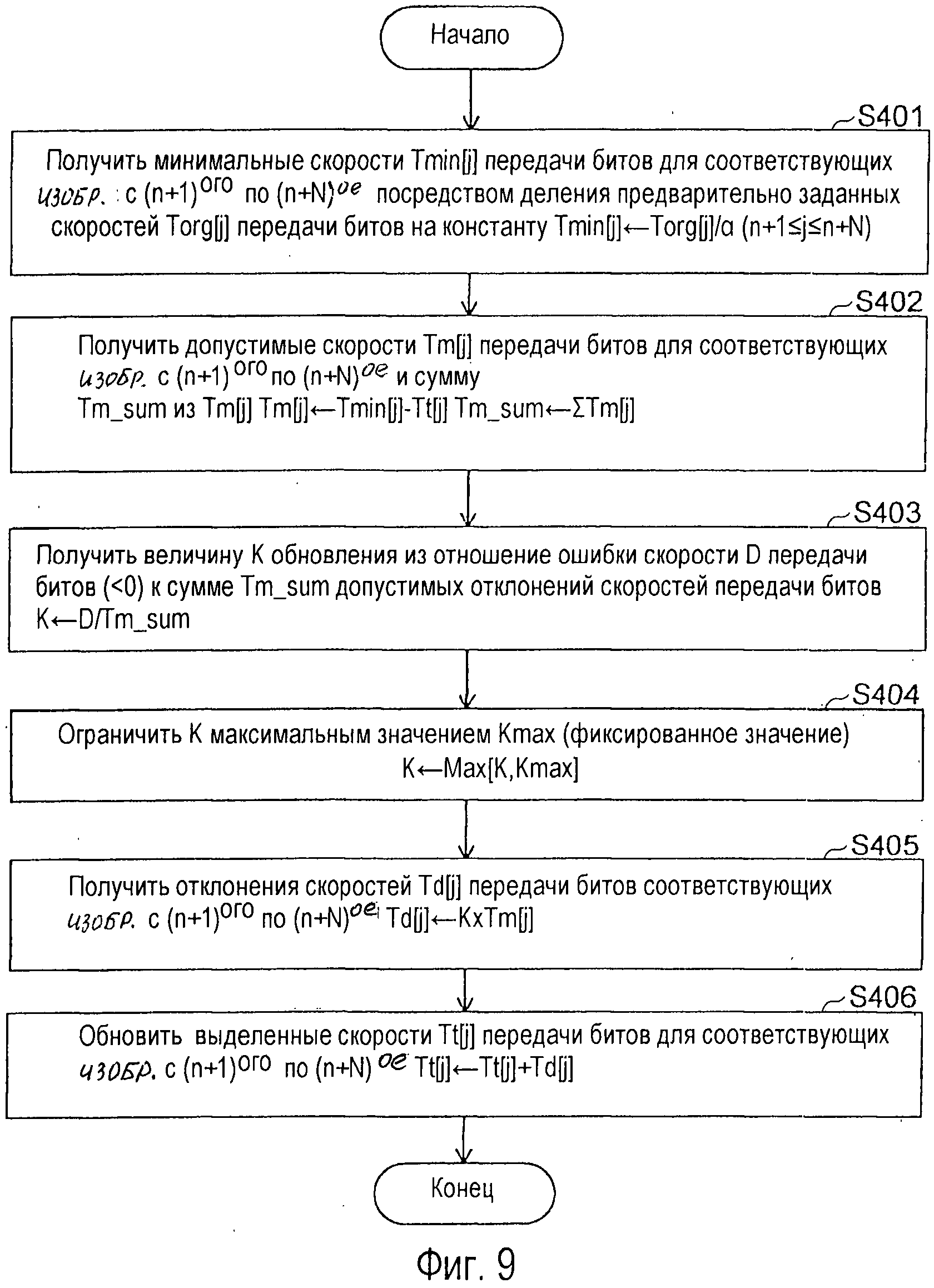

Фиг.9 является блок-схемой, которая выполняется модулем вычисления выделенной скорости передачи битов;

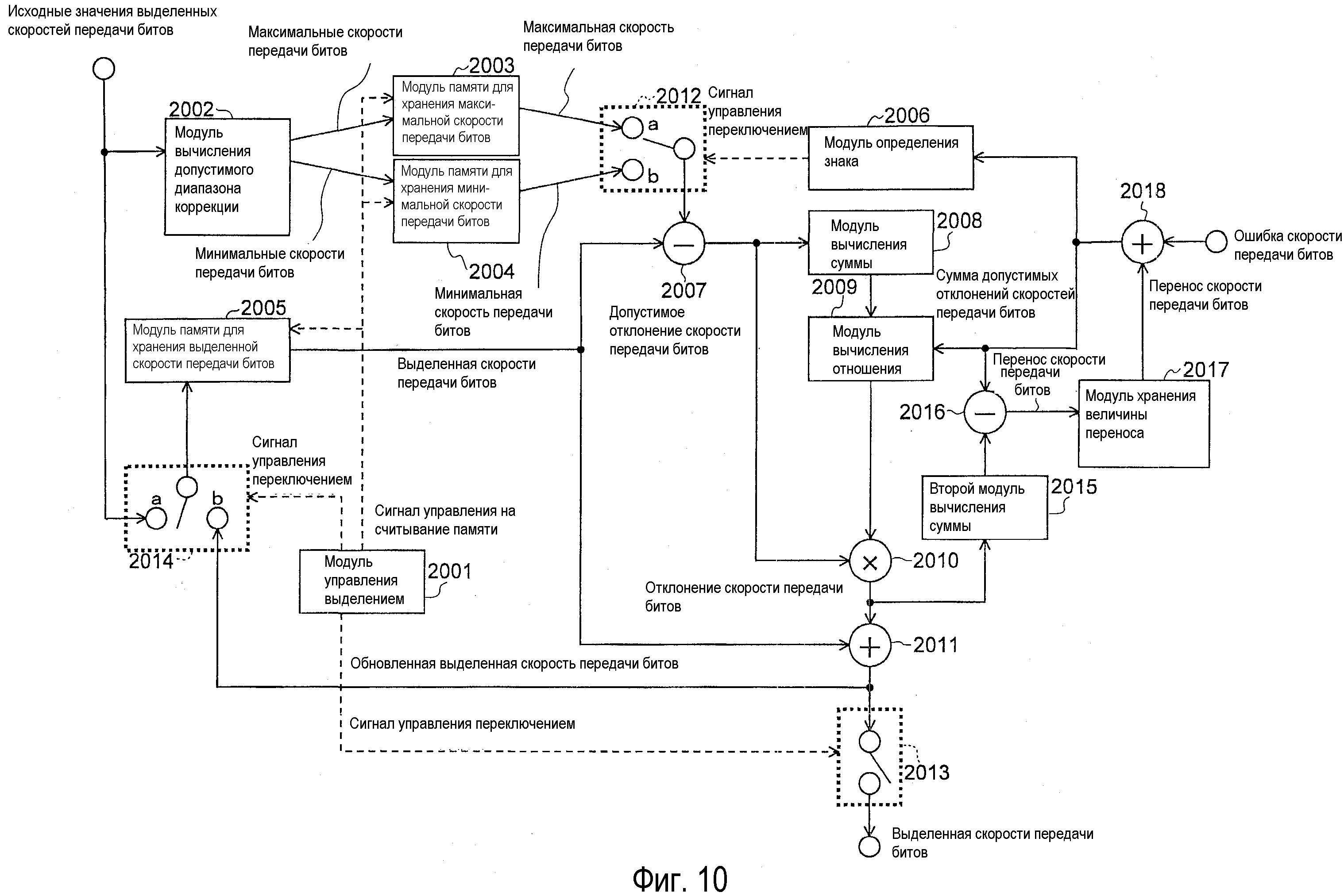

Фиг.10 является схемой, которая показывает пример конфигурации устройства для модуля вычисления выделенной скорости передачи битов;

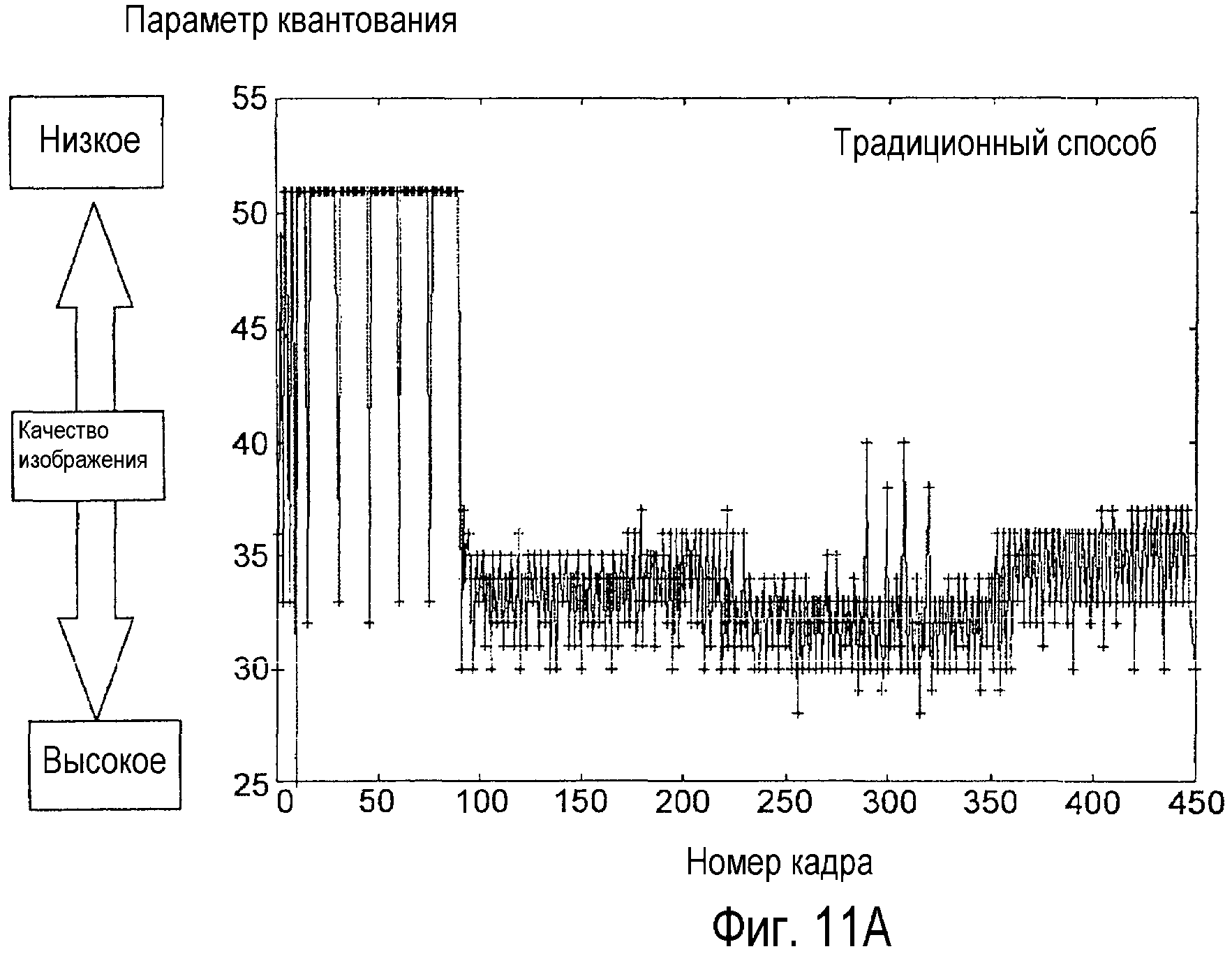

Фиг.11A является пояснительной схемой, которая показывает результат эксперимента, основанного на традиционном способе, который выполнен, для того чтобы проверить эффективность настоящего изобретения;

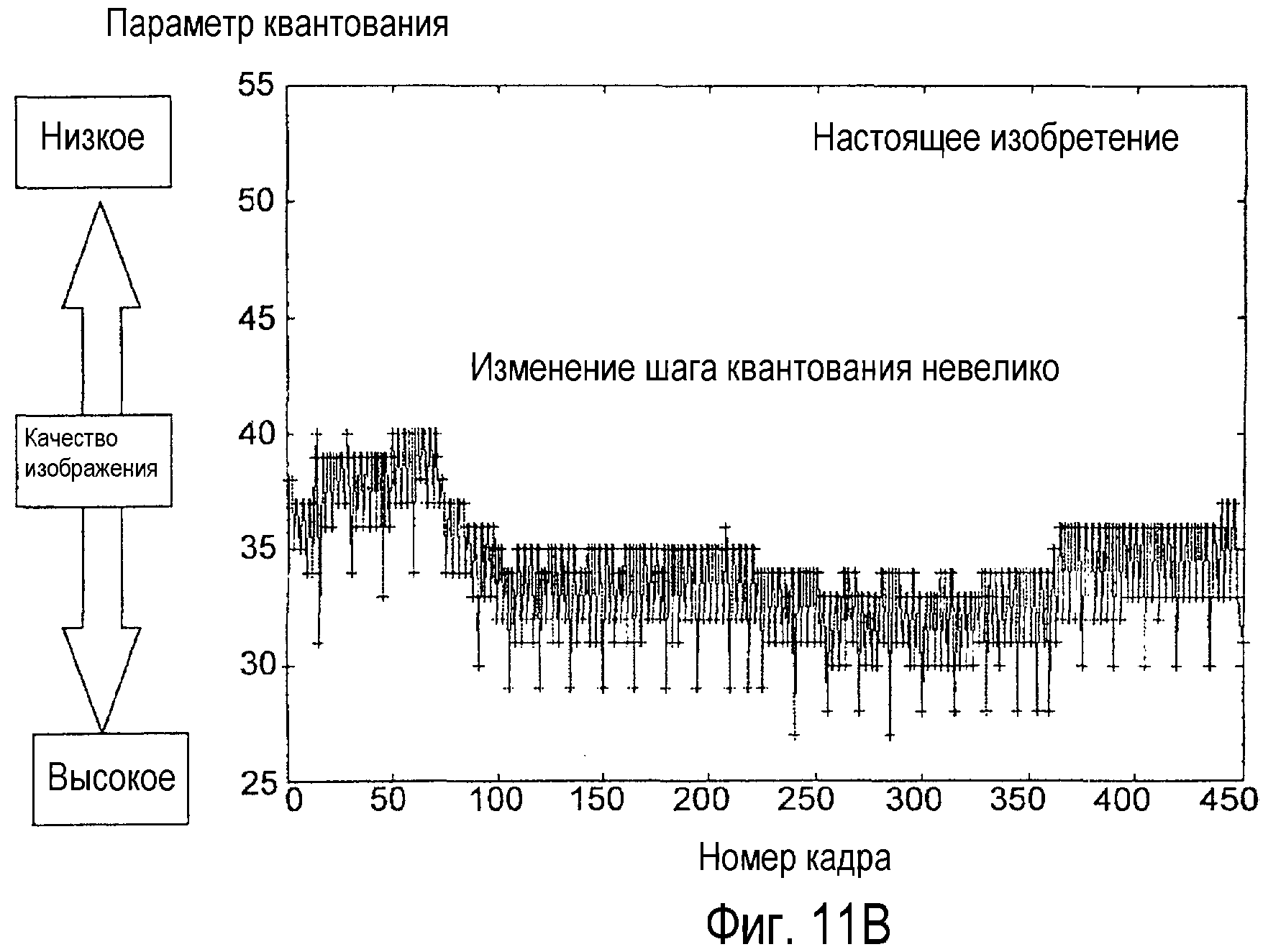

Фиг.11B является пояснительной схемой, которая показывает результат эксперимента, основанного на настоящем изобретении, который выполнен, для того чтобы проверить эффективность настоящего изобретения;

Фиг.12 является блок-схемой в соответствии с предшествующим уровнем техники;

Фиг.13 является блок-схемой процесса кодирования изображения; и

Фиг.14 является схемой конфигурации устройства в соответствии с предшествующим уровнем техники.

ВАРИАНТ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

[0042] Здесь и далее настоящее изобретение будет описано более подробно в соответствии с вариантами осуществления.

[0043] Перед началом описания вариантов осуществления настоящего изобретения сначала будут описаны основные принципы устройства управления скоростью передачи битов видео, к которому применяется настоящее изобретение.

[1] Конфигурация устройства управления скоростью передачи битов видео

В том случае, если это устройство управления скоростью передачи битов видео принимает конфигурацию для управления формируемой скоростью передачи битов кодируемого изображения, основанную на исходном значении выделенной скорости передачи битов, которое заранее задано для каждого изображения, то устройство управления скоростью передачи битов видео обеспечено: (1) первым средством вычисления для получения в качестве ошибки скорости передачи битов разности между выделенной скоростью передачи битов и фактически сформированной скоростью передачи битов закодированного изображения; (2) средством выбора для выбора для множества последующих изображений одного из максимального значения и минимального значения выделенной скорости передачи битов, которые вычислены из исходного значения выделенной скорости передачи битов, и предварительно заданной константы в качестве допустимого диапазона коррекции, на основании знака ошибки скорости передачи битов, который получен первым средством вычисления; (3) вторым средством вычисления для получения в качестве допустимого отклонения скорости передачи битов для множества изображений разности между допустимым диапазоном коррекции, который выбран средством выбора, и выделенной скоростью передачи битов; (4) третьим средством вычисления для вычисления суммы допустимых отклонений скоростей передачи битов, полученных вторым средством вычисления, и получения в качестве величины обновления отношения вычисленной суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов, которое получено первым средством вычисления; и (5) средством обновления для вычисления, для множества последующих изображений, отклонений скоростей передачи битов, которые соответствуют выделенным скоростям передачи битов, на основании допустимого отклонения скорости передачи битов, полученного вторым средством вычисления, и величины обновления, полученной третьим средством вычисления, и обновления выделенных скоростей передачи битов для множества изображений на основании вычисленных отклонений скоростей передачи битов.

[0044] Здесь максимальное значение и минимальное значение выделенной скорости передачи битов, которые могут быть выбраны средством выбора, могут получаться не каждый раз при получении ошибки скорости передачи битов, которая получается первым средством вычисления, а может быть предоставлено «четвертое средство вычисления для получения заранее для каждого изображения максимального значения и минимального значения выделенной скорости передачи битов на основании исходного значения выделенной скорости передачи битов и предварительно заданной константы» и средство выбора может считывать соответствующее одно из значений, полученных посредством четвертого средства вычисления.

[0045] Например, это четвертое средство вычисления может получать максимальное значение выделенной скорости передачи битов посредством умножения исходного значения выделенной скорости передачи битов на константу, а минимальное значение выделенной скорости передачи битов посредством деления исходного значения выделенной скорости передачи битов на константу, или может получать максимальное значение выделенной скорости передачи битов посредством сложения константы с исходным значением выделенной скорости передачи битов, а минимальное значение выделенной скорости передачи битов посредством вычитания константы из исходного значения выделенной скорости передачи битов.

[0046] В том случае, когда применяется эта конфигурация, могут быть дополнительно предоставлены: (6) средство ограничения для ограничения величины обновления, полученной третьим средством вычисления, таким образом, чтобы она была в заданном диапазоне; (7) пятое средство вычисления для вычисления суммы отклонений скоростей передачи битов, которые вычислены средством коррекции, и получения в качестве переноса скорости передачи битов разности между ошибкой скорости передачи битов, которая получена первым средством вычисления, и суммой; и (8) средство сложения для сложения переноса скорости передачи битов (который может указывать отрицательное значение), полученного пятым средством вычисления, с ошибкой скорости передачи битов, полученной при кодировании следующего изображения.

[0047] Более того, средство выбора выбирает максимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда ошибка скорости передачи битов указывает на положительное значение (в том случае, когда выделенная скорость передачи битов выше фактически сформированной скорости передачи битов), и выбирает минимальное значение выделенной скорости передачи битов в качестве допустимого диапазона коррекции в том случае, когда ошибка скорости передачи битов указывает на отрицательное значение (в том случае, когда выделенная скорость передачи битов меньше фактически сформированной скорости передачи битов). Отмечено, что случай, при котором ошибка скорости передачи битов равна 0, может обрабатываться как случай, при котором ошибка скорости передачи битов указывает положительное значение, или он может обрабатываться как в случае, при котором ошибка скорости передачи битов ошибки указывает отрицательное значение.

[0048] Способ управления скоростью передачи битов видео, реализуемый процессами в описанных выше соответствующих средствах обработки, также может быть реализован в компьютерной программе. Эта компьютерная программа является записанной на соответствующий машиночитаемый носитель записи и предоставляется или предоставляется посредством сети, в качестве установленной, в тот момент, когда данный способ управления скоростью передачи битов видео выполняется, и при этом выполняется на средстве управления, таком как центральное устройство обработки (CPU), тем самым реализуя данный способ управления скоростью передачи битов видео.

[0049]

[2] Пример процесса в устройстве управления скоростью передачи битов видео

Здесь и далее пример процесса в данном устройстве управления скоростью передачи битов видео, будет описан, с использованием конкретных примеров процессов, которые выполняются в том случае, когда предоставлено четвертое средство вычисления.

[0050] В устройстве управления скоростей передачи битов видео при такой конфигурации, исходное значение выделенной скорости передачи битов определяется для каждого кодируемого изображения, как показано на Фиг.1A, на основании определенного предварительного анализа, такого как первое кодирование. Например, в качестве максимального значения выделенной скорости передачи битов установлено исходное значение выделенной скорости передачи битов, умноженное на константу, а в качестве минимального значения выделенной скорости передачи битов установлено исходное значение выделенной скорости передачи битов, деленное на константу. Соответственно, диапазон отклонения выделенной скорости передачи битов (от максимального значения до минимального значения) определяется для каждого кодируемого изображения, как показано на Фиг.1B.

[0051] Так как определенный диапазон отклонения выделенной скорости передачи битов определяется на основании исходного значения выделенной скорости передачи битов, то для процесса кодирования диапазон отклонения является постоянным.

[0052] После этого начинается процесс кодирования и в качестве ошибки скорости передачи битов получают разность между выделенной скоростью передачи битов и фактически сформированной скоростью передачи битов закодированного изображения.

[0053] В предшествующем уровне техники, ошибка скорости передачи битов, полученная в этот момент, уменьшается посредством ее сложения с выделенной скоростью передачи битов следующего изображения, но этот способ вызывает увеличение отклонения от предварительно полученной выделенной скорости передачи битов.

[0054] Соответственно, данное устройство управления скоростью передачи битов видео принимает конфигурацию для распределения ошибки скорости передачи битов, полученную в этот момент, для N изображений, которые кодируются в дальнейшем, как показано на Фиг.2.

[0055] В этом случае не является предпочтительным использовать способ деления ошибки скорости передачи битов на N для равномерного распределения. Так как для изображения с большой выделенной скоростью передачи битов, по сути, требуется высокая скорость передачи битов, а для изображения с низкой выделенной скоростью передачи битов, по сути, не требуется такой скорости передачи битов, то не является предпочтительным использовать способ деления ошибки скорости передачи битов на N для равномерного распределения.

[0056] Соответственно, в данном устройстве управления скоростью передачи битов видео, для каждого из последующих N изображений получают запас регулирования от выделенного предела, скорость передачи битов получают посредством умножения запаса регулирования на постоянную величину обновления и полученная таким образом скорость передачи битов распределяется на соответствующие N изображений. В этом случае величина обновления определяется на основании того факта, что сумма скоростей передачи битов, распределенных на последующие N изображений, равна ошибке скорости передачи битов.

[0057] То есть данное устройство управления скоростью передачи битов видео получает разность между выделенной скоростью передачи битов и фактически сформированной скоростью передачи битов закодированного изображения в качестве ошибки скорости передачи битов. На основании знака ошибки скорости передачи битов данное устройство управления скоростью передачи битов выбирает в качестве допустимого диапазона коррекции максимальное значение выделенной скорости передачи битов, полученной до момента начала кодирования, в том случае, когда ошибка скорости передачи битов указывает положительное значение, для того чтобы распределить ошибку скорости передачи битов подобно сложению ошибки скорости передачи битов с выделенной скоростью передачи битов для множества последующих изображений. С другой стороны, данное устройство управления скоростью передачи битов видео выбирает в качестве допустимого диапазона коррекции минимальное значение выделенной скорости передачи битов, полученной до начала кодирования, в том случае, когда ошибка скорости передачи битов указывает отрицательное значение, для того чтобы распределить ошибку скорости передачи битов подобно вычитанию ошибки скорости передачи битов из выделенных скоростей передачи битов для множества последующих изображений.

[0058] Отмечено, что в том случае, когда четвертое средство вычисления не предоставлено, то в том случае, когда значение скорости передачи битов ошибки указывает на положительное значение в момент, когда выбирается данный допустимый диапазон коррекции, для множества последующих изображений, максимальные значения выделенных скоростей передачи битов получают, например, посредством умножения исходных значений выделенных скоростей передачи битов на константу, и максимальные значения выбираются в качестве допустимых диапазонов коррекции. С другой стороны, в том случае, когда ошибка скорости передачи битов указывает отрицательное значение, для множества последующих изображений, минимальные значения выделенных скоростей передачи битов получают, например, посредством деления исходных значений выделенных скоростей передачи битов на константу, и минимальные значения выбираются в качестве допустимых диапазонов коррекции.

[0059] Затем для множества последующих изображений получают в качестве допустимых отклонений скоростей передачи битов разности между допустимыми диапазонами коррекции и выделенными скоростями передачи битов, а в качестве величины обновления получают отношение суммы полученных таким образом допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов.

[0060] Затем на основании допустимых отклонений скоростей передачи битов и величины обновления, для множества последующих изображений вычисляют отклонения скоростей передачи битов для выделенных скоростей передачи битов и на их основании корректируются выделенные скорости передачи битов для соответствующих изображений.

[0061] Например, в том случае, когда исходное значение выделенной скорости передачи битов для последующего изображения равно 50, предполагается, что исходное значение выделенной скорости передачи битов, умноженное на 2, установлено в качестве максимального значения выделенной скорости передачи битов, а исходное значение выделенной скорости передачи битов, деленное на 2, установлено в качестве минимального значения выделенной скорости передачи битов, максимальное значение выделенной скорости передачи битов 100, а минимальное значение выделенной скорости передачи битов 25.

[0062] В таком случае, когда текущее значение выделенной скорости передачи битов для изображения равно 70 и величина обновления равна 20%, в том случае, если ошибка скорости передачи битов положительна, допустимое отклонение скорости передачи битов равно 30 (=100-70) в большую сторону, а в том случае, если ошибка скорости передачи битов отрицательная, допустимое отклонение скорости передачи битов равно 45 (=70-25) в меньшую сторону. Вследствие этого, в том случае, если ошибка скорости передачи битов положительная, выделенная скорость передачи битов для изображения обновляется до «76(=70+30×0,2)», а в том случае, если ошибка скорости передачи битов отрицательная, выделенная скорость передачи битов для изображения обновляется до «61(=70-45×0,2)».

[0063] Здесь в том случае, когда допустимое отклонение скорости передачи битов для изображения j указывается как Tm[j], ошибка скорости передачи битов указывается как D, а величина обновления указывается как K, величина K обновления получается как отношение суммы ΣTm[j] допустимых отклонений скоростей передачи битов для последующих N изображений к ошибке D скорости передачи битов:

K=D/ΣTm[j]

На основании этой величины K обновления, отклонение скорости Td[j] передачи битов для изображения j получается как:

Td[j]=K×Tm[j]

Соответственно сумма отклонений Td[j] скоростей передачи битов для последующих N изображений выражается как:

ΣTd[j]=ΣK×Tm[j]=K×ΣTm[j]=(D/ΣTm[j])×ΣTm[j]=D

[0064] Как видно из этого, данное устройство управления скоростью передачи битов видео определяет величину K обновления на основании того факта, что сумма отклонений Td[j] скоростей передачи битов, распределенных на последующие N изображений, равна ошибке скорости передачи битов D.

[0065] Таким образом, данное устройство управления скоростью передачи битов получает ошибки скорости передачи битов на основании разности между выделенной скоростью передачи битов и фактически сформированной скоростью передачи битов закодированного изображения, и вместо того, чтобы уменьшать эту ошибку скорости передачи битов путем ее сложения с выделенной скоростью передачи битов следующего изображения, выравнивает ее посредством распределения ошибки скорости передачи битов на множество последующих кодируемых изображений в зависимости от потребности изображений.

[0066] В соответствии с этой конфигурацией, при реализации кодирования видео с целевой скоростью передачи битов, данное устройство управления скоростью передачи битов видео может снизить отклонение качества изображения между изображениями и может реализовать улучшение в субъективном качестве изображения.

[0067] В том случае, когда применяется данная конфигурация, если выделенные скорости передачи битов накапливаются (затягиваются) до выделенного предела, выделенные скорости передачи битов далее не накапливаются (затягиваются) и соответственно ошибка скорости передачи битов не может быть распределена полностью.

[0068] Соответственно, в данном устройстве управления скоростью передачи битов видео, разность формируется между ошибкой скорости передачи битов и суммой отклонений скоростей передачи битов, посредством ограничения величины обновления, чтобы он был в заданном диапазоне, и соответственно сформированная разность складывается как перенос скорости передачи битов остатка с ошибкой скорости передачи битов, полученной после кодирования следующего изображения.

[0069] То есть, как показано на Фиг.3, не участвующая в накоплении часть (не затянутую часть) распределяется в момент, когда обрабатывается следующее изображение.

[0070] Далее будет описан вариант осуществления настоящего изобретения на основании описанного выше основного принципа.

Фиг.4 иллюстрирует пример конфигурации устройства для устройства кодирования видео, которое предоставлено с устройством управления скоростью передачи битов видео, к которому применяется настоящее изобретение.

[0071] Как показано на Фиг.4, это устройство кодирования видео предоставлено с модулем 101 хранения выделенной скорости передачи битов, модулем 103 вычитания, модулем 104 хранения характеристик, модулем 105 вычисления шага квантования, модулем 106 вычитания, модулем 107 DCT, модулем 108 квантования, модулем 109 обратного квантования, модулем 110 IDCT, модулем 111 сложения, буфером 112 хранения декодированного изображения, модулем 113 формирования предсказанного изображения и модулем 114 кодирования с переменной длиной, которые имеют те же функции, что и у модулей, показанных на Фиг.14. Дополнительно к этим модулям, устройство кодирования видео предоставлено с модулем 200 вычисления выделенной скорости передачи битов, который выполняет процесс, который и отличает настоящий вариант осуществления. Устройство управления скоростью передачи битов видео сконфигурировано посредством включения модуля 200 вычисления выделенной скорости передачи битов и модуля 103 вычитания.

[0072] Фиг.5 показывает пример блок-схемы процесса, выполняемого модулем 200 вычисления выделенной скорости передачи битов, который и отличает настоящий вариант осуществления. Здесь настоящее изобретение применяется в части, очерченной пунктирной линией, в сравнении с блок-схемой традиционного способа, показанного на Фиг.12.

[0073] В тот момент, когда на этапе S101 инициируется процесс, устройство кодирования видео сначала в качестве процесса инициализации, ошибке скорости передачи битов и номеру n изображения устанавливает исходные значения, равные 0.

[0074] Затем на этапе S102, в соответствии с предварительно заданной выделенной скоростью передачи битов кодируется nое изображение. Здесь предполагается, что исходные значения выделенной скорости передачи битов для каждого изображения являются заранее установленными на основании результатов первого кодирования.

[0075] Затем на этапе S103 определяют, были или нет закодированы все кадры (все изображения), и в том случае, когда были закодированы все кадры, процесс прекращается, а в том случае, когда были закодированы не все кадры, выполняется нижеследующий процесс.

[0076] То есть на этапе S104 вычисляют ошибку скорости передачи битов из разности между выделенной скоростью передачи битов и сформированной скоростью передачи битов для nого изображения и на последующем этапе S105, определяют, является ли знак вычисленной ошибки скорости передачи битов положительным или отрицательным.

[0077] В том случае, если, в соответствии с процессом определения на этапе S105, определено, что вычисленная на этапе S104 ошибка скорости передачи битов положительна, то поток обработки переходит к этапу S106, и из исходных значений выделенных скоростей передачи битов соответствующих изображений и константы вычисляют максимальные скорости передачи битов (описанное выше максимальное значение выделенной скорости передачи битов) для изображений с (n+1)ого по (n+N)ый (где N является заранее определенной константой больше 1).

[0078] Затем на этапе S107 из разности между максимальными скоростями передачи битов и выделенными скоростями передачи битов для этих соответствующих изображений вычисляют допустимые отклонения скорости передачи битов для изображений с (n+1)ого по (n+N)ый.

[0079] С другой стороны, в том случае, если, в соответствии с процессом определения на этапе S105, определено, что ошибка скорости передачи битов, вычисленная на этапе S104, является отрицательной, то поток обработки переходит к этапу S108 и из исходных выделенных скоростей передачи битов для соответствующих изображений и константы вычисляют минимальные скорости передачи битов (описанное выше минимальное значение выделенной скорости передачи битов) для изображений с (n+1)ого по (n+N)ый (где N является заранее определенной константой больше 1).

[0080] Затем на этапе S109 из разности между минимальными скоростями передачи битов и выделенными скоростями передачи битов для этих соответствующих изображений вычисляют допустимые отклонения скорости передачи битов для изображений с (n+1)ого по (n+N)ый.

[0081] Таким образом, после того как на этапах S107 и 109 были вычислены допустимые отклонения скорости передачи битов для изображений с (n+1)ого по (n+N)ый, затем на этапе S110 получают сумму вычисленных допустимых отклонений скоростей передачи битов, а из отношения суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов получают величину обновления.

[0082] Затем на этапе S111, для этих соответствующих изображений посредством умножения допустимых отклонений скоростей передачи битов на полученную величину обновления, получают отклонения скоростей передачи битов для изображений с (n+1)ого по (n+N)ый.

[0083] Затем на этапе S112, посредством сложения полученных отклонений скоростей передачи битов с выделенными скоростями передачи битов для соответствующих изображений корректируют выделенные скорости передачи битов для изображений с (n+1)ого по (n+N)ый. Отмечено, что исходные значения выделенных скоростей передачи битов для соответствующих изображений заранее установлены на основании результатов первого кодирования, но не обновлены.

[0084] Затем на этапе S113 объект обработки смещается на следующее изображение, поток обработки возвращается к процессу S102, и вышеописанные процессы выполняются повторно.

[0085] В соответствии с настоящим вариантом осуществления, посредством вышеописанных процессов, сформированная в закодированном изображении ошибка скорости передачи битов распределяется как на следующее изображение, так и на множество изображений, тем самым подавляя отклонение выделенной скорости передачи битов для следующего изображения.

[0086] Так как максимальные значения и минимальные значения выделенных скоростей передачи битов не фиксированы, но определены из предварительно заданных исходных значений выделенных скоростей передачи битов, а величина распределения определяется на их основе, то изменение шага квантования, вызванное коррекцией ошибки скорости передачи битов, может находиться в определенном диапазоне даже в том случае, когда отклонение значения выделенной скорости передачи битов между изображениями большое, подобно VBR.

[0087] Так как величину распределения получают посредством умножения общей величины обновления на допустимое отклонение скорости передачи битов для каждого изображения, шаги квантования для соответствующих изображений изменяются в той же степени, тем самым сохраняя малым изменение качества изображения между изображениями, вызванное настоящим процессом.

[0088] Здесь, в блок-схеме на Фиг.5, максимальные скорости передачи битов вычисляются на этапе S106, а минимальные скорости передачи битов вычисляются на этапе S108. Тем не менее, так как максимальные скорости передачи битов и минимальные скорости передачи битов вычисляются из исходных значений выделенных скоростей передачи битов для соответствующих изображений и константы, максимальные скорости передачи битов и минимальные скорости передачи битов могут вычисляться до этапа S101 начала процесса. Соответственно, максимальные скорости передачи битов и минимальные скорости передачи битов могут вычисляться до этапа S101 начала процесса, а на этапах S106 и 108 может быть выбран соответствующий один из вычисленных скоростей передачи битов. Посредством выполнения этого, становится ненужным несколько раз вычислять максимальные скорости передачи битов и минимальные скорости передачи битов, которые имеют одинаковые значения.

[0089] Фиг.6 иллюстрирует пример конфигурации устройства модуля 200 вычисления выделенной скорости передачи битов, который выполняет блок-схему Фиг.5.

[0090] Как показано на Фиг.6, модуль 200 вычисления выделенной скорости передачи битов, который выполняет процесс, который и отличает настоящее изобретение, предоставлен с модулем 2001 управления выделением, модулем 2002 вычисления допустимого диапазона коррекции, модулем 2003 памяти для хранения максимальной скорости передачи битов, модулем 2004 памяти для хранения минимальной скорости передачи битов, модулем 2005 памяти для хранения выделенной скорости передачи битов, модулем 2006 определения знака, модулем 2007 вычитания, модулем 2008 вычисления суммы, модулем 2009 вычисления отношения, модулем 2010 перемножения, модулем 2011 сложения, переключателем 2012 A, переключателем 2013 B и переключателем 2014 C.

[0091] Данный модуль 2001 управления выделением отправляет сигнал управления на считывание памяти трем модулям 2003, 2004 и 2005 памяти, для того чтобы управлять выходными данными соответствующих модулей 2003, 2004 и 2005 памяти и управлять состояниями Включено/Выключено переключателя 2013 B и переключением переключателя 2014 C.

[0092] Модуль 2002 вычисления допустимого диапазона коррекции вычисляет максимальные скорости передачи битов и минимальные скорости передачи битов для соответствующих изображений на основании исходных значений выделенных скоростей передачи битов для соответствующих изображений и выдает их модулю 2003 памяти для хранения максимальной скорости передачи битов и модулю 2004 памяти для хранения минимальной скорости передачи битов.

[0093] Модуль 2003 памяти для хранения максимальной скорости передачи битов сохраняет максимальные скорости передачи битов для соответствующих изображений, которые выдаются модулем 2002 вычисления допустимого диапазона коррекции. В момент получения сигнала управления на считывание памяти от модуля 2001 управления выделением, модуль 2003 памяти для хранения максимальной скорости передачи битов выдает переключателю 2012 A максимальную скорость передачи битов, которая соответствует назначенному номеру изображения.

[0094] Модуль 2004 памяти для хранения минимальной скорости передачи битов сохраняет минимальные скорости передачи битов для соответствующих изображений, которые выдаются модулем 2002 вычисления допустимого диапазона коррекции. В момент получения сигнала управления на считывание памяти от модуля 2001 управления выделением, модуль 2004 памяти для хранения минимальной скорости передачи битов выдает переключателю 2012 A максимальную скорость передачи битов, которая соответствует назначенному номеру изображения.

[0095] Модуль 2005 памяти для хранения выделенной скорости передачи битов сохраняет выделенные скорости передачи битов для соответствующих изображений, которые выдаются переключателем 2014 C и выдает выделенные скорости передачи битов, которые соответствуют назначенному номеру изображения модулю 2007 вычитания и модулю 2011 сложения в соответствии с сигналом управления на считывание памяти от модуля 2011 управления выделением.

[0096] Модуль 2006 определения знака определяет знак ошибки скорости передачи битов для изображения, который был закодирован, и выдает сигнал управления переключением в зависимости от результата определения, переключателю 2012 A для управления переключателем 2012 A, чтобы в свою очередь выбрать и выдать выходные данные максимальной скорости передачи битов модулем 2003 памяти для хранения максимальной скорости передачи битов в том случае, когда результат определения положительный, и для управления переключателем 2012 A, чтобы выбрать и выдать выходные данные минимальной скорости передачи битов модулем 2004 памяти для хранения минимальной скорости передачи битов в том случае, когда результат определения отрицательный.

[0097] Модуль 2007 вычитания вычисляет разность между максимальной скоростью передачи битов или минимальной скоростью передачи битов, которые выданы переключателем 2012 A, и выделенной скоростью передачи битов, которая выдана модулем 2005 памяти для хранения выделенной скорости передачи битов, для того чтобы вычислить допустимое отклонение скорости передачи битов для каждого изображения, и выдает его модулю 2008 вычисления суммы и модулю 2010 перемножения.

[0098] Модуль 2008 вычисления суммы вычисляет сумму допустимых отклонений скоростей передачи битов, которые выданы модулем 2007 вычитания, для того чтобы вычислить сумму допустимых отклонений скоростей передачи битов для соответствующих изображений и выдает ее модулю 2009 вычисления отношения.

[0099] Модуль 2009 вычисления отношения получает отношение суммы допустимых отклонений скоростей передачи битов, которая выдана модулем 2008 вычисления суммы, и ошибки скорости передачи битов для закодированного изображения, для того чтобы вычислить величину обновления и выдать его модулю 2010 перемножения.

[0100] Модуль 2010 перемножения умножает допустимое отклонение скорости передачи битов, которое выдано модулем 2007 вычитания, на величину обновления, которая выдана модулем 2009 вычисления отношения, для того чтобы вычислить отклонение скорости передачи битов для каждого изображения и выдать его модулю 2011 сложения.

[0101] Модуль 2011 сложения складывает выделенную скорость передачи битов, которая выдана модулем 2005 памяти для хранения выделенной скорости передачи битов, с отклонением скорости передачи битов, которое выдано модулем 2010 перемножения, для того чтобы получить скорректированное значения выделенной скорости передачи битов для каждого изображения, и выдает его переключателю 2013 B и переключателю 2014 C.

[0102] Переключатель 2012 A выбирает либо максимальную скорость передачи битов, которая выдана модулем 2003 памяти для хранения максимальной скорости передачи битов, либо минимальную скорость передачи битов, которая выдана модулем 2004 памяти для хранения минимальной скорости передачи битов, посредством выбора вывода a в том случае, когда выбирается максимальная скорость передачи битов, и посредством выбора вывода b в том случае, когда выбирается минимальная скорость передачи битов в соответствии с сигналом управления переключением от модуля 2006 определения знака, и выдает его модулю 2007 вычитания.

[0103] Переключатель 2013 B выдает скорректированное значение выделенной скорости передачи битов, которое выдается модулем 2011 сложения, модулю 105 вычисления шага квантования и модулю 103 вычитания, показанным на Фиг.4, в соответствии с сигналом управления переключением от модуля 2001 управления выделением.

[0104] Переключатель 2014 C выбирает либо исходное значение выделенной скорости передачи битов, либо скорректированное значение выделенной скорости передачи битов, посредством выбора вывода a в том случае, когда выбирается исходное значение выделенной скорости передачи битов, или вывода b в том случае, когда выбирается скорректированное значение выделенной скорости передачи битов, которая выдана модулем 2011 сложения, в соответствии с сигналом управления переключением от модуля 2001 управления выделением, и выдает его модулю 2005 памяти для хранения выделенной скорости передачи битов.

[0105] Далее, подробно будет описан процесс, который выполняется соответственно сконфигурированным модулем 200 вычисления выделенной скорости передачи битов.

[0106] В модуле вычисления выделенной скорости передачи битов в том случае, когда процесс инициирован, исходные значения выделенных скоростей передачи битов вводятся в модуль 2002 вычисления допустимого диапазона коррекции, который получает максимальные скорости передачи битов и минимальные скорости передачи битов для изображений с первого по Nый и отправляет их в модуль 2003 памяти для хранения максимальной скорости передачи битов и модуль 2004 хранения минимальной скорости передачи битов соответственно. Затем сигнал управления переключением отправляется модулем 2001 управления выделением переключателю 2014 C для того, чтобы переключить переключатель 2014 C на вывод a, таким образом, что исходные значения выделенных скоростей передачи битов для изображений с первого по Nый вводятся в модуль 2005 памяти для хранения выделенной скорости передачи битов.

[0107] С другой стороны, модуль 2006 определения знака определяет знак ошибки скорости передачи битов входного сигнала и отправляет сигнал управления переключением переключателю 2012 A, для того чтобы переключить переключатель 2012 A на вывод a в том случае, когда знак положительный и на вывод b в том случае, когда знак отрицательный. Впоследствии, модуль 2001 управления выделением отправляет сигнал управления на считывание памяти модулю 2003 памяти для хранения максимальной скорости передачи битов, модулю 2004 памяти для хранения минимальной скорости передачи битов и модулю 2005 памяти для хранения выделенной скорости передачи битов, таким образом, что соответствующие значения для изображений с первого по Nый хранящиеся в соответствующих модулях памяти выдаются.

[0108] Затем модуль 2007 вычитания получает в качестве допустимого отклонения скорости передачи битов разность между выходными данными, а модуль 2008 вычисления суммы вычисляет их сумму. Затем модуль 2009 вычисления отношения получает величину обновления из отношения полученной суммы допустимых отклонений скоростей передачи битов и ошибки скорости передачи битов.

[0109] После того как вычислена величина обновления, модуль 2001 управления выделением вновь отправляет сигнал управления на считывание памяти модулю 2003 памяти для хранения максимальной скорости передачи битов, модулю 2004 памяти для хранения минимальной скорости передачи битов и модулю 2005 памяти для хранения выделенной скорости передачи битов таким образом, что соответствующие значения для изображений с первого по Nый, хранящиеся в соответствующих модулях памяти, выдаются.

[0110] Затем модуль 2007 вычитания получает допустимое отклонение скорости передачи битов для каждого изображения как разность между соответствующими выходными значениями, а модуль 2010 перемножения вычисляет отклонение скорости передачи битов для каждого изображения посредством умножения допустимого отклонения скорости передачи битов на величину обновления, который был получен только что. Затем модуль 2011 сложения складывает полученное отклонение скорости передачи битов для каждого изображения с выделенной скоростью передачи битов для каждого изображения, для того чтобы вычислить обновленное значение выделенной скорости передачи битов для каждого изображения.

[0111] Затем переключатель 2014 C переключается на вывод b посредством сигнала управления переключением от модуля 2001 управления выделением и полученное скорректированное значение выделенной скорости передачи битов для каждого изображения выдается модулю 2005 хранения выделенной скорости передачи битов, тем самым обновляя выделенную скорость передачи битов для каждого изображения.

[0112] В итоге, переключатель 2013 B переводится в состояние Включено посредством сигнала управления переключением от модуля 2001 управления выделением и обновленная выделенная скорость передачи битов для следующего изображения выдается модулю 105 вычисления шага квантования и модулю 103 вычитания, показанным на Фиг.4.

[0113] Для процесса в отношении следующего изображения, когда переключатель 2014 C переключен на вывод a, только исходное значение выделенной скорости передачи битов для (N+1)ого изображения отправляется в модуль 2005 памяти для хранения выделенной скорости передачи битов, а выделенные скорости передачи битов для изображений со второго по Nый остаются неизменными.

[0114] Далее процесс, который отличает настоящий вариант изобретения и который указан на Фиг.5 пунктирной рамкой, будет описан с привязкой к структурной схеме на Фиг.6.

[0115] Предполагается, что nое изображение закодировано и для него была получена ошибка скорости передачи битов. В этом случае, предполагается, что переключатель 2014 C переключен на вывод a.

[0116] Модуль 2006 определения знака определяет знак ошибки скорости передачи битов и отправляет сигнал управления переключением переключателю 2012 A, для того чтобы переключить переключатель 2012 A на вывод a в том случае, когда ошибка скорости передачи битов положительная, и на вывод b в том случае, когда ошибка скорости передачи битов отрицательная.

[0117] В том случае, если ошибка скорости передачи битов положительная, модуль 2002 вычисления допустимого диапазона коррекции вычисляет максимальные скорости передачи битов для (n+1)ого и (n+N)ого изображений на основании исходных значений выделенных скоростей передачи битов и константы и сохраняет их в модуле 2003 памяти для хранения максимальной скорости передачи битов. Затем модуль 2007 вычитания вычисляет допустимые отклонения скорости передачи битов отклонения для (n+1)ого и (n+N)ого изображений. В этом процессе вычисления, максимальные скорости передачи битов для соответствующих изображений выдаются модулем 2003 памяти для хранения максимальной скорости передачи битов модулю 2007 вычитания по одному в соответствии с сигналом управления на считывание памяти от модуля 2001 управления выделением, и выделенных скоростей передачи битов для соответствующих изображений в это время по одному выдаются модулем 2005 памяти для хранения выделенной скорости передачи битов модулю 2007 вычитания, тем самым вычисляются допустимые отклонения скорости передачи битов.

[0118] С другой стороны, в том случае, если ошибка скорости передачи битов отрицательная, модуль 2002 вычисления допустимого диапазона коррекции вычисляет минимальные скорости передачи битов для (n+1)ого и (n+N)ого изображения на основании исходных значений выделенных скоростей передачи битов и константы и сохраняет их в модуле 2004 памяти для хранения минимальной скорости передачи битов. Затем модуль 2007 вычитания вычисляет допустимые отклонения скорости передачи битов для (n+1)ого и (n+N)ого изображения. В этом процессе вычисления, минимальные скорости передачи битов для соответствующих изображений выдаются модулем 2004 памяти для хранения минимального скорости передачи битов модулю 2007 вычитания по одному в соответствии с сигналом управления на считывание памяти от модуля 2001 управления выделением, и выделенные скорости передачи битов для соответствующих изображений в это время выдаются модулем 2005 памяти для хранения выделенной скорости передачи битов модулю 2007 вычитания по одному, тем самым вычисляются допустимые отклонения скорости передачи битов.

[0119] Затем вычисляется величина обновления из отношения суммы допустимых отклонений скоростей передачи битов к ошибке скорости передачи битов. Сумма допустимых отклонений скоростей передачи битов получается посредством модуля 2008 вычисления суммы, который суммирует выходные данные модуля 2007 вычитания. Модуль 2009 вычисления отношения получает величину обновления на основании этой суммы и ошибки скорости передачи битов.

[0120] Затем модуль 2010 перемножения получает отклонения скорости передачи битов для каждого изображения. То есть после того как вычислена величина обновления, от модуля 2001 управления выделением отправляется сигнал управления на считывания памяти модулю 2005 памяти для хранения выделенной скорости передачи битов, модулю 2003 памяти для хранения максимальной скорости передачи битов и модулю 2004 памяти для хранения минимальной скорости передачи битов, и модуль 2007 вычитания вычисляет допустимое отклонение скорости передачи битов, в соответствии с описанием выше. Затем модуль 2010 перемножения умножает это значение на величину обновления, для того чтобы получить отклонение скорости передачи битов для каждого из изображений с (n+1)ого по (n+N)ый.

[0121] С другой стороны, модуль 2011 сложения складывает это отклонение скорости передачи битов с выделенной скоростью передачи битов для каждого изображения из модуля 2005 памяти для хранения выделенной скорости передачи битов, для того чтобы получить обновленное значение выделенной скорости передачи битов для каждого изображения. Затем переключатель 2014 C переключается на вывод b посредством сигнала управления переключением от модуля 2001 управления выделением, и выделенная скорость передачи битов для каждого изображения, сохраненная в модуле 2005 памяти для хранения выделенной скорости передачи битов, обновляется на обновленную выделенную скорость передачи битов посредством перезаписи.

[0122] Процесс блок-схемы, показанной на Фиг.5, может быть реализован посредством конфигураций, показанных на Фиг.4 и 6, описанных выше.

Пример 1

[0123] Настоящее изобретение теперь будет описано подробно в соответствии с примером.

[0124] Пример, который будет описан ниже, предполагает, что максимальное значение и минимальное значение выделенной скорости передачи битов для каждого изображения получены соответственно как предварительно заданное значение выделенной скорости передачи битов для каждого изображения, умноженное на константу и предварительно заданное исходное значение выделенной скорости передачи битов для каждого изображения, деленное на константу соответственно. Дополнительно, предполагается, что предоставлена функция ограничения величины обновления, такая, чтобы быть меньше или быть равной максимальному значению (чтобы быть в заданном диапазоне). В соответствии с этим, предполагается, что предоставлена функция установки скорости передачи битов, которая не была распределена на каждое изображение из части ошибки скорости передачи битов, в качестве переноса скорости передачи битов (который может указывать отрицательное значение) и ее сложения с ошибкой скорости передачи битов следующего изображения.

[0125] Фиг.7 показывает пример блок-схемы, которую выполняет модуль 200 вычисления выделенной скорости передачи битов для того, чтобы реализовать настоящий пример.

[0126] В настоящем примере, когда процесс инициирован, на этапе S201 в качестве процесса инициализации, ошибка скорости D передачи битов, перенос скорости C передачи битов и номер n изображения вначале устанавливаются в исходное значение, равное 0.

[0127] Затем на этапе S202 в соответствии с предварительно заданной выделенной скоростью передачи битов кодируется nое изображение. Кодирование, выполняемое здесь, точно такое же, как кодирование, выполняемое на этапе S102 блок-схемы на Фиг.5.

[0128] Затем на этапе S203 определяют, были или нет закодированы все кадры (все изображения) и в том случае, когда были закодированы все кадры, процесс прекращается, а в том случае, когда были закодированы не все кадры, выполняется нижеследующие процессы.

[0129] То есть на этапе S204 как разность между выделенной скоростью передачи битов Tt и фактически сформированной скоростью передачи битов Tg для nого изображения вычисляют ошибку скорости передачи битов D.

D←t-Tg

[0130] Затем на этапе S205 перенос скорости C передачи битов складывается с ошибкой скорости D передачи битов для того, чтобы вычислить ошибку скорости D передачи битов, с которым складывается перенос скорости C передачи битов :

D←D+C

[0131] Затем на этапе 206 производится определение того, является или нет ошибка скорости D передачи битов большей или равной 0, и в том случае, если определено, что ошибка скорости D передачи битов больше или равна 0, поток обработки переходит к этапу S207 и выполняется процесс, показанный на блок-схеме Фиг. 8.

[0132] То есть, как показано на блок-схеме Фиг. 8, на этапе S301 сначала получают максимальные скорости передачи битов Tmax[j](n+1≤j≤n+N) посредством умножения предварительно заданных скоростей передачи битов Torg[j] на константу для изображений с (n+1)ого по (n+N)ый (где N является заранее заданной константой больше 1). В том случае, когда при перемножении с константой используется обозначение константы α, то получают Tmax[j]←Torg[j]×α. В частности, Torg[j] является исходным значением выделенной скорости передачи битов для jого изображения, которое установлено на основании результатов первого кодирования.

[0133] Затем на этапе S302 для изображений с (n+1)ого по (n+N)ый получают допустимые отклонения скорости передачи битов Tm[j] и их сумму Tm_sum. То есть допустимые отклонения скорости передачи битов Tm[j] вычисляются как:

Tm[j]←Tmax[j]-Tt[j]

на основании максимальных скоростей передачи битов Tmax[j] и выделенной скорости передачи битов Tt[j], а их сумма Tm_sum вычисляется как:

Tm_sum←ΣTm[j]

где Σ является суммой для n+1≤j≤n+N.

[0134] Затем на этапе S303 получают величину K обновления:

K←D/Tm_sum

из отношения ошибки скорости передачи битов D (≥0) к сумме Tm_sum (≥0) допустимых отклонений скоростей передачи битов.

[0135] Затем на этапе S304 полученная величина K коррекции ограничивается максимальным значением Kmax (предварительно заданным фиксированным значением). То есть

K←Max[K,Kmax]

получают на основании полученной величины K коррекции и заранее установленного максимального значения Kmax.

[0136] Затем на этапе S305, используя соответственно полученную величину K обновления, для изображений с (n+1)ого по (n+N)ый получают отклонения скоростей Td[j] передачи битов. То есть отклонения скоростей Td[j] передачи битов:

Td[j]←K×Tm[j]

вычисляют на основании величины K коррекции и допустимых скоростей передачи битов Tm[j].

[0137] Затем на этапе S306 полученные таким образом отклонения скоростей Td[j] передачи битов складывают с выделенными скоростями Tt[j] передачи битов для того, чтобы обновить выделенные Tt[j] скорости передачи битов для изображений с (n+1)ого по (n+N)ый и процесс блок-схемы на Фиг.7 завершается на этапе S207. То есть выделенные скорости Tt[j] передачи битов обновляют в соответствии со следующим выражением:

Tt[j]←Tt[j]+Td[j]

на основании отклонений скоростей Td[j] передачи битов и выделенных скоростей Tt[j] передачи битов и процесс блок-схемы на Фиг.7 завершается на этапе S207.

[0138] С другой стороны, в том случае, если на этапе S206 блок-схемы на Фиг.7 определено, что ошибка скорости D передачи битов не больше или равна 0, поток обработки переходит к этапу S208 и выполняется процесс, показанный на блок-схеме Фиг.9

[0139] То есть, как показано на блок-схеме Фиг.9, на этапе S401 сначала получают минимальные скорости передачи битов Tmin[j](n+1≤j≤n+N) посредством деления предварительно заданных скоростей передачи битов Torg[j] на константу для изображений с (n+1)ого по (n+N)ый (где N является заранее заданной константой больше 1). То есть в том случае, когда при делении на константу используется обозначение константы α, то получают Tmax[j]←Torg[j]/α. В частности, Torg[j] является исходным значением выделенной скорости передачи битов для jого изображения, которое установлено на основании результатов первого кодирования. Отмечено, что константа, используемая при делении на константу, предпочтительно имеет то же самое значение (α), что и описанная выше константа, которая используется при умножении на константу, но эти две константы не обязательно должны быть одинаковыми.

[0140] Затем на этапе S402 для изображений с (n+1)ого по (n+N)ый получают допустимые отклонения скорости Tm[j] передачи битов и их сумму Tm_sum. То есть допустимые отклонения скорости передачи битов Tm[j] вычисляются как:

Tm[j]←Tmin[j]-Tt[j]

на основании минимальных скоростей Tmin[j] передачи битов и выделенных скоростей Tt[j] передачи битов, а их сумма Tm_sum вычисляется как:

Tm_sum←ΣTm[j]

где Σ является суммой для n+1≤j≤n+N.

[0141] Затем на этапе S403 получают величину K обновления:

K←D/Tm_sum

из отношения ошибки скорости D передачи битов (<0) к сумме Tm_sum (<0) допустимых отклонений скоростей передачи битов.

[0142] Затем на этапе S404 полученная величина K обновления ограничивается максимальным значением Kmax (предварительно заданным фиксированным значением). То есть

K←Max[K,Kmax]

получают на основании полученной величины K коррекции и заранее установленного максимального значения Kmax.

[0143] Затем на этапе S405, используя соответственно полученную величину K обновления, для изображений с (n+1)ого по (n+N)ый получают отклонения скоростей Td[j] передачи битов. То есть отклонения скоростей Td[j] передачи битов отклонения:

Td[j]←K×Tm[j]

вычисляют на основании величины K обновления и допустимых скоростей передачи битов Tm[j] отклонения.

[0144] Затем на этапе S406 полученные таким образом отклонения скоростей Td[j] передачи битов складывают с выделенными скоростями Tt[j] передачи битов для того, чтобы обновить выделенные скорости Tt[j] передачи битов для изображений с (n+1)ого по (n+N)ый и процесс блок-схемы на Фиг.7 завершается на этапе S208. То есть в соответствии со следующим выражением:

Tt[j]←Tt[j]+Td[j]

выделенные Tt[j] скорости передачи битов обновлены на основании отклонений скоростей Td[j] передачи битов и выделенных скоростей Tt[j] передачи битов и процесс блок-схемы на Фиг.7 завершается на этапе S208.

[0145] На блок-схеме Фиг.7, когда на этапах S207 и S208 процессы завершаются, затем на этапе S209 получают сумму Td_sum отклонений скоростей Td[j] передачи битов. То есть вычисляется Td_sum←ΣTd[j], где Σ является суммой для n+1≤j≤n+N.

[0146] Затем на этапе S210 вычисляют перенос скорости C передачи битов из разности между ошибкой скорости D передачи битов и вычисленной суммой отклонений скоростей Td_sum передачи битов:

C←D-Td_sum

Как описано выше, на этапе S205, вычисленная таким образом перенос скорости C передачи битов, складывается с ошибкой скорости D передачи битов.

[0147] Затем на этапе S211 объект обработки перемещается на следующее изображение, поток обработки возвращается к процессу на этапе S202 и процесс для кодирования следующего изображения с выделенной скоростью Tt передачи битов выполняется повторно.

[0148] Основная конфигурация устройства кодирования видео для реализации процесса в соответствии с настоящим примером является точно такой же, как показанная на Фиг.4, но модуль 200 вычисления выделенной скорости передачи битов отличается от того, что показан на Фиг.6, и к конфигурации, показанной на Фиг.6, добавлена новая конфигурация.

[0149] Фиг.10 иллюстрирует пример конфигурации модуля 200 вычисления выделенной скорости передачи битов для реализации процесса в настоящем примере.

[0150] Как показано на Фиг.10, когда реализуется процесс в соответствии с настоящим примером, модуль 200 вычисления выделенной скорости передачи битов дополнительно обеспечен вторым модулем 2015 вычисления суммы, модулем 2016 вычитания, модулем 2017 хранения величины остатка и модулем 2018 сложения, дополнительно к соответствующим средствам с 2001 по 2008 и с 2010 по 2014 обработки, показанным на Фиг.6, а модуль 2009 вычисления отношения имеет функцию ограничения вычисленной величины обновления таким образом, чтобы она была меньше или равна максимальному значению.

[0151] Этот второй модуль 2015 вычисления суммы принимает отклонения скоростей Td[j] передачи битов, которые выдаются модулем 2010 перемножения, вычисляет сумму Td_sum отклонения скоростей передачи битов посредством вычисления их суммы и выдает ее модулю 2016 вычитания.

[0152] Модуль 2016 вычитания вычисляет разность между ошибкой скорости D передачи битов и суммой отклонений скоростей Td_sum передачи битов отклонения, которая выдана вторым модулем 2015 вычисления суммы, для того чтобы вычислить значение C скорости передачи битов остатка, и выдает его модулю 2017 хранения величины остатка.

[0153] Модуль 2017 хранения переноса величины хранит перенос скорости C передачи битов, которая выдана модулем 2016 вычитания, и выдает сохраненный перенос скорости C передачи битов модулю 2018 сложения, когда кодируется следующее изображение.

[0154] Когда кодируется следующее изображение, модуль 2018 сложения складывает перенос скорости C передачи битов, который выдан модулем 2017 хранения величины переноса, с ошибкой скорости D передачи битов, полученным посредством текущего кодирования, для того чтобы скорректировать ошибку скорости D передачи битов, и выдает его модулю 2006 определения знака, модулю 2009 вычисления отношения и модулю 2016 вычитания.

[0155] В соответствии с описанной выше конфигурацией на Фиг.10, могут быть реализованы процессы в блок-схемах настоящего примера, показанные на Фиг. с 7 по 9.

[0156] Далее будет описан эксперимент, направленный на проверку эффективности настоящего изобретения.

[0157] Этот эксперимент проводился посредством сравнениния традиционного способа с настоящим изобретением с использованием контрольного программного обеспечения JM 12.1 стандарта кодирования видео H.264. В качестве экспериментального изображения использована стандартная ITE (институт инженеров электросвязи) последовательность 07 изображения именуемая «European Market» (разрешением 1400×1080, продолжительностью 450 кадров от начала, с субтитрами). Более того, в качестве способа кодирования использовалась схема двухпроходного кодирования, при этом первое кодирование было выполнено с фиксированным шагом квантования, и в качестве целевой скорости передачи битов для второго кодирования было выбрано значение, составляющее половину скорости передачи битов каждого изображения. Параметр квантования (шаг квантования, представленный в логарифмической шкале) после первого кодирования составлял 24 для I изображения, 27 для P изображения и 30 для B изображения.