Результат интеллектуальной деятельности: ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ НАПРЯЖЕНИЯ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ОТРИЦАТЕЛЬНЫХ ВЫБРОСОВ ПРИ ПОДКЛЮЧЕНИИ ИНДУКТИВНОЙ НАГРУЗКИ

Вид РИД

Изобретение

Область техники

Изобретение относится к области микроэлектроники и, в частности, к сенсорным и микромощным микросхемам.

Уровень техники

В быстродействующих цифровых и аналоговых микросхемах паразитная инжекция электронов в подложку не оказывает существенного влияния на параметры изделий. В микросхемах, включающих датчики физических величин, микромощные аналоговые блоки и цифровые блоки обработки сигналов, паразитная инжекция электронов в подложку может катастрофически искажать обрабатываемую информацию. Экспериментально наблюдалась инжекция электронов в подложку микросхемы матричного фотоприемника [1] ([1] Gergel V.A., Vanyushin I.V. CMOS Color Image Sensor. Current State and Aspects. Proceedings of The International Conference "Micro- and nanoelectronics - 2009" (ICMNE-2009)). Электроны инжектировались в подложку при переключении выходного формирователя цифровых сигналов. На полученном с фотоприемника изображении наблюдалось светлое пятно диаметром около 1 мм в масштабе кристалла микросхемы. Выходной транзистор формирователя цифровых сигналов находился в центре этого пятна. При этом отрицательные выбросы выходного сигнала появлялись только за счет индуктивности проводников на печатной плате фотоприемного блока. Таким образом, задача подавления инжекции электронов в подложку микросхем, предназначенных для регистрации и обработки слабых электрических сигналов, имеет принципиальное значение.

Известные технические решения основаны на включении в состав микросхемы дополнительных элементов, переключающих ток отрицательных выбросов в шину питания, соединенную с подложкой. Эти решения позволяют уменьшить величину выбросов, но не могут исключить их полностью. Технические решения, снижающие скорость изменения выходного напряжения формирователя импульсов, значительно увеличивают энергопотребление. Подобные решения описаны в патентах: RU 215876 С2 (27.10.2000 г.), RU 2287219 С1 (10.11.2006 г.), RU 2397612 С1 (8.04.2010 г.), RU 2422984 С2 (10.11.2011 г.).

Однако в этих решениях не используется принцип прямого ограничения скорости изменения выходного тока, поскольку именно скорость изменения тока определяет величину выброса на индуктивности. Наиболее близким аналогом предлагаемого изобретения можно считать техническое решение, описанное в патенте RU 2287219 С1 (10.11.2006 г.).

Раскрытие изобретения

Задачей настоящего изобретения является стабилизация параметров микромощных и сенсорных микросхем за счет исключения влияния неосновных носителей (электронов), инжектированных в подложку при возникновении отрицательных выбросов на выходах микросхем, подключенных к индуктивной нагрузке. Технический результат, позволяющий достичь поставленной задачи, состоит в управляемом установлении скорости изменения выходного тока формирователя импульсов напряжения, что, в свою очередь, позволяет уменьшить отрицательные выбросы до безопасного уровня и исключить паразитную инжекцию электронов в подложку.

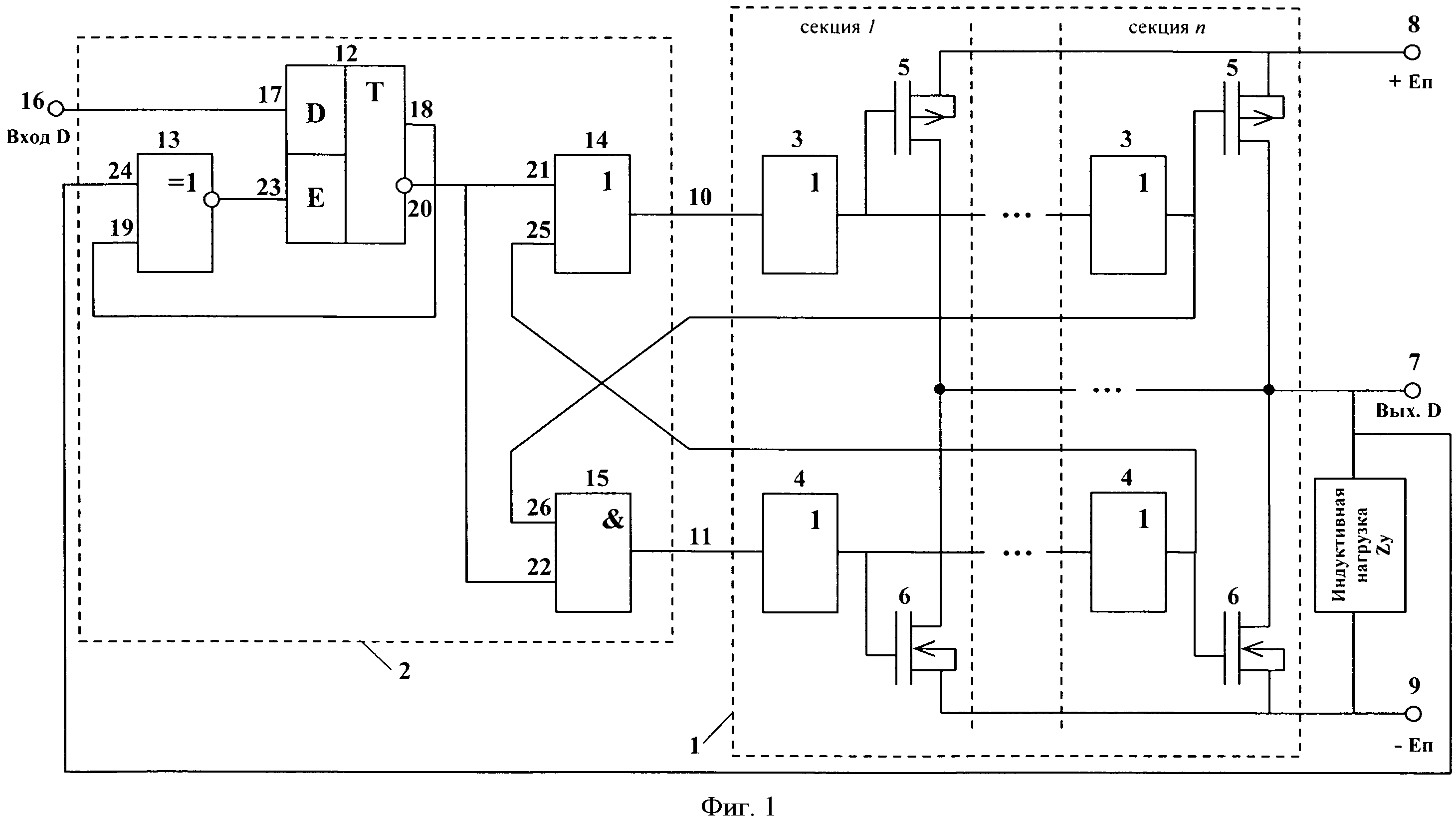

Согласно изобретению этот технический результат достигается за счет того, что в формирователе импульсов напряжения с устройством защиты от отрицательных выбросов при подключении индуктивной нагрузки (см. чертеж), включающем выходной каскад на комплементарных транзисторах (1) и логический блок управления выходными транзисторами (2), выходной каскад (2) реализован на основе КМОП-транзисторов и разделен на несколько секций, каждая из которых содержит первый (3) и второй элементы задержки сигнала (4), Р-МОП-транзистор (5) и N-МОП-транзистор (6), объединенные стоки которых подключены к выходу формирователя (7), истоки подключены к шинам положительного (8) и отрицательного питания (9), а затворы транзисторов (5) и (6) к выходам первого (3) и второго (4) элементов задержки сигнала соответственно; при объединении секций выходного каскада (1) первый выход (10) логического блока (2) подключается ко входу первого элемента задержки (3) в первой секции, а второй выход (11) ко входу второго элемента задержки (4) в первой секции, далее во второй и последующих секциях вход первого элемента задержки (3) соединяется с выходом первого элемента (3) в предыдущей секции, а вход второго элемента задержки (4) - с выходом второго элемента задержки (4) в предыдущей секции; логический блок управления (2) включает асинхронный D-триггер (12), логический элемент совпадения состояний (13), логические элементы «ИЛИ» (14), «И» (15), причем вход формирователя (16) соединен с информационным входом D-триггера (17), прямой выход (18) которого соединен с первым входом (19) элемента совпадения (13), инверсный выход (20) соединен с первыми входами (21) и (22) элементов «ИЛИ» (14), «И» (4), вход разрешения записи (23) - с выходом элемента совпадения (13), второй вход (24) которого соединен с выходом формирователя (7), второй вход (25) элемента «ИЛИ» (14) подключен к выходу второго элемента задержки (4) в последней секции выходного каскада, а второй вход (26) элемента «И» (15) подключен к выходу первого элемента задержки (3) в последней секции выходного каскада.

Краткое описание чертежей

На фигуре представлена схема формирователя импульсов напряжения с устройством защиты от отрицательных выбросов при подключении индуктивной нагрузки. Выделены логический блок и выходной каскад из n-секций.

Осуществление изобретения

Формирователь импульсов напряжения с устройством защиты от отрицательных выбросов при подключении индуктивной нагрузки (см. чертеж) включает выходной каскад на комплементарных транзисторах (1) и логический блок управления выходными транзисторами (2). Выходной каскад (2) реализован на основе КМОП-транзисторов и разделен на несколько секций, каждая из которых содержит первый (3) и второй элементы задержки сигнала (4), Р-МОП-транзистор (5) и N-МОП-транзистор (6), объединенные стоки которых подключены к выходу формирователя (7), истоки подключены к шинам положительного (8) и отрицательного питания (9), а затворы транзисторов (5) и (6) к выходам первого (3) и второго (4) элементов задержки сигнала соответственно; при объединении секций выходного каскада (1) первый выход (10) логического блока (2) подключается к входу первого элемента задержки (3) в первой секции, а второй выход (11) к входу второго элемента задержки (4) в первой секции, далее во второй и последующих секциях вход первого элемента задержки (3) соединяется с выходом первого элемента (3) в предыдущей секции, а вход второго элемента задержки (4) - с выходом второго элемента задержки (4) в предыдущей секции. Секционирование выходного каскада и последовательное переключение секций с установленной задержкой позволяет контролировать изменение скорости выходного тока формирователя импульсов напряжения. Элементы задержки сигнала (3) и (4) могут быть постоянными, если известна индуктивность нагрузки, или управляемыми, если индуктивность не известна.

Логический блок управления (2) включает асинхронный D-триггер (12), логический элемент совпадения состояний (13), логические элементы «ИЛИ» (14), «И» (15), причем вход формирователя (16) соединен с информационным входом D-триггера (17), прямой выход (18) которого соединен с первым входом (19) элемента совпадения (13), инверсный выход (20) соединен с первыми входами (21) и (22) элементов «ИЛИ» (14), «И» (4), вход разрешения записи (23) - с выходом элемента совпадения (13), второй вход (24) которого соединен с выходом формирователя (7), второй вход (25) элемента «ИЛИ» (14) подключен к выходу второго элемента задержки (4) в последней секции выходного каскада, а второй вход (26) элемента «И» (15) подключен к выходу первого элемента задержки (3) в последней секции выходного каскада. Логический блок обеспечивает отсутствие сквозных токов между источниками питания за счет того, что в любом состоянии закрыты либо все Р-МОП-транзисторы (6), либо все N-МОП-транзисторы (7) в выходном каскаде.

Технический результат достигается путем ограничения амплитуды отрицательных выбросов напряжения на выходе формирователя импульсов при установлении заданной скорости изменения выходного тока формирователя импульсов с использованием секционирования выходного каскада и линии задержки, последовательно переключающей секции. Скорость изменения выходного тока не должна превышать установленную величину dI/dt≤0,4B/Lнагр. Требуемая скорость изменения выходного тока достигается последовательным включением и отключением секций выходных транзисторов с заданным интервалом времени. Интервал времени между включениями (отключениями) секций определяется величиной задержки одной секции выходного транзисторного каскада.

Таким образом элементы задержки сигнала в каждой секции выходного каскада и величина максимального тока переключаемых транзисторов обеспечивает ограничение выбросов напряжения на индуктивной нагрузке величиной в 0,4 В и паразитной инжекции электронов в подложку практически не будет. Для индуктивности проводника 50 нГн или менее скорость изменения тока не превысит 0,8·107 А/с, что соответствует 8 мА/с. Для емкости нагрузки 10 пФ и логического перепада 3 В длительность фронта выходного сигнала не будет превышать 4 нс, что соответствует большинству реальных вариантов применения сенсорных и микромощных микросхем. Все элементы формирователя импульсов напряжения реализованы с использованием типовой промышленной КМОП-технологии. Результаты моделирования подтверждаются измерениями тестовых кристаллов.

Изобретение предназначено для улучшения характеристик сенсорных и микромощных микросхем и позволяет исключить влияние паразитной инжекции электронов в подложку на параметры КМОП-транзисторов.

Формирователь импульсов напряжения с устройством защиты от отрицательных выбросов при подключении индуктивной нагрузки, включающий выходной каскад на комплементарных транзисторах и логический блок управления выходными транзисторами, отличающийся тем, что выходной каскад реализован на основе КМОП-транзисторов и разделен на несколько секций, каждая из которых содержит первый и второй элементы задержки сигнала, р-МОП-транзистор и n-МОП-транзистор, объединенные стоки которых подключены к выходу формирователя, истоки подключены к шинам положительного и отрицательного питания, а затворы транзисторов к выходам первого и второго элементов задержки сигнала соответственно; при объединении секций выходного каскада первый выход логического блока подключается к входу первого элемента задержки в первой секции, а второй выход к входу второго элемента задержки в первой секции, далее во второй и последующих секциях вход первого элемента задержки соединяется с выходом первого элемента в предыдущей секции, а вход второго элемента задержки - с выходом второго элемента задержки в предыдущей секции; логический блок управления включает асинхронный D-триггер, логический элемент совпадения состояний, логические элементы ИЛИ, И, причем вход формирователя соединен с информационным входом D-триггера, прямой выход которого соединен с первым входом элемента совпадения, инверсный выход соединен с первыми входами элементов ИЛИ, И, вход разрешения записи - с выходом элемента совпадения, второй вход которого соединен с выходом формирователя, второй вход элемента ИЛИ подключен к выходу второго элемента задержки в последней секции выходного каскада, а второй вход элемента И подключен к выходу первого элемента задержки в последней секции выходного каскада.