ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ"

Вид РИД

Изобретение

Изобретение относится к логическим полупроводниковым К-МОП интегральным схемам.

Известны: Электрические схемы К-МОП логических элементов отрицания «НЕ» - инверторов, в частности:

- электрическая схема двоичного инвертора «НЕ» - [1], содержащая два n-МОП и p-МОП транзистора;

- электрические схемы троичных инверторов «НЕ», содержащие четыре и более МОП транзисторов [2, 3, 4].

Недостатки:

- электрическая схема двоичного инвертора «НЕ» [1] обеспечивает информационную емкость, равную только 1 биту информации (два логических состояния - лог «0» и лог «1»);

- электрические схемы известных троичных инверторов «НЕ» [2, 3, 4] обеспечивают большую информационную емкость 1,5 бита (три логических состояния - лог «0», лог «-1», лог «+1», однако, сложны, поскольку содержат относительно двоичной логики большее количество МОП транзисторов и их соединений.

Наиболее близкой по технической сущности является электрическая схема и конструкция интегральной схемы двоичного инвертора «НЕ» - [1], которые выбраны за прототип, содержащая входную и выходную шины, общую шину и шину питания, два n - МОП и p - МОП транзистора, затворы которых соединены между собой и подсоединены к входной шине, исток n-МОП транзистора подсоединен к обшей шине, исток p-МОП транзистора подсоединен к шине питания.

Подзатворная область n-МОП транзистора подсоединена к обшей шине питания, а подзатворная область р-МОП транзистора подсоединена к шине питания (подзатворные области могут иметь «плавающий» потенциал, см. чертеж 1, фиг.1а).

Конструкция интегральной схемы (см. фиг.1б) прототипа содержит полупроводниковую подложку, на поверхности которой расположены подзатворные области p и n типа проводимости, на поверхности подзатворной области p-типа расположены области стока и истока n-типа n-МОП транзистора, между которыми расположен подзатворный диэлектрик, на котором расположен затвор n-МОП транзистора, на поверхности подзатворной области n-типа расположены области стока и истока p-типа p-МОП транзистора, между которыми расположен подзатворный диэлектрик, на котором расположен затвор р-МОП транзистора, МОП транзисторы частично отделены толстым диэлектриком.

Затворы МОП транзисторов соединены с входной шиной. На поверхности стоков и истоков n-МОП и p-МОП транзисторов расположены соответствующие электроды стоков, причем электрод истока n-МОП транзистора подключен к общей шине, а причем электрод истока p-МОП транзистора подключен к шине питания.

Данная электрическая схема не позволяет более двух логических уровней сигнала (1 бита информации).

Техническим результатом изобретения является повышение информационной емкости логического элемента-инвертора.

Технический результат достигается за счет:

- введения в электрическую схему 2-х дополнительных конденсаторов, соединенных соответственно, первый со стоком n-МОП транзистора и выходной шиной, второй со стоком р-МОП транзистора и выходной шиной инвертора;

- расположения в конструкции интегральной схемы на поверхности стоков МОП транзисторов подзатворных диэлектриков, с расположенными на них затворами, соединенными с выходной шиной (см. чертеж 2, фиг.2 а, б).

Следует отметить, что в данной интегральной схеме функционально интегрируются области стоков и МОП конденсаторы схемы.

Изобретение поясняется приведенными чертежами.

Электрическая схема прототипа

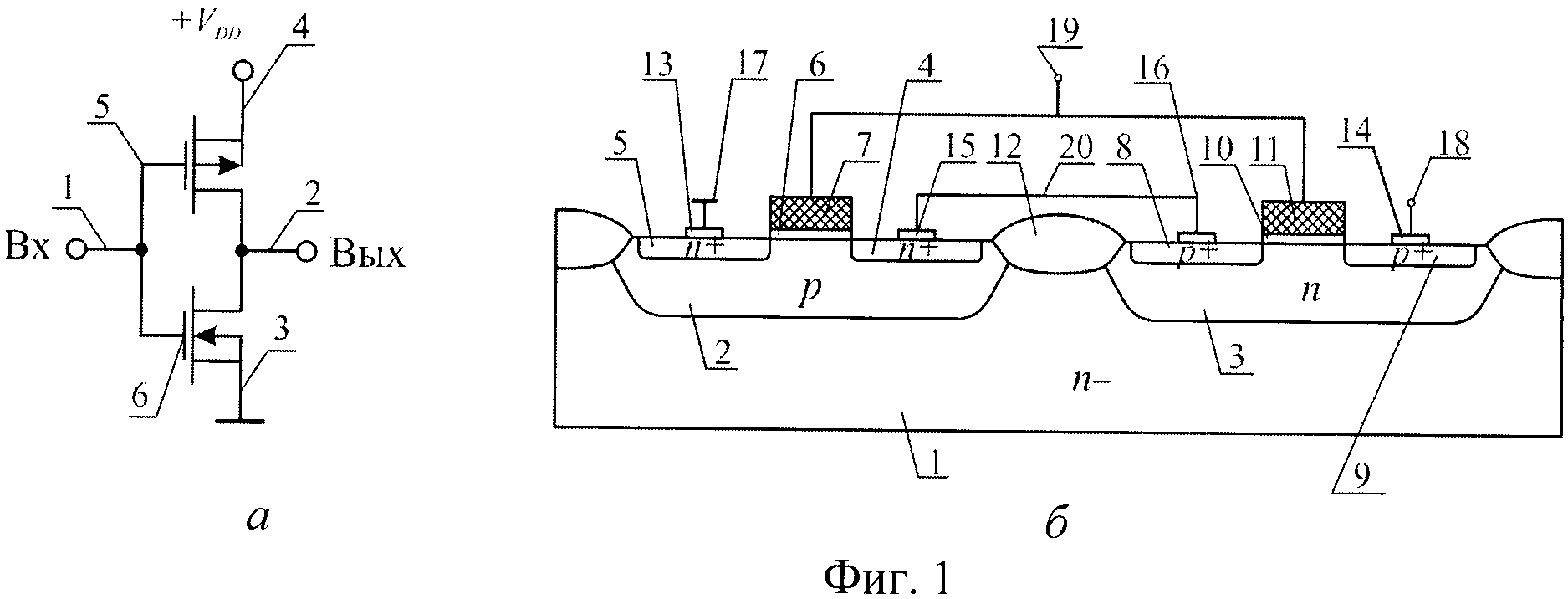

На фиг.1а приведена электрическая схема прототипа, содержащая входную - 1 и выходную - 2 шины, общую шину - 3 и шину питания - 4, два n-МОП - 5 и р-МОП - 6 транзистора, затворы которых соединены между собой и подсоединены к входной шине, исток p-МОП транзистора подсоединен к обшей шине, исток p-МОП транзистора подсоединен к шине питания. Подзатворная область n-МОП транзистора подсоединена к обшей шине питания, а подзатворная область p-МОП транзистора подсоединена к шине питания

Интегральная схема для прототипа

На чертеже 1, фиг.1б представлена интегральная схема прототипа, которая содержит полупроводниковую подложку-1, на поверхности которой расположены подзатворные области р - 2 и n - 3 типа проводимости, на поверхности подзатворной области р - 2 типа расположены области стока - 4 и истока - 5 n-типа n-МОП транзистора, между которыми расположен подзатворный диэлектрик - 6, на котором расположен затвор - 7 n-МОП транзистора. На поверхности подзатворной области n - 3 типа расположены области стока - 8 и истока р - 9 типа p-МОП транзистора, между которыми расположен подзатворный диэлектрик - 10, на котором расположен затвор - 11 p-МОП транзистора. МОП транзисторы частично отделены толстым диэлектриком - 12. Затворы - 7, 11 МОП транзисторов соединены с входной шиной - 19. На поверхности стоков и истоков n-МОП и p-МОП транзисторов расположены соответствующие электроды истоков - 13, 14 и стоков - 15, 16, соединенных с выходной шиной - 20, причем электрод истока - 13 n-МОП транзистора подключен к общей шине - 17, а причем электрод истока - 14 p-МОП транзистора подключен к шине питания - 18.

Электрическая схема изобретения

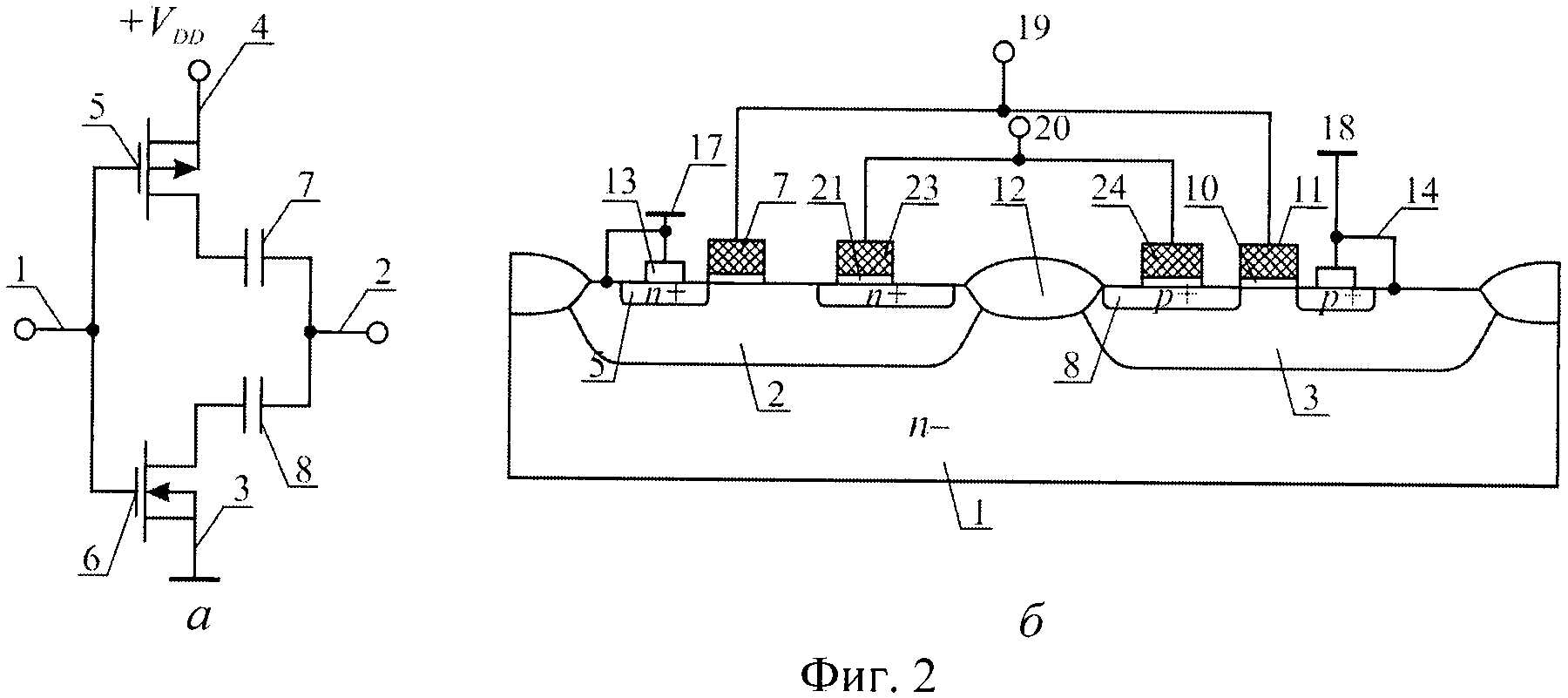

На чертеже 2, фиг.2а приведена электрическая схема изобретения, содержащая входную - 1 и выходную - 2 шины, общую шину - 3 и шину питания 4, два n-МОП - 5 и р-МОП - 6 транзистора, затворы которых соединены между собой и подсоединены к входной шине, исток n-МОП транзистора подсоединен к обшей шине, исток р-МОП транзистора подсоединен к шине питания. Подзатворная область n-МОП транзистора подсоединена к обшей шине питания, а подзатворная область р-МОП транзистора подсоединена к шине питания, при этом первый из двух дополнительных конденсаторов - 7 соединен соответственно со стоком n - МОП - транзистора - 5 и выходной шиной - 2, второй конденсатор - 8 со стоком р-МОП транзистора - 6 и выходной шиной - 2 инвертора.

Интегральная схема изобретения показана на чертеже 2, фиг.2б. Она содержит полупроводниковую подложку-1, на поверхности которой расположены подзатворные области р - 2 и n - 3 типа проводимости. На поверхности подзатворной области р - 2 типа расположены области стока - 4 и истока-5 n-типа n-МОП транзистора, между которыми расположен подзатворный диэлектрик - 6, на котором расположен затвор - 7n - МОП транзистора. На поверхности подзатворной области n - 3 типа расположены области стока - 8 и истока р - 9 типа р-МОП транзистора, между которыми расположен подзатворный диэлектрик - 10, на котором расположен затвор - 11 р - МОП транзистора. МОП транзисторы частично отделены толстым диэлектриком - 12. Затворы - 7, 11 МОП транзисторов соединены с входной шиной - 19. На поверхности истоков n-МОП и р-МОП транзисторов расположены соответствующие электроды истоков - 13, 14, причем электрод истока - 13 n-МОП транзистора подключен к общей шине -17, а причем электрод истока -14 р-МОП транзистора подключен к шине питания - 18. На поверхности стоков n-МОП и р-МОП транзисторов расположены подзатворные диэлектрики - 21, 22, на которых расположены затворы - 23, 24, соединенные с выходной шиной - 20.

Троичный К - МОП -С Логический элемент «НЕ» работает следующим образом.

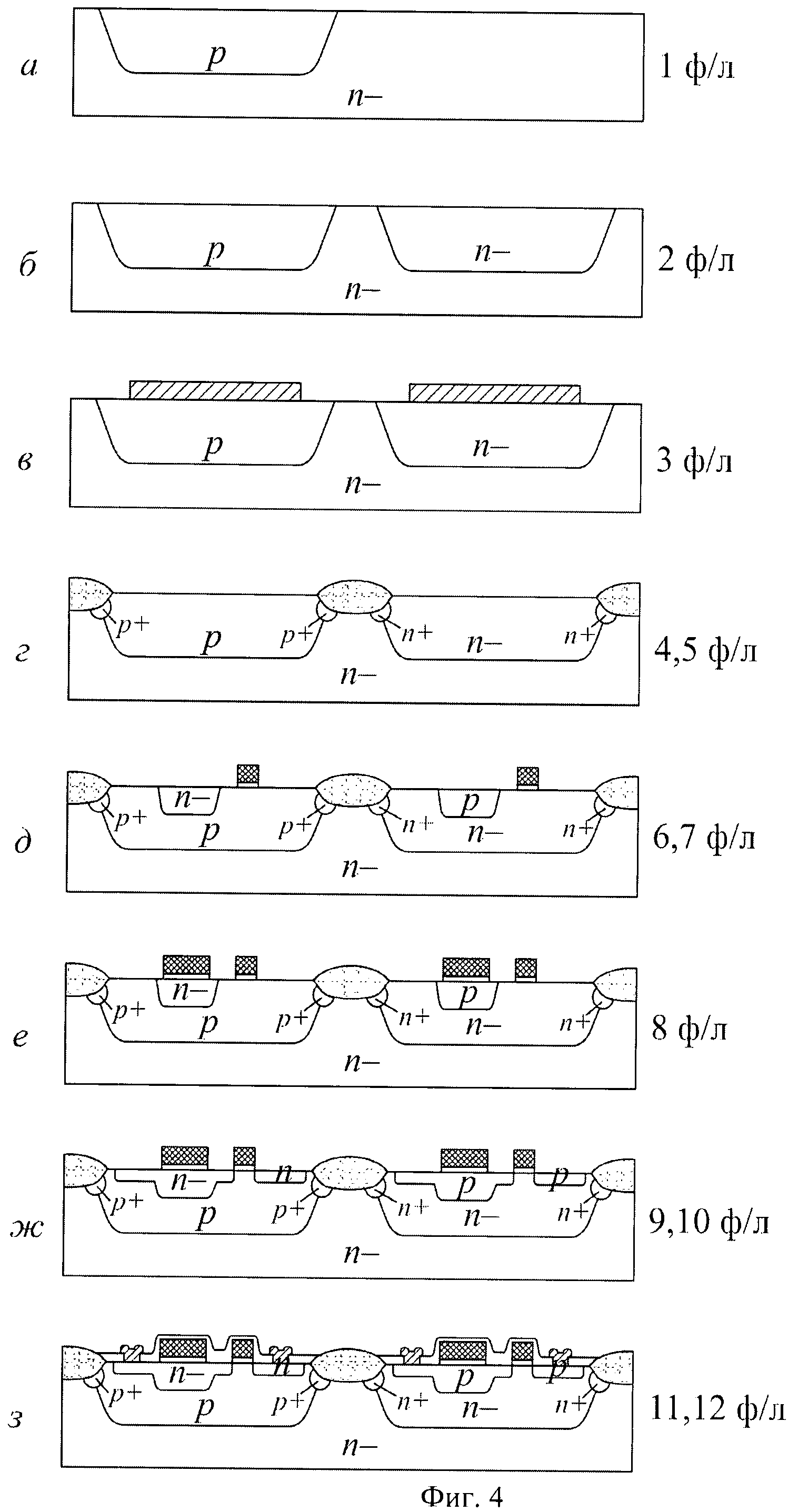

При подаче низкого (нулевого потенциала), соответствующего состоянию логической «лог - 1», n- МОП транзистор закрывается, а р-МОП транзистор открывается, при этом на его стоке появляется положительный потенциал (+Vdd) шины питания - 4, который через емкость конденсатора образуемого стоком р-МОП транзистора и выходной шиной (Сср.в), в поступает на вход следующего логического элемента, например, такого же «НЕ»-инвертора, см.рис 3 а, б.

При подаче высокого потенциала, соответствующего состоянию логической «лог+1», р-МОП транзистор закрывается, а n-МОП транзистор открывается, при этом на его стоке появляется низкий - нулевой потенциал общей шины, который через емкость конденсатора образуемого стоком n-МОП транзистора и выходной шиной (Сср), в поступает на вход следующего логического элемента.

Причем емкость каждого конденсатора Сс,n в Сср,в больше суммарной емкости р-n перехода сток - подзатворная область, соответственно Сз,п и Сз,п и нагрузочной емкости, образованной в данном случае суммарной (входной) емкостью затворов n- и р- МОП транзисторов логического элемента, стоящего в нагрузке (Сн).

Ccn,в>Сн+Сс,р

Сср,в>Сн+Сс,n

где Сн=Сз,п+Сз,р

Сн - емкость нагрузки логического элемента;

Ccn,в - емкость конденсатора образуемого стоком n-МОП транзистора и выходной шиной;

Сср,в - емкость конденсатора образуемого стоком p-МОП транзистора и выходной шиной;

Сс,n - емкость конденсатора образуемого стоком n-МОП транзистора и его подзатворной областью;

Сс,р - емкость конденсатора образуемого стоком p-МОП транзистора и его подзатворной областью;

Сз,n - емкость конденсатора, образованного затвором и подзатворной областью n-МОП транзистора;

Сз,р - емкость конденсатора, образованного затвором и подзатворной областью р-МОП транзистора.

При наличии на входе логического элемента состояния логического «лог 0», соответствующему потенциалу +Vdd/2, оба транзистора логического элемента будут открыты, поскольку пороговые напряжения (Vт,п, Vт.p) n-МОП и p-МОП транзисторов меньше по абсолютной величине +Vdd/2, т.е.(+Vdd / 2)>(Vт,п)

…(+Vdd/2)>(Vт,p)

и потенциал напряжения питания +Vdd поделится равными емкостями, соответственно пополам, т.е +Vdd/2, что соответствует состоянию «лог 0» на выходе логического элемента и таблице истинности 1.

|

Пример конкретной реализации.

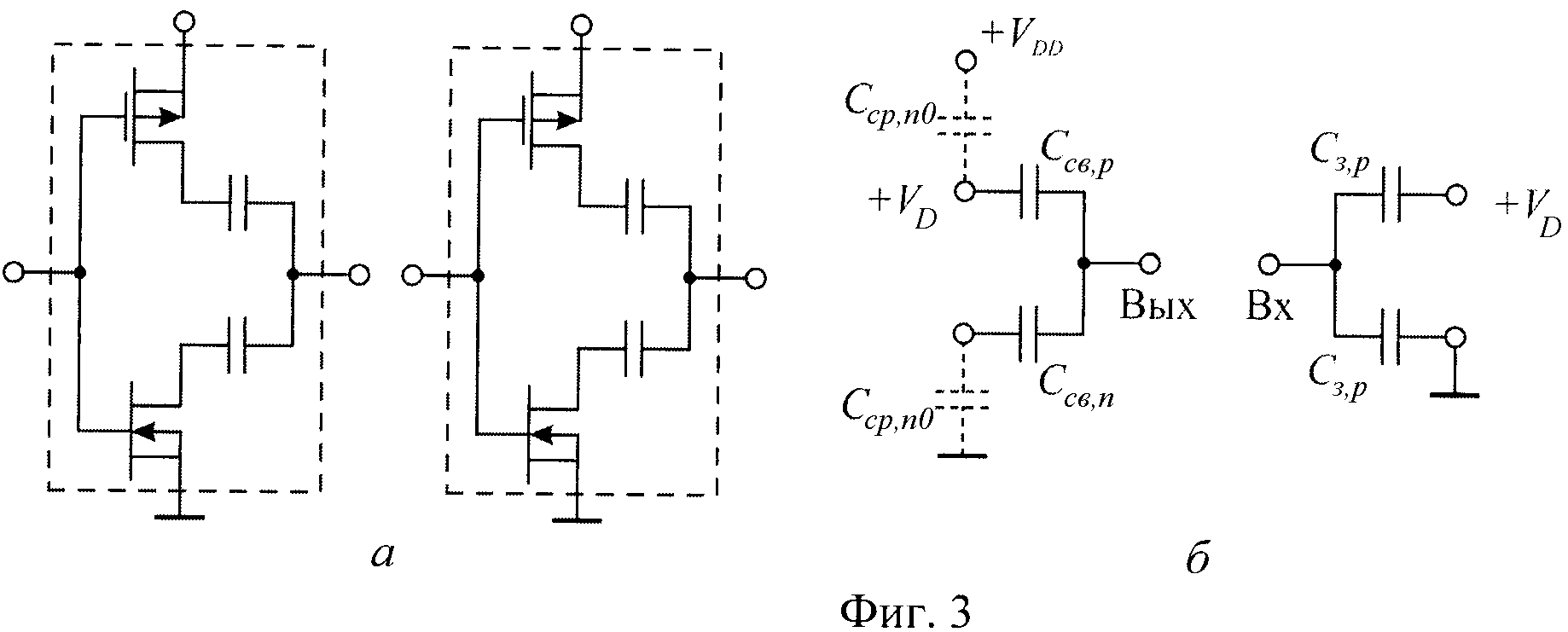

Логический элемент может быть выполнен по технологии, близкой к стандартной для К-МОП микросхем, (например, см. фиг.4), основанной на:

а) проведении 1-й фотолитографий и формировании ионным легированием бора в подложке - р - «кармана», т.е. подзатворной области p-типа, см. рис.4а;

б) проведении 2-й фотолитографий и формировании ионным легированием фосфора в подложке - р - кармана, т.е. подзатворной области n-типа, см. рис.4б;

в) формировании 3-й фотолитографией жесткой маски из нитрида кремния, см. рис.4в;

г) формировании 4-й и 5-й фотолитографией и ионным легированием р+ и n+ охранных областей;

- локальном окислении (формировании толстого диэлектрика) и удалении нитрида кремния, см. рис.4г;

д) формировании путем проведения 6 и 7 фотолитографий и ионного легирования фосфора и бора «первоначальных» n+ и р+ стоковых областей, см. рис.4д;

е) формировании затворных областей, т.е. окислении поверхности кремния, т.е создании тонкого, подзатворного оксида и осаждении поликристаллического слоя кремния на поверхность пластины и проведения операции 8-й фотолитографии - обтрава - разводки поликремния, см. рис.4е;

ж) проведении 9-й и - 10-й фотолитографии и последующая имплантация бора и фосфора, т.е. формировании «основных» областей стока истока n-типа и р-типа МОП транзисторов, см. рис.4ж;

з) формировании металлической разводки - соединения стоков - истоков - затворов МОП транзисторов, путем осаждения плазмохимического оксида, формирование 11-й фотолитографией контактных окон, осаждения алюминия и его образа с помощью 12-й литографии, см. рис.4з.

Примечание.

Формировать «первоначальные» n+ и р+ стоковые области можно ионным легированием примеси с высокой энергией ионов не до, а после формирования затворных областей.

Литература

1. Джонс М.Х. Электроника - практический курс. Москва: Постмаркет, 1999. - 528 с.(с.380), Practical Introduction to Electronic Circuits. By Martin Hartley Jones. Cambridge University Press, 40 West 20th Street, New York, N.Y. 10011-4211.. 522 pages.

2. А.Кушнеров. Троичная цифровая техника. Ретроспектива и современность (http://314159.ru/kushnerov/kushnerovl.pdf).

3. Попов Н.Д. Лукашенко В.А. «Логическое устройство отрицания». Патент RU №238.78.95 С2 от 01.11.2004, Заявка №2004.131.582.09.

4. Пат. 2005080257 Япония. Симосу дорайба кайро оёби симосу инба:та кайро (Схема КМОП-драйвера, а также схема КМОП-инвертора) / Хидэки Фукуда. Заявл. 04.09.2003, опубл. 24.03.2005.