Результат интеллектуальной деятельности: ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ

Вид РИД

Изобретение

Изобретение относится к наноэлектронике, более конкретно к энергонезависимым электрически программируемым постоянным запоминающим устройствам (ЭСППЗУ).

Известны однотранзисторные ячейки памяти для запоминающих устройств (ЗУ). Например: ячейка «Деннарда» [1] для динамической оперативной памяти (ДОЗУ), ячейка памяти "с плавающим затвором" FAMOS [2] для ЭСППЗУ, ячейка памяти на основе транзистора со структурой "кремний-оксид-нитрид-оксид-поликремний" (МНОП, КОНОП, SONOS) [3]. В этих ячейках подзатворная область (подложка) МОП-транзистора подсоединена к общей шине (земля), затвор к адресной шине, сток к разрядной шине, а исток к числовой шине.

В такой ячейке [1] сложно обеспечить энергонезависимость ЗУ и она имеет относительно большие размеры из-за необходимости иметь большую площадь информационной емкости. Ячейки [2, 3] не обеспечивают быстрое программирование ЭППЗУ из-за последовательного по времени способа их программирования.

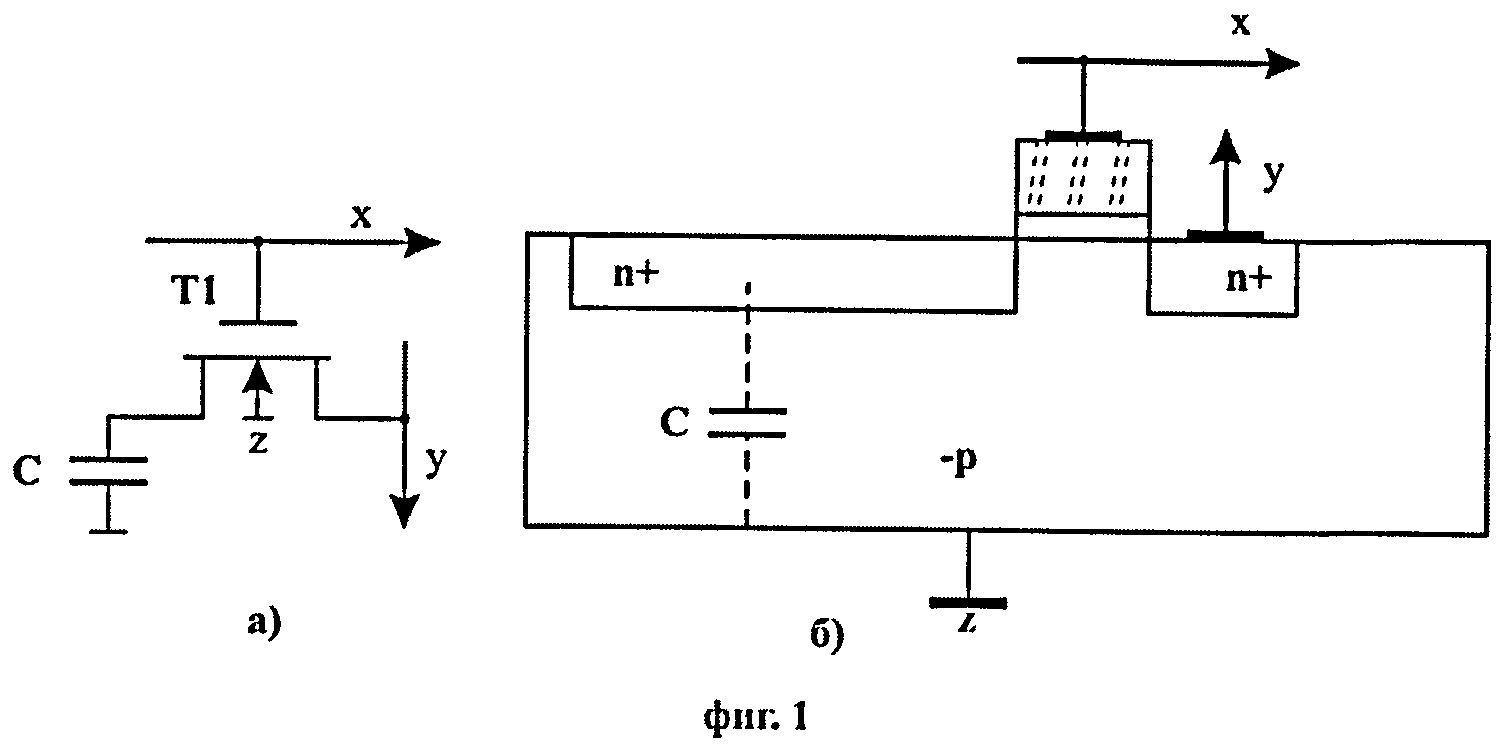

Наиболее близкой по технической сущности к изобретению является ячейка памяти «Деннарда» [1]. На фиг.1а и 1б показаны соответственно электрическая схема и конструкция ячейки памяти. Она содержит n(p)-МОП-транзистор, сток которого подсоединен с разрядной шиной, затвор с адресной шиной, подзатворная область с общей шиной, а исток с первым выводом конденсатора, второй вывод которого соединен с общей шиной.

При этом конструкция ячейки памяти является функционально-интегрированной структурой, у которой информационная емкость образована областью истока n(p)-типа, областью пространственного заряда p-n-переход исток-подложка и самой подложкой n(p)-типа МОП-транзистора, область затвора образует адресную шину, а на области стока n(p)-типа расположен электрод (контакт) разрядной шины.

Такая ячейка памяти не обладает предельно малыми размерами из-за необходимости размещать информационную емкость, которую желательно иметь большей величины. Вторым недостатком является сложность технологической реализации энергонезависимого элемента на ее основе /для него требуется изготовление и размещение дополнительного конденсатора из сегнетодиэлектрика/.

Целью изобретения является повышение быстродействия, надежности и интеграции ЭСППЗУ.

Поставленная цель достигается тем, что электрическая схема ячейки памяти содержит дополнительно первый и второй диоды и числовую шину, при этом катод (анод) первого диода соединен с числовой шиной и истоком n(p)-МОП-транзистора, его анод соединен с анодом второго диода, с подзатворной областью n(p)-МОП-транзистора и первым выводом конденсатора, второй вывод которого подсоединен к затвору n(p)-МОП-транзистора и к адресной шине, а катод второго диода соединен с областью стока n(p)-МОП-транзистора и разрядной шиной.

С целью упрощения электрической схемы затвор n(p)-МОП-транзистора соединен с катодом (анодом) первого диода.

Конструкция ячейки памяти (как и прототип) является единой функционально-интегрированной структурой, которая содержит n(p)-МОП-транзистор с «плавающей» подзатворной областью, при этом его n(p)-область истока является одновременно областью n(p)-типа катода (анода) первого диода, а p(n) подзатворная область является областью p(n)-типа анода (катода) первого диода; n(p)-область стока является областью n(p) катода (анода) второго диода, а p(n) подзатворная область образует область p(n)-типа анода (катода) второго диода; конденсатор соответственно образован затвором, диэлектриком и подзатворной областью МОП-транзистора.

Программирование ячейки памяти происходит в два этапа

- на первом этапе осуществляют запись оперативной информации (т.е. логической единицы "лог 1") путем подачи на адресную шину высокого (низкого) нулевого потенциала, а на разрядную шину низкого (высокого) потенциала (+V') и заряжают конденсатор через второй диод, при этом «плавающая» подзатворная область МОП-транзистора (являющаяся первой обкладкой конденсатора) приобретает отрицательный заряд и потенциал по отношению к затвору, который является второй обкладкой конденсатора.

Произведенная запись оперативной информации в виде заряда в конденсаторе может сохраняться (аналогично, как в ячейке памяти-прототипе) достаточно долго и время его хранения определяется токами утечки p-n-переходов сток-истока МОП-транзистора, при этом величина разности потенциалов в конденсаторе образованным затвором подзатворным диэлектриком и подзатворной областью Vc не превышает величину потенциалов (Vnp) в подзатворной системе МОП транзистора, необходимую для программирования ячейки памяти, т.е. Vnp<Vnp.

На втором этапе на затвор МОП-транзистора подается дополнительный (высокий) потенциал (Vд), причем такой, что сумма потенциалов Vc и Vд превышает напряжение программирования ячейки памяти, т.е.

Vc+Vд>Vnp,

при этом происходит запись постоянной (энергонезависимой) информации в ячейку памяти.

В случае «записи» логического нуля «лог 0» конденсатор не заряжается отрицательным потенциалом, и записи информации в ячейку памяти при подаче дополнительного Vд напряжения не происходит.

Преимущество заявленной ячейки памяти по сравнению с аналогами и прототипом очевидно из конструкций матриц ЭППЗУ, которые представлены на фиг.2 и 3, при этом интеграция памяти ЭППЗУ, как это видно из чертежей, достигает теоретического предела.

Быстродействие традиционного ЭППЗУ по сравнению с ДОЗУ достаточно медленное и определяется длительностью процесса последовательного по времени программирования ячеек памяти ЭППЗУ.

Предлагаемая ячейка памяти решает эту проблему за счет того, что вначале на первом этапе в ячейке памяти записывается оперативная информация в виде зарядов в емкостях затворов соответствующих МОП-транзисторов, как в ДОЗУ, относительно быстро.

На втором этапе подается кратковременно (1-2 миллисекунды) дополнительное напряжение (или проводят облучение ионизирующим излучением), в результате чего программируются все ячейки памяти ЭППЗУ одновременно. Таким образом, время программирования ЭППЗУ сокращается с десятков минут до нескольких миллисекунд.

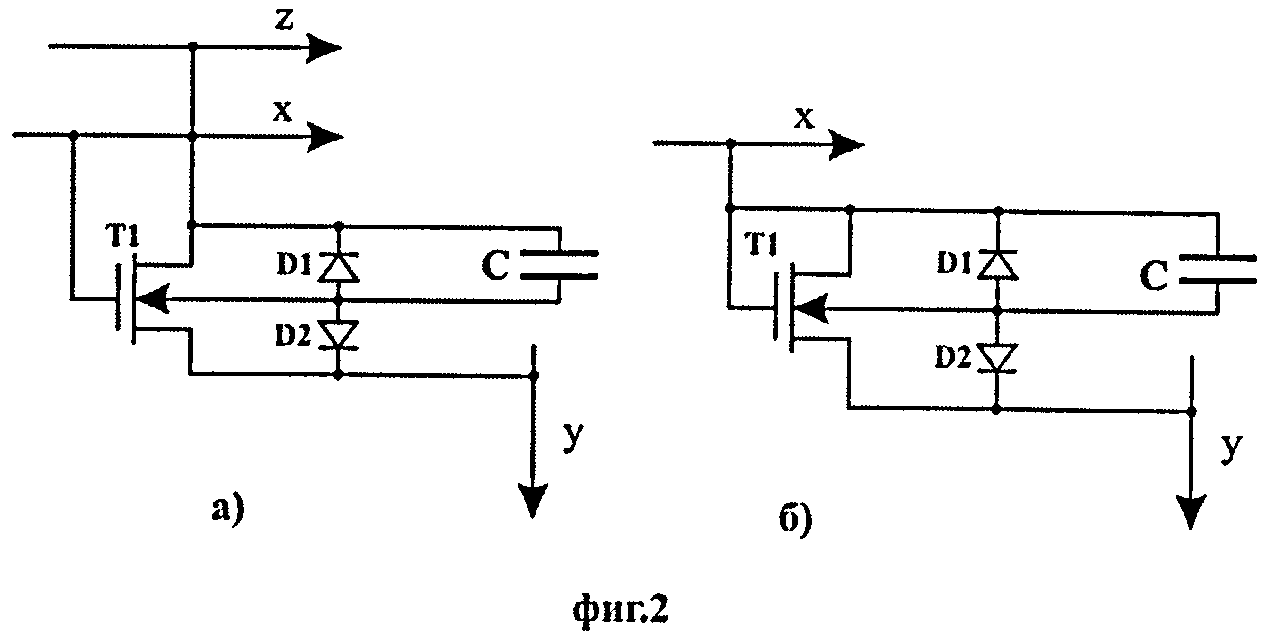

Электрическая схема ячейки памяти (см. фиг.2а)

Она содержит n(p)-МОП-транзистор Т1, исток которого соединен с катодом (анодом) первого диода D1, числовой шиной Z, анод (катод) первого диода соединен с анодом (катодом) второго диода D2 подзатворной областью МОП-транзистора Т1 и первым выводом конденсатора C, второй вывод которого соединен с затвором n(p)-МОП-транзистора Т1 и адресной шиной X, катод (анод) второго диода D2 соединен со стоком n(p)-МОП-транзистора и разрядной шиной Y.

С целью упрощения электрической схемы затвор МОП транзистора соединен с областью стока (см. фиг.2б).

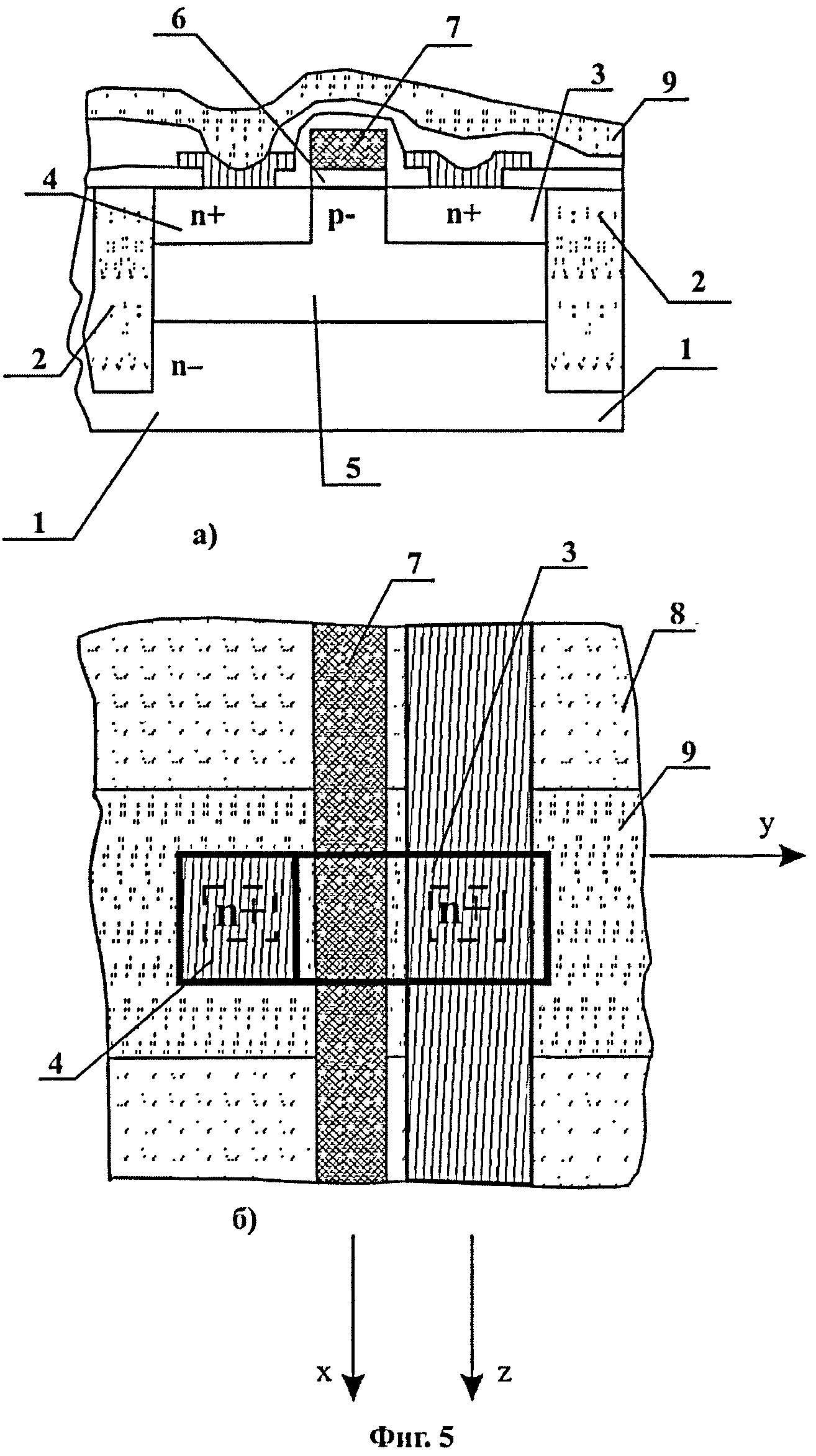

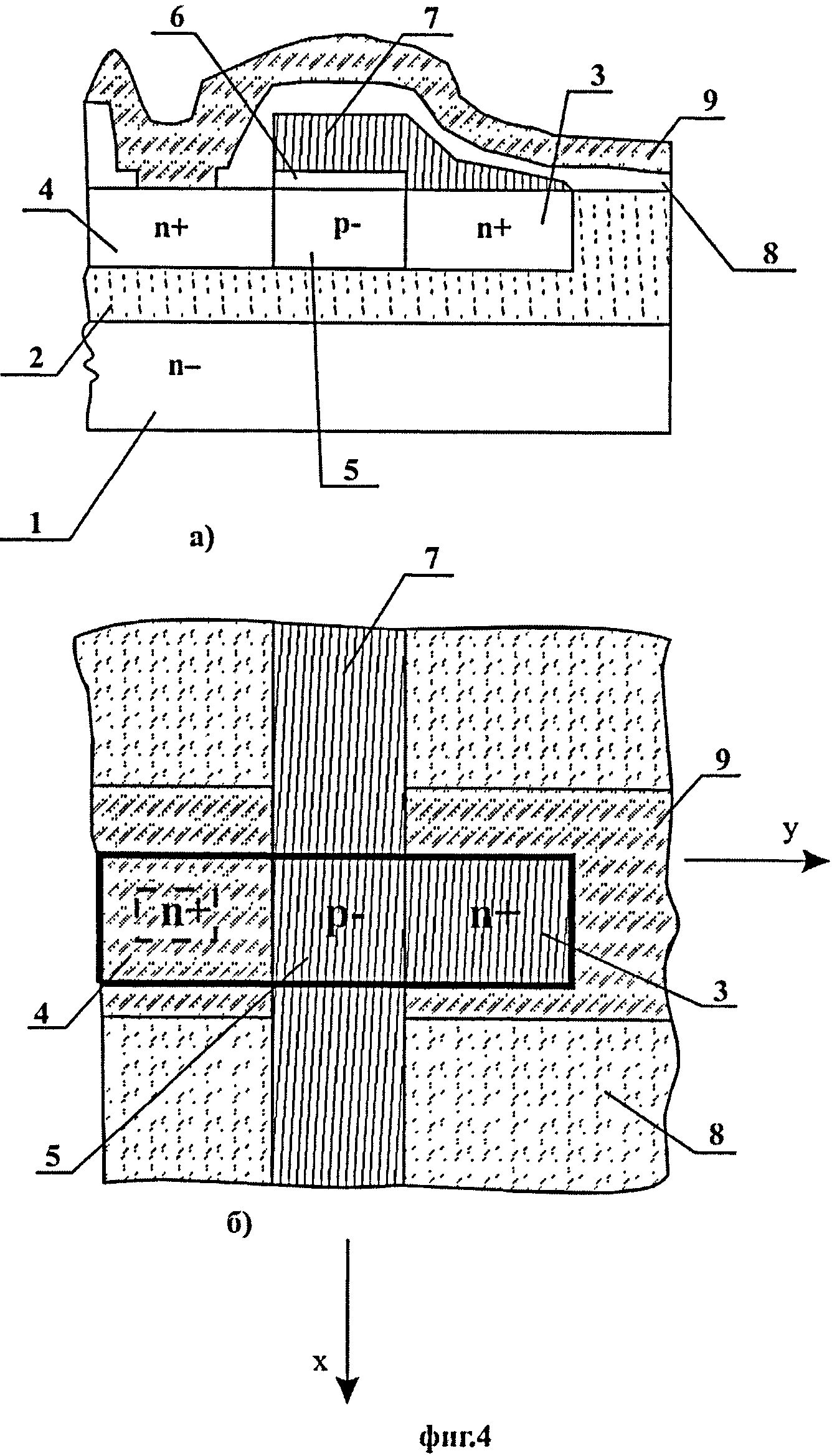

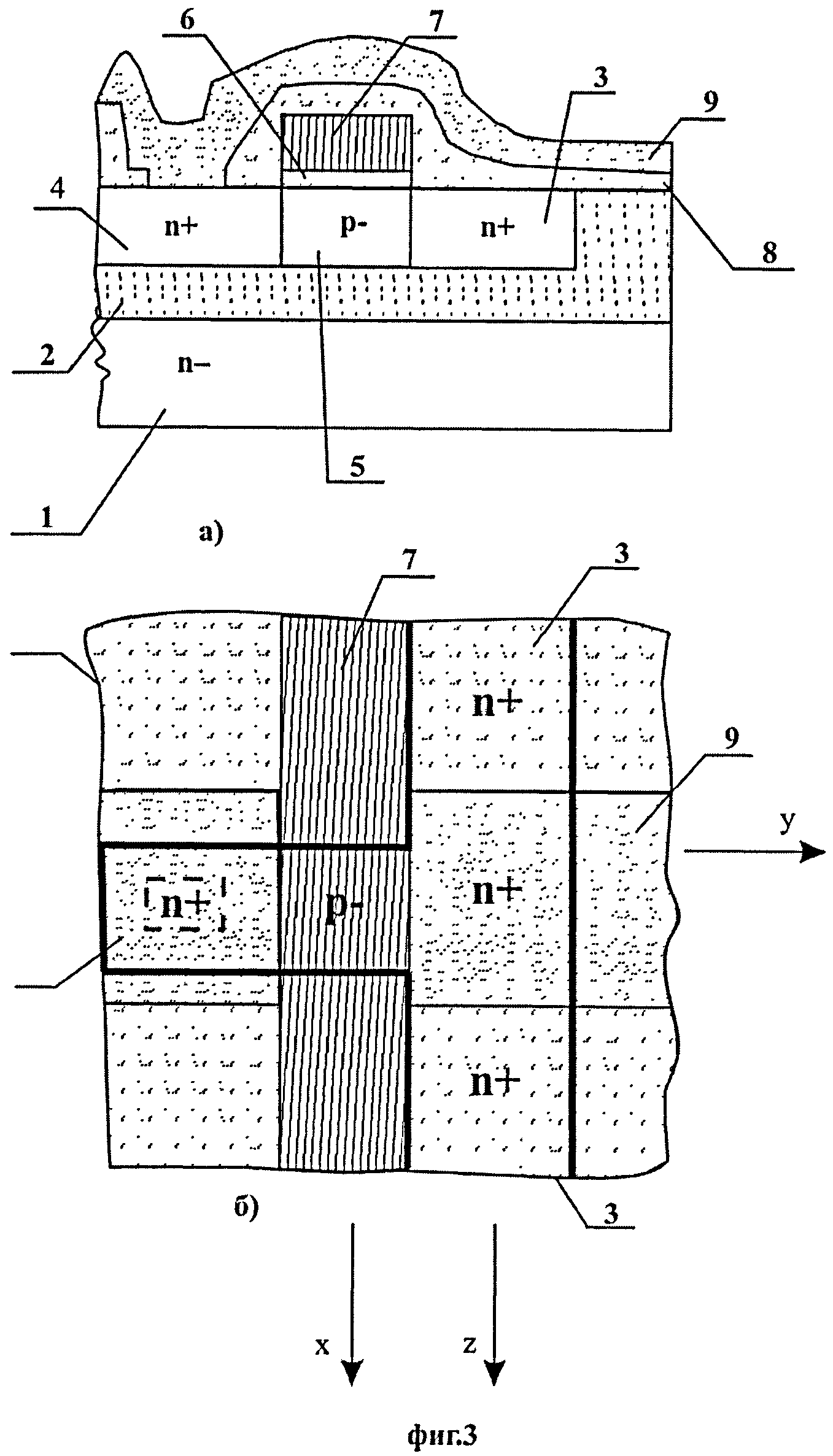

Конструкция и топология ячейки памяти (см. рис.3а, б)

Она состоит из подложки - 1, на поверхности которой расположен слой диэлектрика - 2, на поверхности которого расположена область стока - 3, образующая числовую шину, область истока - 4, образующая разрядную шину, подзатворная область - 5, на поверхности которой расположен подзатворный диэлектрик - 6, на поверхности которого расположен затвор - 7, образующий адресную шину, на поверхности областей стока, истока, затвора расположен изолирующий диэлектрик - 8, а на области истока - 4 расположен электрод разрядной шины - 9.

С целью упрощения конструкции ячейки памяти затвор 7 МОП транзистора образует электрический контакт с областью стока - 3 (см. фиг.4а, 4б).

Ячейка памяти работает следующим образом.

В решетке записи оперативной информации «лог 1» при поступлении положительного потенциала на адресную шину х, нулевого - на разрядную шину у происходит разрядка информационного конденсатора С через диод D2, при этом на «плавающей» подзатворной области МОП-транзистора формируется отрицательный потенциал (заряд) по отношению к затвору, который может хранится достаточно долго в режиме хранения оперативной информации, т.е. при нулевом потенциале на затворе (адресной шины X) и положительном потенциале на стоке разрядной шины Y. Время хранения информации заряда в конденсаторе определяется токами утечки диодов, т.е. сток-истоковых p-n-переходов МОП-транзистора, и обычно составляет сотни миллисекунд (как в обычном ДОЗУ на основе ячейки памяти «Деннарда», взятой за прототип).

Состояние «лог 0» соответствует отсутствию записи в ячейку памяти информационного заряда в конденсатор, как в обычном ДОЗУ.

Таким образом, во все ячейки ЭППЗУ записывается оперативная информация в виде «лог 1» и «лог 0». При этом время записи оперативной памяти также соответствует времени ее записи в обычное ДОЗУ, т.е. ~10-9 с на ячейку. После записи оперативной информации в ячейке памяти ее фактически переводят в постоянную путем одновременного программирования всех МОП-транзисторов, например, подачей дополнительного напряжения на все затворы транзисторов.

При этом важно, что физический принцип программирования МОП-транзистора ячейки памяти ЭСППЗУ не имеет существенного значения. В ячейке памяти может быть использован, в частности, МНОП-транзистор, FAMOS-транзистор с «плавающим» затвором, МОП-транзистор, программируемый ионами водорода [4] и т.д.

Примеры реализации

Быстродействующая ЭСППЗУ на основе предлагаемой ячейки памяти может быть реализована, например, на основе традиционной К-МОП технологии кремний на изоляторе (КНИ) см. фиг.3, 4 или на монокремнии см. фиг.5.

Источники информации

1. Matsue S, Vamamoto Н, Kobayski K, et al / A 256 Kbit dynamia RAM IEEE, J. 1980. V sc-. 15. №5, p.872-874.

2. Al Fazio, Mark Bauer "Intel Strata Flesh тм Memory Tecnology Dievopment end Impmentation / "Intel Tecnology Gournal Q 4, 1997 1-13.

3. M.L.French end M.H.White "Scaling of miltidielectric nonvolatile Sonos Memory Structurec" Solid-State Elec., vol, 37, p.1913, 1995.

4. K.Vanheusden, W.L: Warren, R.A.B Devine, D.M.Fleetwood, J.R.Schwank et.al. Non-volatile memory device based on mobile protons in SiO2 thin films Nature |Vol 386| 10 April 1997.