Результат интеллектуальной деятельности: СПОСОБ РЕГЕНЕРАЦИИ И ЗАЩИТЫ ОТ СБОЕВ ДИНАМИЧЕСКОЙ ПАМЯТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Вид РИД

Изобретение

Изобретение относится к области вычислительной техники, а именно к вычислительным системам на основе микропроцессоров с динамической памятью.

Известен способ коррекции ошибок в данных в динамической памяти, когда используют период обращения для операции чтения-модификации-записи, меньший или равный периоду регенерации динамической памяти в обычном режиме работы динамической памяти, а в режиме пониженного энергопотребления период много больше периода регенерации динамической памяти (Патент US №6838331, кл. H01L 21/00, опублик. 09.04.2002 г.).

Недостатком описанного способа является низкое быстродействие системы.

Наиболее близкими по технической сути и достигаемому результату являются способ регенерации и защиты от сбоев динамической памяти, включающий последовательное считывание данных, обнаружение ошибок в данных, содержащихся в памяти, модификацию данных путем коррекции найденных ошибок в данных по каждому адресу в памяти и чтение с периодом времени, не превышающим время регенерации памяти, и устройство для осуществления этого способа, включающее динамическую память, шину управления динамической памятью, шину адреса динамической памяти, шину данных динамической памяти, устройство контроля динамической памяти, связанное с устройством динамической памяти шиной управления динамической памятью, шиной адреса динамической памяти и шиной данных динамической памяти (Заявка US №2007/0022244, кл. G06F 13/28, опублик. 25.01.2007 г.).

Недостатками описанного выше способа и устройства являются низкое быстродействие системы вследствие необходимости сразу же записывать данные в случае их модификации (коррекция ошибок в данных при их обнаружении) из-за отсутствия возможности хранения модифицированных данных и возможности прослушивания адреса обращения к основной динамической памяти для отложенной записи модифицированных данных, а также низкая сбоеустойчивость вследствие отсутствия анализа найденных ошибок на устойчивость.

Технический результат от использования данного изобретения заключается в повышении быстродействия и сбоеустойчивости системы.

Указанный технический результат достигается тем, что в способе регенерации и защиты от сбоев динамической памяти, включающем последовательное считывание данных, обнаружение ошибок в данных, содержащихся в памяти, модификацию данных путем коррекции найденных ошибок в данных по каждому адресу в памяти и чтение с периодом времени, не превышающим время регенерации памяти, запись модифицированных данных производят по тому же адресу в памяти с низшим приоритетом, и во время ожидания записи производят прослушивание обращений по тому же адресу в памяти, а затем производят анализ ошибки на устойчивость, а также тем, что анализ ошибки на устойчивость производят путем повторного чтения модифицированных данных, и, в случае обнаружения в них ошибки, производят сравнение обнаруженной ошибки с предыдущей и запись данных о наличии и характере ошибки в регистр ошибок.

И тем, что анализ ошибки на устойчивость производят путем записи инвертированных данных относительно модифицированных, их чтения и записи в память модифицированных данных, причем, в случае обнаружения в инвертированных данных ошибки, производят сравнение обнаруженной ошибки с предыдущей и осуществляют запись данных о наличии и характере ошибки в регистр ошибок. При этом в устройстве для осуществления вышеописанного способа, включающем динамическую память, шину управления динамической памятью, шину адреса динамической памяти, шину данных динамической памяти, устройство контроля динамической памяти, связанное с устройством динамической памяти шиной управления динамической памятью, шиной адреса динамической памяти и шиной данных динамической памяти, дополнительно имеется буфер данных, схема прослушивания адреса, схема управления защитой от сбоев, регистр ошибок, шина управления буфером данных, шина модифицированных данных, шина управления устройством контроля, шина управления регистром ошибок и шина прослушивания адреса, причем буфер данных связан с устройством контроля динамической памяти шиной модифицированных данных и со схемой управления защитой от сбоев шиной управления буфером данных, схема управления защитой от сбоев связана с устройством контроля динамической памяти шиной управления устройством контроля, а регистр ошибок связан со схемой управления защитой от сбоев шиной управления регистром ошибок, при этом схема прослушивания адреса связана со схемой управления защитой от сбоев шиной прослушивания адреса и с устройством контроля динамической памяти шиной управления динамической памятью и шиной адреса динамической памяти.

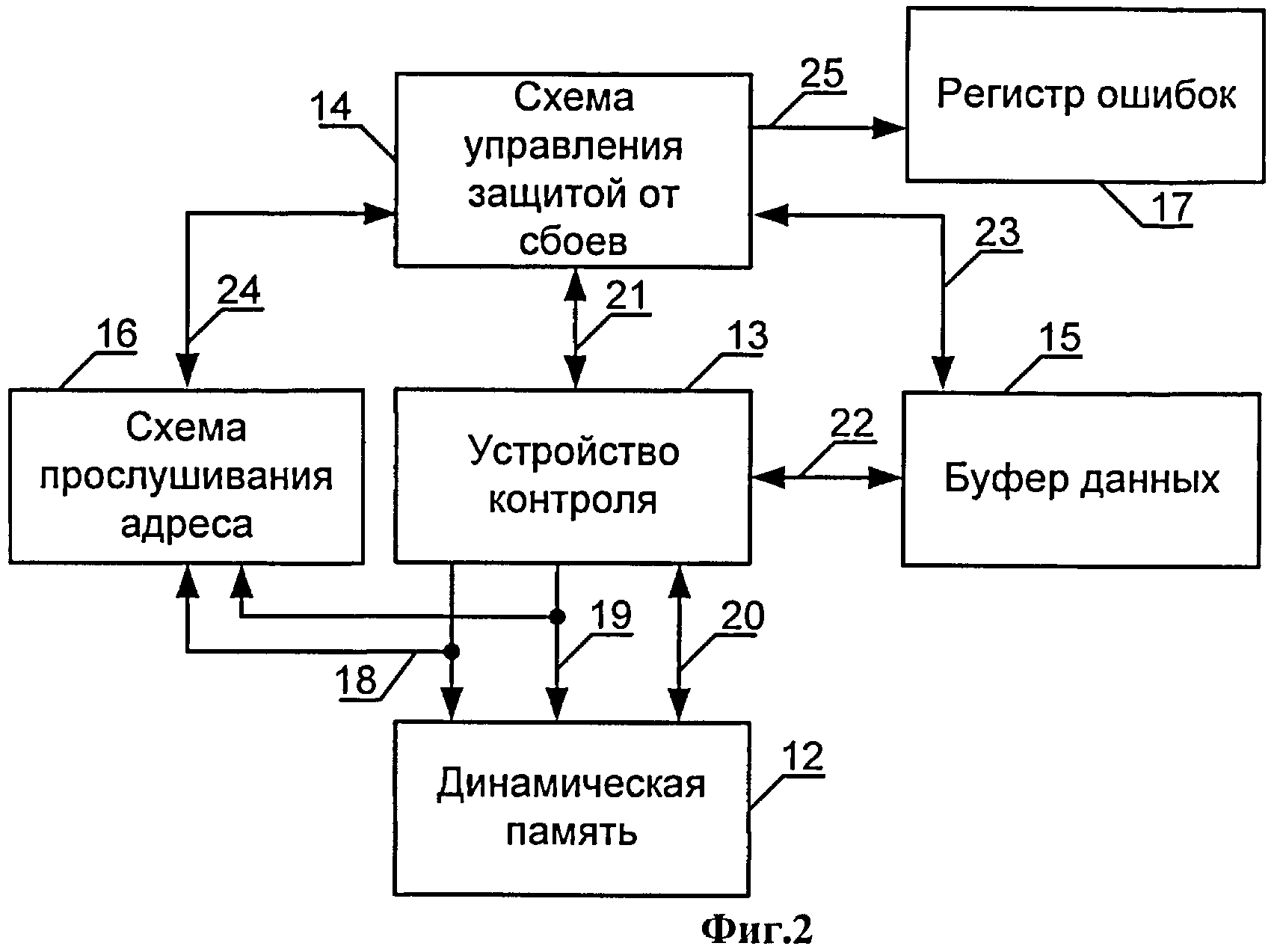

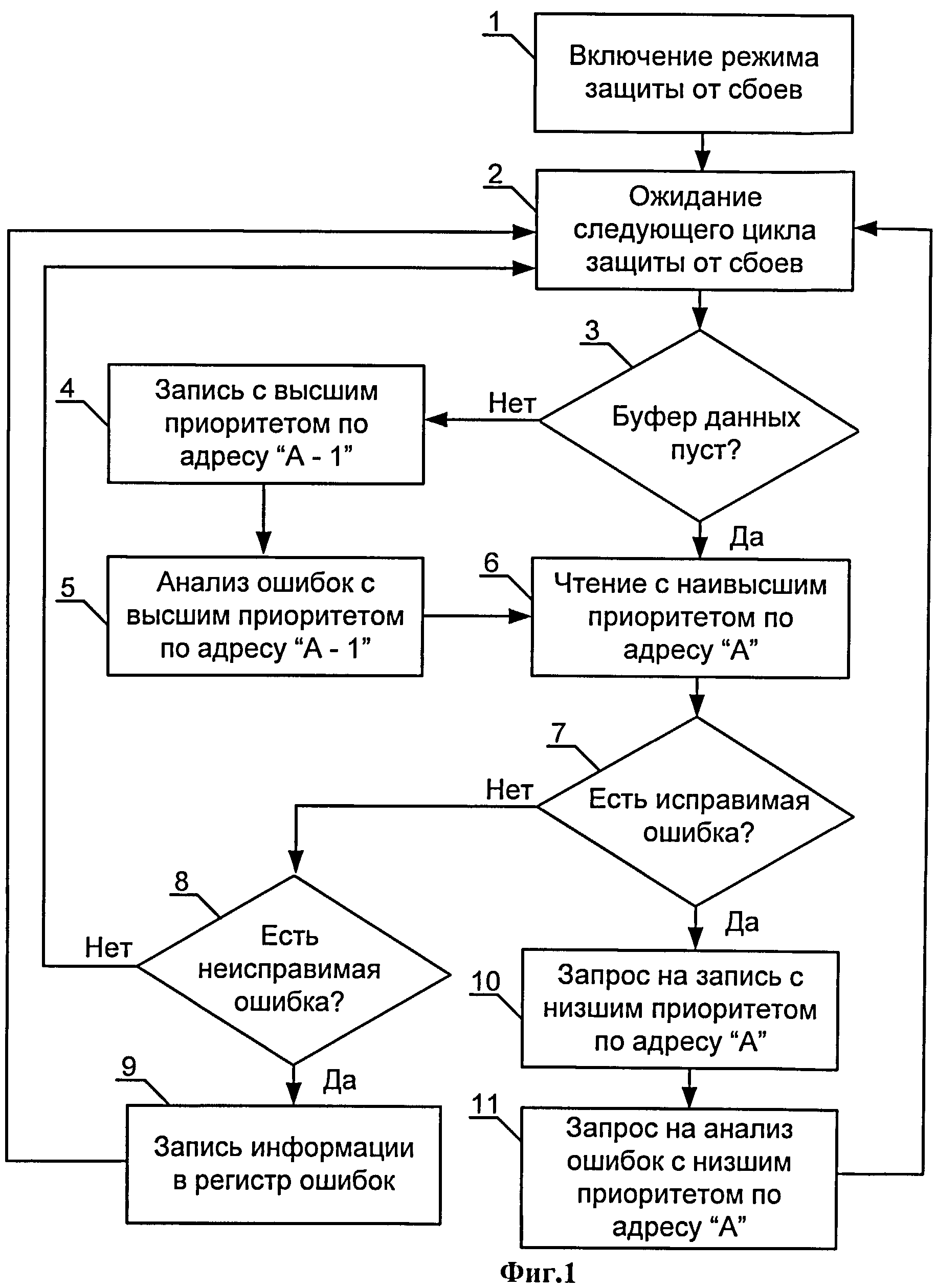

Изобретение поясняется чертежами, где на фиг.1 представлена блок-схема алгоритма способа регенерации и защиты от сбоев динамической памяти, а на фиг.2 - блок-схема устройства для регенерации и защиты от сбоев динамической памяти.

Алгоритм способа защиты от сбоев динамической памяти состоит из следующих этапов: после включения режима защиты от сбоев 1 сначала производят ожидание следующего цикла защиты от сбоев 2, после чего делают проверку на наличие модифицированных, но не записанных обратно в память данных с прошлого цикла защиты от сбоев в буфере данных 3. Также буфер данных объявляют пустым, если в процессе хранения данных, считанных из динамической памяти, произошло обращение к этим данным от внешнего устройства. Если буфер данных не пустой, то производят запись с высшим приоритетом по тому же адресу «А-1» 4 и производят анализ ошибок с высшим приоритетом 5, а именно: в устройство контроля динамической памяти с высшим приоритетом подают цепь запросов на чтение и запись по адресу, из которого были считаны данные в предыдущий раз («А-1») с записью в регистр ошибок данных о наличии и характере ошибок. Затем производят переход к чтению с высшим приоритетом по адресу «А» 6, а именно: в устройство контроля динамической памяти подают запрос на чтение с высшим приоритетом по адресу «А», выставленному в данный момент схемой управления защитой от сбоев, что и происходит после обработки предыдущего запроса устройством контроля динамической памяти. Если буфер данных пустой, то переход к чтению с высшим приоритетом по адресу «А» 6 производят сразу.

После чтения данных 6 их проверяют на наличие исправимой ошибки 7 и в случае отсутствия исправимой ошибки происходит проверка на наличие неисправимой ошибки 8. В случае наличия неисправимой ошибки производят запись информации о ней в регистр ошибок 9 и переход к ожиданию следующего цикла защиты от сбоев 2. В случае отсутствия неисправимой ошибки совершают переход к ожиданию следующего цикла защиты от сбоев 2.

В случае обнаружения исправимой ошибки при проверке на наличие исправимых ошибок 7 производят запрос запись данных по адресу «А» 10, а затем запрос на анализ ошибок с низшим приоритетом 11, а именно: с низшим приоритетом в устройство контроля динамической памяти подают цепь запросов на запись и чтение по адресу, из которого были считаны данные («А») для определения характера обнаруженной исправимой ошибки.

После чего систему переводят к ожиданию следующего цикла защиты от сбоев 2, а буфер данных очищают. Если запрос не удовлетворяется в течение ожидания следующего цикла защиты от сбоев, то буфер данных остается не пустым и на этапе анализа его содержимого 3 производят переход к этапу 4.

Устройство для осуществления способа регенерации и защиты от сбоев динамической памяти состоит из блока динамической памяти 12, устройства контроля динамической памяти 13, схемы управления защитой от сбоев 14, буфера данных 15, схемы прослушивания адреса 16 и регистра ошибок 17.

Устройство контроля динамической памяти 13 связано с блоком динамической памяти 12 шиной управления динамической памятью 18, шиной адреса динамической памяти 19 и шиной данных динамической памяти 20.

Схема управления защитой от сбоев 14 связана с устройством контроля динамической памяти 13 шиной управления устройством контроля 21.

Буфер данных 15 связан устройством контроля динамической памяти 13 шиной модифицированных данных 22, а также со схемой управления защитой от сбоев 3 шиной управления буфером данных 23.

Схема прослушивания адреса 16 связана с устройством контроля динамической памяти 13 шиной управления динамической памятью 18 и шиной адреса динамической памяти 19, а также со схемой управления защитой от сбоев 14 шиной прослушивания адреса 24.

Регистр ошибок 17 связан со схемой управления защитой от сбоев 14 шиной управления регистром ошибок 25.

Устройство работает следующим образом. При считывании данных из блока динамической памяти 12 по шине данных динамической памяти 20 в цикле защиты от сбоев происходит обнаружение ошибок, а также модификация данных путем коррекции ошибок в случае, когда это возможно. После чего модифицированные данные записываются в буфер данных 15 по шине модифицированных данных 22. Затем схема управления защитой от сбоев 14 по шине управления устройством контроля 21 подает запрос на обратную запись модифицированных данных с низшим приоритетом в устройство контроля динамической памяти 13. Адрес, по которому произошло считывание и коррекция ошибок, передается по шине прослушивания адреса 24 схеме прослушивания адреса 16. После чего схема прослушивания адреса 16 анализирует данные на шине управления динамической памятью 18 и на шипе адреса динамической памяти 19, ожидая записи по адресу, по которому произошло считывание и модификация данных. В случае выполнения устройством контроля динамической памяти 13 ожидаемой записи, сигнал об этом передается схемой прослушивания адреса 16 по шине прослушивания адреса 24 схеме управления защитой от сбоев 14. После этого схема управления защитой от сбоев 14 выставляет с низшим приоритетом устройству контроля динамической памяти 13 по шине управления устройства контроля 21 запрос для анализа ошибки, а именно: запрос на повторное чтение данных по этому адресу, после выполнения которого устройство контроля динамической памяти 13 проверяет на ошибки считанные данные. В случае обнаружения той же ошибки, что и при прошлом чтении по этому адресу, схема управления защитой от сбоев 14 производит запись об устойчивой ошибке в регистр ошибок 6 по шине управления регистром ошибок 25. В случае отсутствия той же ошибки в повторно считанных данных схема управления защитой от сбоев 14 производит запись о неустойчивой ошибке в регистр ошибок 17 по шине управления регистром ошибок 25.

В случае, когда ожидаемой записи не произошло за время ожидания следующего цикла защиты от сбоев, схема управления защитой от сбоев 14 подает запрос на обратную запись модифицированных данных в динамическую память 12 с высшим приоритетом в устройство контроля динамической памяти 13. Затем с высшим приоритетом осуществляется анализ ошибки на устойчивость. После чего схема управления защитой от сбоев 14 подает запрос на чтение данных по следующему адресу в динамической памяти 13 с высшим приоритетом в устройство контроля динамической памяти 13 по шипе управления устройством контроля 21. Затем осуществляется считывание данных из динамической памяти 12 по шипе данных динамической памяти 20, что представляет собой следующую итерацию цикла алгоритма защиты от сбоев динамической памяти 13.

Если в период ожидания записи модифицированных данных произошло обращение на запись в динамическую память 12 по тому же адресу, по которому ожидается запись модифицированных данных, но от внешнего устройства (на чертеже не показано), то в этом случае информацию о записи внешним устройством (на чертеже не показано), переданную от схемы прослушивания адреса 16 по шине прослушивания адреса 24, анализирует схема управления защитой от сбоев 14 и снимает свой запрос на обратную запись в динамическую память 12. Это делается для того, чтобы избежать замены актуальных данных, записанных в динамическую память 12 внешним устройством (па чертеже не показано) неактуальными данными, хранящимися в буфере данных 15.

В случае обнаружения устройством контроля динамической памяти 13 неисправимой ошибки в данных, считанных по шине данных динамической памяти 20 из динамической памяти 12, информация о ней поступает по шипе управления устройством контроля 21 в схему управления защитой от сбоев 14 и записывается схемой управления защитой от сбоев 14 в регистр ошибок 17 с помощью шины управления регистром ошибок 25.

Выставление данных на обратную запись после модификации с низшим приоритетом вместо высшего позволяет снизить общий приоритет служебных запросов, повысив, таким образом, общий приоритет запросов, отвечающих за выполнение основных задач микропроцессорной системы.

Прослушивание обращений по адресу хранящихся данных позволяет избежать коллизий в результате замены данных, записанных внешним устройством (на чертеже не показано), данными, хранящимися в буфере данных, что позволяет без снижения функциональности системы повысить ее быстродействие.

Анализ ошибок 4, 11 представляет собой анализ найденной исправимой ошибки на устойчивость, а именно проверку на наличие иных устойчивых сбоев в кодовом слове, записанном в динамической памяти.

В случае обнаружения исправимой ошибки производится ее коррекция и обратная запись модифицированного кодового слова. В случае, когда ошибка является результатом устойчивого сбоя в динамической памяти, ячейка может хранить только значение логического нуля или единицы. Для выявления таких ошибок производят повторное чтение записанного обратно модифицированного кодового слова и, в случае обнаружения исправимой ошибки в том же бите кодового слова, производят запись в регистр ошибок о наличие постоянной ошибки.

Также в качестве анализа ошибок 4, 11 производят обратную запись кодового слова, значения всех битов которого инвертированы относительно их изначальных значений, чтение, анализ ошибок и запись изначального значения кодового слова. В случае, когда в результате анализа ошибок обнаруживается исправимая ошибка, то производят запись в регистр ошибок о наличие постоянной ошибки.

Изобретение позволяет повысить сбоеустойчивость микропроцессорной системы путем информирования пользователя через регистр ошибок о наличии и характере выявленных в подсистеме динамической памяти ошибок.