Результат интеллектуальной деятельности: УСТРОЙСТВО КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ

Вид РИД

Изобретение

Предлагаемое изобретение относится к вычислительной технике, дискретной автоматике и системам связи и может быть использовано для защиты информации в системах обработки информации и дистанционного управления в реальном времени (подвижные средства, особо ответственные объекты, закрытая коммерческая или служебная связь).

Известны программные системы шифрования двоичной информации на основе блочных шифров с использованием методов логического преобразования информации по закрытому ключу с последующим рассеиванием информации [1, 2, 8-10]. Преобразование информации в большинстве случаев связано со сложением по модулю два (операция XOR) порции информации с кодом секретного ключа. После операции XOR часть сообщения подвергается перемешиванию, а другая переставляется на место первой (основа метода Фейстеля и др.). Эти процедуры повторяются 32-64 раза.

Недостатком существующих программных систем является низкое быстродействие, требующее даже на сверхбыстродействующих ЭВМ десятки минут для кодирования или декодирования информации, что совершенно неприемлемо для систем реального времени.

Известны также способы, включающие нелинейные операции типа возведения в степень n и сложения по модулю Р (n < Р). Эти способы описаны в [1, 2, 8-10], а также в изобретениях. Хотя указанные аналоги имеют более высокое быстродействие, чем программные системы, тем не менее они сложны в реализации.

Известны три полезные модели авторов настоящего изобретения (№82974, №82889, №82890, БИ №3, 2009), в которых использованы новые способы и алгоритмы преобразования и рассеивания информации, позволяющие при аппаратной реализации без многоцикловой процедуры осуществить криптозащиту за несколько десятков микросекунд или при переходе на сверхбыстродействующие БИС и за единицы микросекунд. Однако каждое из этих решений обладает недостатками.

В патенте РФ №82890 используется только один ключ, состоящий из набора коэффициентов (L1, L2 … Lk) полиадической системы счисления.

В патенте РФ №82974, несмотря на наличие большого числа ключей-констант (до нескольких тысяч), хранящихся в постоянном запоминающем устройстве, используется процедура с зависимостью модификации ключа по предыдущей порции информации, что делает систему уязвимой для расшифровки, т.к. остается неизмененной последняя «порция» информации, а предположив наличие именно этой рекуррентной процедуры обратного восстановления сохраняется возможность расшифровки за счет переборного изменения содержимого ПЗУ расшифровщика с использованием датчика случайных чисел.

В патенте РФ №82889 при оригинальной процедуре рассеивания информации все-таки сохраняется необходимость наличия одного секретного ключа ограниченной разрядности, что, как известно, не дает возможности достичь необходимого уровня криптозащиты информации.

По количеству совпадающих элементов и блоков наиболее близким к предлагаемому изобретению является патент РФ №82974 [5].

Целью настоящего изобретения является повышение уровня криптозащиты при сохранении быстродействия аппаратурной реализации устройств.

Поставленная цель достигается за счет создания нового устройства, в котором используются части предыдущих патентов авторов.

Комплексирование вышеназванных полезных моделей 82974,82889, 82890, 63588, 82888 производится не путем механического последовательного соединения пяти устройств по патентам, а создание нового устройства с изменениями состава блоков и связей между ними и введением дополнительных функциональных возможностей, не свойственных аналогам и прототипам.

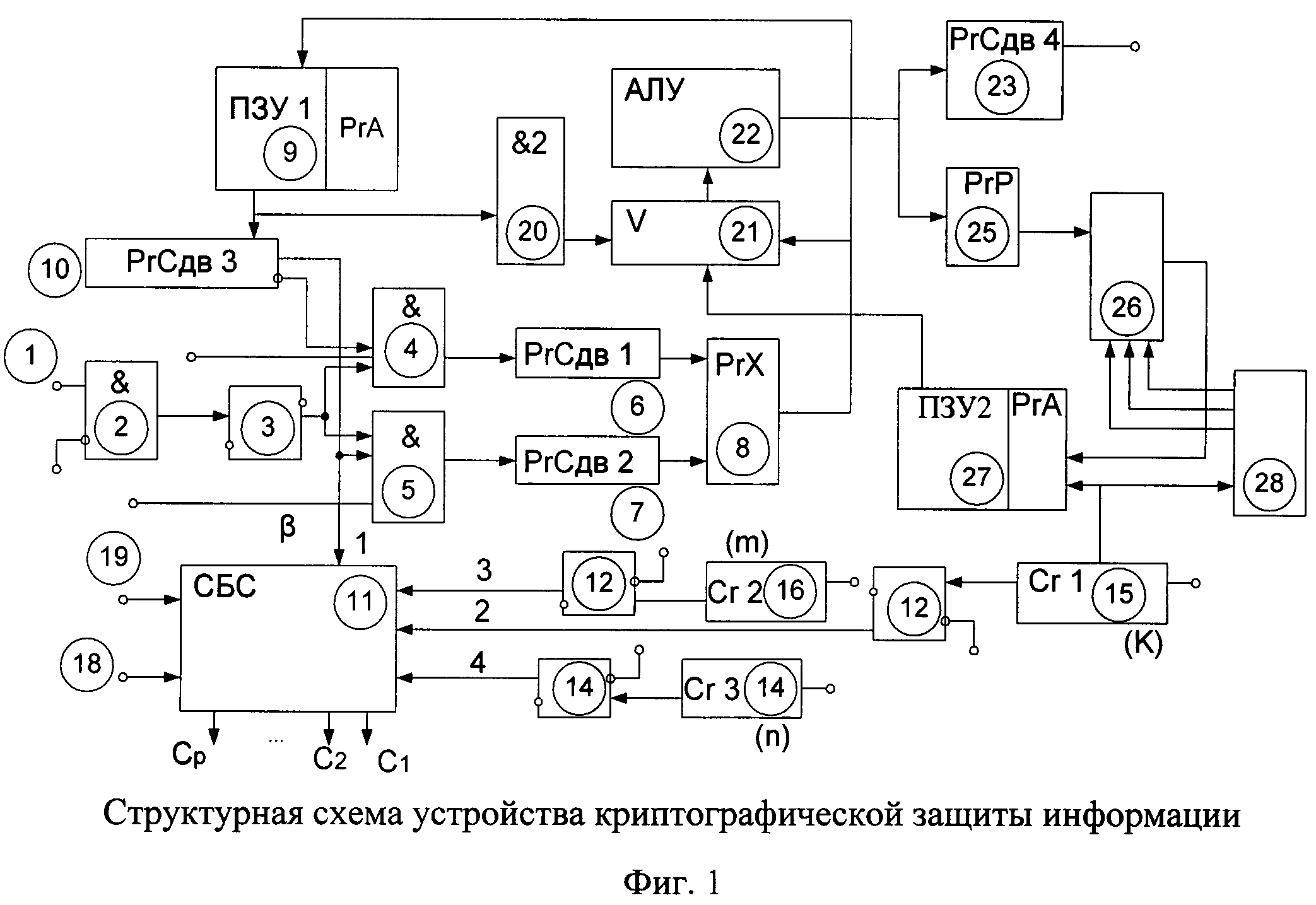

Устройство криптографической защиты информации (фиг.1) состоит из последовательных цепей элементов и блоков в виде первой клеммы (1), связанной через первый элемент И (2) с единичным входом триггера Тр (3), единичные выходы которого связаны с первыми входами второго и третьего элементов И (4), И (5), выходы которых связанны соответственно с последовательными входами первого и второго регистров сдвига РгС (6), РгС (7), параллельные выходы которых связаны соответственно со старшими и младшими разрядами регистра информационного слова РгХ (8), выход которого связан со входом первого постоянно запоминающего устройства ПЗУ1 (9), соединенного выходом со входом третьего регистра сдвига РгС (10), нулевой выход старшего разряда которого связан со вторым входом второго элемента И (4), а единичный выход связан со вторым входом третьего элемента И (5) и первым входом самоконтролируемого блока синхронизации СБС(11), имеющего также входы от единичных выходов второго, третьего и четвертого триггеров Тр (12), Тр (13), Тр (14), связанных с выходами переполнения первого, второго и третьего счетчиков Cr1 (15), Cr2 (16), Cr3 (17) соответственно, причем самоконтролируемый блок синхронизации СБС (11) имеет две входные внешние клеммы Пуск (18) и Останов (19); вторая последовательная цепь блоков образуется с выхода первого постоянного запоминающего устройства ПЗУ1 (9) через блок схем И - БИ (20), затем блок схем ИЛИ - ИЛИ (21), связанных со входом арифметико-логического устройства АЛУ (22), связанного с четвертым регистром сдвига РгС (23), имеющего последовательный вход на клемму (24) и регистр результата РгР (25), связанного через блок групповых схем И (26) младшими разрядами входов второго постоянного запоминающего устройства ПЗУ2 (27), выходы которого связаны со вторыми входами блока схем ИЛИ (21), третьи входы которого связаны с выходами регистра информационного слова РгХ (8). Причем параллельные выходы первого счетчика Сг1 (15) связаны старшими разрядами входов второго постоянного запоминающего устройства ПЗУ2 (27) и со входами дешифратора DC (28), выходы которого связаны со входами синхронизации соответствующих групп блока групповых схем И (26); причем выходы самоконтролирующего блока синхронизации СБС (11) C1 C2 … Сp связаны со всеми управляющими входами элементов и блоков устройства криптографической защиты информации.

Разрядность регистров памяти различна. Для регистров Рг3 (10), РгХ (8), РгР (25) разрядность равна m, для Рг (6), (7) равна m/2, а разрядность АЛУ и Рг (27) определяется числом группы (k), на которые делится m, и значениями (р) коэффициентов L1 L2 … Lk. Для m=16 разрядность Рг (27) р ≤ 24. Соответственно различна и разрядность счетчиков: Сг1 (15) - разрядность определяется разрядностью двоичного кода групп К, для Сг (2) - m, а для Сг (3) - р.

Для блока синхронизации СБС (11) применена характеристика самоконтролируемого для того, чтобы отметить его принципиальное отличие от ранее использованных блоков синхронизации в аналогах и прототипах. Хотя далее для сокращения текста он будет называться как блок синхронизации СБС (11) без слова самоконтролируемый.

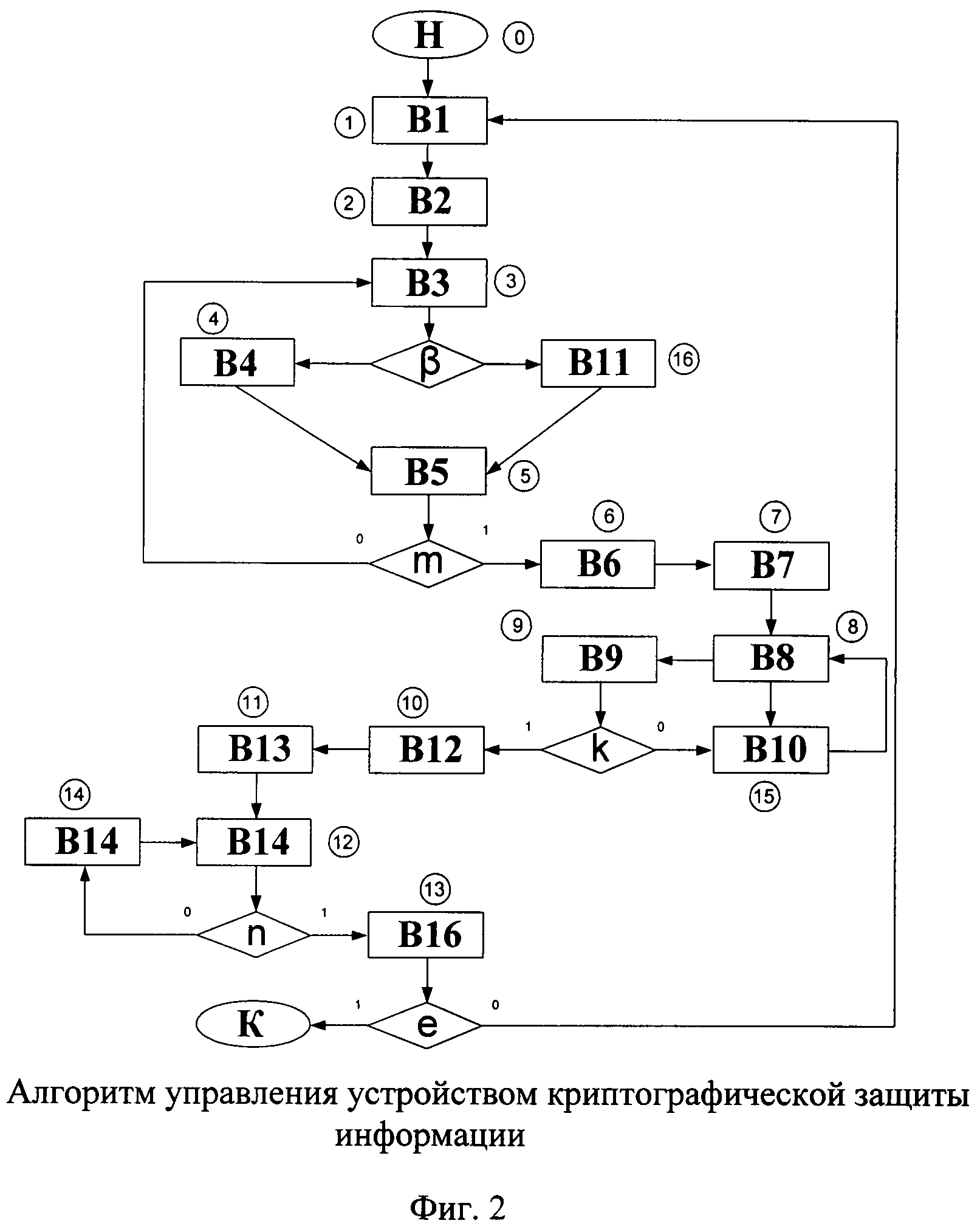

Предлагаемое устройство функционирует в следующей последовательности по алгоритму (фиг.2):

- после подачи сигнала Пуск на клемму (18) блока синхронизации СБС (11) начинается последовательный прием m - разрядов входного сообщения через клемму 1 с одновременным рассеиванием информации по коду РгС3 (10) в РгСдв 1(6) и РгСдв (7) и соединение их в единую конкатенацию на регистре РгХ (8), когда i=m. Константы ПЗУ (19) выбираются такими, чтобы число «1» и «0» в них было одинаковым, но расположены они в случайном порядке, т.е. число единиц и нулей равно m/2. Тогда C(i)=(i)/D(i)=1; В(i)=(i)/D(i)=0, где (i) - i-тый разряд информационного слова; C(i) - значение i-того разряда регистра РгС2 (5); B(i) - значение i-того разряда регистра РгС1 (4); D(i) - значение i-того разряда константы в РГСЗ (10). Предыдущее x(t-1) значение информационного сообщения, рассеянное по первой процедуре и записанное в регистр адреса ПЗУ, рассматривается как адрес для выбора секретного кода ключа из ПЗУ-1 (9) с записью его на накапливающий сумматор арифметико-логического устройства АЛУ (22). В следующих тактах на АЛУ(22)поступает информационное слово x(t), также предварительно «перепутанное» (рассеянное). Далее находится значение x(t) по процедуре x(t)=х⊕К (х-1), где K(x(t-1)) - константа, определяемая адресом x(t-l); ⊕ - операция неравнозначности (XOR).

Примечание: так же, как регистр адреса ПЗУ входит в состав ПЗУ, так и накапливающий сумматор входит в состав АЛУ и не выносится в виде отдельного блока в структуре устройства криптографической защиты информации.

Преобразованное таким образом сообщение x(t) переводится из двоичного в полиадический код по формуле

R(x)=a0+x1L1+x2L1L2+…+L1L2…Lpxp,

где x1 x2, … xn - арифметическое значение кодов групп хi (i=1, 2, … р) преобразованного сообщения, зафиксированного на РгР(25) и разделенного на р групп. Коэффициенты L1, L2 … Lp могут быть любыми, в том числе Li=Lj, но любое L>2m/p, т.к. в m/p разряд ах группы записано число (2m/p-1).

Пример для двухразрядных групп приведен в табл.1. Как видно, значение первой и пятой групп взято равным 5. Число, которое может быть получено при выбранных значениях Li, равно Q(x).

Q=5.1+35.3+315.2+3465.0=18065

Максимальное число, которое можно записать в группе из двух разрядов (xi), равно трем, тогда

Q=(5+35+315+3465+17325)·3=21.145×3=63.435<216

Здесь Q - максимально возможное полиадическое число, соответствующее информационному слову; Ri - коэффициенты полиадической системы счисления, соответствующие каждому разряду числа. Т.е 10-разрядное число, представленное в двоичном позиционном коде, преобразуется в 16-разрядный двоичный код полиадического числа. Конкретно заданное число xi(t) со значениями xi из табл.1 (строка 2) будет равно 18065.

Для трехразрядных групп пример приведен в табл.2. Как видно в данном случае 12-разрядное информационное слово x(t) будет преобразовываться в 19-разрядное полиадическое число. В табл.3 приведен пример для 16-разрядного x(t), которое будет преобразовываться в 22-разрядный двоичный код полиадического числа.

Таким образом каждая m - разрядная часть сообщения подвергается рассеиванию, сложению с секретным ключом, значение которого выбирается из ПЗУ1 (9) и преобразованием этой части сообщения в двоичный r-разрядный код полиадического числа. Причем r ≤ 1,5m и может не быть кратным числу 2 в целой степени.

Нетрудно видеть, что произведя обратные преобразования делением на R5, затем остатка на R4 и т.д. до Ri, получим коэффициенты 1, 0, 2, 3, 1 соответствующие значениям xi. Во всех примерах (табл.1, 2, 3) для простоты пояснений константа а0 взята равной «0».

В табл.2 дан пример деления x(t) на четыре группы по 3 разряда в каждой. Все блоки и логические элементы предлагаемого изобретения, типовые не имеют специфических особенностей, кроме блока групповых схем И (26) и блока синхронизации БС (11).

Блок групповых схем И (26) отличается от типового набора параллельно работающих схем И тем, что они разделены на группы по (2, 3 или 4 разряда) с общими для группы входами синхронизации, соединенными с выходами дешифратора DC (28). Постоянные запоминающие устройства (ПЗУ) типовые, но содержимое числовой части ПЗУ определяется в соответствии с заложенными в изобретении принципами.

1) ПЗУ (27) позволяет реализовать операцию умножения m разрядных чисел на коэффициенты Pi методом прямого считывания. При n-разрядном коде результата (выход ПЗУ) потребуется объем ПЗУ, равный n2m+p, где p - число разрядов, необходимое для представления наибольшего номера константы. Для получения верного результата константы Р(i) должны быть той же разрядности, как и х, т.е. должны иметь разрядность m. При классическом выполнении операции умножения табличным способом объем ПЗУ определится величиной n22m. При n=m-12, V=12*224=192*220=200 Мбит. В изобретении применен прием нахождения результата умножения переменной величины x(t) на константу той же разрядности m через ПЗУ объемом V=n2m+p, а не через ПЗУ объемом V=n22m по методу прямого считывания результата. При m=16 и n=3 объем ПЗУ будет уменьшен более чем в 8000 раз по сравнению с методом прямого считывания результата. Поскольку количество констант Pi ограничено (к=4, 5, 6), то для их представления в адресе ПЗУ достаточно взять р=2-3 разрядам. Сами константы известны заранее, а значение Х(m/k) - это неизвестная часть сообщения Х(t), поступившая в данный момент, тогда содержимое ПЗУ можно определить заранее так, чтобы по значению Х(t) разрядностью m/k (здесь обозначено Х(m)) и номеру константы (р) можно было определить значение n разрядного ответа как результата операции умножения. Обоснование выбора числа к=4, 5, 6 дается далее в тексте описания изобретения.

В ПЗУ1 (9) записаны 2m констант разрядностью m (секретные ключи), рассортированные с помощью датчика случайных чисел так, что нет прямой корреляции между номером адреса и значением константы. Причем константы таковы, что в них равное число «0» и «1».

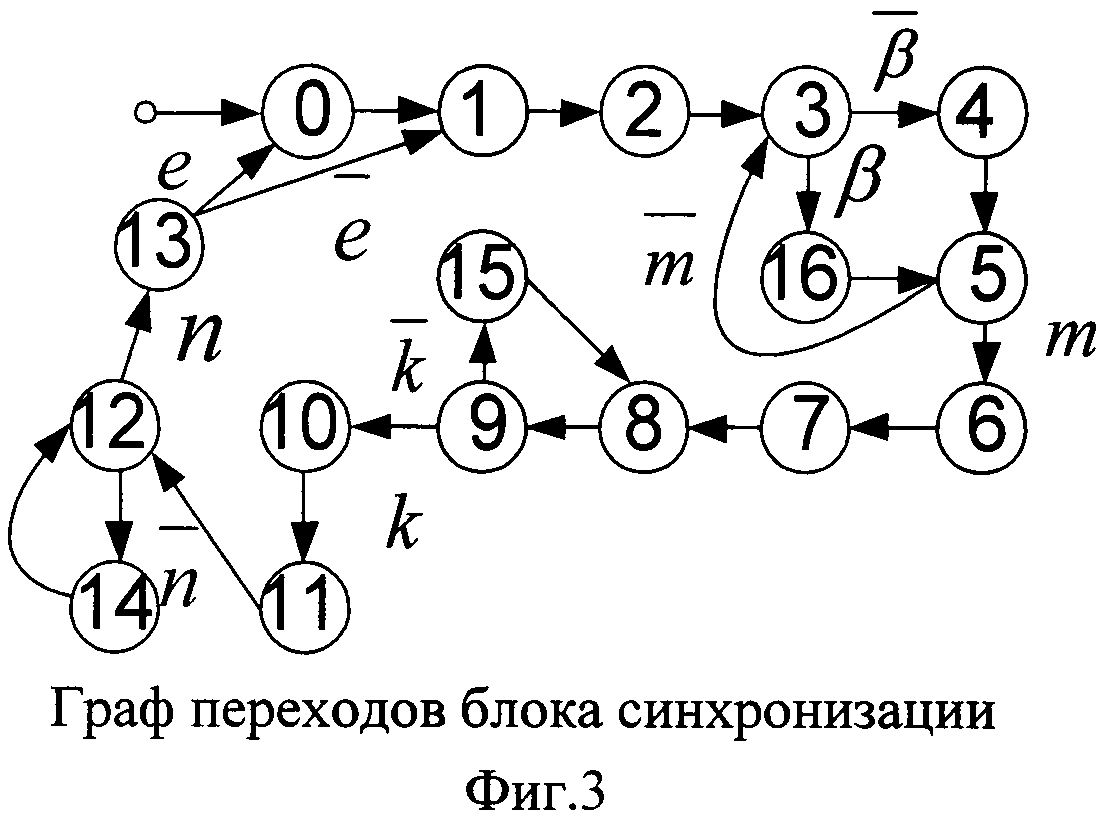

Блок синхронизации СБС (11) проектируется по графу переходов (фиг.3), полученному из граф-схемы алгоритма (фиг.2). Структура СБС (11) не типовая, т.к. основана на применении полезных моделей авторов по патентам РФ №63588 Би №15, 2007 и №82888 Би №13, 2009.

Формализованное описание во времени функционирования устройства криптографической защиты информации представлено в виде ГСА на фиг.2 с расшифровкой команд синхронизации  в табл.4. На основании ГСА фиг.2 по методике [3], а также [4, 11, 12] СБС (11) проектируется как автомат Мура с мультиплексором для выделения одного единственного логического условия αj Є {α} по коду a(t). Ha ГСА фиг.2 множество {α} представлено в виде β, m, k, n, e, где

в табл.4. На основании ГСА фиг.2 по методике [3], а также [4, 11, 12] СБС (11) проектируется как автомат Мура с мультиплексором для выделения одного единственного логического условия αj Є {α} по коду a(t). Ha ГСА фиг.2 множество {α} представлено в виде β, m, k, n, e, где

β - значение «1» или «0» на выходе РгС3 (10);

m - разрядность информационного слова;

k - количество групп;

n - разрядность выходного слова;

е - признак окончания программы (end).

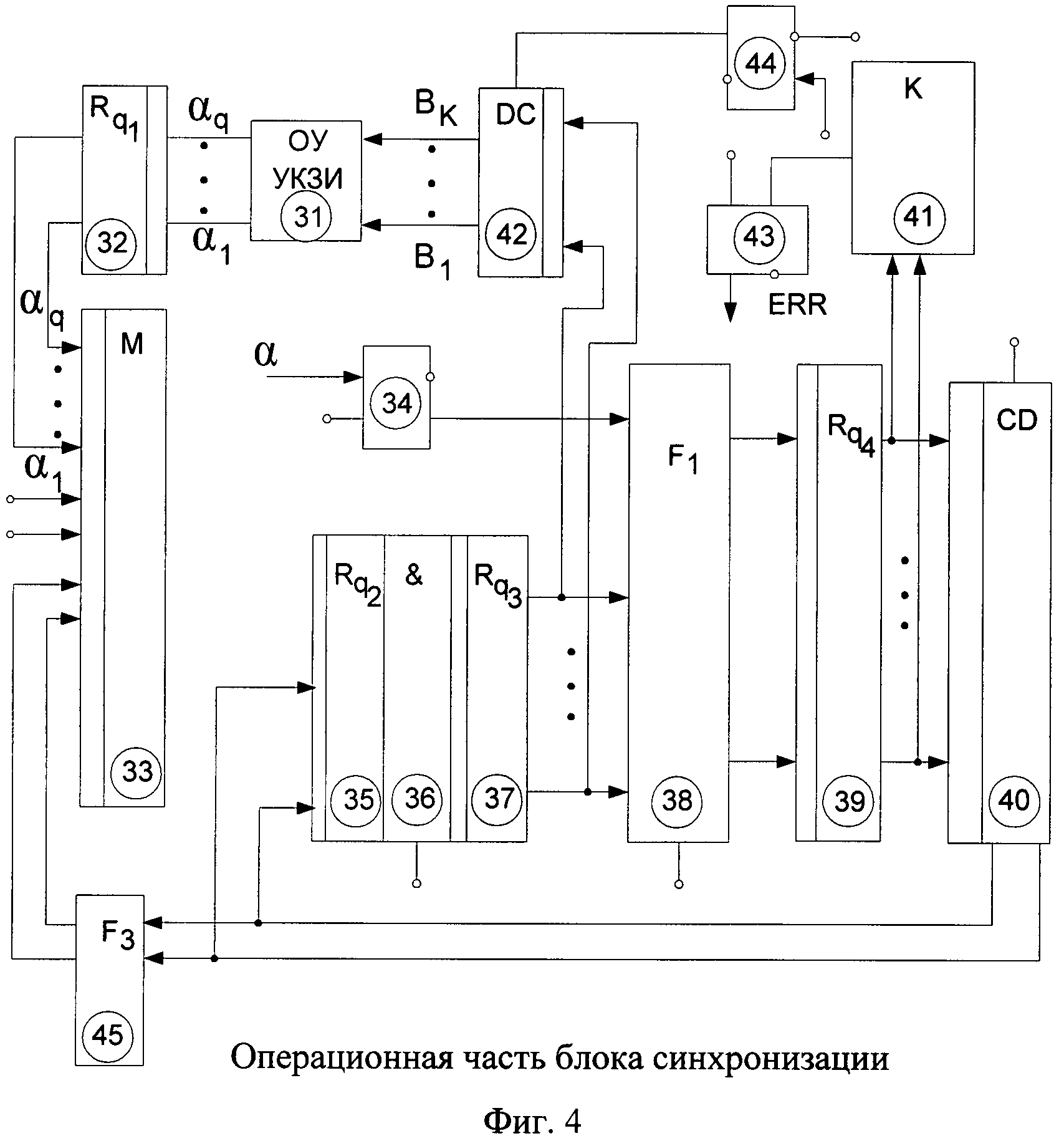

На фиг.4 обозначены М (33) - мультиплексор с информационными входами от регистра памяти Rq1 (32) и с адресными входами от схемы F3 (45). Rq1, 2, 3, 4 - запоминающие регистры; К(41) - схема контроля; Тр 34, 43, 44 - триггеры; DC - дешифратор; CD - шифратор для перевода кода МГК в код ДНК. F3 (45) - комбинационная схема перевода кода ДНК в порядковый номер логического условия α.

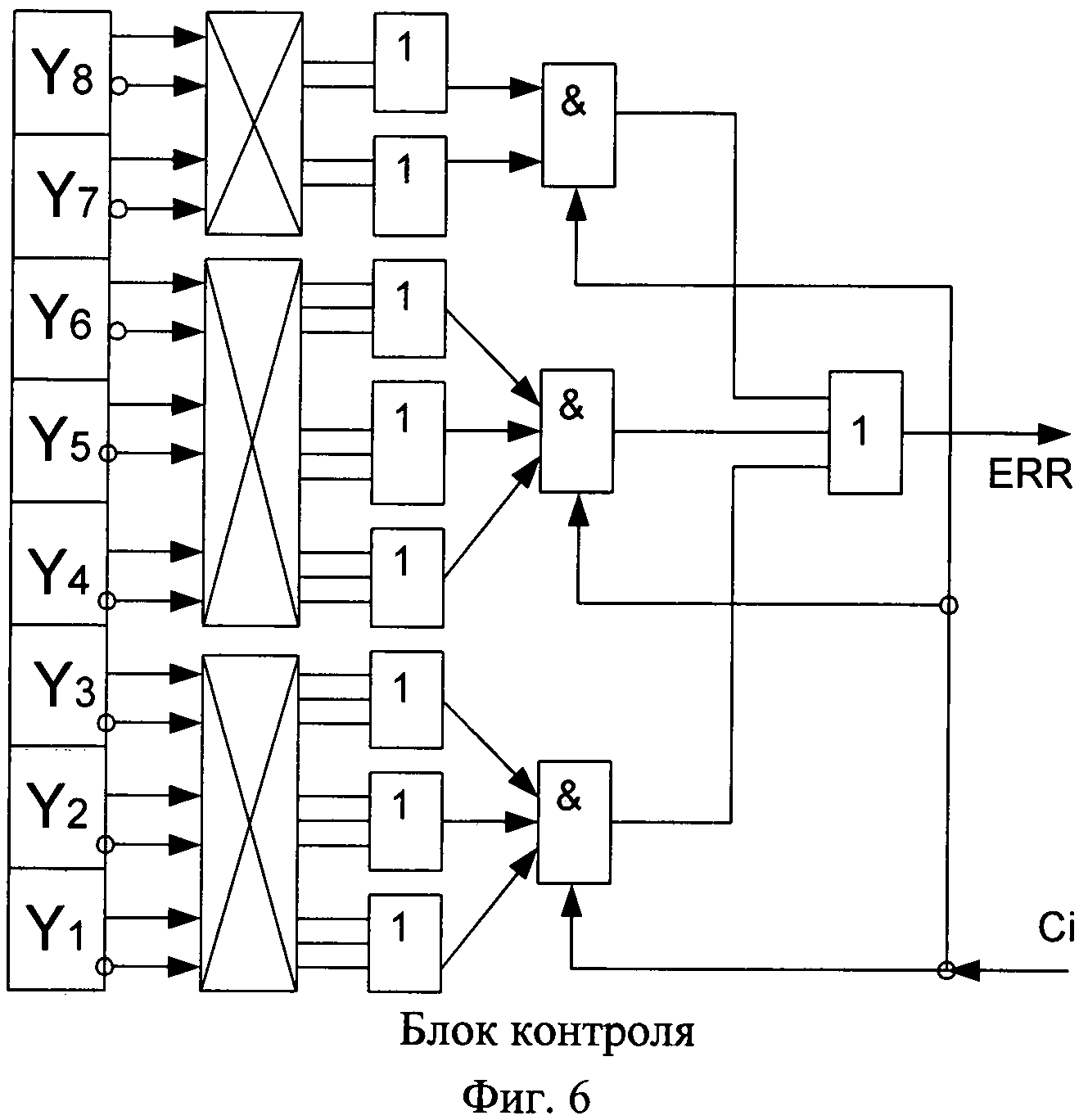

В схему автомата блока синхронизации СБС (11), представленную на фиг.4, введена схема контроля правильности переходов из состояния a(t) в a(t+1). Для контроля использован способ, предложенный в патенте на полезную модель [5], заключающийся в том, что a(t+1) представляется в виде модифицированного геометрического кода (МГК), тогда как состояния a(t) представлены в виде двоичного непозиционного кода (ДНК). МГК основан на представлении каждых двух разрядов двоичного позиционного кода (ДПК) в виде трехразрядного кода с соответствием 00-001, 01-010, 10-100. Для комбинации 11 потребуется изменение в группе более старших разрядов МГК. Соответствие ДПК - МГК - ДНК представлено в табл.5.

Как видно из таблицы 5, в МГК в каждой группе из трех разрядов возможна комбинация только с одной единицей.

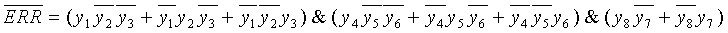

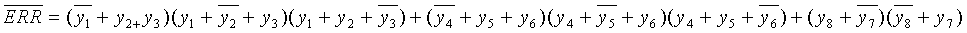

Если для примера обозначить в виде y1 y2 … y8 выходы комбинационной схемы F1 на фиг.6, то отсутствие ошибки определяется выражением

.

.

Тогда ошибка фиксируется в случае:

Формуле (ERR) соответствует схема контроля фиг 5. На схеме в блоках с перекрестием зачеркиванием обозначена коммутация выходов y1 y2 … y8 по группам в соответствии с записью для ERR.

Из фиг.6, представленной для примера, ясен принцип создания схемы контроля и для большего числа переменных y1 y2 … yn.

Необходимость контроля правильности функционирования блока синхронизации СБС(11) определяется тем, что в устройстве криптографической защиты информации фиг.1 (при наличии ~30 элементов и блоков в основной схеме) именно СБС(11) работает на каждом такте генератора импульсов (ГИ). Поэтому от правильной работы СБС(11) в первую очередь зависит корректность результатов всего устройства.

На фиг.4 все элементы и блоки автомата СБС(11) пронумерованы, начиная с цифр более 30 для того, чтобы в описаниях блоки основного устройства и блока синхронизации отличались по номерам.

Все блоки в автомате СБС(11) синхронизируются тактовыми импульсами, кроме шифратора CD(40) для перевода МГК в ДНК и схемы F3(45) для перевода ДНК в порядковый номер αjЄ{α}, Соответствующие булевы функции определяются по таблице 4 и их реализация по типовой методике тривиальна.

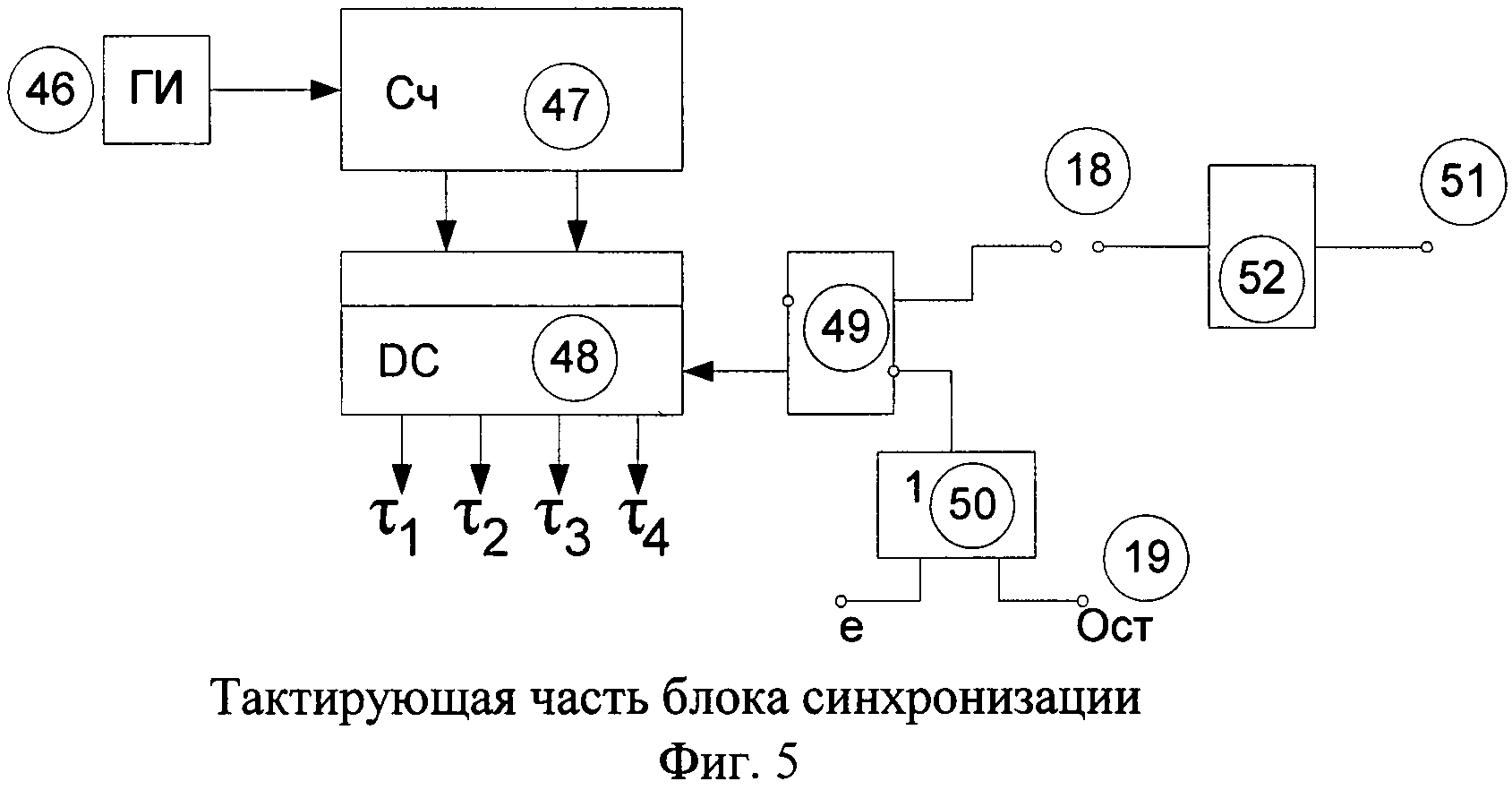

Схема автомата СБС(11), представленная на фиг.4, тактируется от генератора тактовых импульсов, формирующего последовательность непересекающихся во времени импульсов τ1 τ2 τ3 τ4, причем τ1 (t) & τ2 (t) & τ3 (t) & τ4(t)=ø. Такие генераторы известны [13] или могут выполняться на основе типового генератора импульсов с одним выходом ГИ(46) по схеме фиг 5, на которой обозначено: ГИ(46)- генератор импульсов; Cr(47) - двухразрядный счетчик; DC(48) - дешифратор на два входа с четырьмя выходами; ИЛИ(50) - схема перевода Тр(49) в нулевые состояния по сигналу окончания программы (е) или внешнему сигналу Останов (19); (18) - вход сигнала Пуск.

Для правильности работы сигнал Пуск должен подаваться кнопкой (18) после нажатия кнопки (51) для того, чтобы блоки СБС(11) и все необходимые блоки всего устройства криптографической защиты установились в исходное «нулевое» состояние. Это действие осуществляет элемент (52).

Автомат управления блока СБС(11) выдает команды синхронизации B1 B2 … B16 в соответствии с граф-схемой алгоритма фиг.2. Комбинационная схема F1(38) реализована по таблице переходов (табл.6), полученной по графу переходов фиг.3. Вместо комбинационной схемы F1(38) могут быть использованы запоминающее устройство (ПЗУ) или программируемая логическая матрица (ПЛМ).

Автомат блока СБС(11) фиг.4 осуществляет свое функционирование под действием импульсов τ1 τ2 τ3 τ4 по условиям:

τ1 - счит М(3); <Rq5>→Rq7; Вкл. DC(12)

τ2 - счит F1(8) →Зп Rq(9); Уст «0» Тр(13)

τ3 - счит CD(10); Счит К(11); ЗпМ(3); Зп Rq(5)

τ4 - откл DC(12); Уст «0» Тр(4).

Структурная организация автоматов и их функционирование во времени подробно описаны в литературе [3, 13, 14], включая и автоматы с мультиплексором [4, 5], поэтому последовательность связей и внутренних элементов блока синхронизации не описывается.

Предлагаемое устройство криптографической защиты информации принципиально отличается от известных решений, приведенных в патентах и цитируемой научной литературе, комплексом блоков и связей между ними, обеспечивающих преобразование двоичного кода информационного сообщения (которое рассматривается как целое число в двоичной позиционной системе счисления), в новое двоичное число с несколькими основаниями счисления (полиадическая система). Причем прежде чем это полиадическое число будет получено, часть сообщения (информационное слово) подвергается процедуре рассеивания информации и сложения с одним из нескольких тысяч секретных ключей. Несмотря на ограниченное число коэффициентов такой системы L0 L1 … Lk (где значение (k) может быть выбрано равным 3, 4, 5, 6) наличие повторяющихся коэффициентов в ряду L0 L1 … Lk, а также наличие постоянного слагаемого а0 делают невозможным нахождение конкретных значений Li, если противнику даже известно, что используется полиадическая система счисления.

Криптостойкость повышается также за счет наличия блока перемешивания и применяемого преобразования (практически во всех изобретениях и в том числе здесь) с помощью операции сложения по модулю 2. Поскольку за несколько преобразований m -разрядных частей полного сообщения выполняется операция Y(t)=x(t)+Kx(t-1), где Kx(t-1) - константа (секретный ключ) разрядностью m, выбранная из ПЗУ, то такая процедура обеспечивает фактически выполнение операции логического сложения по mod2(XOR) как бы с единым секретным ключом разрядностью r2m, где r - число различных m-разрядных участков в полном тексте сообщения. Если используются для кодирования все константы ПЗУ, но 30% из них совпадают, то величина М=0.7m2m. Даже взяв случаи 50% совпадений получим М=2m-1.

Единая методика оценки криптостойкости аппаратной реализации устройств криптографической защиты информации нам не известна, т.к. она возможно и не существует.

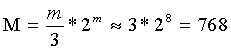

Однако из источников [1, 2, 8, 9, 10] известно, что при длине секретного ключа М=128 взлом простым подбором практически нереален на современных ЭВМ. Тем не менее, для некоторых систем программной защиты величина М выбирается с запасом М=512. В предлагаемом устройстве величину М оценим следующим образом.

Разрядность информационного слова и секретного ключа с равным числом «0» и «1» равна m. Без требований к равенству «0» и «1» число ключей равнялось бы 2m. Однако, хотя секретные ключи - константы перемешены по случайному закону, так что нет прямого соответствия между ключами их адресом, тем не менее реальное число различных констант меньше 2m из-за требований равенства количества «0» и «1» в константе. Рассматривая m=4,6 и 8 логично заключить, что число различных констант более (m/3)2m. Действительно:

Для m=8

Для m=12 M=4*212=214>16000

Для m=16 M=5*216=320000000

т.е. уже при m=12 предлагаемое устройство обеспечивает защиту, эквивалентную использованию секретного ключа разрядностью М=16000. Кроме того, следует учесть дополнительную защиту за счет полиадической системы и несоответствия длины принимаемого от средств информационного слова (m) и длины передаваемого в канал связи зашифрованного слова (n).

Известно, что расшифровка сообщения простым перебором на сверхбыстродействующих ЭВМ невозможна за приемлемое время при М=128, т.к. число комбинаций равно 2M. Поэтому во всех известных программных алгоритмах величина М=128-512. Но и при таких значениях М программные способы криптографической защиты требуют для реализации десятки минут времени, а при значении М>1000 они вообще не реализуются, т.к. требуется многомесячная непрерывная работа на ЭВМ. В предлагаемом изобретении осуществляется процедура криптозащиты за единицы микросекунд даже при М>16000. Действительно, пусть m=16, тогда разрядность выходного слова равна 22. Поскольку прием и передача производятся синхронно последовательным кодом, то для приема и передачи потребуется 22+16 синхроимпульсов. Обработка информации по алгоритму фиг.2 потребует еще 20 импульсов для формирования 45 микроопераций, большинство из которых реализуется параллельно на структуре фиг.1. Следовательно, общее число синхросигналов ≤ 60. Самые сложные операции в структуре фиг.2 это сложение и считывание результата из ПЗУ, время реализуемости которых практически одинаково. Вместо ПЗУ могут быть взяты более быстродействующие программируемые логические матрицы (ПЛМ). На сегодня для быстродействующих интегральных схем время выполнения указанных операций за 10-20 нс не является предельным. Тогда, взяв даже 20 нс, получим общее быстродействие равным 60*20 нс=1.2 мкс. При длительности синхроимпульса τ=0.05 мкс время полной работы для криптозащиты информационного 16-разрядного слова составит t.

t=60*0.05 мкс=3 мкс.

Для интегральных схем среднего быстродействия τ=0.1 мкс, тогда t=6 мкс. Такого результата нельзя получить ни на одном из известных аналогов при той степени защиты, которая обеспечивается в предлагаемом изобретении.

Методы количественной оценки степени защищенности устройств авторам не известны. Что касается предлагаемого изобретения, то здесь степень наивысшая по сравнению с известными решениями, что и доказывалось выше.

Достоинством предлагаемого изобретения является высокое быстродействие, а достигаемый уровень криптозащиты не требует повторения операции несколькими раундами как в известных алгоритмах Фейстеля, Блоуфиш.

Отличием предлагаемого устройства является также наличие нескольких параметров настройки:

1 - величины m, k;

2 - значение коэффициентов L0 L1 … Lp полиадической системы счисления.

Очевидно, что величины L0 L1 … Lp так же как m, k могут меняться периодически с заменой содержимого ПЗУ1 и ПЗУ2 в аппаратуре приема и передачи сообщений.

3 - значение постоянного слагаемого а0 в полиадической системе счисления;

4 - введение секретных ключей с равным числом «1» и «0» для перемешивания информации;

5 - использование для операции логического сложения не одного ключа разрядностью m, а 2m ключей для «покрытия» всего сообщения;

6 - возможность аппаратной реализации с разрядностью передаваемого информационного слова, не кратной целой степени двойки, как в типовых микроконтроллерах, использующихся для процедуры «взлома»;

7 - эффективно построенный блок синхронизации со встроенным контролем.

Все перечисленные достоинства предлагаемого устройства выгодно отличают его от прототипов и известных авторам аналогов.

Аппаратная реализация алгоритма раскодирования в принципе будет мало отличаться от структуры фиг.1, однако в число операций сумматора для кодирования нужно включить вычитание и деление чисел с фиксированной запятой, а также изменить алгоритм функционирования на обратный с теми же, по сути, командами (за малым исключением) и микрооперациями.

|

|

|

|

|

|

Литература

1. Молдовян, А.А. Криптография / А.А.Молдовян, Н.А.Молдовян, Б.Я.Советов. - СПб: Изд-во Лань, 2001. - 224 с.

2. Лагутин В.А. Утечка и защита информации в телефонных каналах / В.А.Лагутин. - M.: Энергоатомиздат, 1998. - 364 с.

3. Мухопад Ю.Ф. Теория дискретных устройств / Ю.Ф.Мухопад. - Иркутск: ИрГУПС, 2010. - 172 с.

4. Мухопад, Ю.Ф. Микроэлектронные системы управления / Ю.Ф.Мухопад. - Братск: БГУ, 2009. - 285 с.

5. Мухопад, Ю.Ф. Устройство криптографической защиты информации / Ю.Ф.Мухопад, А.Ю.Мухопад, Т.Б.Агафонов // Патент РФ на полезную модель №82974. - БИ №13, 2009.

6. Мухопад, Ю.Ф. Устройство криптографической защиты информации / Ю.Ф.Мухопад, А.Ю.Мухопад Б.Н.Антошкин // Патент РФ на полезную модель №82889. - БИ №13, 2009.

7. Мухопад, А.Ю. Устройство криптографической защиты информации / А.Ю.Мухопад, Ю.Ф.Мухопад // Патент РФ на полезную модель №82890. -БИ №13, 2009.

8. Чмора А. Современная прикладная криптография / А.Чмора. - М.: Гелиос АРВ, 2001. - 244 с.

9. Фергюсон Н. Прикладная криптография / Н.Фергюсон, Шнайер. Б.М., СПб., Киев: Диалектика, 2005. - 421 с.

10. Шаньгин В.Ф. Информационная безопасность компьютерных систем и сетей / В.Ф.Шаньгин. - М.: ИД «Форум» - ИНФРА-М, 2008. - 415 с.

11. Мухопад Ю.Ф., Мухопад А.Ю., Бадмаева Т.С. Самоконтролируемый автомат управления. Патент на полезную модель РФ №63588 БИ №15. - 2007.

12. Мухопад А.Ю., Мухопад Ю.Ф. Микропрограммный автомат. Патент на полезную модель РФ №82888, БИ №13. - 2009.

13. Угрюмов Е.П. Цифровая схемотехника.- СПб.: БхВ - Питер, 2010. - 797 с.

14. Соловьев В.В. Климович А. Логическое проектирование цифровых схем на ПЛИС.- М.: Горячая Линия - Телеком, 2008. - 375 с.

Устройство криптографической защиты информации, содержащее три элемента «И», постоянное запоминающее устройство, четыре регистра сдвига и два счетчика с триггерами переполнения, отличающееся тем, что в конструкцию устройства встроены дополнительно триггер, второе постоянное запоминающее устройство, блок групповых схем «И», дешифратор, блок схем «ИЛИ», счетчик с триггером переполнения, арифметико-логическое устройство и самоконтролируемый блок синхронизации, причем устройство криптографической защиты информации состоит из последовательных цепей элементов и блоков в виде первой клеммы, связанной через первый элемент И с единичным входом триггера, единичные выходы которого связаны с первыми входами второго и третьего элементов И, выходы которых связаны соответственно с последовательными входами первого и второго регистров сдвига, параллельные выходы которых связаны соответственно со старшими и младшими разделами регистра информационного слова, выход которого связан со входом первого постоянно запоминающего регистра ПЗУ1, соединенного выходом со входом третьего регистра сдвига, нулевой выход старшего разряда которого связан со вторым входом второго элемента И, а единичный выход связан со вторым входом третьего элемента И и первым входом самоконтролируемого блока синхронизации, имеющего также входы от единичных выходов второго, третьего и четвертого триггеров, связанных с выходами переполнения первого, второго и третьего счетчиков соответственно, причем самоконтролируемый блок синхронизации имеет две входных внешних клеммы «Пуск» и «Останов», а вторая последовательная цепь блоков образуется с выхода первого постоянного запоминающего устройства ПЗУ1 через блок схем «И», затем блок схем «ИЛИ», связанных с входом арифметико-логического устройства, связанного с четвертым регистром сдвига, имеющего последовательный вход на клемму и регистр результата, связанного через блок групповых схем И младшими разрядами входов второго постоянного запоминающего устройства ПЗУ2, выходы которого связаны со вторыми входами блока схем ИЛИ, третьи входы которого связаны с выходами регистра информационного слова, причем параллельные выходы первого счетчика связаны старшими разрядами входов второго постоянного запоминающего устройства ПЗУ2 и с входами дешифратора, выхода которого связаны с входами синхронизации соответствующих групп блока групповых схем И, причем выходы самоконтролирующего блока синхронизации C С... Ср связаны со всеми управляющими входами элементов и блоков устройства криптографической защиты информации.