Результат интеллектуальной деятельности: Триггерный асинхронный Т триггер

Вид РИД

Изобретение

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной техники, выполненных с использованием T триггеров, регистров и счётчиков импульсов.

Известен асинхронный Т триггер, выполненный на двухтактном D триггере [1 Гольбенберг Л.М. Импульсные устройства. − М.: Радио и связь, 1981, с. 99, рис. 4.13, б], содержащий пять логических элемента И-НЕ и два R-S триггера (общее количество логических элементов − девять) [1, c. 98, рис. 4.12, б].

Недостаток его заключается в том, что у него малая нагрузочная способность. Внешняя нагрузка подключается к выходу R-S триггера второй ступени двухступенчатого D триггера. В частности, при выполнении этого R-S триггера на логических элементах И-НЕ [1, c. 90, рис. 4.9, в] транзисторно-транзисторного (ТТЛ) варианта [1, c. 41, рис. 2.20] электрический ток внешней нагрузки формирует только один из имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовало больше транзисторов, то это повысило бы силу электрического тока в нагрузке и соответственно повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа триггер с дополнительной симметрией [Гольбенберг Л.М. Импульсные и цифровые устройства. - М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и три источника постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного асинхронного Т триггера.

Это достигается тем, что в триггерный асинхронный Т триггер, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, в первой из имеющихся двух ступеней триггера последовательно включённые первый резистор, первый (n-p-n) транзистор и второй резистор, свободный вывод первого резистора подключён к выходу (плюсовой вывод) источника питающего постоянного напряжения, также в первой ступени триггера последовательно включенные третий резистор, второй (p-n-p) транзистор и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, общий вывод коллектора этого второго транзистора и четвёртого резистора подсоединён к базе первого транзистора, а свободный вывод четвёртого резистора соединён со свободным выводом второго резистора, приведённые выше резисторы и транзисторы также имеются и во второй ступени триггера, и они имеют такое же включение, как и в первой ступени, а именно последовательно между собой включены пятый резистор, третий (n-p-n) транзистор и шестой резистор, свободный вывод пятого резистора подключён к общему выводу первого, третьего резисторов и выхода источника питающего постоянного напряжения, также последовательно между собой включены седьмой резистор, четвёртый (p-n-p) транзистор и восьмой резистор, свободный вывод седьмого резистора подключён к общему выводу первого, третьего, пятого резисторов и выхода источника питающего постоянного напряжения, база четвёртого транзистора соединена с общим выводом пятого резистора и коллектора третьего транзистора, общий вывод коллектора четвёртого транзистора и восьмого резистора подсоединён к базе третьего транзистора, свободный вывод восьмого резистора соединён со свободным выводом шестого резистора, введены двенадцать дополнительных транзисторов и двадцать дополнительных резисторов, последовательно между собой включены первый дополнительный резистор и первый дополнительный (p-n-p) транзистор, свободный вывод первого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, последовательно между собой включены второй дополнительный (n-p-n) транзистор, второй дополнительный резистор, третий дополнительный (n-p-n) транзистор и третий дополнительный резистор, коллектор второго дополнительного транзистора подключён к общему выводу третьего резистора и эмиттера второго транзистора, база второго дополнительного транзистора подсоединена к базе первого дополнительного транзистора, вывод базы третьего дополнительного транзистора образует относительно «земли» информационный вход Т асинхронного триггера, свободный вывод третьего дополнительного резистора заземлён, последовательно включены четвёртый и пятый дополнительные резисторы, свободный вывод четвёртого дополнительного резистора подсоединён к коллектору первого дополнительного транзистора, а свободный вывод пятого дополнительного резистора соединён с общим выводом второго дополнительного резистора и коллектора третьего дополнительного транзистора, последовательно включены четвёртый дополнительный (n-p-n) транзистор и шестой дополнительный резистор, коллектор четвёртого дополнительного транзистора соединён с общим выводом первого резистора, коллектора первого транзистора и базы второго транзистора, свободный вывод шестого дополнительного резистора соединён с общим выводом второго, пятого дополнительных резисторов и коллектора третьего дополнительного транзистора, база четвёртого дополнительного транзистора подключена к общему выводу четвёртого и пятого дополнительных резисторов, последовательно включены пятый дополнительный (n-p-n) транзистор и седьмой дополнительный резистор, коллектор пятого дополнительного транзистора подключён к общему выводу третьего резистора, эмиттера второго транзистора и коллектора второго дополнительного транзистора, вывод базы пятого дополнительного транзистора образует относительно «земли» вход «Сброс 0» установки асинхронного триггера в исходное начальное состояние 0, где уровень выходного напряжения триггера соответствует логическому нулю, свободный вывод седьмого дополнительного резистора заземлён, последовательно включены шестой дополнительный (n-p-n) транзистор и восьмой дополнительный резистор, коллектор шестого дополнительного транзистора соединён с общим выводом первого резистора, базы второго транзистора и коллекторов первого и дополнительного четвёртого транзисторов, вывод базы шестого транзистора образует относительно «земли» вход «Сброс 1» установки асинхронного триггера в исходное начальное состояние 1, где уровень выходного напряжения триггера соответствует логической единице, свободный вывод восьмого дополнительного резистора заземлён, девятый дополнительный резистор включён между «землёй» и общим выводом второго и четвёртого резисторов, общий вывод последних трёх резисторов образует относительно «земли» выход q первой ступени асинхронного триггера, последовательно включены десятый дополнительный резистор, седьмой дополнительный (p-n-p) транзистор, одиннадцатый и двенадцатый дополнительные резисторы, свободный вывод десятого дополнительного резистора подключён к выходу источника питающего постоянного напряжения, база седьмого дополнительного транзистора подсоединена к информационному входу T асинхронного триггера, свободный вывод двенадцатого дополнительного резистора заземлён, последовательно включены тринадцатый дополнительный резистор и восьмой дополнительный (p-n-p) транзистор, свободный вывод тринадцатого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база восьмого дополнительного транзистора соединена с выходом q первой ступени асинхронного триггера, последовательно включены девятый дополнительный (n-p-n) транзистор, четырнадцатый дополнительный резистор, десятый дополнительный (n-p-n) транзистор и пятнадцатый дополнительный резистор, коллектор девятого дополнительного транзистора подключён к общему выводу пятого резистора, коллектора третьего транзистора, и базы четвёртого транзистора, база девятого дополнительного транзистора соединена с выходом q первой ступени асинхронного триггера, база десятого дополнительного транзистора подсоединена к общему выводу одиннадцатого и двенадцатого дополнительных резисторов, свободный вывод пятнадцатого дополнительного резистора заземлён, последовательно включены шестнадцатый и семнадцатый дополнительные резисторы, свободный вывод шестнадцатого дополнительного резистора подключён к коллектору восьмого дополнительного транзистора, свободный вывод семнадцатого дополнительного резистора соединён с общим выводом коллектора десятого дополнительного транзистора и четырнадцатого дополнительного резистора, последовательно включены одиннадцатый дополнительный (n-p-n) транзистор и восемнадцатый дополнительный резистор, коллектор одиннадцатого дополнительного транзистора соединён с общим выводом седьмого резистора и эмиттера четвёртого транзистора, база одиннадцатого дополнительного транзистора подсоединена к общему выводу шестнадцатого и семнадцатого дополнительных резисторов, свободный вывод восемнадцатого дополнительного резистора соединён с общим выводом коллектора десятого дополнительного транзистора, четырнадцатого и семнадцатого дополнительных резисторов, последовательно включены девятнадцатый и двадцатый дополнительные резисторы, свободный вывод девятнадцатого резистора соединён с общим выводом эмиттера одиннадцатого дополнительного транзистора и восемнадцатого дополнительного резистора, свободный вывод двадцатого дополнительного резистора заземлён, двенадцатый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом шестого и восьмого резисторов, общий вывод коллектора этого транзистора, шестого и восьмого резисторов образует относительно «земли» выход Q асинхронного триггера, этот выход соединён также с общим выводом баз первого и второго дополнительных транзисторов, база двенадцатого дополнительного транзистора подключена к общему выводу девятнадцатого и двадцатого дополнительных резисторов.

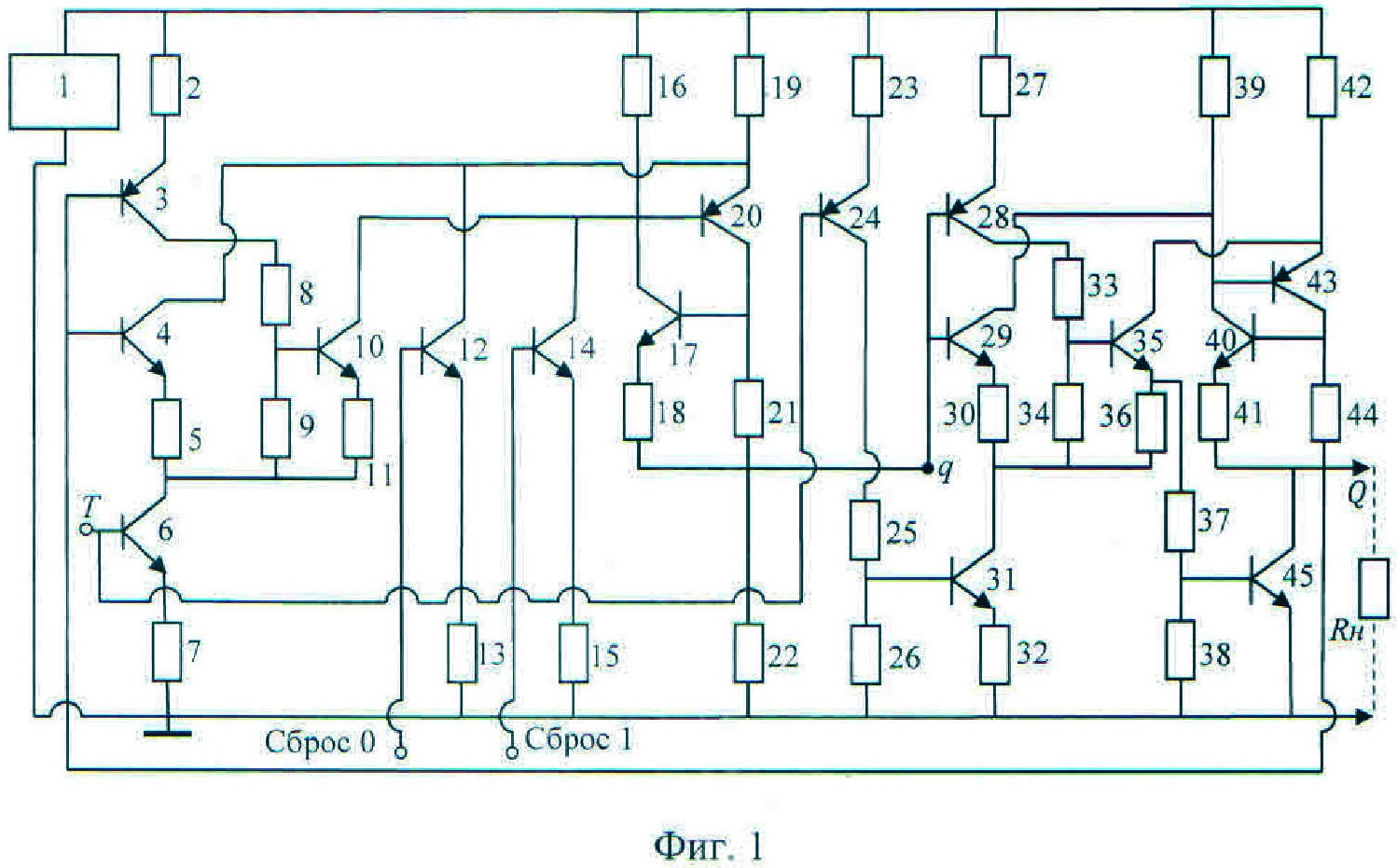

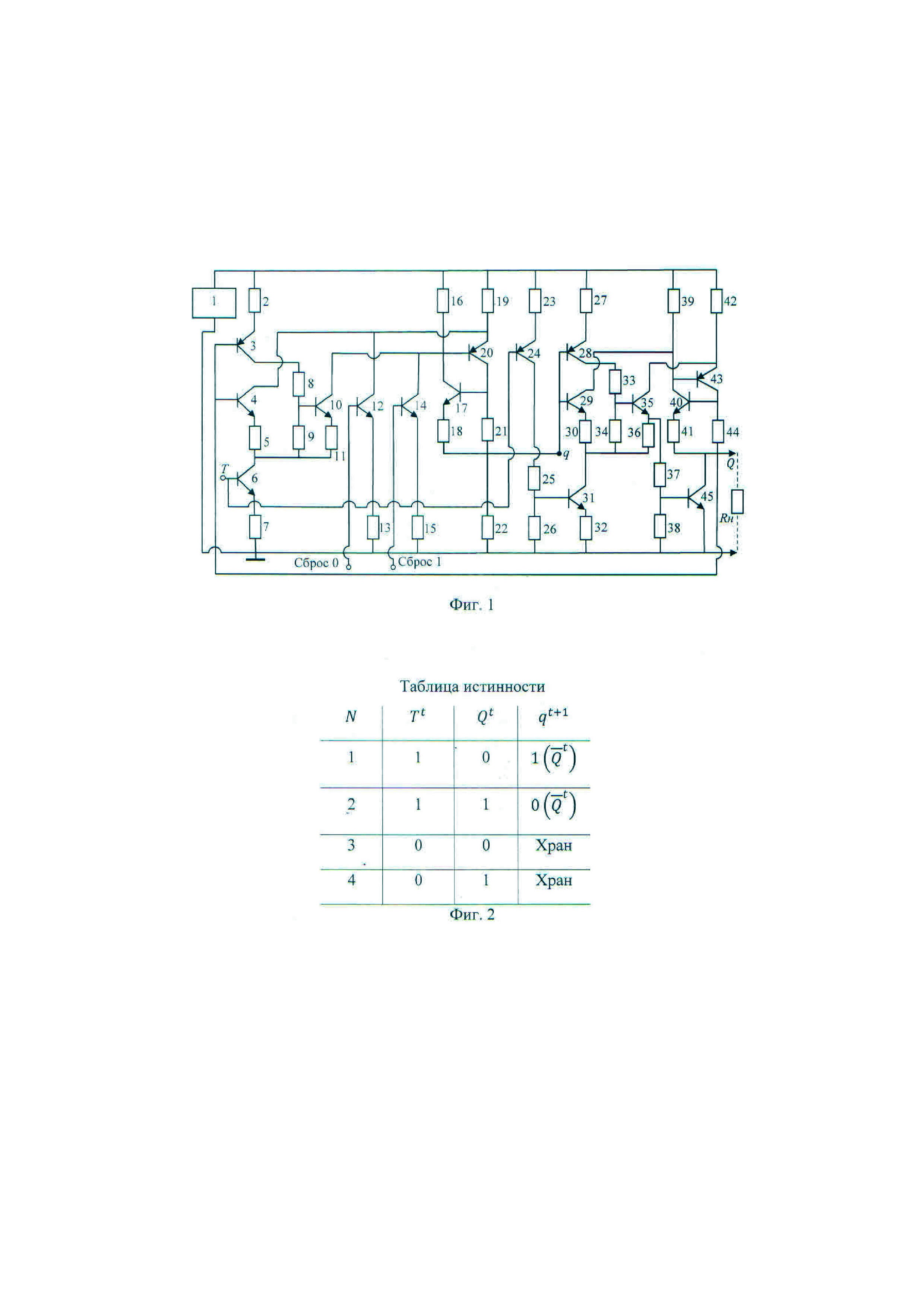

Сущность изобретения поясняется схемой триггерного асинхронного Т триггера (фиг. 1) и для первой ступени асинхронного триггера таблицей истинности (фиг. 2).

В триггерном асинхронном Т триггере общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. Последовательно между собой включены резистор 2 и p-n-p транзистор 3. Свободный вывод резистора 2 подключен к выходу (плюсовой вывод) источника 1. Последовательно между собой включены n-p-n транзистор 4, резистор 5, n-p-n транзистор 6 и резистор 7. База транзистора 4 подключена к базе транзистора 3. Вывод базы транзистора 6 образует относительно «земли» информационный вход T. Свободный вывод резистора 7 заземлен. Последовательно включены резисторы 8 и 9. Свободный вывод резистора 8 подключён к коллектору транзистора 3. Свободный вывод резистора 9 соединён с общим выводом резистора 5 и коллектора транзистора 6. Последовательно включены n-p-n транзистор 10 и резистор 11. База транзистора 10 подключена к общему выводу резисторов 8 и 9, а свободный вывод резистора 11 соединён с общим выводом резисторов 5, 9 и коллектора транзистора 6.

Последовательно включены n-p-n транзистор 12 и резистор 13. Коллектор транзистора 12 подключён к коллектору транзистора 4. Вывод базы транзистора 12 образует относительно «земли» вход «Сброс 0» установки асинхронного триггера перед началом работы в исходное (начальное) состояние 0 (уровень выходного напряжения соответствует уровню логического нуля). Свободный вывод резистора 13 заземлён. Последовательно включены n-p-n транзистор 14 и резистор 15. Коллектор транзистора 14 подключён к коллектору транзистора 10. Вывод базы транзистора 14 образует относительно «земли» вход «Сброс 1» установки асинхронного триггера перед началом работы в исходное (начальное) состояние 1 (уровень выходного напряжения соответствует уровню логической единице). Свободный вывод резистора 15 заземлён.

Последовательно включены резистор 16, n-p-n транзистор 17 и резистор 18. Свободный вывод резистора 16 подключён к выходу источника 1. Общий вывод этого резистора и коллектора транзистора 17 подключён к общему выводу коллекторов транзисторов 10 и 14. Последовательно включены резистор 19, p-n-p транзистор 20 и резистор 21. Свободный вывод резистора 19 подключён к выходу источника 1. Общий вывод этого резистора и эмиттера транзистора 20 подключён к общему выводу коллекторов транзисторов 4 и 12. База транзистора 20 подсоединена к общему выводу резистора 16 и коллекторов транзисторов 10, 14, и 17.Общий вывод резистора 21 и коллектора транзистора 20 соединён с базой транзистора 17. Свободный вывод резистора 21 подключён к свободному выводу резистора 18. Часть схемы на фиг. 1 на транзисторах 17, 20 и резисторах 16, 18, 19, 21 является триггером на транзисторах противоположного типа проводимости. Резистор 22 включён между «землёй» и общим выводом резисторов 18 и 21. Общий вывод последних трёх резисторов образует относительно «земли» выход первой ступени асинхронного триггера и обозначен q.

Последовательно включены резистор 23, p-n-p транзистор 24, резисторы 25 и 26. Свободный вывод резистора 23 подключён к выходу источника 1. База транзистора 24 соединена со входом T асинхронного триггера, а свободный вывод резистора 26 заземлён.

Последовательно включены резистор 27 и p-n-p транзистор 28. Свободный вывод резистора 27 подключён к выходу источника 1. База транзистора 28 соединена с выходом q первой ступени асинхронного триггера. Последовательно включены n-p-n транзистор 29, резистор 30, n-p-n транзистор 31 и резистор 32. База транзистора 29 подключена к общему выводу базы транзистора 28 и выхода q первой ступени асинхронного триггера. База транзистора 31 соединена с общим выводом резисторов 25 и 26, а свободный вывод резистора 32 заземлён. Последовательно включены транзисторы 33 и 34. Свободный вывод резистора 33 подключён к коллектору транзистора 28, свободный вывод резистора 34 соединён с общим выводом резистора 30 и коллектора транзистора 31. Последовательно включены n-p-n транзистор 35 и резистор 36. База транзистора 35 подключена к общему выводу резисторов 33 и 34. Свободный вывод резистора 36 соединён с общим выводом резисторов 30, 34 и коллектора транзистора 31. Последовательно включены резисторы 37 и 38. Свободный вывод резистора 37 подключён к общему выводу эмиттера транзистора 35 и резистора 36, а свободный вывод резистора 38 заземлён.

Последовательно включены резистор 39, n-p-n транзистор 40 и резистор 41. Свободный вывод резистора 39 подключён к выходу источника 1. Общий вывод этого резистора и коллектора транзистора 40 соединён с коллектором транзистора 29. Последовательно включены резисторов 42, p-n-p транзистор 43 и резистор 44. Свободный вывод резистора 42 подключён к выходу источника 1. Общий вывод этого резистора и эмиттера транзистора 43 подключён к коллектору транзистора 35. База транзистора 43 подсоединена к общему выводу резистора 39 и коллекторов транзисторов 29 и 40. Общий вывод коллектора транзистора 43 и резистора 44 соединён с базой транзистора 40. Свободный вывод резистора 44 подключён к свободному выводу резистора 41. Схема на транзисторах 40, 43 и резисторах 39, 41, 42, и 44 представляет собой ещё один (второй) триггер на транзисторах противоположного типа проводимости.

Коллектор n-p-n транзистора 45 соединён с общим выводом резисторов 41, 44 и общий вывод последних трёх элементов образует относительно «земли» выход Q асинхронного триггера. База транзистора 45 подключена к общему выводу резисторов 37 и 38, а эмиттер его - заземлён. Выход асинхронного триггера также соединён с общим выводом баз транзисторов 3 и 4. Приведённый пунктирными линиями резистор Rн условно отображает внешнюю нагрузку асинхронного триггера.

Триггерный асинхронный Т триггер работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень − уровень логического нуля соответствует значениям напряжения в районе нуля или в районе ближе к нулю, высокий уровень − уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт).

Работа первой ступени триггерного асинхронного T триггера отображается таблицей истинности (фиг. 2), где − номер строки по порядку,

− номер строки по порядку,  − условное отображение входного сигнала в данный момент времени t,

− условное отображение входного сигнала в данный момент времени t, − условное отображения выходного сигнала асинхронного триггера тоже в данный момент времени t и

− условное отображения выходного сигнала асинхронного триггера тоже в данный момент времени t и  − условное отображения выходного сигнала первой ступени асинхронного триггера в последующее время (состояние на его выходе).

− условное отображения выходного сигнала первой ступени асинхронного триггера в последующее время (состояние на его выходе).

Триггер на транзисторах 17, 20 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 16 и 21 нулевые значения напряжения. Они прикладываются к базам транзисторов 17 и 20, меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 17, 20 открыты, их электрические токи создают напряжения в том числе на резисторах 16 и 21 больше по абсолютной величине и по значениям пороговых напряжений транзисторов и поддерживают транзисторы 17, 20 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера. Точно так же работает второй триггер на транзисторах 40 и 43 противоположного типа проводимости,

После установки асинхронного триггера в исходное (начальное) состояние на его первую ступень поступают следующие сигналы: на входе «Сброс 0» и «Сброс 1» - уровень логического нуля, на вход T - уровни или логического нуля, или единицы, на общий вывод баз транзисторов 3 и 4 - тоже уровни или нуля, или единицы с выхода Q асинхронного триггера. При названных сигналах на входах состояния транзисторов 12 и 14 в районе порогового напряжения и возможные весьма малые значения силы электрических токов этих транзисторов не могут создать на резисторах 16 и 19 достаточные напряжения для изменения состояния триггера на транзисторах 17, 20 противоположного типа проводимости.Для первой ступени асинхронного триггера в соответствии с первой строкой таблицы истинности (фиг. 2) с выхода Q на базы транзисторов 3 и 4 поступает низкий уровень напряжения - уровень логического нуля, на базу транзистора 6 воздействует высокий уровень напряжения и обеспечивает его проводящее электрический ток состояние. Тогда состояние n-p-n транзистора 4 в районе его порогового напряжения и возможное весьма малое значение силы его коллекторного тока не может создать на резисторе 19 напряжение, достаточное для изменения состояния триггера на транзисторах 17, 20 и не влияет на его состояние. При напряжении на базе p-n-p транзистора 3 уровня логического нуля (первая строка таблицы истинности на фиг. 2) повышенную силу имеют электрические токи базы и коллектора транзистора 3 и базы и коллектора транзистора 10, которые замыкаются на «землю» через транзистор 6 в проводящем электрический ток состоянии. Тогда напряжение на резисторе 16 имеет повышенное значение, превышает порог срабатывания триггера на транзисторах 17, 20 и переводит его во второе состояние. Электрические токи последних двух транзисторов создают на выходе q первой ступени асинхронного триггера высокий уровень напряжения - уровень логической единицы.

В соответствии со второй строкой таблицы истинности (фиг. 2) с выхода Q на базы транзисторов 3 и 4 поступает высокий уровень напряжения. При этом пониженное значение силы имеют электрические токи базы и коллектора транзистора 3, соответственно токи базы и коллектора транзистора 10. На резисторе 16 малое значение напряжения, меньше напряжения порога срабатывания триггера на транзисторах 17, 20. Высокий уровень напряжения на базе транзистора 4 вызывает повышенное значение силы коллекторного тока транзистора 4, который замыкается на «землю» через транзистор 6 в проводящем электрический ток состоянии, и повышенное значение падения напряжения на резисторе 19. Последнее напряжение превышает напряжение порога срабатывания триггера на транзисторах 17, 20 по абсолютной величине и переводит этот триггер в первое состояние. Тогда на выходе q первой ступени асинхронного триггера имеется напряжение уровня логического нуля (фиг. 2).

При наличии высокого уровня напряжения на входе T (первые две строки таблицы истинности на фиг. 2) имеются пониженные значения силы электрических токов базы и коллектора p-n-p транзистора 24, что позволяет обеспечивать напряжение на базе транзистора 31 в районе его порогового напряжения. Тогда сила электрических токов через транзистор 31 и соответственно через транзисторы 29 и 35 могут иметь только малые значения, настолько малые, что возможные значения напряжений на резисторах 39 и 42 меньше напряжений порога срабатывания триггера на транзисторах 40, 43 противоположного типа проводимости. В итоге изменения состояния первой ступени асинхронного триггера при уровне напряжения логической единицы на входе T не вызывает изменение состояния второй его ступени, т.е. не влияет на состояние второй ступени и на изменение напряжения на выходе Q.

При наличии низкого уровня напряжения на входе T (третья и четвёртая строки таблицы истинности на фиг. 2) состояние транзистора 6 находится в районе его порогового напряжения. Тогда аналогично положениям предыдущего абзаца сила электрических токов через транзистор 6 и соответственно через транзисторы 4 и 10 могут иметь только малые значения, настолько малые, что возможные значения напряжений на резисторах 16, 19 меньше напряжений порога срабатывания триггера на транзисторах 17 и 20. В итоге состояние первой ступени асинхронного триггера не изменяется при любых сигналах с выхода Q (ноль или единица). Т.е. в первой ступени хранится ранее имевшаяся информация (ноль или единица). Низкий уровень напряжения на входе T вызывает повышенные значения силы электрических токов базы и коллектора p-n-p транзистора 24 и соответственно напряжения на базе транзистора 31, и он (этот транзистор) проводит электрический ток. Тогда информация с первой ступени асинхронного триггера перезаписывается в его вторую ступень.

При низком уровне напряжения на выходе q первой ступени асинхронного триггера оно имеется на базах транзисторов 28, 29. При таком напряжении состояние транзистора 29 находится в районе его порогового напряжения, сила его электрического тока мала, напряжение от него на резисторе 39 тоже мало, меньше напряжения порога срабатывания триггера на транзисторах 40, 43 и в итоге не влияет на его состояние. Но низкий уровень на выходе q вызывает повышенное значение силы электрических токов p-n-p транзистора 28, соответственно транзистора 35 и в итоге напряжения на резисторе 42. Последнее превышает напряжение порога срабатывания триггера на транзисторах 40, 43 по абсолютной величине и переводит триггер в первое состояние. В итоге на выходе Q асинхронного триггера имеется напряжение уровня логического нуля. Электрические токи транзисторов 28, 29 и 35 замыкаются на землю через транзистор 31, который проводит электрический ток (в открытом состоянии). С общего вывода эмиттера транзистора 35 и резистора 36 через делитель на резисторах 37, 38 на базу транзистора 45 подаётся напряжение, поддерживающее его проводящее электрический ток состояние. Ранее паразитная ёмкость (сумма входной ёмкости нагрузки и выходной ёмкости асинхронного триггера) заряжена до напряжения уровня логической единицы. Теперь эта ёмкость разряжается, и длительность её разряда уменьшает быстродействие асинхронного триггера. Наличие транзистора 45 в проводящем электрический ток состоянии уменьшает постоянную времени разряда паразитной ёмкости, время её разряда и тем самым ослабляет уменьшение быстродействия асинхронного триггера.

При высоком уровне напряжения на выходе q первой ступени асинхронного триггера состояние p-n-p транзистора 28 находится в районе его порогового напряжения. Сила электрического тока этого транзистора и соответственно транзистора 35 имеет пониженное значение. Тогда напряжение на резисторе 42 за счёт коллекторного тока транзистора 35 имеет малое значение, меньше напряжения порога срабатывания триггера на транзисторах 40, 43 и не влияет на состояние этого триггера. Напряжение относительно «земли» на общем выводе эмиттера транзистора 35 и резистора 36 существенно меньше по сравнению с аналогичным положением в предыдущем абзаце, что позволяет получить состояние транзистора 45 в районе его порогового напряжения и малое значение силы его коллекторного тока. Высокий уровень напряжения на выходе q вызывает повышенную силу электрического тока транзистора 29 и напряжение на резисторе 39, превышающее по абсолютной величине напряжение порога срабатывания триггера на транзисторах 40, 43. Это переводит названный триггер во второе состояние, и электрические токи его двух транзисторов создают на выходе Q напряжение уровня логической единицы. До этого напряжения заряжается ранее упомянутая паразитная ёмкость. Электрические токи транзисторов 28, 29 и 35 по-прежнему замыкаются на землю через открытый транзисторов 31.

В итоге после окончания импульса на входе T (это напряжение становится низким - уровня логического нуля) при низком напряжении на выходе q первой ступени асинхронного триггера на выходе Q тоже устанавливается напряжение уровня логического нуля, при напряжении уровня логической единицы на выходе q - на выходе асинхронного триггера Q тоже напряжение уровня логической единицы. В соответствии с первой строкой таблицы истинности (фиг. 2) при Tt-1 и Qt-0 на выходе первой ступени триггера qt+1-1 и этот уровень напряжения перезаписывается во вторую ступень после окончания входного импульса (T-0), т.е. на выходе теперь  , что соответствует работе T триггера. Такой же результат получается в соответствии со второй строкой таблицы истинности, т.е. тоже

, что соответствует работе T триггера. Такой же результат получается в соответствии со второй строкой таблицы истинности, т.е. тоже

(фиг. 2).

(фиг. 2).

Для установки триггерного асинхронного T триггера перед началом работы в требующееся исходное (начальное) состояние используются входы: «Сброс 0» и «Сброс 1». При отсутствии сигнала на входе T (T-0) и поступлении напряжения уровня логической единицы на вход «Сброс 0» транзистор 12 проводит электрический ток, который на резисторе 19 создаёт напряжение достаточное для перевода триггера на транзисторах 17, 20 в первое состояние. В результате на выходе q напряжение уровня логического нуля. При поступлении напряжения уровня логической единицы на вход «Сброс 1» транзистор 14, проводит электрический ток. Сила этого тока достаточна для получения такого напряжения на резисторе 16, которое переводит триггер на транзисторах противоположного типа проводимости во второе состояние. В итоге на выходе q напряжение уровня логической единицы. При напряжении уровня логического нуля на входах «Сброс 0», «Сброс 1» и T имеем уже изложенную выше ситуацию, где информация из первой ступени двухступенчатого триггера перезаписывается в его вторую ступень и появляется на выходе Q. Тогда здесь отпадает необходимость в использовании дополнительных элементов для установки второй ступени и в итоге всего триггера в исходное начальное состояние.

Таким образом, в рассмотренном триггерном асинхронном T триггере сила электрического тока внешней нагрузки почти равна сумме силы токов двух транзисторов 40 и 43, а не одного транзистора, как в известных решениях, что повышает нагрузочную способность триггера.

Можно обратить внимание, что приведённая схема (фиг. 1). существенно (значительно) упрощает и удешевляет асинхронный триггер. В ней 44 элемента (16 транзисторов и 28 резисторов), а, например, в приведённом аналоге на транзисторно-транзисторных логических элементах имеется 81 элемент (36 транзисторов, 9 диодов и 36 резисторов). Отсутствие в схеме такого большого количества элементов значительно уменьшает число соединений этих элементов и соответственно количество технологических операций для их реализации, упрощает конструирование схемы и уменьшает её габаритные размеры. Всё это тоже удешевляет триггерный асинхронный T триггер.

Триггерный асинхронный T триггер, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, в первой из имеющихся двух ступеней триггера последовательно включённые первый резистор, первый (n-p-n) транзистор и второй резистор, свободный вывод первого резистора подключён к выходу (плюсовой вывод) источника питающего постоянного напряжения, также в первой ступени триггера последовательно включенные третий резистор, второй (p-n-p) транзистор и четвёртый резистор, свободный вывод третьего резистора подключен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, общий вывод коллектора этого второго транзистора и четвёртого резистора подсоединён к базе первого транзистора, а свободный вывод четвёртого резистора соединён со свободным выводом второго резистора, приведённые выше резисторы и транзисторы также имеются и во второй ступени триггера, и они имеют такое же включение, как и в первой ступени, а именно последовательно между собой включены пятый резистор, третий (n-p-n) транзистор и шестой резистор, свободный вывод пятого резистора подключён к общему выводу первого, третьего резисторов и выхода источника питающего постоянного напряжения, также последовательно между собой включены седьмой резистор, четвёртый (p-n-p) транзистор и восьмой резистор, свободный вывод седьмого резистора подключён к общему выводу первого, третьего, пятого резисторов и выхода источника питающего постоянного напряжения, база четвёртого транзистора соединена с общим выводом пятого резистора и коллектора третьего транзистора, общий вывод коллектора четвёртого транзистора и восьмого резистора подсоединён к базе третьего транзистора, свободный вывод восьмого резистора соединён со свободным выводом шестого резистора, отличающийся тем, что в него введены двенадцать дополнительных транзисторов и двадцать дополнительных резисторов, последовательно между собой включены первый дополнительный резистор и первый дополнительный (p-n-p) транзистор, свободный вывод первого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, последовательно между собой включены второй дополнительный (n-p-n) транзистор, второй дополнительный резистор, третий дополнительный (n-p-n) транзистор и третий дополнительный резистор, коллектор второго дополнительного транзистора подключён к общему выводу третьего резистора и эмиттера второго транзистора, база второго дополнительного транзистора подсоединена к базе первого дополнительного транзистора, вывод базы третьего дополнительного транзистора образует относительно «земли» информационный вход Т асинхронного триггера, свободный вывод третьего дополнительного резистора заземлён, последовательно включены четвёртый и пятый дополнительные резисторы, свободный вывод четвёртого дополнительного резистора подсоединён к коллектору первого дополнительного транзистора, а свободный вывод пятого дополнительного резистора соединён с общим выводом второго дополнительного резистора и коллектора третьего дополнительного транзистора, последовательно включены четвёртый дополнительный (n-p-n) транзистор и шестой дополнительный резистор, коллектор четвёртого дополнительного транзистора соединён с общим выводом первого резистора, коллектора первого транзистора и базы второго транзистора, свободный вывод шестого дополнительного резистора соединён с общим выводом второго, пятого дополнительных резисторов и коллектора третьего дополнительного транзистора, база четвёртого дополнительного транзистора подключена к общему выводу четвёртого и пятого дополнительных резисторов, последовательно включены пятый дополнительный (n-p-n) транзистор и седьмой дополнительный резистор, коллектор пятого дополнительного транзистора подключён к общему выводу третьего резистора, эмиттера второго транзистора и коллектора второго дополнительного транзистора, вывод базы пятого дополнительного транзистора образует относительно «земли» вход «Сброс 0» установки асинхронного триггера в исходное начальное состояние 0, где уровень выходного напряжения триггера соответствует логическому нулю, свободный вывод седьмого дополнительного резистора заземлён, последовательно включены шестой дополнительный (n-p-n) транзистор и восьмой дополнительный резистор, коллектор шестого дополнительного транзистора соединён с общим выводом первого резистора, базы второго транзистора и коллекторов первого и дополнительного четвёртого транзисторов, вывод базы шестого транзистора образует относительно «земли» вход «Сброс 1» установки асинхронного триггера в исходное начальное состояние 1, где уровень выходного напряжения триггера соответствует логической единице, свободный вывод восьмого дополнительного резистора заземлён, девятый дополнительный резистор включён между «землёй» и общим выводом второго и четвёртого резисторов, общий вывод последних трёх резисторов образует относительно «земли» выход q первой ступени асинхронного триггера, последовательно включены десятый дополнительный резистор, седьмой дополнительный (p-n-p) транзистор, одиннадцатый и двенадцатый дополнительные резисторы, свободный вывод десятого дополнительного резистора подключён к выходу источника питающего постоянного напряжения, база седьмого дополнительного транзистора подсоединена к информационному входу T асинхронного триггера, свободный вывод двенадцатого дополнительного резистора заземлён, последовательно включены тринадцатый дополнительный резистор и восьмой дополнительный (p-n-p) транзистор, свободный вывод тринадцатого дополнительного резистора подключен к выходу источника питающего постоянного напряжения, база восьмого дополнительного транзистора соединена с выходом q первой ступени асинхронного триггера, последовательно включены девятый дополнительный (n-p-n) транзистор, четырнадцатый дополнительный резистор, десятый дополнительный (n-p-n) транзистор и пятнадцатый дополнительный резистор, коллектор девятого дополнительного транзистора подключён к общему выводу пятого резистора, коллектора третьего транзистора и базы четвёртого транзистора, база девятого дополнительного транзистора соединена с выходом q первой ступени асинхронного триггера, база десятого дополнительного транзистора подсоединена к общему выводу одиннадцатого и двенадцатого дополнительных резисторов, свободный вывод пятнадцатого дополнительного резистора заземлён, последовательно включены шестнадцатый и семнадцатый дополнительные резисторы, свободный вывод шестнадцатого дополнительного резистора подключён к коллектору восьмого дополнительного транзистора, свободный вывод семнадцатого дополнительного резистора соединён с общим выводом коллектора десятого дополнительного транзистора и четырнадцатого дополнительного резистора, последовательно включены одиннадцатый дополнительный (n-p-n) транзистор и восемнадцатый дополнительный резистор, коллектор одиннадцатого дополнительного транзистора соединён с общим выводом седьмого резистора и эмиттера четвёртого транзистора, база одиннадцатого дополнительного транзистора подсоединена к общему выводу шестнадцатого и семнадцатого дополнительных резисторов, свободный вывод восемнадцатого дополнительного резистора соединён с общим выводом коллектора десятого дополнительного транзистора, четырнадцатого и семнадцатого дополнительных резисторов, последовательно включены девятнадцатый и двадцатый дополнительные резисторы, свободный вывод девятнадцатого резистора соединён с общим выводом эмиттера одиннадцатого дополнительного транзистора и восемнадцатого дополнительного резистора, свободный вывод двадцатого дополнительного резистора заземлён, двенадцатый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом шестого и восьмого резисторов, общий вывод коллектора этого транзистора, шестого и восьмого резисторов образует относительно «земли» выход Q асинхронного триггера, этот выход соединён также с общим выводом баз первого и второго дополнительных транзисторов, база двенадцатого дополнительного транзистора подключена к общему выводу девятнадцатого и двадцатого дополнительных резисторов.