Результат интеллектуальной деятельности: УСТРОЙСТВО И СПОСОБ УСТАНОВЛЕНИЯ ТАКТОВОЙ ЧАСТОТЫ/НАПРЯЖЕНИЯ КЭШ-ПАМЯТИ НА ОСНОВАНИИ ИНФОРМАЦИИ ЗАПРОСА ПАМЯТИ

Вид РИД

Изобретение

ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

[0001] Данная заявка испрашивает приоритет непредварительной патентной заявки США № 15/217,911, поданной 22 июля 2016 г. под названием ʺAPPARATUS AND METHOD FOR SETTING A CLOCK SPEED/VOLTAGE OF CACHE MEMORY BASED ON MEMORY REQUEST INFORMATIONʺ, которая включена в данное описание посредством ссылки, как при воспроизведении в полном объеме.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Настоящее изобретение относится к кэш-памяти и, более конкретно, к установлению тактовой частоты и/или напряжения для кэш-памяти.

УРОВЕНЬ ТЕХНИКИ

[0003] Современные процессоры обычно используют кэш-память для хранения данных с возможностью более быстрого доступа к таким данным, тем самым повышая общую производительность. Такая кэш-память обычно снабжена способностью динамического масштабирования напряжения/частоты (DVFS) для изменения напряжения и/или тактовой частоты, на которых работает кэш-память, в целях энергосбережения. В настоящее время такая способность DVFS часто ограничивается системами, которые масштабируют напряжение/тактовую частоту в неактивном режиме (например, когда запросы памяти не обслуживаются, и т.д.) или просто масштабируют напряжение/тактовую частоту строго на основании тактовой частоты процессора, агента и т.д., который обслуживается.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] Обеспечен способ установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти. В ответ на прием запроса памяти, информация идентифицируется в связи с запросом памяти, с использованием оборудования, которое находится в электрической связи с кэш-памятью. На основании информации, тактовая частота и/или напряжение, по меньшей мере, части кэш-памяти устанавливается с использованием оборудования, которое находится в электрической связи с кэш-памятью.

[0005] Также обеспечено устройство и система для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти. Включена схема, которая выполнена с возможностью идентифицировать информацию в связи с запросом памяти, в ответ на прием запроса памяти. На основании информации, дополнительная схема выполнена с возможностью устанавливать тактовую частоту и/или напряжение, по меньшей мере, части кэш-памяти.

[0006] В первом варианте осуществления, информация может относиться к, по меньшей мере, части по меньшей мере одного процессора, который вызвал запрос памяти. Например, информация может относиться к тактовой частоте и/или напряжению части процессора, который вызвал запрос памяти.

[0007] Во втором варианте осуществления (который может быть или не быть объединен с первым вариантом осуществления), информация может относиться к типу запроса памяти (например, типу чтения, типу когерентности, типу записи, типу упреждающей выборки или типу очистки и т.д.).

[0008] В третьем варианте осуществления (который может быть или не быть объединен с первым и/или вторым вариантами осуществления), информация может относиться к статусу данных, которые являются предметом запроса памяти (например, статусу успеха, статусу неудачи или статусу успеха после неудачи и т.д.).

[0009] В четвертом варианте осуществления (который может быть или не быть объединен с первым, вторым и/или третьим вариантами осуществления), информация может относиться к действию кэш-памяти, которое вызвано запросом памяти (например, действию чтения, действию записи, запросу к внешней памяти, действию очистки или пустому действию и т.д.).

[0010] В пятом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим и/или четвертым вариантами осуществления), информацию можно идентифицировать из поля запроса памяти (например, поля идентификации инициатора запроса, поля типа и т.д.).

[0011] В шестом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым и/или пятым вариантами осуществления) по меньшей мере одно из тактовой частоты или напряжения может устанавливаться как по меньшей мере одно из тактовой частоты или напряжения, по меньшей мере, части по меньшей мере одного процессора, который демонстрирует наибольшую тактовую частоту или напряжение.

[0012] В седьмом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым, пятым и/или шестым вариантами осуществления) по меньшей мере одно из тактовой частоты или напряжения может устанавливаться для поднабора кэш-памяти.

[0013] В восьмом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым, пятым, шестым и/или седьмым вариантами осуществления) по меньшей мере одно из тактовой частоты или напряжения может устанавливаться для всей кэш-памяти.

[0014] В девятом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым, пятым, шестым, седьмым и/или восьмым вариантами осуществления), и тактовая частота, и напряжение могут устанавливаться на основании информации.

[0015] В десятом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и/или девятым вариантами осуществления), оборудование может объединяться с кэш-памятью.

[0016] В одиннадцатом варианте осуществления (который может быть или не быть объединен с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым и/или десятым вариантами осуществления), информацию можно идентифицировать из поля запроса памяти в форме поля идентификации инициатора запроса и/или поля типа.

[0017] Для этого, в некоторых необязательных вариантах осуществления, один или более из вышеприведенных признаков вышеупомянутых устройства, системы и/или способа могут обеспечивать управление тактовой частотой и/или напряжением, когда кэш-память активна, где такое управление может администрироваться с более высокой точностью в результате конкретной информации, которая идентифицируется в связи с запросами активной памяти. Это, в свою очередь, может приводить к улучшению энергосбережения, которое иначе было бы неизбежно в системах, где отсутствует такое точное управление тактовой частотой и/или напряжением. В других вариантах осуществления, производительность также может повышаться. Следует отметить, что вышеупомянутые потенциальные преимущества изложены только в целях иллюстрации и ни в коем случае не в порядке ограничения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

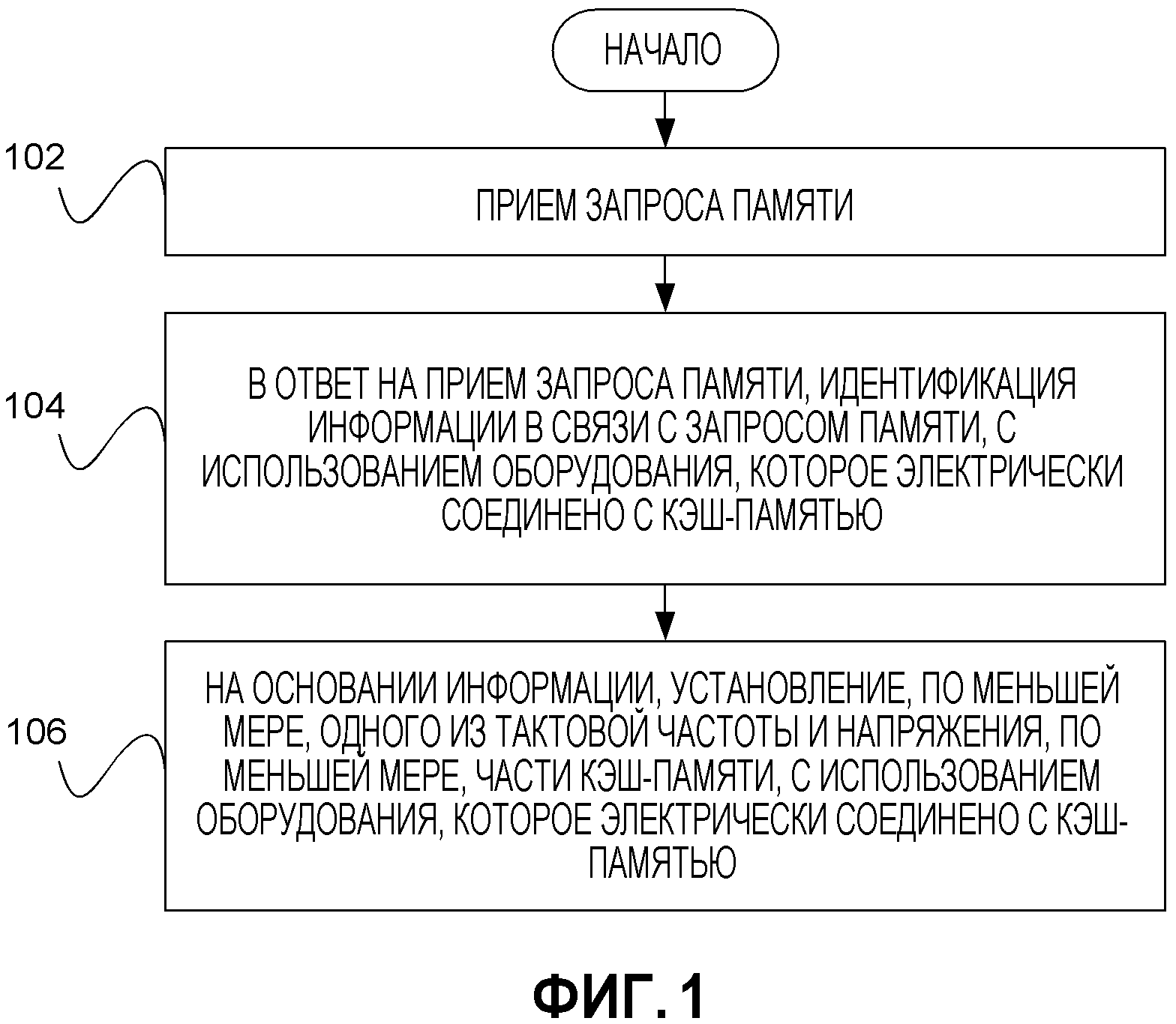

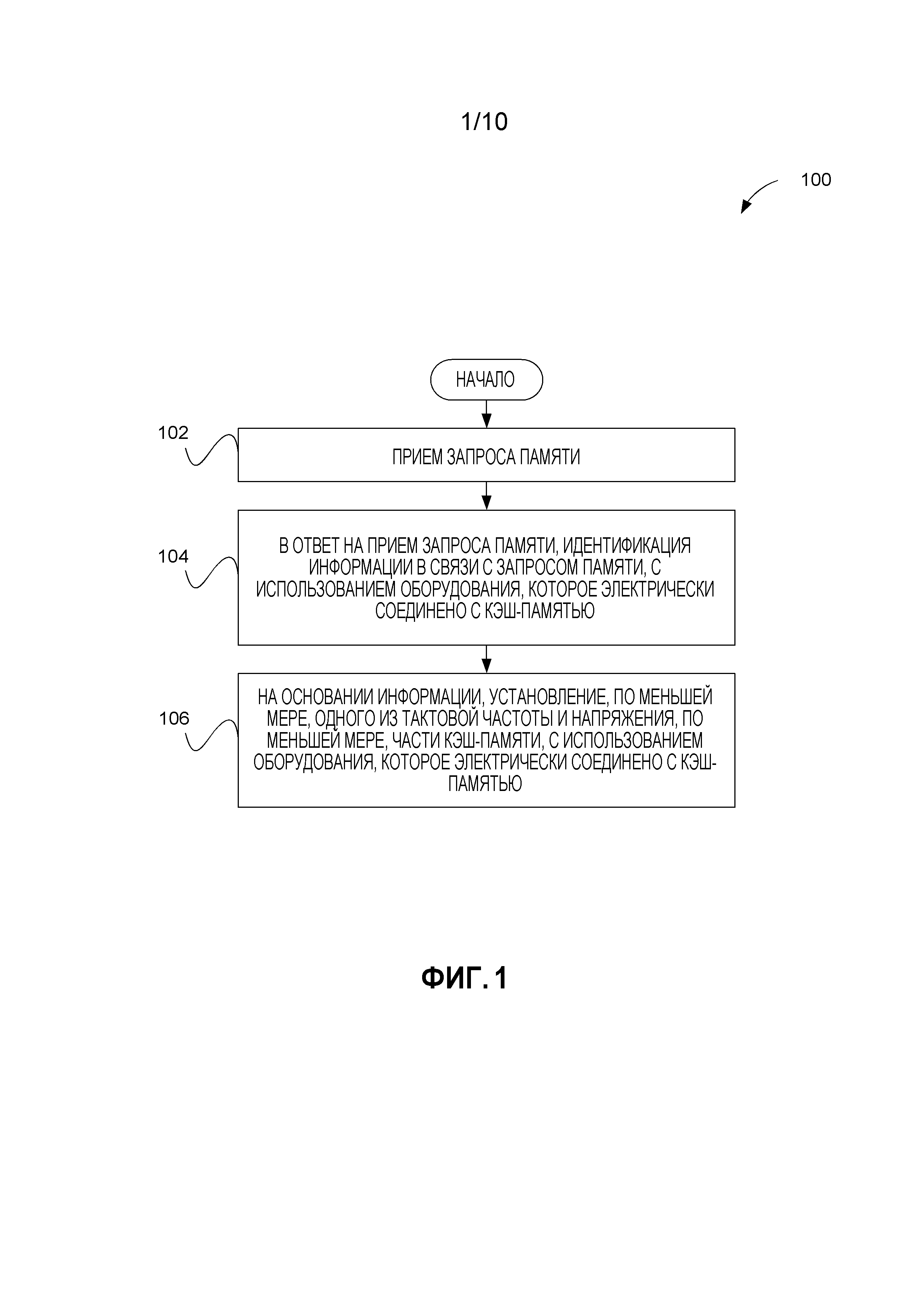

[0018] Фиг. 1 демонстрирует способ установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с одним вариантом осуществления.

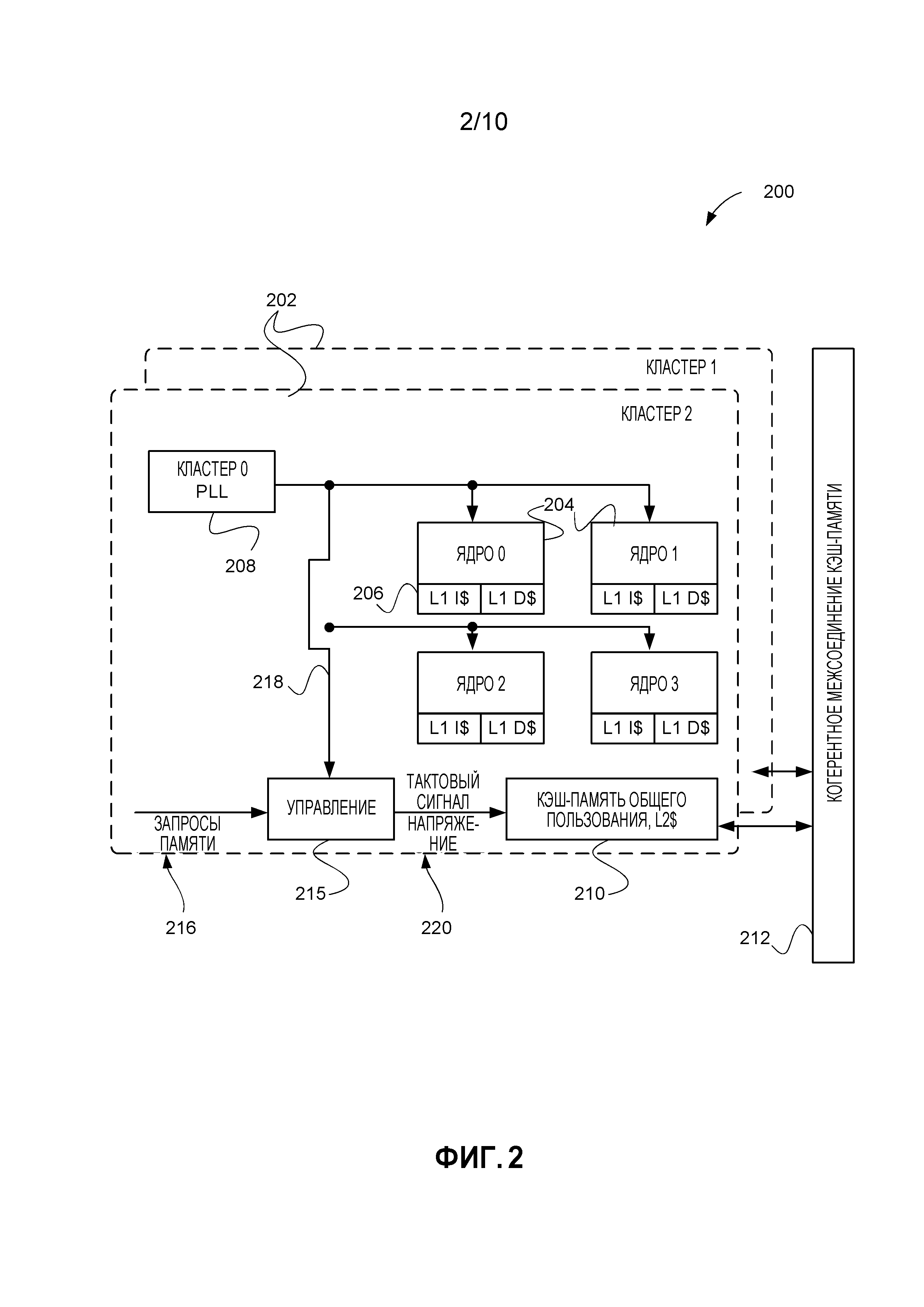

[0019] Фиг. 2 демонстрирует систему для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с другим вариантом осуществления.

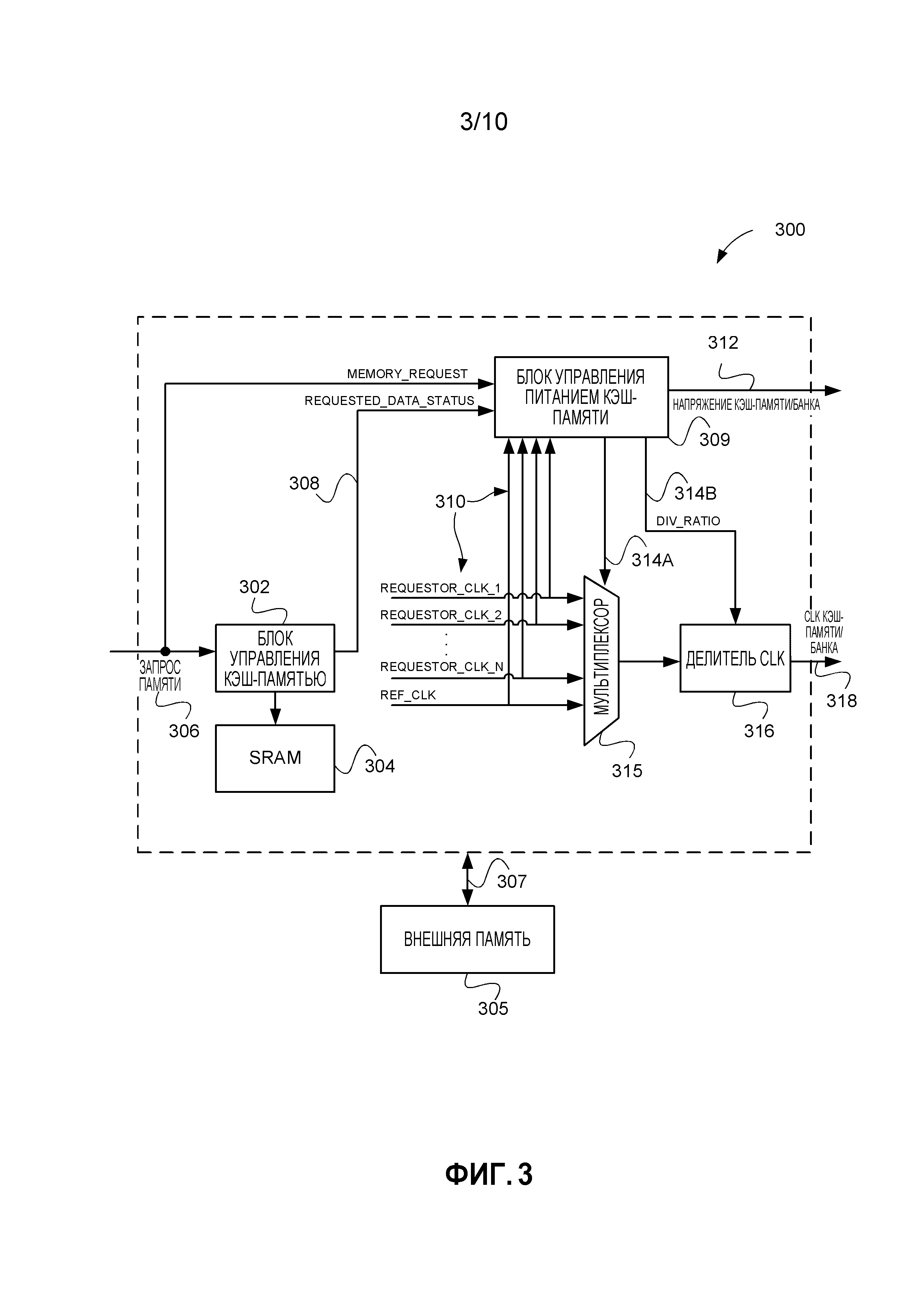

[0020] фиг. 3 демонстрирует контроллер совместной кэш-памяти для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления.

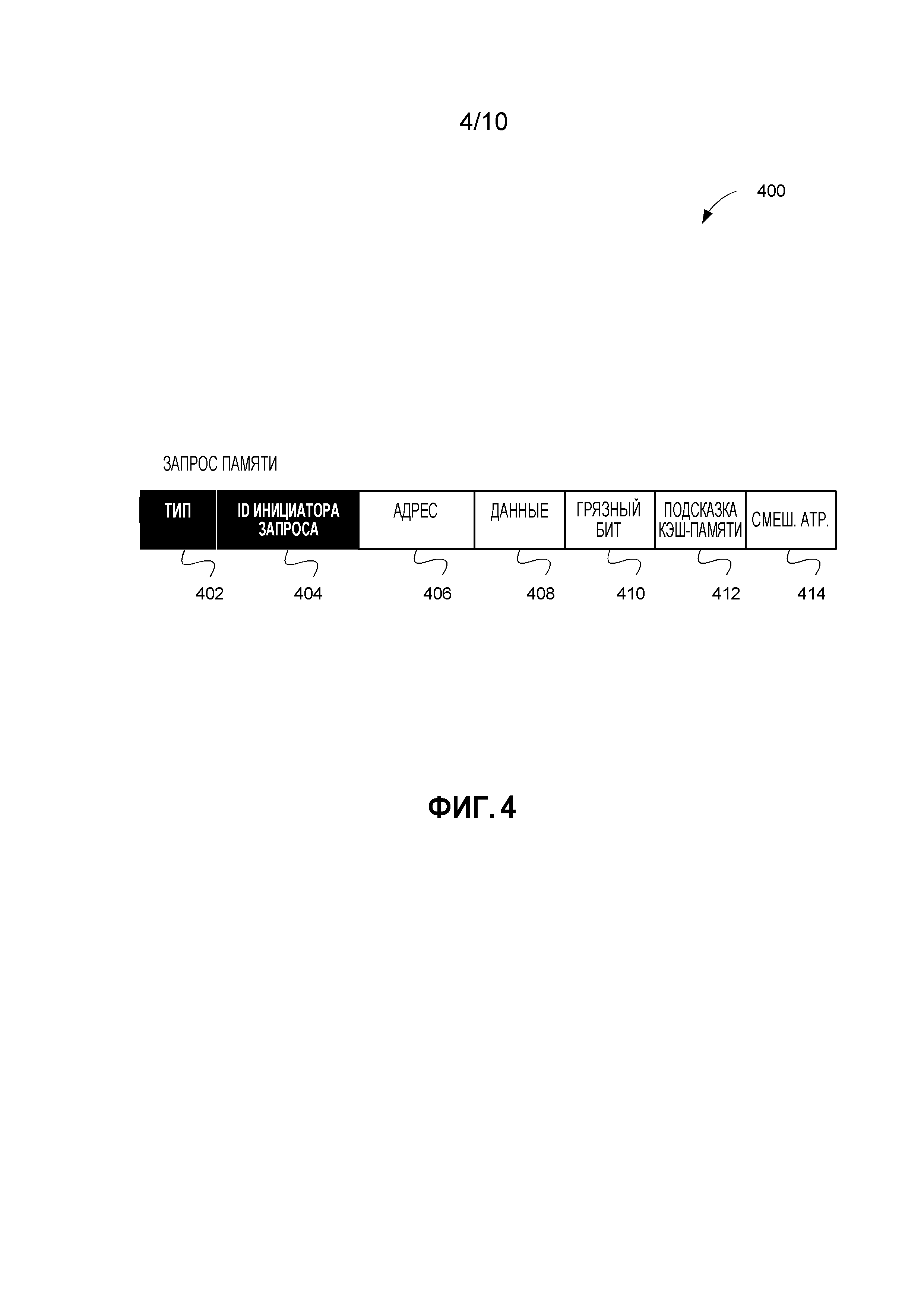

[0021] Фиг. 4 демонстрирует образцовый запрос памяти с информацией, которую можно использовать для установления тактовой частоты/напряжения кэш-памяти, в соответствии с еще одним вариантом осуществления.

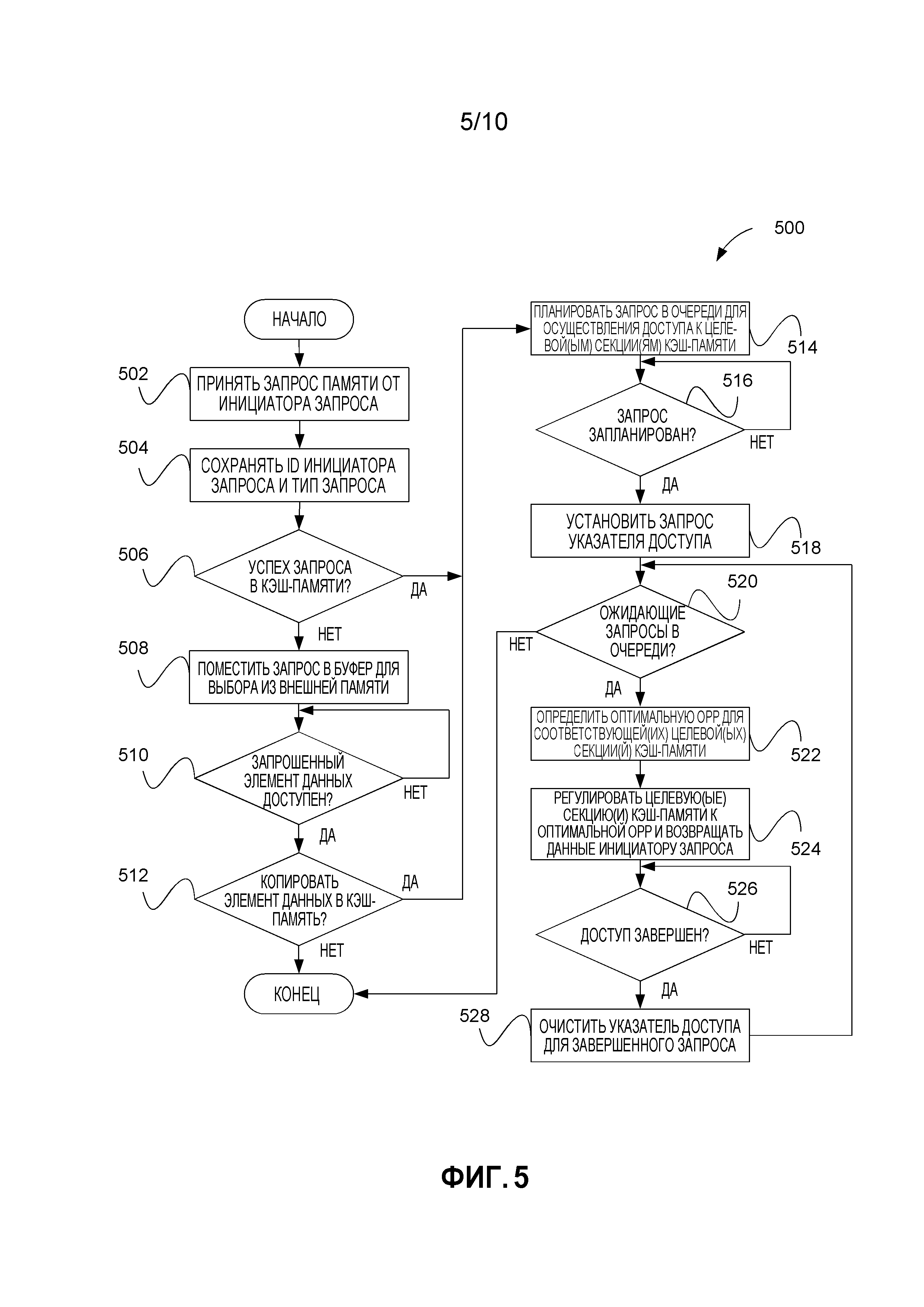

[0022] Фиг. 5 демонстрирует способ установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления.

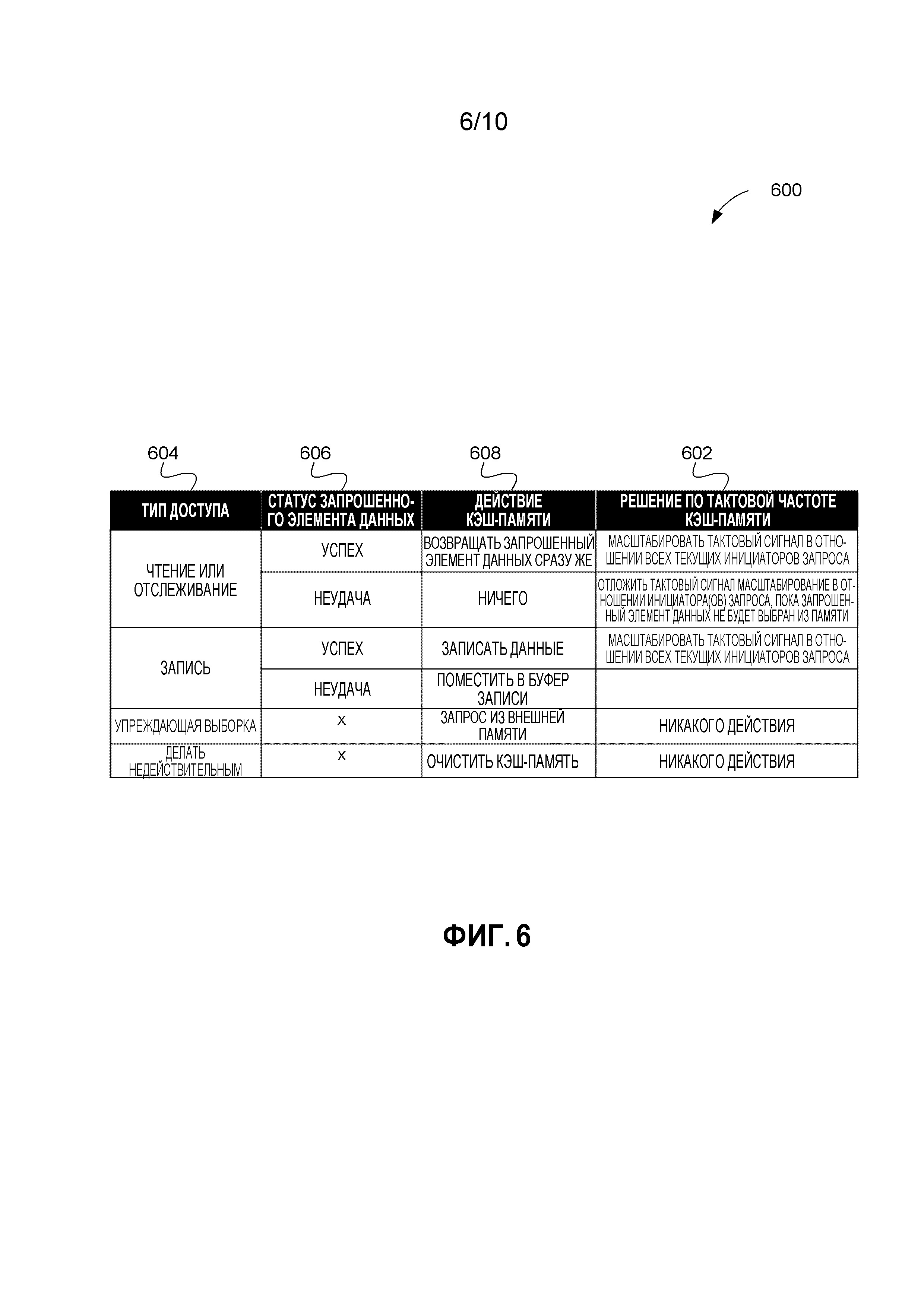

[0023] Фиг. 6 демонстрирует дополнительные вариации для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления.

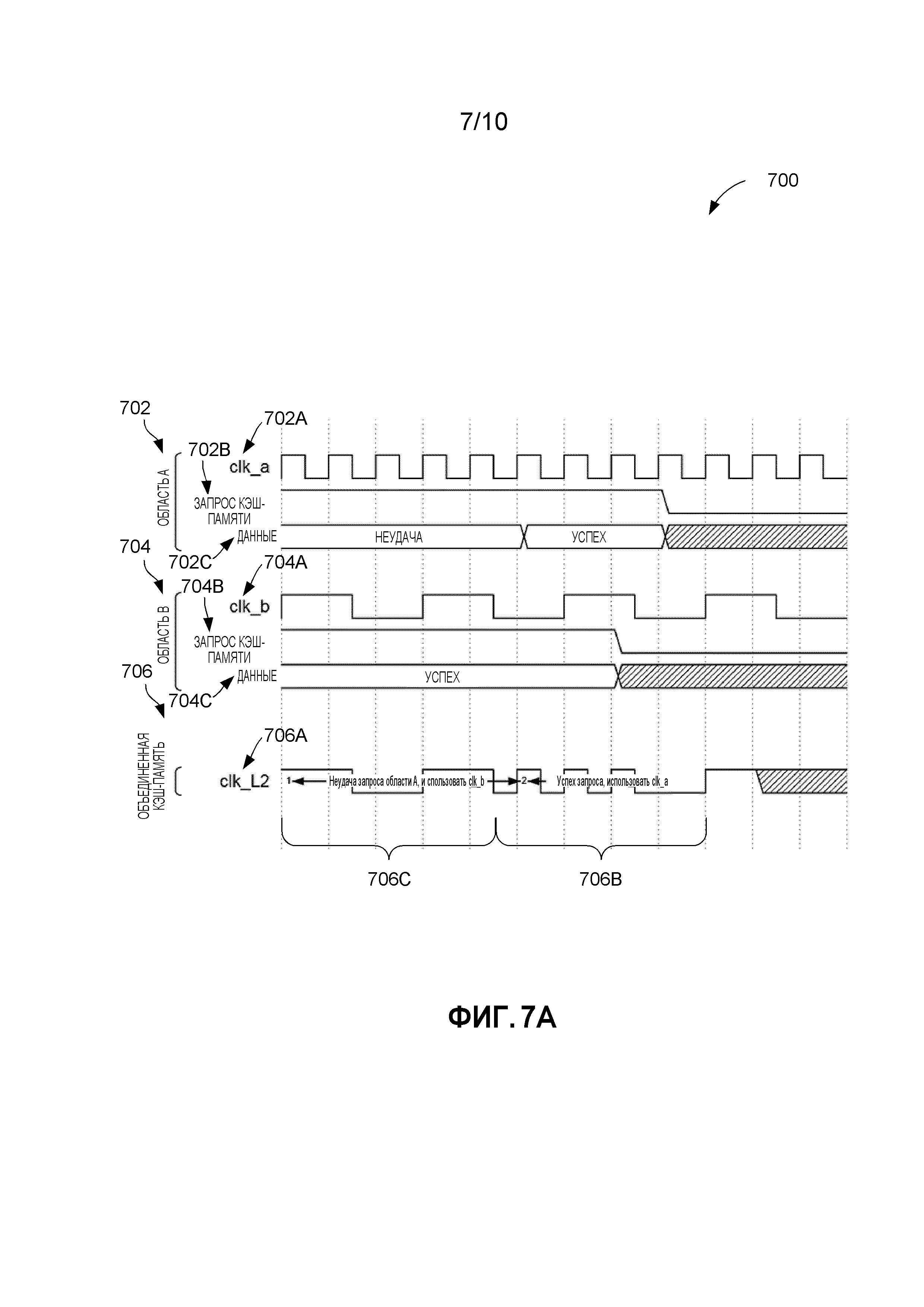

[0024] фиг. 7A демонстрирует иллюстративную временную диаграмму для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления.

[0025] Фиг. 7B демонстрирует систему для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с одним вариантом осуществления.

[0026] фиг. 8 демонстрирует сетевую архитектуру, в соответствии с одним возможным вариантом осуществления.

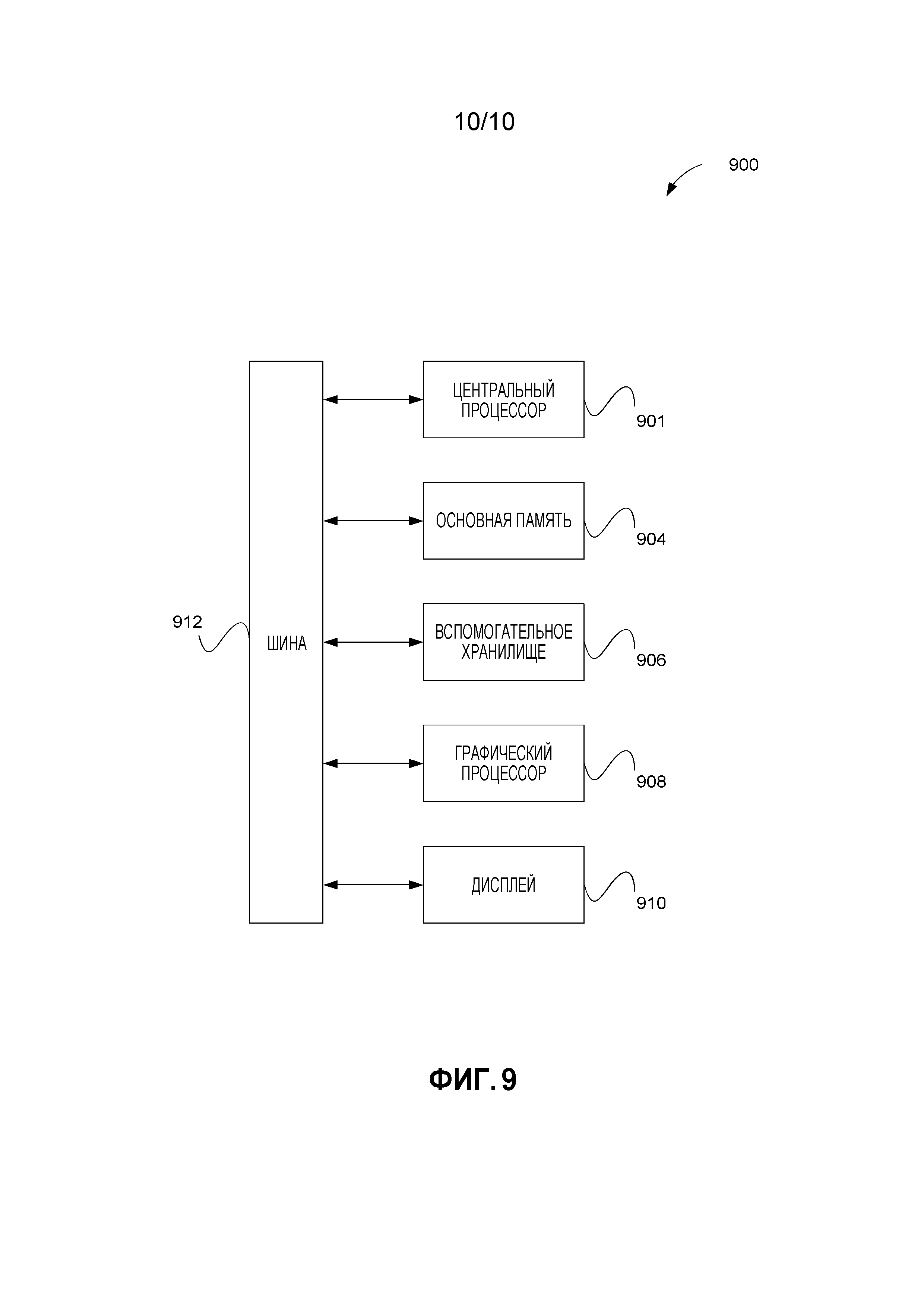

[0027] фиг. 9 демонстрирует иллюстративную систему, в соответствии с одним вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

[0028] Фиг. 1 демонстрирует способ 100 установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с одним вариантом осуществления. Как показано, запрос памяти принимается на этапе 102. В контексте настоящего описания, такой запрос памяти может включать в себя любой запрос, предназначенный вызывать действие в кэш-памяти.

[0029] Как указано на этапе 104, информация идентифицируется в связи с запросом памяти в ответ на прием запроса памяти. В настоящем описании, такая информация может включать в себя любую информацию, которая включена в запрос памяти, или любую информацию, выведенную из содержания запроса памяти и/или подлежащую созданию на его основе. Как показано на фиг. 1, этап 104 осуществляется с использованием оборудования, которое находится в электрической связи с кэш-памятью. Такое оборудование может включать в себя любое оборудование (например, интегральные, дискретные компоненты и т.д.), способные идентифицировать информацию и использовать ее. Кроме того, термин ʺэлектрическая связь,ʺ в контексте настоящего описания, может относиться к любому прямому и/или непрямому электрическому соединению между релевантными электрическими компонентами. Например, такие электрические компоненты могут находиться в электрической связи с промежуточными компонентами между ними или без них.

[0030] Также в контексте настоящего описания, кэш-память может включать в себя любую оперативную память (RAM), к которой можно получать доступ быстрее, чем к другой RAM в системе. Например, в одном возможном варианте осуществления, кэш-память может включать в себя статическую оперативную память (SRAM) или RAM любого другого типа. Также можно рассматривать варианты осуществления, где кэш-память включает в себя гибридную систему типов/классов памяти.

[0031] В одном варианте осуществления, кэш-память может включать в себя совместную кэш-память, отдельную от локальной кэш-памяти. В таком варианте осуществления, к отдельным экземплярам локальной кэш-памяти может получать доступ только один из множества отдельных компонентов компьютера или процессора (например, кластеров, ядер, отслеживающих агентов и т.д.), тогда как совместная кэш-память может совместно использоваться множеством отдельных компонентов компьютера или процессора. Следует отметить, что вышеупомянутый(е) процессор(ы) может(ут) включать в себя процессор общего назначения, центральный процессор, графический процессор и/или процессор любого другого желаемого типа.

[0032] В одном варианте осуществления, информация может относиться к, по меньшей мере, части по меньшей мере одного процессора, который вызвал запрос памяти. Например, информация может относиться к тактовой частоте и/или напряжению, по меньшей мере, части по меньшей мере одного процессора, который вызвал запрос памяти. В другом варианте осуществления, информация может относиться к типу запроса памяти (например, типу чтения, типу записи, типу когерентности, типу упреждающей выборки или типу очистки и т.д.). В контексте настоящего описания, запрос памяти типа чтения может включать в себя запрос на чтение данных из памяти, запрос памяти типа записи может включать в себя запрос на запись данных в память, запрос памяти типа когерентности может включать в себя запрос, который гарантирует, что данные согласуются между множественными местами хранения в системе, запрос памяти типа упреждающей выборки может включать в себя запрос, который пытается сделать данные доступными во избежание неудачи, и запрос памяти типа очистки может включать в себя запрос, который опустошает, по меньшей мере, часть кэш-памяти.

[0033] В еще одном варианте осуществления, информация может относиться к статусу данных, которые являются предметом запроса памяти (например, статусу успеха, статусу неудачи или статусу успеха после неудачи и т.д.). В контексте настоящего описания, статус успеха может относиться к ситуации, когда запрос памяти в отношении данных приводит к возможности осуществления доступа к данным в кэш-памяти, статус неудачи может относиться к ситуации, когда запрос памяти в отношении данных не приводит к возможности осуществления доступа к данным в кэш-памяти, статус успеха после неудачи может относиться к ситуации, когда запрос памяти в отношении данных приводит к возможности осуществления доступа к данным в кэш-памяти после того, как предыдущий запрос памяти в отношении тех же данных не привел к возможности осуществления доступа к данным в кэш-памяти.

[0034] В еще одном варианте осуществления, информация может относиться к действию кэш-памяти, которое вызвано запросом памяти (например, действию чтения, действию записи, запросу к внешней памяти, действию очистки или пустому действию и т.д.). В контексте настоящего описания, действие чтения может относиться к любому действию, которое приводит к чтению данных из кэш-памяти, действие записи может относиться к любому действию, которое приводит к записи данных в кэш-память, запрос к внешней памяти может относиться к любому действию, где данные запрашивается из памяти, отличной от кэш-памяти, действие очистки может относиться к любому действию, которое приводит к опустошению, по меньшей мере, некоторых данных из кэш-памяти, и пустое действие может относиться к любой ситуации, когда в ответ на запрос памяти не предпринимается действие.

[0035] Хотя вышеприведенную информацию можно идентифицировать любым желаемым образом, информацию, в одном варианте осуществления, можно идентифицировать из поля запроса памяти (например, поля идентификации инициатора запроса, поля типа и т.д.). Дополнительные детали, касающиеся вышеприведенной информации, будут изложены ниже более подробно при описании последующих вариантов осуществления.

[0036] На основании информации, идентифицированной на этапе 104, тактовая частота и/или напряжение, по меньшей мере, части кэш-памяти устанавливается в операции 106, с использованием оборудования, которое находится в электрической связи с кэш-памятью. Следует отметить, что одна или более частей оборудования, которое используется в связи с этапами 104 и 106, могут быть одинаковыми или не одинаковыми. Кроме того, оборудование может интегрироваться или не интегрироваться с кэш-памятью (или любым другим компонентом, включающим в себя, но без ограничения, процессор, контроллер памяти и т.д.).

[0037] В одном варианте осуществления, и тактовая частота, и напряжение могут устанавливаться, хотя, в других вариантах осуществления, может устанавливаться только тактовая частота или только напряжение. Например, в одном варианте осуществления, тактовая частота и напряжение может включать в себя рабочую точку (OPP) кэш-памяти. Кроме того, тактовая частота и/или напряжение может устанавливаться для поднабора кэш-памяти или всей кэш-памяти. В первом случае, поднабор кэш-памяти может включать в себя по меньшей мере один банк кэш-памяти, или, собственно говоря, любой его поднабор.

[0038] Ниже приведена дополнительная иллюстративная информация, касающаяся различных необязательных архитектур и вариантов использования, в которых вышеприведенный способ может быть или не быть реализован по желанию пользователя. Следует отметить, что следующая информация изложена в целях иллюстрации и ни в коем случае не в порядке ограничения. Любой из следующих признаков в необязательном порядке может быть включен за исключением или без исключения других описанных признаков.

[0039] Например, в некоторых необязательных вариантах осуществления, способ 100 может обеспечивать управление тактовой частотой и/или напряжением, когда кэш-память активна. Такое управление может администрироваться с более высокой точностью в результате информации, которая идентифицируется в связи с запросами активной памяти. Это, в свою очередь, может приводить к улучшению энергосбережения, которое иначе было бы неизбежно в системах, где отсутствует такое точное управление тактовой частотой и/или напряжением. В других вариантах осуществления, производительность также может повышаться. Исключительно в порядке примера, в одном возможном варианте осуществления, кэш-память, которая подлежит высокочастотному отслеживанию (для обеспечения когерентности кэш-памяти и т.д.), может избегать остановок, обусловленным тем, что управление тактовой частотой и/или напряжением установлено соразмерным с отслеживающим устройством. Конечно, вышеприведенные потенциальные преимущества являются строго необязательными.

[0040] Фиг. 2 демонстрирует систему 200 для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с другим вариантом осуществления. В качестве опции, система 200 может быть реализована в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Однако очевидно, что система 200 может быть реализована в контексте любого желаемого окружения.

[0041] Как показано, система 200 включает в себя множество кластеров 202, каждый из которых включают в себя множество ядер 204. В ходе эксплуатации, каждому из ядер 204 могут независимо и/или совместно назначаться вычислительные задачи, которые, в свою очередь, могут иметь различные требования к вычислению и хранению. По меньшей мере, часть таких требований к хранению может обслуживаться локальной кэш-памятью 206, которая объединена с множеством ядер 204. Кроме того, ядра 204 могут возбуждаться тактовым генератором 208 кластера [например, схемой фазовой автоподстройки частоты (PLL) и т.д.], показанным образом.

[0042] Кроме того, предусмотрена совместная кэш-память 210, которая находится в электрической связи с ядрами 204 кластеров 202 через когерентное межсоединение 212 кэш-памяти. Благодаря этой конструкции, ядра 204 могут осуществлять доступ к совместной кэш-памяти 210 аналогично тому, как осуществляется доступ к локальной кэш-памяти 206. Кроме того, когерентное межсоединение 212 кэш-памяти может дополнительно использоваться, чтобы гарантировать, что, пока общие данные хранятся как в локальной кэш-памяти 206, так и в совместной кэш-памяти 210, такие общие данные остаются согласованными.

[0043] Продолжая рассматривать фиг. 2, предусмотрен контроллер 215 совместной кэш-памяти, который находится в электрической связи с совместной кэш-памятью 210. Как дополнительно показано, контроллер 215 совместной кэш-памяти принимает, в качестве ввода, запросы 216 памяти, которые инициируются ядрами 204 кластеров 202 (и/или другими источниками) и могут приниматься по любому желаемому маршруту (например, через контроллер памяти (не показан) напрямую из ядер 204 через другие компоненты и т.д.). В качестве дополнительного ввода, контроллер 215 совместной кэш-памяти дополнительно принимает один или более тактовых сигналов 218 в связи с ядрами 204 и/или любыми другими системными компонентами, которые обслуживаются контроллером 215 совместной кэш-памяти.

[0044] В операции, контроллер 215 совместной кэш-памяти использует запросы 216 памяти и/или один или более тактовых сигналов 218 (и/или любую информацию, собранную из них) для вывода по меньшей мере одного тактового сигнала и/или сигнала 220 напряжения в совместную кэш-память 210 с целью установления тактовой частоты и/или напряжения, на которых работает совместная кэш-память 210. Для этого совместная кэш-память 210 может использоваться с улучшенным энергосбережением путем установления тактовой частоты и/или напряжения как функции запросов 216 памяти и, возможно, тактовых сигналов 218. В различных вариантах осуществления, уровень такого улучшенного энергосбережения может зависеть от того, как информация собирается и как она используется для установления тактовой частоты и/или напряжения совместной кэш-памяти 210. Далее будет изложена дополнительная информация, касающаяся одной возможной архитектуры контроллера 215 совместной кэш-памяти.

[0045] Фиг. 3 демонстрирует контроллер 300 совместной кэш-памяти для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления. В качестве опции, контроллер 300 совместной кэш-памяти может быть реализован в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Например, в одном варианте осуществления контроллер 300 совместной кэш-памяти может включать в себя контроллер 215 совместной кэш-памяти на фиг. 2. Однако, очевидно, что контроллер 300 совместной кэш-памяти может быть реализован в контексте любого желаемого окружения.

[0046] Как показано, контроллер 300 совместной кэш-памяти включает в себя блок 302 управления кэш-памятью, который остается в электрической связи с SRAM 304, которая действует как кэш-память. В ходе эксплуатации, блок 302 управления кэш-памятью принимает множество запросов 306 памяти, которые могут относиться к любому одному или более из различных типов (например, типу чтения, типу записи, типу когерентности, типу упреждающей выборки или типу очистки и т.д.). Как будет видно ниже при описании последующих вариантов осуществления, запросы 306 памяти могут включать в себя различные поля, включающие в себя поле данных с данными, подлежащими использованию, поле типа, идентифицирующее тип запроса памяти, и т.д. В ответ на запросы 306 памяти, блок 302 управления кэш-памятью инициирует одно или более действий (например, действие чтения, действие записи, запрос к внешней памяти, действие очистки или пустое действию и т.д.) в связи с SRAM 304.

[0047] Как дополнительно показано, запросы 306 памяти могут также инструктировать контроллеру 300 совместной кэш-памяти взаимодействовать с внешней памятью 305 (например, считывать из нее, записывать в нее и т.д.) через одну или более шин 307. Кроме того, блок 302 управления кэш-памятью может дополнительно передавать сигналы 308 статуса данных (например, успеха, неудачи или успеха после неудачи, и т.д.), обусловленные каждым запросом 306 памяти. В одном варианте осуществления, такие сигналы 308 статуса данных могут передаваться принудительно без запроса, хотя, в других вариантах осуществления, сигналы 308 статуса данных могут запрашиваться другими компонентами контроллера 300 совместной кэш-памяти.

[0048] Контроллер 300 совместной кэш-памяти дополнительно включает в себя блок 309 управления питанием кэш-памяти, который принимает, в качестве ввода, запросы 306 памяти, сигналы 308 статуса данных и множество тактовых сигналов 310. Такие тактовые сигналы 310 могут включать в себя тактовый сигнал для каждого из множества компонентов (например, компьютеров, процессоров, ядер, отслеживающих агентов, их частей и т.д.), которые должны обслуживаться SRAM 304 (например REQUESTOR_CLK1, REQUESTOR_CLK2, …, REQUESTOR_CLKN и т.д.). Кроме того, может быть предусмотрен опорный тактовый сигнал (REF_CLK).

[0049] В операции, контроллер 300 совместной кэш-памяти служит для вывода настроек 312 напряжения для установления рабочего напряжения для SRAM 304 (и/или любой ее части), а также внутренних настроек 314A, 314B тактовой частоты для установления рабочей тактовой частоты для SRAM 304 (и/или любой ее части). Кроме того, такие настройки 312 напряжения и внутренние настройки 314A, 314B тактовой частоты конкретно устанавливаются как функция информации, собранной, выведенной и/или возникающей (посредством причинной связи) из содержания запросов 306 памяти, включающих в себя, но без ограничения, поля запросов 306 памяти, сигналов 308 статуса данных и/или любой другой информации, которая собирается и/или обрабатывается в связи с запросами 306 памяти.

[0050] Как показано, для установления тактовой частоты SRAM 304, внутренние настройки 314A, 314B тактовой частоты включают в себя сигнал 314A выбора тактовой частоты, который поступает на мультиплексор 315, который подает один из тактовых сигналов 310 на делитель 316 тактовых сигналов, который делит тактовые сигналы 310 как функция сигнала 314B отношения делителя, который обеспечивается блоком 309 управления питанием кэш-памяти. Для этого, внешние настройки 318 тактовой частоты выводятся для установления тактовым сигналом SRAM 304. Благодаря этой конструкции, надлежащим образом выбранный один из тактовых сигналов 310 (который тактирует обслуживаемый компонент и т.д.) может ступенчато снижаться для тактирования SRAM 304.

[0051] В этой конструкции предусмотрен первый модуль (например, блок 302 управления кэш-памятью, другая схема и т.д.) для идентификации, в ответ на прием запроса памяти, информации в связи с запросом памяти. Кроме того, предусмотрен второй модуль (например, блок 309 управления питанием кэш-памяти, другая схема и т.д.) для установки по меньшей мере одного из тактовой частоты и напряжения, по меньшей мере, части кэш-памяти, на основании информации. Как упомянуто выше, такое управление напряжением/тактовой частотой может администрироваться с более высокой точностью в результате информации, которая идентифицируется в связи с запросами активной памяти. Это, в свою очередь, может приводить к улучшению энергосбережения, которое иначе было бы неизбежно в системах, где отсутствует такое интеллектуальное, точное управление тактовой частотой и/или напряжением.

[0052] Фиг. 4 демонстрирует образцовый запрос 400 памяти с информацией, которую можно использовать для установления тактовой частоты/напряжения кэш-памяти, в соответствии с еще одним вариантом осуществления. В качестве опции, образцовый запрос 400 памяти может использоваться в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Например, в одном варианте осуществления, образцовый запрос 400 памяти может приниматься контроллером 215 совместной кэш-памяти на фиг. 2, контроллером 300 совместной кэш-памяти на фиг. 3, и т.д.

[0053] Как показано, запрос 400 памяти включает в себя множество полей, включающих в себя поле 402 типа, поле 404 идентификатора инициатора запроса, поле 406 адреса, поле 408 данных, поле 410 грязного бита, поле 412 подсказки кэш-памяти и поле 414 смешанного(ых) атрибута(ов). В ходе эксплуатации, поле 402 типа может идентифицировать тип (например, тип чтения, тип записи, тип когерентности, тип упреждающей выборки или тип очистки и т.д.) запроса памяти, тогда как поле 404 идентификатора инициатора запроса может идентифицировать компонент (например, кластеры, ядра, агент отслеживания и т.д.), который вызвал запрос 400 памяти. Это можно осуществлять с использованием любого желаемого идентификатора (например, уникального двоичного числа и т.д.). Благодаря этой конструкции, содержание поля 402 типа, поля 404 идентификатора инициатора запроса и/или любого другого поля, собственно говоря, может использоваться для установления тактовой частоты/напряжения кэш-памяти. Далее будет изложена дополнительная информация, касающаяся одного возможного способа, согласно которому запрос 400 памяти может использоваться для установления тактовой частоты/напряжения кэш-памяти.

[0054] Фиг. 5 демонстрирует способ 500 установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти в соответствии с еще одним вариантом осуществления. В качестве опции, способ 500 может быть реализован в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Например, в одном варианте осуществления, способ 500 может осуществляться контроллером 215 совместной кэш-памяти на фиг. 2, контроллером 300 совместной кэш-памяти на фиг. 3, и т.д. Кроме того, способ 500 может действовать в окружении, которое включает в себя неблокирующую многобанковую кэш-память с возможностями обратной записи/выделения под запись, а также машину опережающей выборки, множественные буферы записи и очереди наполнения/исключения. Однако, очевидно, что способ 500 может быть реализован в контексте любого желаемого окружения.

[0055] Как показано, на этапе 502 принимается запрос памяти. В различных вариантах осуществления, запрос памяти может приниматься любым раскрытым здесь компонентом (например, контроллером 215 совместной кэш-памяти на фиг. 2, контроллером 300 совместной кэш-памяти на фиг. 3 и т.д.) или, собственно говоря, любым другим компонентом. На этапе 504 сохраняется содержание поля типа и поля идентификатора инициатора запроса для запроса памяти (например, поля 402 типа, поля 404 идентификатора инициатора запроса на фиг. 4 и т.д.).

[0056] Затем на блоке 506 принятия решения производится определение, приводит ли запрос памяти, принятый на этапе 502, к успеху (т.е. удается осуществлять доступ к запрошенным данным, и т.д.). Если нет, данные запрашиваются из внешней памяти (отдельной от кэш-памяти) путем помещения запроса в буфер для выборки данных из внешней памяти. См. этап 508. Затем способ 500 опрашивает, пока не будут доступны запрошенные данные (например, элемент данных и т.д.), для каждого принятия решения 510. Затем производится определение, скопированы ли данные в кэш-память для каждого принятия решения 512. Следует отметить, что, в некоторых вариантах осуществления, данные, которые запрашиваются, отправляется напрямую на запрашивающий компонент (и, таким образом, не копируются в кэш-память).

[0057] Таким образом, если на блоке 506 принятия решения определено, что запрос памяти приводит к успеху, или на блоке 512 принятия решения определено, что данные скопированы в кэш-память; способ 500 продолжается путем планирования запроса памяти в очереди для осуществления доступа к целевой(ым) секции(ям) (например, банку(ам) и т.д.) кэш-памяти, на этапе 514. Затем способ 500 опрашивает, пока запрос не будет запланирован для каждого принятия решения 516, после чего указатель доступа устанавливается для запроса памяти на этапе 518. В различных вариантах осуществления, таким указателем доступа может быть любым одним или более битов, которые хранятся совместно с запросом памяти или отдельно от него, с целью указания, что запрос памяти (и любая информация, содержащаяся в нем/выведенная из него) активен и, таким образом, должен рассматриваться при установлении напряжения/тактовой частоты кэш-памяти, когда к ней обращае(ю)тся важный(е) компонент(ы) (или его/их секция(и)), который(е) вызвал(и) запрос памяти.

[0058] Далее способ 500 определяет на блоке 520 принятия решения, существуют ли ожидающие запросы памяти в вышеупомянутой очереди. Если нет, способ 500 заканчивается (и другие методы энергосбережения могут применяться или не применяться). С другой стороны, если существуют какие-либо ожидающие запросы памяти в вышеупомянутой очереди (например, способ 500 выполняется), оптимальное напряжение и/или тактовая частота (например, OPP и т.д.) определяется для соответствующей(их) целевой(ых) секции(й) кэш-памяти. См. этап 522.

[0059] В различных вариантах осуществления, такая OPP может определяться любым желаемым образом с использованием запроса памяти (и/или его содержания или информации, выведенной/в результате полученной из него) для улучшения энергосбережения, когда кэш-память активна. В одном варианте осуществления, оптимальная OPP может определяться блоком управления питанием кэш-памяти (например, блоком 309 управления питанием кэш-памяти на фиг. 3 и т.д.) как наивысшая (т.е. самая быстрая по сравнению с другими) тактовая частота инициаторов запроса, которые в данный момент обращаются к кэш-памяти, что указано указателями доступа ожидающих запросов памяти в очереди.

[0060] В другом варианте осуществления, минимальный квант времени может использоваться до смены OPP, для ограничения частоты, на которой сменяется OPP. Таким образом, запросы памяти могут буферизоваться каждый цикл для смены OPP, но смена может происходить только каждые N циклов, где N=1, 2, 3, …, X (любое целое число). Для этого, решение масштабировать тактовую частоту кэш-памяти может откладываться, на основании контекста, в котором осуществляется доступ к кэш-памяти, где такой контекст может задаваться информацией запроса памяти.

[0061] В другом возможном варианте осуществления, такой квант может быть обязательным для компенсации задержек при смене OPP на основании частоты запросов памяти. В прочих вариантах осуществления могут использоваться безотказные конструкции мультиплексора, которые минимизируют задержки тактового сигнала при выборе и смене тактового сигнала. Кроме того, выбранное напряжение кэш-памяти/банка кэш-памяти может отличаться или не отличаться от напряжения, необходимого для тактового генератора.

[0062] В любом случае, целевая(ые) секция(и) кэш-памяти можно регулировать до оптимальной OPP и затем возвращать данные инициатору запроса. См. этап 524. Затем способ 500 осуществляет опрос для каждого принятия решения 526, пока доступ не завершится, после чего вышеупомянутый указатель доступа очищается на этапе 528 для запроса памяти, который вызвал доступ, поскольку такой запрос памяти, в такой точке, уже обслужен, и больше нерелевантен в любом последующем вычислении оптимальной OPP.

[0063] Фиг. 6 демонстрирует дополнительные вариации 600 для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления. В качестве опции, дополнительные вариации 600 могут быть реализованы в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Однако очевидно, что дополнительные вариации 600 могут быть реализованы в контексте любого желаемого окружения.

[0064] Как показано, различные решения 602 по тактовой частоте кэш-памяти могут обеспечиваться как функция различных комбинаций типа 604 доступа, статуса 606 данных и действия 608 кэш-памяти. Например, в случае чтения или типа доступа отслеживания, где статус данных указывает успех, и действие кэш-памяти является чтением, таковой сигнал может масштабироваться в отношении всех текущих инициаторов запроса. Дополнительно, также в случае чтения или типа доступа отслеживания, но когда статус данных указывает неудачу, и действие кэш-памяти пусто, таковой сигнал может масштабироваться в отношении инициатора(ов) запроса пока запрошенные данные не будут выбраны из памяти. Кроме того, в случае типа доступа записи, где статус данных указывает успех, и действие кэш-памяти является записью, таковой сигнал может масштабироваться в отношении всех текущих инициаторов запроса. Кроме того, проиллюстрированы другие примеры, где никакого действия не осуществляется для оптимизации тактовой частоты/напряжения.

[0065] Фиг. 7A демонстрирует иллюстративную временную диаграмму 700 для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с еще одним вариантом осуществления. В качестве опции, иллюстративная временная диаграмма 700 может отражать операцию любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании.

[0066] Как показано, первая область 702 (например, включающая в себя по меньшей мере один запрашивающий компонент и т.д.) включает в себя первый тактовый сигнал 702A и запрос 702B кэш-памяти, который приводит к статусу 702C данных. Дополнительно, вторая область 704 (например, включающая в себя по меньшей мере один другой запрашивающий компонент и т.д.) включает в себя второй тактовый сигнал 704A, и запрос 704B кэш-памяти, который приводит к статусу 704C данных. Кроме того, показано, что кэш-память 706 включает в себя третий тактовый сигнал 706A. Хотя две области 702, 704 описаны в контексте настоящего варианта осуществления, следует отметить, что другие варианты осуществления рассматриваются с большим или меньшим количеством таких областей.

[0067] На основании того факта, что статус 702C данных первой области 702 указывает неудачу в течение периода 706C, второй тактовый сигнал 704A используется для возбуждения третьего тактового сигнала 706A кэш-памяти путем его установления равным второму тактовому сигналу 704A второй области 704 в течение такого периода, как показано. Однако, когда статус 702C данных указывает успех в течение периода 706B, первый тактовый сигнал 702A используется для возбуждения третьего тактового сигнала 706A кэш-памяти 706 путем его установления равным первому тактовому сигналу 702A первой области 702 в течение такого периода. Хотя показано, что третий тактовый сигнал 706A кэш-памяти 706 переключается между двумя разными тактовыми частотами, следует отметить, что в такой переход может быть включена некоторая задержка.

[0068] Таким образом, решение масштабировать тактовую частоту кэш-памяти может откладываться на более позднее время, на основании контекста, в котором осуществляется доступ к кэш-памяти. Благодаря откладыванию любого масштабирования напряжения/тактовой частоты, может обеспечиваться энергосбережение.

[0069] Фиг. 7B демонстрирует систему 750 для установления тактовой частоты/напряжения кэш-памяти на основании информации запроса памяти, в соответствии с другим вариантом осуществления. В качестве опции, система 750 может быть реализована в контексте любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании. Однако, очевидно, что система 750 может быть реализована в контексте любого желаемого окружения.

[0070] Как показано, система 750 включает в себя первое средство в форме первого модуля 752 (например, первой схемы, модуля, осуществляющего операцию 104 на фиг. 1, первой части контроллера 215 на фиг. 2, например, блока 302 управления кэш-памятью на фиг. 3 и т.д.), который выполнен с возможностью, в ответ на прием запроса памяти, идентифицировать информацию в связи с запросом памяти. Также включено второе средство в форме второго модуля 754 (например, второй схемы, модуля, осуществляющего операцию 106 на фиг. 1, второй части контроллера 215 на фиг. 2, например, блока 309 управления питанием кэш-памяти и делителя 316 тактовых сигналов на фиг. 3 и т.д.), осуществляющего связь с первым модулем 752, где второй модуль 754 выполнен с возможностью устанавливать по меньшей мере одно из тактовой частоты или напряжения, по меньшей мере, части кэш-памяти, на основании информации. В одном варианте осуществления, система 750 может быть выполнена с возможностью действовать в соответствии со способом 100 на фиг. 1. Например, система 750 может, в таком варианте осуществления, включать в себя модуль (или средство) приема для приема запросов памяти в соответствии с операцией 102 на фиг. 1.

[0071] Фиг. 8 демонстрирует сетевую архитектуру 800, в соответствии с одним вариантом осуществления. В одном варианте осуществления, вышеупомянутое управление напряжением/тактовой частотой кэш-памяти любого одного или более из вариантов осуществления, изложенных в любой предыдущей и/или последующей фигур(ах) и/или их описании, может быть включено в любой из компонентов, показанных на фиг. 8.

[0072] Как показано, предусмотрена по меньшей мере одна сеть 802. В контексте настоящей сетевой архитектуры 800, сеть 802 может принимать любую форму, включающую в себя, но без ограничения, сеть телекоммуникации, локальную сеть (LAN), беспроводную сеть, глобальную сеть (WAN), такую как интернет, одноранговую сеть, кабельную сеть и т.д. Хотя показана только одна сеть, следует понимать, что может быть предусмотрено две или более аналогичных или разных сетей 802.

[0073] К сети 802 подключено множество устройств. Например, компьютер-сервер 812 и компьютер 808 конечного пользователя могут быть подключены к сети 802 в целях связи. Такой компьютер 808 конечного пользователя может включать в себя настольный компьютер, портативный компьютер и/или логику любого другого типа. Кроме того, к сети 802 могут быть подключены различные другие устройства, включающие в себя устройство 810 персональный цифровой помощник (PDA), устройство 806 мобильный телефон, телевизор 804 и т.д.

[0074] Фиг. 9 демонстрирует примерную систему 900, в соответствии с одним вариантом осуществления. В качестве опции, система 900 может быть реализована в контексте любого из устройств сетевой архитектуры 800 на фиг. 8. Однако, очевидно, что система 900 может быть реализована в любом желаемом окружении.

[0075] Как показано, предусмотрена система 900, включающая в себя по меньшей мере один центральный процессор 902, который подключен к шине 912. Система 900 также включает в себя основную память 904 [например, жесткий диск, твердотельный привод, оперативную память (RAM) и т.д.]. Система 900 также включает в себя графический процессор 908 и дисплей 910.

[0076] Система 900 также может включать в себя вспомогательное хранилище 906. Вспомогательное хранилище 906 включает в себя, например, жесткий диск и/или привод сменных носителей, представляющий привод флоппи-диска, привод магнитной ленты, привод компакт-дисков и т.д. Привод сменных носителей считывает с и/или записывает на сменное устройство хранения общеизвестным образом.

[0077] Компьютерные программы или логические алгоритмы управления компьютером, могут храниться в основной памяти 904, вспомогательном хранилище 906 и/или, собственно говоря, в любой другой памяти. Такие компьютерные программы, при исполнении, позволяют системе 900 осуществлять различные функции (например, вышеупомянутые). Память 904, вспомогательное хранилище 906 и/или любое другое хранилище являются возможными примерами невременных компьютерно-считываемых носителей.

[0078] Заметим, что описанные здесь методы, согласно аспекту, воплощены в исполнимых инструкциях, хранящихся на компьютерно-считываемом носителе для использования машиной, оборудованием или устройством исполнения инструкций или в связи с ней/ним, например, компьютерной(ым) или содержащей(им) процессор машиной, оборудованием или устройством. Специалистам в данной области техники будет очевидно, что для некоторых вариантов осуществления, включены другие типы компьютерно-считываемых носителей, где могут храниться данные, к которым осуществляет доступ компьютер, например, магнитные кассеты, карты флэш-памяти, цифровые видеодиски, картриджи Бернулли, оперативную память (RAM), постоянную память (ROM) и пр.

[0079] Используемый здесь термин "компьютерно-считываемый носитель" включает в себя один или более из любых пригодных носителей для хранения исполнимых инструкций компьютерной программы таким образом, что машина, система, оборудование или устройство исполнения инструкций может считывать (или выбирать) инструкции из компьютерно-считываемого носителя и исполнять инструкции для осуществления описанных способов. Пригодные форматы хранения включают в себя один или более из электронного, магнитного, оптического и электромагнитного формата. Открытый список традиционных иллюстративных компьютерно-считываемым носителей включает в себя: портативную компьютерную дискету; RAM; ROM; стираемую программируемую постоянную память (EPROM или флеш-память); оптические запоминающие устройства, включающие в себя портативный компакт-диск (CD), портативный цифровой видеодиск (DVD), DVD высокой четкости (HD-DVD™), диск BLU-RAY; и пр.

[0080] Следует понимать, что компоновка компонентов, проиллюстрированная в чертежах, является иллюстративной, и что возможны другие компоновки. Следует также понимать, что различные системные компоненты (и средства), заданные нижеприведенной формулой изобретения и проиллюстрированные в различных блок-схемах представляют логические компоненты в некоторых системах, сконфигурированных согласно раскрытому здесь предмету изобретения.

[0081] Например, один или более из этих системных компонентов (и средств) могут быть реализованы, полностью или частично, по меньшей мере, некоторыми из компонентов, проиллюстрированных в компоновках, проиллюстрированных в описанных чертежах. Кроме того, хотя по меньшей мере один из этих компонентов реализован, по меньшей мере, частично как электронный аппаратный компонент и, таким образом, образует машину, другие компоненты могут быть реализованы в программном обеспечении, которое, будучи включено в окружение исполнения, образует машину, оборудование или комбинацию программного обеспечения и оборудования.

[0082] Более конкретно, по меньшей мере один компонент, заданный формулой изобретения, реализован, по меньшей мере, частично как электронный аппаратный компонент, например, машина исполнения инструкций (например, машина на основе процессора или содержащая процессор) и/или как специализированные схемы или схема (например, дискретные логические вентили, соединенные между собой для осуществления специализированной функции). Другие компоненты могут быть реализованы в программном обеспечении, оборудовании или комбинации программного обеспечения и оборудования. Кроме того, некоторые или все из этих других компонентов могут быть объединены, некоторые могут быть вовсе опущены, и дополнительные компоненты могут добавляться, достигая при этом описанных здесь функциональных возможностей. Таким образом, описанный здесь предмет изобретения может быть реализован во многих разных вариациях, и все такие вариации рассматриваются в объеме формулы изобретения.

[0083] В вышеприведенном описании, предмет изобретения описан со ссылкой на действия и символические представления операций, осуществляемых одним или более устройствами, если не указано иное. Таким образом, следует понимать, что такие действия и операции, которые иногда именуются компьютерно-исполняемыми, включают в себя манипуляцию процессором данных в структурированной форме. Эта манипуляция преобразует данные или поддерживает их в положениях в системе памяти компьютера, которая переконфигурирует или иначе изменяет операцию устройства способом, известным специалистам в данной области техники. Данные поддерживаются в физических положениях памяти в качестве структур данных, которые имеют конкретные свойства, заданные форматом данных. Однако, хотя предмет изобретения описан в вышеприведенном контексте, это не является ограничением, поскольку специалистам в данной области техники будет очевидно, что различные описанные ниже действия и операции также можно реализовать в оборудовании.

[0084] Для облегчения понимания описанного здесь предмета изобретения, многие аспекты описаны в отношении последовательностей действий. По меньшей мере один из этих аспектов, заданных формулой изобретения, осуществляется электронным аппаратным компонентом. Например, очевидно, что различные действия могут осуществляться специализированными схемами или схемой, программными инструкциями, исполняемыми одним или более процессорами, или их комбинацией. Приведенное здесь описание любой последовательности действий не означает, что конкретный описанный порядок осуществления этой последовательность является обязательным. Все описанные здесь способы могут осуществляться в любом пригодном порядке, если не указано иное или иначе явно не противоречит контексту.

[0085] Использование форм единственного числа в контексте описания предмета изобретения (в частности, в контексте нижеследующей формулы изобретения) призвано охватывать как единственное число, так и множественное число, если здесь не указано обратное или явно не противоречит контексту. Указание диапазонов значений призвано служить лишь сокращенным способом указания по-отдельности каждого отдельного значения, принадлежащего диапазону, если здесь не указано обратное, и каждое отдельное значение включено в описание изобретения, как если бы они были по отдельности упомянуты здесь. Кроме того, вышеприведенное описание служит только для иллюстрации, но не ограничения, поскольку объем защиты задается нижеследующей формулой изобретения совместно с любыми их эквивалентами. Использование любых и всех примеров или обеспеченного здесь иллюстративного языка (например, "такой как"), призвано лишь лучше иллюстрировать предмет изобретения и не налагает ограничения на объем изобретения, если не утверждается обратное. Использование термина ʺна основанииʺ и других аналогичных выражений, указывающих условие получения результата, как в формуле изобретения, так и в записанном описании, не призвано предотвращать любые другие условия, которые приводят к этому результату. Никакой язык в описании изобретения не следует рассматривать как указывающий любой незаявленный элемент как существенный для практики заявленного изобретения.

[0086] Описанные здесь варианты осуществления включают в себя один или более режимов, известных автору изобретения, для осуществления заявленного изобретения. Очевидно, что вариации этих вариантов осуществления будут понятны специалистам в данной области техники из вышеприведенного описания. Автор изобретения полагает, что специалисты в данной области техники будут использовать такие вариации при необходимости, и автор изобретения полагает, что заявленное изобретение будет осуществляться на практике иначе, чем конкретно описано здесь. Соответственно, это заявленное изобретение включает в себя все модификации и эквиваленты предмета изобретения, изложенного в нижеследующей формуле изобретения, разрешенные применимым правом. Кроме того, включена любая комбинация вышеописанных элементов во всех возможных их вариациях, если здесь не указано обратное или иначе явно не противоречит контексту.