Результат интеллектуальной деятельности: Устройство преобразования информации

Вид РИД

Изобретение

Изобретение относится к цифровой технике в области обработки информации и может быть использовано в космической отрасли при построении специализированных ЭВМ, включающих в себя запоминающие устройства (ЗУ) различной разрядности.

Известен патент на изобретение RU 2292581 с приоритетом от 12.12.2002 г. «Команды загрузки / перемещения и копирования для процессора». Указанные в патенте команды предназначены для специализированных задач.

Недостатком является дополнительные затраты времени (тактов) процессора на программную обработку информации при работе с ЗУ различной разрядности.

Известен патент на изобретение RU №2554546 «Средство разделенной загрузки / сохранения и команда для него» Указанные в патенте команды предназначены для специализированных задач.

Недостатком является дополнительные затраты времени (тактов) процессора на программную обработку информации при работе с ЗУ различной разрядности.

Прототипа заявленного изобретения не выявлено.

Вычислительный процесс в ЭВМ всегда включает в себя хранение и обработку данных. Хранение данных выполняется в запоминающих устройствах. Обработку данных выполняет процессор. Как правило, данные должны быть предварительно загружены во внутренние регистры процессора, а после обработки вновь помещены в ЗУ.

При программной реализации обмена информацией между 16-ти разрядным или 8-ми разрядным ЗУ и 32-х разрядными регистрами общего назначения процессора требуется не менее 2 свободных регистров общего назначения (РОН) и специальная подпрограмма, которая включает в себя специализированные команды процессора.

При этом:

- один обмен между 16-ти разрядным ЗУ и внутренней памятью процессора занимает ~ 10 тактов процессора (Тцп);

- один обмен между 8-ми разрядным ЗУ и внутренней памятью процессора занимает ~ 18Тцп.

Задачей изобретения является создание устройства, обеспечивающего сокращение количества тактов процессора, необходимых для эффективной загрузки данных между запоминающими устройствами различной разрядности и внутренней памятью процессора.

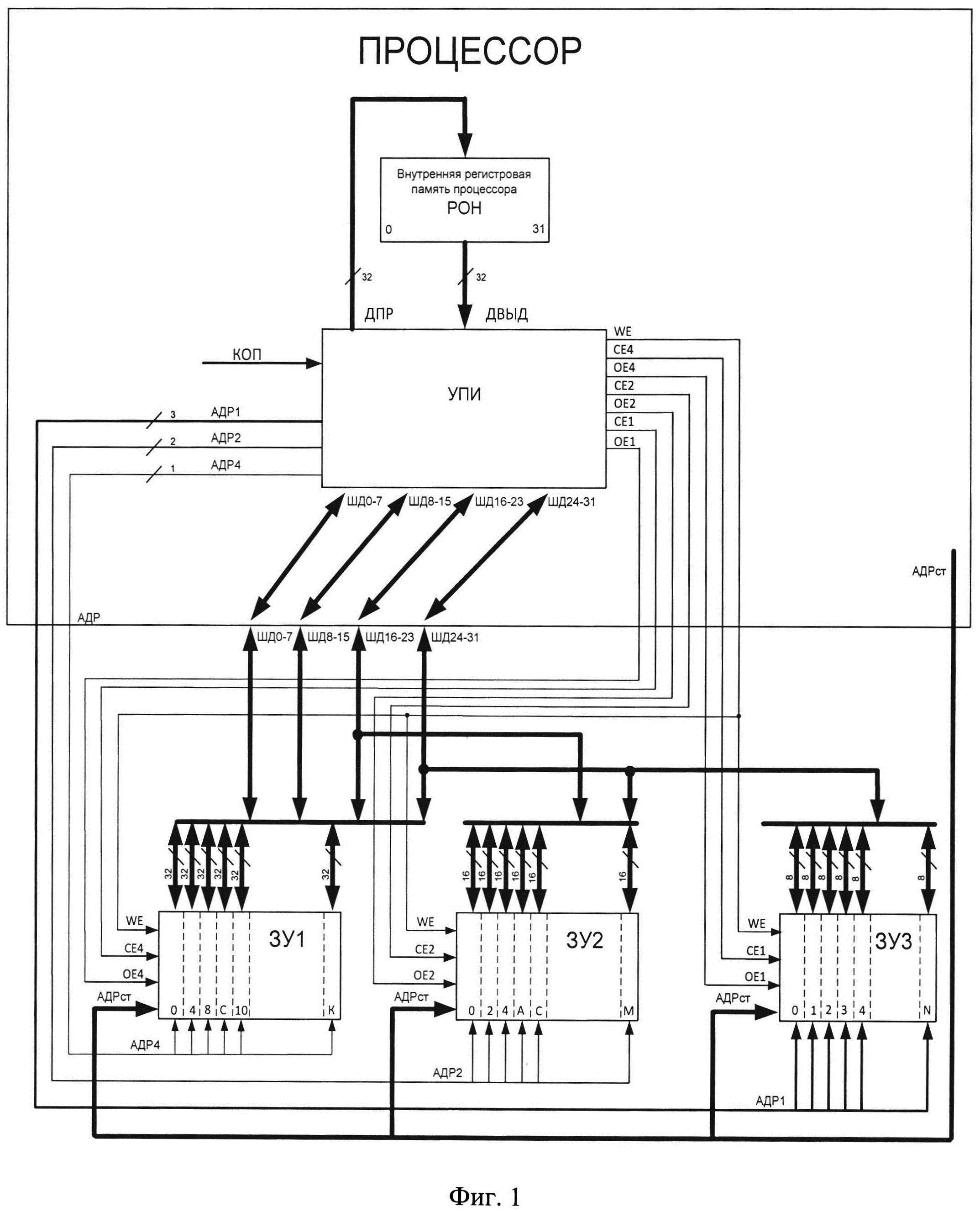

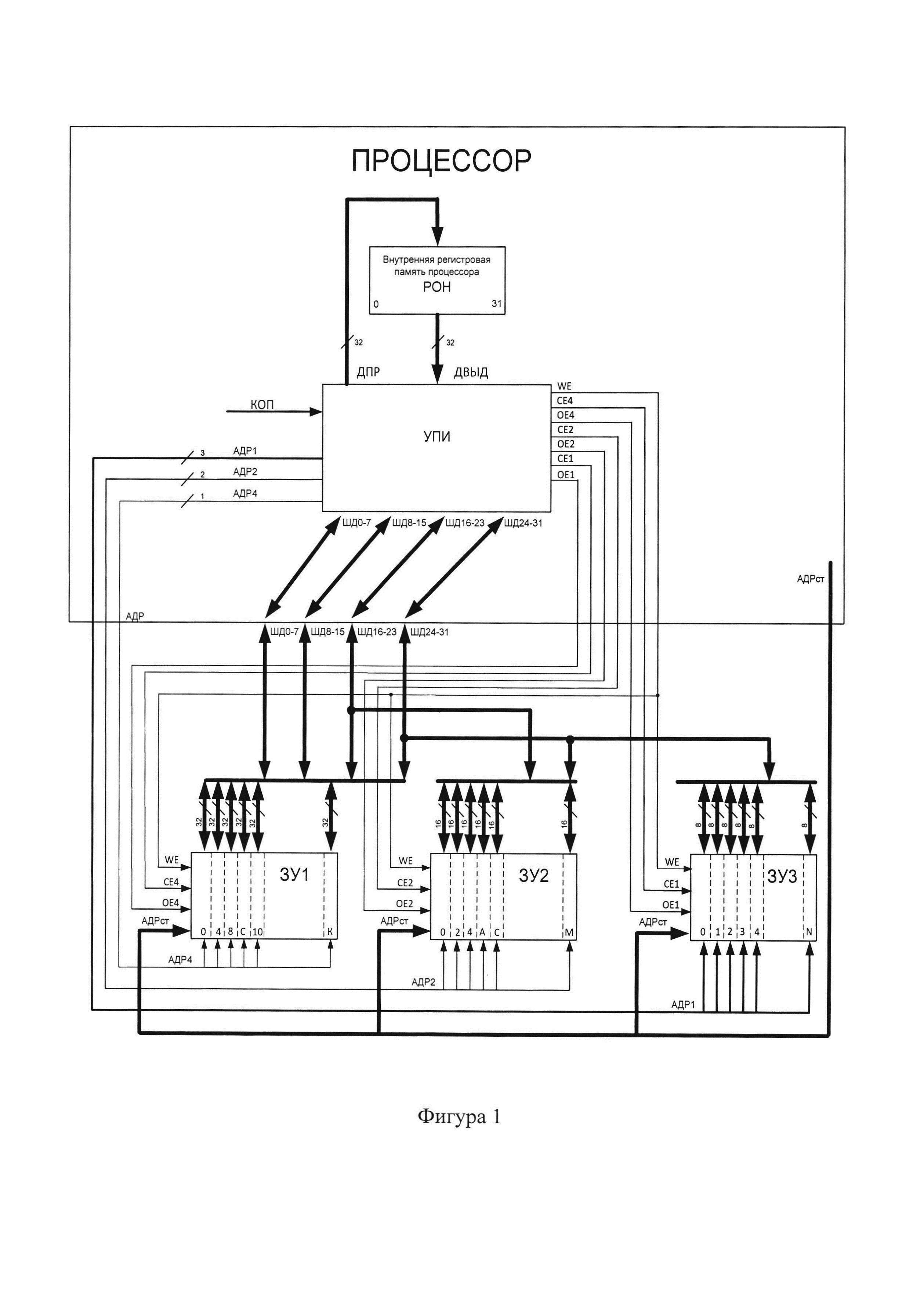

На фигуре 1 показана структурная схема включения устройства преобразования информации (УПИ) в схему 32-х разрядного процессора, к которому подключены 32-х, 16-ти и 8-ми разрядные ЗУ.

ЗУ подключаются к общей 32-х разрядной шине данных процессора, при этом:

- 16-ти разрядное ЗУ подключается к младшим 16-ти разрядам общей шины;

- 8-ми разрядное ЗУ подключается к младшим 8-ми разрядам общей шины.

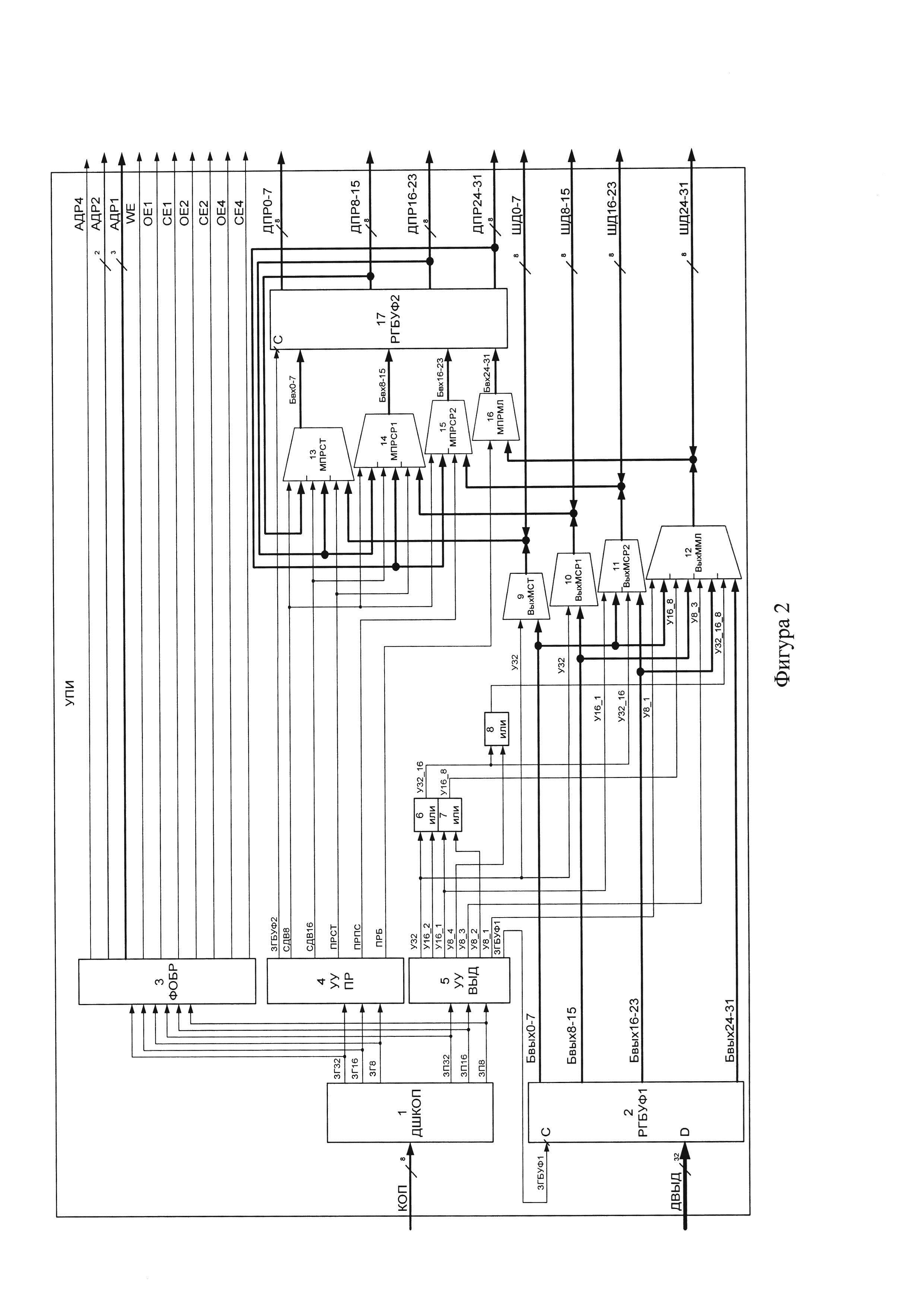

На фигуре 2 представлена структурная схема устройства преобразования информации (УПИ), включающая в себя следующие элементы:

1 - дешифратор кода операции (ДШКОП);

2 - первый регистр буфера (РГБУФ1);

3 - формирователь обращений (ФОБР);

4 - устройство управления приемом (УУПР);

5 - устройство управления выдачей (УУВЫД);

6, 7 и 8 - первый, второй и третий элементы «ИЛИ»;

9 - старший выходной мультиплексор (ВыхМСТ);

10 - первый средний выходной мультиплексор (ВыхМСР1);

11 - второй средний выходной мультиплексор (ВыхМСР2);

12 - младший выходной мультиплексор (ВыхММЛ);

13 - старший мультиплексор приема (МПРСТ);

14 - первый средний мультиплексор приема (МПРСР1);

15 - второй средний мультиплексор приема (МПРСР2);

16 - младший мультиплексор приема (МПРМЛ);

17 - второй регистр буфера (РГБУФ2).

Сигналы согласно фигуре 2:

КОП - восьмиразрядный код операции, определяющий команду процессор;

ДВЫД - 32-х разрядная информация из регистра общего назначения (РОН), предназначенная для записи в ЗУ;

ЗГ32 - команда загрузки 32-х разрядной информации;

ЗГ16 - команда загрузки 16-ти разрядной информации;

ЗГ8 - команда загрузки 8-ми разрядной информации;

ЗП32 - команда записи 32-х разрядной информации;

ЗП16 - команда записи 16-ти разрядной информации;

ЗП8 - команда записи 8-ми разрядной информации;

ЗГБУФ2 - сигнал загрузки регистра РГБУФ2;

ЗГБУФ1 - сигнал загрузки регистра РГБУФ1;

СДВ8 - сдвиг на 8 разрядов;

СДВ16 - сдвиг на 16 разрядов;

ПРСТ - прием старшего полуслова;

ПРПС - прием младшего полуслова;

ПРБ - прием байта;

У32 - управление выдачей слова;

У16_1 - управление выдачей старшего полуслова;

У16_2 - управление выдачей младшего полуслова;

У8_1 - управление выдачей первого байта;

У8_2 - управление выдачей второго байта;

У8_3 - управление выдачей третьего байта;

У8_4 - управление выдачей четвертого байта;

У32_16 - управление выдачей слова/полуслова;

У 16_8 - управление выдачей полуслова/байта;

У32_16_8 - управление выдачей слова/полуслова/байта;

Бвых0-7 - первый байт выходной;

Бвых8-15 - второй байт выходной;

Бвых 16-23 - третий байт выходной;

Бвых24-31 - четвертый байт выходной;

Бвх0-7 - первый байт входной;

Бвх8-15 - второй байт входной;

Бвх 16-23 - третий байт входной;

Бвх24-31 - четвертый байт входной;

ДПР0-7 - первый байт приема из ЗУ в РОН;

ДПР8-15 - второй байт приема из ЗУ в РОН;

ДПР16-23 - третий байт приема из ЗУ в РОН;

ДПР24-31 - четвертый байт приема из ЗУ в РОН;

ШД0-7 - первый байт шины данных;

ШД8-15 - второй байт шины данных;

ШД16-23 - третий байт шины данных;

ШД24-31 - четвертый байт шины данных;

АДР1 - три младших разряда адреса (адрес байта);

АДР2 - два младших разряда адреса (адрес полуслова);

АДР4 - один младший разряд адреса (адрес слова);

WE - сигнал разрешения записи в память;

ОЕ1 - сигнал разрешения вывода информации 8-ми разрядного ЗУ;

СЕ1 - сигнал разрешения 8-ми разрядного ЗУ;

ОЕ2 - сигнал разрешения вывода информации 16-ти разрядного ЗУ;

СЕ2 - сигнал разрешения 16-ти разрядного ЗУ;

ОЕ4 - сигнал разрешения вывода информации 32-х разрядного ЗУ;

СЕ4 - сигнал разрешения 32-х разрядного ЗУ;

Элементы устройства преобразования информации имеют следующие связи:

Код операции (КОП) поступает на дешифратор кода операции (1), который связан с устройством управления приемом (4) сигналами ЗГ32, ЗГ16, ЗГ8, а с устройством управления выдачей (5) - сигналами ЗП32, ЗП16 и ЗП8, при этом все шесть сигналов поступают на формирователь обращений, в котором формируются сигналы для обращения к запоминающим устройствам, которые поступают на выход УПИ: сигнал записи WE, сигналы выбора микросхемы запоминающего устройства - ОЕ4, ОЕ2 и ОЕ1, сигналы обращения к ЗУ - СЕ4, СЕ2 и СЕ1, младшие разряды адреса - три разряда АДР1, два разряда АДР2, и один разряд АДР4.

Информация, предназначенная для записи в запоминающее устройство (ДВЫД) поступает на первый регистр буфера (2), который связан сигналами: Бвых0-7 со старшим (9), вторым средним (11) и младшим (12) выходными мультиплексорами; Бвых8-15 с первым средним (10) и младшим (12) выходными мультиплексорами; Бвых16-23 с вторым средним (10) и младшим (12) выходными мультиплексорами; Бвых24-31 с младшим выходным мультиплексором (12).

Четыре двунаправленных сигнала ШД0-7, ШД8-15, ШД16-23 и ШД24-31 соответственно поступают на старший (13), первый средний (14), второй средний (15) и младший (16) мультиплексоры приема и выдаются со старшего (9), первого среднего (10), второго среднего (11) и младшего (12) выходных мультиплексоров и связывают их с находящимися за пределами схемы тремя запоминающими устройствами.

Устройство управления выдачей (5) связано сигналом ЗГБУФ1 с первым регистром буфера (2), а семь сигналов управления выдачей поступают: У32 и У16_2 на первый элемент «ИЛИ» (6), при этом У32 дополнительно поступает на старший (9) и первый средний (10) выходные мультиплексоры; У161 и У8_2 на второй элемент «ИЛИ» (7), при этом У16_1 дополнительно поступает на второй средний выходной мультиплексор (11); У8_4 на третий элемент «ИЛИ» (8); У8_3 и У8_1 на младший выходной мультиплексор (12). Первый элемент «ИЛИ» (6) связан сигналом У32_16 со вторым средним выходным мультиплексором (11) и третьим элементом «ИЛИ» (8), который связан сигналом У32_16_8 с младшим выходным мультиплексором (12), на который также поступает сигнал У16_8 со второго элемента «ИЛИ» (7).

Устройство управления приемом (4) связано: сигналом ЗГБУФ2 со вторым регистром буфера (17); сигналами СДВ8, СДВ 16 и ПРСТ со старшим (13) и первым средним (14) мультиплексорами приема, при этом сигнал СДВ 8 дополнительно поступает на второй средний мультиплексор приема (15) на который также поступает сигнал ПРПС; сигналом ПРБ с младшим мультиплексором приема (16).

Старший (13), первый средний (14), второй средний (15) и младший (16) мультиплексоры приема связаны со вторым регистром буфера (17) сигналами Бвх0-7, Бвх8-15, Бвх16-23 и Бвх24-31 соответственно. Второй регистр буфера (17) генерирует выходные сигналы ДПР0-7, ДПР8-15, ДПР 16-23 и ДПР24-31, при этом: ДПР8-15 дополнительно поступает на МПРСТ (13); ДПР 16-23 дополнительно поступает на МПРСТ (13) и МПРСР1 (14); ДПР 24-31 дополнительно поступает на МПРСР1 (14) и МПРСР2 (15).

Принципы работы устройства преобразования информации.

В системе команд процессора операции чтения информации из ЗУ и записи информации в ЗУ определяются по коду операции (КОП).

В восьмиразрядном коде операции закодированы команды чтения или записи 32-х разрядных слов, 16-ти разрядных полуслов и 8-ми разрядных байт.

При выполнении указанных команд КОП поступает на УПИ и по коду операции на выходе ДШКОП (1) вырабатывается один из сигналов: загрузка 32-х слов (ЗГ32), загрузка 16-ти разрядных полуслов (ЗГ16), загрузка 8-ми разрядных байт (ЗГ8), запись 32-х разрядных слов (ЗП32), запись 16-ти разрядных полуслов (ЗП16) и запись 8-ми разрядных байт (ЗП8), при этом каждый из этих сигналов дополнительно поступает на ФОБР (3).

При выполнении команды загрузки 32-х разрядных слов в УУПР (4) по сигналу ЗГ32 формируются три сигнала: ПРСТ, ПРПС и ПРБ, которые открывают МПРСТ (13), МПРСР1 (14), МПРСР2 (15) и МПРМЛ (16) для приема входной информации с ШД0-7, ШД8-15, ШД16-23 и ШД24-31 соответственно. Далее информация, с помощью сигнала ЗГБУФ2, по сигналам Бвх0-7, Бвх8-15, Бвх16-23 и Бвх24-31 фиксируется в РГБУФ2 (17), который генерирует информационные сигналы ДПР0-7, ДПР8-15, ДПР 16-23, ДПР24-31, поступающие на выход УПИ.

Одновременно в ФОБР (3) формируются сигналы: АДР4 - один младший разряд адреса слова при загрузке слова и СЕ4, ОЕ4 - сигналы выбора 32-х разрядной микросхемы ЗУ.

При загрузке в один 32-х разрядный РОН сигналы АДР4, СЕ4 и ОЕ4 вырабатываются один раз.

При выполнении команды загрузки 16-ти разрядных слов в УУПР (4) по сигналу ЗГ16 формируются два сигнала: ПРПС и ПРБ, которые открывают МПРСР2 (15) и МПРМЛ (16) для приема входной информации с ШД16-23 и ШД24-31, которые несут в себе разряды 0-7 и 8-15 соответственно. Эта информация, с помощью сигнала ЗГБУФ2, по сигналам Бвх16-23 и Бвх24-31 фиксируется в РГБУФ2 (17), после чего формируются сигнал СДВ16, открывающий МПРСТ (13) и МПРСР1 (14) для приема информации с сигналов ДПР 16-23 и ДПР24-31 соответственно, в результате чего на них записываются разряды 0-7 и 8-15.

Далее повторно формируются сигналы ПРПС и ПРБ, с помощью которых повторяется цикл записи информации ШД16-23 и ШД24-31, по которым поступают разряды 16-23 и 24-31 соответственно.

В результате этих действий на МПРСТ (13), МПРСР1 (14), МПРСР2 (15) и МПРМЛ (16) фиксируется 32 разряда информации, которая сигналами Бвх0-7, Бвх8-15, Бвх16-23 и Бвх24-31, по сигналу ЗГБУФ2, передается в РГБУФ2, из которого на выход и УПИ поступает информация ДПР0-7, ДПР8-15, ДПР16-23, ДПР24-31.

Одновременно в ФОБР (3) формируются сигналы: АДР2 - два младших разряда адреса полуслова и СЕ2, ОЕ2 - сигналы выбора 16-ти разрядной микросхемы ЗУ.

При загрузке в один 32-х разрядный РОН сигналы АДР2, СЕ2 и ОЕ2 вырабатываются два раза.

При выполнении команды загрузки 8-ми разрядных слов в УУПР (4) по сигналу ЗГ8 формируется сигнал ПРБ, который открывает МПРМЛ (16) для приема входной информации с ШД24-31, которая несет в себе разряды 0-7. Эта информация, с помощью сигнала ЗГБУФ2, по сигналу Бвх24-31 фиксируется в РГБУФ2 (17), после чего формируются сигнал СДВ8, открывающий МПРСТ (13), МПРСР1 (14) и МПРСР2 (15) для приема информации с сигналов ДПР8-15, ДПР 16-23 и ДПР24-31 соответственно.

Таким образом разряды 0-7, по сигналу ДПР24-31, записывается в МПРСР2. Сигнал ПРБ вырабатывается повторно, что повторяет цикл записи информации ШД24-31, по которому во второй раз передаются разряды 8-15, с последующей генерацией сигнала СДВ 8, в результате чего разряды 0-7 перезаписываются в МПРСР1 (14), а разряды 8-15 в МПРСР2 (15).

В третий раз по сигналу ПРБ, принимаются разряды 16-23, которые по сигналу СДВ8 фиксируются в МПРСР2 (15), при этом разряды 0-7 и 8-15 записываются в МПРСТ (13) и МПРСР1 (14) соответственно.

В четвертый раз по сигналу ПРБ принимаются разряды 24-31, при этом сигнал СДВ8 не формируется.

Одновременно в ФОБР (3) формируются сигналы: АДР1 - четыре младших разряда адреса байта и СЕ1, ОЕ1 - сигналы выбора 8-ми разрядной микросхемы ЗУ.

При загрузке в один 32-х разрядный РОН сигналы АДР1, СЕ1 и ОЕ1 вырабатываются четыре раза.

При выполнении команды записи 32-х разрядных слов в УУВЫД (5) по сигналу ЗП32 формируется сигнал ЗГБУФ1, по которому 32-х разрядное слово ДВЫД параллельным кодом фиксируется в РГБУФ1, после чего в УУВЫД (5) формируется сигнал У32, на первом элементе «ИЛИ» (6) формируется сигнал У32_16 и на третьем элементе «ИЛИ» (8) формируется сигнал У32_16_8. В результате информация Бвых0-7, Бвых8-15, Бвых16-23, Бвых24-31 передается на входы ВыхМСТ (9) ВыхМСР1 (10), ВыхМСР2 (11) и ВыхММЛ (12) соответственно, которые передают информацию ШД0-7, ШД8-15, ШД16-23 и ШД24-31 соответственно на выход УПИ.

Одновременно в ФОБР (3) формируются сигналы: АДР4 - младший разряд адреса слова, WE - сигнал записи и СЕ4, ОЕ4 - сигналы выбора 32-х разрядной микросхемы ЗУ.

При записи из одного 32-х разрядного РОН сигналы АДР4, WE, СЕ4 и ОЕ4 вырабатываются один раз.

При выполнении команды записи 16-ти разрядных слов в УУВЫД (5) по сигналу ЗП16 формируется сигнал ЗГБУФ1, по которому 32-х разрядное слово ДВЫД параллельным кодом фиксируется в РГБУФ1, в УУВЫД (5) формируется сигнал У161 и на второй схеме «ИЛИ» (7) формируется сигнал У16_8 по которым информация Бвых0-7 на входе ВыхМСР2» (11) и информация Бвых8-15 на входе ВыхММЛ (12) передается на его выход, и параллельным кодом поступает на выход УПИ через ШД16-23 и ШД24-31.

Затем формируется сигнал У16_2, на первой схеме «ИЛИ» (6) формируется сигнал У32_16 и на третьей схеме «ИЛИ» (8) формируется сигнал У32_16_8 по которым информация Бвых16-23 на входе ВыхМСР2 (11) и информация Бвых24-31 на входе ВыхММЛ (12) передается на его выход, и параллельным кодом поступает на выход УПИ через ШД 16-23 и ШД24-31.

Одновременно в ФОБР (3) формируются сигналы: АДР2 - два младших разряда адреса полуслова, WE - сигнал записи и СЕ2, ОЕ2 - сигналы выбора 16-ти разрядной микросхемы ЗУ.

При записи из одного 32-х разрядного РОН сигналы АДР2, WE, СЕ2 и ОЕ2 вырабатываются два раза.

При выполнении команды записи 8-ми разрядных слов по сигналу ЗП8 в УУВЫД (5) формируется сигнал ЗГБУФ1, по которому 32-х разрядное слово ДВЫД параллельным кодом фиксируется в РГБУФ1, в УУВЫД (5) формируется сигнал У8_1 по которому информация Бвых0-7 на входе ВыхММЛ (12) передается на его выход, и параллельным кодом поступает на выход УПИ через ШД24-31.

Затем в УУВЫД (5) формируется сигнал У8_2 и на второй схеме «ИЛИ» (7) формируется сигнал У16_8, по которому информация Бвых8-15 на входе ВыхММЛ (12) передается на его выход, и параллельным кодом поступает на выход УПИ через ШД24-31.

В третий раз УУВЫД (5) формируется сигнал У8_3, по которому информация Бвых 16-23 на входе ВыхММЛ (12) п передается на его выход, и параллельным кодом поступает на выход УПИ через ШД24-31.

В четвертый раз УУВЫД (5) формируется сигнал У8_4 и на третьей схеме «ИЛИ» (8) формируется сигнал У32_16_8, по которому информация Бвых24-31 на входе ВыхММЛ (12) передается на его выход, и параллельным кодом поступает на выход УПИ через ШД24-31.

Одновременно в ФОБР (3) формируются сигналы: АДР1 - четыре младших разряда адреса байта, WE - сигнал записи и СЕ1, ОЕ1 - сигналы выбора 8-ми разрядной микросхемы ЗУ.

При записи из одного 32-х разрядного РОН сигналы АДР1, WE, СЕ1 и ОЕ1 вырабатываются четыре раза.

При аппаратной реализации указанных команд требуется:

- один обмен между 16-ти разрядным ЗУ и внутренней памятью процессора занимает ~ 4Тцп;

- один обмен между 8-ми разрядным ЗУ и внутренней памятью процессора занимает ~ 6Тцп.

Достоинства УПИ:

1. обеспечивает выполнение операций загрузки и записи информации из ЗУ различной разрядности в РОН и наоборот без использования дополнительных команд процессора.

2. позволяет сократить время выполнение операций обмена по сравнению с программной реализацией более чем в два раза:

- обмен с 16-ти разрядным ЗУ занимает 4Тцп (10Тцп без УПИ);

- обмен с 8-ми разрядным ЗУ занимает 6Тцп (18Тцп без УПИ).

Техническим результатом является устройство, обеспечивающее сокращение количества тактов процессора при загрузке данных между запоминающими устройствами различной разрядности и внутренней памятью процессора.

Таким образом, заявлено устройство преобразования информации, содержащее дешифратор кода операции (1) принимающий входной сигнал, определяющий команду процессора (КОП), и вырабатывающий 8 ми, 16 ти и 32х разрядные команды загрузки (ЗГ8, ЗГ16, ЗГ32) и записи (ЗП8, ЗП16, ЗП32) информации, из которых сигналы загрузки информации поступают на устройство управления приемом (УУПР) (4), а сигналы записи информации -на устройство управления выдачей (УУВЫД) (5), при этом все шесть команд поступают на формирователь обращений (3), из которого на выход устройства поступают сигналы: адреса байта (АДР1), полуслова (АДР2) и слова (АДР4), разрешения записи в память (WE), выбора (ОЕ1, ОЕ2, ОЕ4) и обращения (СЕ1, СЕ2, СЕ4) к запоминающим устройствам 8 ми, 16 ти и 32х разрядов; первый регистр буфера (2) принимающий входную 32х разрядную информацию для записи (ДВЫД) и сигнал собственной загрузки (ЗГБУФ1), поступающий из УУВЫД (4), вырабатывая четыре сигнала байт, из которых: первый (Бвых0-7) поступает на старший выходной мультиплексор (ВыхМСТ) (9), второй средний выходной мультиплексор (ВыхМСР2) (11) и младший выходной мультиплексор (ВыхММЛ) (12), второй (Бвых8-15) на первый средний выходной мультиплексор (ВыхМСР1) (10) и ВыхММЛ (12), третий (Бвых16-23) на ВыхМСР2 (11) и ВыхММЛ (12), четвертый (Бвых24-31) на ВыхММЛ (12); УУВЫД (5) вырабатывает семь сигналов управления выдачей, из которых: сигнал управления выдачей слова (УЗ2) поступает на ВыхМСТ (9), ВыхМСР1 (10) и, совместно с сигналом управления выдачей младшего полуслова (У16_2), на первый элемент ИЛИ (6), который вырабатывает сигнал управления выдачей слова/полу слова (У32_16), поступающий на ВыхМСР2 (11) и третий элемент ИЛИ (8), сигнал управления выдачей старшего полуслова (У16_1) поступает на ВыхМСР2 (11) и, совместно с сигналом управления выдачей второго байта (У8_2), на второй элемент ИЛИ (7), который вырабатывает сигнал управление выдачей полуслова/байта (У16_8), поступающий на ВыхММЛ (12), сигнал управления выдачей четвертого байта (У8_4) поступает на третий элемент ИЛИ (8), вырабатывающий сигнал управление выдачей слова/полуслова/байта (У32_16_8), который совместно с сигналами управления выдачей первого (У8_1) и третьего (У8_3) байта поступают на ВыхММЛ (12); первый (ШД0-7), второй (ШД8-15), третий (ШД16-23) и четвертый (ШД24-31) сигналы байт двунаправленной шины данных, которые поступают в устройство, где соответственно подключены к ВыхМСТ (9), ВыхМСР1 (10), ВыхМСР2 (11), ВыхММЛ (12) и старшему мультиплексору приема (МПРСТ) (13), первому среднему мультиплексору приема (МПРСР1) (14), второму среднему мультиплексору приема (МПРСР2) (15) и младшему мультиплексору приема (МПРМЛ) (16); МПРСТ (13), МПРСР1 (14), МПРСР2 (15) и МПРМЛ (16) подключены сигналами первый (Бвх0-7), второй (Бвх8-15), третий (Бвх16-23) и четвертый (Бвх24-31) входной байт соответственно, ко второму регистру буфера (17), который также принимает сигнал собственной загрузки (ЗГБУФ2), поступающий из УУПР (4) и вырабатывает четыре сигнала байт приема (ДПР0-7, ДПР8-15, ДПР 16-23, ДПР24-31), которые поступают на выход из устройства, из которых: второй (ДПР8-15) дополнительно поступает на МПРСТ (13), третий (ДПР 16-23) - на МПРСТ (13) и МПРСР1 (14), а четвертый (ДПР24-31) - на МПРСР1 (14) и МПРСР2 (15); УУПР (4) вырабатывающий сигналы: приема старшего полуслова (ПРСТ), сдвига на 8 (СДВ8) и на 16 (СДВ 16) разрядов поступающие на МПРСТ (13) и МПРСР1 (14), при этом сигнал сдвиг на 8 разрядов (СДВ8) дополнительно поступает на МПРСР2 (15), куда также поступает сигнал приема младшего полуслова (ПРПС), и сигнал прием байта (ПРБ) поступающий на МПРМЛ (16).

Устройство преобразования информации, содержащее дешифратор кода операции, принимающий входной сигнал, определяющий команду процессора, и вырабатывающий 8-, 16- и 32-разрядные команды загрузки и записи информации, из которых сигналы загрузки информации поступают на устройство управления приемом (УУПР), а сигналы записи информации - на устройство управления выдачей (УУВЫД), при этом все шесть команд поступают на формирователь обращений, из которого на выход устройства поступают сигналы: адреса байта, полуслова и слова, разрешения записи в память, выбора и обращения к запоминающим устройствам 8, 16 и 32 разрядов; первый регистр буфера, принимающий входную 32-разрядную информацию для записи и сигнал собственной загрузки, поступающий из УУВЫД, вырабатывая четыре сигнала байт, из которых: первый поступает на старший выходной мультиплексор (ВыхМСТ), второй средний выходной мультиплексор (ВыхМСР2) и младший выходной мультиплексор (ВыхММЛ), второй - на первый средний выходной мультиплексор (ВыхМСР1) и ВыхММЛ, третий - на ВыхМСР2 и ВыхММЛ, четвертый - на ВыхММЛ; УУВЫД вырабатывает семь сигналов управления выдачей, из которых: сигнал управления выдачей слова поступает на ВыхМСТ, ВыхМСР1 и, совместно с сигналом управления выдачей младшего полуслова, на первый элемент ИЛИ, который вырабатывает сигнал управления выдачей слова/полуслова, поступающий на ВыхМСР2 и третий элемент ИЛИ, сигнал управления выдачей старшего полуслова поступает на ВыхМСР2 и, совместно с сигналом управления выдачей второго байта, на второй элемент ИЛИ, который вырабатывает сигнал управления выдачей полуслова/байта, поступающий на ВыхММЛ, сигнал управления выдачей четвертого байта поступает на третий элемент ИЛИ, вырабатывающий сигнал управления выдачей слова/полуслова/байта, который совместно с сигналами управления выдачей первого и третьего байта поступают на ВыхММЛ; первый, второй, третий и четвертый сигналы байт двунаправленной шины данных, которые поступают в устройство, где соответственно подключены к ВыхМСТ, ВыхМСР1, ВыхМСР2, ВыхММЛ и старшему мультиплексору приема (МПРСТ), первому среднему мультиплексору приема (МПРСР1), второму среднему мультиплексору приема (МПРСР2) и младшему мультиплексору приема (МПРМЛ); МПРСТ, МПРСР1, МПРСР2 и МПРМЛ подключены сигналами первый, второй, третий и четвертый входной байт соответственно ко второму регистру буфера, который также принимает сигнал собственной загрузки, поступающий из УУПР, и вырабатывает четыре сигнала байт приема, которые поступают на выход из устройства, из которых: второй дополнительно поступает на МПРСТ, третий - на МПРСТ и МПРСР1, а четвертый - на МПРСР1 и МПРСР2; УУПР, вырабатывающий сигналы: приема старшего полуслова, сдвига на 8 и на 16 разрядов, поступающие на МПРСТ и МПРСР1, при этом сигнал сдвиг на 8 разрядов дополнительно поступает на МПРСР2, куда также поступает сигнал приема младшего полуслова, и сигнал прием байта, поступающий на МПРМЛ.