Результат интеллектуальной деятельности: СПОСОБ ПРОВЕДЕНИЯ ИСПЫТАНИЙ НА СТОЙКОСТЬ СЛОЖНОФУНКЦИОНАЛЬНЫХ МИКРОСХЕМ К СТАТИЧЕСКОМУ ДЕСТАБИЛИЗИРУЮЩЕМУ ВОЗДЕЙСТВИЮ

Вид РИД

Изобретение

Изобретение относится к испытательной технике и может быть использовано при проведении испытаний на стойкость различных видов сложнофункциональных микросхем, таких как большие интегральные схемы (БИС) и сверхбольшие интегральные схемы (СБИС), к статическим дестабилизирующим факторам, в том числе, к воздействию ионизирующих излучений.

Известен способ проведения испытаний на стойкость микросхем оперативно-запоминающих устройств (ОЗУ) к дестабилизирующему воздействию (ДВ) (патент RU №2438164, «Система функционального тестирования корпусированных микросхем оперативно запоминающих устройств", опубликован 27.12.2011), который заключается в проведении полного функционального контроля микросхем ОЗУ большой емкости с измерением тока энергопотребления при этом.

Основным недостатком известного способа является узкая специализация на проведении испытаний микросхем только одного вида. При этом из электрических параметров контролируется только ток потребления.

Известен также способ проведения испытаний на стойкость сложнофункциональных микросхем (БИС и СБИС) к статическому дестабилизирующему воздействию (патент RU №2485529, «Система для проведения испытаний на безотказность и электротермотренировки цифровых интегральных схем (ИС) и сверхбольших интегральных схем (СБИС)», опубликован 20.06.2013), при котором расширена номенклатура тестируемых микросхем. Этот способ позволяет проводить электротермотренировку и испытания микросхем на безотказность.

Известный способ заключается в следующем: до воздействия испытываемую микросхему (ИМ) устанавливают в испытательную оснастку, включают тестер и производят запуск управляющей программы, производят контроль контактирования выводов микросхемы с испытательной оснасткой, устанавливают испытательную оснастку в область воздействия дестабилизирующего фактора (камеру тепла) и задают требуемый температурный режим. Выполняется функциональное тестирование микросхемы с измерением тока потребления. Функциональное тестирование реализуется подачей (генерацией) тестовых векторов функционального контроля (ТВФК) на входы микросхемы и регистрацией ответных сигналов.

Затем, во время проведения испытаний, информируют оператора о результатах тестирования, а по окончании дестабилизирующего воздействия производят анализ полученных данных, по результатам которых делают заключение о стойкости микросхемы к дестабилизирующему воздействию.

Основным недостатком известного способа, принятого за прототип, является ограниченная область применения, в частности, при некоторых видах дестабилизирующих воздействий, невозможно избежать влияния дестабилизирующего фактора на близко расположенную КИА. В случаях применения пространственного разнесения КИА и объекта испытаний увеличение длины линий связи оказывает значительное влияние на результаты испытаний. Что не позволяет проводить испытания с приемлемым качеством получаемых результатов. В дополнение, отсутствие в прототипе методов оценки и компенсации условий проведения испытаний (до начала дестабилизирующего воздействия) дополнительно снижает качество результатов. Все это существенно сокращает перечень дестабилизирующих воздействий, при которых возможно проведение испытаний без заметного снижения качества результатов испытаний.

Кроме этого, при большой номенклатуре испытываемых изделий использование специализированных тестеров нецелесообразно, так как перенастройка КИА под конкретный типономинал ИМС занимает продолжительное время. Также, использование специализированных тестеров не позволяет оперативно вносить коррективы в процесс испытаний.

Задачей, решаемой данным способом, является проведение испытаний на стойкость различных видов сложнофункциональных микросхем к широкому перечню статических дестабилизирующих воздействий.

Техническим результатом настоящего изобретения является расширение функциональных возможностей способа за счет увеличения перечня дестабилизирующих воздействий. Кроме этого, учет и компенсация влияния условий проведения испытаний повышает качество результатов испытаний.

Другим техническим результатом, обеспечиваемым изобретением, является сокращение трудозатрат и времени на подготовку и проведение испытаний.

Технический результат изобретения обеспечивается тем, что в способе проведения испытаний на стойкость сложнофункциональных микросхем к статическому дестабилизирующему воздействию, при котором испытания проводят с использованием тестера, до воздействия испытываемую микросхему устанавливают в испытательную оснастку, производят конфигурирование тестера, производят контроль контактирования выводов испытываемой микросхемы с испытательной оснасткой, затем во время проведения испытаний производят дестабилизирующее воздействие, выполняют функциональное тестирование с измерением тока потребления испытываемой микросхемы и информируют оператора о результатах тестирования, по окончании дестабилизирующего воздействия производят анализ полученных данных, по результатам которых делают заключение о стойкости микросхемы к дестабилизирующему воздействию, новым является то, что в качестве тестера используют, по меньшей мере, один генератор-анализатор, причем количество генераторов-анализаторов определяется количеством необходимых для проведения параметрического контроля и функционального тестирования испытываемой микросхемы каналов ввода-вывода, при этом на этапе подготовки испытаний производят распределение тестовых векторов функционального тестирования (ТВФТ) по каналам генераторов в соответствии со схемой испытаний, на основе тестовых векторов функционального тестирования генерируют тестовые векторы параметрического контроля (ТВПК), до дестабилизирующего воздействия с целью проведения входного контроля и оценки влияния условий испытаний для каждой микросхемы, предоставленной на испытания, производят функциональное тестирование и параметрический контроль, включающий в себя измерение статических и динамических электрических параметров микросхемы, сначала в лабораторных условиях и затем в условиях, при которых будут проводиться испытания, причем на всех этапах подготовки и проведения испытаний производят параметрический контроль испытываемой микросхемы, для компенсации влияния условий испытаний постоянно учитывают падение напряжения на линиях электропитания испытываемой микросхемы, во время функционального тестирования и параметрического контроля применяют измененные с учетом длины информационных линий связи ТВФТ и ТВПК, а также для автоматической компенсации задержек сигналов в информационных линиях связи используют линию синхронизации.

Проведение испытаний без пространственного разнесения КИА и ИМ не дает возможности проводить испытания на ряд ДВ, так как в этих случаях невозможно избежать влияния дестабилизирующего фактора на близко расположенную КИА.

С увеличением расстояния между КИА и ИМ увеличивается влияние условий испытаний на получаемые результаты, что в некоторых случаях не позволяет проводить испытания с приемлемым качеством. Для учета и компенсации влияния условий испытаний в предлагаемом способе применен ряд мероприятий:

- оценка влияния испытательной оснастки;

- оценка и компенсация влияния линий связи.

Функциональное тестирование и измерение электрических параметров каждой ИМ, до дестабилизирующего воздействия, сначала в лабораторных условиях и затем в условиях, при которых будут проводиться испытания позволяет оценить влияние испытательной оснастки.

Учет падения напряжения на линиях электропитания ИМ, применение во время функционального тестирования измененных с учетом длины линий связи ТВФК, а также использование автоматической компенсации задержек сигналов с помощью цепи синхронизации позволяет снизить влияние длины линий связи.

Применение в предлагаемом способе одного или нескольких генераторов-анализаторов, в отличие от специализированного тестера в прототипе, позволяет оперативно перенастраивать КИА при смене ИМ. При этом количество применяемых генераторов-анализаторов определяется количеством необходимых для проведения функционального тестирования ИМ каналов ввода-вывода. Это дает возможность одновременного проведения испытаний нескольких образцов ИМ различных типономиналов. Что позволяет сократить трудозатраты и время на подготовку и проведение испытаний.

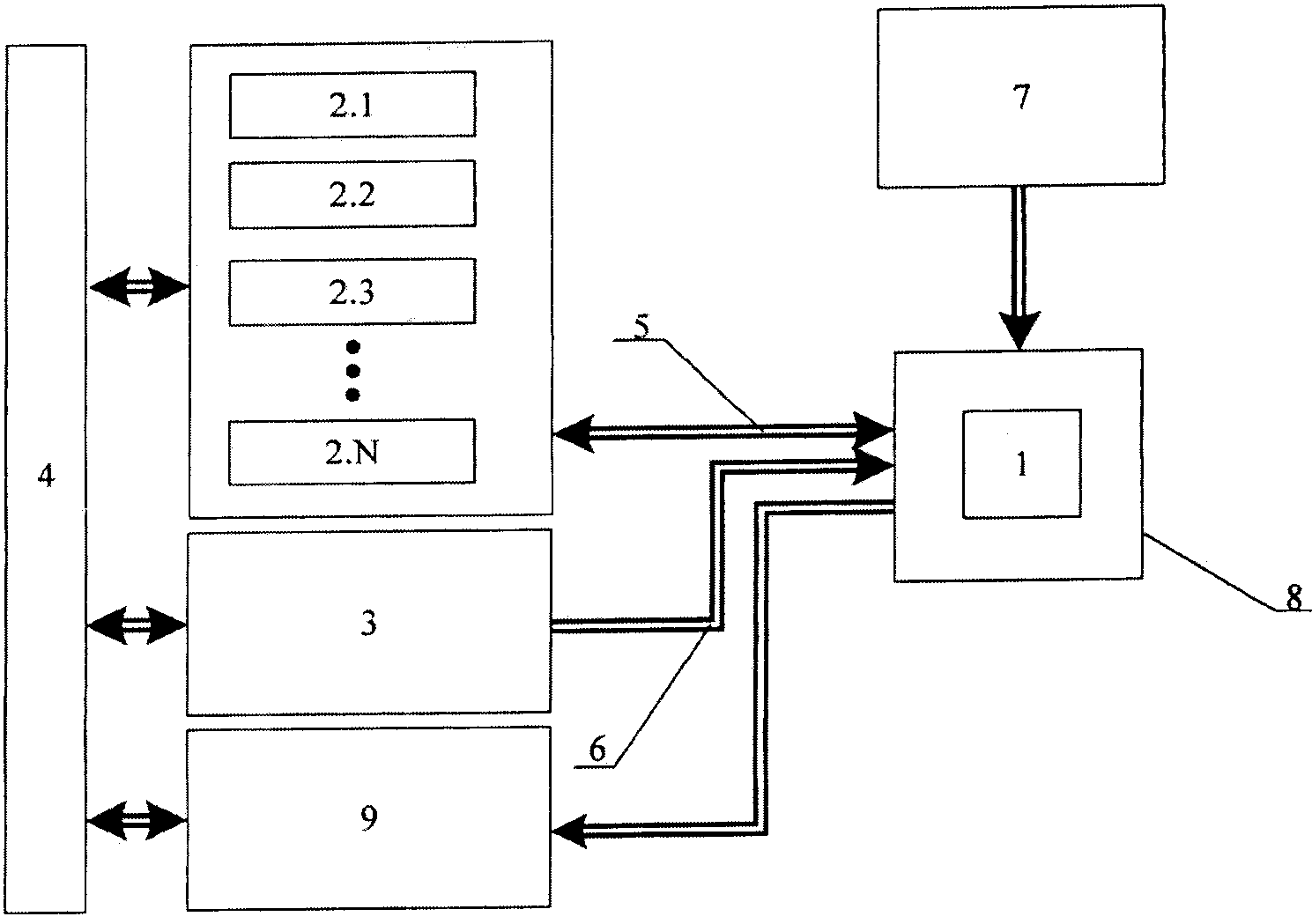

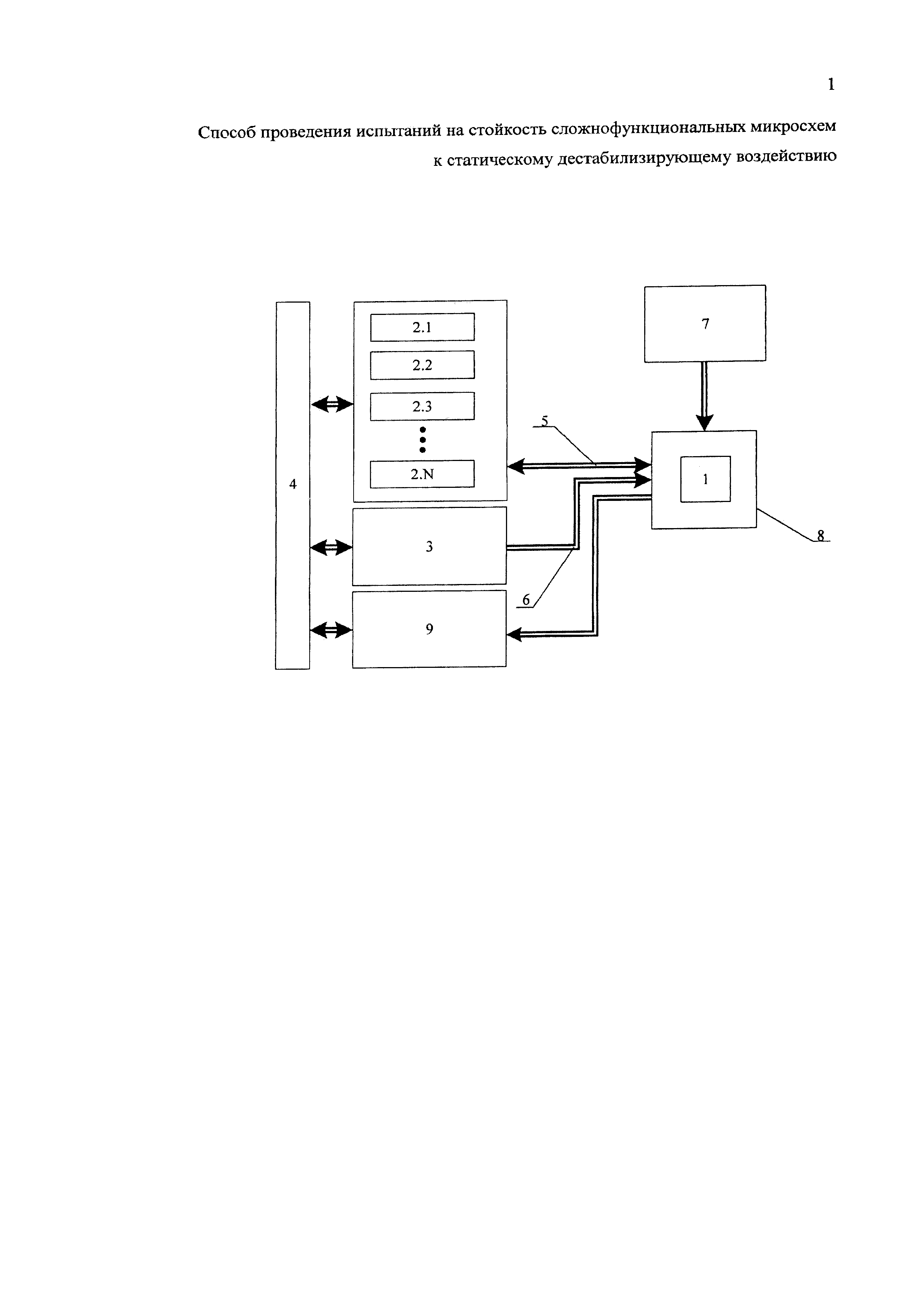

Сущность изобретения поясняется чертежами.

На фиг. показана структурная схема проведения испытаний на стойкость сложнофункциональных микросхем к статическому дестабилизирующему воздействию.

На фигурах введены обозначения:

1 - испытываемая микросхема (ИМ);

2.1, 2.2, 2.3, …, 2.n - генераторы-анализаторы (ГА);

3 - источник питания (ИП);

4 - блок согласования и управления (БСиУ);

5 - информационные линии связи (ИЛС);

6 - линии электропитания (ЛЭ);

7 - источник дестабилизирующего воздействия (ИДВ);

8 - испытательная оснастка (ИО);

9 - дополнительная контрольно-измерительная аппаратура (ДКИА).

Порядок выполнения операций предлагаемого способа проведения испытаний на радиационную стойкость в условиях статического воздействия ионизирующего излучения состоит в следующем:

1. Заказчик испытаний предоставляет партию микросхем и ТУ к ним.

2. Разрабатывается ИО, содержащая контактирующее устройство (КУ) под конкретный корпус ИМ, и обеспечивающая соединение выходов генераторов-анализаторов с выводами ИМ согласно схеме подключения, описанной в ТУ или разработанной для проведения испытаний.

3. Производится формирование ТВФТ и ТВПК.

3.1. Цифровые тестовые последовательности предоставляются заказчиком или разрабатываются на основе функционального назначения ИМ или данных из ТУ.

3.2. Цифровые тестовые последовательности разбиваются на необходимое количество генераторов-анализаторов, преобразуются в ТВФТ.

3.3. Производится сопоставление информационных вводов-выводов ИМ с соответствующими каналами генераторов согласно схеме подключения. Соответствующие изменения вносятся в ТВФТ.

3.4. На основе ТВФТ генерируется ТВПК для измерения статических и динамических электрических параметров, таких как выходные напряжения высокого и низкого уровней, ток потребления. Вектор имеет в своем составе точки остановки в которых производятся измерения статических электрических параметров.

4. Производится входной контроль микросхем, поступивших на испытания.

4.1. В лабораторных условиях собирается схема измерений согласно фиг. (за исключением ИДВ) с линиями связи (информационными и электропитания) не превышающими один метр.

4.2. Для каждой ИМ, предоставленной на испытания производится функциональное тестирование и параметрический контроль.

4.2.1. ИМ устанавливается в КУ.

4.2.2. При необходимости производится настройка параметров дополнительной контрольно-измерительной аппаратуры.

4.2.3. ТВФТ и ТВПК загружаются в память генераторов-анализаторов.

4.2.4. На ИМ подается номинальное значение напряжения питания.

4.2.5. На номинальной рабочей частоте ИМ запускается генерация ТВФТ с фиксацией ошибок функционирования.

4.2.6. После генерации всех ТВФТ запускается генерация ТВПК.

4.2.7. Производится измерение статических и динамических электрических параметров.

4.2.8. Полученные данные сохраняются.

5. Производится оценка влияния условий, при которых будут проводиться испытания.

5.1. Собирается схема измерений согласно фиг. в условиях, при которых будут проводиться испытания. ГА, ИП, БСиУ, ДКИА располагаются в измерительной комнате, обеспечивающей защиту от ДВ. ИО располагается в испытательном зале.

5.2. Для каждого генератора-анализатора, выход сигнала «начало генерации» соединяется с управляющим входом «начало приема данных» с использованием линии синхронизации (не показана на фиг.), Длина линии синхронизации равна сумме длин прямой и обратной ИЛС.

5.3. ИМ устанавливается в КУ.

5.4. Производится контроль контактирования ИМ с ИО.

5.5. Производится определение максимального времени гарантированного установления сигналов на информационных входах ИМ.

5.5.1. К ИЛС со стороны ИМ подключается осциллограф (на фиг. не показан).

5.5.2. С помощью генераторов-анализаторов подается тестовый сигнал. Тестовый сигнал представляет собой переход из состояния логического «нуля» в состояние логической «единицы» и обратно. Напряжения логических «нуля» и «единицы» соответствуют уровням ИМ, описанным в ТУ.

5.5.3. По зарегистрированным осциллограммам измеряется время гарантированного установления сигналов на информационных входах ИМ до стабильного логического уровня и определяется максимальное значение.

5.5.4. Осциллограф отключается от ИЛС.

5.6. Производится определение максимального времени гарантированного установления сигналов на входах генераторов-анализаторов.

5.6.1. К ИЛС со стороны генераторов-анализаторов подключается осциллограф.

5.6.2. Загружаются ТВФТ в память генераторов-анализаторов.

5.6.3. На ИМ подается номинальное значение напряжения питания.

5.6.4. Запускается генерация ТВФТ.

5.6.5. Осциллографом регистрируется форма сигналов, поступающих от ИМ.

5.6.6. По зарегистрированным осциллограммам измеряется время гарантированного установления сигналов на входах генераторов-анализаторов до стабильного логического уровня и определяется максимальное значение.

5.6.7. Осциллограф отключается от ИЛС.

5.7. Производится измерение омического сопротивления ЛЭ.

6. Компенсация условий проведения испытаний.

6.1. В ТВФТ и ТВПК вносятся изменения, компенсирующие влияние информационных линий связи. Для этого сигналы тактирования ИМ задерживаются относительно остальных управляющих сигналов. Время задержки равно максимальному времени гарантированного установления сигналов на информационных входах ИМ.

6.2. Согласно измеренному времени гарантированного установления сигналов на входах генераторов-анализаторов в настройках генераторов-анализаторов устанавливается параметр «задержки начала приема данных».

7. Функциональное тестирование и параметрический контроль испытываемой микросхемы в условиях, при которых будут проводиться испытания.

7.1. В память генераторов-анализаторов загружаются ТВФТ и ТВПК с учетом изменений, произведенных в п. 6.1.

7.2. При необходимости производится настройка параметров ДКИА.

7.3. На ИМ подается номинальное значение напряжения питания.

7.4. На номинальной рабочей частоте ИМ запускается генерация ТВФТ с регистрацией ответных сигналов и фиксацией ошибок функционирования.

7.5. После генерации всех ТВФТ запускается генерация ТВПК и производится измерение статических и динамических электрических параметров.

7.6. На основании заранее измеренного значения омического сопротивления ЛЭ и действующего значения тока потребления ИМ, во время генерации ТВФТ и ТВПК, циклически вычисляется падение напряжения, и вносится поправка в значение выходного напряжения ИП.

7.7. Полученные данные сравниваются с данными, полученными в лабораторных условиях, по результатам сравнения делается вывод о возможности проведения испытаний.

8. Проведение испытаний ИМ.

8.1. Собирается схема проведения испытаний согласно фиг.

8.2. ИМ устанавливается в КУ.

8.3. В память генераторов-анализаторов загружаются ТВФТ и ТВПК с учетом изменений, произведенных в п. 6.1.

8.4. На ИМ подается номинальное значение напряжения питания.

8.5. Начинается воспроизведение ДВ.

8.6. На номинальной рабочей частоте ИМ запускается генерация ТВФК с регистрацией ответных сигналов и фиксацией ошибок функционирования.

8.7. После генерации всех ТВФТ запускается генерация ТВПТ и измерение статических и динамических электрических параметров.

8.8. На основании заранее измеренного значения омического сопротивления ЛЭ и действующего значения тока потребления ИМ, во время генерации ТВФТ и ТВПК, циклически вычисляется падение напряжения, и вносится поправка в значение выходного напряжения ИП.

8.9. До окончания ДВ п.п. 8.6-8.7 циклически повторяют.

Способ был проверен на макете программно-технического комплекса (ПТК). Техническая реализация ПТК выполнена на генераторах-анализаторах NI PXIe-6556 и источнике питания NI PXI-4110. В качестве БСиУ использовалось шасси NI PXIe-1085 с управляющим контроллером NI PXIe-8135, время гарантированного установления сигналов измерялось осциллографом LeCroy WJ-354A, источником дестабилизирующего воздействия служил реактор ВИР-2М работающий в статическом режиме.

В качестве информационных линий связи использовалась витая пара с волновым сопротивлением 100 Ом. Линия электропитания представляла собой коаксиальный кабель волновым сопротивлением 75 Ом. Длина линий связи (информационных и электропитания) составляла 40 м, при этом омическое сопротивление линии электропитания равнялось 4 Ом.

Проверка способа проводилась на образцах микросхем базового матричного кристалла (БМК) 5535 и 5511. Параметрами, определяющими радиационную стойкость образцов БМК, служили:

- отсутствие ошибок при проведении функционального тестирования;

- значение тока потребления;

- значение выходного напряжения высокого уровня;

- значение выходного напряжения низкого уровня.

Каждый образец БМК содержал 240 выводов, из них 133 используется для функционального тестирования, 58 используется для электропитания, остальные 49 выводов не задействованы. Для обеспечения необходимого количества каналов ввода-вывода при проведении функционального тестирования использовалось 6 генераторов-анализаторов, имеющих по 24 канала ввода-вывода в каждом.

Номинальное напряжение питания для ядра и периферии БМК составляло 3,3 В и задавалось отдельными каналами источника питания NI PXI-4110. Во время проведения параметрического контроля напряжение питания ядра и периферии в автоматическом режиме изменялось до предельно допустимых по ТУ, что составило 3,63 В при измерении выходного напряжения низкого уровня и 2,97 В при измерении выходного напряжения высокого уровня.

Для проведения функционального тестирования заказчик предоставил 24 цифровых тестовых последовательности. На основе каждой из них были сформированы ТВФТ. Для параметрического контроля на их основе сформирован ТВПК.

Мероприятия по оценке и компенсации условий проведения испытаний позволили провести измерения параметров, определяющих радиационную стойкость, с использованием существующих на реакторе ВИР-2М линий связи при рабочей частоте БМК 16 МГц.

Во время эксперимента, микросхемы БМК облучались до уровней стойкости, указанных в ТУ. В процессе облучения циклически производилось функциональное тестирование и параметрический контроль, кроме этого, на основании заранее измеренного значения омического сопротивления линий электропитания и действующего значения тока потребления, вносилась поправка в значение выходного напряжения источника питания для поддержания напряжения на образце БМК на постоянном уровне.

На всем протяжении эксперимента значение параметров, определяющих радиационную стойкость, записывались в текстовый файл для последующего анализа.

В случае если во время облучения хотя бы один из параметров, определяющих радиационную стойкость, выходил за установленные в ТУ пределы, микросхема отбраковывалась как нестойкая.

Способ проведения испытаний на стойкость сложнофункциональных микросхем к статическому дестабилизирующему воздействию, при котором испытания проводят с использованием тестера, до воздействия испытываемую микросхему устанавливают в испытательную оснастку, производят конфигурирование тестера, производят контроль контактирования выводов испытываемой микросхемы с испытательной оснасткой, затем во время проведения испытаний производят дестабилизирующее воздействие, выполняют функциональное тестирование с измерением тока потребления испытываемой микросхемы и информируют оператора о результатах тестирования, по окончании дестабилизирующего воздействия производят анализ полученных данных, по результатам которых делают заключение о стойкости микросхемы к дестабилизирующему воздействию, отличающийся тем, что в качестве тестера используют по меньшей мере один генератор-анализатор, причем количество генераторов-анализаторов определяется количеством необходимых для проведения параметрического контроля и функционального тестирования испытываемой микросхемы каналов ввода-вывода, при этом на этапе подготовки испытаний производят распределение тестовых векторов функционального тестирования по каналам генераторов в соответствии со схемой испытаний, на основе тестовых векторов функционального тестирования генерируют тестовые векторы параметрического контроля, до дестабилизирующего воздействия с целью проведения входного контроля и оценки влияния условий испытаний для каждой микросхемы, предоставленной на испытания, производят функциональное тестирование и параметрический контроль, включающий в себя измерение статических и динамических электрических параметров микросхемы, сначала в лабораторных условиях и затем в условиях, при которых будут проводиться испытания, причем на всех этапах подготовки и проведения испытаний производят параметрический контроль испытываемой микросхемы, для компенсации влияния условий испытаний постоянно учитывают падение напряжения на линиях электропитания испытываемой микросхемы, во время функционального тестирования и параметрического контроля применяют измененные с учетом длины информационных линий связи тестовые векторы функционального тестирования и тестовые векторы параметрического контроля, а также для автоматической компенсации задержек сигналов в информационных линиях связи используют линию синхронизации.